(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4672281号

(P4672281)

(45) 発行日 平成23年4月20日(2011.4.20)

(24) 登録日 平成23年1月28日(2011.1.28)

(51) Int.Cl.

G06F 12/14 (2006.01)

F 1

G06F 12/14 510E

請求項の数 28 外国語出願 (全 21 頁)

(21) 出願番号 特願2004-134539 (P2004-134539)

(22) 出願日 平成16年4月28日 (2004.4.28)

(65) 公開番号 特開2004-334870 (P2004-334870A)

(43) 公開日 平成16年11月25日 (2004.11.25)

審査請求日 平成19年4月23日 (2007.4.23)

(31) 優先権主張番号 60/467,343

(32) 優先日 平成15年5月2日 (2003.5.2)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 10/610,666

(32) 優先日 平成15年6月30日 (2003.6.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 500046438

マイクロソフト コーポレーション

アメリカ合衆国 ワシントン州 9805

2-6399 レッドmond ワン マイ

クロソフト ウェイ

(74) 代理人 100077481

弁理士 谷 義一

(74) 代理人 100088915

弁理士 阿部 和夫

(72) 発明者 マーカス ペイナード

アメリカ合衆国 98008 ワシントン

州 ベルビュー ノースイースト 168

アベニュー 7

最終頁に続く

(54) 【発明の名称】最適化を用いたメモリアクセス制御の実装

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリアクセス要求を処理する方法を実施するためのコンピュータ実行可能命令を符号化したコンピュータ読み取り可能な記録媒体であって、前記方法は、

メモリの一部にアクセスするための要求を受け取るステップであって、前記要求は、アドレス変換マップを介して変換可能な識別子によって、アクセスされる前記メモリの一部を識別する、受け取るステップと、

前記アドレス変換マップに関するキャッシュ済み情報に基づいて、前記要求の実行が、前記メモリへのアクセスを制限するポリシーに違反することになるかどうかを判定するステップであって、前記キャッシュ済み情報は、前記アドレス変換マップの、所定のプロパティを有するページの集合を識別するデータを含む、判定するステップと、

前記要求の実行が前記ポリシーに違反しない場合は、前記要求に従って前記メモリへのアクセスを可能にするステップと、

前記要求の実行が前記ポリシーに違反する場合は、

前記要求を阻止すること、または、

前記要求を前記ポリシーに違反しないように修正して、前記修正した要求を実行すること

のどちらかを実施するステップと

を備え、

前記キャッシュ済み情報は、前記アドレス変換マップ中の、前記アドレス変換マップの

10

20

ルートから所定距離にあるページの集合を識別するデータを含む

ことを特徴とするコンピュータ読み取り可能な記録媒体。

**【請求項 2】**

前記要求は、前記メモリの前記一部に書き込む要求を含む

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 3】**

前記アドレス変換マップは前記メモリに記憶され、前記要求は、前記アドレス変換マップが記憶されたメモリの一部に書き込む要求を含む

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 4】**

前記キャッシュ済み情報は、指定のページへの参照の数を示すデータを含む

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 5】**

前記キャッシュ済み情報は、指定のページへの参照の数を示すデータを含み、前記参照は指定の属性を有する

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 6】**

前記キャッシュ済み情報は、前記アドレス変換マップ中の指定のページが参照するページの数を示すデータを含む

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 7】**

前記キャッシュ済み情報は、前記アドレス変換マップ中の指定のページが参照する、また、前記指定のページが指定の属性を割り当てるページの数を示すデータを含む

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 8】**

前記ポリシーへの適合は、集合中のページのメンバシップに基づいて判定され、前記キャッシュ済み情報は、前記集合の適切な上位集合を含み、前記要求の実行が前記ポリシーに違反することになるかどうかを判定する前記動作は、前記ページが前記上位集合のメンバかどうかを評価することを含む

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 9】**

前記ポリシーへの適合は、集合中のページのメンバシップに基づいて判定され、前記キャッシュ済み情報は、前記集合の適切な部分集合を含み、前記要求の実行が前記ポリシーに違反することになるかどうかを判定する前記動作は、前記ページが前記部分集合のメンバかどうかを評価することを含む

ことを特徴とする請求項 1 に記載のコンピュータ読み取り可能な記録媒体。

**【請求項 10】**

アドレス変換マップを介してアクセスが提供されるコンピュータメモリを管理する方法であって、

前記アドレス変換マップの状態の少なくとも 1 つの態様に関する情報を記憶するステップであって、前記記憶済み情報は、前記アドレス変換マップの、所定のプロパティを有するページの集合を識別するデータを含む、記憶するステップと、

前記コンピュータメモリにアクセスするための要求を受け取るステップと、

前記記憶済み情報に少なくとも部分的に基づいて、前記要求の実行が、前記コンピュータメモリへのアクセスを制限するポリシーに違反することにならないと判定するステップと、

前記要求の実行を可能にするステップと、

前記要求の実行から生じる前記アドレス変換マップの状態を反映するように、前記記憶済み情報を更新するステップと

を備え、

10

20

30

40

50

前記記憶済み情報は、前記アドレス変換マップ中の、前記アドレス変換マップのルートから所定距離にあるページの集合を識別するデータを含む

ことを特徴とする方法。

**【請求項 1 1】**

前記要求は、前記コンピュータメモリの一部に書き込む要求を含む

ことを特徴とする請求項1 0に記載の方法。

**【請求項 1 2】**

前記アドレス変換マップは前記メモリに記憶され、前記要求は、前記アドレス変換マップが記憶されたメモリの一部に書き込む要求を含む

ことを特徴とする請求項1 0に記載の方法。 10

**【請求項 1 3】**

前記記憶済み情報は、指定のページへの参照の数を示すデータを含む

ことを特徴とする請求項1 0に記載の方法。

**【請求項 1 4】**

前記記憶済み情報は、指定のページへの参照の数を示すデータを含み、前記参照は指定の属性を有する

ことを特徴とする請求項1 0に記載の方法。 15

**【請求項 1 5】**

前記記憶済み情報は、前記アドレス変換マップ中の指定のページが参照するページの数を示すデータを含む

ことを特徴とする請求項1 0に記載の方法。 20

**【請求項 1 6】**

前記記憶済み情報は、前記アドレス変換マップ中の指定のページが参照する、また、前記指定のページが指定の属性を割り当てるページの数を示すデータを含む

ことを特徴とする請求項1 0に記載の方法。 25

**【請求項 1 7】**

前記ポリシーへの適合は、集合中のページのメンバシップに基づいて判定され、前記記憶済み情報は、前記集合の適切な上位集合を含み、前記要求の実行が前記ポリシーに違反することにならないと判定する前記動作は、前記ページが前記上位集合のメンバかどうかを評価することを含む

ことを特徴とする請求項1 0に記載の方法。 30

**【請求項 1 8】**

前記ポリシーへの適合は、集合中のページのメンバシップに基づいて判定され、前記記憶済み情報は、前記集合の適切な部分集合を含み、前記要求の実行が前記ポリシーに違反することにならないと判定する前記動作は、前記ページが前記部分集合のメンバかどうかを評価することを含む

ことを特徴とする請求項1 0に記載の方法。 35

**【請求項 1 9】**

アドレス変換マップによってアドレス指定されるメモリへのアクセスを制御するためのシステムであって、

前記メモリへのアクセスを制限するポリシーを記憶する1つまたは複数の記憶位置と、 40

前記アドレス変換マップに関する情報を記憶するキャッシュであって、前記キャッシュに記憶された情報は、前記アドレス変換マップの、所定のプロパティを有するページの集合を識別するデータを含む、キャッシュと、

前記メモリにアクセスするための要求を受け取り、前記キャッシュに記憶された前記情報に少なくとも部分的に基づいて、前記要求が前記ポリシーの下で許可できるかどうかを判定する論理とを備え、

前記論理は、前記要求が前記ポリシーの下で許可できると判定された場合は、前記要求の続行を可能にし、前記要求が前記ポリシーの下で許可できないと判定された場合は、(1)前記要求を阻止すること、または、(2)前記要求を前記ポリシーの下で許可できる

40

50

形に修正して、前記修正した要求の続行を可能にすること、のどちらかを実施し、

前記キャッシュに記憶された情報は、前記アドレス変換マップ中の、前記アドレス変換マップのルートから所定距離にあるページの集合を識別するデータを含む

ことを特徴とするシステム。

【請求項 2 0】

前記要求は、前記メモリの一部に書き込む要求を含む

ことを特徴とする請求項1 9に記載のシステム。

【請求項 2 1】

前記アドレス変換マップは前記メモリに記憶され、前記要求は、前記アドレス変換マップが記憶されたメモリの一部に書き込む要求を含む

ことを特徴とする請求項1 9に記載のシステム。 10

【請求項 2 2】

前記キャッシュに記憶された情報は、指定のページへの参照の数を示すデータを含む

ことを特徴とする請求項1 9に記載のシステム。

【請求項 2 3】

前記キャッシュに記憶された情報は、指定のページへの参照の数を示すデータを含み、

前記参照は指定の属性を有する

ことを特徴とする請求項1 9に記載のシステム。

【請求項 2 4】

前記キャッシュに記憶された情報は、前記アドレス変換マップ中の指定のページが参照するページの数を示すデータを含む

ことを特徴とする請求項1 9に記載のシステム。 20

【請求項 2 5】

前記キャッシュに記憶された情報は、前記アドレス変換マップ中の指定のページが参照する、また、前記指定のページが指定の属性を割り当てるページの数を示すデータを含む

ことを特徴とする請求項1 9に記載のシステム。

【請求項 2 6】

前記ポリシーへの適合は、集合中のページのメンバシップに基づいて判定され、前記キャッシュに記憶された情報は、前記集合の適切な上位集合を含み、前記論理は、前記ページが前記上位集合のメンバかどうかを評価することによって、前記要求を許可することが前記ポリシーに違反することになるかどうかを判定する

ことを特徴とする請求項1 9に記載のシステム。 30

【請求項 2 7】

前記ポリシーへの適合は、集合中のページのメンバシップに基づいて判定され、前記キャッシュに記憶された情報は、前記集合の適切な部分集合を含み、前記論理は、前記ページが前記部分集合のメンバかどうかを評価することによって、前記要求を許可することが前記ポリシーに違反することになるかどうかを判定する

ことを特徴とする請求項1 9に記載のシステム。

【請求項 2 8】

前記論理はハードウェアとソフトウェアのうちの少なくとも一方において実現される

ことを特徴とする請求項1 9に記載のシステム。 40

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は一般に、コンピュータセキュリティの分野に関する。より詳細には、本発明は、アドレス変換制御を用いて隔離 (isolated) または「遮蔽 (curtained)」メモリを実現するための効率的な技法に関する。

【背景技術】

【0 0 0 2】

ある状況では、メモリには、アクセスが制限される部分である隔離されたまたは「遮蔽

50

」された部分があることが望ましい。例えば、あるコンピュータが2つのオペレーティングシステムを並行して稼動させているが、一方のオペレーティングシステムは安全であり、他方はそうではない場合がある。この場合、安全なオペレーティングシステムは、安全でないオペレーティングシステムからアクセスできない秘密情報を記憶することのできる遮蔽メモリを有することが望ましい。

#### 【0003】

遮蔽メモリを実現する方法の1つは、アドレス変換制御による方法である。近年の多くのコンピュータは仮想メモリシステムを使用しており、仮想メモリシステムでは、コンピュータ上で稼動するソフトウェアは仮想アドレスを使用してメモリのアドレスを指定し、メモリ管理ユニットが、1組のアドレス変換マップを使用して仮想アドレスを物理アドレスに変換する。通常、各プロセスはそれ自体のアドレス変換マップを有し、したがって、仮想アドレスと物理アドレスとの間のマッピングはプロセスごとに変化する。所与のプロセスのアドレス変換マップは、物理メモリの所与のブロック（例えばページ）用の仮想アドレスをプロセスに露呈しないように構成することが可能である。このように、安全なプロセスだけが物理メモリの所与のブロックについての仮想アドレスを有するようにすることにより、アドレス変換マップの内容を制御して遮蔽メモリを実現することが可能である。

#### 【0004】

このような機構を使用して遮蔽メモリを実現するときに生じる問題の1つは、アドレス変換マップがメモリに記憶されているので、どんなメモリ書き込み動作もマップに影響を与える可能性があり、それにより遮蔽メモリ用の仮想アドレスが、遮蔽メモリにアクセスできるべきでないプロセスに露呈する恐れがあることである。このような仮想アドレスが露呈しないようにする方法の1つは、メモリ書き込み動作が実施されるたびに、あらゆるマップのあらゆる要素をチェックして、遮蔽メモリにアクセスできるべきでないプロセスのマップ中に仮想アドレスがあるような遮蔽メモリページがないことを確実にすることである。しかし、書き込み動作の頻度を考えると、この技法は非効率的である。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0005】

従来のシステムには上述したような種々の問題があり、従来技術の欠点を克服する機構が必要とされており、さらなる改善が望まれている。

#### 【0006】

本発明は、このような状況に鑑みてなされたもので、その目的とするところは、アドレス変換マップの変更を効率的に制御するための、最適化を用いたメモリアクセス制御の実装を提供することにある。

##### 【課題を解決するための手段】

#### 【0007】

本発明は、アドレス変換マップの変更を効率的に制御するための機構を提供する。アドレス変換マップの状態が、遮蔽メモリへのアクセスを許可されないプロセス（またはその他のエンティティ）に対して遮蔽メモリのブロックについての仮想アドレスが露呈する状態に入らないようにすることによって、遮蔽メモリを実現することができる。「ポリシー」が、どんなメモリアクセス動作が許可されるかを定義し、メモリアクセス制御システムが、アドレス変換マップがいずれかのポリシーに違反する状態に入るのを禁じることによって動作する。

#### 【0008】

このような仮想アドレスが露呈することになる状態は、しばしば、一定のプロパティを満たす複数の集合の共通部分（または非共通部分）に基づいて、あるいは一定のプロパティを満たすページの数に基づいて定義することができる。定義された集合のメンバであるページの識別を記憶またはキャッシュすることができ、したがって、アドレス変換マップの状態を変更する可能性のある書き込み動作が実施されるたびに集合のメンバシップを計算

10

20

30

40

50

する必要はない。集合中のページの識別は、例えばビットベクトルとして記憶することができ、このようなビットベクトルに対して和や共通部分などの集合演算を効率的に実施することができる。特定のプロパティを満たす正確な集合を計算するのが難しい場合もあり得るが、何らかの明確な部分集合または上位集合を実際の集合の代わりとして使用することによってポリシーへの適合を保証することは、数学的に証明可能とすることができる。実際の集合よりも部分集合または上位集合の方が相対的に計算しやすい場合は、実際の集合の代わりに部分集合または上位集合を使用することができる。

#### 【0009】

さらに、いくつかの書き込み動作の許可は、何らかの統計のカウント、例えば一定のプロパティを満たすページの数や所与のページへの参照の数などの点から定義することができる。このような統計は、参照カウンタとして効果的に記憶またはキャッシュすることができ、増分または減分動作によって更新することができる。ビットベクトルまたはカウンタは、マップが状態を変更するたびに更新することができ、次いで、これらを効率的に使用して、ポリシーの下でのメモリアクセス動作を評価することができる。

10

#### 【0010】

本発明のその他の特徴については後述する。

#### 【0011】

前述の概要、ならびに後続の好適実施形態の詳細な説明は、添付の図面と共に読めばよりよく理解される。本発明を例示するために、図面には本発明の例示的な構造を示す。ただし本発明は、開示する特定の方法および手段に限定されるわけではない。

20

#### 【発明を実施するための最良の形態】

#### 【0012】

以下、図面を参照して本発明を適用できる実施形態を詳細に説明する。

##### 例示的なコンピューティング構成

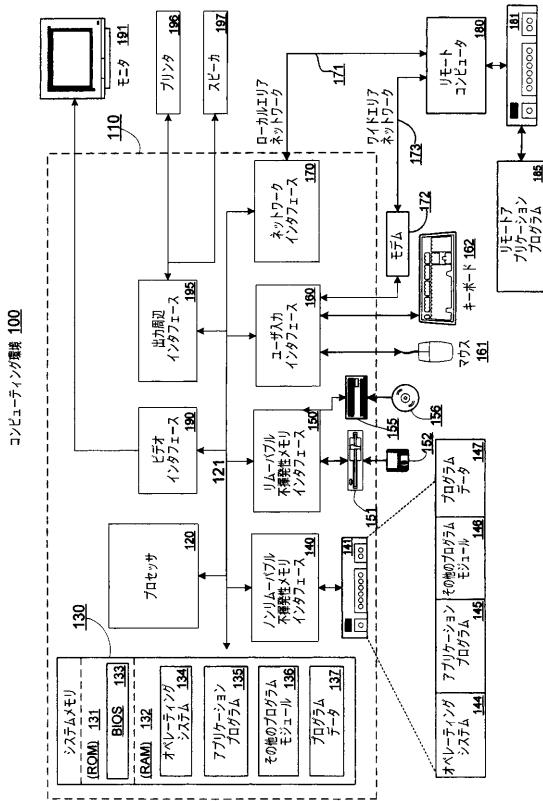

図1に、本発明の態様を実施することのできる例示的なコンピューティング環境を示す。コンピューティングシステム環境100は、適したコンピューティング環境の一例にすぎず、本発明の使用または機能の範囲についてどんな制限も意味しない。またコンピューティング環境100は、この例示的な動作環境のコンピューティングシステム環境100に示すコンポーネントのいずれか1つまたは組合せに関してどんな依存も要件も有するものと解釈すべきではない。

30

#### 【0013】

本発明は、その他多くの汎用または専用コンピューティングシステム環境または構成でも動作する。本発明で使用するのに適するであろう周知のコンピューティングシステム、環境、および/または構成の例には、限定しないがパーソナルコンピュータ、サーバコンピュータ、ハンドヘルドデバイスまたはラップトップデバイス、マルチプロセッサシステム、マイクロプロセッサベースのシステム、セットトップボックス、プログラム可能な家庭用電化製品、ネットワークPC(personal computer)、ミニコンピュータ、メインフレームコンピュータ、組込みシステムや、これらのシステムまたはデバイスのいずれかを含む分散コンピューティング環境などが含まれる。

#### 【0014】

本発明は、プログラムモジュールなど、コンピュータによって実行されるコンピュータ実行可能命令の一般的な状況で述べることができる。一般にプログラムモジュールは、特定のタスクを実施するか特定の抽象データ型を実装するルーチン、プログラム、オブジェクト、コンポーネント、データ構造などを含む。本発明は分散コンピューティング環境で実施することもでき、その場合、タスクは通信ネットワークまたはその他のデータ伝送媒体を介してリンクされたリモート処理デバイスによって実施される。分散コンピューティング環境では、プログラムモジュールおよびその他のデータは、メモリ記憶デバイスを含めたローカルとリモートの両方のコンピュータ記憶媒体に位置することができる。

40

#### 【0015】

図1を参照すると、本発明を実施するための例示的なシステムは、コンピュータ110

50

の形の汎用コンピューティングデバイスを含む。コンピュータ110のコンポーネントには、限定しないがプロセッサ120と、システムメモリ130と、システムメモリを含めた様々なシステムコンポーネントをプロセッサ120に結合するシステムバス121とを含めることができる。システムバス121は、様々なバスアーキテクチャのいずれかを用いた、メモリバスまたはメモリコントローラ、周辺機器バス、ローカルバスを含めて、いくつかのタイプのバス構造のいずれかとすることができます。限定ではなく例として、このようなアーキテクチャには、ISA(Industry Standard Architecture)バス、MCA(Micro Channel Architecture)バス、EISA(Enhanced ISA)バス、VESA(Video Electronics Standards Association)ローカルバス、およびPCI(Peripheral Component Interconnects)バス(メザニンバスとも呼ばれる)が含まれる。10

#### 【0016】

コンピュータ110は通常、様々なコンピュータ可読媒体を備える。コンピュータ可読媒体は、コンピュータ110からアクセスできる任意の利用可能な媒体とすることができます、揮発性と不揮発性媒体、リムーバブルとノンリムーバブル媒体の両方が含まれる。限定ではなく例として、コンピュータ可読媒体には、コンピュータ記憶媒体および通信媒体を含めることができます。コンピュータ記憶媒体には、コンピュータ可読命令、データ構造、プログラムモジュール、その他のデータなどの情報を記憶するための任意の方法または技術で実現された、揮発性と不揮発性、リムーバブルとノンリムーバブルの両方の媒体が含まれる。コンピュータ記憶媒体には、限定しないがRAM、ROM、EEPROM(Electrically Erasable and Programmable Read Only Memory)、フラッシュメモリまたは他のメモリ技術、CD(compact disc)ROM、DVD(Digital Versatile Disc)または他の光ディスク記憶装置、磁気カセット、磁気テープ、磁気ディスク記憶装置または他の磁気記憶デバイスが含まれ、あるいは、所望の情報を記憶するのに使用できコンピュータ110からアクセスできるその他の任意の媒体が含まれる。通信媒体は通常、搬送波や他の移送機構などの変調データ信号中に、コンピュータ可読命令、データ構造、プログラムモジュール、またはその他のデータを組み入れたものであり、任意の情報送達媒体が含まれる。「変調データ信号」という語は、情報が信号中に符号化される形で1つまたは複数の特性が設定または変更された信号を意味する。限定ではなく例として、通信媒体には、有線ネットワークや直接配線接続などの有線媒体と、音響、無線周波、赤外線、その他の無線媒体などの無線媒体とが含まれる。以上の任意の組合せもコンピュータ可読媒体の範囲に含めるべきである。20

#### 【0017】

システムメモリ130は、読み取り専用メモリ(ROM)131やランダムアクセスメモリ(RAM)132など、揮発性および/または不揮発性メモリの形のコンピュータ記憶媒体を含む。ROM131には通常、起動中などにコンピュータ110内の要素間で情報を転送するのを助ける基本ルーチンを含むBIOS(basic input/output system)133が記憶されている。RAM132は通常、プロセッサ120がすぐにアクセス可能な、かつ/またはプロセッサ120によって現在操作されているデータおよび/またはプログラムモジュールを含む。限定ではなく例として、図1には、オペレーティングシステム134、アプリケーションプログラム135、その他のプログラムモジュール136、およびプログラムデータ137を示す。30

#### 【0018】

コンピュータ110は、その他のリムーバブル/ノンリムーバブル、揮発性/不揮発性コンピュータ記憶媒体を備えることもできる。例にすぎないが図1には、ノンリムーバブルかつ不揮発性の磁気媒体に対して読み書きするハードディスクドライブ141と、リムーバブルかつ不揮発性の磁気ディスク152に対して読み書きする磁気ディスクドライブ151と、CD-ROMや他の光媒体などリムーバブルかつ不揮発性の光ディスク156に対して読み書きする光ディスクドライブ155を示す。この例示的な動作環境で使用でき40

るその他のリムーバブル／ノンリムーバブル、揮発性／不揮発性コンピュータ記憶媒体には、限定しないが磁気テープカセット、フラッシュメモリカード、DVD、デジタルビデオテープ、ソリッドステートRAM、ソリッドステートROMなどが含まれる。ハードディスクドライブ141は通常、インターフェース140などの不揮発性メモリインターフェースを介してシステムバス121に接続され、磁気ディスクドライブ151および光ディスクドライブ155は通常、インターフェース150などのリムーバブルメモリインターフェースでシステムバス121に接続される。

#### 【0019】

以上に論じ図1に示した各ドライブおよびそれらに関連するコンピュータ記憶媒体は、コンピュータ可読命令、データ構造、プログラムモジュール、およびその他のデータの記憶域をコンピュータ110に提供する。例えば図1には、ハードディスクドライブ141がオペレーティングシステム144、アプリケーションプログラム145、その他のプログラムモジュール146、およびプログラムデータ147を記憶しているのが示されている。これらのコンポーネントは、オペレーティングシステム134、アプリケーションプログラム135、その他のプログラムモジュール136、およびプログラムデータ137と同じものとすることもでき、異なるものとすることもできることに留意されたい。ここでは、オペレーティングシステム144、アプリケーションプログラム145、他のプログラムモジュール146、およびプログラムデータ147が少なくとも異なるコピーであることを示すために、異なる番号を付してある。ユーザは、キーボード162、マウスやトラックボールやタッチパッドと一般に呼ばれるポインティングデバイス161などの入力デバイスを介して、コンピュータ110にコマンドおよび情報を入力することができる。その他の入力デバイス（図示せず）には、マイクロホン、ジョイスティック、ゲームパッド、衛星放送受信アンテナ、スキャナなどを含めることができる。これらおよび他の入力デバイスは、システムバスに結合されたユーザ入力インターフェース160を介してプロセッサ120に接続されることが多いが、パラレルポート、ゲームポート、ユニバーサルシリアルバス（「USB」）など、他のインターフェースおよびバス構造で接続されてもよい。モニタ191または他のタイプの表示デバイスもまた、ビデオインターフェース190などのインターフェースを介してシステムバス121に接続される。モニタに加えて、コンピュータは通常、スピーカ197やプリンタ196など他の周辺出力デバイスも備えることができ、これらは出力周辺インターフェース195を介して接続することができる。

#### 【0020】

コンピュータ110は、リモートコンピュータ180など1つまたは複数のリモートコンピュータへの論理接続を用いて、ネットワーク化された環境で動作することができる。リモートコンピュータ180は、パーソナルコンピュータ、サーバ、ルータ、ネットワークPC、ピアデバイス、またはその他の一般的なネットワークノードとすることができます、図1にはメモリ記憶デバイス181しか示していないが、通常はパーソナルコンピュータ110に関して上述した要素の多くまたはすべてを備える。図1に示す論理接続は、ローカルエリアネットワーク（LAN）171およびワイドエリアネットワーク（WAN）173を含むが、他のネットワークを含むこともできる。このようなネットワーキング環境は、オフィス、企業全体のコンピュータネットワーク、インターネット、およびインターネットでよくみられるものである。

#### 【0021】

コンピュータ110は、LANネットワーキング環境で使用されるときは、ネットワークインターフェースまたはアダプタ170を介してLAN171に接続される。WANネットワーキング環境で使用されるときは通常、インターネットなどのWAN173を介した通信を確立するためのモデム172または他の手段を備える。モデム172は内蔵でも外付けでもよく、ユーザ入力インターフェース160または他の適切な機構を介してシステムバス121に接続することができる。ネットワーク化された環境では、コンピュータ110に関して示したプログラムモジュールまたはその一部をリモートのメモリ記憶デバイス

10

20

30

40

50

に記憶することができる。限定ではなく例として、図1には、リモートアプリケーションプログラム185がメモリデバイス181上にあるものとして示す。図示のネットワーク接続は例示的なものであり、コンピュータ間に通信リンクを確立する他の手段を使用することもできることは理解されるであろう。

【0022】

アドレス変換を用いたメモリアクセス

コンピュータシステム中のメモリ（例えば図1に示したRAM132）は、各バイトごとに物理アドレスを有する。したがって、メモリを構成するバイトには番号が付いていると見なすことができ、各バイトはその番号で明確に識別することができる。この場合、番号は物理アドレスを構成する。例えば、256バイトのメモリでは、バイトは0から $2^8 - 1$ の範囲の物理アドレスを有することができる。しかし、近年のコンピュータシステムでは、メモリは一般に、その物理アドレスでアクセスされるのではなく仮想アドレスでアクセスされる。アドレス変換マップを使用して、物理アドレスが仮想アドレスに変換される。

10

【0023】

図2に、アドレス変換マップの例と、実際のコンピュータシステムにおけるその使用を示す。図2に示す例示的なアドレス変換マップは「ページング」方式であり、メモリは「ページ」と呼ばれるブロック単位で割り当てられる。図2は、INTEL（登録商標）×86プロセッサ上で使用されるページング方式を表す。

20

【0024】

図2では、ページディレクトリ202が、ページテーブル204（1）、204（2）、204（3）などのページテーブルへの一連のポインタ（すなわちページテーブルの物理ベースアドレス）を含む。各ページテーブルは、ページ（例えばページ206（1）、206（2）、206（3）、206（4））のベースアドレスへの一連のポインタを含み、さらに後述するように、読み取り専用/読み書き可能属性や存在/非存在ビットなどの情報も含むことができる。ページは、RAM132の固定長の部分である。さらに、通常はページディレクトリおよびページテーブルもRAM132に記憶される。図2に示すページング方式は2レベルのページング方式である。というのは、特定のページを突き止めるにはページディレクトリ（レベル1）とページテーブル（レベル2）の両方を通過する必要があるからである。当業者には理解されるであろうが、任意のレベル数のページング方式を設計することが可能であり、本発明はこのようなすべてのページング方式に適用される。また、INTEL（登録商標）×86プロセッサは通常、図2に示す2レベルのページング方式を使用することが当技術分野で知られているが、1レベルまたは3レベルのページング方式を使用するように構成することもできる。

30

【0025】

図2のページング方式では、ページ上のどのバイトも仮想アドレス210で識別することができ、仮想アドレス210は、ページディレクトリ（PD）オフセット211、ページテーブル（PT）オフセット212、およびページオフセット213を含む。したがって、物理アドレスを突き止めるためには、メモリ管理ユニット（MMU）220が、ページディレクトリオフセット211を使用して、ページディレクトリ202中の特定のエントリを突き止める。このエントリはページテーブルの物理ベースアドレスであり、したがってMMU220は、このアドレスをデリファレンスして、ページテーブルのうちの1つ（例えばページテーブル204（1））を突き止める。次いでMMU220は、識別されたページテーブル中の索引としてページテーブルオフセット212を使用し、このオフセットで見つかったエントリを取り出す。このエントリはページ（例えばページ206（1））の物理ベースアドレスであり、したがってMMUは、識別されたページのベースアドレスにページオフセット213を加えて、物理メモリの特定のバイトを突き止める。図3に関して後述するが、MMU220はまた、ページが読み取り専用としてマークされているか読み書き可能としてマークされているか、ページが存在としてマークされているか非存在としてマークされているかなどの情報を考慮するように構成することもできる。

40

50

## 【0026】

図2のページング方式は、ページディレクトリへのポインタを含む記憶位置201も含む。MMU220は、仮想アドレス210の変換を開始すると、このポインタを使用してページディレクトリ202を突き止める。INTEL（登録商標）×86プロセッサの例では、記憶位置201は、CR3という名前のレジスタに対応する。すなわち、INTEL（登録商標）×86プロセッサ上では、レジスタCR3は、現在のコンテキストにおけるページディレクトリの物理アドレスを記憶する。したがって、変換テーブルの代替セット（すなわちページディレクトリとページテーブルの複数のセット）を構築することが可能であり、新しいページディレクトリのベースアドレスを記憶位置201に書き込むだけで、変換テーブルのどのセットが適用されるかを変更することが可能である。この技法の一般的な使用法の1つは、コンピュータ上で稼動している各プロセスがそれ自体のページディレクトリおよびページテーブルを有することであり、新しいプロセスのページディレクトリのベースアドレスを記憶位置201に書き込むことによって、「コンテキスト切替え」（すなわちとりわけ、仮想メモリシステムが新しいプロセスのアドレス空間をポイントするようにする操作）が実施される。各プロセスがそれ自体のページディレクトリを有する場合、現在稼動しているプロセスの識別が、記憶位置201にどの値がロードされるかを決定する。10

## 【0027】

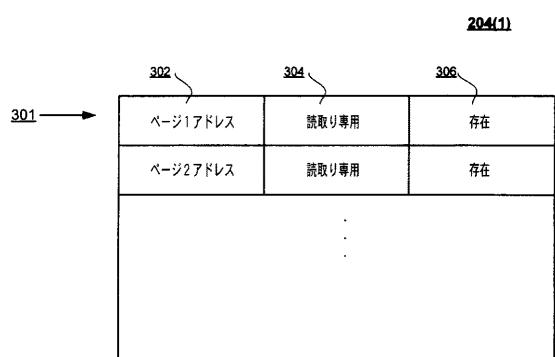

ページへのポインタを含むことに加えて、ページテーブルおよびページディレクトリはまた、ページについて「属性」を含むこともできる。図3に例示的なページテーブル204（1）の詳細を示すが、これはポインタと属性の両方を含んでいる。ページテーブル204（1）中の各エントリは、特定のページのアドレス302と、エントリによってポイントされるページが「読み取り専用」かどうかを示すビット304と、エントリによってポイントされるページが「存在」するかどうかを示すビット306とを含む。したがって、ページテーブル204（1）中の第1のエントリ301がページ206（1）（図2に示す）をポイントする場合、ビット304は、0にセットされているか1にセットされているかに応じて、MMU220（図2に示す）がページ206（1）の読み取りと書き込みの両方を許容すべきか、読み取りだけを許容すべきかを示す。同様に、ビット306は、ページ206（1）がメモリ中に存在するか否かを示す。（例えばページ206（1）の内容がディスクに移動されて、メモリ中に他のページのための空きができた場合、ビット306を0にセットして非存在を示すことができる。）その他の属性をページテーブル204（1）に記憶することもできる。20

## 【0028】

アドレス変換マップをメモリアクセス制御に使用する

仮想アドレスでメモリにアクセスするシステムでは、以下の観察に基づいてメモリへのアクセスを制限するシステムを実現することが可能である。すなわち、所与の物理アドレスに変換される仮想アドレスがないようにアドレス変換マップが構成された場合、この物理アドレスで表されるメモリにはアクセス不可能である。例えば、図2に関して上述したページング方式で、メモリの所与のページ（例えばページ206（1））は、マップを介してこのページに至るパスがないようにすることによって、アクセス不可能にすることができる。このようなパスがない場合、このページに変換される仮想アドレス210はないことになる。すべてのメモリアクセスが仮想アドレスによって行われるシステムでは、アドレス変換マップに対する制御を実施して、メモリの所与のページ（または他の部分）に仮想アドレスを与えないことにより、このメモリ部分は実質的にアクセス不可能になる。メモリに対してある物理アドレス指定が可能なシステムであっても、物理アドレスに基づくアクセス要求に対する制御で、アドレス変換マップに対する制御を補うことにより、メモリをアクセス不可能にすることができる。40

## 【0029】

アドレス変換マップの内容を制御してメモリへのアクセスを制御する技法は、正式には次のように述べることができる。メモリにアクセスできる可能性のあるソースの集合をS50

とする。さらに、どのソースがどのメモリ部分にアクセスできるかを定義するポリシーを  $P$  とする。したがって、 $s \in S$  がソースである場合、 $MP(s)$  は、アドレス変換マップを介してソース  $s$  からアクセス可能なメモリ部分（例えば仮想アドレスを有するメモリ位置の集合）を表し、 $NA(P, s)$  は、ポリシー  $P$  の下でソース  $s$  からのアクセスが許可されないメモリ部分を表す。（各プロセスがそれ自体のアドレス変換マップを有する場合、各プロセスは異なる「ソース」と見なすことができる。ただしソースの概念はプロセスの例にとどまらず一般化されることは理解されるであろう。）したがって、ポリシーの施行は、以下の条件が満たされる限り保証することができる。

$NA(P, s) \cap MP(s) = \emptyset$

【0030】

10

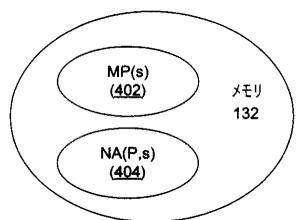

この条件を図4に示す。図4には、メモリ位置の集合であるメモリ132と、アドレス変換マッピングを介してソース  $s$  から見えるメモリ位置の集合である  $MP(s)$  402と、ポリシー  $P$  の下でソース  $s$  からのアクセスが許可されないメモリ位置の集合である  $NA(P, s)$  404が示されている。ソース  $s$  がアドレス変換マッピングを介してアドレス指定できる位置 ( $MP(s)$ ) はどれも、ソース  $s$  がポリシー  $P$  の下でアクセス許可されないメモリ位置の集合には含まれないので、図4に示す条件は、ソース  $s$  に関してポリシー  $P$  を効果的に施行する。

【0031】

したがって、ソース  $s$  からメモリ132の部分へのアクセスを制御する問題は、いくつかの例示的な状況では、図4に示す条件が常に真であるようにすることに還元することができる。この問題に対する解決法の1つは、アドレス変換マッピングを変更する可能性のある任意の動作（例えばメモリ書き込みやCR3レジスタのロードなど）、ポリシー、または現在のソースを評価することである。本発明は、このような評価を効率的に実施できるようにする技法を提供する。

20

【0032】

図4に示す条件は、メモリアクセス制御を実施するのに使用することのできる条件の例にすぎないことは理解されるであろう。図4の主題に対する他の変形も可能であり、例えば、アドレス変換マップに含まれるメモリ位置の集合や、ソース  $s$  からのアクセスは許可されるが書き込み（または読み取り）は許可されないメモリ位置の集合などを含む変形が可能である。ただし、メモリアクセス制御に関する条件は一般に、複数のメモリ位置集合が交差しないことの検証を含むことに留意されたい。

30

【0033】

さらに、 $MP(s)$  は、ソース  $s$  から見える「マッピングされるページ」と見なすことができるが、メモリアクセス制御の概念は、ページング方式を採用するシステムに限定されないことに留意されたい。典型的な実装形態では、ポリシーの下でソースがどのメモリ位置に書き込むことができるか、またはどのメモリ位置がソースにマッピングされるかの決定は、ページごとに行われる。ただし本発明は、メモリがページごとに割り振られる場合、またはメモリへのアクセスがページごとに許可または制約される場合に限定されない。

【0034】

40

#### アドレス変換に関する一般化モデル

図2に示すとともに上述したアドレス変換マップは、ラベル付き有向グラフのモデルを使用して一般化することができる。以下、いくつかのタイプのアドレス変換マップに関する一般化モデルについて述べる。

【0035】

このモデルでは、 $B$  はベース集合であり、 $L$  は英字である。所与の  $B$  および  $L$  について、 $G = (V, E)$  はエッジラベル付き有向グラフであり、 $V \subseteq B$ 、および  $E \subseteq \{(v, w, l) : v \in V, w \in V, l \in L\}$  である。 $E$  のメンバはどれも、ラベル  $l$  の付いた、頂点  $v$  から頂点  $w$  への有向エッジと解釈することができる。頂点にもラベル付けすることができる。

50

## 【0036】

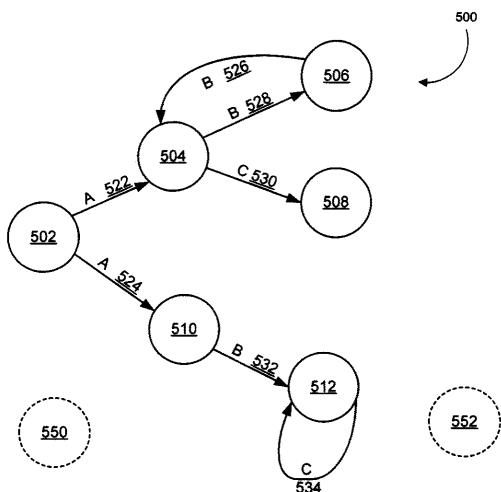

図5に、前述のモデルに従ったグラフを示す。グラフ500は、頂点502、504、506、508、510、512を含む。これらの頂点は、図示のようにしてエッジ522、524、526、528、530、532、534で接続されている。各エッジは、英字からの記号でラベル付けされている。この例では、英字は記号A、B、Cを含む。したがって、エッジ522および524は記号Aでラベル付けされ、エッジ526、528、532は記号Bでラベル付けされ、エッジ530および534は記号Cでラベル付けされている。グラフ500には、頂点ではないベース集合の要素（例えば要素550および552）がある場合もある。

## 【0037】

グラフ500の構成要素は、図2に示したアドレス変換マップのいくつかの構成要素に対応することを理解されたい。例えば図2で、ページディレクトリ202、ページテーブル204(1)～204(3)、およびページ206(1)～206(4)は、グラフ中の頂点と見なすことができる。これらの頂点を接続するポインタ（例えばページテーブル204(1)中のエントリからページ206(1)および206(2)へのポインタ）は、グラフ中のエッジと見なすことができる。また図3に関して、エントリの属性304および306（例えば読み取り専用ビットや存在ビット）は、エッジのラベルと見なすことができる。したがって、「英字」は、可能な属性順列の集合である（2つの2進数属性がある図3の例では、4つの可能な組合せがあり、したがって英字には4つの記号がある）。属性が使用されない場合は、英字は「n i l」記号からなるものとすることができます。さらに、割り振られないメモリページは、入来エッジを有さないベース集合メンバに対応する。

10

## 【0038】

前述のようなグラフのモデル内では、「状態」を定義することが可能である。所与のBおよびLについて、「状態」は( $R, G$ )の対であり、ここでGは、上に定義したラベル付き有向グラフであり、 $R \cup V$ は、Gの頂点の集合である。 $R$ は、「ルート頂点」の集合を表す。ルート頂点は、グラフのルートとして正当に働くことのできる、ベース集合中の頂点の集合を表す。図2の例では、正当なページディレクトリの集合（すなわち、INTEL（登録商標）×86プロセッサ上のCR3レジスタなどの記憶位置201にロードすることが許可されたそれらの値）が、「ルート頂点」の集合である。所与のBおよびLについて、すべての状態の集合はSである。

20

## 【0039】

上に定義したモデルに従って、アドレス変換機構(ATM)を以下のようにモデル化することができる。

- 頂点のベース集合B

- 英字L（空の場合もある）

- 初期状態 $s_0 \in S$ （Sは状態）

- 状態遷移規則のセット（空の場合もある）

- アドレス変換関数

- グローバルフラグ

30

## 【0040】

状態遷移規則は、ATMがある状態から別の状態に変更する。したがって、状態遷移規則のセット $r_i : S \rightarrow S$ （iは何らかの指標）を定義することが可能であり、これはATMの現在状態を変更する。ATMは、以下のタイプの遷移規則のいずれかを有することができる。

- Gのエッジの変更（追加、削除、再ラベル付け）

- Gの頂点の追加または削除

- ルート集合Rの変更

40

## 【0041】

例えば図2および3の例では、ページへのポインタを削除すること、またはページの属

50

性を変更することは、グラフのエッジの変更に対応する。新しいページディレクトリ、新しいページテーブル、または新しいデータページを追加することは、頂点の追加または削除に対応する。記憶位置 201 ( 例えばレジスタ C R 3 ) にロードすることのできるベースアドレスを有する新しいページディレクトリを定義することは、ルート集合の変更に対応する。本質的に、現在状態は、アドレス変換によってどのメモリ位置にアクセスできる可能性があるかを定義する。

#### 【 0 0 4 2 】

前述のように、ポリシーの下でソースからのアクセスが許容されないメモリ部分についてのどんな仮想アドレスもソースに露呈しないように、アドレス変換マップに対して制限条件を課すことによって、メモリへのアクセスを制御することができる。さらに、前述のように、条件の真偽に影響を与える可能性のある動作が実施されたとき、これらの条件が継続的に存在することを評価することができる。このメモリアクセス制御技法に対する考え方の 1 つは、A T M の正当な状態が  $S$  の何らかの部分集合  $T$  に限定されること、または現在状態に関する何らかのプロパティ ( または述語 )  $P$  が常に真でなければならないことである。

#### 【 0 0 4 3 】

何らかのプロパティ  $P$  ( 前述のポリシー  $P$  とは異なる ) がある場合に、状態を  $s$  から  $r_i(s)$  に変更する可能性のあるアクション ( 何らかの  $i$  の場合の  $r_i$  の実行 ) を実施するための要求を評価して、 $P(r_i(s))$  が真であるかどうか、すなわち、 $r_i$  を実行することによって生じる新しい ( 提案 ) 状態がプロパティ  $P$  を有することになるかどうかを判定することができる。  $P$  が真であることが、メモリアクセスに対する制限に違反しないことを意味する場合、 $P(r_i(s))$  が真であることは、 $r_i$  を実行することによって生じる状態変更を続行できるべきであることを意味する。そうでない場合は、この動作は続行できるべきではない。

#### 【 0 0 4 4 】

あらゆるメモリ書き込みは A T M の状態を変更する可能性があることがわかるはずである。したがって、以下の 2 つのことがわかるはずである。

- アルゴリズムは、場合によっては頻繁に、 $P(s)$  を計算しなければならない。

- 通常、新しい状態  $s'$  は古い状態  $s$  から派生する。古い状態がプロパティ  $P$  を有していた場合は、 $P(s)$  を仮定し、 $s'$  を生み出した  $s$  に対する変更 ( 有限数 ) が  $P$  の違反につながるかどうかを分析するだけで、 $P(s')$  を決定する複雑さを低減することができる場合がある。

#### 【 0 0 4 5 】

本発明は、 $P$  の真偽を効率的に計算できるようにする技法を提供する。前述のように、多くの場合、この効率は、A T M の現在状態を表す何らかの情報を記憶 ( またはキャッシュ ) することによって達成することができ、この情報を後で使用して、状態遷移の下における  $P$  の真偽を確認するためにどんなテストを実施する必要があるか、およびどのテストを回避することができるかを決定することができる。

#### 【 0 0 4 6 】

##### 例示的なプロパティの種類

プロパティ  $P$  のタイプの 1 つは、頂点の集合で表すことができるプロパティである。例えば、図 4 に示すとともに上に論じた条件は、本質的に、集合  $M P(s)$  と  $N A(P, s)$  が相互に交差しないプロパティである。頂点の集合およびこれらの集合間の関係で表すことのできる多くのプロパティは、集合中の頂点の識別を記憶 ( またはキャッシュ ) することによって効率的に実装することができる。

#### 【 0 0 4 7 】

A T M の状態がメモリアクセス制御条件を満たす状態にあるかどうかを評価する際に有用な集合の例を、以下に挙げる。

#### 【 0 0 4 8 】

1. ルート頂点から距離  $k$  にある頂点の集合。より正式には、頂点の集合を  $S$  とし、あ

10

20

30

40

50

る頂点を  $w$  とした場合、 $d_k(S, w)$  は、 $S$  中の何らかの頂点から頂点  $w$  までに距離  $k$  の（有向）パスがあることのステートメントを表す。 $S_d = \{v \in V : d_k(S, v)\}$  である。この場合、 $S$  がルート頂点である場合、 $S_d$  は、ルートから距離  $d$  にあるページの集合を指す。例えば、頂点 502 がグラフ 500 のルートである場合、ルート頂点から距離 1 にある頂点の集合は、頂点 504 および 510 からなる。というのは、これらの頂点はどちらも、1 つのエッジを横断することによってルートから到達することができるからである。図 2 に示したページマップを参照すると、ページディレクトリ 202 は、ルートからの距離 1 であり、ページテーブル 204(1) から 204(3) は、ルートからの距離 2 である。したがって図 2 の例では、ページディレクトリおよびページテーブルのアドレスは、ルートからの距離がそれぞれ 1 および 2 であるページの識別を記憶することによって、キャッシュすることができる。

#### 【0049】

2. エッジラベルによって判定される集合。例えば図 5 を参照すると、ラベル「A」の付いた入エッジを有する頂点の集合は、頂点 504 および 510 からなり、ラベル「B」の付いた入エッジを有する頂点の集合は、頂点 504、506、512 からなる。図 2 のページマップでは、属性がエッジラベルに対応し、所与の属性を有するページとして集合を定義することができる。例えば、読み取り専用としてマークされたページの集合を定義（およびキャッシュ）するのが有用なことがあるが、この場合、読み取り専用ビット（図 3 に示した参照番号 304）が「オン」になっているページの集合を定義することができる。（1 つのページがページマップ中で複数回にわたって参照されることもあり得るが、その場合、ページへの異なる参照は、それらの読み取り専用属性が個別にセットされているものとすることができる。この場合、集合の定義は競合を解決することができる。例えば、ページへの少なくとも 1 つの参照が読み取り専用属性を有する場合や、ページへのあらゆる参照が読み取り専用属性を有する場合などに、ページは集合に含まれる。）

ローカルプロパティと非ローカルプロパティとの間に区別を設けることができる。ローカルプロパティは、所与の頂点に入射するエッジから計算することができる。すなわち、頂点  $v$  がプロパティ  $P$  を有するかどうかを、 $v$  に入射するエッジだけから決定することができる場合、 $P$  はローカルであると言う。そうでない場合は、 $P$  は非ローカルである。ローカルプロパティの例は、「読み書き可能とラベル付けされた入エッジを頂点が有する」である。非ローカルプロパティの例は、「ページ（ $\times 86$  マシン上の）が読み書き可能マッピングを有する」である。

#### 【0050】

3. 何らかのプロパティを有する  $k$  個のエッジのターゲットである頂点の集合。より正式には、 $P$ 、 $Q$  を述語とし、 $w$  を頂点として、以下のように定められる。

$\text{In-degree}_{P, Q}(w) = |\{v \in V : P(v) \text{ および } (v, w, 1) \in E \text{ および } Q(1)\}|$

#### 【0051】

所与の入次数（in-degree）を有する頂点の集合として集合を定義することができる。

$\{v \in V : \text{In-degree}_{P, Q}(v) = k\}$

#### 【0052】

同様に、不等式に基づいて集合を定義することもできる。例えば、何らかのプロパティを有する  $k$  個よりも多い（または少ない）エッジのターゲットである頂点の集合を定義することができる。

#### 【0053】

例えば図 5 を参照すると、「C」のラベルが付いた少なくとも 1 つの入エッジを有する頂点の集合は、頂点 508 および 512 からなる。図 2 のページマップを参照すると、このタイプの集合定義を使用して、いくつかのカテゴリのページをキャッシュすることができる。例えば、複数のマッピングを有するページの集合や、ちょうど 1 つの読み出し専用マッピングを有するページの集合などである。

#### 【0054】

10

20

30

40

50

4. 同様の集合を、出次数 (out-degree) に基づいて定義することもできる。すなわち、何らかのプロパティを備える  $k$  個の出エッジ (または  $k$  個よりも多い出エッジか、  $k$  個よりも少ない出エッジ) を有する頂点の集合である。例えば図 5 を参照すると、「A」のラベルが付いたちょうど 2 つの出エッジを有する頂点の集合は、頂点 502 からなる。図 2 も類似の例を含む。例えば、少なくとも 3 つの出エッジ (他のページへの参照) を有するページの集合は、ページディレクトリ 202 を含む。

#### 【0055】

これらの集合を、通常の集合演算 (例えば和、共通部分、補集合、集合差) によって結合することができる。例えば、ルートから距離 2 にあるページの集合を  $S_2$  とすると、一定構成の  $\times 86CPU$  における読み書き可能マッピングを有するページの集合は、以下のように表すことができる。

( {  $x : x$  はラージページ入エッジを有する } 共通部分 {  $x : x$  は読み書き可能入エッジを有する } 共通部分  $S_2$  ) 和

( {  $x : x$  はスマートページ入エッジを有する } 共通部分 {  $x : x$  は読み書き可能マッピングを有する } 共通部分  $S_3$  )

#### 【0056】

ナイーブなアルゴリズムで、あらゆる頂点  $v$  を通ってそれが集合に属するかどうかをテストすることによって、状態変更時ごとにこれらの集合を再計算することもできる。これは高価であろう。述べたタイプの集合で表すことのできる状態プロパティをアルゴリズムで計算する場合、以下に述べるようなキャッシング方式を利用することができる。

#### 【0057】

##### キャッシング方式

状態変更を効率的に評価する際に使用するためのデータをキャッシングするために、様々な方式を使用することができる。例示的なキャッシング方式について以下に述べる。

#### 【0058】

##### 方式 1：単純な集合キャッシング

この方式では、集合を明示的に計算して記憶 (キャッシング) する。その後の状態変更のたびに、アルゴリズムはキャッシングを更新する。一例では、以下のアクセス演算を公開するキャッシングを維持することができる。

- `Init()` 空集合など、何らかの明確な値にキャッシングを初期化する。

- `Add(S)`  $S$  (单一要素または要素集合) をキャッシングに加える。

- `Remove(S)`  $S$  (单一要素または要素集合) をキャッシングから削除する。

- `ShowCache(S)` 現在キャッシングされているすべての要素を返す。

キャッシングは追加のアクセス演算を公開することもできる (例えば効率を高めるために)。

#### 【0059】

このようなキャッシングを表す方法の 1 つは、ビットベクトルによる方法である。例えば、システムが  $2^{16}$  個のメモリ物理ページを有する場合、 $2^{16}$  ビット長 (すなわち 8 キロバイト) のベクトルが、各ページごとのブール値を表すことができる。定義された集合中に  $n$  番目のページがあるかどうかに応じて、 $n$  番目のビットはオンとオフのどちらかをとる。したがって、定義されたページ集合について、1 ページあたり 1 ビットのコストで集合中のメンバシップをキャッシングすることができる。このタイプの表現を使用すると、和や共通部分などの集合演算は、ビットごとの「OR」および「AND」演算子を使用して非常に単純に実施されることが理解されるであろう。

#### 【0060】

##### 方式 2：上位集合化、部分集合化

メモリアクセス制御を実施する基礎のアルゴリズムの詳細によっては、キャッシングが正確なターゲット集合を含む必要がない場合がある。例えば、ターゲット集合の何らかの上位集合または部分集合をキャッシングするだけで十分な場合がある。これにより、キャッシングを維持するコストを削減することができる。図 3 の例では、メモリアクセス制御条件は

10

20

40

50

、 $M_P(s)$  が  $N_A(P, s)$  と交差しないことを要求する。しかし、 $N_A(P, s)$  の正確なメンバを計算するのが不都合であるか実際的でない場合は、 $N_A(P, s)$  の何らかの上位集合を計算してキャッシュし、次いで、 $M_P(s)$  が、計算した  $N_A(P, s)$  の上位集合と交差しないことを保証することが可能である。この技法では、通常なら許容できる何らかの状態変更を拒否することになる場合があるが、禁じるべき状態変更は許容しないことになる。これにより、メモリアクセス制御のための条件が保存される。

#### 【0061】

##### 方式3：反転エッジ表現

通常、エッジはソース頂点に記憶されるか、またはソース頂点と共に記憶される。例えば図2では、ページディレクトリおよびページテーブルは、他のページへのポインタ、ならびにそれらの属性を記憶する。所与の頂点について、すべての出エッジのターゲットを見つけるのは、通常は容易である。同時に、すべての入エッジのソースを見つけるのは、通常は高くつく。頂点はその入エッジに関する情報を持たないので、すべての入エッジを見つけるには、すべてのエッジの全数探索が必要である。

10

#### 【0062】

アルゴリズムが頂点の入エッジ、または入エッジから得られる情報に素早くアクセスする必要がある場合は、各頂点の入エッジに関する情報を、頂点に何らかの形で関連するデータ構造に明示的に記憶するのが有利であろう。「何らかの形で関連する」という言葉は、所与の頂点についてデータ構造（例えばアレイルックアップ）を容易に見つけられることを意味する。

20

#### 【0063】

最も極端な場合では、データ構造はすべての入エッジを記憶する。この場合、データ構造は、上に定義したような、エッジを要素とするキャッシュとすることができます。（また、キャッシュは集合または多重集合を記憶することもできる。）この構造が占める記憶域は、頂点の入エッジの数に比例し、このタイプの構造がすべての頂点について維持される場合、総記憶域はグラフ中のエッジの数に比例する。

#### 【0064】

派生情報を記憶すれば十分なことが多く、その方が、必要な記憶域は少ない。例えば、アルゴリズムは、各頂点の入エッジの数だけを記憶することができる。この場合、キャッシュは参照カウンタとして実装することができる。参照カウンタは通常、以下のアクセス演算を公開する。

30

- `Init()` 0など、何らかの明確な値にキャッシュを初期化する。

- `Increment()`

- `Decrement()`

- `GetValue()`

#### 【0065】

参照カウンタ（または同様のデータ構造）の一般的な使用法の1つは、集合を構築することである。例えば、例示的なメモリアクセス制御アルゴリズムは、入エッジのない頂点の集合、すなわち参照カウントが0である頂点の集合を計算しなければならない場合がある。参照カウンタの集まりは、この集合のキャッシュ（方式1）を次のように制御することができます。すなわち、参照カウンタの値が変化したときは常に、アルゴリズムはそれが0になったかどうかをテストする。0になった場合は、頂点をキャッシュに加える。同様に、アルゴリズムは、0であった参照カウンタが別の値をとるイベントがあったかどうかを監視する。このイベントがあった場合、アルゴリズムは頂点をキャッシュから削除する。

40

#### 【0066】

以下は、いくつかのキャッシング使用例である。

- $d = 1, 2, 3$ について、 $S_d$  の上位集合  $S_d'$  をキャッシュする。

- $d = 2, 3$ について、キャッシュを（a）明示的に記憶するか、（b）参照カウンタによって駆動することができる。

50

- ローカルラベルプロパティ「読み書き可能入エッジを有する」および「ラージ／スマートページ入エッジを有する」を計算する。

- 非ローカルプロパティ「読み書き可能マッピングを有する」を計算する。

- $S_2$  中の頂点の読み書き可能入エッジの数について、参照カウンタを使用する。この情報を使用して、非ローカルプロパティ「読み書き可能マッピングを有する」の計算を加速することができる。

#### 【0067】

##### 記憶済み情報を使用した例示的なメモリアクセス制御プロセス

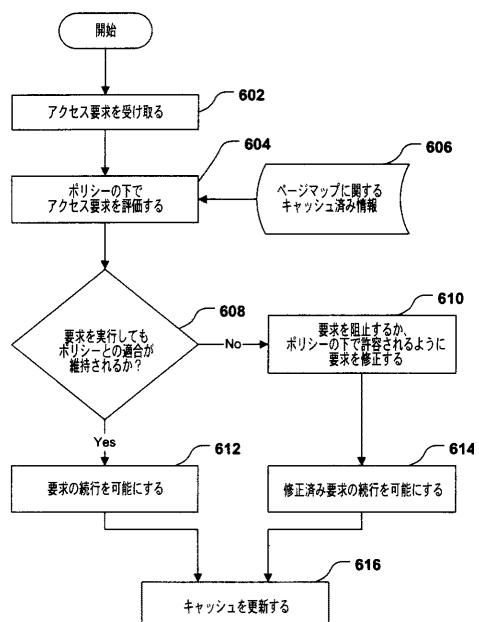

図6に、本明細書に述べた技法を使用した、メモリアクセス制御を実施するための例示的なプロセスを示す。

10

#### 【0068】

最初に、メモリにアクセスするための要求を受け取る(602)。アクセス要求が受け取られると、メモリアクセス制御システムが要求を評価して、メモリアクセスを統制するポリシーに要求の実行が適合するかどうかを判定する(604)。メモリアクセスポリシーの例は、上に論じたものである。一例としてポリシーは、ソースの集合に対していくつかのページを立入り禁止と定義することができ、ポリシーは、立入り禁止ページの1つに対して、このページへのアクセスを許可されていないソースの1つから見えるマッピングを生み出すことになるアクセス要求は、どれも禁止することができる。要求の評価は、記憶済みまたはキャッシュ済み情報(606)の助けを借りて行うことができる。この記憶済みまたはキャッシュ済み情報は、ページマップに関する情報、例えば正当なページディレクトリを含むことがわかっているページの集合を含むものとすることができます。

20

#### 【0069】

要求を実施してもポリシーとの適合が維持されると判定された場合(608)は、要求の続行を可能にする(612)。そうでない場合は、要求を阻止するか、ポリシーに違反しない形に修正する(610)。要求をポリシーに違反しない形に修正することの一例は、次のとおりである。要求が、ページテーブルにエントリを書き込むことを求めており、その結果として立入り禁止ページにマッピングすることになる場合は、この要求を修正して、エントリは書き込まれるが「存在」ビットはオフになるようにすることができる。このため、新たにマッピングされたページに以後アクセスしようとしても、例外が生成されることになり、したがって最終的には例外ハンドラが立入り禁止ページへのアクセスを妨げることができる。このように(または他の何らかのやり方で)要求を修正した場合、修正済み要求の続行を可能にする(614)。修正済みまたは未修正の要求が実施された後、要求の実施によってキャッシュ済み情報が変更される場合は、キャッシュを更新することができる(616)。

30

#### 【0070】

以上の例は単に説明のために提供したものであり、本発明を限定するものと考えるべきでは決してないことに留意されたい。本発明を様々な実施形態に関して述べたが、本明細書で使用した言葉は、限定の言葉ではなく記述および例示の言葉であることを理解されたい。さらに、本発明を特定の手段、材料、および実施形態に関して本明細書に述べたが、本発明は、本明細書に開示した詳細に限定されるものではない。そうではなく本発明は、添付の特許請求の範囲に含まれるものなど、機能的に均等なあらゆる構造、方法、および使用に及ぶ。本明細書の教示があれば、当業者なら、多くの修正を実施することができ、本発明の範囲および趣旨を逸脱することなくその態様に変更を加えることができる。

40

#### 【図面の簡単な説明】

#### 【0071】

【図1】本発明を適用できる実施形態のコンピューティング環境のブロック図である。

【図2】本発明を適用できる実施形態のアドレス変換マップを介して仮想アドレス指定を実施するメモリシステムのブロック図である。

【図3】本発明を適用できる実施形態の属性を有する例示的なページテーブルのブロック図である。

50

【図4】本発明を適用できる実施形態のメモリアクセス制御を実施するのに使用できる条件を表す、2つの例示的な交差しない集合のブロック図である。

【図5】本発明を適用できる実施形態のアドレス変換マップを表す、ラベル付き有向グラフのブロック図である。

【図6】本発明を適用できる実施形態の例示的なメモリアクセス制御プロセスの流れ図である。

【符号の説明】

【0072】

|                             |                         |    |

|-----------------------------|-------------------------|----|

| 100                         | コンピューティング環境             |    |

| 110                         | コンピュータ                  | 10 |

| 120                         | プロセッサ                   |    |

| 121                         | システムバス                  |    |

| 130                         | システムメモリ                 |    |

| 131                         | 読み取り専用メモリ(ROM)          |    |

| 132                         | ランダムアクセスメモリ(RAM)        |    |

| 133                         | BIOS                    |    |

| 134                         | オペレーティングシステム            |    |

| 135                         | アプリケーションプログラム           |    |

| 136                         | その他のプログラムモジュール          |    |

| 137                         | プログラムデータ                | 20 |

| 140                         | ノンリムーバブル不揮発性メモリインターフェース |    |

| 141                         | ハードディスクドライブ             |    |

| 144                         | オペレーティングシステム            |    |

| 145                         | アプリケーションプログラム           |    |

| 146                         | その他のプログラムモジュール          |    |

| 147                         | プログラムデータ                |    |

| 150                         | リムーバブル不揮発性メモリインターフェース   |    |

| 151                         | 磁気ディスクドライブ              |    |

| 152                         | 磁気ディスク                  |    |

| 155                         | 光ディスクドライブ               | 30 |

| 156                         | 光ディスク                   |    |

| 160                         | ユーザ入力インターフェース           |    |

| 161                         | ポインティングデバイス             |    |

| 162                         | キーボード                   |    |

| 170                         | ネットワークインターフェース          |    |

| 171                         | ローカルエリアネットワーク(LAN)      |    |

| 172                         | モデム                     |    |

| 173                         | ワイドエリアネットワーク(WAN)       |    |

| 180                         | リモートコンピュータ              |    |

| 181                         | メモリ記憶デバイス               | 40 |

| 185                         | リモートアプリケーションプログラム       |    |

| 190                         | ビデオインターフェース             |    |

| 191                         | モニタ                     |    |

| 195                         | 出力周辺インターフェース            |    |

| 196                         | プリンタ                    |    |

| 197                         | スピーカ                    |    |

| 201                         | 記憶位置                    |    |

| 202                         | ページディレクトリ               |    |

| 204(1)、204(2)、204(3)        | ページテーブル                 |    |

| 206(1)、206(2)、206(3)、206(4) | ページ                     | 50 |

- 2 1 0 仮想アドレス

- 2 1 1 ページディレクトリオフセット

- 2 1 2 ページテーブルオフセット

- 2 1 3 ページオフセット

- 2 2 0 メモリ管理ユニット (MMU)

- 3 0 1 第1のエントリ

- 3 0 2 アドレス

- 3 0 4 ページが「読み取り専用」かどうかを示すビット

- 3 0 6 ページが「存在」するかどうかを示すビット

- 4 0 2 ソース s から見えるメモリ位置の集合 M\_P(s)

- 4 0 4 ポリシー P の下でソース s からのアクセスが許可されないメモリ位置の集合 N\_A(P, s)

- 5 0 0 グラフ

- 5 0 2, 5 0 4, 5 0 6, 5 0 8, 5 1 0, 5 1 2 頂点

- 5 2 2, 5 2 4, 5 2 6, 5 2 8, 5 3 0, 5 3 2, 5 3 4 エッジ

- 5 5 0, 5 5 2 頂点ではない要素

【 义 1 】

【 図 2 】

【図3】

【図5】

【図4】

【図6】

---

フロントページの続き

(72)発明者 ポール イングランド

アメリカ合衆国 98008 ワシントン州 ベルビュー ノーサップ ウェイ 16659

審査官 前田 浩

(56)参考文献 特開2000-353127 (JP, A)

米国特許出願公開第2002/0144077 (US, A1)

米国特許出願公開第2002/0116590 (US, A1)

特開平07-319735 (JP, A)

特開平02-056653 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/14