(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-111663

(P2015-111663A)

(43) 公開日 平成27年6月18日(2015.6.18)

| (51) Int.Cl.                  | F 1        | テーマコード (参考) |           |  |

|-------------------------------|------------|-------------|-----------|--|

| <b>H01L 29/786</b> (2006.01)  | H01L 29/78 | 6 1 6 V     | 4 M 1 O 4 |  |

| <b>H01L 29/417</b> (2006.01)  | H01L 29/78 | 6 1 8 B     | 5 F O 4 8 |  |

| <b>H01L 29/41</b> (2006.01)   | H01L 29/78 | 6 2 6 A     | 5 F O 8 3 |  |

| <b>H01L 21/28</b> (2006.01)   | H01L 29/78 | 6 1 6 U     | 5 F 1 1 O |  |

| <b>H01L 21/8242</b> (2006.01) | H01L 29/50 | M           |           |  |

審査請求 未請求 請求項の数 5 O L (全 38 頁) 最終頁に続く

|              |                              |                                                                                                                                                      |                                                |

|--------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| (21) 出願番号    | 特願2014-221300 (P2014-221300) | (71) 出願人                                                                                                                                             | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成26年10月30日 (2014.10.30)     | (72) 発明者                                                                                                                                             | 田中 哲弘<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2013-227917 (P2013-227917) | (72) 発明者                                                                                                                                             | 郷戸 宏充<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (32) 優先日     | 平成25年11月1日 (2013.11.1)       | F ターム (参考) 4M104 AA03 AA09 BB04 BB06 BB08<br>BB36 BB39 CC01 DD34 DD37<br>DD43 DD63 DD66 DD79 DD83<br>DD90 DD92 FF04 FF06 FF17<br>FF18 GG08 GG16 HH20 |                                                |

| (33) 優先権主張国  | 日本国 (JP)                     |                                                                                                                                                      |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置およびその作製方法

## (57) 【要約】

【課題】オン電流が高く、オフ電流が低い半導体装置を提供する。また、安定な電気特性をもつ半導体装置を提供する。

【解決手段】酸化反応のギブス自由エネルギーが酸化物半導体よりも高いソース電極およびドレイン電極を用いる半導体装置である。酸化物半導体の下面に接する第1の電極と、酸化物半導体の上面に接する第2の電極と、酸化物半導体の側面と面するゲート絶縁膜およびゲート電極を有し、加熱処理を行うことで第1の電極および第2の電極から酸化物半導体へ酸素を供給する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

酸化物半導体と、

前記酸化物半導体の下面に接する第1の電極と、

前記酸化物半導体の上面に接する第2の電極と、

前記酸化物半導体の側面と面するゲート電極と、

前記酸化物半導体と前記ゲート電極との間に設けられたゲート絶縁膜と、を有し、

前記第1の電極は前記第2の電極と重なる領域を有し、

前記第1の層および前記第2の層の一方または双方は、少なくとも第1の層および第2の層を含み、

前記第1の層は前記酸化物半導体と接し、かつ前記第2の層よりも酸素濃度が低いことを特徴とする半導体装置。

10

**【請求項 2】**

請求項1において、

前記第1の層は前記酸化物半導体よりも酸化反応のギブス自由エネルギーが高い物質を含むことを特徴とする半導体装置。

**【請求項 3】**

請求項1または請求項2において、

前記第1の層および前記第2の層が、銀、銅、ルテニウム、イリジウム、白金および金から選ばれた一種以上を含むことを特徴とする半導体装置。

20

**【請求項 4】**

請求項1乃至請求項3のいずれか一項において、

前記第1の層および前記第2の層よりも酸素透過性の低い導電膜を有し、

前記第1の層および前記第2の層が、前記酸化物半導体と前記導電膜との間に設けられることを特徴とする半導体装置。

**【請求項 5】**

酸化物半導体と、

前記酸化物半導体の下面に接する第1の電極と、

前記酸化物半導体の上面に接する第2の電極と、

前記酸化物半導体の側面と面するゲート電極と、

30

前記酸化物半導体と前記ゲート電極との間に設けられたゲート絶縁膜と、を有し、

前記第1の電極は前記第2の電極と重なる領域を有し、

前記第1の層および前記第2の層の一方または双方は、少なくとも第1の層および第2の層を含み、

前記第1の層は前記酸化物半導体と接し、かつ前記第2の層よりも酸素濃度が低いことを特徴とする半導体装置の作製方法において、

加熱処理を行うことで、前記第1の電極または前記第2の電極から前記酸化物半導体へ酸素を供給することを特徴とする前記半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、物、方法、又は製造方法に関する。又は、本発明は、プロセス、マシン、マニュファクチャ、又は組成物（コンポジション・オブ・マター）に関する。また、本発明の一態様は、半導体装置、表示装置、発光装置、蓄電装置、記憶装置、それらの駆動方法又はそれらの製造方法に関する。特に、本発明の一態様は、酸化物半導体を含む半導体装置、表示装置、又は発光装置に関する。

40

**【0002】**

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置、電気光学装置、半導体回路及び電子機器は、半導体装置を有する場合がある。

50

**【背景技術】****【0003】**

近年、半導体装置の高集積化はトランジスタの微細化によって達成されてきた。ところが、従来用いられてきた平面的に作製するプレーナー型トランジスタでは、短チャネル効果が深刻になり、微細化の限界が近づいている。上述の問題を克服するために、半導体基板を立体的に加工し、基板に対して上下方向に電流が流れるように、ソース領域、ドレイン領域、およびゲート電極を形成する縦型トランジスタが提案されている（非特許文献2）。特に、ゲート電極が半導体の周囲を囲む構造の縦型トランジスタはSGT（Surrounding Gate Transistor）と呼ばれ、トランジスタの占有面積が小さくできる点と、高いオン電流が実現できる点で注目されている（非特許文献1、非特許文献3）。

10

**【0004】**

ところで、シリコン以外にトランジスタに適用可能な半導体として、酸化物半導体が注目されている。酸化物半導体を用いたトランジスタは、製造工程が容易で、アモルファスシリコンを用いたトランジスタよりも動作が速く、オフ状態のリーク電流が極めて低いことから、集積回路や画像表示装置（単に表示装置とも表記する）への応用が期待されている。

**【0005】**

酸化物半導体の膜中および界面に存在する酸素欠損は、トランジスタの電気特性を変動させていることが知られているが、酸化物半導体の界面および膜中に、効果的に酸素を供給することで、上記課題を克服できることが知られている。酸化物半導体に酸素を供給する方法として、酸化物半導体と接する絶縁体から酸素を供給する方法（特許文献1）や、電極から酸素を供給する方法（特許文献2、特許文献3）が開示されている。

20

**【先行技術文献】****【特許文献】****【0006】**

【特許文献1】特開2012-009836号公報

【特許文献2】特開2013-131740号公報

【特許文献3】特開2013-138195号公報

30

**【非特許文献】****【0007】**

【非特許文献1】IEEE International Electron Devices Meeting (IEDM) Technical Digest pp. 23-26, 1989

【非特許文献2】IEEE International Electron Devices Meeting (IEDM) Technical Digest pp. 949-951, 2002

【非特許文献3】IEEE Symposium VLSI Technology Technical Digest pp. 21-22, 1993

40

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

本発明の一態様は、新規な半導体装置などを提供すること、または、オン電流が高い半導体装置を提供すること、または、オフ電流が低い半導体装置を提供すること、または、短チャネル効果が発現しにくい半導体装置を提供すること、または、占有面積の小さい半導体装置を提供すること、または、安定な電気特性をもつ半導体装置を提供することを課題の一とする。

**【0009】**

なお、複数の課題の記載は、互いの課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全て解決する必要はない。また、列記した以外の課題が、明細書

50

、図面、請求項などの記載から、自ずと明らかとなるものであり、これらの課題も、本発明の一形態の課題となり得る。

【課題を解決するための手段】

【0010】

本発明の一態様は、酸化物半導体と、酸化物半導体の下面に接する第1の電極と、酸化物半導体の上面に接する第2の電極と、酸化物半導体の側面と面するゲート電極と、酸化物半導体とゲート電極との間に設けられたゲート絶縁膜と、を有する半導体装置である。第1の電極は第2の電極と重なる領域を有する。第1の電極および第2の電極の一方または双方は、少なくとも第1の層および第2の層を含む。第1の層は酸化物半導体と接し、かつ第2の層よりも酸素濃度が低いことが好ましい。

10

【0011】

上記態様において、第1の層は酸化物半導体よりも酸化反応のギブス自由エネルギーが高い物質を含むことが好ましい。

【0012】

上記態様において、第1の層および第2の層が、銀、銅、ルテニウム、イリジウム、白金および金から選ばれた一種以上を含むことが好ましい。

20

【0013】

上記態様に記載の半導体装置は、第1の層および第2の層よりも酸素透過性の低い導電膜を有する。第1の層および第2の層は、酸化物半導体と導電膜との間に設けられることが好ましい。

20

【0014】

本発明の一態様は、酸化物半導体と、酸化物半導体の下面に接する第1の電極と、酸化物半導体の上面に接する第2の電極と、酸化物半導体の側面と面するゲート電極と、酸化物半導体とゲート電極との間に設けられたゲート絶縁膜と、を有し、第1の電極は第2の電極と重なる領域を有し、第1の電極および第2の電極の一方または双方は、少なくとも第1の層および第2の層を含み、第1の層は酸化物半導体と接し、かつ第2の層よりも酸素濃度が低いことを特徴とする半導体装置の作製方法である。加熱処理を行うことで、第1の電極または第2の電極から酸化物半導体へ酸素を供給することが可能になる。

30

【0015】

なお、本明細書において、チャネルに酸化物半導体を用いたトランジスタの構成例を示したが、本発明の一態様は、これに限定されない。例えば、チャネルやその近傍、ソース領域、ドレイン領域などにおいて、場合によっては、または、状況に応じて、Si（シリコン）、Ge（ゲルマニウム）、SiGe（シリコンゲルマニウム）、GaAs（ガリウム砒素）、などを有する材料で形成してもよい。

40

【発明の効果】

【0016】

本発明の一態様により、新規な半導体装置などを提供すること、オン電流が高い半導体装置を提供すること、または、オフ電流が低い半導体装置を提供すること、または、短チャネル効果が発現しにくい半導体装置を提供すること、または、占有面積の小さい半導体装置を提供すること、または、安定な電気特性をもつ半導体装置を提供することが可能になる。

40

【0017】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

【図面の簡単な説明】

【0018】

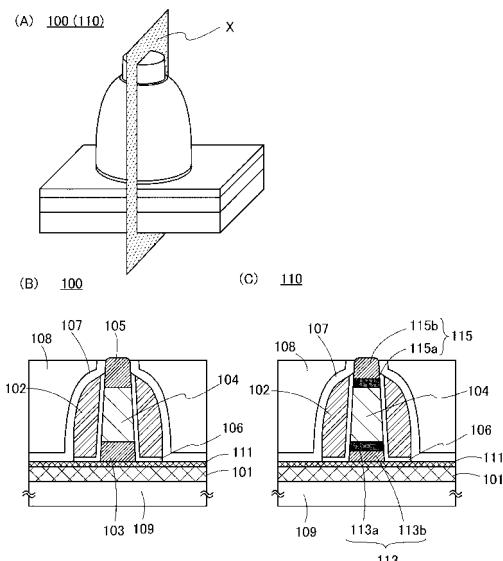

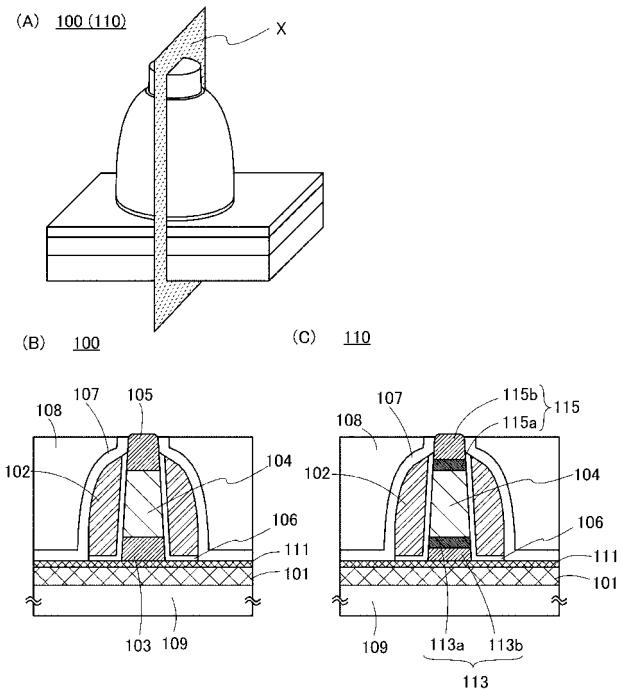

【図1】トランジスタの構成例を示す斜視図。

50

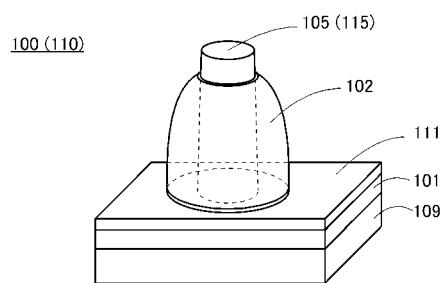

【図2】トランジスタの構成例を示す斜視図および断面図。

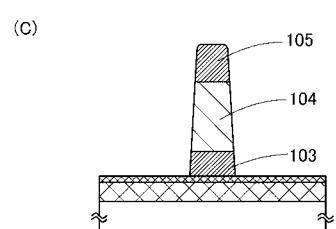

- 【図 3】トランジスタの作製方法の一例を示す断面図。

- 【図 4】トランジスタの作製方法の一例を示す断面図。

- 【図 5】トランジスタの作製方法の一例を示す断面図。

- 【図 6】半導体領域の形状例を示す図。

- 【図 7】トランジスタの構成例を示す断面図。

- 【図 8】トランジスタの構成例を示す断面図。

- 【図 9】記憶装置の構成例を示す上面図。

- 【図 10】記憶装置の構成例を示す断面図。

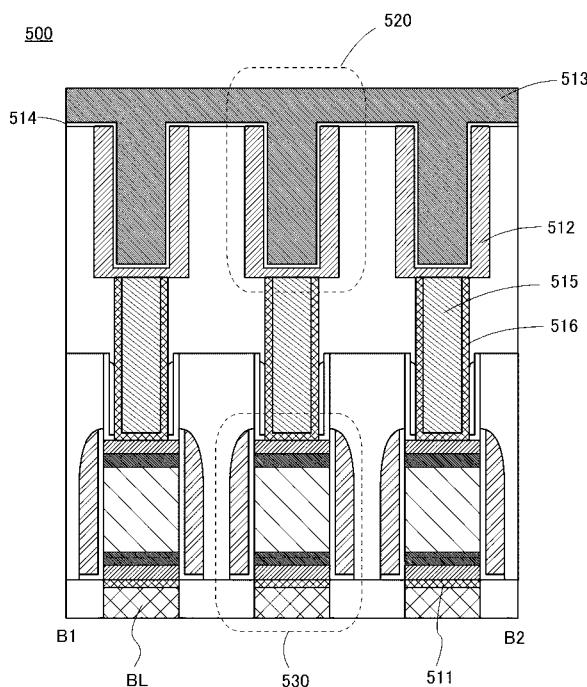

- 【図 11】記憶装置の構成例を示す断面図。

- 【図 12】記憶装置の構成例を示す断面図。

- 【図 13】記憶装置の構成例を示す断面図。

- 【図 14】記憶装置の一例を示す回路図。

- 【図 15】表示装置の一例を示す上面図および回路図。

- 【図 16】電子機器の一例を示す外観図。

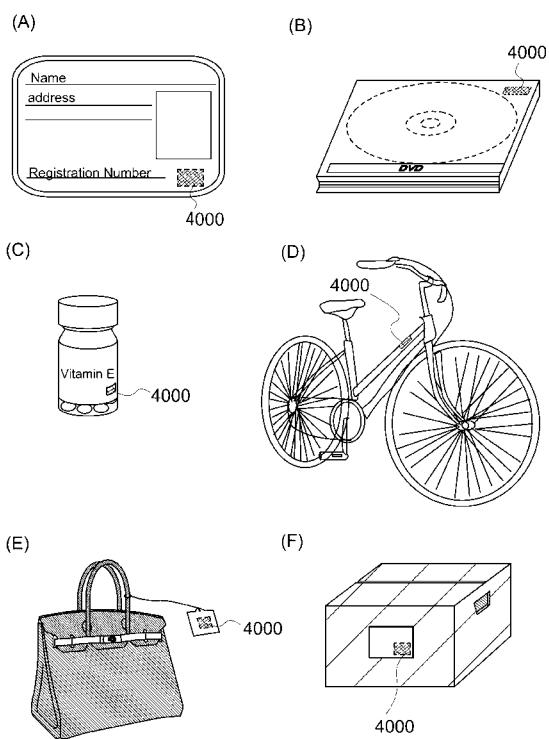

- 【図 17】R F タグの使用例を説明する図。

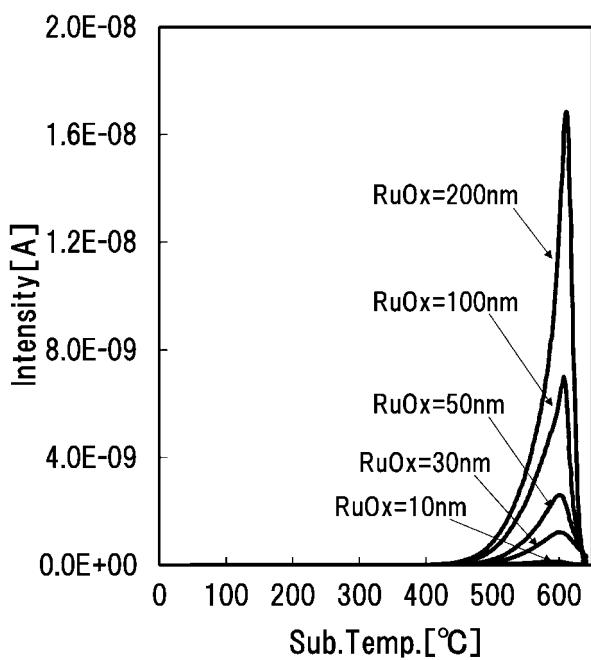

- 【図 18】T D S 分析の結果を示す図。

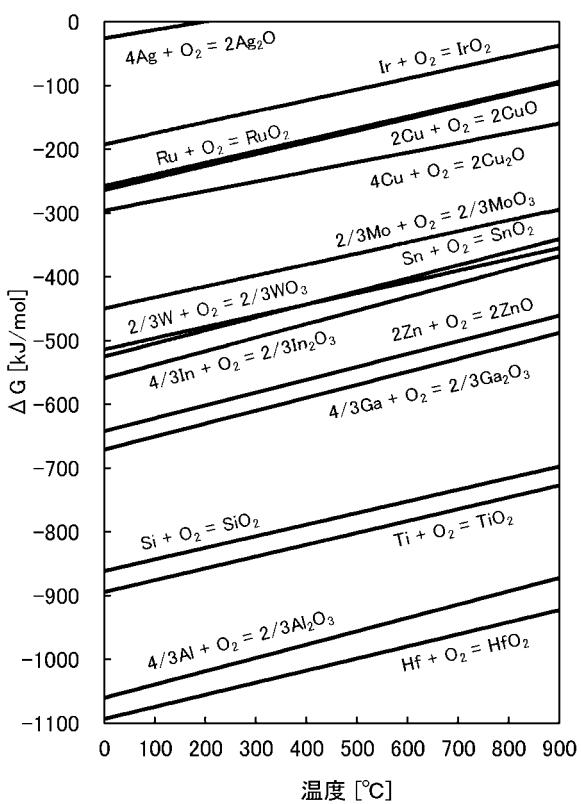

- 【図 19】酸化反応のギブス自由エネルギーを示す図。

【発明を実施するための形態】

【0 0 1 9】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ること、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。また、以下に説明する実施の形態及び実施例において、同一部分又は同様の機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

【0 0 2 0】

なお、本明細書にて用いる第 1、第 2 等の序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば「第 1 の」を「第 2 の」又は「第 3 の」等を適宜置き換えて説明することができる。また、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。

【0 0 2 1】

(実施の形態 1)

本実施の形態では、本発明の一態様に係るトランジスタについて図を用いて説明する。

【0 0 2 2】

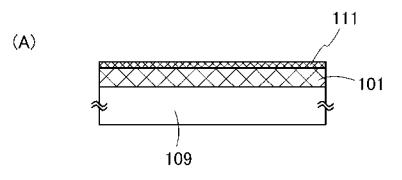

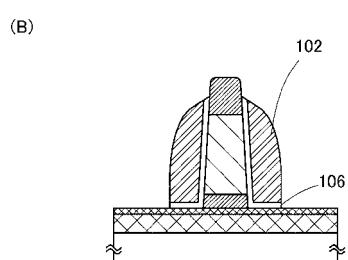

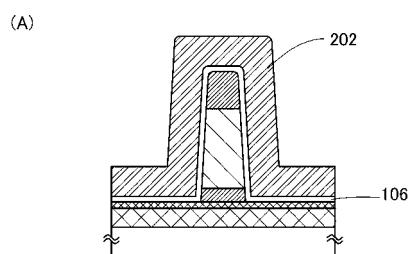

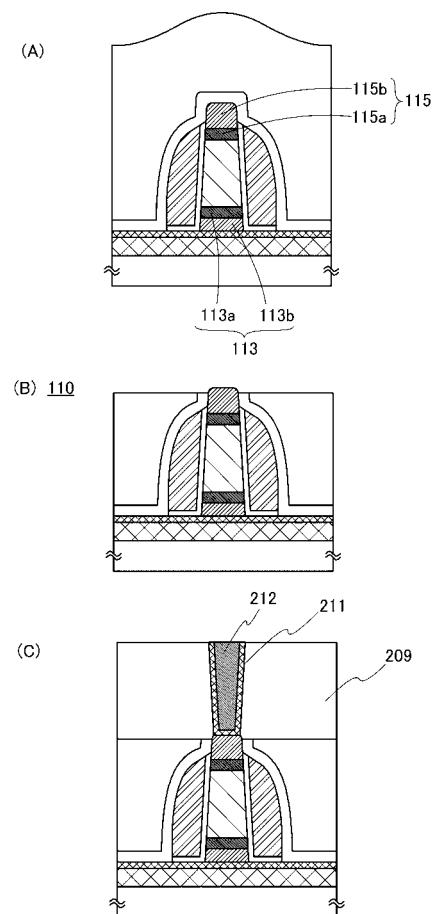

図 1 は、本発明の一態様のトランジスタの斜視図である。なお、図 1 は図の明瞭化のために一部の要素を省いて図示している。図 1 に示すトランジスタ 1 0 0 ( または 1 1 0 ) は、基板 1 0 9 と、配線 1 0 1 と、導電膜 1 1 1 と、ゲート電極 1 0 2 と、ドレイン電極 1 0 5 ( または 1 1 5 ) を有している。

【0 0 2 3】

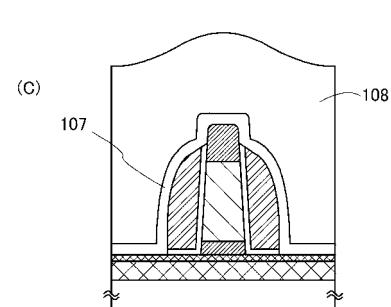

図 2 ( B ) は図 1 に示すトランジスタの平面 X による断面図を示している ( 図 2 ( A ) 参照 )。図 2 ( B ) に示すトランジスタ 1 0 0 は、基板 1 0 9 と、基板 1 0 9 上に形成された配線 1 0 1 と、配線 1 0 1 上に形成された導電膜 1 1 1 と、導電膜 1 1 1 上に形成されたソース電極 1 0 3 と、ソース電極 1 0 3 上に形成された酸化物半導体 1 0 4 と、ソース電極 1 0 3 と重なるように酸化物半導体 1 0 4 上に形成されたドレイン電極 1 0 5 と、ソース電極 1 0 3 、酸化物半導体 1 0 4 およびドレイン電極 1 0 5 の側面と接するように設

10

20

30

40

50

けられたゲート絶縁膜106と、ゲート絶縁膜106を介して、ソース電極103、酸化物半導体104およびドレイン電極105の側面と面するように設けられたゲート電極102と、ドレイン電極105、ゲート電極102、ゲート絶縁膜106および導電膜111と接する保護絶縁膜107と、保護絶縁膜107上に設けられた層間絶縁膜108を有している。

#### 【0024】

基板109は、単なる支持体に限らず、他のトランジスタやキャパシタなどの素子が形成された基板であってもよい。この場合、トランジスタのゲート電極102、配線101の少なくとも一つが、上記の他の素子と電気的に接続されていてもよい。また、基板109と配線101との間に、基板109からの不純物拡散を防止するために絶縁膜を設けてよい。

10

#### 【0025】

なお、例えば、本明細書等において、様々な基板109を用いて、トランジスタを形成することが出来る。基板109の種類は、特定のものに限定されることはない。その基板の一例としては、半導体基板（例えば単結晶基板又はシリコン基板）、SOI基板、ガラス基板、石英基板、プラスチック基板、金属基板、ステンレス・スチール基板、ステンレス・スチール・ホイルを有する基板、タンクステン基板、タンクステン・ホイルを有する基板、可撓性基板、貼り合わせフィルム、纖維状の材料を含む紙、又は基材フィルムなどがある。ガラス基板の一例としては、バリウムホウケイ酸ガラス、アルミニオホウケイ酸ガラス、又はソーダライムガラスなどがある。可撓性基板の一例としては、ポリエチレンテレフタレート（PET）、ポリエチレンナフタレート（PEN）、ポリエーテルサルファン（PES）に代表されるプラスチック、又はアクリル等の可撓性を有する合成樹脂などがある。貼り合わせフィルムの一例としては、ポリプロピレン、ポリエステル、ポリフッ化ビニル、又はポリ塩化ビニルなどがある。基材フィルムの一例としては、ポリエステル、ポリアミド、ポリイミド、無機蒸着フィルム、又は紙類などがある。特に、半導体基板、単結晶基板、又はSOI基板などを用いてトランジスタを製造することによって、特性、サイズ、又は形状などのばらつきが少なく、電流能力が高く、サイズの小さいトランジスタを製造することができる。このようなトランジスタによって回路を構成すると、回路の低消費電力化、又は回路の高集積化を図ることができる。

20

#### 【0026】

なお、ある基板を用いてトランジスタを形成し、その後、別の基板にトランジスタを転置し、別の基板上にトランジスタを配置してもよい。トランジスタが転置される基板の一例としては、上述したトランジスタを形成することが可能な基板に加え、紙基板、セロファン基板、石材基板、木材基板、布基板（天然纖維（絹、綿、麻）、合成纖維（ナイロン、ポリウレタン、ポリエステル）若しくは再生纖維（アセテート、キュプラ、レーヨン、再生ポリエステル）などを含む）、皮革基板、又はゴム基板などがある。これらの基板を用いることにより、特性のよいトランジスタの形成、消費電力の小さいトランジスタの形成、壊れにくい装置の製造、耐熱性の付与、軽量化、又は薄型化を図ることができる。

30

#### 【0027】

なお、所定の機能を実現させるために必要な回路の全てを、同一の基板（例えば、ガラス基板、プラスチック基板、単結晶基板、又はSOI基板など）に形成することが可能である。こうして、部品点数の削減によるコストの低減、又は回路部品との接続点数の低減による信頼性の向上を図ることができる。

40

#### 【0028】

トランジスタ100はSGT（Surrounding Gate Transistor）で、ソース電極103とドレイン電極105との間の距離、すなわち酸化物半導体104の高さがトランジスタ100のチャネル長に相当する。トランジスタ100は、酸化物半導体104の側面全体がゲート電極102で囲まれているため完全空乏で動作し、オン電流が高く、DIBL（Drain Induced Barrier Lowering）によるリーク電流（オフ電流）の増加を防ぐことができる。トランジスタ100の

50

チャネル長は、例えば 30 nm 以上 500 nm 以下、好ましくは、50 nm 以上 300 nm 以下、さらに好ましくは 100 nm 以上 200 nm 以下とすることができます。

#### 【0029】

単結晶シリコンで作製された SGT は、立体的に加工された単結晶シリコン基板にチャネルが形成されるので、界面準位密度が高い面方位にもチャネルが形成される。そのため、プレーナー型のトランジスタと比べて電気特性が劣化しやすい場合がある。一方、酸化物半導体で作製された SGT は、面方位に対する界面準位の依存性が非常に少なく、上述した問題が発生しない。そのため SGT を酸化物半導体で作製することは好ましい。

#### 【0030】

また、単結晶シリコンで SGT を作製する場合、ソース領域およびドレイン領域を形成するためには高度な不純物注入技術が要求されるが、酸化物半導体で SGT を作製する場合、不純物注入を行わずともトランジスタを作製することができるので、単結晶シリコンに比べて製造工程が容易である。

10

#### 【0031】

一般的に、酸化物半導体を使ったトランジスタは、酸素欠損によりトランジスタの電気特性が変動することが知られている。そのため、トランジスタ 100 も酸化物半導体 104 に酸素を供給するのが好ましい。保護絶縁膜 107 および層間絶縁膜 108 に酸素を含ませて酸素供給を試みた場合、酸化物半導体 104 は上下と側面を電極で囲まれているため、上記絶縁膜から供給された酸素が電極を透過できず、酸化物半導体 104 まで到達しない。ゲート絶縁膜 106 から酸素を供給する方法もあるが、微細化されたトランジスタは、ゲート容量を確保するために、ゲート絶縁膜 106 を薄く形成することが一般的である。そのため、ゲート絶縁膜 106 は十分な量の酸素を含むことができず、酸化物半導体 104 の酸素欠損を十分に修復することができないおそれがある。上述の理由で、トランジスタ 100において、周囲に存在する絶縁膜から酸化物半導体 104 に酸素を供給することは難しい。

20

#### 【0032】

本実施の形態では、ソース電極およびドレイン電極に酸素供給能力を与えることで、上述の問題を解決する方法を示す。ソース電極およびドレイン電極が酸素供給能力を持つことで、縦型トランジスタにおいても、動作を安定化させることができる。以下にその詳細を説明する。

30

#### 【0033】

ソース電極 103 およびドレイン電極 105 は酸素を含む導電膜であり、酸化物半導体 104 よりも酸化反応のギブス自由エネルギーが高い物質を有する。即ち、ソース電極 103 およびドレイン電極 105 は酸化物半導体 104 よりも還元しやすい性質を有する。言い換えると、ソース電極 103 およびドレイン電極 105 は酸化物半導体 104 よりも酸化しにくい性質を有する。

#### 【0034】

ソース電極 103 およびドレイン電極 105 の厚さは、例えば 3 nm 以上 300 nm 以下、好ましくは 5 nm 以上 100 nm 以下、さらに好ましくは 10 nm 以上 50 nm 以下にするとよい。

40

#### 【0035】

酸素を含むソース電極 103 およびドレイン電極 105 は、酸化物半導体 104 よりも還元しやすい物質で構成されているため、加熱処理を施すと、ソース電極 103 およびドレイン電極 105 が還元し酸素を放出する。ソース電極 103 およびドレイン電極 105 から放出された酸素は、酸化物半導体 104 に供給され、酸化物半導体 104 の酸素欠損を低減させることができる。

#### 【0036】

なお、加熱処理は、250 以上 650 以下、好ましくは 300 以上 500 以下の温度で、不活性ガス雰囲気、酸化性ガスを 10 ppm 以上含む雰囲気、または減圧状態で行えばよい。

50

## 【0037】

参考として、図19に各元素の酸化反応のギブス自由エネルギーを示す。図19の横軸は温度 [ ] であり、縦軸はギブス自由エネルギー ( G [ kJ / mol ] ) である。図19に示す酸化反応のギブス自由エネルギーは、以下の計算によって求めたものである。まず、表1に示す各物質における標準生成エンタルピー  $\Delta H$  および標準エントロピー  $S$  の値を用いて、表2に示す各酸化反応の式に代入することで、各酸化反応における標準生成エンタルピー  $\Delta H$  および標準生成エントロピー  $S$  の値を算出する。表2に、算出した各酸化反応における標準生成エンタルピー  $\Delta H$  および標準生成エントロピー  $S$  の値を示す。なお、表1に示す各物質における標準生成エンタルピー  $\Delta H$  および標準エントロピー  $S$  の値は、主として日本化学会編「化学便覧基礎編II改訂4版285頁、丸善株式会社」から引用したものである。

## 【0038】

## 【表1】

| 物質                             | $\Delta H$ [ kJ/mol ] | $S$ [ J/(Kmol) ] |

|--------------------------------|-----------------------|------------------|

|                                | 標準生成エンタルピー            | 標準エントロピー         |

| O <sub>2</sub>                 | 0                     | 205.1            |

| Si                             | 0                     | 18.83            |

| SiO <sub>2</sub>               | -910.9                | 41.84            |

| In                             | 0                     | 57.82            |

| In <sub>2</sub> O <sub>3</sub> | -925.8                | 104.2            |

| Ga                             | 0                     | 40.88            |

| Ga <sub>2</sub> O <sub>3</sub> | -1089                 | 84.98            |

| Zn                             | 0                     | 41.63            |

| ZnO                            | -348.3                | 43.64            |

| Sn                             | 0                     | 51.55            |

| SnO <sub>2</sub>               | -580.7                | 52.3             |

| Al                             | 0                     | 28.33            |

| Al <sub>2</sub> O <sub>3</sub> | -1676                 | 50.92            |

| W                              | 0                     | 32.64            |

| WO <sub>3</sub>                | -842.9                | 75.9             |

| Mo                             | 0                     | 28.66            |

| MoO <sub>3</sub>               | -745.1                | 77.74            |

| Cu                             | 0                     | 33.15            |

| CuO                            | -157.3                | 42.63            |

| CuO <sub>2</sub>               | -168.6                | 93.14            |

| Ti                             | 0                     | 30.63            |

| TiO <sub>2</sub> (ルチル)         | -944.7                | 50.33            |

| Hf                             | 0                     | 43.56            |

| HfO <sub>2</sub>               | -1145                 | 59.33            |

| Ru                             | 0                     | 28.53            |

| RuO <sub>2</sub>               | -307                  | 52.2             |

| Ag                             | 0                     | 42.55            |

| Ag <sub>2</sub> O              | -31.05                | 121.3            |

| Ir                             | 0                     | 35.48            |

| IrO <sub>2</sub>               | -249.5                | 50.99            |

## 【0039】

10

20

30

40

【表2】

| 酸化反応式                      | 標準生成エンタルピー<br>$\Delta H$ [ kJ/mol ] | 標準生成エントロピー<br>$\Delta S$ [ J/(Kmol) ] |

|----------------------------|-------------------------------------|---------------------------------------|

| $Si + O_2 = SiO_2$         | -910.9                              | -182.1                                |

| $4/3In + O_2 = 2/3In_2O_3$ | -617.2                              | -212.8                                |

| $Sn + O_2 = SnO_2$         | -580.7                              | -204.4                                |

| $4/3Ga + O_2 = 2/3Ga_2O_3$ | -726.1                              | -203.0                                |

| $2Zn + O_2 = 2ZnO$         | -696.6                              | -201.1                                |

| $2/3W + O_2 = 2/3WO_3$     | -561.9                              | -176.3                                |

| $2/3Mo + O_2 = 2/3MoO_3$   | -496.7                              | -172.4                                |

| $2Cu + O_2 = 2CuO$         | -314.6                              | -186.2                                |

| $4Cu + O_2 = 2Cu_2O$       | -337.2                              | -151.5                                |

| $4/3Al + O_2 = 2/3Al_2O_3$ | -1117                               | -209.0                                |

| $Ti + O_2 = TiO_2$         | -944.7                              | -185.4                                |

| $Hf + O_2 = HfO_2$         | -1145                               | -189.4                                |

| $4Ag + O_2 = 2Ag_2O$       | -62.10                              | -132.7                                |

| $Ru + O_2 = RuO_2$         | -307.0                              | -181.5                                |

| $Ir + O_2 = IrO_2$         | -249.5                              | -189.6                                |

## 【0040】

次に、表2に示す標準生成エンタルピー  $H$  および標準生成エントロピー  $S$  の値を下記の数式(1)に代入して、温度が0以上900以下の範囲における各酸化反応のギブス自由エネルギーの値を算出した。なお、数式(1)のTは、温度[K]である。

## 【0041】

$$G = H - T \times 10^{-3} \quad (1)$$

## 【0042】

図19より、例えば、ソース電極103およびドレイン電極105は、銀、銅、ルテニウム、イリジウム、白金および金から選ばれた一種以上の元素を含む酸化物からなる層を用いればよい。白金および金は図19には記載されていないが、酸化しにくい金属として知られている。当該元素を含む酸化物は、酸化反応のギブス自由エネルギーが高いため、自身は還元しやすく、かつ接する膜を酸化しやすい。なお、導電率が高いため、ルテニウムまたはイリジウムを含む酸化物を用いると好ましい。ルテニウムまたはイリジウムを含む酸化物の一例としては、 $RuO_x$ (Xは0.5以上4以下)、 $IrO_x$ (Xは0.5以上4以下)、 $SrRuO_x$ (Xは1以上5以下)などが挙げられる。

## 【0043】

保護絶縁膜107は酸素を遮断する機能を有する。酸素を遮断する保護絶縁膜107がドレイン電極105と接することで、ドレイン電極105を還元する際に、ドレイン電極105の上面および側面から酸素が漏れるのを防ぐことができ、酸化物半導体104に効果的に酸素供給できる。

## 【0044】

保護絶縁膜107は、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タン

タルなどから選ばれた一種以上含む絶縁体を用いることができる。特に、酸化アルミニウム膜は、水素、水分などの不純物及び酸素の双方に対して膜を透過させない遮断（ブロッキング）効果が高く、保護絶縁膜107に適用するのに好ましい。

#### 【0045】

導電膜111は、酸素を遮断する機能を有する導電膜である。導電膜111はソース電極103よりも酸素透過性が低いことが好ましい。導電膜111がソース電極103の下面と接することで、ソース電極103を還元する際に、ソース電極103の下面から酸素が漏れることを防ぐことができ、効果的に酸化物半導体104に酸素を供給することができる。また、導電膜111は、ソース電極103から放出された酸素が配線101を酸化し、ソース電極103と配線101との間に高抵抗な酸化物層が形成されることを防ぐ。

10

#### 【0046】

導電膜111は、銀、銅、ルテニウム、イリジウム、モリブデン、タングステン、白金および金から選ばれた一種以上の元素、または金属窒化物を含む層とする。特に窒化タンタルは酸素に対してブロッキング効果が高く、導電膜111に好ましい。

#### 【0047】

図2(C)に示すトランジスタ110は、トランジスタ100に加熱処理を施して、ソース電極103およびドレイン電極105を還元させた後の状態を示している。

#### 【0048】

トランジスタ110は、導電膜113aおよび導電膜113bを含むソース電極113と、導電膜115aおよび導電膜115bを含むドレイン電極115と、を有し、導電膜113aおよび導電膜115aは、酸化物半導体104と接している。導電膜113aは、導電膜113bよりも酸素濃度が低い膜である。また、導電膜115aは、導電膜115bよりも酸素濃度が低い膜である。トランジスタ110において、ソース電極113およびドレイン電極115以外の構成は、図2(B)のトランジスタ100と同一である。

20

#### 【0049】

図2(B)のソース電極103は、加熱処理を施すことで、酸化物半導体104近傍の領域が還元され、ソース電極103よりも酸素濃度が低減された導電膜113aと、ソース電極103と同程度の酸素濃度を有する導電膜113bへと変化する。同様に、図2(B)のドレイン電極105は、加熱処理を施すことで、酸化物半導体104近傍の領域が還元され、ドレイン電極105よりも酸素濃度が低減された導電膜115aと、ドレイン電極105と同程度の酸素濃度を有する導電膜115bへと変化する。このとき、ソース電極103およびドレイン電極105から放出された酸素は、酸化物半導体104の酸素欠損を低減させる役割をもつ。

30

#### 【0050】

導電膜113aおよび導電膜115aの厚さは、例えば1nm以上100nm以下、好ましくは1nm以上50nm以下、さらに好ましくは1nm以上10nm以下にすればよい。

#### 【0051】

なお、加熱処理の条件によって、ソース電極103のすべての領域が導電膜113aへと変化し、ドレイン電極105のすべての領域が導電膜115aへと変化する場合もある。つまり、導電膜113bおよび導電膜115bが形成されない場合もある。

40

#### 【0052】

導電膜111は導電膜113a及び導電膜113bよりも酸素透過性が低いことが好ましい。導電膜111が酸素を遮断する機能を有することで、酸化物半導体104から配線101に酸素が吸収されることを防ぐ。また、ソース電極103と配線101との間に高抵抗な酸化物層が形成されることを防ぐ。

#### 【0053】

ゲート絶縁膜106は酸化シリコン、酸化窒化シリコン、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウムおよび酸化タンタルを含む絶縁体から一種以上選択して、単層または積層して用いればよい。

50

## 【0054】

ゲート絶縁膜106の積層構造の一例について説明する。ゲート絶縁膜106は、例えば酸素、窒素、シリコン、ハフニウムなどを有する。具体的には、酸化ハフニウム、および酸化シリコンまたは酸化窒化シリコンを含むと好ましい。酸化ハフニウムは、酸化シリコンや酸化窒化シリコンと比べて比誘電率が高い。したがって、等価酸化膜厚に対して物理的な膜厚を大きくできるため、等価酸化膜厚を10nm以下または5nm以下とした場合でも、トンネル電流によるリーク電流を小さくすることができる。即ち、オフ電流の小さいトランジスタを実現することができる。さらに、結晶構造を有する酸化ハフニウムは、非晶質構造を有する酸化ハフニウムと比べて高い比誘電率を備える。したがって、オフ電流の小さいトランジスタとするためには、結晶構造を有する酸化ハフニウムを用いることが好ましい。結晶構造の例としては、単斜晶系、正方晶系、立方晶系などが挙げられる。ただし、本発明の一態様は、これらに限定されない。

## 【0055】

ところで、結晶構造を有する酸化ハフニウムの被形成面は、欠陥に起因した界面準位を有する場合がある。該界面準位はトラップセンターとして機能する場合がある。そのため、酸化ハフニウムがトランジスタのチャネル領域に近接して配置されるとき、該界面準位によってトランジスタの電気特性が劣化する場合がある。そこで、該界面準位の影響を低減するために、トランジスタのチャネル領域と酸化ハフニウムとの間に、別の層を配置することによって互いに離間させることができることが好ましい場合がある。この層は、緩衝機能を有する。緩衝機能を有する層としては、酸化シリコン、酸化窒化シリコン、酸化物半導体などを用いることができる。なお、緩衝機能を有する層には、例えば、チャネル領域となる半導体よりもエネルギー・ギャップの大きい半導体または絶縁体を用いる。または、緩衝機能を有する層には、例えば、チャネル領域となる半導体よりも電子親和力の小さい半導体または絶縁体を用いる。または、緩衝機能を有する層には、例えば、チャネル領域となる半導体よりもイオン化エネルギーの大きい半導体または絶縁体を用いる。

## 【0056】

ゲート電極102は、Al、Ti、Cr、Co、Ni、Cu、Y、Zr、Mo、Ru、Ag、TaおよびWなどの導電体を用いることができる。また、当該ゲート電極は、上記材料の積層であってもよい。また、ゲート電極102には、窒素を含んだ導電体を用いてもよい。たとえば、ゲート電極102に窒化チタン上にタングステンの積層、窒化タンゲステン上にタングステンの積層、窒化タンタル上にタングステンの積層などを用いることができる。

## 【0057】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【0058】

(実施の形態2)

本実施の形態では、実施の形態1で示した酸化物半導体104について、詳細な説明を行う。

## 【0059】

酸化物半導体104は、インジウムを含む酸化物である。酸化物は、例えば、インジウムを含むと、キャリア移動度(電子移動度)が高くなる。また、酸化物半導体104は、元素Mを含むと好ましい。元素Mとして、例えば、アルミニウム、ガリウム、イットリウムまたはスズなどがある。元素Mは、例えば、酸素との結合エネルギーが高い元素である。元素Mは、例えば、酸化物のエネルギー・ギャップを大きくする機能を有する元素である。また、酸化物半導体104は、亜鉛を含むと好ましい。酸化物が亜鉛を含むと、例えば、酸化物を結晶化しやすくなる。酸化物の価電子帯上端のエネルギーは、例えば、亜鉛の原子数比によって制御できる。

## 【0060】

ただし、酸化物半導体104は、インジウムを含む酸化物に限定されない。酸化物半導体

10

20

30

40

50

104は、例えば、Zn-Sn酸化物、Ga-Sn酸化物であっても構わない。

【0061】

また酸化物半導体104は、エネルギーギャップが大きい酸化物を用いる。酸化物半導体104のエネルギーギャップは、例えば、2.5eV以上4.2eV以下、好ましくは2.8eV以上3.8eV以下、さらに好ましくは3eV以上3.5eV以下とする。

【0062】

酸化物半導体104は、スパッタリング法、CVD(Chemical Vapor Deposition)法(MOCVD(Metal Organic Chemical Vapor Deposition)法、ALD(Atomic Layer Deposition)法、熱CVD法またはPECVD(Plasma Enhanced Chemical Vapor Deposition)法を含むがこれに限定されない)、MBE(Molecular Beam Epitaxy)法またはPLD(Pulsed Laser Deposition)法を用いて成膜するとよい。特に、MOCVD法、ALD法または熱CVD法を用いると、プラズマを使わないと酸化物半導体104にダメージを与えにくく、トランジスタのオフ状態のリーク電流を低く抑えることができるので好ましい。

【0063】

MOCVD法やALD法などの熱CVD法を用いて、In-Ga-Zn-O膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、及びジメチル亜鉛を用いる。なお、トリメチルインジウムの化学式は、In(CH<sub>3</sub>)<sub>3</sub>である。また、トリメチルガリウムの化学式は、Ga(CH<sub>3</sub>)<sub>3</sub>である。また、ジメチル亜鉛の化学式は、Zn(CH<sub>3</sub>)<sub>2</sub>である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム(化学式Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛(化学式Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>)を用いることもできる。

【0064】

酸化物半導体104をスパッタリング法で成膜する場合、パーティクル数低減のため、インジウムを含むターゲットを用いると好ましい。また、元素Mの原子数比が高い酸化物ターゲットを用いた場合、ターゲットの導電性が低くなる場合がある。インジウムを含むターゲットを用いる場合、ターゲットの導電率を高めることができ、DC放電、AC放電が容易となるため、大面積の基板へ対応しやすくなる。したがって、半導体装置の生産性を高めることができる。

【0065】

酸化物半導体104をスパッタリング法で成膜する場合、ターゲットの原子数比は、In:M:Znが3:1:1、3:1:2、3:1:4、1:1:0.5、1:1:1、1:1:2、1:4:4、などとすればよい。

【0066】

酸化物半導体104をスパッタリング法で成膜する場合、ターゲットの原子数比からずれた原子数比の膜が形成される場合がある。特に、亜鉛は、ターゲットの原子数比よりも膜の原子数比が小さくなる場合がある。具体的には、ターゲットに含まれる亜鉛の原子数比の40atomic%以上90atomic%程度以下となる場合がある。

【0067】

以下では、酸化物半導体104中における不純物の影響について説明する。なお、トランジスタの電気特性を安定にするためには、酸化物半導体104中の不純物濃度を低減し、低キャリア密度化および高純度化することが有効である。なお、酸化物半導体104のキャリア密度は、8×10<sup>11</sup>個/cm<sup>3</sup>未満、好ましくは1×10<sup>11</sup>個/cm<sup>3</sup>未満、さらに好ましくは1×10<sup>10</sup>個/cm<sup>3</sup>未満であり、1×10<sup>-9</sup>以上とする。酸化物半導体104中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。

【0068】

例えば、酸化物半導体104中のシリコンは、キャリアトラップやキャリア発生源となる

10

20

30

40

50

場合がある。そのため、酸化物半導体 104 のシリコン濃度を、二次イオン質量分析法 (S I M S : Secondary Ion Mass Spectrometry)において、 $1 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup> 未満、さらに好ましくは $2 \times 10^{18}$  atoms / cm<sup>3</sup> 未満とする。

#### 【0069】

また、酸化物半導体 104 中に水素が含まれると、キャリア密度を増大させてしまう場合がある。酸化物半導体 104 の水素濃度は S I M S において、 $2 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下とする。また、酸化物半導体 104 中に窒素が含まれると、キャリア密度を増大させてしまう場合がある。酸化物半導体 104 の窒素濃度は、S I M S において、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。10

#### 【0070】

また、酸化物半導体 104 の水素濃度を低減するために、ゲート絶縁膜 106 の水素濃度を低減すると好ましい。ゲート絶縁膜 106 の水素濃度は S I M S において、 $2 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下とする。また、酸化物半導体 104 の窒素濃度を低減するために、ゲート絶縁膜 106 の窒素濃度を低減すると好ましい。ゲート絶縁膜 106 の窒素濃度は、S I M S において、 $5 \times 10^{19}$  atoms / cm<sup>3</sup> 未満、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。20

#### 【0071】

以下では、酸化物半導体 104 に適用可能な酸化物半導体膜の結晶構造について説明する。。

#### 【0072】

なお、本明細書において、「平行」とは、二つの直線が -10° 以上 10° 以下の角度で配置されている状態をいう。したがって、-5° 以上 5° 以下の場合も含まれる。また、「略平行」とは、二つの直線が -30° 以上 30° 以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80° 以上 100° 以下の角度で配置されている状態をいう。したがって、85° 以上 95° 以下の場合も含まれる。また、「略垂直」とは、二つの直線が 60° 以上 120° 以下の角度で配置されている状態をいう。30

#### 【0073】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。。

#### 【0074】

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに分けられる。または、酸化物半導体は、例えば、結晶性酸化物半導体と非晶質酸化物半導体とに分けられる。40

#### 【0075】

なお、非単結晶酸化物半導体としては、C A A C - O S ( C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などがある。また、結晶性酸化物半導体としては、単結晶酸化物半導体、C A A C - O S 、多結晶酸化物半導体、微結晶酸化物半導体などがある。

#### 【0076】

まずは、C A A C - O S 膜について説明する。

#### 【0077】

10

20

30

40

50

C AAC - OS 膜は、c 軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

【0078】

透過型電子顕微鏡 (TEM : Transmission Electron Microscope) によって、AAC - OS 膜の明視野像および回折パターンの複合解析像 (高分解能 TEM 像ともいう。) を観察することで複数の結晶部を確認することができる。一方、高分解能 TEM 像によっても明確な結晶部同士の境界、即ち結晶粒界 (グレインバウンダリーともいう。) を確認することができない。そのため、AAC - OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

【0079】

試料面と略平行な方向から、AAC - OS 膜の断面の高分解能 TEM 像を観察すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、AAC - OS 膜の膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映した形状であり、AAC - OS 膜の被形成面または上面と平行に配列する。

【0080】

一方、試料面と略垂直な方向から、AAC - OS 膜の平面の高分解能 TEM 像を観察すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

【0081】

AAC - OS 膜に対し、X 線回折 (XRD : X - Ray Diffraction) 装置を用いて構造解析を行うと、例えば InGaN<sub>0.4</sub> の結晶を有する AAC - OS 膜の out-of-plane 法による解析では、回折角 ( $2\theta$ ) が  $31^\circ$  近傍にピークが現れる場合がある。このピークは、InGaN<sub>0.4</sub> の結晶の (009) 面に帰属されることから、AAC - OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

【0082】

なお、InGaN<sub>0.4</sub> の結晶を有する AAC - OS 膜の out-of-plane 法による解析では、 $2\theta$  が  $31^\circ$  近傍のピークの他に、 $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$  近傍のピークは、AAC - OS 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。AAC - OS 膜は、 $2\theta$  が  $31^\circ$  近傍にピークを示し、 $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。

【0083】

AAC - OS 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径 (または分子半径) が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

【0084】

また、AAC - OS 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

【0085】

不純物濃度が低く、欠陥準位密度が低い (酸素欠損の少ない) ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。したがって、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性 (ノーマリーオンともいう。) になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導

10

20

30

40

50

体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

#### 【0086】

なお、本明細書等において実質的に真性という場合、酸化物半導体膜のキャリア密度は、 $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上である。酸化物半導体膜を高純度真性化することで、トランジスタに安定した電気特性を付与することができる。

10

#### 【0087】

また、C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【0088】

次に、微結晶酸化物半導体膜について説明する。

#### 【0089】

微結晶酸化物半導体膜は、高分解能 TEM 像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体膜に含まれる結晶部は、 $1 \text{ nm}$  以上  $100 \text{ nm}$  以下、または  $1 \text{ nm}$  以上  $10 \text{ nm}$  以下の大きさであることが多い。特に、 $1 \text{ nm}$  以上  $10 \text{ nm}$  以下、または  $1 \text{ nm}$  以上  $3 \text{ nm}$  以下の微結晶であるナノ結晶 (n c : nanocrystalline) を有する酸化物半導体膜を、n c - O S (nanocrystalline Oxide Semiconductor) 膜と呼ぶ。また、n c - O S 膜は、例えば、高分解能 TEM 像では、結晶粒界を明確に確認できない場合がある。

20

#### 【0090】

n c - O S 膜は、微小な領域（例えば、 $1 \text{ nm}$  以上  $10 \text{ nm}$  以下の領域、特に  $1 \text{ nm}$  以上  $3 \text{ nm}$  以下の領域）において原子配列に周期性を有する。また、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S 膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、n c - O S 膜に対し、結晶部よりも大きい径の X 線を用いる XRD 装置を用いて構造解析を行うと、out-of-plane 法による解析では、結晶面を示すピークが検出されない。また、n c - O S 膜に対し、結晶部よりも大きいプローブ径（例えば  $50 \text{ nm}$  以上）の電子線を用いる電子回折（制限視野電子回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S 膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O S 膜に対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、n c - O S 膜に対しナノビーム電子回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

30

#### 【0091】

n c - O S 膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、n c - O S 膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O S 膜は、C A A C - O S 膜と比べて欠陥準位密度が高くなる。

40

#### 【0092】

次に、非晶質酸化物半導体膜について説明する。

#### 【0093】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体膜である。石英のような無定形状態を有する酸化物半導体膜が一例である。

#### 【0094】

50

非晶質酸化物半導体膜は、高分解能TEM像において結晶部を確認することができない。

【0095】

非晶質酸化物半導体膜に対し、XRD装置を用いた構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体膜に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体膜に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンが観測される。

【0096】

なお、酸化物半導体膜は、nc-OS膜と非晶質酸化物半導体膜との間の物性を示す構造を有する場合がある。そのような構造を有する酸化物半導体膜を、特に非晶質ライク酸化物半導体(a-like OS: amorphous-like Oxide Semiconductor)膜と呼ぶ。10

【0097】

a-like OS膜は、高分解能TEM像において鬆(ボイドともいう。)が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。a-like OS膜は、TEMによる観察程度の微量な電子照射によって、結晶化が起こり、結晶部の成長が見られる場合がある。一方、良質なnc-OS膜であれば、TEMによる観察程度の微量な電子照射による結晶化はほとんど見られない。

【0098】

なお、a-like OS膜およびnc-OS膜の結晶部の大きさの計測は、高分解能TEM像を用いて行うことができる。例えば、InGaN<sub>0.4</sub>の結晶は層状構造を有し、In-O層の間に、Ga-Zn-O層を2層有する。InGaN<sub>0.4</sub>の結晶の単位格子は、In-O層を3層有し、またGa-Zn-O層を6層有する、計9層がc軸方向に層状に重なった構造を有する。よって、これらの近接する層同士の間隔は、(009)面の格子面間隔(d値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。そのため、高分解能TEM像における格子縞に着目し、格子縞の間隔が0.28nm以上0.30nm以下である箇所においては、それぞれの格子縞がInGaN<sub>0.4</sub>の結晶のa-b面に対応する。20

【0099】

また、酸化物半導体膜は、構造ごとに密度が異なる場合がある。例えば、ある酸化物半導体膜の組成がわかれば、該組成と同じ組成における単結晶の密度と比較することにより、その酸化物半導体膜の構造を推定することができる。例えば、単結晶の密度に対し、a-like OS膜の密度は78.6%以上92.3%未満となる。また、例えば、単結晶の密度に対し、nc-OS膜の密度およびCAC-OS膜の密度は92.3%以上100%未満となる。なお、単結晶の密度に対し密度が78%未満となる酸化物半導体膜は、成膜すること自体が困難である。30

【0100】

上記について、具体例を用いて説明する。例えば、In:Ga:Zn=1:1:1[原子数比]を満たす酸化物半導体膜において、菱面体晶構造を有する単結晶InGaN<sub>0.4</sub>の密度は6.357g/cm<sup>3</sup>となる。よって、例えば、In:Ga:Zn=1:1:1[原子数比]を満たす酸化物半導体膜において、a-like OS膜の密度は5.0g/cm<sup>3</sup>以上5.9g/cm<sup>3</sup>未満となる。また、例えば、In:Ga:Zn=1:1:1[原子数比]を満たす酸化物半導体膜において、nc-OS膜の密度およびCAC-OS膜の密度は5.9g/cm<sup>3</sup>以上6.3g/cm<sup>3</sup>未満となる。40

【0101】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成の単結晶に相当する密度を算出することができる。所望の組成の単結晶の密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて算出すればよい。ただし、密度は、可能な限り少ない種類の単結晶を50

組み合わせて算出することが好ましい。

【0102】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、a-like OS膜、微結晶酸化物半導体膜、CAAC-OS膜のうち、二種以上を有する積層膜であってもよい。

【0103】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0104】

(実施の形態3)

本実施の形態では、実施の形態1で示したトランジスタ110の作製方法について、図面を用いて説明する。 10

【0105】

まず、基板109上に配線101および導電膜111を形成する(図3(A)参照)。

【0106】

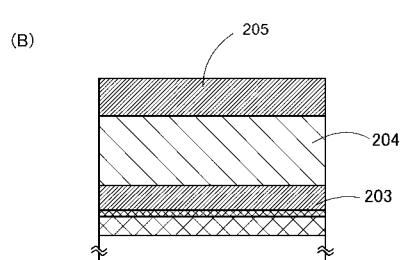

次に、導電膜203、酸化物半導体204および導電膜205を成膜する(図3(B)参照)。

【0107】

導電膜203および導電膜205は、スパッタリング法、CVD法(ALD法、MOCVD法、熱CVD法またはPECVD法を含むがこれに限定されない)、MBE法またはPLD法を用いて成膜すればよい。特にALD法、MOCVD法または熱CVD法は、プラズマを使わないとダメージが少なく好ましい。 20

【0108】

酸化物半導体204は、実施の形態2で記載した方法を用いて成膜する。

【0109】

次に、導電膜203、酸化物半導体204および導電膜205を、共通のフォトリソグラフィーを使ってエッチングし、ソース電極103、酸化物半導体104およびドレイン電極105を形成する(図3(C)参照)。導電膜203、酸化物半導体204および導電膜205をエッチングする際にハードマスクを用いてもよい。また、導電膜111を同時にエッチングしてもよい。

【0110】

次に、ゲート絶縁膜106、導電膜202を成膜する(図4(A)参照)。ゲート絶縁膜106および導電膜202は、スパッタリング法、CVD法(ALD法、MOCVD法、熱CVD法またはPECVD法を含むがこれに限定されない)、MBE法またはPLD法を用いて成膜すればよい。特にALD法、MOCVD法または熱CVD法は、プラズマを使わないとダメージが少なく好ましい。 30

【0111】

次に、導電膜202およびゲート絶縁膜106を異方性エッチングで加工し、ゲート電極102を形成する(図4(B)参照)。異方性エッチングにより、ゲート絶縁膜106を介して酸化物半導体104の側面と面する位置にゲート電極102が形成される。なお、エッチング方法によってはドレイン電極105上にゲート絶縁膜106の一部がエッチングされずに残る場合もあるが、後の研磨工程で除去されるので問題にならない。また、ドレイン電極105が消失しないように、ゲート電極102とドレイン電極105との間に選択比が得られるエッチング方法が好ましいが、上述の選択比が得られない場合は、ドレイン電極105上にエッチングストップを設けてよい。 40

【0112】

次に、保護絶縁膜107および層間絶縁膜108を成膜する(図4(C)参照)。保護絶縁膜107および層間絶縁膜108は、スパッタリング法、CVD法(ALD法、MOCVD法、熱CVD法またはPECVD法を含むがこれに限定されない)、MBE法またはPLD法を用いて成膜すればよい。特にALD法、MOCVD法または熱CVD法は、プラズマを使わないとダメージが少なく好ましい。 50

## 【0113】

次に、加熱処理を行う。加熱処理は、250以上650以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10ppm以上含む雰囲気、または減圧状態で行えばよい。加熱処理により、ソース電極103およびドレイン電極105を還元させて、導電膜113a、導電膜113b、導電膜115aおよび導電膜115bを作製する(図5(A)参照)。その際、ソース電極103およびドレイン電極105から放出された酸素は、酸化物半導体104へ供給され、酸化物半導体104の酸素欠損を低減させる。

## 【0114】

次に、保護絶縁膜107および層間絶縁膜108をCMP(Chemical Mechanical Polishing)法で研磨し、平坦化処理を行う(図5(B)参照)。この際に、ドレイン電極115をCMP法のストップとして利用することができる。もし、ドレイン電極115をストップとして利用できない場合は、ドレイン電極115の上にストップを設けてもよい。

## 【0115】

最後に、層間絶縁膜209、プラグ212、導電膜211を形成する。プラグ212は、Al、Ti、Co、Ni、Cu、W、Moを一種類以上含む導電体を用いることができる。また、導電膜211は導電膜115a及び導電膜115bよりも酸素透過性が低いことが好ましい。導電膜211は、導電膜111と同様に、酸素に対するプロッキング効果を有し、ドレイン電極115とプラグ212との間に抵抗の高い酸化物層が形成されるのを防ぐ。特に窒化タンタルは酸素に対してプロッキング効果が高く、導電膜211に好ましい。

## 【0116】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【0117】

## (実施の形態4)

本実施の形態では、実施の形態1で示した酸化物半導体104およびトランジスタ110の変形例について、図面を用いて説明する。

## 【0118】

## &lt;酸化物半導体の変形例&gt;

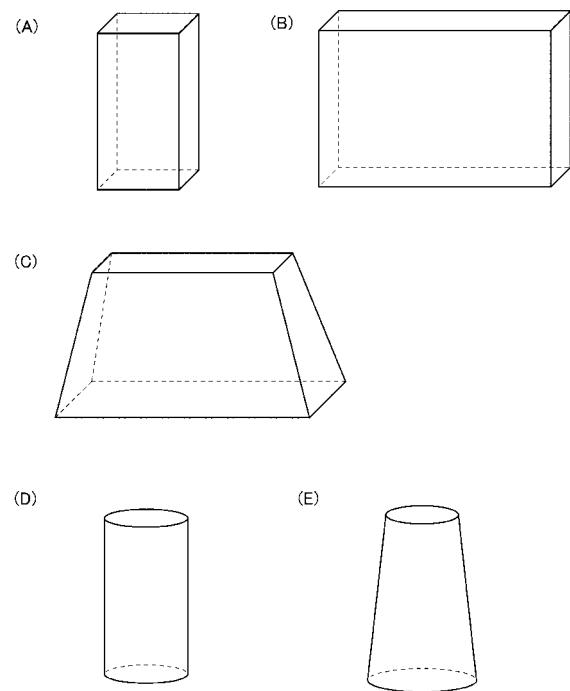

実施の形態1では、半導体領域が円錐台形状の場合を示したが、半導体領域の形状はこれに限定されない。図6に半導体領域を立体的に加工した際の形状例を示す。

## 【0119】

図6(A)は角柱形状に半導体領域を形成した例である。角柱形状はレイアウトが容易で、トランジスタの占有面積を小さくできる。

## 【0120】

図6(B)は壁形状に半導体領域を形成した例である。壁形状は半導体領域の側面の面積を大きくすることができるため、トランジスタのオン電流を増大させることができる。

## 【0121】

図6(C)は角錐台形状に半導体領域を形成した例である。角錐台形状は壁形状に比べて、半導体領域側面に成膜されるゲート絶縁膜またはゲート電極の被覆性を高めることができる。なお、図6(A)、図6(B)および図6(C)は、意図しないゲート電界の集中を避けるために角を丸めてよい。

## 【0122】

図6(D)は円柱形状に半導体領域を形成した例である。円柱形状は側面に角が存在しないため、均一にゲート電界を半導体領域に印加することができる。

## 【0123】

図6(E)は円錐台形状に半導体領域を形成した例である。円錐台形状は円柱形状に比べて、半導体領域側面に成膜されるゲート絶縁膜またはゲート電極の被覆性を高めることができる。

10

20

30

40

50

できる。

【0124】

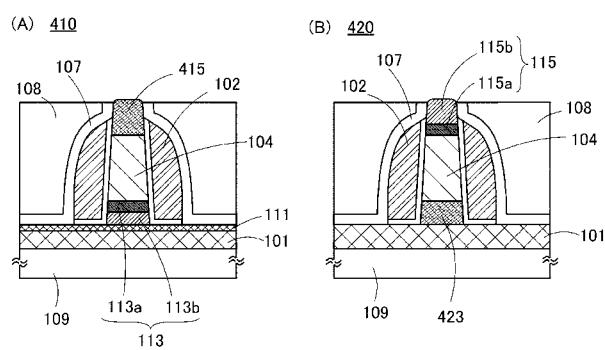

<トランジスタの変形例1>

図7(A)に示すトランジスタ410は、図2(C)のトランジスタ110において、ソース電極113のみが酸素供給能力を有し、ドレイン電極415は酸素供給能力を有さない場合の例である。この場合、ドレイン電極415は、材料の選択肢が広がるため、ゲート電極102を異方性エッティングで形成する際にゲート電極102と選択比のとれる材料を選択することが可能になる。

【0125】

<トランジスタの変形例2>

図7(B)に示すトランジスタ420は、図2(C)のトランジスタ110において、ドレイン電極115のみが酸素供給能力を有し、ソース電極423は酸素供給能力を有さない場合の例である。この場合、ソース電極423と配線101との間に、酸素を遮断するための導電膜111を設ける必要がなく、工程を簡略化することが可能になる。

【0126】

<トランジスタの変形例3>

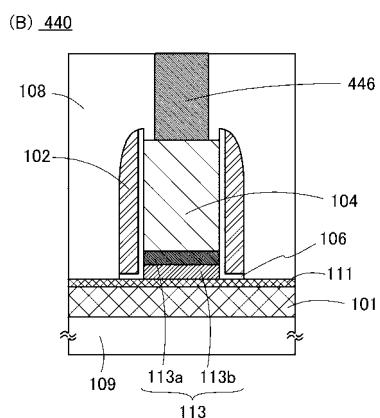

図8(A)に示すトランジスタ430は、図2(C)のトランジスタ110において、ソース電極113および導電膜111を省略した場合のトランジスタである。この場合、配線101がソース電極を兼ねている。トランジスタ430はソース電極113を省略したこと、工程の短縮およびソース電極113をエッティングで形成する際に、酸化物半導体104に加わるダメージを無くすことができる。

【0127】

<トランジスタの変形例4>

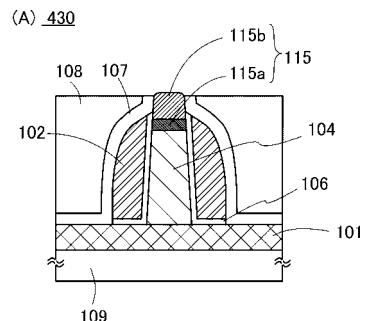

図8(B)に示すトランジスタ440は、図2(C)のトランジスタ110において、ドレイン電極115を省略し、酸化物半導体104とプラグ446を直接接合させた場合の例である。この場合、プラグ446がソース電極を兼ねている。なお、図8(B)において、ハッチパターンが施されていない領域は絶縁体で構成されている。また、プラグ446は抵抗の低い導電層と、半導体中に金属が拡散することを防ぐ導電性バリア膜の積層であってもよい。トランジスタ440はドレイン電極115を省略したこと、工程の短縮およびドレイン電極115をエッティングで形成する際に、酸化物半導体104に加わるダメージを無くすことができる。

【0128】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0129】

(実施の形態5)

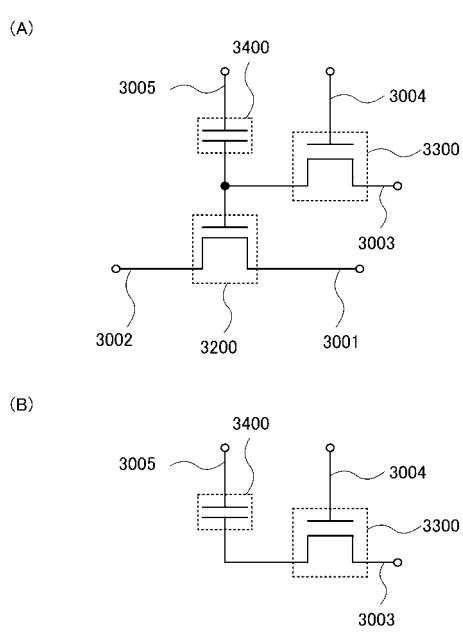

本実施の形態では、本発明の一態様であるトランジスタを使用した記憶装置の一例について図面を参照して説明する。

【0130】

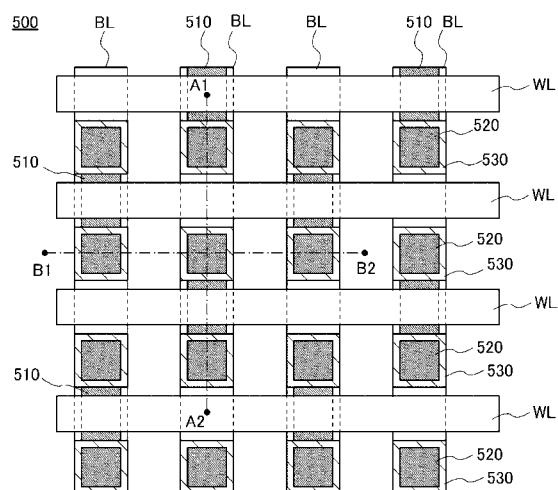

図9は本発明の一態様のトランジスタを利用した記憶装置500の上面図である。なお、図9は図の明瞭化のために一部の要素を省いて図示している。記憶装置500は、列方向に延伸する複数のビット線BLと、行方向に延伸する複数のワード線WLと、ワード線WLに挟まれかつビット線BL上に配置されたトランジスタ530と、トランジスタ530上の記憶素子520と、ワード線WLの底面およびトランジスタ530の側面と接するコントクト510を有する。トランジスタ530は本発明の一態様の縦型トランジスタである。トランジスタ530および記憶素子520は2F間隔でマトリックス状に配置され、記憶装置500は4F<sup>2</sup>のメモリセルで構成されている。

【0131】

記憶装置500がDRAM(Dynamic Random Access Memory)の場合は記憶素子520にキャパシタが用いられ、記憶装置500がPRAM(Phase

10

20

30

40

50

ase change Random Access Memory) の場合は記憶素子 520 に相変化膜が用いられ、記憶装置 500 が ReRAM (Resistance Random Access Memory) の場合は記憶素子 520 に抵抗変化素子が用いられる。以下では、記憶装置 500 が DRAM の場合について説明を行う。

#### 【0132】

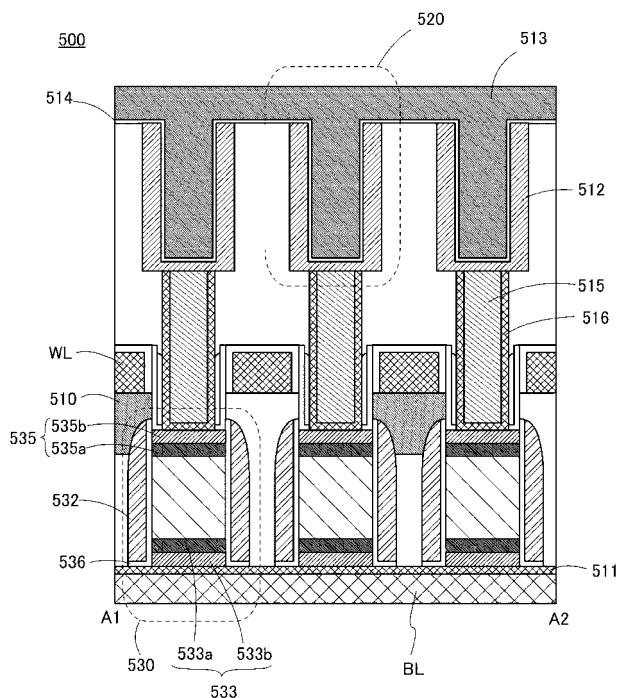

図 10 は図 9 の A1 A2 線断面図を示している。図 10 に示す記憶装置 500 は、トランジスタ 530 と、ビット線 BL と、導電膜 511 と、ワード線 WL と、コンタクト 510 と、プラグ 515 と、導電膜 516 と、第 1 キャパシタ電極 512、第 2 キャパシタ電極 513 およびキャパシタ絶縁体 514 を有する記憶素子 520 と、を有している。コンタクト 510 はトランジスタ 530 の側面に配置されたゲート電極 532 およびワード線 WL に接続され、ワード線 WL の電位をトランジスタ 530 のゲート電極 532 に伝える機能をもつ。トランジスタ 530 のソース電極 533 (導電膜 533a 及び導電膜 533b を含む) はビット線 BL に接続され、トランジスタ 530 のドレイン電極 535 (導電膜 535a 及び導電膜 535b を含む) は記憶素子 520 に接続されている。導電膜 511 は酸素を遮断する機能を有し、ビット線 BL とソース電極 533との間に高抵抗な酸化物が形成されるのを防ぐ。導電膜 516 は酸素を遮断する機能を有し、プラグ 515 とドレイン電極 535 との間に高抵抗な酸化物が形成されるのを防ぐ。

10

#### 【0133】

トランジスタ 530 は、図 2 (C) で示したトランジスタ 110 と比較して、ゲート電極の頂点とドレイン電極の位置関係が異なる。トランジスタ 530 は、ゲート電極 532 の頂点がドレイン電極 535 よりも高い位置にあり、コンタクト 510 とドレイン電極 535 の間にゲート電極 532 およびゲート絶縁膜 536 が存在する (図 10 参照)。上述の構成により、トランジスタ 530 は、コンタクト 510 とドレイン電極 535 が短絡することを防いでいる。上記の特徴以外は、トランジスタ 530 はトランジスタ 110 と同一である。

20

#### 【0134】

図 11 は図 9 の B1 B2 線断面図を示している。図 11 に示す記憶装置 500 は、トランジスタ 530 と、ビット線 BL と、導電膜 511 と、プラグ 515 と、導電膜 516 と、第 1 キャパシタ電極 512、第 2 キャパシタ電極 513 およびキャパシタ絶縁体 514 を有する記憶素子 520 を有している。

30

#### 【0135】

なお、図 10 および図 11 でハッチパターンが施されていない領域は絶縁体で構成された領域を表している。該当領域には、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどから選ばれた一種以上含む絶縁体を用いることができる。

#### 【0136】

トランジスタ 530 はオフ電流の低いトランジスタであるため、DRAM のメモリセルに用いることで、記憶素子 520 に蓄積された電荷の保持時間を長くすることができる。その結果、DRAM のリフレッシュの頻度を少なくすることができ、消費電力を下げる事が可能になる。

40

#### 【0137】

また、単結晶シリコンを使った SG T で  $4\text{F}^2$  のメモリセルを作製する場合、ソース領域およびドレイン領域を形成する際の不純物注入工程が複雑であるが、トランジスタ 530 で  $4\text{F}^2$  のメモリセルを作製する場合は、ソース領域およびドレイン領域形成の際の不純物注入工程が不要なので、製造工程を短縮することができる。

#### 【0138】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0139】

50

## (実施の形態 6 )

本実施の形態では、実施の形態 5 で示した記憶装置と半導体基板上に作製したトランジスタを組み合わせた例について図面を参照して説明する。

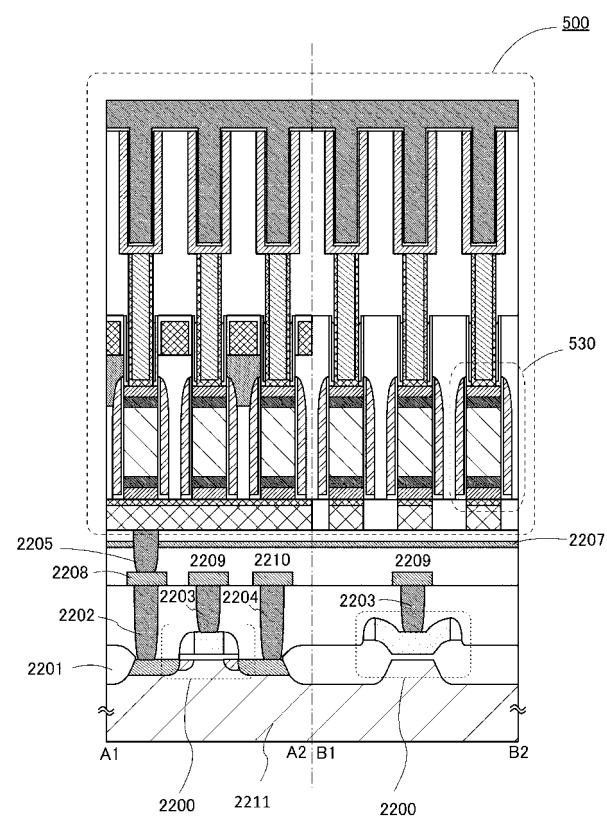

## 【0140】

図 12 は実施の形態 5 で示した記憶装置 500 と、トランジスタ 2200 と、素子分離層 2201 と、プラグ 2202 乃至 2205 と、配線 2208 乃至 2210 と、絶縁層 2207 と、半導体基板 2211 を有している。図 12 でハッチパターンが施されていない領域は、絶縁体で構成されている。図 12 の左半分の領域は、図 9 の A1-A2 線断面図を示し、図 12 の右半分の領域は、図 9 の B1-B2 線断面図を示している。

## 【0141】

半導体基板 2211 に使用される第 1 の半導体材料は、トランジスタ 530 に使用される第 2 の半導体材料とは異なる禁制帯幅を持つ材料とすることが好ましい。例えば、第 1 の半導体材料を酸化物半導体以外の半導体材料（多結晶構造、単結晶構造などのシリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素など）とし、第 2 の半導体材料を酸化物半導体とすることができます。酸化物半導体以外の材料として単結晶シリコンなどを用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、オフ電流が低い。

10

## 【0142】

例えば、第 1 の半導体として歪みシリコンなどの歪みを有する半導体を用いてもよい。または、第 1 の半導体として高電子移動度トランジスタ（HEMT：High Electron Mobility Transistor）に適用可能なヒ化ガリウム、ヒ化アルミニウムガリウム、ヒ化インジウムガリウム、窒化ガリウム、リン化インジウム、シリコンゲルマニウムなどを用いてもよい。これらの半導体を第 1 の半導体に用いることで、高速動作をすることに適したトランジスタ 2200 とすることができます。

20

## 【0143】

トランジスタ 2200 は、n チャネル型のトランジスタまたは p チャネル型のトランジスタのいずれであってもよく、回路によって適切なトランジスタを用いればよい。また、酸化物半導体を用いた本発明の一態様のトランジスタを用いるほかは、用いる材料や構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

30

## 【0144】

このように、2種類のトランジスタを積層することにより、回路の占有面積が低減され、より高密度に複数の回路を配置することができる。例えば、トランジスタ 2200 を用いて記憶装置 500 の駆動回路を形成してもよい。

## 【0145】

ここで、下層に設けられるトランジスタ 2200 にシリコン系半導体材料を用いた場合、トランジスタ 2200 の半導体層の近傍に設けられる絶縁層中の水素はシリコンのダングリングボンドを終端し、トランジスタ 2200 の信頼性を向上させる効果がある。一方、上層に設けられるトランジスタ 530 に酸化物半導体を用いた場合、酸化物半導体層の近傍に設けられる絶縁層中の水素は、酸化物半導体中にキャリアを生成する要因の一つとなるため、トランジスタ 530 の信頼性を低下させる要因となる場合がある。したがって、シリコン系半導体材料を用いたトランジスタ 2200 の上層に酸化物半導体を用いたトランジスタ 530 を積層して設ける場合、これらの間に水素の移動を防止する機能を有する絶縁層 2207 を設けることは特に効果的である。絶縁層 2207 により、下層に水素を閉じ込めてトランジスタ 2200 の信頼性が向上することに加え、下層から上層への水素拡散が抑制されることでトランジスタ 530 の信頼性も同時に向上させることができる。

40

## 【0146】

絶縁層 2207 としては、例えば酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、イットリア安定化ジルコニア（YSZ）等を用いることができる。

50

## 【0147】

なお、トランジスタ2200は、プレーナー型のトランジスタだけでなく、様々なタイプのトランジスタとすることができる。例えば、FIN(フィン)型、TRI-GATE(トライゲート)型などのトランジスタなどとすることができる。その場合の断面図の例を、図13に示す。半導体基板2211の上に、絶縁層2212が設けられている。半導体基板2211は、先端の細い凸部(フィンともいう。)を有する。なお、凸部の上には、絶縁膜が設けられてもよい。その絶縁膜は、凸部を形成するときに、半導体基板2211がエッチングされないようにするためのマスクとして機能するものである。なお、凸部は、先端が細くなくてもよく、例えば、略直方体の凸部であってもよいし、先端が太い凸部であってもよい。半導体基板2211の凸部の上には、ゲート絶縁膜2214が設けられ、その上には、ゲート電極2213が設けられている。半導体基板2211には、ソース領域およびドレイン領域2215が形成されている。なお、ここでは、半導体基板2211が、凸部を有する例を示したが、本発明の一態様に係る半導体装置は、これに限定されない。例えば、SOI基板を加工して、凸部を有する半導体領域を形成しても構わない。

10

## 【0148】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【0149】

20

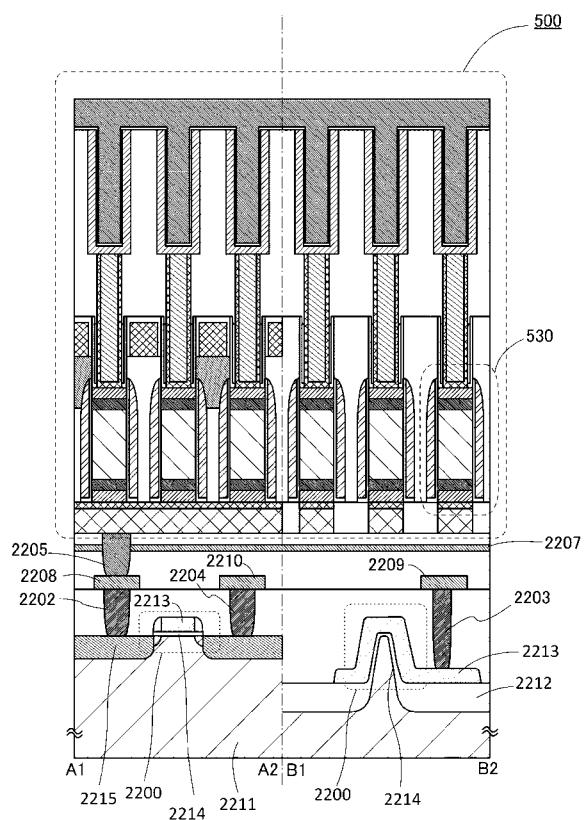

## (実施の形態7)

本実施の形態では、本発明の一態様であるトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い記憶装置の一例を、図面を参照して説明する。

## 【0150】

30

図14(A)に示すメモリセルは、第1の半導体材料を用いたトランジスタ3200と第2の半導体材料を用いたトランジスタ3300、および容量素子3400を有している。なお、トランジスタ3300としては、上記実施の形態で説明したトランジスタを用いることができる。

## 【0151】

40

トランジスタ3300は、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタである。トランジスタ3300は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

## 【0152】

50

図14(A)において、第1の配線3001はトランジスタ3200のソース電極と電気的に接続され、第2の配線3002はトランジスタ3200のドレイン電極と電気的に接続されている。また、第3の配線3003はトランジスタ3300のソース電極またはドレイン電極の一方と電気的に接続され、第4の配線3004はトランジスタ3300のゲート電極と電気的に接続されている。そして、トランジスタ3200のゲート電極、およびトランジスタ3300のソース電極またはドレイン電極の他方は、容量素子3400の第1の端子と電気的に接続され、第5の配線3005は容量素子3400の第2の端子と電気的に接続されている。

## 【0153】

図14(A)に示すメモリセルでは、トランジスタ3200のゲート電極の電位が保持可能という特徴を活かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

## 【0154】

情報の書き込みおよび保持について説明する。まず、第4の配線3004の電位を、トランジスタ3300がオン状態となる電位にして、トランジスタ3300をオン状態とする

50

。これにより、第3の配線3003の電位が、トランジスタ3200のゲート電極、および容量素子3400に与えられる。すなわち、トランジスタ3200のゲートには、所定の電荷が与えられる（書き込み）。ここでは、異なる二つの電位レベルを与える電荷（以下Lowレベル電荷、Highレベル電荷という）のいずれかが与えられるものとする。その後、第4の配線3004の電位を、トランジスタ3300がオフ状態となる電位にして、トランジスタ3300をオフ状態とすることにより、トランジスタ3200のゲートに与えられた電荷が保持される（保持）。

#### 【0155】

トランジスタ3300のオフ電流は極めて小さいため、トランジスタ3200のゲートの電荷は長時間にわたって保持される。

10

#### 【0156】

次に情報の読み出しについて説明する。第1の配線3001に所定の電位（定電位）を与えた状態で、第5の配線3005に適切な電位（読み出し電位）を与えると、トランジスタ3200のゲートに保持された電荷量に応じて、第2の配線3002は異なる電位をとる。一般に、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲート電極にHighレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、トランジスタ3200のゲート電極にLowレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ3200を「オン状態」とするために必要な第5の配線3005の電位をいうものとする。したがって、第5の配線3005の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ3200のゲートに与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$ （ $> V_{th\_H}$ ）となれば、トランジスタ3200は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0$ （ $< V_{th\_L}$ ）となつても、トランジスタ3200は「オフ状態」のままである。このため、第2の配線3002の電位を判別することで、保持されている情報を読み出すことができる。

20

#### 【0157】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲートの状態にかかわらずトランジスタ3200が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線3005に与えればよい。または、ゲートの状態にかかわらずトランジスタ3200が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線3005に与えればよい。

30

#### 【0158】

図14(B)に示すメモリセルは、トランジスタ3200を設けていない点で図14(A)と相違している。この場合も上記と同様の動作により情報の書き込み及び保持動作が可能である。

#### 【0159】

次に、情報の読み出しについて説明する。トランジスタ3300がオン状態となると、浮遊状態である第3の配線3003と容量素子3400とが導通し、第3の配線3003と容量素子3400の間で電荷が再分配される。その結果、第3の配線3003の電位が変化する。第3の配線3003の電位の変化量は、容量素子3400の第1の端子の電位（または容量素子3400に蓄積された電荷）によって、異なる値をとる。

40

#### 【0160】

例えば、容量素子3400の第1の端子の電位をV、容量素子3400の容量をC、第3の配線3003が有する容量成分をCB、電荷が再分配される前の第3の配線3003の電位をVB0とすると、電荷が再分配された後の第3の配線3003の電位は、 $(CB \times VB0 + C \times V) / (CB + C)$ となる。したがって、メモリセルの状態として、容量素子3400の第1の端子の電位がV1とV0 ( $V1 > V0$ ) の2状態をとるとすると、電

50

位  $V_1$  を保持している場合の第 3 の配線 3003 の電位 ( $= (C_B \times V_B 0 + C \times V_1) / (C_B + C)$ ) は、電位  $V_0$  を保持している場合の第 3 の配線 3003 の電位 ( $= C_B \times V_B 0 + C \times V_0) / (C_B + C)$ ) よりも高くなることがわかる。

#### 【0161】

そして、第 3 の配線 3003 の電位を所定の電位と比較することで、情報を読み出すことができる。

#### 【0162】

この場合、メモリセルを駆動させるための駆動回路に上記第 1 の半導体材料が適用されたトランジスタを用い、トランジスタ 3300 として第 2 の半導体材料が適用されたトランジスタを駆動回路上に積層して設ける構成とすればよい。

10

#### 【0163】

本実施の形態に示すメモリセルでは、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合（ただし、電位は固定されていることが望ましい）であっても、長期にわたって記憶内容を保持することが可能である。

#### 【0164】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁膜の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。

20

#### 【0165】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0166】

##### （実施の形態 8）

30

本実施の形態では、本発明の一態様であるトランジスタを使用した表示装置の構成例について説明する。

#### 【0167】

##### [構成例]

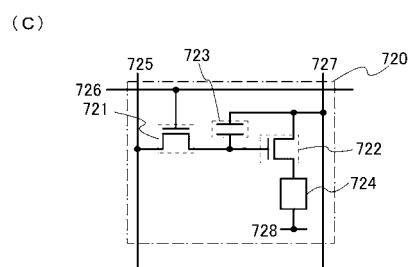

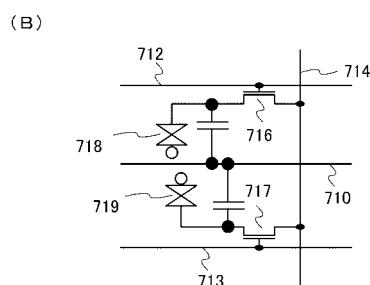

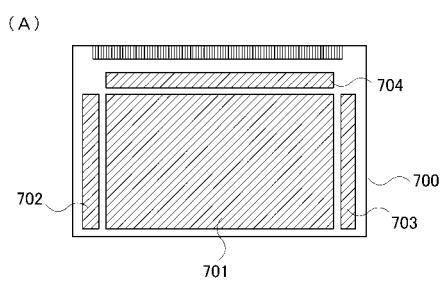

図 15 (A) は、本発明の一態様の表示装置の上面図であり、図 15 (B) は、本発明の一態様の表示装置の画素に液晶素子を適用する場合に用いることができる画素回路を説明するための回路図である。また、図 15 (C) は、本発明の一態様の表示装置の画素に有機 E L (エレクトロルミネッセンス) 素子を適用する場合に用いることができる画素回路を説明するための回路図である。

40

#### 【0168】

画素部に配置するトランジスタは、上記実施の形態に従って形成することができる。また、当該トランジスタは  $n$  チャネル型とすることが容易なので、駆動回路のうち、 $n$  チャネル型トランジスタで構成することができる駆動回路の一部を画素部のトランジスタと同一基板上に形成する。このように、画素部や駆動回路に上記実施の形態に示すトランジスタを用いることにより、信頼性の高い表示装置を提供することができる。

#### 【0169】

アクティブラーマトリクス型表示装置の上面図の一例を図 15 (A) に示す。表示装置の基板 700 上には、画素部 701、第 1 の走査線駆動回路 702、第 2 の走査線駆動回路 703、信号線駆動回路 704 を有する。画素部 701 には、複数の信号線が信号線駆動回路 704 から延伸して配置され、複数の走査線が第 1 の走査線駆動回路 702、及び第 2 の

50

走査線駆動回路 703 から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に設けられている。また、表示装置の基板 700 は FPC (Flexible Printed Circuit) 等の接続部を介して、タイミング制御回路（コントローラ、制御 IC ともいう）に接続されている。

#### 【0170】

図 15 (A) では、第 1 の走査線駆動回路 702、第 2 の走査線駆動回路 703、信号線駆動回路 704 は、画素部 701 と同じ基板 700 上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板 700 外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板 700 上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。10

#### 【0171】

##### 〔液晶表示装置〕

また、画素の回路構成の一例を図 15 (B) に示す。ここでは、VA 型液晶表示装置の画素に適用することができる画素回路を示す。

#### 【0172】

この画素回路は、一つの画素に複数の画素電極層を有する構成に適用できる。それぞれの画素電極層は異なるトランジスタに接続され、各トランジスタは異なるゲート信号で駆動できるように構成されている。これにより、マルチドメイン設計された画素の個々の画素電極層に印加する信号を、独立して制御できる。20

#### 【0173】

トランジスタ 716 のゲート配線 712 と、トランジスタ 717 のゲート配線 713 には、異なるゲート信号を与えることができるよう分離されている。一方、データ線として機能するソース電極又はドレイン電極 714 は、トランジスタ 716 とトランジスタ 717 で共通に用いられている。トランジスタ 716 とトランジスタ 717 は上記実施の形態で説明するトランジスタを適宜用いることができる。これにより、信頼性の高い液晶表示装置を提供することができる。

#### 【0174】

トランジスタ 716 と電気的に接続する第 1 の画素電極層と、トランジスタ 717 と電気的に接続する第 2 の画素電極層の形状について説明する。第 1 の画素電極層と第 2 の画素電極層の形状は、スリットによって分離されている。第 1 の画素電極層は V 字型に広がる形状を有し、第 2 の画素電極層は第 1 の画素電極層の外側を囲むように形成される。30

#### 【0175】

トランジスタ 716 のゲート電極はゲート配線 712 と接続され、トランジスタ 717 のゲート電極はゲート配線 713 と接続されている。ゲート配線 712 とゲート配線 713 に異なるゲート信号を与えてトランジスタ 716 とトランジスタ 717 の動作タイミングを異らせ、液晶の配向を制御できる。

#### 【0176】

また、容量配線 710 と、誘電体として機能するゲート絶縁膜と、第 1 の画素電極層または第 2 の画素電極層と電気的に接続する容量電極とで保持容量を形成してもよい。

#### 【0177】

マルチドメイン構造は、一画素に第 1 の液晶素子 718 と第 2 の液晶素子 719 を備える。第 1 の液晶素子 718 は第 1 の画素電極層と対向電極層とその間の液晶層とで構成され、第 2 の液晶素子 719 は第 2 の画素電極層と対向電極層とその間の液晶層とで構成される。

#### 【0178】

なお、図 15 (B) に示す画素回路は、これに限定されない。例えば、図 15 (B) に示す画素に新たにスイッチ、抵抗素子、容量素子、トランジスタ、センサ、又は論理回路などを追加してもよい。

#### 【0179】

10

20

30

40

50

## 〔有機 E L 表示装置〕

画素の回路構成の他の一例を図 15 (C) に示す。ここでは、有機 E L 素子を用いた表示装置の画素構造を示す。

## 【0180】

有機 E L 素子は、発光素子に電圧を印加することにより、一対の電極の一方から電子が、他方から正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、電子および正孔が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

## 【0181】

図 15 (C) は、適用可能な画素回路の一例を示す図である。ここでは n チャネル型のトランジスタを 1 つの画素に 2 つ用いる例を示す。なお、本発明の一態様の金属酸化物膜は、n チャネル型のトランジスタのチャネル形成領域に用いることができる。また、当該画素回路は、デジタル時間階調駆動を適用することができる。

## 【0182】

適用可能な画素回路の構成及びデジタル時間階調駆動を適用した場合の画素の動作について説明する。

## 【0183】

画素 720 は、スイッチング用トランジスタ 721、駆動用トランジスタ 722、発光素子 724 及び容量素子 723 を有している。スイッチング用トランジスタ 721 は、ゲート電極が走査線 726 に接続され、第 1 電極（ソース電極及びドレイン電極の一方）が信号線 725 に接続され、第 2 電極（ソース電極及びドレイン電極の他方）が駆動用トランジスタ 722 のゲート電極に接続されている。駆動用トランジスタ 722 は、ゲート電極が容量素子 723 を介して電源線 727 に接続され、第 1 電極が電源線 727 に接続され、第 2 電極が発光素子 724 の第 1 電極（画素電極）に接続されている。発光素子 724 の第 2 電極は共通電極 728 に相当する。共通電極 728 は、同一基板上に形成される共通電位線と電気的に接続される。

## 【0184】

スイッチング用トランジスタ 721 および駆動用トランジスタ 722 は上記実施の形態で説明するトランジスタを適宜用いることができる。これにより、信頼性の高い有機 E L 表示装置を提供することができる。

## 【0185】

発光素子 724 の第 2 電極（共通電極 728）の電位は低電源電位に設定する。なお、低電源電位とは、電源線 727 に供給される高電源電位を基準にして低電源電位 < 高電源電位を満たす電位であり、低電源電位としては例えば GND、0 V などが設定されていても良い。発光素子 724 の順方向のしきい値電圧以上となるように高電源電位と低電源電位を設定し、その電位差を発光素子 724 に印加することにより、発光素子 724 に電流を流して発光させる。なお、発光素子 724 の順方向電圧とは、所望の輝度とする場合の電圧を指しており、少なくとも順方向しきい値電圧を含む。

## 【0186】

なお、容量素子 723 は駆動用トランジスタ 722 のゲート容量を代用することにより省略できる。駆動用トランジスタ 722 のゲート容量については、チャネル形成領域とゲート電極との間で容量が形成されていてもよい。

## 【0187】

次に、駆動用トランジスタ 722 に入力する信号について説明する。電圧入力電圧駆動方式の場合、駆動用トランジスタ 722 が十分にオンするか、オフするかの二つの状態となるようなビデオ信号を、駆動用トランジスタ 722 に入力する。なお、駆動用トランジスタ 722 を線形領域で動作させるために、電源線 727 の電圧よりも高い電圧を駆動用トランジスタ 722 のゲート電極にかける。また、信号線 725 には、電源線電圧に駆動用トランジスタ 722 の閾値電圧  $V_{th}$  を加えた値以上の電圧をかける。

10

20

30

40

50

## 【0188】

アナログ階調駆動を行う場合、駆動用トランジスタ722のゲート電極に発光素子724の順方向電圧に駆動用トランジスタ722の閾値電圧V<sub>th</sub>を加えた値以上の電圧をかける。なお、駆動用トランジスタ722が飽和領域で動作するようにビデオ信号を入力し、発光素子724に電流を流す。また、駆動用トランジスタ722を飽和領域で動作させるために、電源線727の電位を、駆動用トランジスタ722のゲート電位より高くする。ビデオ信号をアナログとすることで、発光素子724にビデオ信号に応じた電流を流し、アナログ階調駆動を行うことができる。

## 【0189】

なお、画素回路の構成は、図15(C)に示す画素構成に限定されない。例えば、図15(C)に示す画素回路にスイッチ、抵抗素子、容量素子、センサ、トランジスタ又は論理回路などを追加してもよい。

## 【0190】

図15で例示した回路に上記実施の形態で例示したトランジスタを適用する場合、低電位側にソース電極(第1の電極)、高電位側にドレイン電極(第2の電極)がそれぞれ電気的に接続される構成とする。さらに、制御回路等により第1のゲート電極の電位を制御し、第2のゲート電極には図示しない配線によりソース電極に与える電位よりも低い電位など、上記で例示した電位を入力可能な構成とすればよい。

## 【0191】

例えば、本明細書等において、表示素子、表示素子を有する装置である表示装置、発光素子、及び発光素子を有する装置である発光装置は、様々な形態を用いること、又は様々な素子を有することが出来る。表示素子、表示装置、発光素子又は発光装置の一例としては、E L(エレクトロルミネッセンス)素子(有機物及び無機物を含むE L素子、有機E L素子、無機E L素子)、L E D(白色L E D、赤色L E D、緑色L E D、青色L E Dなど)、トランジスタ(電流に応じて発光するトランジスタ)、電子放出素子、液晶素子、電子インク、電気泳動素子、グレーティングライトバルブ(G L V)、プラズマディスプレイ(P D P)、M E M S(マイクロ・エレクトロ・メカニカル・システム)、デジタルマイクロミラーデバイス(D M D)、D M S(デジタル・マイクロ・シャッター)、M I R A S O L(登録商標)、I M O D(インターフェアレンス・モジュレーション)素子、エレクトロウェッティング素子、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用により、コントラスト、輝度、反射率、透過率などが変化する表示媒体を有するものがある。E L素子を用いた表示装置の一例としては、E Lディスプレイなどがある。電子放出素子を用いた表示装置の一例としては、フィールドエミッションディスプレイ(F E D)又はS E D方式平面型ディスプレイ(S E D:Surface-conduction E lectr on - e mitter D isplay)などがある。液晶素子を用いた表示装置の一例としては、液晶ディスプレイ(透過型液晶ディスプレイ、半透過型液晶ディスプレイ、反射型液晶ディスプレイ、直視型液晶ディスプレイ、投射型液晶ディスプレイ)などがある。電子インク又は電気泳動素子を用いた表示装置の一例としては、電子ペーパーなどがある。

## 【0192】

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

## 【0193】

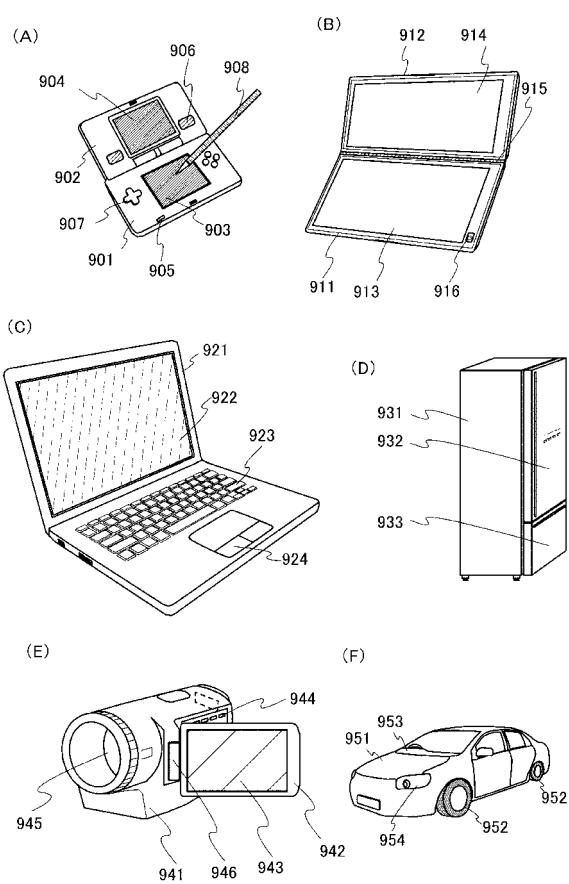

## (実施の形態9)

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置(代表的にはD V D:D i g i t a l V e r s a t i l e D i s c等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置)に用いることができる。その他に、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍端末、ビデオカメラ、デジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタ

10

20

30

40

50

ルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリンタ複合機などが挙げられる。これら電子機器の具体例を図16に示す。

#### 【0194】

図16(A)は携帯型ゲーム機であり、筐体901、筐体902、表示部903、表示部904、マイクロフォン905、スピーカー906、操作キー907、スタイルス908等を有する。なお、図16(A)に示した携帯型ゲーム機は、2つの表示部903と表示部904とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

#### 【0195】

図16(B)は携帯データ端末であり、第1筐体911、第2筐体912、第1表示部913、第2表示部914、接続部915、操作キー916等を有する。第1表示部913は第1筐体911に設けられており、第2表示部914は第2筐体912に設けられている。そして、第1筐体911と第2筐体912とは、接続部915により接続されており、第1筐体911と第2筐体912との間の角度は、接続部915により変更が可能である。第1表示部913における映像を、接続部915における第1筐体911と第2筐体912との間の角度に従って、切り替える構成としても良い。また、第1表示部913および第2表示部914の少なくとも一方に、位置入力装置としての機能が付加された表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、表示装置にタッチパネルを設けることで付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を表示装置の画素部に設けることでも、付加することができる。

#### 【0196】

図16(C)はノート型パーソナルコンピュータであり、筐体921、表示部922、キーボード923、ポインティングデバイス924等を有する。

#### 【0197】

図16(D)は電気冷凍冷蔵庫であり、筐体931、冷蔵室用扉932、冷凍室用扉933等を有する。

#### 【0198】

図16(E)はビデオカメラであり、第1筐体941、第2筐体942、表示部943、操作キー944、レンズ945、接続部946等を有する。操作キー944およびレンズ945は第1筐体941に設けられており、表示部943は第2筐体942に設けられている。そして、第1筐体941と第2筐体942とは、接続部946により接続されており、第1筐体941と第2筐体942との間の角度は、接続部946により変更が可能である。表示部943における映像を、接続部946における第1筐体941と第2筐体942との間の角度に従って切り替える構成としても良い。

#### 【0199】

図16(F)は普通自動車であり、車体951、車輪952、ダッシュボード953、ライト954等を有する。

#### 【0200】

(実施の形態10)

上記の実施の形態で説明した記憶装置は、様々なプロセッサ(例えば、CPU、マイクロコントローラ、FPGAなどのプログラマブルデバイス、RFタグ)のキャッシュメモリ、メインメモリ、ストレージに用いることができる。本実施の形態では、上記記憶装置を用いたRFタグの使用例について図17を用いながら説明する。RFタグの用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類(運転免許証や住民票等、図17(A)参照)、包装用容器類(包装紙やボトル等、図17(C)参照)、記録媒体(DVDやビデオテープ等、図17(B)参照)、乗り物類(自転車等、図17(D)参照)、身の回り品(鞄や眼鏡等)、食品類、植物類、動物類、人体、衣類、生活用品類、薬品や薬剤を含む医療品、または電子機器(液晶表示装置、EL表示装置、テレビジョン装置、または携帯電話)等の物品、若しくは各物品に取り付ける荷札(図17(E)

10

20

30

40

50

)、図17(F参照)等に設けて使用することができる。

**【0201】**

本発明の一態様に係るRFタグ4000は、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込み、有機樹脂からなるパッケージであれば当該有機樹脂の内部に埋め込み、各物品に固定される。本発明の一態様に係るRFタグ4000は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類等に本発明の一態様に係るRFタグ4000を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器等に本発明の一態様に係るRFタグを取り付けることにより、検品システム等のシステムの効率化を図ることができる。また、乗り物類であっても、本発明の一態様に係るRFタグを取り付けることにより、盗難などに対するセキュリティ性を高めることができる。

**【0202】**

以上のように、本発明の一態様に係わるRFタグを本実施の形態に挙げた各用途に用いることにより、情報の書き込みや読み出しを含む動作電力を低減できるため、最大通信距離を長くとることが可能となる。また、電力が遮断された状態であっても情報を極めて長い期間保持可能であるため、書き込みや読み出しの頻度が低い用途にも好適に用いることができる。

**【0203】**

本実施の形態は、少なくともその一部を本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

**【実施例1】**

**【0204】**

本実施例では、昇温脱離分析(TDS分析)により、酸化ルテニウムに含まれる酸素の脱離に関して調査した結果について説明する。

**【0205】**

昇温脱離分析とは、高真空で試料を赤外線加熱しながら放出されるガス分子を質量分析することにより、温度毎に試料からの脱離成分の質量スペクトルを得るものである。測定装置のバックグラウンド真空度は、 $1.33 \times 10^{-7}$  Pa ( $10^{-9}$  Torr) であるため、極微量成分についての分析が可能である。本実施例では、ESCO社のEMD-WA1000Sを使用した。

**【0206】**

また、TDS分析の結果を示す曲線におけるピークは、分析した試料に含まれる原子または分子が外部に放出されることで現れるピークである。なお、外部に放出される原子または分子の総量は、当該ピークの積分値に相当する。それゆえ、当該ピーク強度の高低によって、酸化ルテニウム膜に含まれる原子または分子の総量を評価することができる。

**【0207】**

本実施例では、シリコンウェハ上に、スパッタリング法を用いて酸化ルテニウム膜を成膜した。酸化ルテニウムの成膜条件は、酸素流量を20 sccm、処理室内の圧力を0.4 Pa、100 W(DC)、ターゲット-基板間距離を60 mm、基板温度を150 °とした。なお、酸化ルテニウムの膜厚を、10 nm、30 nm、50 nm、100 nm、200 nmの5条件とした。ここで、膜厚が10 nmの酸化ルテニウムを試料Aとし、30 nmの酸化ルテニウムを試料Bとし、50 nmの酸化ルテニウムを試料Cとし、100 nmの酸化ルテニウムを試料Dとし、200 nmの酸化ルテニウムを試料Eとする。

**【0208】**

次に、試料A乃至試料Eに対して、TDS分析を行った結果を、図18に示す。図18は、基板温度に対する酸素分子放出量を示したグラフである。

**【0209】**

図18に示すTDS分析結果より、酸化ルテニウムが10 nmの場合であっても、酸素分

10

20

30

40

50

子の放出が確認された。また、酸化ルテニウムの膜厚が増加するにつれ、酸素分子の放出量が増加することが確認された。

## 【0210】

以上の結果から、酸化ルテニウムは、加熱によって、酸素を脱離させることが可能な膜であることが確認された。

## 【符号の説明】

## 【0211】

|       |          |    |

|-------|----------|----|

| 100   | トランジスタ   |    |

| 101   | 配線       |    |

| 102   | ゲート電極    | 10 |

| 103   | ソース電極    |    |

| 104   | 酸化物半導体   |    |

| 105   | ドレイン電極   |    |

| 106   | ゲート絶縁膜   |    |

| 107   | 保護絶縁膜    |    |

| 108   | 層間絶縁膜    |    |

| 109   | 基板       |    |

| 110   | トランジスタ   |    |

| 111   | 導電膜      |    |

| 113   | ソース電極    | 20 |

| 113 a | 導電膜      |    |

| 113 b | 導電膜      |    |

| 115   | ドレイン電極   |    |

| 115 a | 導電膜      |    |

| 115 b | 導電膜      |    |

| 202   | 導電膜      |    |

| 203   | 導電膜      |    |

| 204   | 酸化物半導体   |    |

| 205   | 導電膜      |    |

| 209   | 層間絶縁膜    | 30 |

| 211   | 導電膜      |    |

| 212   | プラグ      |    |

| 410   | トランジスタ   |    |

| 415   | ドレイン電極   |    |

| 420   | トランジスタ   |    |

| 423   | ソース電極    |    |

| 430   | トランジスタ   |    |

| 440   | トランジスタ   |    |

| 446   | プラグ      |    |

| 500   | 記憶装置     | 40 |

| 510   | コントラクト   |    |

| 511   | 導電膜      |    |

| 512   | キャパシタ電極  |    |

| 513   | キャパシタ電極  |    |

| 514   | キャパシタ絶縁体 |    |

| 515   | プラグ      |    |

| 516   | 導電膜      |    |

| 520   | 記憶素子     |    |

| 530   | トランジスタ   |    |

| 532   | ゲート電極    | 50 |

|         |               |    |

|---------|---------------|----|

| 5 3 3   | ソース電極         |    |

| 5 3 3 a | 導電膜           |    |

| 5 3 3 b | 導電膜           |    |

| 5 3 5   | ドレイン電極        |    |

| 5 3 5 a | 導電膜           |    |

| 5 3 5 b | 導電膜           |    |

| 5 3 6   | ゲート絶縁膜        |    |

| 7 0 0   | 基板            |    |

| 7 0 1   | 画素部           |    |

| 7 0 2   | 走査線駆動回路       | 10 |

| 7 0 3   | 走査線駆動回路       |    |

| 7 0 4   | 信号線駆動回路       |    |

| 7 1 0   | 容量配線          |    |

| 7 1 2   | ゲート配線         |    |

| 7 1 3   | ゲート配線         |    |

| 7 1 4   | ドレイン電極        |    |

| 7 1 6   | トランジスタ        |    |

| 7 1 7   | トランジスタ        |    |

| 7 1 8   | 液晶素子          |    |

| 7 1 9   | 液晶素子          | 20 |

| 7 2 0   | 画素            |    |

| 7 2 1   | スイッチング用トランジスタ |    |

| 7 2 2   | 駆動用トランジスタ     |    |

| 7 2 3   | 容量素子          |    |

| 7 2 4   | 発光素子          |    |

| 7 2 5   | 信号線           |    |

| 7 2 6   | 走査線           |    |

| 7 2 7   | 電源線           |    |

| 7 2 8   | 共通電極          |    |

| 9 0 1   | 筐体            | 30 |

| 9 0 2   | 筐体            |    |

| 9 0 3   | 表示部           |    |

| 9 0 4   | 表示部           |    |

| 9 0 5   | マイクロフォン       |    |

| 9 0 6   | スピーカー         |    |

| 9 0 7   | 操作キー          |    |

| 9 0 8   | スタイルス         |    |

| 9 1 1   | 筐体            |    |

| 9 1 2   | 筐体            |    |

| 9 1 3   | 表示部           | 40 |

| 9 1 4   | 表示部           |    |

| 9 1 5   | 接続部           |    |

| 9 1 6   | 操作キー          |    |

| 9 2 1   | 筐体            |    |

| 9 2 2   | 表示部           |    |

| 9 2 3   | キーボード         |    |

| 9 2 4   | ポインティングデバイス   |    |

| 9 3 1   | 筐体            |    |

| 9 3 2   | 冷藏室用扉         |    |

| 9 3 3   | 冷凍室用扉         | 50 |

|         |         |    |

|---------|---------|----|

| 9 4 1   | 筐体      |    |

| 9 4 2   | 筐体      |    |

| 9 4 3   | 表示部     |    |

| 9 4 4   | 操作キー    |    |

| 9 4 5   | レンズ     |    |

| 9 4 6   | 接続部     |    |

| 9 5 1   | 車体      |    |

| 9 5 2   | 車輪      |    |

| 9 5 3   | ダッシュボード |    |

| 9 5 4   | ライト     | 10 |

| 2 2 0 0 | トランジスタ  |    |

| 2 2 0 1 | 素子分離層   |    |

| 2 2 0 2 | プラグ     |    |

| 2 2 0 5 | プラグ     |    |

| 2 2 0 7 | 絶縁層     |    |

| 2 2 0 8 | 配線      |    |

| 2 2 1 0 | 配線      |    |

| 2 2 1 1 | 半導体基板   |    |

| 2 2 1 2 | 絶縁層     |    |

| 2 2 1 3 | ゲート電極   | 20 |

| 2 2 1 4 | ゲート絶縁膜  |    |

| 2 2 1 5 | ドレイン領域  |    |

| 3 0 0 1 | 配線      |    |

| 3 0 0 2 | 配線      |    |

| 3 0 0 3 | 配線      |    |

| 3 0 0 4 | 配線      |    |

| 3 0 0 5 | 配線      |    |

| 3 2 0 0 | トランジスタ  |    |

| 3 3 0 0 | トランジスタ  |    |

| 3 4 0 0 | 容量素子    | 30 |

| 4 0 0 0 | R F タグ  |    |

【図 1】

【図 2】

【図 3】

【図 4】

【図5】

【図6】

【図7】

【図8】

【図9】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図17】

【図18】

【図19】

## フロントページの続き

| (51) Int.Cl.             | F I          | テーマコード(参考) |

|--------------------------|--------------|------------|

| H 01 L 27/108 (2006.01)  | H 01 L 29/44 | S          |

| H 01 L 27/10 (2006.01)   | H 01 L 21/28 | 3 0 1 B    |

| H 01 L 21/8234 (2006.01) | H 01 L 21/28 | 3 0 1 R    |

| H 01 L 27/088 (2006.01)  | H 01 L 27/10 | 6 2 1 C    |

|                          | H 01 L 27/10 | 6 7 1 A    |

|                          | H 01 L 27/10 | 3 2 1      |

|                          | H 01 L 27/10 | 6 8 1 F    |

|                          | H 01 L 27/10 | 4 6 1      |

|                          | H 01 L 27/08 | 1 0 2 E    |

F ターム(参考) 5F048 AB01 AB03 AC01 AC10 BA01 BA14 BA16 BA19 BA20 BB11

BC06 BD06 BD07 BF15 BF16 BG06 BG11 CB01 CB03 CB04

CB07 DA23

5F083 AD02 AD06 AD24 AD48 AD69 GA06 GA10 GA25 GA28 HA06

HA10 JA02 JA03 JA05 JA36 JA37 JA38 JA39 JA40 JA43

JA56 JA60 KA01 KA05 LA00 LA12 LA16 MA06 MA16 MA19

NA01 PR21 PR22 PR33 PR40 ZA04 ZA12 ZA13 ZA15

5F110 AA04 AA06 AA07 AA16 BB01 BB06 BB08 BB11 CC09 CC10

DD01 DD02 DD03 DD05 DD13 EE01 EE02 EE03 EE04 EE14

EE22 EE24 EE42 EE44 EE45 FF01 FF02 FF04 FF09 FF12

FF27 FF28 FF29 FF30 GG01 GG13 GG14 GG15 GG16 GG17

GG22 GG23 GG24 GG28 GG35 GG42 GG43 GG44 GG45 HK01

HK02 HK03 HK06 HK17 HK18 HK21 HK22 HK26 HK33 HK34

HK35 HL01 HL02 HL03 HL04 HL14 HM02 HM04 HM12 HM17

HM19 NN03 NN22 NN23 NN24 NN33 NN34 NN35 NN40 NN72

NN73 NN74 NN77 NN78 QQ03 QQ19