(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2010-520662

(P2010-520662A)

(43) 公表日 平成22年6月10日(2010.6.10)

|                       |            |             |

|-----------------------|------------|-------------|

| (51) Int.Cl.          | F 1        | テーマコード (参考) |

| HO4N 5/335 (2006.01)  | HO4N 5/335 | 4M118       |

| HO1L 27/148 (2006.01) | HO1L 27/14 | 5C024       |

|                       | HO4N 5/335 | Z           |

審査請求 未請求 予備審査請求 未請求 (全 14 頁)

(21) 出願番号 特願2009-551679 (P2009-551679)

(86) (22) 出願日 平成20年2月20日 (2008.2.20)

(85) 翻訳文提出日 平成21年10月13日 (2009.10.13)

(86) 國際出願番号 PCT/US2008/002237

(87) 國際公開番号 WO2008/106035

(87) 國際公開日 平成20年9月4日 (2008.9.4)

(31) 優先権主張番号 11/680,078

(32) 優先日 平成19年2月28日 (2007.2.28)

(33) 優先権主張国 米国(US)

(71) 出願人 590000846

イーストマン コダック カンパニー

アメリカ合衆国 ニューヨーク州 ロチェ

スター ステート ストリート 343

(74) 代理人 100075258

弁理士 吉田 研二

(74) 代理人 100096976

弁理士 石田 純

(72) 発明者 マイセンザール エリック ジョン

アメリカ合衆国 ニューヨーク オンタリ

オ カウンティ ライン ロード 692

6

最終頁に続く

(54) 【発明の名称】可変解像度可変感度イメージセンサ

## (57) 【要約】

電荷結合素子(CCD)イメージセンサであって、(a)行列配置された複数個のCCDを有する二次元画素アレイと、(i)そのアレイ内の各CCDを一種類又は複数種類の共通タイミング信号でクロッキングできるよう各CCDに複数個ずつ設けられたゲートと、(ii)上記アレイに電気的に接続されており、第1共通タイミング信号でクロッキングされるゲートが並ぶ第1行、並びに第2又は第3共通タイミング信号でクロッキングされるゲートが並ぶ第2行を有する転送用領域であって、その第2行内に、第2共通タイミング信号でクロッキングされ電気的に連動するゲートの対たる第1連動対、並びに第3共通タイミング信号でクロッキングされ電気的に連動するゲートの対たる第2連動対が、それぞれ複数個ある転送用領域と、(b)第2行内ゲート下から信号電荷を受け取れるよう第2行付近に形成された水平シフトレジスタと、を備える。

FIG. 1

**【特許請求の範囲】****【請求項 1】**

(a) 行列配置された複数個の電荷結合素子を有する二次元画素アレイと、

(i) そのアレイ内の各電荷結合素子を一種類又は複数種類の共通タイミング信号でクロッキングできるよう各電荷結合素子に複数個ずつ設けられたゲートと、

(ii) 上記アレイに電気的に接続されており、第1共通タイミング信号でクロッキングされるゲートが並ぶ第1行、並びに第2又は第3共通タイミング信号でクロッキングされるゲートが並ぶ第2行を有する転送用領域であって、その第2行内に、第2共通タイミング信号でクロッキングされ電気的に連動するゲートの対たる第1連動対、並びに第3共通タイミング信号でクロッキングされ電気的に連動するゲートの対たる第2連動対が、それぞれ複数個ある転送用領域と、

(b) 第2行内ゲート下から信号電荷を受け取れるよう第2行付近に形成された水平シフトレジスタと、

を備える電荷結合素子イメージセンサ。

**【請求項 2】**

請求項1記載の電荷結合素子イメージセンサであって、その水平シフトレジスタが、容量超過分の信号電荷を排出するためのラテラルオーバフロードラインを有する電荷結合素子イメージセンサ。

**【請求項 3】**

請求項1記載の電荷結合素子イメージセンサであって、その水平シフトレジスタが双方にシフト可能なシフトレジスタである電荷結合素子イメージセンサ。

**【請求項 4】**

電荷結合素子上の電荷を転送する方法であって、

(a) 電荷結合素子アレイから転送用領域第1行内ゲート下へと電荷を転送するステップと、

(b) 転送用領域第1行内ゲート下から水平シフトレジスタへと一部画素対の電荷をシリアル転送するステップと、

(c) 転送用領域第1行内ゲート下に残っている電荷と水平シフトレジスタ内の同色電荷とでその水平位置が揃うよう水平シフトレジスタ内の電荷を第1方向に順次シフトさせるステップと、

(d) 同色画素間で電荷が結合されるよう転送用領域第1行内ゲート下に残っている電荷を水平シフトレジスタへと転送するステップと、

(e) 電荷結合素子アレイから転送用領域第1行内ゲート下へと次の1行分の電荷を転送するステップと、

(f) その電荷についてステップ(b)～(e)を繰り返すステップと、

を有する方法。

**【請求項 5】**

請求項4記載の方法であって、水平シフトレジスタ上の電荷を第1方向とは逆の第2方向にシフトするステップと、電荷結合素子アレイから転送されてくる更に2行分の電荷についてステップ(b)～(e)を繰り返すステップと、を有する方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明はカラーCCD(電荷結合素子)イメージセンサ、特に可変解像度低雑音イメージセンサに関する。

**【背景技術】****【0002】**

イメージセンサには三種類の属性が重視される。解像度、感度及び(多くの場合)フレームレートである。イメージセンサは、解像度が高い(画素数が多い)方が一般により精細な画像を得ることができ、感度が高い方がSNR(信号対雑音比)が良好になるため微

10

20

30

40

50

かな光景を好適に解像することができ、フレームレートが高い方が短時間で多くの画像を撮影できるため被写体の移動をうまく捉えることができる。

#### 【0003】

一般に、その光学的方式が同じなら、画素サイズが小さいイメージセンサの方が解像度が高く、画素サイズが大きい方が感度が高い。即ち、光学的サイズが同じなら解像度と感度は互いに反比例する。更に、解像度を高めると、フレームレートによって決まる画素読出レートが低下する。

#### 【0004】

そのため、普通の色配置を有するベイヤー色フィルタアレイを伴ったカラーイメージセンサにて、そのチップ上での処理で解像度向上と感度・フレームレート向上とを両立可能にすることが求められている。10

#### 【0005】

チップ上での処理が求められるのは、隣接する（通常は同色の）画素間で信号電荷をチップ外（＝オフチップ）デジタル処理により結合（ビニング）して感度を向上させる、という従来のオフチップ画素ビニングでは、次の式

##### [数1]

$$S N R_{off} = n^{1/2} S / (S + \dots^2)^{1/2}$$

から判るように、そのSNRがあまり改善されないからである。この式中、Sは画素1個分の信号電荷、 $\dots$ は増幅器雑音（一定値）、nは結合対象画素数、 $S^{1/2}$ の項は光ショット雑音である。この式の前提は、画素間で信号レベル差がないこと、並びにセンサ内増幅器雑音に比べ暗電流ショット雑音、クロッキング雑音、オフチップ電子回路/A D C（アナログデジタル変換）雑音等といった種類の雑音を無視しうることである（そのシステム構成に不備のないカメラならこれらの前提は普通に成り立つ）。また、このSNR改善と引き替えに解像度は $1/n$ 倍に低下する（フレームレートは変わらない）。20

#### 【0006】

これに対し、後述の通り、同色隣接画素の信号電荷をチップ上（＝オンチップ）で結合させた場合、次の式

##### [数2]

$$S N R_{on} = n S / (n S + \dots^2)^{1/2}$$

から判るように、SNRがより改善される可能性がある。特に、出力信号レベルが低いとき（光ショット雑音が増幅器雑音に勝るとき）に、増幅器雑音の影響を抑えることができる。30

#### 【0007】

特許文献1（発明者：D r a i j e r）には、こうしたオンチップ画素ビニング回路についての記載がある。ただ、この回路では、所望の出力が得られるよう一次記憶レジスタ及びそれに関わる制御ラインを設けねばならないため、その回路規模ひいてはチップサイズが大きくなる。即ち、生産歩留まりが低く高コストなデバイスになる。加えて、画素ビニング処理の際、個々の画素の電荷を上下方向だけでなく左右方向にも転送しなければならないため、不可避な製造欠陥による電荷転送エラーのリスクが高い。こちらの方は非特許文献1で詳細に説明されている。そして、画素ビニング処理を終えた後、一次記憶レジスタから読出レジスタへと信号電荷を転送するのである程度の時間がかかる分、そのフレームレートが低くなってしまう。40

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

【特許文献1】米国特許出願公開第2006/0109352号明細書（A1）

【特許文献2】米国特許第4613402号明細書

【特許文献3】米国特許第5130774号明細書

【特許文献4】米国特許第6624453号明細書（B2）

【特許文献5】米国特許出願公開第2004/0150733号明細書50

【特許文献 6】米国特許出願公開第 2006 / 0125943 号明細書

【特許文献 7】米国特許出願公開第 2005 / 0280726 号明細書

【非特許文献】

【0009】

【非特許文献 1】James R. Janesick, "Scientific Charge-Coupled Devices", SPIE Press, 2001, Chapter 5.4, pgs.449-450

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の目的は、上述した諸問題を克服することにある。

10

【課題を解決するための手段】

【0011】

上述した諸問題のうち 1 個又は複数個を克服するため、本発明の好適な実施形態に係る CCD イメージセンサは、(a) 行列配置された複数個の CCD を有する二次元画素アレイと、(i) そのアレイ内の各 CCD を一種類又は複数種類の共通タイミング信号でクロッキングできるよう各 CCD に複数個ずつ設けられたゲートと、(ii) 上記アレイに電気的に接続されており、第 1 共通タイミング信号でクロッキングされるゲートが並ぶ第 1 行、並びに第 2 又は第 3 共通タイミング信号でクロッキングされるゲートが並ぶ第 2 行を有する転送用領域(transition region)であって、その第 2 行内に、第 2 共通タイミング信号でクロッキングされ電気的に連動するゲートの対たる第 1 連動対、並びに第 3 共通タイミング信号でクロッキングされ電気的に連動するゲートの対たる第 2 連動対が、それぞれ複数個ある転送用領域と、(b) 第 2 行内ゲート下から信号電荷を受け取れるよう第 2 行付近に形成された水平シフトレジスタ(horizontal shift register)と、を備える。

20

【発明の効果】

【0012】

本発明によれば、構成部材追加によるコスト増無しに、従ってその部材への入出力に係るクロックサイクルの追加による処理時間増加無しに、カラー画素ピニングを行うことができる。

30

【図面の簡単な説明】

【0013】

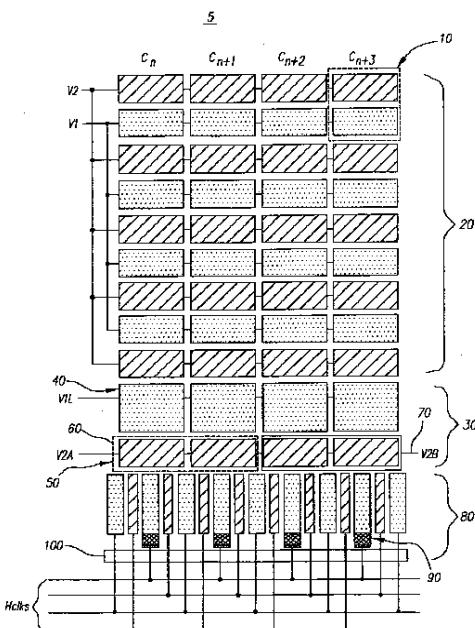

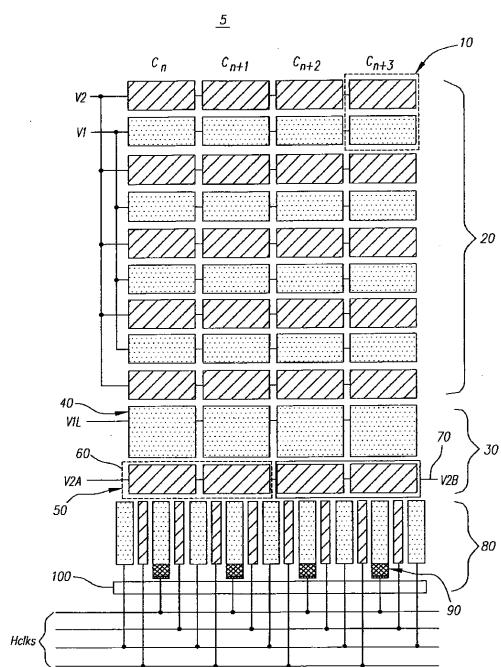

【図 1】本発明のイメージセンサ及びその HCCD を示す図である。

【図 2 a】そのイメージセンサにおける電荷転送動作を示す図である。

【図 2 b】その続きを示す図である。

【図 2 c】その続きを示す図である。

【図 2 d】その続きを示す図である。

【図 2 e】その続きを示す図である。

【図 2 f】その続きを示す図である。

【図 2 g】その続きを示す図である。

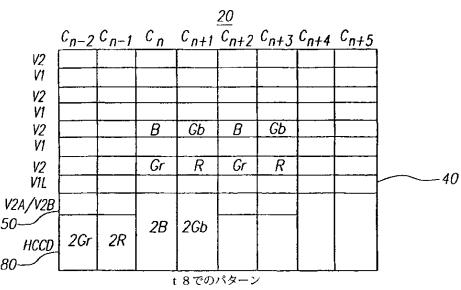

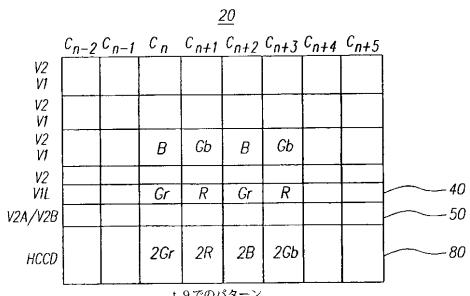

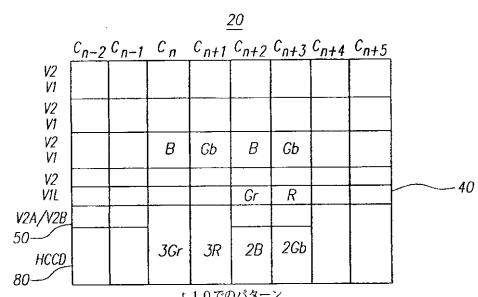

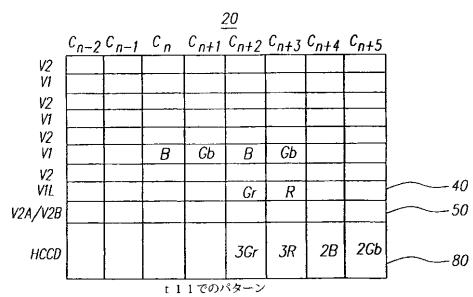

【図 2 h】その続きを示す図である。

【図 2 i】その続きを示す図である。

【図 2 j】その続きを示す図である。

【図 2 k】その続きを示す図である。

【図 2 l】その続きを示す図である。

【図 2 m】その続きを示す図である。

【図 2 n】その続きを示す図である。

【図 2 o】その続きを示す図である。

【図 2 p】その続きを示す図である。

【図 2 q】その続きを示す図である。

【図 2 r】その続きを示す図である。

40

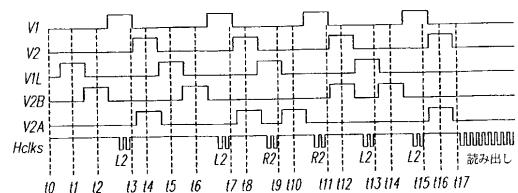

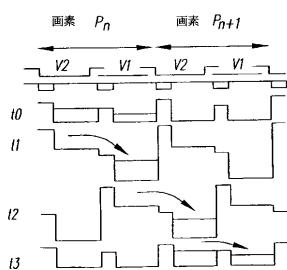

【図 3】図 2 a ~ 図 2 r に示した動作のタイミング図である。

50

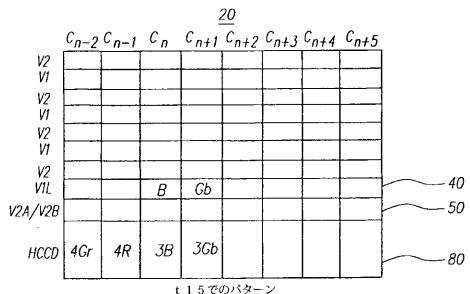

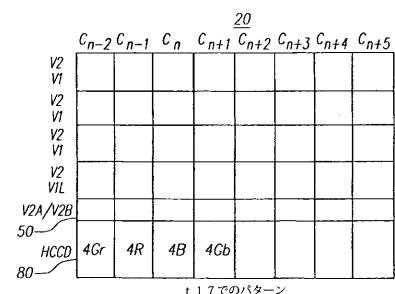

【図4a】フル解像度読出時の対画素アレイ及び転送用領域クロッキング動作を示す図である。

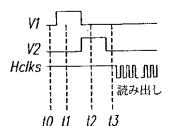

【図4b】本発明の画素アレイによる真正二相クロッキング動作を示す図である。

【発明を実施するための形態】

【0014】

以下、上記以外のものも含めて本発明の実施形態、目的、構成及び効果をより的確にご理解頂けるよう、別紙特許請求の範囲に基づき且つ別紙図面を参照しつつ、本発明の好適な実施形態に関し説明する。

【0015】

なお、本願中の「共通タイミング信号」は同じタイミング及び電位でゲートを駆動する電気信号のことである。同じタイミング及び電位であればよいので、共通タイミング信号の供給に使用する入力ラインの物理的本数は1本でも複数本でもよい。

【0016】

図1に、本発明の一実施形態に係る真正二相イメージセンサ5の構成を示す。このセンサ5では、各画素10(図中破線)が本件技術分野で周知の2ゲートアーキテクチャを探っている。例えば個々の画素10をNMOS構造のCCD(=nチャネルCCD)にし、そのCCDをこの2ゲートアーキテクチャにした場合、両ゲートと共に低電位になると画素10上の信号電荷が両ゲート下に分散し、一方のゲートを高電位、他方のゲートを低電位になると画素10上の全信号電荷が高電位な方のゲート下に帰集する。なお、各画素10をPMOS構造のCCD(=pチャネルCCD)にした場合は電位の関係が逆になる。真正二相イメージセンサの更なる詳細については特許文献2を参照されたい。

【0017】

まず、本センサ5は、画素アレイ20、そのアレイ20に電気的に接続されている転送用領域30、並びにその領域30に電気的に接続されている水平シフトレジスタ80を備えている。領域30は、あるライン(=第1行)に沿って複数個のゲートが配された第1部分40と、別のライン(=第2行)に沿って別の複数個のゲートが配された第2部分50とを有しており、第2部分50に属する複数個のゲートによって二種類の連動対60,70が各複数個形成されている。第1行内ゲートは共通タイミング信号V1Lによってクロッキングされており、第2行内ゲートのうち第1連動対60を形成するゲート(図中破線)は共通タイミング信号V2Aによって、また第2連動対70を形成するゲート(図中実線)は共通タイミング信号V2Bによって、それぞれクロッキングされている。特に、第1,第2各行内のゲートは、アレイ20を形成している画素のゲートと同じく真正二相アーキテクチャを探っているので、従来と違い一次記憶領域は必要ない。更に、本実施形態では、アレイ20全体が色フィルタアレイでカバーされ、被写体のカラー画像が得られることとなるよう、アレイ20内の各画素10に色フィルタが組み込まれている。また、他の種類の色フィルタアレイを形成してもよいが、ここではベイヤー方式の色フィルタアレイが形成されるようにしている。即ち、

B G b

G r R

という $2 \times 2$ アレイのパターンが繰り返されるよう、ブルーB、グリーン-ブルーG b、グリーン-レッドG r及びレッドRの色フィルタを配してある。これについて示したのは、対応するフィルタ色が同じ画素10間でその信号電荷を結合(即ちビニング)させる動作を説明するためである。こうした例に基づきビニングについて説明する関係上、以下の説明ではレッド、グリーン及びブルーの各色に着目するが、同色同士がビニングされる限り、電気的な接続、使用する色等が違う別の種類の色フィルタアレイを使用する形態でも、本発明を実施することもできる。

【0018】

なお、説明の明瞭化のため、転送用領域30にある第1ロー内ゲートをクロッキングするための共通タイミング信号を第1共通タイミング信号、第2ロー内ゲートのうち第1連動対60をなすゲートをクロッキングするための共通タイミング信号を第2共通タイミン

10

20

30

40

50

グ信号、第2連動対70をなすゲートをクロッキングするための共通タイミング信号を第3共通タイミング信号と称することとする。

#### 【0019】

そして、水平シフトレジスタ80はHCCD（水平CCD）として構成されている。HCCD80は、転送用領域30の第2部分50から信号電荷を受け取れるようその部分50と電気的に接続されており、且つ電荷を双方向にシフトできるよう構成されている。更に、このHCCD80には複数個のラテラルオーバーフロー・チャネル90が接続されており、それらはラテラルオーバーフロードレイン100と結合されている。HCCD80上の電荷のうちその容量を超過した分はそれらのドレイン100へと排出される。なお、ドレン100の構成及び動作については、特許文献3及び4中の詳細な説明を参照されたい。

10

#### 【0020】

図2aに、画素アレイ20及びその上の画像信号を示す。この図では、より好適にご理解頂けるようアレイ20の一部分（4×4サイズ）のみを表し、慣習に倣い画素毎に信号色を付記してある。以下、この部分を例に動作説明を行う。その説明はアレイ20上のどの画素10にも同様に当てはまる。

#### 【0021】

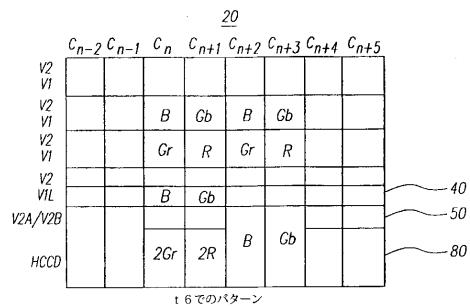

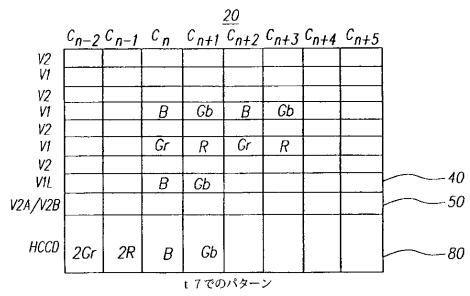

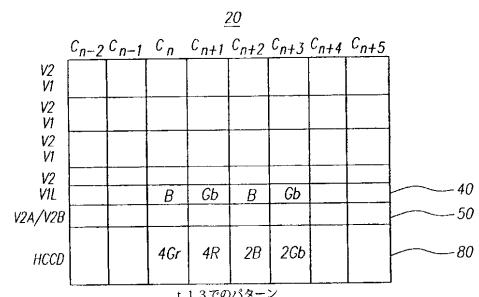

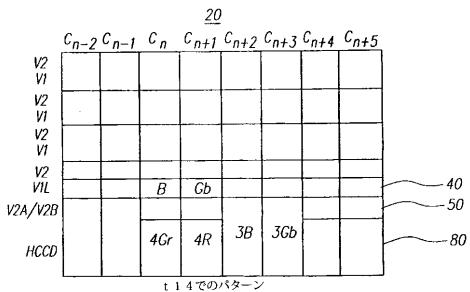

動作時には、この画素アレイ20の状態が、図3に示すタイミング即ち共通タイミング信号に従い図2a～図2rの如く変化していく。具体的には、アレイ20上に捉えた画像（明瞭化のため16画素分のみを示す）のうち（図2a）、最下行画素の信号電荷を転送用領域30内第1部分40に転送する（図2b）。次いで、信号V1Lを低電位にしてその部分40のゲート下にその電荷を保持させる。この部分40のゲートは適正なサイズにしてあるので丸ごと1画素分の電荷を保持することができる。次に、領域30内第2部分50にあるゲートのうち第2連動対70のゲートを制御することで、第1部分40に存する電荷Gr,Rの一部をまず連動対70のゲート下及びHCCD80に転送し、そこから更にHCCD80へと転送する（図2c）。次いで、第1部分40に残っている方の電荷Gr,Rと水平位置が揃うまで、HCCD80上の電荷Gr,RをそのHCCD80上で左シフトさせる（図2d）。次に、第2部分50内ゲートのうち第1連動対60のゲートを制御することで、第1部分40に残っている方の電荷Gr,Rを第1連動対60のゲート下及びHCCD80へと転送し、左シフトで送り込まれている電荷Gr,Rとの結合即ちビニングによって電荷2Gr,2Rに成長させる一方、アレイ20内の各行画素内で、信号V2に係るゲート下にその画素の全電荷を収集させる（図2e）。

20

#### 【0022】

次いで、結合後の電荷2Gr,2Rを全てHCCD80に転送した上で、次の1行分の電荷を画素アレイ20から第1部分40へと転送する（図2f）。次に、第2連動対70のゲートを制御することにより、第1部分40に存する電荷B,Gbの一部を第2部分50内ゲート下及びHCCD80上の対応部分に転送する（図2g）。次いで、転送された電荷B,Gbを全てHCCD80に転送した上で、その電荷B,Gbと第1部分40に残っている同色電荷B,Gbとでその水平位置が揃うよう、HCCD80上の電荷を左シフトさせる（図2h）。次に、第1部分40に存する方の電荷B,Gbを第2部分50内第1連動対60のゲート下及びHCCD80に転送し、それによって既にそこにある電荷B,Gbと結合させる（図2i）。更に、結合後の電荷2B,2Gbを全てHCCD80に転送した上で、次の1行分の電荷をアレイ20から第1部分40へと転送する一方、HCCD80上に存する電荷2Gr,2Rと第1部分40に存する同色電荷Gr,Rとでその水平位置が揃うよう、HCCD80上の電荷を右シフトさせる（図2j）。次いで、第1部分40の電荷Gr,Rを第2部分50内第1連動対60のゲート下及びHCCD80に転送することで、その電荷Gr,Rを既にそこにある電荷2Gr,2Rと結合させて電荷3Gr,3Rに成長させる（図2k）。次に、その電荷3Gr,3Rを全てHCCD80に転送した上で、HCCD80上に存する電荷3Gr,3Rと第1部分40に存する電荷Gr,Rとでその水平位置が揃うよう、HCCD80上にある全ての電荷を右シフトさせる（図2l）。

40

50

## 【0023】

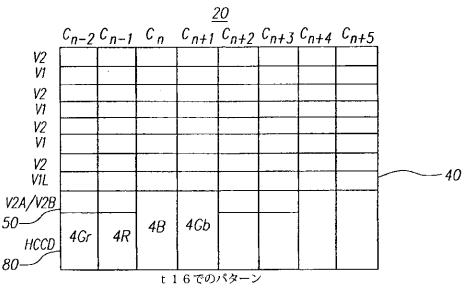

次に、第1部分40に残っている方の電荷G<sub>r</sub>，Rを第2部分50内第2連動対70のゲート下及びHCCD80に転送することによって、そこにある電荷3G<sub>r</sub>，3Rと結合させて電荷4G<sub>r</sub>，4Rに成長させる(図2m)。次いで、その電荷4G<sub>r</sub>，4Rを全てHCCD80に転送した上で、HCCD80上の電荷2B，2Gbと第1部分40にある電荷B，Gbとでその水平位置が揃うようHCCD80上の全ての電荷を左シフトさせる(図2n)。次に、第1部分40にある電荷B，Gbを第2部分50内第2連動対70のゲート下及びHCCD80に転送することによって、その電荷B，Gbをそこにある電荷2B，2Gbと結合させて電荷3B，3Gbに成長させる(図2o)。次いで、第2部分50にある電荷B，Gbを全てHCCD80に転送した上で、第1部分40にある方の電荷B，GbとHCCD80上にある同色電荷3B，3Gbとでその水平位置が揃うようHCCD80上の全ての電荷を左シフトさせる(図2p)。次に、第1部分40にある方の電荷B，Gbを第2部分50内第1連動対60のゲート下及びHCCD80に転送することによって、電荷4B，4Gbに成長させる(図2q)。そして、第2部分50にある電荷を全てHCCD80に転送した上で、HCCD80上の電荷を、本件技術分野で周知の処理に供するためHCCD80外にシフト出力する(図2r)。

10

## 【0024】

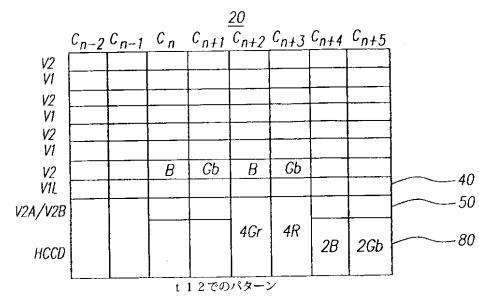

図3に、本センサ5におけるオンチップ画素ピニング動作のタイミングを示す。この図には、画素アレイ20用の信号V1及びV2、転送用領域30用の信号V1L、V2A及びV2B、並びにHCCD80用の信号Hc1ksが示されている。また、この図では、HCCD80の各相動作が、タイミング信号Hc1ksの概略パターンによって示されている。即ち、図中の表記L2はアレイ20に対し2列分だけHCCD80上の信号電荷を左シフトさせることを、R2は同じく右シフトさせることを、それぞれ表している。

20

## 【0025】

なお、ここまで画素ピニングを例にして本発明を説明したが、このイメージセンサ5でフル解像度の画像を得るには、信号V1Lと信号V1、信号V2A及びV2Bと信号V2を、それぞれ同じ電気信号にすればよい。図4aに、そうしたフル解像度読出の際の動作タイミングを示す。また、図4bに、上述した真正二相クロッキング動作における本センサ5内の電荷転送動作を示す。フル解像度読出時に画素アレイ20及び転送用領域30で実行される電荷転送動作もこれと同様の動作になる。

30

## 【符号の説明】

## 【0026】

5 イメージセンサ、10 画素、20 画素アレイ、30 転送用領域、40 転送用領域第1部分、50 転送用領域第2部分、60 第2部分内第1連動ゲート対、70 第2部分内第2連動ゲート対、80 水平シフトレジスタ又は水平電荷結合素子(HCCD)、90 ラテラルオーバフローチャネル、100 ラテラルオーバードレイン。

【図1】

FIG. 1

【図2 a】

|           |      | $C_{n-2}$ | $C_{n-1}$ | $C_n$     | $C_{n+1}$ | $C_{n+2}$ | $C_{n+3}$ | $C_{n+4}$ | $C_{n+5}$ |

|-----------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| $V2$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  | <i>Gr</i> | <i>R</i>  |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  | <i>Gr</i> | <i>R</i>  |           |           |

| $V2A/V2B$ |      |           |           |           |           |           |           |           |           |

| $HCCD$    |      |           |           |           |           |           |           |           |           |

$t = 0$  でのパターン

【図2 b】

|           |      | $C_{n-2}$ | $C_{n-1}$ | $C_n$     | $C_{n+1}$ | $C_{n+2}$ | $C_{n+3}$ | $C_{n+4}$ | $C_{n+5}$ |

|-----------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| $V2$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  | <i>Cr</i> | <i>R</i>  |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  | <i>Gr</i> | <i>R</i>  |           |           |

| $V2A/V2B$ |      |           |           |           |           |           |           |           |           |

| $HCCD$    |      |           |           |           |           |           |           |           |           |

$t = 1$  でのパターン

【図2 c】

|           |      | $C_{n-2}$ | $C_{n-1}$ | $C_n$     | $C_{n+1}$ | $C_{n+2}$ | $C_{n+3}$ | $C_{n+4}$ | $C_{n+5}$ |

|-----------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| $V2$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  | <i>Gr</i> | <i>R</i>  |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  |           |           |           |           |

| $V2A/V2B$ |      |           |           |           |           |           |           |           |           |

| $HCCD$    |      |           |           |           |           |           |           |           |           |

$t = 2$  でのパターン

【図2 e】

|           |      | $C_{n-2}$ | $C_{n-1}$ | $C_n$     | $C_{n+1}$ | $C_{n+2}$ | $C_{n+3}$ | $C_{n+4}$ | $C_{n+5}$ |

|-----------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| $V2$      |      |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  | <i>Gr</i> | <i>R</i>  |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  |           |           |           |           |

| $V2A/V2B$ |      |           |           |           |           |           |           |           |           |

| $HCCD$    |      |           |           |           |           |           |           |           |           |

$t = 4$  でのパターン

【図2 d】

|           |      | $C_{n-2}$ | $C_{n-1}$ | $C_n$     | $C_{n+1}$ | $C_{n+2}$ | $C_{n+3}$ | $C_{n+4}$ | $C_{n+5}$ |

|-----------|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| $V2$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  | <i>Gr</i> | <i>R</i>  |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>  | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |           |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i> | <i>R</i>  |           |           |           |           |

| $V2A/V2B$ |      |           |           |           |           |           |           |           |           |

| $HCCD$    |      |           |           | <i>Gr</i> | <i>R</i>  |           |           |           |           |

$t = 3$  でのパターン

【図2 f】

|           |      | $C_{n-2}$ | $C_{n-1}$ | $C_n$      | $C_{n+1}$ | $C_{n+2}$ | $C_{n+3}$ | $C_{n+4}$ | $C_{n+5}$ |

|-----------|------|-----------|-----------|------------|-----------|-----------|-----------|-----------|-----------|

| $V2$      |      |           |           |            |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>   | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |            |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i>  | <i>R</i>  | <i>Gr</i> | <i>R</i>  |           |           |

| $V2$      | $V1$ |           |           |            |           |           |           |           |           |

| $V1$      |      |           |           | <i>B</i>   | <i>Gb</i> | <i>B</i>  | <i>Gb</i> |           |           |

| $V2$      | $V1$ |           |           |            |           |           |           |           |           |

| $V1$      |      |           |           | <i>Gr</i>  | <i>R</i>  |           |           |           |           |

| $V2A/V2B$ |      |           |           |            |           |           |           |           |           |

| $HCCD$    |      |           |           | <i>2Gr</i> | <i>2R</i> |           |           |           |           |

$t = 5$  でのパターン

【図2g】

【図2h】

【図2i】

【図2j】

【図2k】

【図2l】

【図2m】

【図2n】

【図2o】

【図2q】

【図2p】

【図2r】

【図3】

【図4a】

【図4b】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2008/002237

A. CLASSIFICATION OF SUBJECT MATTER

INV. H04N5/335 H04N9/04 H04N3/15

ADD. H01L27/146 H01L27/148

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01L H04N

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                    | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2004/150733 A1 (NAGAYOSHI RYOICHI [JP])<br>ET AL) 5 August 2004 (2004-08-05)<br>abstract; figures 1-13,22,23,26,29-57<br>page 1, paragraph 6<br>page 3, paragraph 67<br>page 6, paragraph 91<br>page 7, paragraph 102 - page 8, paragraph 118<br>page 9, paragraph 123<br>page 10, paragraph 138 - page 11,<br>paragraph 146<br>page 12, paragraph 164 - page 13,<br>paragraph 175 | 1,3-5                 |

| Y         | US 2006/125943 A1 (PARKS CHRISTOPHER [US])<br>15 June 2006 (2006-06-15)<br>abstract<br>page 5, paragraph 71                                                                                                                                                                                                                                                                           | 2                     |

| Y         | -----                                                                                                                                                                                                                                                                                                                                                                                 | 2                     |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the International filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the International filing date but later than the priority date claimed

\*T\* later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

\*&\* document member of the same patent family

Date of the actual completion of the International search

21 May 2008

Date of mailing of the International search report

29/05/2008

## Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL-2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

## Authorized officer

Dolezel, Tomás

**INTERNATIONAL SEARCH REPORT**International application No

PCT/US2008/002237**C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                      | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 2005/280726 A1 (PARKS CHRISTOPHER [US]<br>ET AL) 22 December 2005 (2005-12-22)<br>the whole document | 1-5                   |

Form PCT/ISA/210 (continuation of second sheet) (April 2005)

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

|                              |

|------------------------------|

| International application No |

| PCT/US2008/002237            |

| Patent document cited in search report | Publication date | Patent family member(s)                                               | Publication date                                     |

|----------------------------------------|------------------|-----------------------------------------------------------------------|------------------------------------------------------|

| US 2004150733                          | A1 05-08-2004    | EP 1562370 A1<br>WO 2004045205 A1<br>JP 3848650 B2<br>JP 2004180284 A | 10-08-2005<br>27-05-2004<br>22-11-2006<br>24-06-2004 |

| US 2006125943                          | A1 15-06-2006    | NONE                                                                  |                                                      |

| US 2005280726                          | A1 22-12-2005    | EP 1766966 A1<br>JP 2008503936 T<br>WO 2006009721 A1                  | 28-03-2007<br>07-02-2008<br>26-01-2006               |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MT,NL,NO,PL,PT,RO,SE,SI,SK,T

R),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,

BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,D0,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,K

G,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT

,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(72)発明者 マッカートン ジヨン ピー

アメリカ合衆国 ニューヨーク ペンフィールド ティンバーリン ドライブ 138

F ターム(参考) 4M118 BA10 BA12 CA08 DB06 FA06 FA14 FA38 GC07 GC14

5C024 AX01 CX41 CY47 EX52 GY01 GY04 GZ12 GZ26 JX36