(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5636319号

(P5636319)

(45) 発行日 平成26年12月3日(2014.12.3)

(24) 登録日 平成26年10月24日(2014.10.24)

(51) Int.Cl.

F 1

|      |       |           |      |       |

|------|-------|-----------|------|-------|

| GO2B | 6/42  | (2006.01) | GO2B | 6/42  |

| GO2B | 6/13  | (2006.01) | GO2B | 6/12  |

| HO1S | 5/022 | (2006.01) | HO1S | 5/022 |

| GO2F | 1/377 | (2006.01) | GO2F | 1/377 |

M

請求項の数 5 (全 16 頁)

(21) 出願番号

特願2011-60916 (P2011-60916)

(22) 出願日

平成23年3月18日(2011.3.18)

(65) 公開番号

特開2012-198295 (P2012-198295A)

(43) 公開日

平成24年10月18日(2012.10.18)

審査請求日

平成25年12月26日(2013.12.26)

(73) 特許権者 000001960

シチズンホールディングス株式会社

東京都西東京市田無町六丁目1番12号

(74) 代理人 100099759

弁理士 青木 篤

(74) 代理人 100092624

弁理士 鶴田 準一

(74) 代理人 100114018

弁理士 南山 知広

(74) 代理人 100165191

弁理士 河合 章

(74) 代理人 100151459

弁理士 中村 健一

最終頁に続く

(54) 【発明の名称】光モジュールの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に接合された第1光学素子及び第2光学素子を含む光モジュールの製造方法において、

前記基板上に金属から構成される接合用バンプを形成する工程と、

前記第1光学素子を前記基板に接合させる工程と、

前記接合用バンプを介して前記基板上に前記第2光学素子を接合させる工程と、を有し、

前記第2光学素子を接合させる工程では、

前記第1光学素子から前記第2光学素子を介して出射された光を検出する光検出器を利用して、前記第2光学素子に印加する荷重を増加させながら、前記第1光学素子と前記第2光学素子とが最も効率良く光結合する位置を検出し、

前記最も効率良く光結合する荷重より大きな荷重を前記第2光学素子に印加し、荷重を解放した後に最も効率良く光結合する最終荷重を予め求め、

前記最終荷重を前記第2光学素子に印加する、

ことを特徴とする光モジュールの製造方法。

## 【請求項 2】

前記第2光学素子は、前記接合用バンプを介して表面活性化結合で前記基板上に接合される、請求項1に記載の光モジュールの製造方法。

## 【請求項 3】

10

20

前記第2光学素子は、接着材で前記基板上に接合される、請求項1又は2に記載の光モジュールの製造方法。

【請求項4】

前記接合用バンプは、複数の突起を含む、請求項1～3の何れか一項に記載の光モジュールの製造方法。

【請求項5】

前記接合用バンプは、A uから構成される、請求項1～4の何れか一項に記載の光モジュールの製造方法。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、光モジュールの製造方法に関し、特に接合用バンプを利用して接合された複数の光学素子を含む光モジュールの製造方法に関する。

【背景技術】

【0002】

半導体レーザ素子を実装後、接合用バンプによってフォトダイオードを銅ヒートシンクに接合して、半導体レーザ素子とフォトダイオードとの光学的位置合わせを高精度に行う方法が知られている（例えば、特許文献1参照）。

【0003】

上記の方法において、接合用バンプによってフォトダイオードを接合する場合には、接合用バンプに印加される加圧力と、加圧力に応じて変形する接合用バンプの高さとの関係を調べておき、前記関係に応じて適正な加圧力を選択している。

20

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平10-208269号公報（図1）

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、接合用バンプを潰すことによって光学素子の高さ方向の位置決めをサブミクロンオーダで行うものは存在しなかった。

30

【0006】

さらに、接合用バンプに荷重を与えて変形させた後に荷重を開放すると、変形された接合用バンプには、接合用バンプの弾性によって変形された位置から元の位置に戻ろうとする力が働く。したがって、接合用バンプに荷重を与えた状態で、光学素子間の位置合わせを行っても、その後荷重を開放すると（印加されていた荷重を取り除くと）、接合用バンプが変形前の状態に戻ろうと再度変形するので、光学素子間の相対位置が変化してしまうという不具合があった。

【0007】

なお、荷重を開放した後に接合用バンプが変形前の状態に戻ろうと再度変形することを「接合用バンプの弾性戻り」と言い、その変形量を「弾性戻り量」と言う。なお、「弾性戻り量」は、印加される荷重量、接合用バンプの材質、接合用バンプの形状等に対応して変化する。

40

【0008】

そこで、本発明は、上記の課題を解決するための光モジュールの製造方法を提供することを目的とする。

また、本発明は、接合用バンプの弾性戻りに拘わらず、光学素子間の光学的位置合わせを高精度に行うことと可能とする光モジュールの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

50

本発明に係る光モジュールの製造方法では、基板上に金属から構成される接合用バンプを形成し、第1光学素子と第2光学素子とが最も効率良く光結合する位置よりも所定量だけ接合用バンプがより変形するような荷重を印加後、荷重を開放することによって、接合用バンプ上に第2光学素子を接合する工程を有することを特徴とする。

【発明の効果】

【0010】

本発明によれば、接合用バンプの弾性戻り量を考慮して、接合用バンプに第2光学素子を接合するため、荷重を開放した状態においても、第1光学素子と第2光学素子の光学的位置合わせを高精度に行うことが可能となった。

【図面の簡単な説明】

10

【0011】

【図1】半導体レーザモジュール1を示す図である。

【図2】半導体レーザモジュール1の製造過程を説明するためのフロー図である。

【図3】半導体レーザモジュール1の製造過程示す図(1)である。

【図4】半導体レーザモジュール1の製造過程示す図(2)である。

【図5】半導体レーザモジュール1の製造過程示す図(3)である。

【図6】LD素子20とPPLN素子30との位置関係を示す図である。

【図7】検出器102の出力電圧と調芯実装器103によって印加される荷重との関係を示したグラフである。

【図8】半導体レーザモジュール1の製造過程の他の例を示す図である。

20

【図9】他のマイクロバンプを説明するための図である。

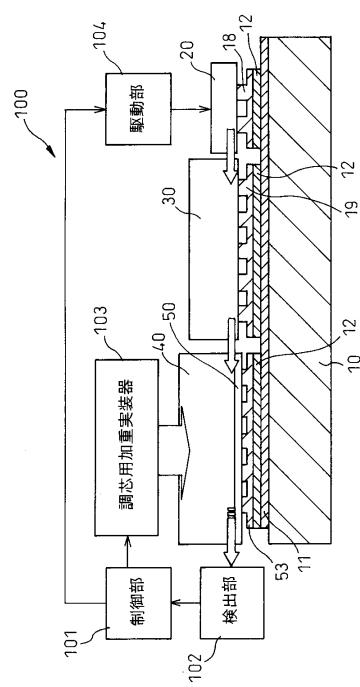

【図10】他の半導体レーザモジュール2の製造過程を説明するためのフロー図である。

【図11】他の半導体レーザモジュール2の製造過程示す図である。

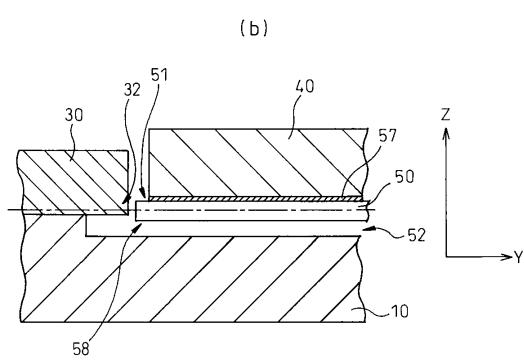

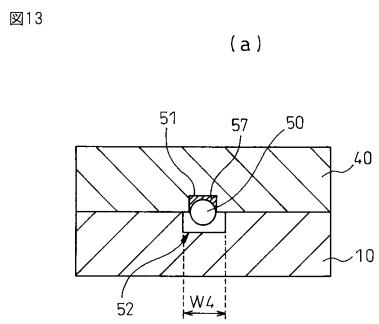

【図12】基板10とサブ基板40との接合を説明するための図である。

【図13】PPLN素子30とファイバ50との位置関係を示す図である。

【図14】半導体レーザモジュール1の製造過程を示す図(4)である。

【発明を実施するための形態】

【0012】

以下図面を参照して、本発明に係る光モジュールの製造方法について説明する。但し、本発明の技術的範囲はそれらの実施の形態に限定されず、特許請求の範囲に記載された発明とその均等物に及ぶ点に留意されたい。

30

【0013】

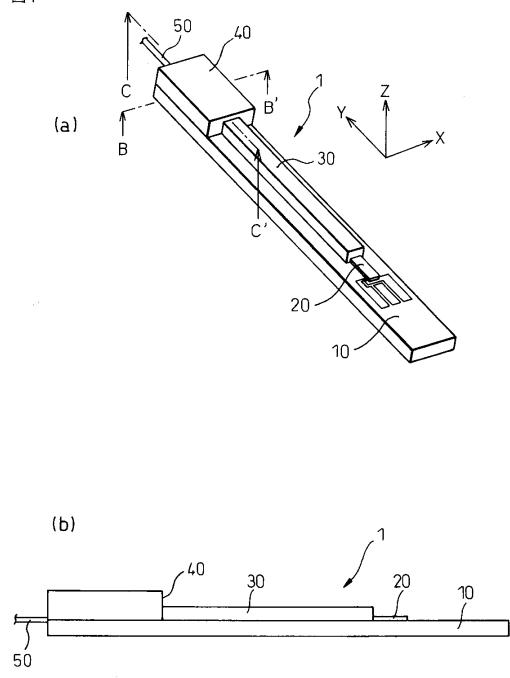

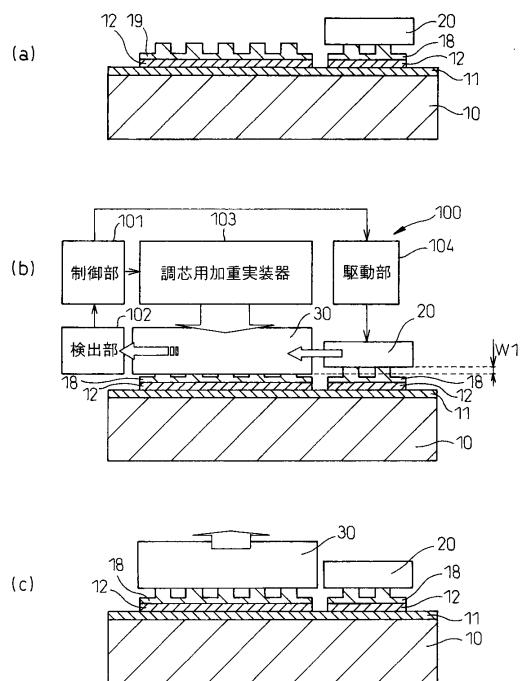

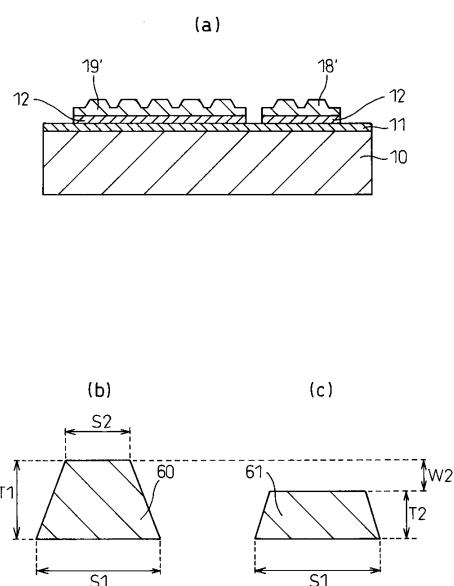

図1(a)は光モジュールの一例として示す半導体レーザモジュール1の斜視図であり、図1(b)は半導体レーザモジュール1のY軸方向の側面図である。

【0014】

半導体レーザモジュール1は、シリコン基板10、LD(レーザ・ダイオード)素子20、LD素子20から出射された光の波長変換を行うためのPPLN(Periodically Poled Lithium Niobate)素子30、シリコン又はガラスから構成されるサブ基板40及び光ファイバ50を含んで構成されている。例えば、半導体レーザモジュール1は、LD素子20から出射される波長1064nmのシングルモードレーザ近赤外光を、PPLN素子30において532nmの緑色レーザに波長変換して、出射するように機能する。なお、PPLN素子30から出射された光はサブ基板40を介してシリコン基板10に接合されたシングルモード(SMF)光ファイバ50で伝播されるように構成される。

40

【0015】

半導体レーザモジュール1では、LD素子20から出射された光を効率良くPPLN素子に入射できるように光結合されているが、光結合効率を高めるためには、両素子間に非常に高精度位置合わせが求められる。図1(a)におけるシリコン基板10上の平面方向(XY平面)の位置精度はアライメントマーク等の基準マークをシリコン基板10上に設けることによって実装する際に、実装装置によって調整を行っている。

【0016】

50

しかしながら、通常では、図1(a)における高さ方向(Z方向)の精度は、そのままでは、シリコン基板10とLD素子20及びPPLN素子30との間の接触ポイントで実装高さが決まってしまう。そこで、シリコン基板10上に後述する接合用バンプとしてのマイクロバンプを形成し、マイクロバンプ上にPPLN素子30を実装する際に所定の荷重を加えて、マイクロバンプを変形させることによって、高さ方向(Z方向)の精度を保てるような処理を実施している。

【0017】

なお、シリコン基板10に対してLD素子20及びPPLN素子30を実装する場合には、樹脂、AuSn又は半田といった接合材料を用いることも可能である。しかしながら、そのような接合材料が液状化している最中には、素子を上下に移動して位置の調整を行うことも可能であるが、冷却して固化すると、接合材料が予測不能に縮小・変形してしまうため、高精度な高さ方向(Z方向)の位置調整を行うことは難しい。

10

【0018】

半導体レーザモジュール1は、本発明に係る光モジュールの一例を示すものであって、光モジュールは半導体レーザモジュール1に限定して解釈されるものではない。本発明に係る光モジュールは、光結合する2つ以上の光学素子を有する他のモジュールにも好適に適用することが可能である。例えば、後述するように、LD素子20とPPLN素子30との間の光結合、又はPPLN素子30とサブ基板40に固定された光ファイバ50との間の光結合にも利用することができる。なお、光結合とは、一方の光学素子から出力された光を直接他方の光学素子に入射できるように、相互に位置関係が定められているという意味である。

20

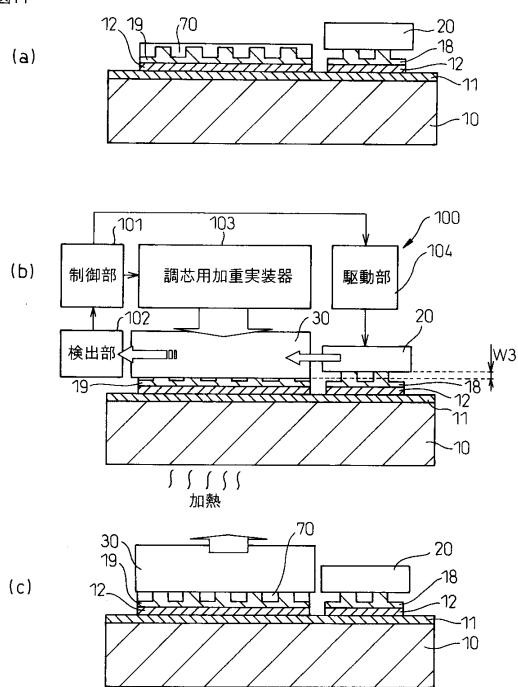

【0019】

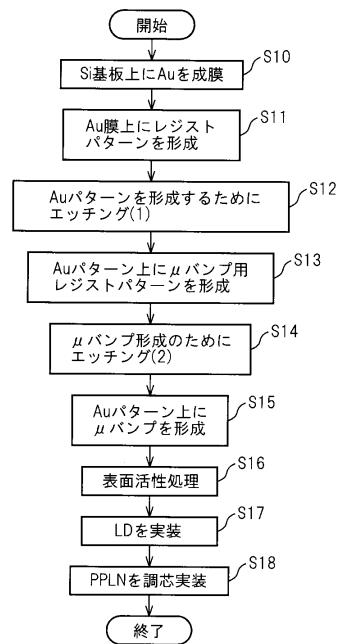

図2～図5を用いて、光モジュールの一例である半導体レーザモジュール1の製造過程の内、LD素子20及びPPLN素子30の接合に係る部分について説明する。図2は、半導体レーザモジュール1の製造過程を説明するためのフロー図であり、図3～図5は、図2に示す半導体レーザモジュール1の製造過程をより詳しく説明するための図である。

【0020】

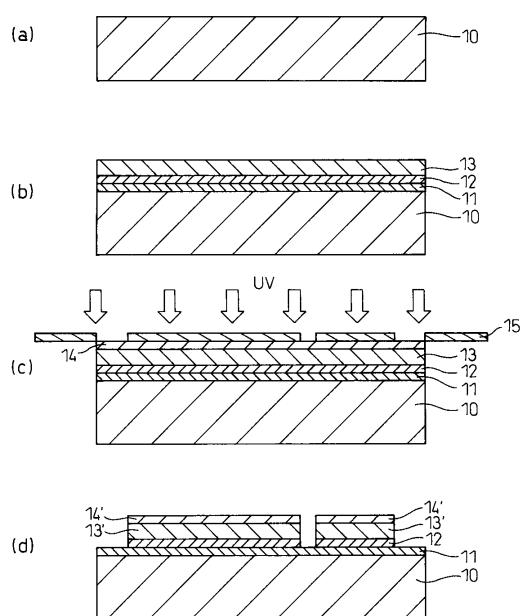

最初に、シリコン基板10を用意する。図3(a)は、シリコン基板10の断面図である。

【0021】

30

次に、シリコン基板10全体を酸化性雰囲気中で加熱して、シリコン基板10上にSiO<sub>2</sub>(二酸化ケイ素)薄膜11を形成する。また、SiO<sub>2</sub>薄膜11上に蒸着によってTi(チタン)薄膜12を形成する。さらに、Ti薄膜12上に蒸着によって厚さ3μmのAu層13を成膜する(S10)(図3(b)参照)。Au層13は、蒸着の他に、スパッタリング又は電気メッキ法等によって形成しても良い。なお、SiO<sub>2</sub>薄膜11は、シリコン基板10と後述するマイクロバンプ18との間を絶縁する絶縁層として機能する。また、Ti薄膜12は、SiO<sub>2</sub>薄膜11とAu層13との密着性を高めるために形成されている。

【0022】

次に、Au層13上に、フォトレジスト層14を形成し、マスク層15を配置して、マスク層15に対応したフォトレジスト14'が形成されるように紫外線の照射を行う(S11)(図3(c)参照)。

40

【0023】

次に、ドライエッチングによりフォトレジスト14'が形成された部分以外のAu層13及びTi薄膜12をエッチングして、Au層パターン13'を形成する(S12)(図3(d)参照)。なお、ドライエッチングの代わりに、ウェットエッチングによりAu層パターン13'を形成しても良い。

【0024】

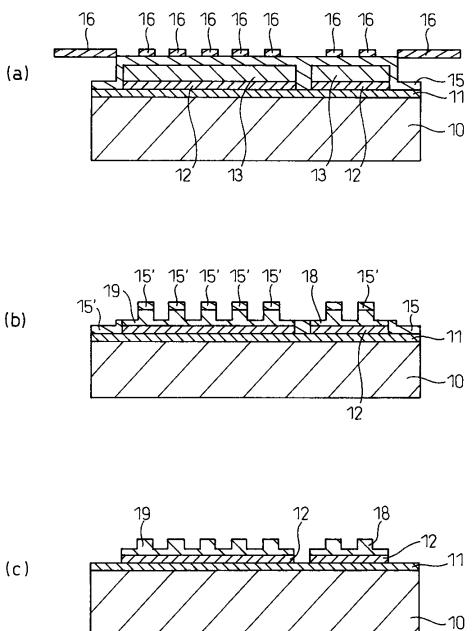

次に、フォトレジスト14'を除去したのち、再度フォトレジスト層15を形成し、マスク層16を配置して、マスク層16に対応したフォトレジスト15'が形成されるよう

50

に紫外線の照射を行う (S 1 3) (図 4 (a) 参照)。

【0025】

次に、ドライエッチングによりフォトレジスト 15' が形成された部分以外の Au 層パターン 13' をハーフエッチングして、マイクロバンプ 18 及び 19 を形成する (S 1 4) (図 4 (b) 参照)。なお、ドライエッチングの代わりに、ウエットエッチングによりマイクロバンプ 18 及び 19 を形成しても良い。なお、ハーフエッチングとは、フォトレジスト 15' が形成された部分以外を全て除去するのではなく、一部が残るようにエッチングを行うことを言う。本例では、フォトレジスト 15' が形成された部分以外では、Au 層パターン 13' の厚さが 1 μm になるまでエッチングを行っている。

【0026】

次に、フォトレジスト 15' を除去して、シリコン基板上にマイクロバンプ 18 及び 19 の形成を完了する (S 1 5) (図 4 (c) 参照)。マイクロバンプ 18 及び 19 は、複数の高さ 2 μm で直径 5 μm の円柱状の突起が 10 ~ 25 μm ピッチで左右均等に配置されたものである。なお、突起の形状、高さ、幅、ピッチ等は一例であって、上記に限定されるものではない。マイクロバンプ 18 及び 19 は、スパッタリングによって形成された Au 層 13 に基づいており (S 1 0)、且つハーフエッチングによって成形されているため (S 1 4)、マイクロバンプ 18 及び 19 に含まれる全ての突起の高さは高精度に均一化されている。

【0027】

次に、マイクロバンプ 18 及び 19 の表面を覆っている酸化膜又はコンタミ等の不活性層を、プラズマ洗浄処理することによって表面活性化を行う (S 1 6)。表面活性化によって、表面エネルギーの高い原子同士を接触させることができるので、原子間の凝着力を利用して常温で強固に接合することができる。本接合方法は、特別な加熱を要しないことから、熱膨張係数差の残留応力による各部品の位置ずれが発生しにくいことから、高精度の位置決め実装をすることができる。また、熱膨張係数差の残留応力による部品破壊が発生しにくい、部品に対するストレスがなく機能劣化が少ない、等の利点も備えている。

【0028】

次に、LD 素子 20 を表面活性化されたマイクロバンプ 18 上に実装する (S 1 7) (図 5 (a) 参照)。LD 素子 20 の接合面にも、Au 層が形成され、その表面は活性化処理が施されている。したがって、マイクロバンプ 18 の上部に所定の荷重を加えて LD 素子 20 を実装するだけで、LD 素子 20 はマイクロバンプ 18 上に表面活性化結合して固定される。また、LD 素子 20 は、マイクロバンプ 18 を介して駆動電流の供給を受けるように構成することができる。その際には、マイクロバンプ 18 を形成するための Au 層パターン 13' に駆動電流を供給用の所定のパターンニングが施されるようにすれば良い。

【0029】

LD 素子 20 の実装は、不図示の電子部品を回路基板上に装着する実装器により行う。なお、LD 素子 20 の実装を、後述する S 1 8 で利用する調芯実装器 103 を利用して行っても良い。

【0030】

次に、PPLN 素子 30 を表面活性化されたマイクロバンプ 19 上に調芯実装して (S 1 8) (図 5 (b) 参照)、一連の処理を終了する。PPLN 素子 30 の接合面にも、Au 層が形成され、その表面は活性化処理が施されている。したがって、マイクロバンプ 19 の上部に所定の荷重を加えて PPLN 素子 30 を実装するだけで、PPLN 素子 30 はマイクロバンプ 19 上に表面活性化結合して固定される。

【0031】

S 1 8 における調芯実装は、調芯実装装置 100 を用いて行う。調芯実装装置 100 は、CPU 及び所定のメモリ等を含む PC 等から構成される制御部 101、PPLN 素子 30 から出力される波長変換されたレーザ光の強度を検出し、強度に応じた検出出力電圧 V

10

20

30

40

50

(mV)を出力する検出部102、電子部品をシリコン基板20上の所定の位置に実装し且つ実装時に制御量に応じた荷重(N)を加えることが可能な調芯実装器103、及びLD素子20を駆動させてレーザ光を出射させるための駆動部104等を含んで構成されている。

【0032】

制御部101は、駆動部104を制御してLD素子20を駆動させてレーザ光をPPLN素子30に入射させ、PPLN素子30から出射される波長変換されたレーザ光の強度を検出部102で検出する。さらに、制御部101は、検出部102で検出された検出出力電圧Vをモニタしながら、調芯実装器103を制御してPPLN素子30に印加する荷重を制御する。

10

【0033】

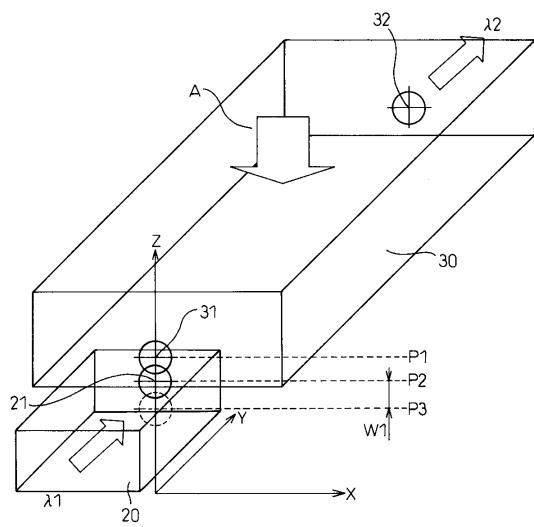

図6は、LD素子20とPPLN素子30との位置関係を示す図である。

【0034】

LD素子20の発光中心21から出射された波長1のレーザ光が、PPLN素子30の入射位置31から入射され、PPLN素子30の出射中心32から波長2のレーザ光となって出射する。図6に示す様に、LD素子20及びPPLN素子30は、調芯実装器103によってシリコン基板10上に実装されるので、LD素子20の発光中心21とPPLN素子30の入射位置31との平面上の位置関係(X-Y軸方向の位置関係)は精度良く位置決めされている。しかしながら、シリコン基板10の高さ方向(Z軸方向)の位置関係を精度良く定める必要がある。なお、図6において、矢印Aは、調芯実装器103によってPPLN素子30に荷重が印加される方向を示している。

20

【0035】

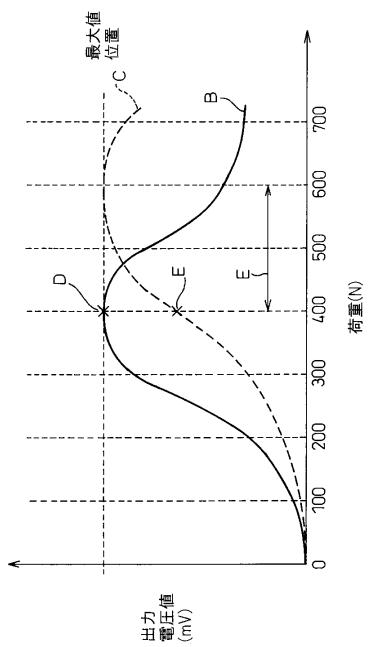

図7は、検出器102の出力電圧と調芯実装器103によって印加される荷重との関係を示したグラフである。

【0036】

図7において、曲線Bは、荷重を印加している状態における、検出器102の出力電圧(mV)と調芯実装器103によって印加される荷重(N)との関係を示している。また、曲線Cは、荷重を開放した後における、検出器102の出力電圧(mV)と調芯実装器103による最終荷重(N)との関係を示している。図7の例では、荷重を印加している状態では、荷重が400(N)の場合に、検出器102の出力電圧(mV)が最大値となる(点D参照)。しかしながら、荷重を開放した後では、最終荷重が400(N)の場合には、検出器102の出力電圧(mV)が最大値とはならない(点E参照)。

30

【0037】

点Dは、例えば、PPLN素子30に荷重を印加することによって、マイクロバンプ19を変形させ、PPLN素子30の入射位置31を、LD素子20の発光中心21と最も効率良く光結合するような位置(図6の位置P2参照)とした状態で、荷重を開放した場合に対応する。マイクロバンプ19は、荷重がかかると変形して(潰れて)縮むが、弾性反発によって、荷重が開放されると、元の状態の戻ろうとする力が働き、弾性戻り量分だけ戻るという特性を有している。即ち、点Eは、点Dの状態において荷重を開放すると、弾性戻りによって、PPLN素子30の入射位置31が、他の位置(例えば、図6の位置P1参照)に移動してしまった場合に対応する。

40

【0038】

荷重を開放した状態(実際に半導体レーザモジュール1が利用される状態)において、PPLN素子30の入射位置31を、LD素子20の発光中心21と最も効率良く光結合する位置(図6のP2参照)とする必要がある。そこで、S18の調芯実装において、制御部101は、PPLN素子30をマイクロバンプ19の所定位置に配置した後に、印加する過重を増加させながら、検出部102からの出力電圧Vが最大値となった後、マイクロバンプ19を更に変形させるように所定の荷重量を印加してから、荷重を開放するように調芯実装器103を制御している。

【0039】

50

即ち、制御部 101 は、検出部 102 からの出力電圧  $V$  が最大値となった後（点 D 参照）、更に所定の荷重量（ $F : 200$ （N））を更に印加し、その後荷重を開放している。PPLN 素子 30 の入射位置 31 が、LD 素子 20 の発光中心 21 よりも、図 6 に示す距離  $W$  1 分だけ、更に深く押し込まれた位置（図 6 の位置 P3 参照）となるように、所定の荷重  $F$  を更に印加している。その後、荷重が開放されることによって、PPLN 素子 30 の入射位置 31 が、LD 素子 20 の発光中心 21 と最も効率良く光結合する位置（図 6 の P2 参照）に弾性戻りによって戻る（図 5（c）参照）。

#### 【0040】

上述した所定の荷重量（ $F : 200$ （N））は、調芯実装器 103、荷重を印加する PPLN 素子 30 の形状、マイクロバンプ 19 の材質及び形状等によって異なるので、図 7 に示す曲線 B 及び C を求める実験を行うことによって、算出することが可能である。また、S18 の調芯実装においては、制御部 101 が、検出部 102 からの出力電圧  $V$  が最大値となった後に、所定の荷重を印加するように調芯実装器 103 を制御した。しかしながら、ユーザが、検出部 102 からの出力電圧  $V$  をモニタで観測しながら、調芯実装器 103 の制御を行うようにしても良い。

#### 【0041】

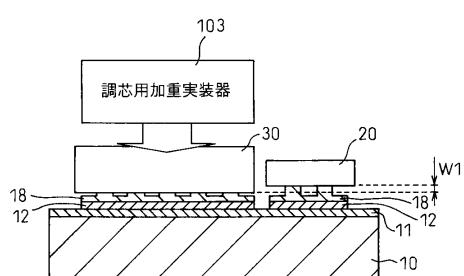

図 8 は、半導体レーザモジュール 1 の製造過程の他の例を示す図である。

#### 【0042】

図 8 を用いて、他の PPLN 素子 30 の芯調実装について説明する。図 5（b）（図 2 の S18）の例では、制御部 101 が、検出部 102 からの出力電圧  $V$  が最大値となった後に、所定の荷重を印加するように調芯実装器 103 を制御した。しかしながら、一定の基準で製造されたマイクロバンプ 18 及び 19、LD 素子 20、及び PPLN 素子 30 であれば、個別に LD 素子 20 を発光させて検出部 102 からの出力電圧  $V$  に応じた調芯実装を行う必要は必ずしもない。

#### 【0043】

そこで、図 8 の例では、検出部 102 からの出力電圧  $V$  が最大値となる荷重（図 7 の点 D 参照）を予め予想して、その荷重（例えば、400（N））に更に上述した所定の荷重量（ $F : 200$ （N））を印加する（全体で、例えば、600（N））。それによって、PPLN 素子 30 の入射位置 31 が、LD 素子 20 の発光中心 21 よりも、図 6 に示す距離  $W$  1 分だけ、更に深く押し込まれた位置（図 6 の位置 P3 参照）となった後に、荷重が開放する。すると、PPLN 素子 30 の入射位置 31 が、LD 素子 20 の発光中心 21 と最も効率良く光結合する位置（図 6 の P2 参照）に弾性戻りによって戻る。即ち、図 8 の例では、図 5（b）に示した、制御部 101、検出部 102、駆動部 104 を用いずに、調芯実装器 103 のみを用いて、PPLN 素子 30 と LD 素子 20 との間の高さ方向（Z 軸方向）位置関係を設定している。

#### 【0044】

図 8 に示す方法において、芯調実装工程（図 2 の S18）で制御部 101、検出部 102、駆動部 104 を用いずに、調芯実装器 103 のみを用いて行う点のみが、図 2 に示した半導体レーザモジュール 1 の製造過程と異なる。他の点、特に、マイクロバンプ 18 及び 19 の製造過程、LD 素子 20 及び PPLN 素子 30 とマイクロバンプ 18 及び 19 との接合方法については全く同じであるので、その説明を省略する。

#### 【0045】

図 9 は、他のマイクロバンプを説明するための図である。

#### 【0046】

図 4 及び 5 に示したマイクロバンプ 18 及び 19 は、高さ  $2 \mu m$  且つ直径  $5 \mu m$  の円柱状で  $10 \sim 25 \mu m$  ピッチで左右均等に配置された突起を複数含むものである。しかしながら、図 9 に示す他のマイクロバンプ 18' 及び 19' は、切頭円錐型の突起を複数含んでいる。図 9（a）は図 4（c）に対応するマイクロバンプ 18' 及び 19' を含んだ断面図であり、図 9（b）はマイクロバンプ 18' 及び 19' に含まれる突起部分 60 の断面図であり、図 9（c）はマイクロバンプ 18' 及び 19' に含まれる潰された突起部分

10

20

30

40

50

6 1 の一例を示す図である。

【 0 0 4 7 】

図 9 ( b ) に示すように、切頭円錐型の突起部分 6 0 は、底面が直径 S 1 ( 例えは、 2  $\mu\text{m}$  ) の円形、上面が直径 S 2 ( 例えは、 1  $\mu\text{m}$  ) の円形、高さ T 1 ( 例えは、 2  $\mu\text{m}$  ) である。また、マイクロバンプ 1 8 ' 及び 1 9 ' は、 2  $\mu\text{m}$  ピッチで左右均等に配置された突起部分 6 0 を含むものとする。

【 0 0 4 8 】

図 9 ( c ) は、 P P L N 素子 3 0 を調芯実装した場合に潰れた突起部分 6 1 の一例を示している。切頭円錐型の突起部分 6 1 は、底面が直径 S 1 ( 例えは、 2  $\mu\text{m}$  ) の円形、高さ T 2 ( 例えは、 1  $\mu\text{m}$  ) である。したがって、この場合、調芯実装によって距離 W 2 ( 例えは、 1  $\mu\text{m}$  ) 分だけ、切頭円錐型の突起部分が潰されたこととなる。

10

【 0 0 4 9 】

図 4 及び 5 に示す、円柱状の突起を有するマイクロバンプ 1 8 及び 1 9 より、上面が少し小さい切頭円錐型の突起を有するマイクロバンプ 1 8 ' 及び 1 9 ' の方が、同じ荷重を印加した場合に、容易に潰れ易く、したがって、調芯のための制御がし易い ( 調芯実装器 1 0 3 が高い荷重を印加しなくとも良いので ) という効果を有する。

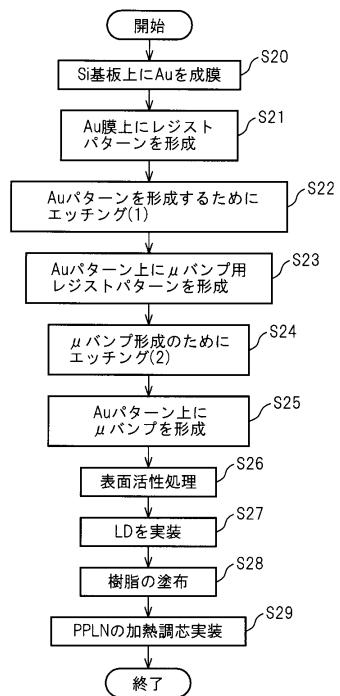

【 0 0 5 0 】

図 1 0 及び図 1 1 を用いて、光モジュールの一例である半導体レーザモジュール 1 の製造過程の内、 L D 素子 2 0 及び P L L N 素子 3 0 の接合に係る部分の他の方法について説明する。図 1 0 は、半導体レーザモジュール 2 の製造過程を説明するためのフロー図であり、図 1 1 は、図 1 0 に示す半導体レーザモジュール 2 の製造過程をより詳しく説明するための図である。

20

【 0 0 5 1 】

半導体レーザモジュール 2 と前述した半導体レーザモジュール 1 との相違点は、半導体レーザモジュール 2 では、 P P L N 素子 3 0 はマイクロバンプ 1 9 とは熱硬化性の接合用樹脂によって固定されている点である。したがって、 P P L N 素子 3 0 のマイクロバンプ側の基板には、 A u 層は形成されていない。半導体レーザモジュール 2 では、 P P L N 素子 3 0 には電流を供給する必要が無いことから、コストのかかる A u 層を用いずに、熱硬化性の接合用樹脂によってマイクロバンプ 1 9 上に固定している。半導体レーザモジュール 2 において、他の点は、全て半導体レーザモジュール 1 と同様である。したがって、図 1 0 に示す半導体レーザモジュール 2 の製造過程における S 2 0 ~ S 2 5 及び S 2 7 は、図 2 に示す半導体レーザモジュール 1 の製造過程における S 1 0 ~ S 1 5 及び S 1 7 と全く同じであるので、説明を省略する。

30

【 0 0 5 2 】

図 1 0 に示す半導体レーザモジュール 2 の製造過程では、 S 2 6 において、マイクロバンプ 1 8 の表面のみ、洗浄及び / 又はプラズマを利用した処理を施して、表面活性化が行われる。なお、マイクロバンプ 1 9 についても、表面活性化処理を行っても良い。

【 0 0 5 3 】

S 2 7 において、図 2 の S 1 7 と同様に L D 素子 2 0 の実装を行った後、マイクロバンプ 1 9 上に、接合用樹脂 7 0 を塗布する ( 図 1 1 ( a ) 参照 ) 。接合用樹脂 7 0 としては、光学部品用の熱硬化性樹脂又は U V 硬化性樹脂等を利用することができる。

40

【 0 0 5 4 】

次に、接合用樹脂 7 0 上に、 P P L N 素子 3 0 の加熱調芯実装を行う ( S 2 9 ) ( 図 1 1 ( b ) 参照 ) 。 S 2 9 における調芯実装の方法は、図 2 の S 1 8 及び図 5 ( b ) で示した調芯実装と全く同じである。したがって、制御部 1 0 1 は、マイクロバンプ 1 9 の弾性戻り量を予め考慮して、 P P L N 素子 3 0 を、検出部 1 0 2 からの出力電圧 V が最大値となつた後 ( 点 D 参照 ) 、更に所定の荷重量 ( F : 2 0 0 ( N ) ) を更に印加する。即ち、 P P L N 素子 3 0 の入射位置 3 1 が、 L D 素子 2 0 の発光中心 2 1 よりも、図 1 1 ( b ) に示す距離 W 3 分だけ、更に深く押し込まれた位置となるように、所定の荷重を更に印加する。しかしながら、加熱調芯実装では、さらに荷重を加えた状態で加熱を行い、接合用

50

樹脂 70 を硬化させている。

【0055】

次に、荷重を開放すると、PPLN 素子 30 の入射位置 31 が、LD 素子 20 の発光中心 21 と最も効率良く光結合する位置に弾性戻りによって戻るので(図 11 (c) 参照)、一連の工程を終了する。

【0056】

上述したように、図 10 及び図 11 を用いて、接合用接着材 70 を利用した PPLN 素子 30 とシリコン基板 10 との接合について説明した。しかしながら、接合用接着材 70 を用いて LD 素子 20 とシリコン基板 10 とを接合するようにしても良い。なお、LD 素子 20 とシリコン基板 10 との導通をマイクロバンプ 18 によって取る必要がある場合には、接合用接着材 70 をマイクロバンプ 18 が突き破るような構成とすれば良い。さらには、LD 素子 20 とシリコン基板 10 との導通を接着剤により取る必要がある場合には、導電性接着材を利用して LD 素子 20 とシリコン基板 10 とを接合するようにすれば良い。

10

【0057】

さらに、接着材を利用して、LD 素子 20 又は PPLN 素子 30 とシリコン基板 10 とを接合する場合でも、図 8 を用いて説明したように、芯調実装工程(図 2 の S18)において、制御部 101、検出部 102、駆動部 104 を用いずに、調芯実装器 103 のみを用いて行うようにしても良い。

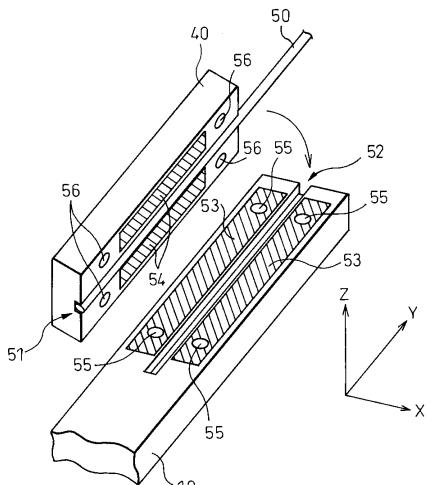

【0058】

図 12 ~ 図 14 を用いて、光モジュールの一例である半導体レーザモジュール 1 の製造過程の内、サブ基板 40 の接合について説明する。図 12 は、基板 10 とサブ基板 40 との接合を説明するための図であり、図 13 は、PPLN 素子 30 とファイバ 50 との位置関係を示す図であり、図 14 は、サブ基板 40 の調芯実装を説明するための図である。

20

【0059】

図 12 に示すように、サブ基板 40 には、凹溝 51 が形成されており、凹溝 51 に光ファイバ 50 の先端部 58 が嵌め込まれ、接着材 57 によって固定されている。凹溝 51 のかわりに V 溝をサブ基板 40 に形成し、この V 溝に光ファイバ 50 の先端部 58 を嵌め込み、固定しても良い。サブ基板 40 の接合面には、金薄膜 54 及びアライメントマーク 56 が設けられている。また、シリコン基板 10 のサブ基板 40 に対応する部分には、ファイバ逃がし溝 52、マイクロバンプ 53、及びアライメントマーク 55 が設けられている。

30

【0060】

サブ基板 40 は、後述するように調芯実装加重実装器 103 によってシリコン基板 10 上に実装される。サブ基板 40 が実装される際には、アライメントマーク 55 及び 56 によって大まかな位置が決定され、その後光ファイバ 50 からの出力を検知器 102 で検知しながら、X 軸方向、Y 軸方向及び Z 軸方向の位置がサブミクロンオーダで決定されて、シリコン基板 10 上に接合される。サブ基板 40 の接合面及びシリコン基板 10 上に形成されたマイクロバンプ 53 は、プラズマ洗浄処理が施された後、調芯実装加重実装器 103 から加わる加重によって、表面活性化接合される。なお、シリコン基板 10 上に形成された金により構成されるマイクロバンプ 53 は、前述したマイクロバンプ 18 及び 19 と同様の方法によってシリコン基板 10 上に形成される。

40

【0061】

図 13 (a) は、図 1 の B-B' 断面図である。図 13 (a) に示すように、サブ基板 40 の凹溝 51 に接着材 57 で固定された光ファイバ 50 は、調芯実装加重実装器 103 がサブ基板 40 を X 軸及び Y 軸方向に移動させることによって、シリコン基板 10 に設けられたファイバ逃がし溝 52 内で移動可能となる。即ち、ファイバ逃がし溝 52 の幅 W4 の範囲内で、X 軸及び Y 軸方向の位置調整が可能となる。なお、図 13 (a) では、マイクロバンプ 52 等は省略している。

【0062】

図 13 (b) は、図 1 の C-C' 断面図である。図 13 (b) に示すように、サブ基板 4

50

0に固定された光ファイバ50の先端部58は、PPLN素子30の出射中心32と精度よく光結合され、PPLN素子30の出射中心32から出射される波長変換された532nmの緑色レーザを受光する。光ファイバ50の先端部58で受光された532nmの緑色レーザは、光ファイバ50で伝播される。図13(b)では、マイクロバンプ53等は省略して記載しているが、Z方向のおけるPPLN素子30の出射中心32と光ファイバ50の先端部58の位置合わせは、マイクロバンプ53によって制御される。

#### 【0063】

図14を用いて、サブ基板40の芯調実装について説明する。図5(b)(図2のS18)の例では、PPLN素子30の調芯実装について説明したが、図14では、同様に方法によって、PPLN素子30の出射中心32と光ファイバ50の先端部58とが精度よく光結合されるようにサブ基板40の芯調実装が行われる。図14に示す調芯実装を行う前に、サブ基板40の接合面側の金薄膜54及びシリコン基板10のマイクロバンプ53の表面にはプラズマ洗浄処理が施されているものとする。

10

#### 【0064】

図14における調芯実装は、図5(b)の場合と同様に調芯実装装置100を用いて行う。制御部101は、駆動部104を制御してLD素子20を駆動させてレーザ光をPPLN素子30に入射させ、PPLN素子30から出射され、光ファイバ50で伝播されたレーザ光の強度を検出部102で検出する。

#### 【0065】

最初に、制御部101は、検出部102で検出された検出出力電圧Vをモニタしながら、調芯実装器103を制御し、サブ基板40をX軸及びY軸方向に移動ながら、最も出力電圧Vが高い位置を決定する(第1段階)。前述したように、光ファイバ50は、光ファイバ逃がし溝52の幅W4内の範囲内で移動可能であるので、この範囲で調芯実装器103はサブ基板40をX軸及びY軸方向に移動させることとなる。

20

#### 【0066】

次に、制御部101は、調芯実装器103を制御し、第1段階で最も出力電圧Vが高い位置でサブ基板40をマイクロバンプ53に配置する。

#### 【0067】

次に、制御部101は、検出部102で検出された検出出力電圧Vをモニタしながら、調芯実装器103を制御してサブ基板40に印加する荷重を制御して、サブ基板40のZ方向の位置決めを行う(第2段階)。ここで、制御部101は、検出部102からの出力電圧Vが最大値となった後、更に所定の荷重量を更に印加し、その後荷重を開放する。サブ基板40に固定されている光ファイバ50の先端部58が、PPLN素子30の出射中心32よりも、所定距離だけ、更に深く押し込まれた位置となるように、所定の荷重を更に印加する。その後、荷重が開放されることによって、サブ基板40に固定されている光ファイバ50の先端部58が、PPLN素子30の出射中心32と最も効率良く光結合する位置に弾性戻りによって戻る。なお、上記の点は、図5～図7を用いて説明したPPLN素子30とLD素子20との光結合を行うための調芯実装と同様の理論に基づく。このように、サブ基板40は、第1段階でX軸及びY軸方向の位置決めがなされ、第2段階としてZ軸方向の位置決めがなされることとなる。

30

#### 【0068】

なお、図12～図14を用いて説明したサブ基板40の接合方法において、図8を用いて説明したように、芯調実装工程(図14)において、制御部101、検出部102、駆動部104を用いず、調芯実装器103のみを用いて、予め定められた荷重の印加のみを行うようにしても良い。また、図12～図14を用いて説明したサブ基板40の接合方法において、図9に示した異なったマイクロバンプ18'及び19'を用いても良い。さらに、図12～図14を用いて説明したサブ基板40の接合方法において、図10及び11で説明したように、接着材を利用して、サブ基板40をシリコン基板10と接合しても良い。

40

#### 【0069】

50

上記の例では、接合用バンプの例として、A u から成形された円柱状の突起を有するマイクロバンプ 18、19 及び 53（図 4（c）参照）、及び A u から成形された切頭円錐形状の突起を有するマイクロバンプ 18' 及び 19'（図 9 参照）を説明した。しかしながら、精度良く形成された形状を有する金属から構成される接合用バンプであれば、他の接合用バンプを利用することも可能である。接合用バンプに求められる条件は、一定の荷重を印加した場合の変形量と、一定の荷重を印加後に荷重を開放した場合の弾性戻り量が、常にほぼ一定となるような材質及び形状を有することである。

#### 【0070】

上記の例では、光モジュール 1 は、LD 素子 20、PPLN 素子 30、光ファイバ 50 が固定されたサブ基板 40 がマイクロバンプを利用して表面活性化接合によりシリコン基板 10 に接合されている。しかしながら、LD 素子 20 及び PPLN 素子 30 のみ、又は PPLN 素子 30 及び光ファイバ 50 が固定されたサブ基板 40 のみが、良好に光結合するようにマイクロバンプを利用して表面活性化接合によりシリコン基板 10 に接合されても良い。

10

#### 【符号の説明】

#### 【0071】

|                  |         |    |

|------------------|---------|----|

| 10               | シリコン基板  | 20 |

| 18、18'、19、19'、53 | マイクロバンプ |    |

| 20               | LD 素子   |    |

| 30               | PPLN 素子 | 20 |

| 40               | サブ基板    |    |

| 50               | 光ファイバ   |    |

| 70               | 接合用樹脂   |    |

| 100              | 調芯実装装置  |    |

| 101              | 制御部     |    |

| 102              | 検出部     |    |

| 103              | 調芯実装器   |    |

| 104              | 駆動部     |    |

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

【図14】

図14

---

フロントページの続き

(72)発明者 依田 薫

長野県北佐久郡御代田町大字御代田4107番地5 シチズンファインテックミヨタ株式会社内

審査官 高 芳徳

(56)参考文献 特開2005-311298 (JP, A)

特開2002-111113 (JP, A)

特開2001-189339 (JP, A)

特開2007-133011 (JP, A)

特開2009-134320 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02B 6/12 - 6/43

G02F 1/00 - 7/00

H01S 5/02 - 5/022