(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7202145号**

**(P7202145)**

(45)発行日 令和5年1月11日(2023.1.11)

(24)登録日 令和4年12月27日(2022.12.27)

(51)国際特許分類

|         |                 |     |         |        |         |

|---------|-----------------|-----|---------|--------|---------|

| G 0 9 G | 3/20 (2006.01)  | F I | G 0 9 G | 3/20   | 6 2 4 B |

| G 0 9 G | 3/3233(2016.01) |     | G 0 9 G | 3/20   | 6 1 1 A |

| H 1 0 K | 59/00 (2023.01) |     | G 0 9 G | 3/20   | 6 4 2 F |

|         |                 |     | G 0 9 G | 3/20   | 6 9 1 G |

|         |                 |     | G 0 9 G | 3/3233 |         |

請求項の数 3 (全36頁) 最終頁に続く

(21)出願番号 特願2018-207883(P2018-207883)

(22)出願日 平成30年11月5日(2018.11.5)

(65)公開番号 特開2019-144528(P2019-144528)

A)

(43)公開日 令和1年8月29日(2019.8.29)

審査請求日 令和3年9月17日(2021.9.17)

(31)優先権主張番号 特願2017-216389(P2017-216389)

(32)優先日 平成29年11月9日(2017.11.9)

(33)優先権主張国・地域又は機関

日本国(JP)

(31)優先権主張番号 特願2018-28368(P2018-28368)

(32)優先日 平成30年2月21日(2018.2.21)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

川島 進

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

楠 純慈

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

渡邊 一徳

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

豊高 耕平

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

最終頁に続く

(54)【発明の名称】 表示装置

**(57)【特許請求の範囲】****【請求項1】**

画素と、回路と、を有する表示装置であって、

前記画素は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第1の容量素子と、第2の容量素子と、表示素子と、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記第1の容量素子の一方の電極と電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、

前記第2のトランジスタのソース又はドレインの一方は、前記第1の容量素子の他方の電極と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、

前記第1の容量素子の一方の電極は、前記第3のトランジスタのゲートと電気的に接続され、

前記第3のトランジスタのゲートは、前記第2の容量素子の一方の電極と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第2の容量素子の他方の電極と電気的に接続され、

前記第2の容量素子の他方の電極は、前記第4のトランジスタのソース又はドレインの

10

20

一方と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記表示素子の一方の電極と電気的に接続され、

前記回路は、前記第1の配線及び前記第2の配線と電気的に接続され、

前記回路は、前記第1の配線に、第1の画像信号を供給する機能を有し、

前記回路は、前記第2の配線に、参照電位を供給する機能を有し、

前記参照電位は、外光の照度に応じた大きさの電位であり、且つ、前記外光の照度が高いほど、前記参照電位の電位は小さく設定され、且つ、負電位であり、

前記回路は、前記第2の配線に、第2の画像信号を供給する機能を有する、表示装置。

#### 【請求項2】

10

請求項1において、

前記第1の容量素子の容量値は、前記第2の容量素子の容量値より大きい、表示装置。

#### 【請求項3】

請求項1又は請求項2において、

前記表示素子は、有機EL素子である、表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明の一態様は、表示装置及びその動作方法、並びに電子機器に関する。

##### 【0002】

20

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、又は、製造方法に関するものである。又は、本発明の一態様は、プロセス、マシン、マニュファクチャ、又は、組成物（コンポジション・オブ・マター）に関するものである。そのため、より具体的に本明細書で開示する本発明の一態様の技術分野としては、半導体装置、表示装置、液晶表示装置、発光装置、照明装置、蓄電装置、記憶装置、撮像装置、それらの動作方法、又は、それらの製造方法、を一例として挙げることができる。

##### 【0003】

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。トランジスタ、半導体回路は半導体装置の一態様である。また、記憶装置、表示装置、撮像装置、電子機器は、半導体装置を有する場合がある。

30

##### 【背景技術】

##### 【0004】

基板上に形成された金属酸化物を用いてトランジスタを構成する技術が注目されている。例えば、酸化亜鉛又はIn-Ga-Zn系酸化物を用いたトランジスタを表示装置の画素のスイッチング素子等に用いる技術が特許文献1及び特許文献2に開示されている。

##### 【0005】

また、オフ電流が極めて低いトランジスタをメモリセルに用いる構成の記憶装置が特許文献3に開示されている。

##### 【先行技術文献】

40

##### 【特許文献】

##### 【0006】

【文献】特開2007-123861号公報

特開2007-96055号公報

特開2011-119674号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0007】

EL（Electro Luminescence）素子等を有する表示装置において、高輝度の画像を表示する場合、ソースドライバが高い電位の画像信号を生成して、EL素

50

子等を有する画素に供給しなければならない。しかし、ソースドライバの耐圧等のため、ソースドライバが生成できる画像信号の電位の高さには限界がある。また、ソースドライバが高い電位の画像信号を生成すると、表示装置の消費電力が増加する。

【0008】

本発明の一態様は、ソースドライバが出力可能な電位より高い電位の画像信号に対応する画像を表示することができる表示装置を提供することを課題の一つとする。又は、高輝度の画像を表示することができる表示装置を提供することを課題の一つとする。又は、高ダイナミックレンジの表示装置を提供することを課題の一つとする。又は、低消費電力の表示装置を提供することを課題の一つとする。又は、外光の照度に応じた輝度の画像を表示することができる表示装置を提供することを課題の一つとする。又は、視認性の高い画像を表示することができる表示装置を提供することを課題の一つとする。又は、信頼性の高い表示装置を提供することを課題の一つとする。又は、新規な表示装置等を提供することを課題の一つとする。又は、上記表示装置の動作方法を提供することを課題の一つとする。又は、新規な半導体装置等を提供することを課題の一つとする。

10

【0009】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項等の記載から、自ずと明らかとなるものであり、明細書、図面、請求項等の記載から、これら以外の課題を抽出することが可能である。

【課題を解決するための手段】

20

【0010】

本発明の一態様は、画素と、回路と、を有する表示装置であって、画素は、第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、第4のトランジスタと、第1の容量素子と、第2の容量素子と、表示素子と、を有し、第1のトランジスタのソース又はドレインの一方は、第1の容量素子の一方の電極と電気的に接続され、第1のトランジスタのソース又はドレインの他方は、第1の配線と電気的に接続され、第2のトランジスタのソース又はドレインの一方は、第1の容量素子の他方の電極と電気的に接続され、第2のトランジスタのソース又はドレインの他方は、第2の配線と電気的に接続され、第1の容量素子の一方の電極は、第3のトランジスタのゲートと電気的に接続され、第3のトランジスタのソース又はドレインの一方は、第2の容量素子の他方の電極と電気的に接続され、第3のトランジスタのゲートは、第2の容量素子の一方の電極と電気的に接続され、第3のトランジスタのソース又はドレインの一方は、第2の容量素子の他方の電極と電気的に接続され、第4のトランジスタのソース又はドレインの一方は、表示素子の一方の電極と電気的に接続され、回路は、第1の配線及び第2の配線と電気的に接続され、回路は、第1の配線に、第1の画像信号を供給する機能を有し、回路は、第2の配線に、参照電位を供給する機能を有し、回路は、第2の配線に、第2の画像信号を供給する機能を有する表示装置である。

30

【0011】

または、上記態様において、参照電位は、外光の照度に応じた大きさの電位であってよい。

40

【0012】

または、上記態様において、外光の照度が高いほど、参照電位の電位は小さくてもよい。

【0013】

または、上記態様において、参照電位は、負電位であってよい。

【0014】

または、上記態様において、第1の容量素子の容量値は、第2の容量素子の容量値より大きくてよい。

【0015】

または、上記態様において、表示素子は、有機EL素子であってよい。

【0016】

50

または、上記態様において、第1のトランジスタは、チャネル形成領域に金属酸化物を有し、金属酸化物は、Inと、Znと、M(MはAl、Ti、Ga、Sn、Y、Zr、La、Ce、Nd又はHf)と、を有してもよい。

#### 【0017】

または、本発明の一態様の表示装置と、カメラと、を有する電子機器も本発明の一態様である。

#### 【0018】

または、本発明の一態様は、表示素子と、第1の配線及び第2の配線と電気的に接続されたメモリ回路と、が設けられた画素を有する表示装置の動作方法であって、第1の配線に、参照電位を供給し、第2の配線を介して、メモリ回路に第1の画像信号を格納し、第1の配線を介して、メモリ回路に第2の画像信号を供給することにより、第1の画像信号に第2の画像信号を付加し、表示素子により、第1の画像信号に対応する画像と、第2の画像信号に対応する画像と、を重ね合わせた画像を表示する表示装置の動作方法である。10

#### 【0019】

または、上記態様において、参照電位は、外光の照度に応じた大きさの電位であってよい。

#### 【0020】

または、上記態様において、外光の照度が高いほど、参照電位の電位は小さくてもよい。

#### 【0021】

または、上記態様において、参照電位は、負電位であってよい。20

#### 【発明の効果】

#### 【0022】

本発明の一態様により、ソースドライバが出力可能な電位より高い電位の画像信号に対応する画像を表示することができる表示装置を提供することができる。又は、高輝度の画像を表示することができる表示装置を提供することができる。又は、高ダイナミックレンジの表示装置を提供することができる。又は、低消費電力の表示装置を提供することができる。又は、外光の照度に応じた輝度の画像を表示することができる表示装置を提供することができます。又は、視認性の高い画像を表示することができる表示装置を提供することができます。又は、信頼性の高い表示装置を提供することができます。又は、新規な表示装置等を提供することができます。又は、上記表示装置の動作方法を提供することができます。又は、新規な半導体装置等を提供することができます。30

#### 【図面の簡単な説明】

#### 【0023】

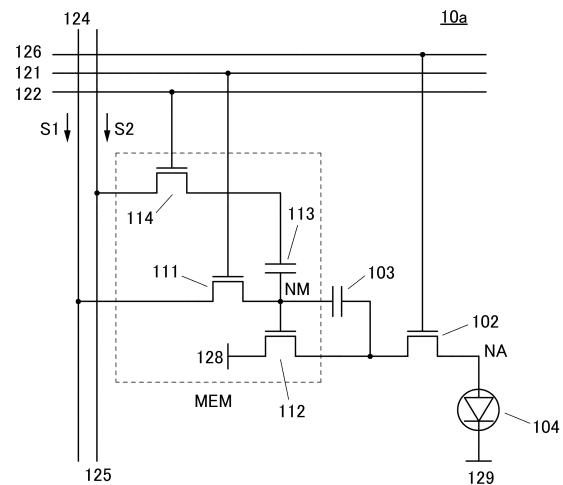

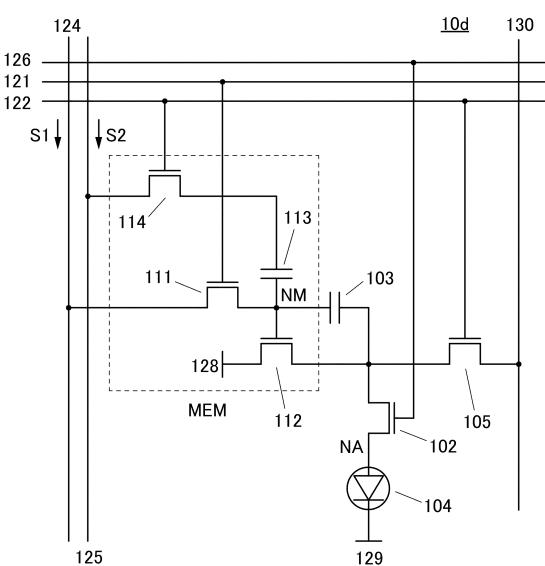

【図1】画素回路の構成例を説明する図。

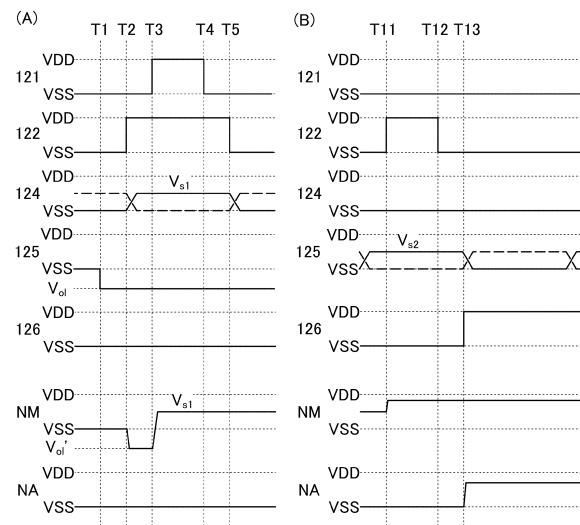

【図2】画素回路の動作例を説明するタイミングチャート。

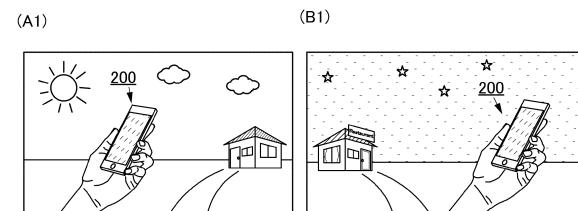

【図3】画素回路の動作例を説明する図。

【図4】表示装置の動作例を説明する図。

【図5】表示装置の構成例を説明するブロック図。

【図6】画素について説明する図。

【図7】画素回路の構成例を説明する図。

【図8】画素回路の構成例を説明する図。

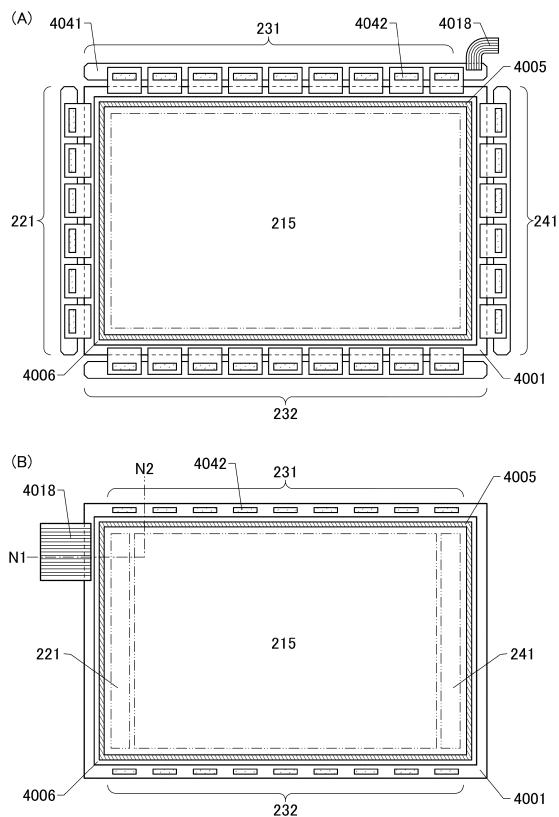

【図9】表示装置の構成例を説明する図。

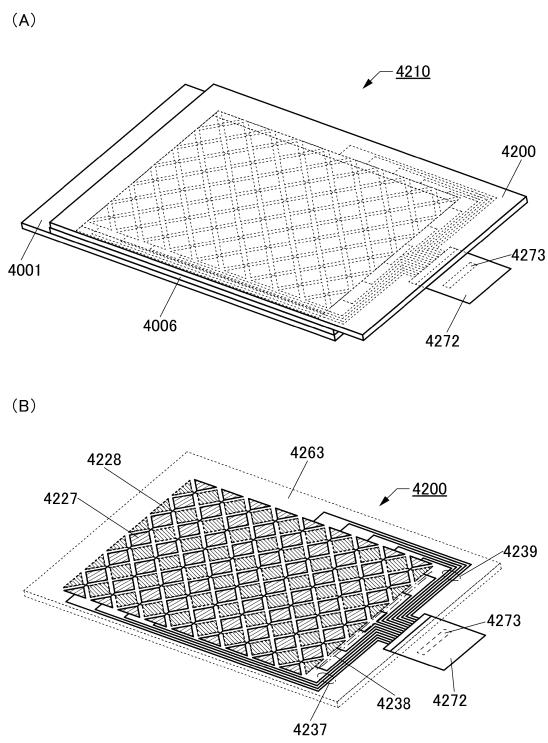

【図10】タッチパネルの構成例を説明する図。

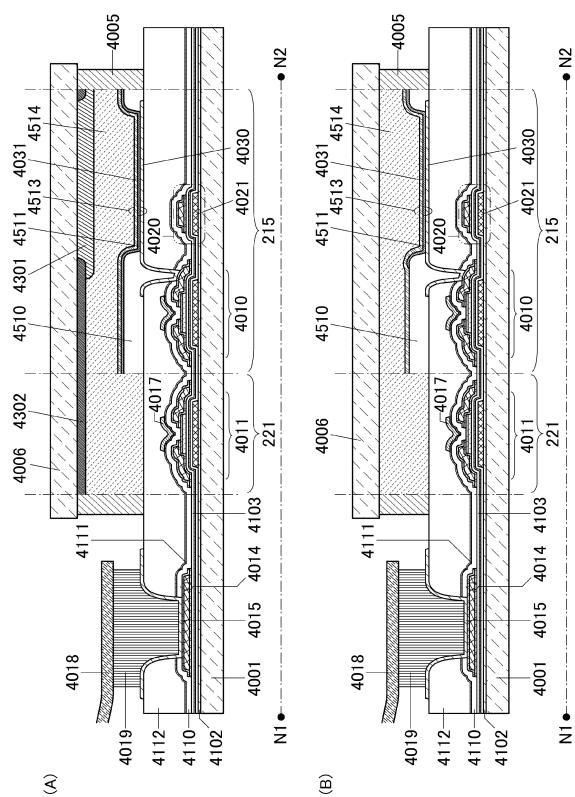

【図11】表示装置の構成例を説明する図。

【図12】トランジスタの構成例を説明する図。

【図13】トランジスタの構成例を説明する図。

【図14】電子機器の一例を説明する図。

【図15】DOSRAMの構成例を示す断面図。

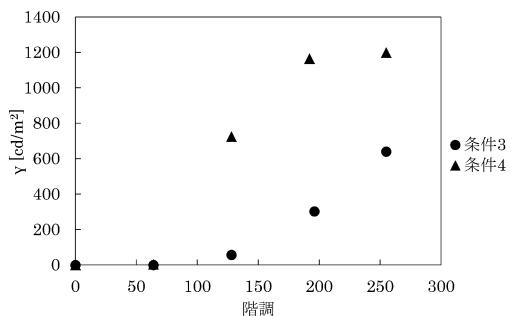

【図16】値と階調との関係を説明するグラフ。

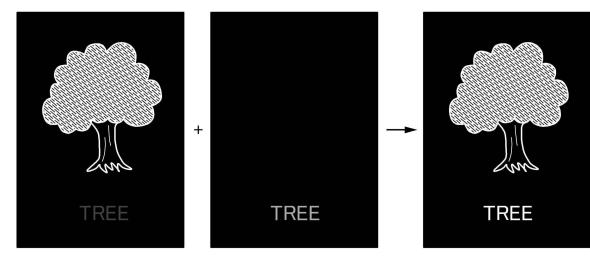

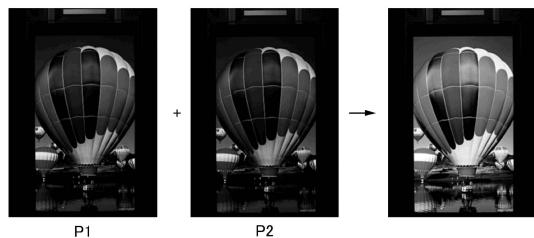

【図17】表示結果を説明する図。

10

20

30

40

50

**【発明を実施するための形態】**

**【0024】**

実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略することがある。なお、図を構成する同じ要素のハッティングを異なる図面間で適宜省略又は変更する場合もある。

**【0025】**

本明細書等において、“第1”、“第2”、“第3”という序数詞は構成要素の混同を避けるために付す場合があり、その場合は数的に限定するものではなく、また順序を限定するものでもない。

**【0026】**

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタ等のスイッチング素子、抵抗素子、コイル、容量素子、その他の各種機能を有する素子等が含まれる。

**【0027】**

(実施の形態1)

本実施の形態では、本発明の一態様である表示装置について、図面を参照して説明する。

**【0028】**

本発明の一態様は、画素に第1の画像信号を供給し、当該第1の画像信号に第2の画像信号を付加する機能を有する表示装置である。ここで、第1の画像信号及び第2の画像信号は、ソースドライバ等の、画素の外部に設けられる回路により生成することができる。各画素にはメモリ回路が設けられ、当該メモリ回路に第1の画像信号が保持される。

**【0029】**

その後、第1の画像信号が保持されたメモリ回路に、第2の画像信号が付加され、表示素子に供給される。したがって、表示素子では、第1の画像信号に対応する画像と、第2の画像信号に対応する画像と、を重ね合わせて表示することができる。これにより、ソースドライバ等が生成可能な電位より高い電位の画像信号に対応する画像を、表示装置が表示することができる。以上により、画像信号を付加せず、1つの画像信号のみに対応する画像を表示する場合より、高輝度の画像を表示装置が表示することができ、表示装置のダイナミックレンジを高めることができる。また、ソースドライバ等が生成する画像信号の電位を低くすることができるので、表示装置の消費電力を低減することができる。

**【0030】**

本明細書等において、第1の画像信号という用語と、第2の画像信号という用語は、必要に応じて、又は適宜入れ替えることができるものとする。

**【0031】**

(画素回路の構成例)

図1は、本発明の一態様の表示装置に用いることができる画素10aを説明する図である。画素10aは、トランジスタ102と、トランジスタ111と、トランジスタ112と、トランジスタ114と、容量素子103と、容量素子113と、EL素子104を有する。

**【0032】**

トランジスタ111のソース又はドレインの一方は、容量素子113の一方の電極と電気的に接続される。トランジスタ114のソース又はドレインの一方は、容量素子113の他方の電極と電気的に接続される。容量素子113の一方の電極は、トランジスタ112

10

20

30

40

50

のゲートと電気的に接続される。トランジスタ 112 のゲートは、容量素子 103 の一方の電極と電気的に接続される。トランジスタ 112 のソース又はドレインの一方は、容量素子 103 の他方の電極と電気的に接続される。容量素子 103 の他方の電極は、トランジスタ 102 のソース又はドレインの一方と電気的に接続される。トランジスタ 102 のソース又はドレインの他方は、EL 素子 104 の一方の電極と電気的に接続される。

#### 【0033】

ここで、トランジスタ 111 のソース又はドレインの一方、容量素子 113 の一方の電極、トランジスタ 112 のゲート、及び容量素子 103 の一方の電極が接続される配線をノード NM とする。また、トランジスタ 102 のソース又はドレインの他方、及び EL 素子 104 の一方の電極が接続される配線をノード NA とする。

10

#### 【0034】

トランジスタ 111 のゲートは、配線 121 に電気的に接続される。トランジスタ 114 のゲートは、配線 122 と電気的に接続される。トランジスタ 102 のゲートは、配線 126 と電気的に接続される。トランジスタ 111 のソース又はドレインの他方は、配線 124 と電気的に接続される。トランジスタ 114 のソース又はドレインの他方は、配線 125 と電気的に接続される。

#### 【0035】

トランジスタ 112 のソース又はドレインの他方は、電源線 128 (高電位) と電気的に接続される。EL 素子 104 の他方の電極は、共通配線 129 と電気的に接続される。なお、共通配線 129 には、任意の電位を供給することができる。

20

#### 【0036】

配線 121、配線 122、及び配線 126 は、トランジスタの動作を制御するための走査線としての機能を有する。配線 124 は、画像信号 S1 を供給する信号線としての機能を有する。配線 125 は、画像信号 S2 を供給する信号線としての機能を有する。なお、画像信号 S1 及び画像信号 S2 は、ソースドライバ等の、画素 10a の外部に設けられる回路 (図 1 には図示せず) により生成することができる。

#### 【0037】

トランジスタ 111、トランジスタ 112、容量素子 113、及びトランジスタ 114 は、メモリ回路 MEM を構成する。なお、トランジスタ 114 をメモリ回路 MEM に含めなくてよい。

30

#### 【0038】

ノード NM は記憶ノードであり、トランジスタ 111 を導通させることで、配線 124 に供給された信号をノード NM に書き込むことができる。トランジスタ 111 に極めてオフ電流の低いトランジスタを用いることで、ノード NM の電位を長時間保持することができる。当該トランジスタには、例えば、金属酸化物をチャネル形成領域に用いたトランジスタ (以下、OS トランジスタ) を用いることができる。

#### 【0039】

なお、トランジスタ 111 だけでなく、画素を構成するその他のトランジスタに OS トランジスタを適用してもよい。また、トランジスタ 111 に Si をチャネル形成領域に有するトランジスタ (以下、Si トランジスタ) を適用してもよい。又は、画素を構成するトランジスタの一部に OS トランジスタを用い、その他に Si トランジスタを用いてもよい。なお、上記 Si トランジスタとしては、アモルファスシリコンを有するトランジスタ、結晶性のシリコン (代表的には、低温ポリシリコン) を有するトランジスタ、単結晶シリコンを有するトランジスタ等が挙げられる。

40

#### 【0040】

表示素子に EL 素子を用いる場合はシリコン基板を用いることができ、Si トランジスタと OS トランジスタとが重なる領域を有するように形成することができる。したがって、トランジスタ数が比較的多くても画素密度を向上させることができる。

#### 【0041】

OS トランジスタに用いる半導体材料としては、エネルギーギャップが 2 eV 以上、好ま

50

しくは2.5 eV以上、より好ましくは3 eV以上である金属酸化物を用いることができる。代表的には、インジウムを含む酸化物半導体等であり、例えば、後述する C A A C - O S 又は C A C - O S 等を用いることができる。C A A C - O S は結晶を構成する原子が安定であり、信頼性を重視するトランジスタ等に適する。また、C A C - O S は、高移動度特性を示すため、高速動作を行うトランジスタ等に適する。

#### 【0042】

O S トランジスタはエネルギーギャップが大きいため、極めて低いオフ電流特性を示す。また、O S トランジスタは、インパクトイオン化、アバランシェ降伏、及び短チャネル効果等が生じない等 S i トランジスタとは異なる特徴を有し、信頼性の高い回路を形成することができる。

10

#### 【0043】

O S トランジスタが有する半導体層は、例えばインジウム、亜鉛、及びM（アルミニウム、チタン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、セリウム、スズ、ネオジム、又はハフニウム等の金属）を含む I n - M - Z n で表記される酸化物膜とすることができます。

#### 【0044】

半導体層を構成する酸化物半導体が I n - M - Z n 系酸化物の場合、I n - M - Z n 系酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、I n : M : Z n = 1 : 1 : 1 、 I n : M : Z n = 1 : 1 : 1 . 2 、 I n : M : Z n = 3 : 1 : 2 、 I n : M : Z n = 4 : 2 : 3 、 I n : M : Z n = 4 : 2 : 4 . 1 、 I n : M : Z n = 5 : 1 : 6 、 I n : M : Z n = 5 : 1 : 7 、 I n : M : Z n = 5 : 1 : 8 等が好ましい。なお、成膜される半導体層の原子数比はそれぞれ、上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス 40 % の変動を含む。

20

#### 【0045】

半導体層としては、キャリア密度の低い酸化物半導体を用いる。例えば、半導体層は、キャリア密度が  $1 \times 10^{17} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{15} / \text{cm}^3$  以下、さらに好ましくは  $1 \times 10^{13} / \text{cm}^3$  以下、より好ましくは  $1 \times 10^{11} / \text{cm}^3$  以下、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上のキャリア密度の酸化物半導体を用いることができる。そのような酸化物半導体を、高純度真性又は実質的に高純度真性な酸化物半導体という。当該酸化物半導体は欠陥準位密度が低く、安定な特性を有する酸化物半導体であるといえる。

30

#### 【0046】

なお、これらに限らず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、半導体層のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0047】

半導体層を構成する酸化物半導体において、第14族元素の一つであるシリコンや炭素が含まれると、酸素欠損が増加し、n型化してしまう。このため、半導体層におけるシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、好ましくは  $2 \times 10^{17} \text{ atoms} / \text{cm}^3$  以下とする。

40

#### 【0048】

また、アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、半導体層におけるアルカリ金属又はアルカリ土類金属の濃度（二次イオン質量分析法により得られる濃度）を、 $1 \times 10^{18} \text{ atoms} / \text{cm}^3$  以下、好ましくは  $2 \times 10^{16} \text{ atoms} / \text{cm}^3$  以下にする。

#### 【0049】

また、半導体層を構成する酸化物半導体に窒素が含まれていると、キャリアである電子が

50

生じてキャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため半導体層における窒素濃度（二次イオン質量分析法により得られる濃度）は、 $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下にすることが好ましい。

#### 【0050】

また、半導体層は、例えば非単結晶構造でもよい。非単結晶構造は、例えば、c軸に配向した結晶を有するCAC-OS (C-Axis Aligned Crystalline Oxide Semiconductor)、多結晶構造、微結晶構造、又は非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、CAC-OSは最も欠陥準位密度が低い。

10

#### 【0051】

非晶質構造の酸化物半導体膜は、例えば、原子配列が無秩序であり、結晶成分を有さない。又は、非晶質構造の酸化物膜は、例えば、完全な非晶質構造であり、結晶部を有さない。

#### 【0052】

なお、半導体層が、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAC-OSの領域、単結晶構造の領域のうち、二種以上を有する混合膜であってもよい。混合膜は、例えば上述した領域のうち、いずれか二種以上の領域を含む単層構造、又は積層構造を有する場合がある。

#### 【0053】

以下では、非単結晶の半導体層の一態様であるCAC (Cloud-Aligned C composite) - OSの構成について説明する。

20

#### 【0054】

CAC-OSとは、例えば、酸化物半導体を構成する元素が、0.5nm以上10nm以下、好ましくは、1nm以上2nm以下、又はその近傍のサイズで偏在した材料の一構成である。なお、以下では、酸化物半導体において、一つあるいはそれ以上の金属元素が偏在し、該金属元素を有する領域が、0.5nm以上10nm以下、好ましくは、1nm以上2nm以下、又はその近傍のサイズで混合した状態をモザイク状、又はパッチ状ともいう。

#### 【0055】

なお、酸化物半導体は、少なくともインジウムを含むことが好ましい。特にインジウム及び亜鉛を含むことが好ましい。また、それらに加えて、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンゲステン、マグネシウム等から選ばれた一種、又は複数種が含まれていてよい。

30

#### 【0056】

例えば、In-Ga-Zn酸化物におけるCAC-OS (CAC-OSの中でもIn-Ga-Zn酸化物を、特にCAC-IGZOと呼称してもよい。)とは、インジウム酸化物（以下、InO<sub>X1</sub> (X1は0よりも大きい実数)とする。）、又はインジウム亜鉛酸化物（以下、In<sub>X2</sub>Zn<sub>Y2</sub>O<sub>Z2</sub> (X2、Y2、及びZ2は0よりも大きい実数)とする。）と、ガリウム酸化物（以下、GaO<sub>X3</sub> (X3は0よりも大きい実数)とする。）、又はガリウム亜鉛酸化物（以下、Ga<sub>X4</sub>Zn<sub>Y4</sub>O<sub>Z4</sub> (X4、Y4、及びZ4は0よりも大きい実数)とする。）等と、に材料が分離することでモザイク状となり、モザイク状のInO<sub>X1</sub>、又はIn<sub>X2</sub>Zn<sub>Y2</sub>O<sub>Z2</sub>が、膜中に均一に分布した構成（以下、クラウド状ともいう。）である。

40

#### 【0057】

つまり、CAC-OSは、GaO<sub>X3</sub>が主成分である領域と、In<sub>X2</sub>Zn<sub>Y2</sub>O<sub>Z2</sub>、又はInO<sub>X1</sub>が主成分である領域とが、混合している構成を有する複合酸化物半導体である。なお、本明細書において、例えば、第1の領域の元素Mに対するInの原子数比が、第2の領域の元素Mに対するInの原子数比よりも大きいことを、第1の領域は、第2の

50

領域と比較して、Inの濃度が高いとする。

#### 【0058】

なお、IGZOは通称であり、In、Ga、Zn、及びOによる1つの化合物をいう場合がある。代表例として、 $InGaO_3 (ZnO)_{m1}$  ( $m1$ は自然数)、又は $In(1+x_0)Ga(1-x_0)O_3 (ZnO)_{m0}$  ( $-1 < x_0 < 1$ 、 $m0$ は任意数)で表される結晶性の化合物が挙げられる。

#### 【0059】

上記結晶性の化合物は、単結晶構造、多結晶構造、又はCAC構造を有する。なお、CAC構造とは、複数のIGZOのナノ結晶がc軸配向を有し、かつa-b面においては配向せずに連結した結晶構造である。

10

#### 【0060】

一方、CAC-Osは、酸化物半導体の材料構成に関する。CAC-Osとは、In、Ga、Zn、及びOを含む材料構成において、一部にGaを主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。したがって、CAC-Osにおいて、結晶構造は副次的な要素である。

#### 【0061】

なお、CAC-Osは、組成の異なる二種類以上の膜の積層構造は含まないものとする。例えば、Inを主成分とする膜と、Gaを主成分とする膜との2層からなる構造は、含まない。

20

#### 【0062】

なお、 $GaO_{x3}$ が主成分である領域と、 $In_{x2}Zn_{y2}O_{z2}$ 、又は $InO_{x1}$ が主成分である領域とは、明確な境界が観察できない場合がある。

#### 【0063】

なお、ガリウムの代わりに、アルミニウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、マグネシウム等から選ばれた一種、又は複数種が含まれている場合、CAC-Osは、一部に該金属元素を主成分とするナノ粒子状に観察される領域と、一部にInを主成分とするナノ粒子状に観察される領域とが、それぞれモザイク状にランダムに分散している構成をいう。

30

#### 【0064】

CAC-Osは、例えば基板を意図的に加熱しない条件で、スパッタリング法により形成することができる。また、CAC-Osをスパッタリング法で形成する場合、成膜ガスとして、不活性ガス（代表的にはアルゴン）、酸素ガス、及び窒素ガスの中から選ばれたいずれか一つ又は複数を用いればよい。また、成膜時の成膜ガスの総流量に対する酸素ガスの流量比は低いほど好ましく、例えば酸素ガスの流量比を0%以上30%未満、好ましくは0%以上10%以下とすることが好ましい。

#### 【0065】

CAC-Osは、X線回折(XRD:X-ray diffraction)測定法のひとつであるOut-of-plane法による /2 スキャンを用いて測定したときに、明確なピークが観察されないという特徴を有する。すなわち、X線回折測定から、測定領域のa-b面方向、及びc軸方向の配向は見られないことが分かる。

40

#### 【0066】

また、CAC-Osは、プローブ径が1nmの電子線（ナノビーム電子線ともいう。）を照射することで得られる電子線回折パターンにおいて、リング状に輝度の高い領域と、該リング領域に複数の輝点が観測される。したがって、電子線回折パターンから、CAC-Osの結晶構造が、平面方向、及び断面方向において、配向性を有しないnc(nano-crystral)構造を有することがわかる。

#### 【0067】

また、例えば、In-Ga-Zn酸化物におけるCAC-Osでは、エネルギー分散型X

50

線分光法 ( E D X : Energy Dispersive X-ray spectros copy ) を用いて取得した E D X マッピングにより、  $GaO_{x_3}$  が主成分である領域と、  $In_{x_2}Zn_{y_2}O_{z_2}$  、又は  $InO_{x_1}$  が主成分である領域とが、偏在し、混合している構造を有することが確認できる。

#### 【 0 0 6 8 】

C A C - O S は、金属元素が均一に分布した I G Z O 化合物とは異なる構造であり、 I G Z O 化合物と異なる性質を有する。つまり、 C A C - O S は、  $GaO_{x_3}$  等が主成分である領域と、  $In_{x_2}Zn_{y_2}O_{z_2}$  、又は  $InO_{x_1}$  が主成分である領域と、に互いに相分離し、各元素を主成分とする領域がモザイク状である構造を有する。

#### 【 0 0 6 9 】

ここで、  $In_{x_2}Zn_{y_2}O_{z_2}$  、又は  $InO_{x_1}$  が主成分である領域は、  $GaO_{x_3}$  等が主成分である領域と比較して、導電性が高い領域である。つまり、  $In_{x_2}Zn_{y_2}O_{z_2}$  、又は  $InO_{x_1}$  が主成分である領域を、キャリアが流れることにより、酸化物半導体としての導電性が発現する。したがって、  $In_{x_2}Zn_{y_2}O_{z_2}$  、又は  $InO_{x_1}$  が主成分である領域が、酸化物半導体中にクラウド状に分布することで、高い電界効果移動度 ( $\mu$ ) が実現できる。

10

#### 【 0 0 7 0 】

一方、  $GaO_{x_3}$  等が主成分である領域は、  $In_{x_2}Zn_{y_2}O_{z_2}$  、又は  $InO_{x_1}$  が主成分である領域と比較して、絶縁性が高い領域である。つまり、  $GaO_{x_3}$  等が主成分である領域が、酸化物半導体中に分布することで、リーケ電流を抑制し、良好なスイッチング動作を実現できる。

20

#### 【 0 0 7 1 】

したがって、 C A C - O S を半導体素子に用いた場合、  $GaO_{x_3}$  等に起因する絶縁性と、  $In_{x_2}Zn_{y_2}O_{z_2}$  、又は  $InO_{x_1}$  に起因する導電性とが、相補的に作用することにより、高いオン電流 ( $I_{on}$ ) 、及び高い電界効果移動度 ( $\mu$ ) を実現することができる。

#### 【 0 0 7 2 】

また、 C A C - O S を用いた半導体素子は、信頼性が高い。したがって、 C A C - O S は、様々な表示装置等の構成材料として適している。

#### 【 0 0 7 3 】

30

画素 10 a において、ノード N M に書き込まれた画像信号 S 1 は、配線 125 から供給される画像信号 S 2 と容量結合される。容量結合された画像信号は、ノード N A に出力することができる。なお、トランジスタ 114 は、画素を選択する機能を有する。トランジスタ 102 は、 E L 素子 104 の発光を制御するスイッチとしての機能を有する。

#### 【 0 0 7 4 】

例えば、画像信号 S 1 の電位がトランジスタ 112 のしきい値電圧 ( $V_{th}$ ) より大きい場合、画像信号 S 2 が書き込まれる前にトランジスタ 112 が導通し、 E L 素子 104 が発光してしまう。したがって、トランジスタ 102 を設け、ノード N M の電位が確定したのちにトランジスタ 102 を導通させ、 E L 素子 104 を発光させることが好ましい。

#### 【 0 0 7 5 】

40

すなわち、ノード N M に画像信号 S 1 を格納しておけば、画像信号 S 1 に画像信号 S 2 を付加することができる。画像信号を生成するソースドライバ等の耐圧等により、画像信号の電位には上限がある。そこで、2つの画像信号を重ね合わせることにより、ソースドライバ等が出力可能な電位より高い電位の画像信号に対応する画像を、表示装置が表示することができる。これにより、画像信号を付加せず、1つの画像信号のみに対応する画像を表示する場合より、高輝度の画像を表示装置が表示することができ、表示装置のダイナミックレンジを拡大することができる。また、ソースドライバ等が生成する画像信号の電位を低くすることができるので、表示装置の消費電力を低減することができる。

#### 【 0 0 7 6 】

( 画素回路の動作例 )

50

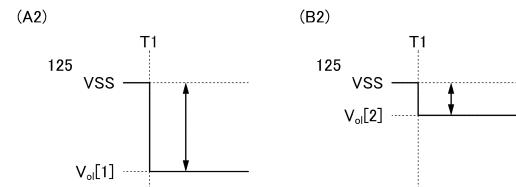

図2(A)、(B)に示すタイミングチャートを用いて、画素10aの動作例の詳細を説明する。なお、以下の説明においては、高電位を電位VDD、低電位を電位VSSで表す。ここで、電位VSSは、例えば接地電位とすることができます。また、配線124に供給される画像信号S1の電位VS1は正負の任意の電位とすることができますが、ここでは電位VSS以上の電位である場合を説明する。

#### 【0077】

まず、図2(A)を用いて画像信号S1をノードNMに書き込む動作を説明する。

#### 【0078】

時刻T1に配線121、配線122、及び配線126の電位を電位VSSとする。また、配線125の電位を、電位VSS以下の電位である電位V<sub>o1</sub>とする。電位V<sub>o1</sub>は、例えば負電位とすることができます。なお、本明細書等において、電位V<sub>o1</sub>を参照電位と呼ぶ場合がある。

10

#### 【0079】

時刻T2に配線122の電位を電位VDDとする。これにより、トランジスタ114が導通し、容量素子113の他方の電極の電位は電位V<sub>o1</sub>となる。また、ノードNMの電位は、電位V<sub>o1</sub>に対応する電位V<sub>o1'</sub>となる。ここで、電位V<sub>o1'</sub>は、容量素子113の容量値と、容量素子103の容量値との比によって変化する。

#### 【0080】

時刻T3に配線121の電位を電位VDDとする。これにより、トランジスタ111が導通し、配線124の電位VS1がノードNMに書き込まれる。

20

#### 【0081】

時刻T4に配線121の電位を電位VSSとする。これにより、トランジスタ111が非導通となり、ノードNMに電位VS1が保持される。

#### 【0082】

時刻T5に配線122の電位を電位VSSとする。これにより、トランジスタ114が非導通となり、画像信号S1の書き込み動作が終了する。

#### 【0083】

次に、図2(B)を用いて画像信号S2を付加する動作と、EL素子104を発光させる動作を説明する。なお、画像信号S2の電位を電位VS2とする。なお、配線125に供給される画像信号S2の電位VS2は正負の任意の電位とすることができますが、ここでは電位VSS以上の電位である場合を説明する。

30

#### 【0084】

時刻T11に配線122の電位を電位VDDとする。これにより、トランジスタ114が導通し、ノードNMの電位VN<sub>M</sub>が次の式で表される値となる。ここで、C<sub>1</sub>は容量素子113の容量値を表し、C<sub>2</sub>は容量素子103の容量値を表す。

#### 【0085】

#### 【数1】

$$V_{NM} = \frac{C_1(V_{S1} + V_{S2} - V_{ol}) + C_2 V_{S1}}{C_1 + C_2} \quad (1)$$

40

#### 【0086】

つまり、電位VN<sub>M</sub>は、容量値C<sub>1</sub>と容量値C<sub>2</sub>との比C<sub>1</sub>/C<sub>2</sub>に依存し、容量値C<sub>1</sub>の値そのもの、及び容量値C<sub>2</sub>の値そのものには依存しない。ここで、電位V<sub>o1</sub>を負電位とすると、数式1は以下のように変形できる。

#### 【0087】

#### 【数2】

$$V_{NM} = \frac{C_1(V_{S1} + V_{S2} + |V_{ol}|) + C_2 V_{S1}}{C_1 + C_2} \quad (2)$$

#### 【0088】

50

よって、 $C_1 / C_2$  が大きいほど、電位  $V_{NM}$  も大きくなる。また、容量値  $C_2$  が容量値  $C_1$  と比べて無視できるほど小さい場合は、電位  $V_{NM}$  は以下の式で表される。なお、この場合、電位  $V_{o1}'$  は電位  $V_{o1}$  と等しくなる。

#### 【0089】

##### 【数3】

$$V_{NM} = V_{s1} + V_{s2} - V_{ol} \quad (3)$$

#### 【0090】

つまり、電位  $V_{NM}$  が、電位  $V_{S1}$  と、電位  $V_{S2}$  と、の和に対応する電位となる。以上より、 $C_1 / C_2$  は大きいことが好ましい。例えば、 $C_1 / C_2$  は 1 より大きいことが好ましく、2 以上とすることがより好ましく、3 以上とすることがさらに好ましい。しかしながら、 $C_1 / C_2$  が大きすぎると、画素 10a の画素面積に対し容量値  $C_2$  が小さくなり、容量値  $C_2$  を十分に確保できなくなるため、 $C_1 / C_2$  は 10 以下とすることが好ましく、5 以下とすることがさらに好ましい。

10

#### 【0091】

なお、電位  $V_{NM}$  は、トランジスタ 112 のゲート容量等に起因する寄生容量の影響で、上記数式 1 乃至数式 3 による計算値より小さくなる場合がある。

#### 【0092】

時刻 T12 に配線 122 の電位を電位  $V_{SS}$  とする。これにより、トランジスタ 114 が非導通となり、ノード NM の電位が確定される。

20

#### 【0093】

時刻 T13 に配線 126 の電位を電位  $V_{DD}$  とすると、トランジスタ 102 が導通し、ノード NA の電位がノード NM に対応する電位となり、EL 素子 104 が発光する。

#### 【0094】

以上が画素 10a の動作例である。以上より、本発明の一態様は、配線 125 を参照電位である電位  $V_{o1}$  とした後に、画像信号 S1 をノード NM に書き込み、その後画像信号 S2 を附加して EL 素子 104 を発光させる、表示装置の動作方法であることができる。

#### 【0095】

なお、図 2 (A) に示す動作と、図 2 (B) に示す動作と、を 1 回ずつ交互に行っててもよいが、本発明の一態様はこれに限らない。例えば、トランジスタ 111 を OS トランジスタとして、ノード NM の電位を長時間保持することができるので、図 2 (A) に示す動作を 1 回行った後、図 2 (B) に示す動作を複数回行ってもよい。

30

#### 【0096】

ここで、図 2 (B) の時刻 T11 において画像信号 S2 が附加された際のノード NM の電位は、数式 1 等に示すように、電位  $V_{o1}$  に依存する。電位  $V_{o1}$  が小さいほど電位  $V_{NM}$  が大きくなるので、EL 素子 104 の発光輝度も大きくなる。つまり、本発明の一態様の表示装置は、電位  $V_{o1}$  が小さいほど高輝度の画像を表示することができる。したがって、電位  $V_{o1}$  は、例えば外光の照度に応じて変化させることが好ましい。例えば、本発明の一態様の表示装置に照度センサを設けて、外光の照度を検出することが好ましい。

40

#### 【0097】

図 3 (A1) は、晴れた昼間における屋外の様子を表し、図 3 (B1) は、夜間ににおける屋外の様子を表す。図 3 (A1)、(B1) に示す表示装置 200 は、本発明の一態様の表示装置である。

#### 【0098】

図 3 (A2) は、図 3 (A1) に示す環境におかれた表示装置 200 の、図 2 (A) に示す時刻 T1 乃至時刻 T2 における配線 125 の電位を示す。図 3 (B2) は、図 3 (B1) に示す環境におかれた表示装置 200 の、図 2 (A) に示す時刻 T1 乃至時刻 T2 における配線 125 の電位を示す。ここで、図 3 (A2) に示す電位  $V_{o1}$  を電位  $V_{o1}[1]$

50

とし、図3(B2)に示す電位 $V_{o1}$ を電位 $V_{o1}[2]$ とする。

#### 【0099】

図3(A1)に示す環境下における外光の照度は、図3(B1)に示す環境下における外光の照度より高い。よって、図3(A1)に示す環境下では、電位 $V_{o1}$ を図3(B1)に示す環境下より小さくして、より高輝度の画像を表示装置200により表示することができる。これにより、表示装置200により表示される画像の視認性を高めることができる。また、図3(B1)に示す環境下では表示装置200が表示する画像の輝度を小さくすることにより、表示装置200の消費電力を低減することができる。

#### 【0100】

なお、画像信号S1に対応する画像と、画像信号S2に対応する画像と、を異ならせてもよい。図4は、画像信号S1に対応する画像P1を、絵と文字が含まれる画像とし、画像信号S2に対応する画像P2を、文字のみを含む画像とする場合を示している。この場合、画像P1と画像P2を重ね合わせることで、文字の輝度を高めることができ、例えば文字を強調することができる。また、図2(A)、(B)に示すように、画像信号S1の電位 $V_{S1}$ を書き換える場合は、画像信号S2の電位 $V_{S2}$ を再度書き込まなければならない。一方、画像信号S2の電位 $V_{S2}$ を書き換える場合は、図2(A)に示す時刻T3においてノードNMに書き込まれた電荷が、トランジスタ111等からリークせずにノードNMに保持されている限り、画像信号S1の電位 $V_{S1}$ を書き換える必要がない。よって、図4に示す場合において、電位 $V_{S2}$ の値を調整することにより、文字の輝度を調整することができる。

10

#### 【0101】

ここで、前述のように、画像信号S1の電位 $V_{S1}$ を書き換える場合は、画像信号S2の電位 $V_{S2}$ を再度書き込まなければならないが、画像信号S2の電位 $V_{S2}$ を書き換える場合は、画像信号S1の電位 $V_{S1}$ を書き換える必要がない。よって、画像P1は、画像P2より書き換え頻度が低い画像とすることが好ましい。なお、画像P1は、絵と文字が含まれる画像に限定されず、画像P2は、文字のみを含む画像に限定されない。

20

#### 【0102】

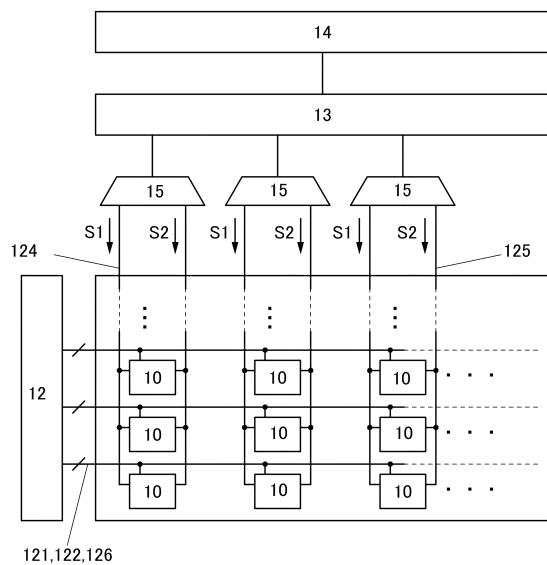

##### 〔表示装置の構成例〕

図5は、本発明の一態様の表示装置の構成例を示すブロック図である。当該表示装置は、画素10がマトリクス状に設けられた画素アレイと、ゲートドライバ12と、ソースドライバ13と、照度センサ14と、デマルチプレクサ15と、を有する。画素10としては、前述した画素10aを適用することができる。なお、デマルチプレクサ15の個数は、例えば画素アレイに設けられた画素10の列数と同数とすることができる。また、ソースドライバ13と、デマルチプレクサ15と、をまとめてソースドライバと呼んでもよい。つまり、デマルチプレクサ15は、ソースドライバに含まれるとしてもよい。

30

#### 【0103】

ゲートドライバ12及びソースドライバ13には、例えばシフトレジスタ回路を用いることができる。ゲートドライバ12は、配線121、配線122、及び配線126を介して画素10と電気的に接続される。照度センサ14は、ソースドライバ13と電気的に接続される。ソースドライバ13は、デマルチプレクサ15の入力端子と電気的に接続される。デマルチプレクサ15の第1の出力端子は、配線124を介して画素10と電気的に接続される。デマルチプレクサ15の第2の出力端子は、配線125を介して画素10と電気的に接続される。

40

#### 【0104】

ゲートドライバ12は、画素10が有するトランジスタの動作を制御するための信号を生成する機能を有する回路である。ソースドライバ13は、画像信号S1及び画像信号S2を生成する機能を有する回路である。また、ソースドライバ13は、参照電位である電位 $V_{o1}$ を生成する機能を有する回路である。なお、電位 $V_{o1}$ は、ソースドライバ以外の回路により生成してもよい。

#### 【0105】

50

デマルチプレクサ 15 は、画像信号 S 1 を配線 124 に供給し、画像信号 S 2 を配線 125 に供給する機能を有する回路である。また、ソースドライバ 13 が電位 V<sub>o1</sub> を生成する機能を有する場合、デマルチプレクサ 15 は、電位 V<sub>o1</sub> を配線 125 に供給する機能を有する。

#### 【 0106 】

照度センサ 14 は、外光の照度を検出する機能を有する回路である。前述のように、本発明の一態様の表示装置において、外光の照度に応じて電位 V<sub>o1</sub> を変化させることができる。よって、照度センサ 14 が外光の照度を検出し、検出した照度に関する情報をソースドライバ 13 に供給することにより、ソースドライバ 13 は外光の照度に応じた電位の電位 V<sub>o1</sub> を生成することができる。なお、ソースドライバ 13 が電位 V<sub>o1</sub> を生成する機能を有しない場合は、照度センサ 14 とソースドライバ 13 が電気的に接続されていない構成とすることができる。10

#### 【 0107 】

なお、照度センサ 14 は光電変換素子を有する構成とすることができます。光電変換素子として、例えばシリコンを光電変換層とする光電変換素子、セレン系材料を光電変換層とする光電変換素子を用いることができる。

#### 【 0108 】

セレン系材料を用いた光電変換素子は、可視光に対する外部量子効率が高いという特性を有する。当該光電変換素子では、アバランシェ増倍を利用することにより、入射される光量に対する電子の增幅を大きくすることができる。また、セレン系材料は光吸収係数が高いため、光電変換層を薄膜で作製できる等の生産上の利点を有する。セレン系材料の薄膜は、真空蒸着法又はスパッタリング法等を用いて形成することができる。20

#### 【 0109 】

セレン系材料としては、単結晶セレン及び多結晶セレン等の結晶性セレン、非晶質セレン、銅とインジウムとセレンとの化合物 ( CIS ) 、又は、銅とインジウムとガリウムとセレンとの化合物 ( CIGS ) 等を用いることができる。

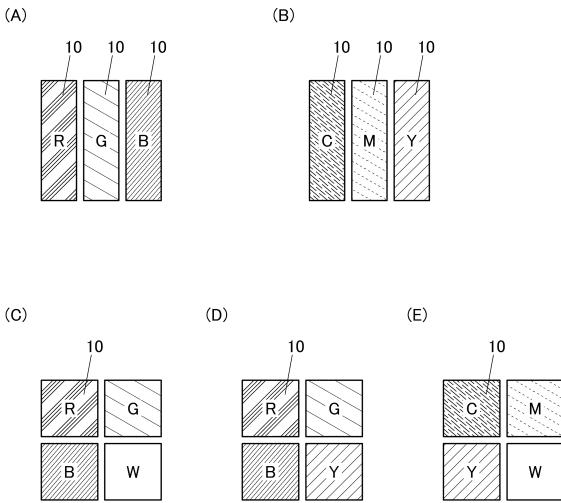

#### 【 0110 】

図 6 ( A ) 乃至 ( E ) は、本発明の一態様の表示装置に設けられる画素 10 が呈する色について説明する図である。図 6 ( A ) に示すように、赤色 ( R ) を呈する画素 10 、緑色 ( G ) を呈する画素 10 、及び青色 ( B ) を呈する画素 10 を本発明の一態様の表示装置に設けることができる。または、図 6 ( B ) に示すように、シアン ( C ) を呈する画素 10 、マゼンタ ( M ) を呈する画素 10 、及び黄色 ( Y ) を呈する画素 10 が本発明の一態様の表示装置に設けられていてもよい。30

#### 【 0111 】

または、図 6 ( C ) に示すように、赤色 ( R ) を呈する画素 10 、緑色 ( G ) を呈する画素 10 、青色 ( B ) を呈する画素 10 、及び白色 ( W ) を呈する画素 10 が本発明の一態様の表示装置に設けられていてもよい。または、図 6 ( D ) に示すように、赤色 ( R ) を呈する画素 10 、緑色 ( G ) を呈する画素 10 、青色 ( B ) を呈する画素 10 、及び黄色 ( Y ) を呈する画素 10 が本発明の一態様の表示装置に設けられていてもよい。または、図 6 ( E ) に示すように、シアン ( C ) を呈する画素 10 、マゼンタ ( M ) を呈する画素 10 、黄色 ( Y ) を呈する画素 10 、及び白色 ( W ) を呈する画素 10 が本発明の一態様の表示装置に設けられていてもよい。40

#### 【 0112 】

図 6 ( C ) 、 ( E ) に示すように、白色を呈する画素 10 を本発明の一態様の表示装置に設けることで、表示される画像の輝度を高めることができる。また、図 6 ( D ) 等に示すように、画素 10 が呈する色の種類を増やすことで、中間色の再現性を高めることができるために、表示品位を高めることができる。

#### 【 0113 】

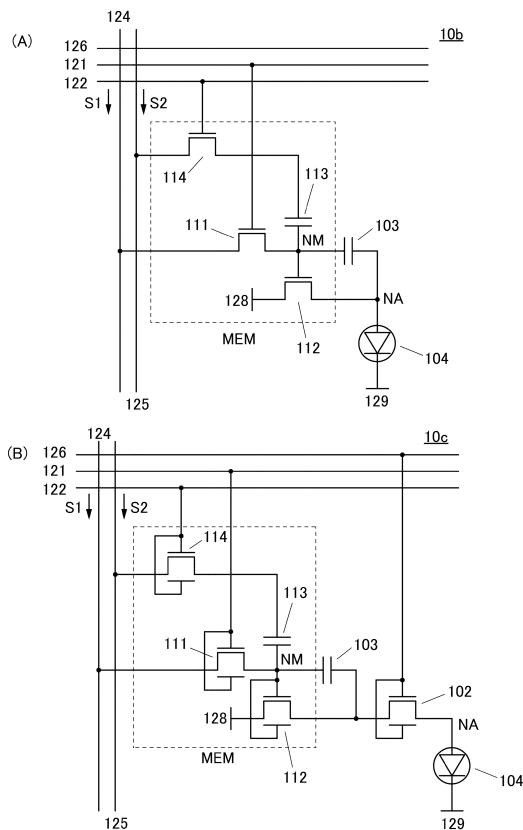

##### 〔 画素回路の変形例 〕

次に、画素 10 の変形例について説明する。画素 10 は、図 7 ( A ) に示す画素 10 b の

構成とすることもできる。画素 10b は、画素 10a からトランジスタ 102 を省いた構成である。

#### 【0114】

前述したように、トランジスタ 102 はノード NM に書き込む信号の電位がトランジスタ 112 のしきい値電圧 ( $V_{th}$ ) 以上である場合に起こる不具合を解消するために設けられる。ただし、ノード NM に書き込まれる信号が  $V_{th}$  より低い値に限定されていればトランジスタ 102 を省くことができる。

#### 【0115】

また、画素 10 は、図 7 (B) に示す画素 10c の構成とすることもできる。画素 10c は、それぞれのトランジスタにバックゲートを設けた構成を有する。当該バックゲートはフロントゲートと電気的に接続されており、オン電流を高める効果を有する。また、バックゲートにフロントゲートと異なる電位を供給できる構成としてもよい。当該構成とすることで、トランジスタのしきい値電圧を制御することができる。なお、図 7 (B) においては、全てのトランジスタにバックゲートを設けた構成を図示しているが、バックゲートが設けられないトランジスタを有していてもよい。また、トランジスタがバックゲートを有する構成は、本実施の形態における他の画素回路にも有効である。

10

#### 【0116】

また、画素 10 は、図 8 に示す画素 10d の構成とすることもできる。画素 10d では、画素 10a にトランジスタ 105 及び配線 130 を付加した構成を有する。

20

#### 【0117】

トランジスタ 105 のソース又はドレインの一方は、トランジスタ 112 のソース又はドレインの一方と電気的に接続される。トランジスタ 105 のソース又はドレインの他方は、配線 130 と電気的に接続される。トランジスタ 105 のゲートは、配線 122 と電気的に接続される。

#### 【0118】

配線 130 は、電源線としての機能を有する。画像信号 S1 の画素 10d への書き込みの最中、及び画像信号 S2 の画素 10d への書き込みの最中に配線 130 からトランジスタ 105 を介して容量素子 103 の他方の電極に特定の電位、例えば低電位を供給することにより、画像信号の書き込みを安定して行うことができる。

30

#### 【0119】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することが可能である。

#### 【0120】

##### (実施の形態 2)

本実施の形態では、EL 素子を用いた表示装置の構成例について説明する。

#### 【0121】

図 9 (A) において、第 1 の基板 4001 上に設けられた表示部 215 を囲むようにして、シール材 4005 が設けられ、表示部 215 がシール材 4005 及び第 2 の基板 4006 によって封止されている。

40

#### 【0122】

表示部 215 には、実施の形態 1 に示した画素を有する画素アレイが設けられる。

#### 【0123】

図 9 (A) では、走査線駆動回路 221、信号線駆動回路 231、信号線駆動回路 232、及び共通線駆動回路 241 は、それぞれがプリント基板 4041 上に設けられた集積回路 4042 を複数有する。集積回路 4042 は、単結晶半導体又は多結晶半導体で形成されている。信号線駆動回路 231 及び信号線駆動回路 232 は、実施の形態 1 に示したソースドライバの機能を有する。走査線駆動回路 221 は、実施の形態 1 に示したゲートドライバの機能を有する。共通線駆動回路 241 は、実施の形態 1 に示した共通配線に規定の電位を供給する機能を有する。

50

#### 【0124】

走査線駆動回路 221、共通線駆動回路 241、信号線駆動回路 231、及び信号線駆動回路 232に与えられる各種信号及び電位は、FPC (Flexible printed circuit) 4018を介して供給される。

#### 【0125】

走査線駆動回路 221 及び共通線駆動回路 241 が有する集積回路 4042 は、表示部 215 に選択信号を供給する機能を有する。信号線駆動回路 231 及び信号線駆動回路 232 が有する集積回路 4042 は、表示部 215 に画像信号を供給する機能を有する。集積回路 4042 は、第 1 の基板 4001 上のシール材 4005 によって囲まれている領域とは異なる領域に実装されている。

#### 【0126】

なお、集積回路 4042 の接続方法は、特に限定されるものではなく、ワイヤボンディング法、COG (Chip On Glass) 法、TCP (Tape Carrier Package) 法、COF (Chip On Film) 法等を用いることができる。

#### 【0127】

図 9 (B) は、信号線駆動回路 231 及び信号線駆動回路 232 に含まれる集積回路 4042 を COG 法により実装する例を示している。また、駆動回路の一部又は全体を表示部 215 と同じ基板上に一体形成して、システムオンパネルを形成することができる。

#### 【0128】

図 9 (B) では、走査線駆動回路 221 及び共通線駆動回路 241 を、表示部 215 と同じ基板上に形成する例を示している。駆動回路を表示部 215 内の画素回路と同時に形成することで、部品点数を削減することができる。よって、生産性を高めることができる。

#### 【0129】

また、図 9 (B) では、第 1 の基板 4001 上に設けられた表示部 215 と、走査線駆動回路 221 及び共通線駆動回路 241 と、を囲むようにして、シール材 4005 が設けられている。また表示部 215、走査線駆動回路 221、及び共通線駆動回路 241 の上に第 2 の基板 4006 が設けられている。よって、表示部 215、走査線駆動回路 221、及び共通線駆動回路 241 は、第 1 の基板 4001 とシール材 4005 と第 2 の基板 4006 とによって、表示素子と共に封止されている。

#### 【0130】

また、図 9 (B) では、信号線駆動回路 231 及び信号線駆動回路 232 を別途形成し、第 1 の基板 4001 に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装してもよいし、信号線駆動回路の一部又は走査線駆動回路の一部を別途形成して実装してもよい。

#### 【0131】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む IC 等を実装した状態にあるモジュールとを含む場合がある。

#### 【0132】

また、第 1 の基板上に設けられた表示部及び走査線駆動回路は、トランジスタを複数有している。当該トランジスタとして、例えば以降に示すトランジスタを適用することができる。

#### 【0133】

周辺駆動回路が有するトランジスタと、表示部の画素回路が有するトランジスタの構造は同じであってもよく、異なっていてもよい。周辺駆動回路が有するトランジスタは、全て同じ構造であってもよく、2種類以上の構造が組み合わせて用いられていてもよい。同様に、画素回路が有するトランジスタは、全て同じ構造であってもよく、2種類以上の構造が組み合わせて用いられていてもよい。

#### 【0134】

また、第 2 の基板 4006 上には入力装置 4200 を設けることができる。図 9 に示す表示装置に入力装置 4200 を設けた構成はタッチパネルとして機能させることができる。

#### 【0135】

10

20

30

40

50

本発明の一態様のタッチパネルが有する検知素子（センサ素子ともいう）に限定は無い。指やスタイルス等の被検知体の、近接又は接触を検知することのできる様々なセンサを、検知素子として適用することができる。

**【0136】**

センサの方式としては、例えば、静電容量方式、抵抗膜方式、表面弾性波方式、赤外線方式、光学方式、感圧方式等様々な方式を用いることができる。

**【0137】**

本実施の形態では、静電容量方式の検知素子を有するタッチパネルを例に挙げて説明する。

**【0138】**

静電容量方式としては、表面型静電容量方式、投影型静電容量方式等がある。また、投影型静電容量方式としては、自己容量方式、相互容量方式等がある。相互容量方式を用いると、同時多点検知が可能となるため好ましい。

10

**【0139】**

本発明の一態様のタッチパネルは、別々に作製された表示装置と検知素子とを貼り合わせる構成、表示素子を支持する基板及び対向基板の、一方又は双方に検知素子を構成する電極等を設ける構成等、様々な構成を適用することができる。

**【0140】**

図10(A)、(B)に、タッチパネルの一例を示す。図10(A)は、タッチパネル4210の斜視図である。図10(B)は、入力装置4200の斜視概略図である。なお、明瞭化のため、代表的な構成要素のみを示している。

20

**【0141】**

タッチパネル4210は、別々に作製された表示装置と検知素子とを貼り合わせた構成である。

**【0142】**

タッチパネル4210は、入力装置4200と、表示装置とを有し、これらが重ねて設けられている。

**【0143】**

入力装置4200は、基板4263、電極4227、電極4228、複数の配線4237、複数の配線4238、及び複数の配線4239を有する。例えば、電極4227は配線4237又は配線4239と電気的に接続することができる。また、電極4228は配線4238と電気的に接続することができる。FPC4272は、複数の配線4237、複数の配線4238、及び複数の配線4239の各々と電気的に接続する。FPC4272にはIC4273を設けることができる。

30

**【0144】**

又は、表示装置の第1の基板4001と第2の基板4006との間にタッチセンサを設けてもよい。第1の基板4001と第2の基板4006との間にタッチセンサを設ける場合は、静電容量方式のタッチセンサのほか、光電変換素子を用いた光学式のタッチセンサを適用してもよい。

**【0145】**

図11(A)は、図9(B)中でN1-N2の鎖線で示した部位の断面図であり、カラーフィルタ方式が適用されたトップエミッショングラフ構造の発光表示装置の構成例を示す。図11(A)に示す表示装置は電極4015を有しており、電極4015はFPC4018が有する端子と異方性導電層4019を介して、電気的に接続されている。図11(A)では、電極4015は、絶縁層4112、絶縁層4111、及び絶縁層4110に形成された開口において配線4014と電気的に接続されている。

40

**【0146】**

電極4015は、第1の電極層4030と同じ導電層から形成され、配線4014は、トランジスタ4010、及びトランジスタ4011のソース電極及びドレイン電極と同じ導電層で形成されている。

**【0147】**

50

また、第1の基板4001上に設けられた表示部215と走査線駆動回路221は、トランジスタを複数有しており、図11(A)では、表示部215に含まれるトランジスタ4010、及び走査線駆動回路221に含まれるトランジスタ4011を例示している。なお、図11(A)では、トランジスタ4010及びトランジスタ4011としてボトムゲート型のトランジスタを例示しているが、トップゲート型のトランジスタであってもよい。

#### 【0148】

図11(A)では、トランジスタ4010及びトランジスタ4011上に絶縁層4112が設けられている。また、絶縁層4112上に隔壁4510が形成されている。

#### 【0149】

また、トランジスタ4010及びトランジスタ4011は、絶縁層4102上に設けられている。また、トランジスタ4010及びトランジスタ4011は、絶縁層4111上に形成された電極4017を有する。電極4017はバックゲート電極として機能することができる。

10

#### 【0150】

また、図11(A)に示す表示装置は、容量素子4020を有する。容量素子4020は、トランジスタ4010のゲート電極と同じ工程で形成された電極4021と、トランジスタ4010のソース電極及びドレイン電極と同じ工程で形成された電極と、を有する。それぞれの電極は、絶縁層4103を介して重なっている。

#### 【0151】

一般に、表示装置の画素部に設けられる容量素子の容量は、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間電荷を保持できるように設定される。容量素子の容量は、トランジスタのオフ電流等を考慮して設定すればよい。

20

#### 【0152】

表示部215に設けられたトランジスタ4010は、表示素子と電気的に接続する。

#### 【0153】

また、図11(A)に示す表示装置は、絶縁層4111と絶縁層4103として、不純物元素を透過しにくい絶縁層を用いる。絶縁層4111と絶縁層4103でトランジスタの半導体層を挟むことで、外部からの不純物の浸入を防ぐことができる。

#### 【0154】

表示装置に含まれる表示素子として、エレクトロルミネッセンスを利用する発光素子(EL素子)を適用することができる。EL素子は、一対の電極の間に発光性の化合物を含む層(「EL層」ともいう。)を有する。一対の電極間に、EL素子のしきい値電圧よりも大きい電位差を生じさせると、EL層に陽極側から正孔が注入され、陰極側から電子が注入される。注入された電子と正孔はEL層において再結合し、EL層に含まれる発光性の化合物が発光する。

30

#### 【0155】

また、EL素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

#### 【0156】

有機EL素子は、電圧を印加することにより、一方の電極から電子、他方の電極から正孔がそれぞれEL層に注入される。そして、それらキャリア(電子及び正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

40

#### 【0157】

なお、EL層は、発光性の化合物以外に、正孔注入性の高い物質、正孔輸送性の高い物質、正孔ブロック材料、電子輸送性の高い物質、電子注入性の高い物質、又はバイポーラ性の物質(電子輸送性及び正孔輸送性が高い物質)等を有していてもよい。

#### 【0158】

EL層は、蒸着法(真空蒸着法を含む)、転写法、印刷法、インクジェット法、塗布法等

50

の方法で形成することができる。

**【 0 1 5 9 】**

無機 E L 素子は、その素子構成により、分散型無機 E L 素子と薄膜型無機 E L 素子とに分類される。分散型無機 E L 素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー - アクセプター再結合型発光である。薄膜型無機 E L 素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機 E L 素子を用いて説明する。

**【 0 1 6 0 】**

発光素子は発光を取り出すために少なくとも一対の電極の一方が透明であればよい。そして、基板上にトランジスタ及び発光素子を形成し、当該基板とは逆側の面から発光を取り出す上面射出（トップエミッション）構造や、基板側の面から発光を取り出す下面射出（ボトムエミッション）構造や、両面から発光を取り出す両面射出（デュアルエミッション）構造の発光素子があり、どの射出構造の発光素子も適用することができる。

10

**【 0 1 6 1 】**

図 11 ( A ) は、表示素子として発光素子を用いた発光表示装置（「 E L 表示装置」ともいう。）の一例である。表示素子である発光素子 4513 は、表示部 215 に設けられたトランジスタ 4010 と電気的に接続している。発光素子 4513 は、白色光を発する素子とすることができます。なお発光素子 4513 の構成は、第 1 の電極層 4030 、発光層 4511 、第 2 の電極層 4031 の積層構造であるが、この構成に限定されない。発光素子 4513 から取り出す光の方向等に合わせて、発光素子 4513 の構成は適宜変えることができる。

20

**【 0 1 6 2 】**

隔壁 4510 は、有機絶縁材料、又は無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第 1 の電極層 4030 上に側面が連続した曲率を持った傾斜面となる開口部を有するように形成することが好ましい。

**【 0 1 6 3 】**

発光層 4511 は、単数の層で構成されていても、複数の層が積層されるように構成されてもよい。

30

**【 0 1 6 4 】**

なお、発光層 4511 は、量子ドット等の無機化合物を有していてもよい。例えば、量子ドットを発光層に用いることで、発光材料として機能させることもできる。

**【 0 1 6 5 】**

発光素子 4513 に酸素、水素、水分、二酸化炭素等が侵入しないように、第 2 の電極層 4031 上に保護層を形成してもよい。保護層としては、窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、DLC (Diamond Like Carbon) 等を形成することができる。また、第 1 の基板 4001 、第 2 の基板 4006 、及びシール材 4005 によって封止された空間には充填材 4514 が設けられ密封されている。このように、外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルム等）やカバー材でパッケージング（封入）することが好ましい。

40

**【 0 1 6 6 】**

充填材 4514 としては窒素やアルゴン等の不活性な気体の他に、紫外線硬化樹脂又は熱硬化樹脂を用いることができ、PVC (ポリビニルクロライド) 、アクリル系樹脂、ポリイミド、エポキシ系樹脂、シリコーン系樹脂、PVB (ポリビニルブチラル) 、又はEVA (エチレンビニルアセテート) 等を用いることができる。また、充填材 4514 に乾燥剤が含まれていてもよい。

**【 0 1 6 7 】**

シール材 4005 には、ガラスフリット等のガラス材料や、二液混合型の樹脂等の常温で

50

硬化する硬化樹脂、光硬化性の樹脂、熱硬化性の樹脂等の樹脂材料を用いることができる。また、シール材 4005 に乾燥剤が含まれていてもよい。

#### 【0168】

また、図 11 (A) に示す表示装置は着色層 4301 及び遮光層 4302 を有する。着色層 4301 は、充填材 4514 を介して発光素子 4513 と重なる領域を有し、遮光層 4302 は、充填材 4514 を介して隔壁 4510 と重なる領域を有する。

#### 【0169】

着色層 4301 は、特定の波長域の光を透過する有色層である。例えば、赤色、緑色、青色、シアン、マゼンタ、又は黄色の光を透過するカラーフィルタ等を用いることができる。着色層 4301 に用いることのできる材料としては、金属材料、樹脂材料、顔料、又は染料が含まれた樹脂材料等が挙げられる。

#### 【0170】

着色層 4301 は、隣接する遮光層 4302 の間に設けられている。遮光層 4302 は発光素子 4513 から発せられる光を遮光し、隣接する発光素子 4513 間における混色を抑制する機能を有する。ここで、着色層 4301 の端部を、遮光層 4302 と重なるように設けることにより、光漏れを抑制することができる。遮光層 4302 としては、発光素子 4513 からの発光を遮る材料を用いることができ、例えば、金属材料、又は、顔料若しくは染料を含む樹脂材料等を用いてブラックマトリクスを形成することができる。

#### 【0171】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板（楕円偏光板を含む）、位相差板（ $\frac{1}{4}$  板、 $\frac{1}{2}$  板）を適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

#### 【0172】

また、発光素子をマイクロキャビティ構造とすることで、色純度の高い光を取り出すことができる。

#### 【0173】

表示素子に電圧を印加する第 1 の電極層（画素電極層ともいう）及び第 2 の電極層（共通電極層、対向電極層等ともいう）においては、取り出す光の方向、電極層が設けられる場所、及び電極層のパターン構造によって透光性、反射性を選択すればよい。

#### 【0174】

第 1 の電極層 4030、及び第 2 の電極層 4031 は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、インジウム錫酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物等の透光性を有する導電性材料を用いることができる。

#### 【0175】

また、第 1 の電極層 4030、第 2 の電極層 4031 はタンゲステン (W)、モリブデン (Mo)、ジルコニウム (Zr)、ハフニウム (Hf)、バナジウム (V)、ニオブ (Nb)、タンタル (Ta)、クロム (Cr)、コバルト (Co)、ニッケル (Ni)、チタン (Ti)、白金 (Pt)、アルミニウム (Al)、銅 (Cu)、銀 (Ag) 等の金属、若しくはその合金、又はその金属窒化物から一種以上を用いて形成することができる。

#### 【0176】

また、第 1 の電極層 4030、第 2 の電極層 4031 として、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆる 電子共役系導電性高分子を用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、又は、アニリン、ピロール及びチオフェンの 2 種以上からなる共重合体若しくはその誘導体等があげられる。

#### 【0177】

10

20

30

40

50

また、トランジスタは静電気等により破壊されやすいため、駆動回路保護用の保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

**【 0 1 7 8 】**

図11(A)に示すように、発光色が白色の発光素子4513と着色層を組み合わせるカラーフィルタ方式を適用することにより、本発明の一態様の表示装置の生産性を高めることができる。

**【 0 1 7 9 】**

図11(B)は、図9(B)中でN1-N2の鎖線で示した部位の断面図であり、カラーフィルタを有さず、塗り分け方式が適用されている点が図11(A)に示す構成の表示装置と異なる。塗り分け方式の表示装置では、発光素子4513の発光色は発光層4511を構成する材料によって、白、赤、緑、青、シアン、マゼンタ、又は黄等とすることができる。

10

**【 0 1 8 0 】**

図11(B)に示すように塗り分け方式を適用することにより、色純度の高い光を取り出すことができる。なお、塗り分け方式の表示装置であってもカラーフィルタを設けることで、さらに色純度の高い光を取り出すことができる。

**【 0 1 8 1 】**

なお、本発明の一態様の表示装置は、色変換方式又は量子ドット方式等を適用してもよい。

**【 0 1 8 2 】**

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することが可能である。

20

**【 0 1 8 3 】**

(実施の形態3)

本実施の形態では、上記実施の形態に示した各トランジスタに置き換えて用いることできるトランジスタの一例について、図面を用いて説明する。

**【 0 1 8 4 】**

本発明の一態様の表示装置は、ボトムゲート型のトランジスタ、及びトップゲート型トランジスタ等の様々な形態のトランジスタを用いて作製することができる。よって、既存の製造ラインに合わせて、使用する半導体層の材料やトランジスタ構造を容易に置き換えることができる。

30

**【 0 1 8 5 】**

[ボトムゲート型トランジスタ]

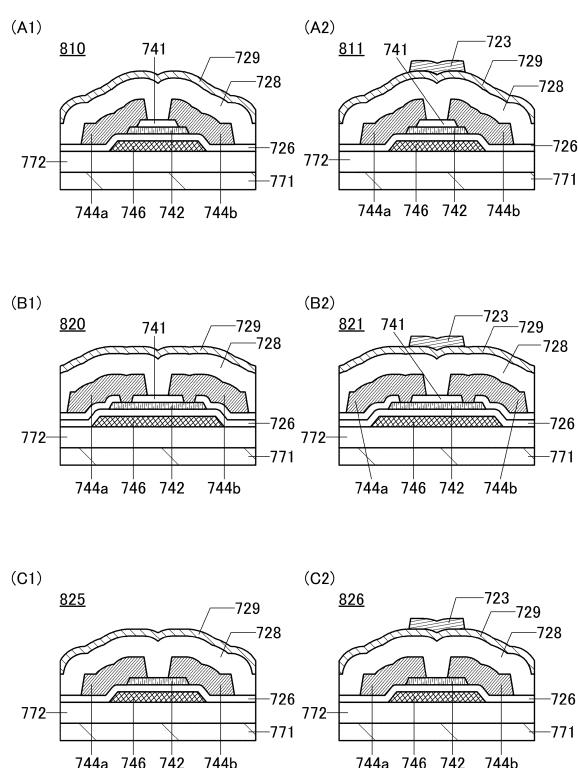

図12(A1)は、ボトムゲート型のトランジスタの一種であるチャネル保護型のトランジスタ810の断面図である。図12(A1)において、トランジスタ810は基板771上に形成されている。また、トランジスタ810は、基板771上に絶縁層772を介して電極746を有する。また、電極746上に絶縁層726を介して半導体層742を有する。電極746はゲート電極としての機能を有する。絶縁層726はゲート絶縁層としての機能を有する。

**【 0 1 8 6 】**

また、半導体層742のチャネル形成領域上に絶縁層741を有する。また、半導体層742の一部と接して、絶縁層726上に電極744a及び電極744bを有する。電極744aは、ソース電極又はドレイン電極の一方としての機能を有する。電極744bは、ソース電極又はドレイン電極の他方としての機能を有する。電極744aの一部、及び電極744bの一部は、絶縁層741上に形成される。

40

**【 0 1 8 7 】**

絶縁層741は、チャネル保護層としての機能を有する。チャネル形成領域上に絶縁層741を設けることで、電極744a及び電極744bの形成時に生じる半導体層742の露出を防ぐことができる。よって、電極744a及び電極744bの形成時に、半導体層742のチャネル形成領域がエッティングされることを防ぐことができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現することができる。

50

**【 0 1 8 8 】**

また、トランジスタ 810 は、電極 744a、電極 744b、及び絶縁層 741 上に絶縁層 728 を有し、絶縁層 728 の上に絶縁層 729 を有する。

**【 0 1 8 9 】**

半導体層 742 に酸化物半導体を用いる場合、電極 744a 及び電極 744b の、少なくとも半導体層 742 と接する部分に、半導体層 742 の一部から酸素を奪い、酸素欠損を生じさせることができた材料を用いることが好ましい。半導体層 742 中の酸素欠損が生じた領域はキャリア濃度が増加し、当該領域は n 型化し、n 型領域 (n<sup>+</sup> 層) となる。したがって、当該領域はソース領域又はドレイン領域として機能することができる。半導体層 742 に酸化物半導体を用いる場合、半導体層 742 から酸素を奪い、酸素欠損を生じさせることができた材料の一例として、タンゲステン、チタン等を挙げることができる。10

**【 0 1 9 0 】**

半導体層 742 にソース領域及びドレイン領域が形成されることにより、電極 744a 及び電極 744b と、半導体層 742 との接触抵抗を低減することができる。よって、電界効果移動度や、しきい値電圧等の、トランジスタの電気特性を良好なものとすることができる。

**【 0 1 9 1 】**

半導体層 742 にシリコン等の半導体を用いる場合は、半導体層 742 と電極 744a の間、及び半導体層 742 と電極 744b の間に、n 型半導体又は p 型半導体として機能する層を設けることが好ましい。n 型半導体又は p 型半導体として機能する層は、トランジスタのソース領域又はドレイン領域として機能することができる。20

**【 0 1 9 2 】**

絶縁層 729 は、外部からのトランジスタへの不純物の拡散を防ぐ、又は低減する機能を有する材料を用いて形成することができた。なお、必要に応じて絶縁層 729 を省略することもできる。

**【 0 1 9 3 】**

図 12 (A2) に示すトランジスタ 811 は、絶縁層 729 上にバックゲート電極としての機能を有する電極 723 を有する点が、トランジスタ 810 と異なる。電極 723 は、電極 746 と同様の材料及び方法で形成することができる。

**【 0 1 9 4 】**

一般に、バックゲート電極は導電層で形成され、ゲート電極とバックゲート電極で半導体層のチャネル形成領域を挟むように配置される。よって、バックゲート電極は、ゲート電極と同様に機能させることができた。バックゲート電極の電位は、ゲート電極と同電位としてもよいし、接地電位 (GND 電位) や、任意の電位としてもよい。また、バックゲート電極の電位をゲート電極と連動させず独立して変化させることで、トランジスタのしきい値電圧を変化させることができた。30

**【 0 1 9 5 】**

電極 746 及び電極 723 は、どちらもゲート電極として機能することができる。よって、絶縁層 726、絶縁層 741、絶縁層 728、及び絶縁層 729 は、それぞれがゲート絶縁層として機能することができた。なお、電極 723 は、絶縁層 728 と絶縁層 729 の間に設けてもよい。40

**【 0 1 9 6 】**

なお、電極 746 又は電極 723 の一方を、「ゲート電極」と呼ぶ場合、他方を「バックゲート電極」と呼ぶ。例えば、トランジスタ 811 において、電極 723 を「ゲート電極」と呼ぶ場合、電極 746 を「バックゲート電極」と呼ぶ。また、電極 723 を「ゲート電極」として用いる場合は、トランジスタ 811 をトップゲート型のトランジスタの一種と考えることができた。また、電極 746 及び電極 723 のどちらか一方を、「第 1 のゲート電極」と呼び、他方を「第 2 のゲート電極」と呼ぶ場合がある。

**【 0 1 9 7 】**

半導体層 742 を挟んで電極 746 及び電極 723 を設けることで、更には、電極 746

10

20

30

40

50

及び電極 723 を同電位とすることで、半導体層 742 においてキャリアの流れる領域が膜厚方向においてより大きくなるため、キャリアの移動量が増加する。この結果、トランジスタ 811 のオン電流が高くなると共に、電界効果移動度が高くなる。

#### 【0198】

したがって、トランジスタ 811 は、占有面積に対して高いオン電流を有するトランジスタである。すなわち、求められるオン電流に対して、トランジスタ 811 の占有面積を小さくすることができる。本発明の一態様によれば、トランジスタの占有面積を小さくすることができる。

#### 【0199】

また、ゲート電極とバックゲート電極は導電層で形成されるため、トランジスタの外部で生じる電界が、チャネルが形成される半導体層に作用しないようにする機能（特に静電気等に対する電界遮蔽機能）を有する。なお、バックゲート電極を半導体層よりも大きく形成し、バックゲート電極で半導体層を覆うことで、電界遮蔽機能を高めることができる。

10

#### 【0200】

また、バックゲート電極を、遮光性を有する導電膜で形成することで、バックゲート電極側から半導体層に光が入射することを防ぐことができる。よって、半導体層の光劣化を防ぎ、トランジスタのしきい値電圧がシフトする等の電気特性の劣化を防ぐことができる。

#### 【0201】

本発明の一態様によれば、信頼性の高いトランジスタを実現することができる。また、信頼性の高い表示装置等を実現することができる。

20

#### 【0202】

図 12 (B1) に、ボトムゲート型のトランジスタの 1 つであるチャネル保護型のトランジスタ 820 の断面図を示す。トランジスタ 820 は、トランジスタ 810 とほぼ同様の構造を有しているが、絶縁層 741 が半導体層 742 の端部を覆っている点が異なる。また、半導体層 742 と重なる絶縁層 741 の一部を選択的に除去して形成した開口部において、半導体層 742 と電極 744a が電気的に接続している。また、半導体層 742 と重なる絶縁層 741 の一部を選択的に除去して形成した他の開口部において、半導体層 742 と電極 744b が電気的に接続している。絶縁層 741 の、チャネル形成領域と重なる領域は、チャネル保護層としての機能を有する。

#### 【0203】

図 12 (B2) に示すトランジスタ 821 は、絶縁層 729 上にバックゲート電極としての機能を有する電極 723 を有する点が、トランジスタ 820 と異なる。

30

#### 【0204】

絶縁層 729 を設けることで、電極 744a 及び電極 744b の形成時に生じる半導体層 742 の露出を防ぐことができる。よって、電極 744a 及び電極 744b の形成時に半導体層 742 の薄膜化を防ぐことができる。

#### 【0205】

また、トランジスタ 820 及びトランジスタ 821 は、トランジスタ 810 及びトランジスタ 811 よりも、電極 744a と電極 746 の間の距離、及び電極 744b と電極 746 の間の距離が長くなる。よって、電極 744a と電極 746 の間に生じる寄生容量を小さくすることができる。また、電極 744b と電極 746 の間に生じる寄生容量を小さくすることができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現できる。

40

#### 【0206】

図 12 (C1) に示すトランジスタ 825 は、ボトムゲート型のトランジスタの 1 つであるチャネルエッチング型のトランジスタである。トランジスタ 825 は、絶縁層 741 を用いずに電極 744a 及び電極 744b を形成する。このため、電極 744a 及び電極 744b の形成時に露出する半導体層 742 の一部がエッチングされる場合がある。一方、絶縁層 741 を設けないため、トランジスタの生産性を高めることができる。

#### 【0207】

50

図12(C2)に示すトランジスタ826は、絶縁層729上にバックゲート電極としての機能を有する電極723を有する点が、トランジスタ825と異なる。

#### 【0208】

##### 〔トップゲート型トランジスタ〕

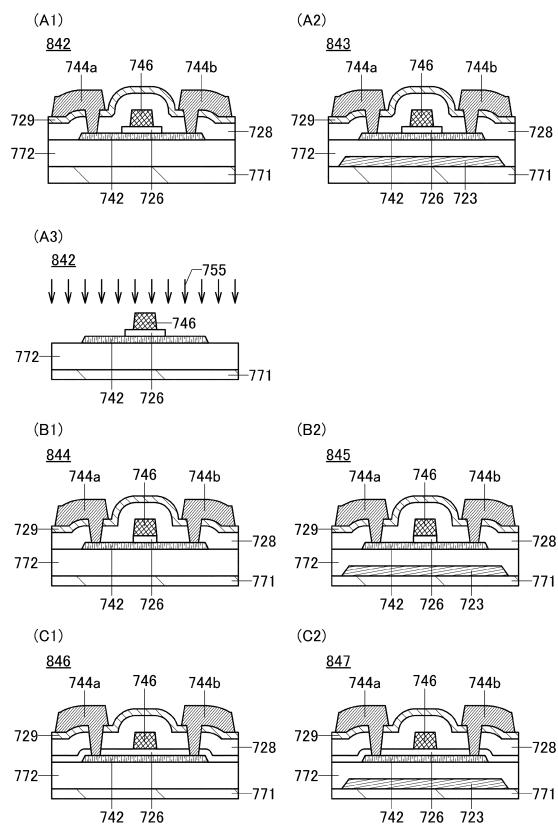

図13(A1)に例示するトランジスタ842は、トップゲート型のトランジスタの1つである。トランジスタ842は、絶縁層729を形成した後に電極744a及び電極744bを形成する。電極744a及び電極744bは、絶縁層728及び絶縁層729に形成した開口部において半導体層742と電気的に接続する。

#### 【0209】

また、電極746と重ならない絶縁層726の一部を除去し、図13(A3)に示すように電極746と残りの絶縁層726をマスクとして用いて不純物755を半導体層742に導入することで、半導体層742中に自己整合(セルフアライメント)的に不純物領域を形成することができる。トランジスタ842は、絶縁層726が電極746の端部を越えて延伸する領域を有する。半導体層742の絶縁層726を介して不純物755が導入された領域の不純物濃度は、絶縁層726を介さずに不純物755が導入された領域よりも小さくなる。半導体層742は、電極746と重ならない領域にLDD(Light1y Doped Drain)領域が形成される。

10

#### 【0210】

図13(A2)に示すトランジスタ843は、基板711の上に形成された電極723を有する点がトランジスタ842と異なる。電極723は、絶縁層772を介して半導体層742と重なる領域を有する。電極723は、バックゲート電極として機能することができる。

20

#### 【0211】

また、図13(B1)に示すトランジスタ844、及び図13(B2)に示すトランジスタ845のように、電極746と重ならない領域の絶縁層726を全て除去してもよい。また、図13(C1)に示すトランジスタ846、及び図13(C2)に示すトランジスタ847のように、絶縁層726を残してもよい。

#### 【0212】

トランジスタ843乃至トランジスタ847も、電極746を形成した後に、電極746をマスクとして用いて不純物755を半導体層742に導入することで、半導体層742中に自己整合的に不純物領域を形成することができる。本発明の一態様によれば、電気特性の良好なトランジスタを実現することができる。

30

#### 【0213】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

#### 【0214】

##### (実施の形態4)

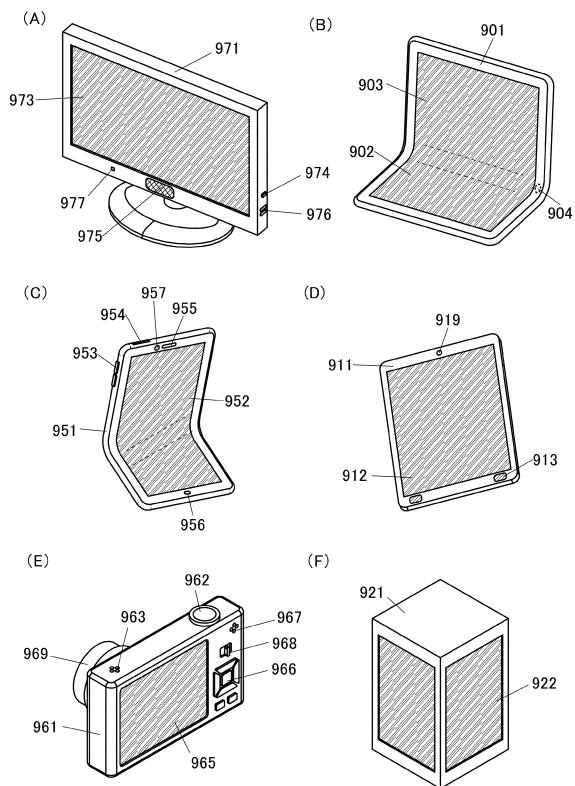

本発明の一態様に係る表示装置を用いることができる電子機器として、表示機器、パソコン用コンピュータ、記録媒体を備えた画像記憶装置又は画像再生装置、携帯電話、携帯型を含むゲーム機、携帯データ端末、電子書籍端末、ビデオカメラ又はデジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、デジタルオーディオプレイヤー等)、複写機、ファクシミリ、プリンタ、プリント複合機、現金自動預け入れ払い機(ATM)、自動販売機等が挙げられる。これら電子機器の具体例を図14に示す。

40

#### 【0215】

図14(A)はテレビであり、筐体971、表示部973、操作キー974、スピーカ975、通信用接続端子976、光センサ977等を有する。表示部973にタッチセンサを設け、入力操作を行うこともできる。表示部973に本発明の一態様の表示装置を用いることで、表示部973に高輝度の画像を表示することができ、ダイナミックレンジを高めることができる。

50

**【 0 2 1 6 】**

図14(B)は情報処理端末であり、筐体901、表示部902、表示部903、センサ904等を有する。表示部902及び表示部903は一つの表示パネルから成り、可撓性を有する。また、筐体901も可撓性を有し、図示するように折り曲げて使用することができるほか、タブレット端末のように平板状にして使用することもできる。センサ904は筐体901の形状を感知することができ、例えば、筐体901が曲げられたときに表示部902及び表示部903の表示を切り替えることができる。表示部902及び表示部903に本発明の一態様の表示装置を用いることで、表示部902及び表示部903に高輝度の画像を表示することができ、ダイナミックレンジを高めることができる。

**【 0 2 1 7 】**

10

図14(C)は携帯電話機の一例であり、筐体951、表示部952、操作ボタン953、外部接続ポート954、スピーカ955、マイク956、カメラ957等を有する。当該携帯電話機は、表示部952にタッチセンサを備える。電話を掛ける、或いは文字を入力する等のあらゆる操作は、指やスタイルス等で表示部952に触れることで行うことができる。また、筐体951及び表示部952は可撓性を有し、図示するように折り曲げて使用することができる。表示部952に本発明の一態様の表示装置を用いることで、表示部952に高輝度の画像を表示することができ、ダイナミックレンジを高めることができる。

**【 0 2 1 8 】**

20

図14(D)は携帯データ端末であり、筐体911、表示部912、スピーカ913、カメラ919等を有する。表示部912が有するタッチパネル機能により情報の入出力を行うことができる。表示部912に本発明の一態様の表示装置を用いることで、表示部912に高輝度の画像を表示することができ、ダイナミックレンジを高めることができる。

**【 0 2 1 9 】**

図14(E)はデジタルカメラであり、筐体961、シャッターボタン962、マイク963、表示部965、操作キー966、スピーカ967、ズームレバー968、レンズ969等を有する。表示部965に本発明の一態様の表示装置を用いることで、表示部965に高輝度の画像を表示することができ、ダイナミックレンジを高めることができる。

**【 0 2 2 0 】**

図14(F)はデジタルサイネージであり、柱921の側面に大型の表示部922が取り付けられた構成を有する。表示部922に本発明の一態様の表示装置を用いることで、表示部922に高輝度の画像を表示することができ、ダイナミックレンジを高めることができる。

30

**【 0 2 2 1 】**

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

**【 0 2 2 2 】****(実施の形態5)**

本実施の形態では、上記実施の形態で例示した、画像記憶装置等の記憶装置に適用可能な半導体装置について説明する。

40

**【 0 2 2 3 】**

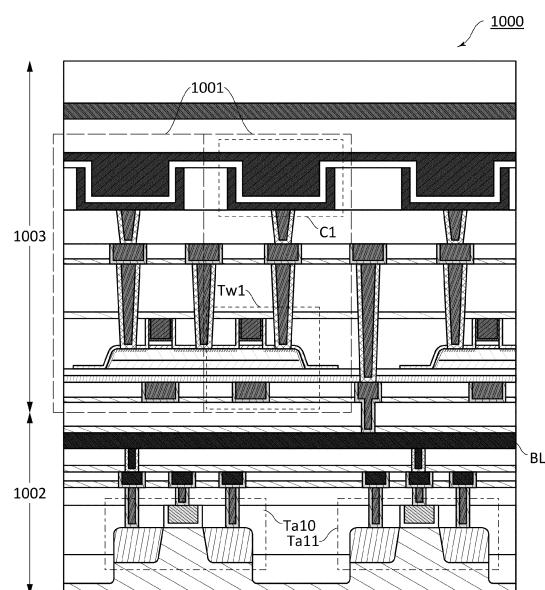

本実施の形態では、酸化物半導体を用いた記憶装置の一例として、DOSRAM(登録商標)について説明する。なお、「DOSRAM」の名称は、Dynamic Oxide Semiconductor Random Access Memoryに由来する。DOSRAMとは、メモリセルが、1T1C(1トランジスタ1容量)型セルであり、かつ書き込みトランジスタが、酸化物半導体が適用されたトランジスタである記憶装置のことである。

**【 0 2 2 4 】**

図15を用いて、DOSRAM1000の積層構造例について説明する。DOSRAM1000は、データの読み出しを行うセンスアンプ部1002と、データを格納するセルア

50

レイ部 1003 とが積層されている。

【0225】

図15に示すように、センスアンプ部1002には、ビット線BL、SiトランジスタTa10、Ta11が設けられている。SiトランジスタTa10、Ta11は、単結晶シリコンウェハに半導体層をもつ。SiトランジスタTa10、Ta11は、センスアンプを構成し、ビット線BLに電気的に接続されている。

【0226】

セルアレイ部1003は複数のメモリセル1001を有する。メモリセル1001は、トランジスタTw1及び容量素子C1を有する。セルアレイ部1003において、2個のトランジスタTw1は半導体層を共有する。半導体層とビット線BLとは図示しない導電体により電気的に接続されている。

10

【0227】

図15に示すような積層構造は、トランジスタ群を有する回路を複数積層して構成される様々な半導体装置に適用できる。

【0228】

図15中の金属酸化物、絶縁体、導電体等は、単層でも積層でもよい。これらの作製には、スパッタリング法、分子線エピタキシー法(MBE法)、パルスレーザアブレーション法(PLA法)、化学気相堆積法(CVD法)、原子層堆積法(ALD法)などの各種の成膜方法を用いることができる。なお、CVD法には、プラズマCVD法、熱CVD法、有機金属CVD法などがある。

20

【0229】

ここでは、トランジスタTw1の半導体層は、金属酸化物(酸化物半導体)で構成されている。ここでは、半導体層が3層の金属酸化物層で構成されている例を示している。半導体層は、In、Ga、およびZnを含む金属酸化物で構成されることが好ましい。

【0230】

ここで、金属酸化物は、酸素欠損を形成する元素、または酸素欠損と結合する元素を添加されることで、キャリア密度が増大し、低抵抗化する場合がある。例えば、金属酸化物を用いた半導体層を選択的に低抵抗化することで、半導体層にソース領域またはドレイン領域を設けることができる。

30

【0231】

なお、金属酸化物を低抵抗化する元素としては、代表的には、ホウ素、またはリンが挙げられる。また、水素、炭素、窒素、フッ素、硫黄、塩素、チタン、希ガス等を用いてもよい。希ガスの代表例としては、ヘリウム、ネオン、アルゴン、クリプトン、及びキセノン等がある。当該元素の濃度は、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)などを用いて測定することができる。

【0232】

特に、ホウ素、及びリンは、アモルファスシリコン、または低温ポリシリコンの製造ラインの装置を使用することができるため、好ましい。既存の設備を転用することができ、設備投資を抑制することができる。

40

【0233】

選択的に低抵抗化した半導体層を有するトランジスタは、例えば、ダミーゲートを用いることで形成することができる。具体的には、半導体層上にダミーゲートを設け、当該ダミーゲートをマスクとして用い、上記半導体層を低抵抗化する元素を添加するとよい。つまり、半導体層が、ダミーゲートと重疊していない領域に、当該元素が添加され、低抵抗化した領域が形成される。なお、当該元素の添加方法としては、イオン化された原料ガスを質量分離して添加するイオン注入法、イオン化された原料ガスを質量分離せずに添加するイオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

【0234】

導電体に用いられる導電材料には、リン等の不純物元素をドーピングした多結晶シリコン

50

に代表される半導体、ニッケルシリサイド等のシリサイド、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属、または上述した金属を成分とする金属窒化物（窒化タンタル、窒化チタン、窒化モリブデン、窒化タングステン）等がある。また、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を用いることができる。

#### 【0235】

絶縁体に用いられる絶縁材料には、窒化アルミニウム、酸化アルミニウム、窒化酸化アルミニウム、酸化窒化アルミニウム、酸化マグネシウム、窒化シリコン、酸化シリコン、窒化酸化シリコン、酸化窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニア、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタル、アルミニウムシリケートなどがある。なお、本明細書等において、酸化窒化物とは、酸素の含有量が窒素よりも多い化合物であり、窒化酸化物とは、窒素の含有量が酸素よりも多い化合物のことをいう。

10

#### 【0236】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

#### 【実施例1】

#### 【0237】

20

本実施例では、本発明の一態様の表示装置が有するEL素子を発光させた場合における発光輝度の測定結果、及び 値と階調との関係の測定結果について説明する。

#### 【0238】

本実施例では、図8に示す構成の画素10dを有する表示装置を用いて、EL素子104の発光輝度を測定した。具体的には、画素10dに画像信号S1のみを供給した場合（条件1）のEL素子104の発光輝度、並びに画素10dに画像信号S1及び画像信号S2を供給した場合（条件2）のEL素子104の発光輝度を測定した。ここで、容量素子113の容量値C<sub>1</sub>と、容量素子103の容量値C<sub>2</sub>との比C<sub>1</sub>/C<sub>2</sub>を4/1、電位V<sub>01</sub>を0V、配線130の電位を0V、電源線128の電位を12V、共通配線129の電位を-2Vとした。また、条件1において、画像信号S1の電位V<sub>S1</sub>を5Vとし、条件2において、画像信号S1の電位V<sub>S1</sub>を5V、画像信号S2の電位V<sub>S2</sub>を5Vとした。

30

#### 【0239】

表1に、条件1及び条件2における、実施の形態1に示す数式1を用いて計算したノードNMの電位V<sub>NM</sub>の計算値を示す。また、条件1及び条件2における、EL素子104の発光輝度の測定結果を示す。

#### 【0240】

#### 【表1】

|                   | 条件1                   | 条件2                    |

|-------------------|-----------------------|------------------------|

| 電位V <sub>NM</sub> | 5V                    | 9V                     |

| 輝度                | 612 cd/m <sup>2</sup> | 1329 cd/m <sup>2</sup> |

40

#### 【0241】

表1に示すように、画像信号S1と共に画像信号S2を画素10dに供給することにより、画像信号S1のみを画素10dに供給する場合よりEL素子104の発光輝度が高くなることが確認された。

#### 【0242】

また、図8に示す構成の画素10dを有する表示装置を用いて、 値と階調との関係を測定した。具体的には、画素10dに画像信号S1のみを供給した場合（条件3）における 値と階調との関係、並びに画素10dに画像信号S1及び画像信号S2を供給した場合

50

(条件4)における 値と階調との関係を測定した。なお、上記条件1及び条件2と同様に、 $C_1 / C_2$ を4/1、電位 $V_{o1}$ を0V、配線130の電位を0V、電源線128の電位を12V、共通配線129の電位を-2Vとした。また、電位 $V_{S1}$ は電位 $V_{S2}$ と等しくし、階調0の場合は電位 $V_{S1}$ と電位 $V_{S2}$ を共に1V、階調255の場合は電位 $V_{S1}$ と電位 $V_{S2}$ を共に5Vとした。

#### 【0243】

図16に、条件3及び条件4における、 値と階調との関係の測定結果を示す。図16より、測定を行った各階調において、画像信号S1と共に画像信号S2を画素10dに供給すること(条件4)により、画像信号S1のみを画素10dに供給する場合(条件3)より 値が増加することが確認された。

10

#### 【実施例2】

#### 【0244】

本実施例では、本発明の一態様の表示装置を用いて画像を表示した場合における表示結果について説明する。

#### 【0245】

本実施例では、図8に示す構成の画素10dを有する表示装置を用いて画像を表示した。具体的には、画像信号S1に対応する画像P1、画像信号S2に対応する画像P2、及び画像P1と画像P2を重ね合わせた画像を表示した。なお、容量素子113の容量値 $C_1$ と、容量素子103の容量値 $C_2$ との比 $C_1 / C_2$ を4/1、電位 $V_{o1}$ を0V、配線130の電位を0V、電源線128の電位を10V、共通配線129の電位を-2Vとした。

20

#### 【0246】

図17に示すように、画像P1と画像P2を重ね合わせることにより、画像P1のみを表示した場合、及び画像P2のみを表示した場合より高輝度の画像が表示されることが確認された。

#### 【符号の説明】

#### 【0247】

10 画素

10a 画素

10b 画素

10c 画素

10d 画素

30

12 ゲートドライバ

13 ソースドライバ

14 照度センサ

15 デマルチプレクサ

102 トランジスタ

103 容量素子

104 EL素子

105 トランジスタ

111 トランジスタ

40

112 トランジスタ

113 容量素子

114 トランジスタ

121 配線

122 配線

124 配線

125 配線

126 配線

128 電源線

129 共通配線

50

|         |          |    |

|---------|----------|----|

| 1 3 0   | 配線       |    |

| 2 0 0   | 表示装置     |    |

| 2 1 5   | 表示部      |    |

| 2 2 1   | 走査線駆動回路  |    |

| 2 3 1   | 信号線駆動回路  |    |

| 2 3 2   | 信号線駆動回路  |    |

| 2 4 1   | 共通線駆動回路  |    |

| 7 2 3   | 電極       |    |

| 7 2 6   | 絶縁層      | 10 |

| 7 2 8   | 絶縁層      |    |

| 7 2 9   | 絶縁層      |    |

| 7 4 1   | 絶縁層      |    |

| 7 4 2   | 半導体層     |    |

| 7 4 4 a | 電極       |    |

| 7 4 4 b | 電極       |    |

| 7 4 6   | 電極       |    |

| 7 5 5   | 不純物      |    |

| 7 7 1   | 基板       |    |

| 7 7 2   | 絶縁層      |    |

| 8 1 0   | トランジスタ   | 20 |

| 8 1 1   | トランジスタ   |    |

| 8 2 0   | トランジスタ   |    |

| 8 2 1   | トランジスタ   |    |

| 8 2 5   | トランジスタ   |    |

| 8 2 6   | トランジスタ   |    |

| 8 4 2   | トランジスタ   |    |

| 8 4 3   | トランジスタ   |    |

| 8 4 4   | トランジスタ   |    |

| 8 4 5   | トランジスタ   |    |

| 8 4 6   | トランジスタ   | 30 |

| 8 4 7   | トランジスタ   |    |

| 9 0 1   | 筐体       |    |

| 9 0 2   | 表示部      |    |

| 9 0 3   | 表示部      |    |

| 9 0 4   | センサ      |    |

| 9 1 1   | 筐体       |    |

| 9 1 2   | 表示部      |    |

| 9 1 3   | スピーカ     |    |

| 9 1 9   | カメラ      |    |

| 9 2 1   | 柱        | 40 |

| 9 2 2   | 表示部      |    |

| 9 5 1   | 筐体       |    |

| 9 5 2   | 表示部      |    |

| 9 5 3   | 操作ボタン    |    |

| 9 5 4   | 外部接続ポート  |    |

| 9 5 5   | スピーカ     |    |

| 9 5 6   | マイク      |    |

| 9 5 7   | カメラ      |    |

| 9 6 1   | 筐体       |    |

| 9 6 2   | シャッターボタン | 50 |

|         |             |    |

|---------|-------------|----|

| 9 6 3   | マイク         |    |

| 9 6 5   | 表示部         |    |

| 9 6 6   | 操作キー        |    |

| 9 6 7   | スピーカ        |    |

| 9 6 8   | ズームレバー      |    |

| 9 6 9   | レンズ         |    |

| 9 7 1   | 筐体          |    |

| 9 7 3   | 表示部         |    |

| 9 7 4   | 操作キー        |    |

| 9 7 5   | スピーカ        | 10 |

| 9 7 6   | 通信用接続端子     |    |

| 9 7 7   | 光センサ        |    |

| 1 0 0 0 | D O S R A M |    |

| 1 0 0 1 | メモリセル       |    |

| 1 0 0 2 | センスアンプ部     |    |

| 1 0 0 3 | セルアレイ部      |    |

| 4 0 0 1 | 基板          |    |

| 4 0 0 5 | シール材        |    |

| 4 0 0 6 | 基板          |    |

| 4 0 1 0 | トランジスタ      | 20 |

| 4 0 1 1 | トランジスタ      |    |

| 4 0 1 4 | 配線          |    |

| 4 0 1 5 | 電極          |    |

| 4 0 1 7 | 電極          |    |

| 4 0 1 8 | F P C       |    |

| 4 0 1 9 | 異方性導電層      |    |

| 4 0 2 0 | 容量素子        |    |

| 4 0 2 1 | 電極          |    |

| 4 0 3 0 | 電極層         |    |

| 4 0 3 1 | 電極層         | 30 |

| 4 0 4 1 | プリント基板      |    |

| 4 0 4 2 | 集積回路        |    |

| 4 1 0 2 | 絶縁層         |    |

| 4 1 0 3 | 絶縁層         |    |

| 4 1 1 0 | 絶縁層         |    |

| 4 1 1 1 | 絶縁層         |    |

| 4 1 1 2 | 絶縁層         |    |

| 4 2 0 0 | 入力装置        |    |

| 4 2 1 0 | タッチパネル      |    |

| 4 2 2 7 | 電極          | 40 |

| 4 2 2 8 | 電極          |    |

| 4 2 3 7 | 配線          |    |

| 4 2 3 8 | 配線          |    |

| 4 2 3 9 | 配線          |    |

| 4 2 6 3 | 基板          |    |

| 4 2 7 2 | F P C       |    |

| 4 2 7 3 | I C         |    |

| 4 3 0 1 | 着色層         |    |

| 4 3 0 2 | 遮光層         |    |

| 4 5 1 0 | 隔壁          | 50 |

4 5 1 1 発光層

4 5 1 3 発光素子

4 5 1 4 充填材

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図5】

【図6】

10

【図7】

【図8】

20

30

40

50

【図9】

【図10】

10

20

30

40

【図11】

【図12】

50

【図13】

【図14】

10

20

30

40

【図15】

金属酸化物 □ □ □

絶縁体 □ □ □

導電体 ■ ■ ■ ■ ■ ■ ■ ■

【図16】

50

【図 1 7】

P1

P2

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

H 01 L 27/32

(72)発明者 高橋 圭

神奈川県厚木市長谷 398 番地 株式会社半導体エネルギー研究所内

(72)発明者 林 健太郎

神奈川県厚木市長谷 398 番地 株式会社半導体エネルギー研究所内

(72)発明者 山崎 舜平

神奈川県厚木市長谷 398 番地 株式会社半導体エネルギー研究所内

審査官 武田 悟

(56)参考文献 特開 2012-185328 (JP, A)

特開 2007-256728 (JP, A)

特開 2001-228818 (JP, A)

特開 2005-292584 (JP, A)

米国特許出願公開第 2003/0098875 (US, A1)

米国特許出願公開第 2017/0025080 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

G 09 G 3/00 - 3/38

H 01 L 27/32