#### (19) **日本国特許庁(JP)**

# (12)公表特許公報(A)

(11)特許出願公表番号

特表2018-521512 (P2018-521512A)

(43) 公表日 平成30年8月2日(2018.8.2)

| (51) Int.Cl. |          |           | F I  |          |     | テーマコード (参考) |

|--------------|----------|-----------|------|----------|-----|-------------|

| HO1L         | 21/336   | (2006.01) | HO1L | 29/78    | 371 | 5F083       |

| HO1L         | 29/788   | (2006.01) | HO1L | 27/11546 |     | 5 F 1 O 1   |

| HO1L         | 29/792   | (2006.01) | HO1L | 27/11524 |     |             |

| HO1L         | 27/11546 | (2017.01) |      |          |     |             |

審査請求 有 予備審査請求 未請求 (全 22 頁)

| (21) 出願番号     | 特願2018-502650 (P2018-502650) |

|---------------|------------------------------|

| (86) (22) 出願日 | 平成28年6月14日 (2016.6.14)       |

| (85) 翻訳文提出日   | 平成30年1月19日 (2018.1.19)       |

| (86) 国際出願番号   | PCT/US2016/037436            |

| (87) 国際公開番号   | W02017/014866                |

| (87) 国際公開日    | 平成29年1月26日 (2017.1.26)       |

| (31) 優先権主張番号  | 62/194, 894                  |

| (32) 優先日      | 平成27年7月21日 (2015.7.21)       |

| (33) 優先権主張国   | 米国 (US)                      |

| (31) 優先権主張番号  | 15/180, 376                  |

| (32) 優先日      | 平成28年6月13日 (2016.6.13)       |

| (33) 優先権主張国   | 米国 (US)                      |

HO1L 27/11524 (2017.01)

(71) 出願人 500147506 シリコン ストーリッジ テクノロージー インコーポレイテッド

SILICON STORAGE TECHNOLOGY. INC.

アメリカ合衆国 95134 カリフォル ニア州 サンノゼ ホルガー ウェイ 4

50

(74)代理人 100094569

弁理士 田中 伸一郎

(74)代理人 100088694

弁理士 弟子丸 健

(74)代理人 100103610

弁理士 ▲吉▼田 和彦

最終頁に続く

(54) 【発明の名称】統合された高K金属ゲート論理デバイス及び無金属消去ゲートを有する不揮発性分割ゲートメモリセル、並びにその作製方法

# (57)【要約】

HKMG論理ゲートを有する論理デバイス及び高電圧デバイスと同じチップ上に分割ゲート不揮発性メモリセルを形成する方法。本方法は、ソース領域及びドレイン領域、浮遊ゲート、制御ゲート、並びに消去ゲート及びワード線ゲートのポリ層をチップのメモリエリア内に形成することを含む。保護絶縁層がメモリエリアの上方に形成され、HKMG層及びポリ層がチップ上に形成され、メモリエリアから除去され、チップの論理エリア内でパターン形成されて、様々な量の下部絶縁を有する論理ゲートを形成する。

#### 【特許請求の範囲】

#### 【請求項1】

メモリデバイスを形成する方法であって、

メモリセルエリア、コアデバイスエリア、及びHVデバイスエリアを有する半導体基板を提供することと、

離間したソース領域及びドレイン領域を前記基板の前記メモリセルエリア内に形成することであって、チャネル領域がそれらの間に延在する、形成することと、

前記チャネル領域の第1の部分及び前記ソース領域の一部分の上方に配設され、かつそれらから絶縁された導電性浮遊ゲートを形成することと、

前記浮遊ゲートの上方に配設され、かつそれから絶縁された導電性制御ゲートを形成することと、

前記ソース領域及び前記チャネル領域の第2の部分の上方に少なくとも延在し、かつそれらから絶縁された第1の導電層を前記メモリセルエリア内に形成することと、

前記メモリセルエリア内の前記第1の導電層、前記コアデバイスエリア内の前記基板の表面部分、及び前記HVデバイスエリア内の前記基板の表面部分の上方に延在する第1の 絶縁層を形成することと、

前記第1の絶縁層を前記コアデバイスエリアから除去することと、

前記メモリセルエリア及び前記HVデバイスエリア内の前記第1の絶縁層の上方に、かつ前記コアデバイスエリア内の前記基板の前記表面部分の上方に延在するHKMG層を形成することであって、前記HKMG層が、

高K誘電材料層と、

前記高 K 誘電材料層上の金属材料層と、を含む、形成することと、

前記メモリセルエリア、前記コアデバイスエリア、及び前記HVデバイスエリア内の前記HKMG層の上方に延在する第2の導電層を形成することと、

前記HKMG層及び前記第2の導電層を前記メモリセルエリアから除去することと、

前記第1の絶縁層を前記メモリセルエリアから除去することと、

前記第1の導電層の部分を除去することであって、前記ソース領域の上方に配設され、かつそれから絶縁された前記第1の導電層の第1の部分が消去ゲートとして留まり、前記チャネル領域の第2の部分の上方に配設され、かつそれから絶縁された前記第1の導電層の第2の部分がワード線ゲートとして留まる、除去することと、

前記HKMG層及び前記第2の導電層の部分を前記コアデバイスエリア及び前記HVデバイスエリアから除去することであって、前記HKMG層の第1の部分及び前記第2の導電層の第1の部分が第1の論理ゲートとして前記コアデバイスエリア内に留まり、前記HKMG層の第2の部分及び前記第2の導電層の第2の部分が第2の論理ゲートとして前記HVデバイスエリア内に留まる、除去することと、を含む、方法。

## 【請求項2】

前記第1の絶縁層が、二酸化シリコンである、請求項1に記載の方法。

#### 【請求項3】

前記第1の導電層及び前記第2の導電層が、ポリシリコンである、請求項1に記載の方法。

# 【請求項4】

第2の論理ゲートが前記第1の絶縁層によって前記基板から絶縁され、前記第1の論理ゲートが前記第1の絶縁層によって前記基板から絶縁されない、請求項1に記載の方法。

## 【請求項5】

前記HVデバイスエリア内の前記HKMG層と前記第1の絶縁層との間に、かつ前記コアデバイスエリア内の前記HKMG層と前記基板との間に配設された絶縁材料の界面層を形成することを更に含む、請求項1に記載の方法。

# 【請求項6】

メモリデバイスを形成する方法であって、

メモリセルエリア、コアデバイスエリア、及びHVデバイスエリアを有する半導体基板

20

10

30

40

を提供することと、

離 間 し た ソ - ス 領 域 及 び ド レ イ ン 領 域 を 前 記 基 板 の 前 記 メ モ リ セ ル エ リ ア 内 に 形 成 す る ことであって、チャネル領域がそれらの間に延在する、形成することと、

前 記 チャネル 領 域 の 第 1 の 部 分 及 び 前 記 ソ ー ス 領 域 の 一 部 分 の 上 方 に 配 設 さ れ 、 か つ そ れらから絶縁された導電性浮遊ゲートを形成することと、

前記浮遊ゲートの上方に配設され、かつそれから絶縁された導電性制御ゲートを形成す ることと、

前記ソース領域の上方に配設され、かつそれから絶縁された導電性消去ゲートを形成す ることと、

第1の絶縁材料を前記消去ゲートの上方に形成することと、

第 2 の 絶 縁 材 料 を 前 記 H V デ バ イ ス エ リ ア 内 の 前 記 基 板 の 表 面 部 分 の 上 方 に 形 成 す る こ とと、

前記メモリセルエリア、前記コアデバイスエリア、及び前記HVデバイスエリアの上方 に延在するHKMG層を形成することであって、前記HKMG層が、

高K誘電材料層と、

前記高K誘電材料層上の金属材料層と、を含む、形成することと、

前記メモリセルエリア、前記コアデバイスエリア、及び前記HVデバイスエリア内の前 記HKMG層の上方に延在する導電層を形成することと、

前記HKMG層及び前記導電層の部分を前記メモリセルエリア、前記コアデバイスエリ ア、及び前記HVデバイスエリアから除去することと、を含み、

前 記 チ ャ ネ ル 領 域 の 第 2 の 部 分 の 上 方 に 配 設 さ れ た 前 記 H K M G 層 の 第 1 の 部 分 及 び 前記導電層の第1の部分がワード線ゲートとして留まり、

前記HKMG層の第2の部分及び前記導電層の第2の部分が第1の論理ゲートとして 前記コアデバイスエリア内に留まり、

前記HKMG層の第3の部分及び前記導電層の第3の部分が第2の論理ゲートとして 前記HVデバイスエリア内に留まる、方法。

前記導電層が、ポリシリコンである、請求項6に記載の方法。

## 【請求項8】

第 2 の 論 理 ゲ ー ト が 前 記 第 2 の 絶 縁 材 料 に よ っ て 前 記 基 板 か ら 絶 縁 さ れ 、 前 記 第 1 の 論 理 ゲート が 前 記 第 2 の 絶 縁 材 料 に よ っ て 前 記 基 板 か ら 絶 縁 さ れ な い 、 請 求 項 6 に 記 載 の 方 法。

#### 【請求項9】

前記 H V デバイスエリア内の前記 H K M G 層と前記第 2 の絶縁材料との間に、前記コア デバイスエリア内の前記HKMG層と前記基板との間に、かつ前記メモリセルエリア内の 前 記 H K M G 層 と 前 記 チ ャ ネ ル 領 域 の 前 記 第 2 の 部 分 と の 間 に 配 設 さ れ た 絶 縁 材 料 の 界 面 層を形成することを更に含む、請求項6に記載の方法。

【発明の詳細な説明】

# 【技術分野】

#### [0001]

本発明は、不揮発性メモリデバイスに関する。

#### [00002]

## (関連出願の相互参照)

本出願は、参照により本明細書に組み込まれる、2015年7月21日出願の米国仮出 願 第 6 2 / 1 9 4 , 8 9 4 号の利益を主張するものである。

# 【背景技術】

#### [00003]

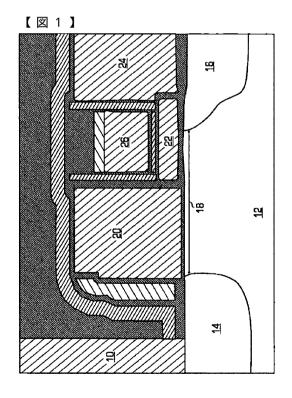

分 割 ゲ ー ト 不 揮 発 性 メ モ リ セ ル は 、 当 技 術 分 野 に お い て 周 知 で あ る 。 例 え ば 、 米 国 特 許 第 7 , 9 2 7 , 9 9 4 号 は 、 分 割 ゲ ー ト 不 揮 発 性 メ モ リ セ ル を 開 示 し て い る 。 図 1 は 、 半 導 体 基 板 1 2 上 に 形 成 さ れ た か か る 分 割 ゲ ー ト メ モ リ セ ル の 一 例 を 例 証 す る 。 ソ ー ス 領 域 10

20

30

40

及びドレイン領域16及び14は、基板12内の拡散領域として形成され、それらの間にチャネル領域18を画定する。メモリセルは、4つの導電性ゲート、すなわち、チャネル領域18の第1の部分及びソース領域16の一部分の上方に配設され、かつそれから絶縁された浮遊ゲート22、浮遊ゲート22の上方に配設され、かつそれから絶縁された制御ゲート26、ソース領域16の上方に配設され、かつそれから絶縁された消去ゲート24、及びチャネル領域18の第2の部分の上方に配設され、かつそれから絶縁された選択ゲート20を含む。導電性接点10が形成されて、ドレイン領域14に電気的に接続することができる。

【発明の概要】

【発明が解決しようとする課題】

[0004]

メモリセルがアレイ状に配置され、かかるメモリセルの列が分離領域の列によって分離される。分離領域は、絶縁材料が形成される基板の部分である。論理(コア)デバイス及び高電圧デバイスは、メモリアレイと同じチップ上に形成され、多くの場合、同じ加工工程のうちのいくつかを共有して形成され得る。高 K 金属材料からのメモリセルゲート並びに論理ゲート及び高電圧ゲート(H K M G - 金属層の下の高 K 誘電体層)の作製も既知である。しかしながら、消去ゲート用の高 K 金属材料の存在がトンネル酸化物上に高密度トラップをもたらし、性能不良につながり得ることが見出された。消去ゲート金属を除去し、ポリシリコンを置き換えることにより、下部トンネル酸化物が損傷され、保持失敗、並びに性能不足がもたらされ得る。

[0005]

本発明は、HKMG論理ゲートを有する論理デバイス及び高電圧デバイスと同じチップ上に分割ゲート不揮発性メモリデバイスを形成するための技術である。

【課題を解決するための手段】

[0006]

メモリデバイスを形成する方法は、

メモリセルエリア、コアデバイスエリア、及びHVデバイスエリアを有する半導体基板を提供することと、

離間したソース領域及びドレイン領域を基板のメモリセルエリア内に形成することであって、チャネル領域がそれらの間に延在する、形成することと、

チャネル領域の第1の部分及びソース領域の一部分の上方に配設され、かつそれから絶縁された導電性浮遊ゲートを形成することと、

浮遊ゲートの上方に配設され、かつそれから絶縁された導電性制御ゲートを形成することと、

ソース領域及びチャネル領域の第2の部分の上方に少なくとも延在し、かつそれらから 絶縁された第1の導電層をメモリセルエリア内に形成することと、

メモリセルエリア内の第1の導電層、コアデバイスエリア内の基板の表面部分、及び H V デバイスエリア内の基板の表面部分の上方に延在する第1の絶縁層を形成することと、 第1の絶縁層をコアデバイスエリアから除去することと、

メモリセルエリア及びHVデバイスエリア内の第1の絶縁層の上方に、かつコアデバイスエリア内の基板の表面部分の上方に延在するHKMG層を形成することであって、HKMG層が、

高K誘電材料層と、

高K誘電材料層上の金属材料層と、を含む、形成することと、

メモリセルエリア、コアデバイスエリア、及びHVデバイスエリア内のHKMG層の上方に延在する第2の導電層を形成することと、

HKMG層及び第2の導電層をメモリセルエリアから除去することと、

第1の絶縁層をメモリセルエリアから除去することと、

第1の導電層の部分を除去することであって、ソース領域の上方に配設され、かつそれから絶縁された第1の導電層の第1の部分が消去ゲートとして留まり、チャネル領域の第

10

20

30

40

2 の 部 分 の 上 方 に 配 設 さ れ 、 か つ そ れ か ら 絶 縁 さ れ た 第 1 の 導 電 層 の 第 2 の 部 分 が ワ ー ド 線ゲートとして留まる、除去することと、

H K M G 層 及 び 第 2 の 導 電 層 の 部 分 を コ ア デ バ イ ス エ リ ア 及 び H V デ バ イ ス エ リ ア から 除 去 す る こ と で あ っ て 、 H K M G 層 の 第 1 の 部 分 及 び 第 2 の 導 電 層 の 第 1 の 部 分 が コ ア デ バイスエリアとして第1の論理ゲート内に留まり、HKMG層の第2の部分及び第2の導 電層の第2の部分が第2の論理ゲートとしてHVデバイスエリア内に留まる、除去するこ とと、を含む。

#### [0007]

メモリデバイスを形成する方法は、

メモリセルエリア、コアデバイスエリア、及びHVデバイスエリアを有する半導体基板 を提供することと、

離 間 し た ソ - ス 領 域 及 び ド レ イ ン 領 域 を 基 板 の メ モ リ セ ル エ リ ア 内 に 形 成 す る こ と で あ って、チャネル領域がそれらn間に延在する、形成することと、

チャネル領域の第1の部分及びソース領域の一部分の上方に配設され、かつそれから絶 縁された導電性浮遊ゲートを形成することと、

浮遊ゲートの上方に配設され、かつそれから絶縁された導電性制御ゲートを形成するこ とと、

ソース領域の上方に配設され、かつそれから絶縁された導電性消去ゲートを形成するこ とと、

第1の絶縁材料を消去ゲートの上方に形成することと、

第 2 の 絶 縁 材 料 を H V デ バ イ ス エ リ ア 内 の 基 板 の 表 面 部 分 の 上 方 に 形 成 す る こ と と 、

メモリセルエリア、コアデバイスエリア、 及び H V デバイスエリアの上方に延在する H KMG層を形成することであって、HKMG層が、

高K誘電材料層と、

高K誘電材料層上の金属材料層と、を含む、形成することと、

メモリセルエリア、コアデバイスエリア、及びHVデバイスエリア内のHKMG層の上 方に延在する導電層を形成することと、

H K M G 層及び導電層の部分をメモリセルエリア、コアデバイスエリア、及び H V デバ イスエリアから除去することと、を含み、

チャネル領域の第2の部分の上方に配設されたHKMG層の第1の部分及び導電層の第 1の部分がワード線ゲートとして留まり、

H K M G 層 の 第 2 の 部 分 及 び 導 電 層 の 第 2 の 部 分 が 第 1 の 論 理 ゲ ー ト と し て コ ア デ バ イ スエリア内に留まり、

H K M G 層の第 3 の部分及び導電層の第 3 の部分が第 2 の論理ゲートとして H V デバイ スエリア内に留まる。

#### [00008]

本発明の他の目的及び特徴は、明細書、請求項、添付図面を精読することによって明ら かになるであろう。

# 【図面の簡単な説明】

[0009]

【図1】従来のメモリセルの側面断面図である。

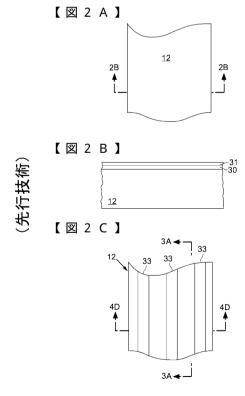

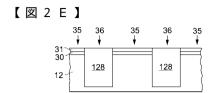

【図2A】STI絶縁の形成時の基板の上面図である。

【図2B】STI分離領域の形成時の基板の側面断面図である。

【図2C】STI絶縁の形成時の基板の上面図である。

【図2D】STI分離領域の形成時の基板の側面断面図である。

【図2E】STI分離領域の形成時の基板の側面断面図である。

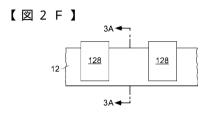

【図2F】STI分離領域の形成時の基板の側面断面図である。

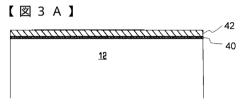

【 図 3 A 】 基 板 上 に 不 揮 発 性 メ モ リ セ ル 及 び 論 理 ゲ ー ト を 形 成 す る 工 程 を 例 証 す る 側 面 断 面図である。

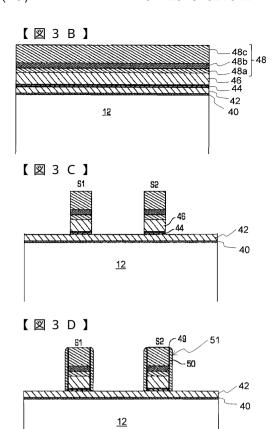

【図3B】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断

20

10

30

40

20

30

40

50

面図である。

- 【図3C】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図3D】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

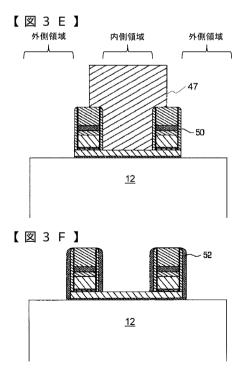

- 【図3E】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図3F】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

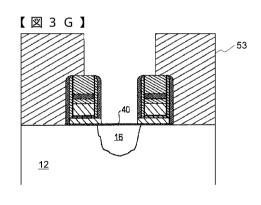

- 【図3G】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図4A】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図4B】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図4C】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図4D】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

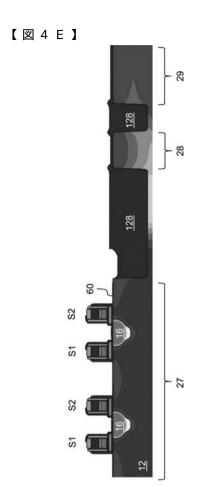

- 【図4E】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

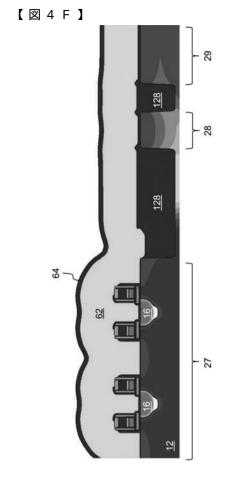

- 【図4F】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

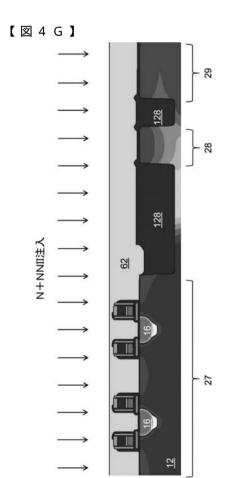

- 【図4G】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

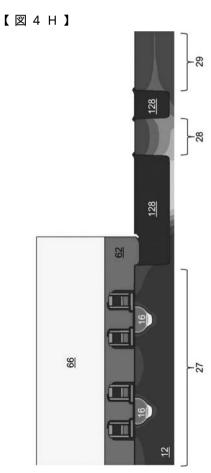

- 【図4H】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

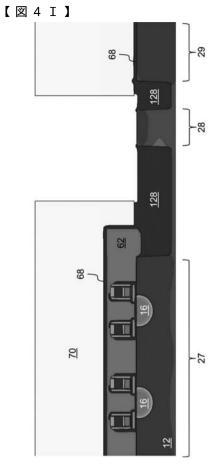

- 【図4Ⅰ】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

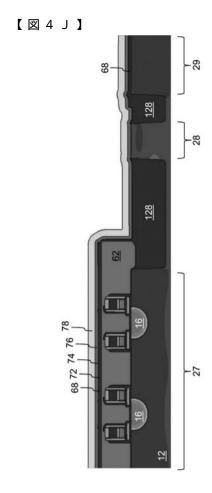

- 【図4J】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図4K】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

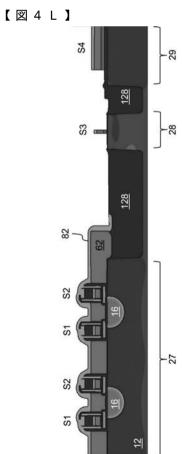

- 【図4L】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図4M】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

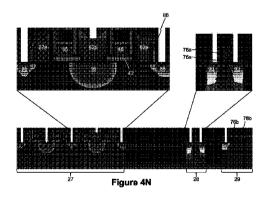

- 【図4N】基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図 5 A 】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【 図 5 B 】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図 5 C】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図 5 D】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図 5 E 】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

- 【図5F】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工

20

30

40

50

程を例証する側面断面図である。

【図 5 G】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

【図5H】代替実施形態による基板上に不揮発性メモリセル及び論理ゲートを形成する工程を例証する側面断面図である。

【発明を実施するための形態】

[ 0 0 1 0 ]

本発明は、高 K 金属材料を使用して論理ゲートを形成するが、消去ゲートをポリシリコン材料で最初に形成することによって上述の課題を解決する。かかるメモリセルを形成する方法は、図 2 A ~ 2 F、 3 A ~ 3 G、及び 4 A ~ 4 Nに例証される。この方法は、好ましくは P 型のものであり、当該技術分野で周知の半導体基板 1 2 から始まる。

分離領域形成

[0011]

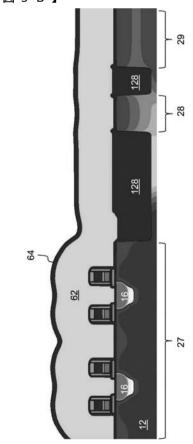

図2A~2Fは、基板上に分離領域を形成する周知のSTI方法を例証する。図2Aを参照して、好ましくはP型のものであり、当該技術分野で周知の半導体基板12(又は半導体ウェル)の平面図が示される。第1の材料層30及び第2の材料層31は、基板上に形成される(例えば、化成又は堆積する)。例えば、第1の層30は、二酸化シリコン(以下、「酸化物」)であってもよく、これは、酸化又は酸化物堆積(例えば、化学気相堆積又はCVD)等の任意の周知の技法によって基板12上に形成される。窒素ドープ酸化物又は他の絶縁性誘電体も使用されてもよい。第2の層31は、窒化シリコン(以下、「窒化物」)、であってもよく、これは、好ましくはCVD又はPECVDによって酸化物層30の上方に形成される。図2Bは、結果として得られた構造の断面を例証する。

[0012]

第1及び第2の層30/31が形成されると、好適なフォトレジスト材料32を窒化物層31上に塗布し、マスキング工程を行い、図2Cに示すように、Y又はカラム方向に延在する特定領域(ストライプ33)からフォトレジスト材料を選択的に除去する。フォトレジスト材料32が除去される場合、露出された窒化物層31及び酸化物層30は、標準のエッチング技法(すなわち、異方性窒化物及び酸化物/誘電体エッチング処理)を使用してストライプ33でエッチングされて、構造内にトレンチ34を形成する。その後、シリコンエッチング処理を使って、図2Dに示すように、シリコン基板12の中へトレンチ34を下方に延在させる。フォトレジスト32が除去されない場合、窒化物層31及び酸化物層30は維持される。図2Dに例証される結果として生じる構造は、分離領域36と織り合わせられた活性領域35を画定するようになる。

[ 0 0 1 3 ]

この構造が更に処理されて、残りのフォトレジスト32を除去する。その後、厚い酸化物層を蒸着することで、トレンチ34内に二酸化珪素のような分離材料が形成され、その後、化学機械研磨(CMP)エッチングが実行され(窒化物層31をエッチングのストッパとして使用)、図2Eに示すように、トレンチ34内の酸化物ブロック128を除いて、酸化物層を除去する。その後、残存する窒化物層31及び酸化物層30は、窒化/酸化エッチング処理を使用して除去され、図2Fに示すように、分離領域36に沿って延在するSTI酸化物ブロック128が残される。

[0014]

図2A~2Fは、基板のメモリセルアレイ領域を例証し、ここで、メモリセルのカラムが分離領域36によって分離される活性領域35内に形成される。基板12が、メモリセルアレイ領域内に形成されたメモリセルを動作させるために使用される制御回路が形成される少なくとも1つの周辺領域も含むことに留意されたい。好ましくは、分離ブロック128も上述の同じSTI処理中に周辺領域内に形成される。

メモリセル形成

[0015]

図2Fに示す構造は、更に以下のとおりに処理される。図3A~3Gは、本発明の処理

における次の工程が行われるときの、図2Fから直角に(図2C及び2Fに示される線3A-3Aに沿って)見た活性領域35内の構造の断面を示す。

#### [0016]

図3Aから始まり、基板12上の二酸化シリコン(酸化物)層40の形成が示される。その後、第1のポリシリコン(又はアモルファスシリコン)層42が二酸化シリコン層40上に堆積するか、又は形成される。第1のポリシリコン(ポリ)層42は、その後、活性領域35に平行の方向にパターン形成される(ポリシリコンを分離領域36から除去する)。

#### [0017]

図3 Bを参照して、二酸化シリコン等の別の絶縁層44(又は更には複合絶縁層、例えば、ONO(酸化物副層、窒化物副層、酸化物副層))が第1のポリシリコン層42上に堆積するか、又は形成される。その後、第2のポリシリコン層46が層44上に堆積するか、又は形成される。絶縁体の別の層48は、ポリシリコンの第2の層46上に堆積されるか、又は形成され、その後のドライエッチング中のハードマスクとして使用される。好ましい実施形態では、層48は、窒化シリコン副層48a、二酸化シリコン副層48b、及び窒化シリコン副層48cから成る複合層である。

#### [0018]

図3Cを参照して、フォトレジスト材料(図示せず)は、図3Bに示される構造上に堆積し、マスキング工程が形成され、フォトレジスト材料の選択された部分を露出する。フォトレジストは現像され、そのフォトレジストをマスクとして使用して、構造体に対するエッチングが行われる。複合層48、ポリシリコンの第2の層46、絶縁層44は、次にポリシリコンの第1の層42が露出されるまで異方性エッチングされる。結果として生じる構造が図3Cに示される。2つの「積層体」S1及びS2のみが示されているが、互いに分離されるかかる「積層体」がいくつか存在することが明らかであろう。

#### [0019]

図3 Dを参照して、二酸化シリコン49がその構造上に堆積するか、又は形成される。この後に窒化ケイ素層50の堆積が続く。二酸化シリコン49及び窒化ケイ素50は、異方性エッチングされ、積層体S1及びS2のそれぞれの周囲に(二酸化シリコン49及び窒化ケイ素50の混合である)スペーサ51を残す。結果として生じる構造が図3Dに示される。

#### [0020]

図3 Eを参照して、フォトレジストマスク47は、積層体51と52との間、かつ他の交互積層体対間の領域の上方に形成される。積層体51と52との間の領域は、本明細書で「内側領域」と称され、積層体の反対側の(フォトレジスト47によって被覆されていない)領域は、本明細書で「外側領域」と称される。外側領域内の露出された第1のポリシリコン42は、異方的にエッチングされる。酸化物層40は、部分的に又は完全にエッチングされ得る。結果として生じる構造が図3Eに示される。

#### [0021]

図3Fを参照して、フォトレジスト材料47は、図3Eに示される構造から除去される。その後、酸化物層52が堆積するか、又は形成される。その後、酸化物層52が異方性エッチングの対象となり、積層体S1及びS2に隣接してスペーサ52を残す。結果として生じる構造が図3Fに示される。

## [0022]

図3 Gを参照して、その後、フォトレジスト材料5 3 が堆積し、マスキングされて、積層体5 1 と5 2 との間の内側領域内に開口部を残すが、外側領域内に留まる。積層体5 1 と5 2 との間(及び他の交互積層体対間)の内側領域内のポリシリコン4 2 が異方的にエッチングされる。ポリシリコン4 2 の下の二酸化シリコン層 4 0 もまた、異方性エッチングされてもよい。結果として生じる構造がイオン注入の対象となり、第 2 の(ソース)領域 1 6 を形成する。結果として生じる構造が図3 Gに示される。

# [0023]

10

20

30

50

20

30

40

50

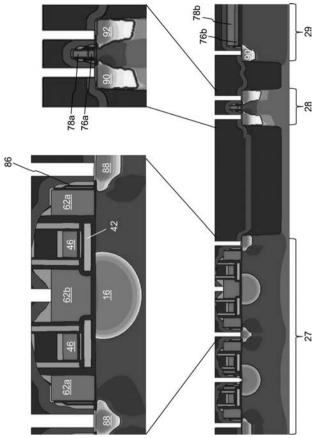

図4A~4Nは、メモリセルエリア27、絶縁アレイ境界領域(すなわち、絶縁エリア128)、コアデバイス(例えば、コア論理デバイス)が形成されるコアデバイスエリア28、及び高電圧デバイス(例えば、高電圧論理デバイス)が形成されるHVデバイスエリア29の活性領域35内の構造の拡大断面図である。図4Aに示されるように、図3Gのメモリセル積層体S1及びS2が形成され、コアデバイスエリア28又はHVデバイスエリア29内には構造がまだ形成されていない。外側壁スペーサ52は、浮遊ゲートとワード線との間の主な分離としての役割を果たす。

## [0024]

マスキング工程が行われて、この構造の上方に(HVII)フォトレジスト54を形成するが、積層体S1とS1との間の内側領域内に露出された状態で残す(すなわち、フォトレジストは、マスクを介して露出され、選択的に除去される)。注入が行われて、ソース領域16を増強する。その後、酸化物エッチングが行われて、図4Bに示されるように、積層体S1及びS2の内側壁及び内側領域内の基板表面に沿って露出された酸化物を除去する。フォトレジスト54が除去された後、酸化物層(すなわち、トンネル酸化物)56がその構造の上方に、具体的には、図4Cに示されるように、好ましくは高温CVD酸化物(HTO)を使用して、浮遊ゲートポリ層42の露出端に形成される。マスキング工程が行われて、(LVOX-0)フォトレジスト58を積層体S1及びS2の外側領域を除いてその構造の上方に形成する。酸化物エッチングが行われて、露出された酸化物を除去し、具体的には、図4Dに示されるように、基板の表面に沿って酸化物を除去する。

#### [ 0 0 2 5 ]

その後、酸化物層60(すなわち、ワード線酸化物層)が露出されたシリコン基板上に形成される。その後、図4Eに示されるように、フォトレジスト58が除去される。その後、ポリシリコン層62(メモリポリ)がその構造の上方に形成される。図4Fに示れるように、酸化物層64(キャップ酸化物)がポリ層62の上方に形成される。キャップ酸化物層64を使用して、周辺ウエハーエリア内でのポリディッシングを阻止する。ポリをは、化学機械研磨(CMP)を使用して平坦化される。メモリセルエリア内のポリアののポリ層の部分は、論理エリア(すなわち、コアデバイス28及びHVデバイスエリア29)人が問の部分よりもわずかに高くてもよい。その後、図4Gに示されるように、注工のポリ層の部分よりもわずなわち、ポリ層のN+NNIIドーピング)。マスキング工程を使用して、フォトレジスト66をその構造の上方に形成し、それを論理エリア28及び日のよりに除去する。その後、図4日に示されるように、ポリエッチングが行われて、計り層62を論理エリア28/29から除去し、酸化物エッチングが行われて、論理エリア28/29内の基板表面上のいかなる酸化物も除去する。

# [0026]

フォトレジスト66が除去された後、酸化物堆積が行われて、酸化物68(すなわち、HV酸化物)層をその構造の上方に、具体的には、論理エリア28/29内の基板表面上に形成する。1つ以上のマスキング工程を使用して、フォトレジストをその構造の上方に形成し、それを選択エリアから選択的に除去する。その後、1回以上の注入、具体的には、ウェル注入が露出されたコアデバイスエリア28及び任意のIOエリア、並びに/フェルンがでは、それらの特定のまる。コアNMOS及びPMOSは、それらの特定の決入のために別個のマスクを使用する。その後、マスク及びIOエリアからの酸化物のみをエッチングする酸化物エッチング(すなわち、LVOX)が行われる。その後、IO酸化物形成を使用して、酸化物層をIOエリア内のみに形成する。マスキング工程を使用して、フォトレジスト70をその構造の上方に形成し、それをコアデバイスエリア28のみから選択的に除去する。酸化物エッチング(すなわち、LLVOX)を使用して、図4Iに示されるように、コアデバイスエリア28内の基板表面上の酸化物68を除去する。

#### [0027]

酸化物薄層72(界面層(IL))がその構造の上方に形成される。その後、高K材料HKの(すなわち、HfO2、ZrO2、TiO2、Ta2O5、又は他の適切な材料等の酸化物の誘電率Kを超える誘電率Kを有する)絶縁層74を備える高K金属ゲート層H

20

30

40

50

КМ G が導電性金属層 7 6 の下に形成される。その後、図 4 」に示されるように、ポリシリコン層 7 8 が金属層 7 6 上に堆積する。マスキング工程が行われて、論理エリア 2 8 / 2 9 をフォトレジスト 8 0 で被覆するが、フォトレジストは、メモリセルエリア 2 7 から除去される。その後、図 4 Kに示されるように、エッチングを使用して、ポリ層 7 8 、金属層 7 6 、高 K 層 7 4 、 I L 層 7 2 、酸化物 6 8 、及び下部ポリ層 6 2 の上部分(すなわち、積層体 S 1 及び S 2 の上部より下)をメモリセルエリア 2 7 から除去する。

[ 0 0 2 8 ]

フォトレジスト80が除去された後、酸化物層82がその構造上に堆積し、その後、マ スキング工程が行われて、フォトレジストによって露出された論理デバイスエリア28/ 2 9 のある特定の部分のみを残す。一連のエッチングを使用して、酸化物 8 2 、ポリ層 7 8、金属層76、高K層74、及びIL層72を除去し、図4Lに示されるように(フォ トレジスト除去後)、論理デバイスのためのそれらのかかる層の積層体S3及びS4を、 それぞれ、コアデバイスエリア 2 8 及び H V デバイスエリア 2 9 内に選択的に残す。各積 層体S3/S4は、高K酸化物層74及びIL層72によって(加えて、より高い電圧で の動作のためにHVデバイスエリア29内の酸化物層68によって)基板から絶縁された ポリ層 6 2 及び金属層 7 6 の論理ゲートを構成する。マスキング工程を使用して、フォト レジスト84をその構造の上方に形成し、フォトレジストをメモリセルエリア27の外側 領域(すなわち、隣接したメモリセル対間の領域)から除去し、ソース線をストラップす るために使用される内側領域を選択する(図4Mの左側のセル対を参照のこと)。その後 、 酸 化 物 及 び ポ リ エ ッ チ ン グ を 使 用 し て 、 図 4 M に 示 さ れ る よ う に 、 外 側 及 び 内 側 積 層 体 領域内の酸化物層82及びポリ層62の露出された部分を除去する。これらのエッチング は、 メ モ リ セ ル ワ ー ド 線 6 2 a ( メ モ リ セ ル エ リ ア 2 7 の 外 側 領 域 内 の ポ リ 層 6 2 の ブ ロ ック)を画定する。ポリ層66の一部分62bは、内側領域内に留まる。

[0029]

フォトレジスト84が除去された後、最終加工が行われて、図4Nに示されるように、ワード線62aと並んで絶縁スペーサ86を形成し、ワード線62aに隣接した基板への注入によってドレイン領域88を形成し、論理ゲートに隣接した基板への注入によってソース領域90/ドレイン領域92をコアデバイスエリア28及びHVデバイスエリア29内に形成する。

[0030]

上述の処理により、HKMGコアデバイス及び高電圧デバイスと同じウエハー上にHKMGを含まないメモリセルが形成される。メモリセルエリア27内で、各メモリセルは、ソース16及びドレイン88を有し、それらの間にチャネル領域を画定する。浮遊ゲート42は、チャネル領域の第1の部分及びソース領域16の一部分の上方に配設され、ワード線ゲート62aは、チャネル領域の第2の部分の上方に配設される。制御ゲート46は、浮遊ゲート42の上方に配設される。消去ゲート62bは、ソース領域16の上方に配設される(ソース線へのストラップ接続のために使用されるメモリセル対は除く)。コア される(ソース線へのストラップ接続のために使用されるメモリセル対は除く)の記理エリア28内で、ソース領域90及びドレイン領域92は、それらの間にチャネル領域を画定し、その上方に高K層74及びIL層72によってそれから絶縁された(ポリ78b及び金属74、IL層72、及び酸化物層68によってそれから絶縁された(ポリ78b及び金属70の)HV論理ゲートが位置する。

[ 0 0 3 1 ]

形成中、消去ゲートポリ62bは、トンネル酸化物56を密封し、その後の加工工程でそれをHKMG材料への曝露から保護する。トンネル酸化物56の完全性は、前清浄、後清浄、乾燥、及びエッチング等のHKMG関連処理工程によって低下しない。論理エリア内のHKMG/ポリ論理ゲートは、ポリシリコンのみから作製されたゲート上に電流を増加させる。消去ゲート62b上でのHKMGの形成を回避することによって、トンネル酸化物上での高密度トラップの導入(これにより、耐久性不足がもたらされ得る)が回避さ

20

30

40

50

れる。更に、形成及びその後のHKMGの消去ゲートエリアからの除去を回避することによって、トンネル酸化物の下側への損傷(これにより、保持失敗、並びに耐久性不足がもたらされる)が回避される。

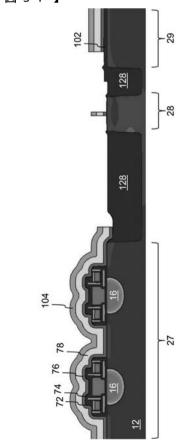

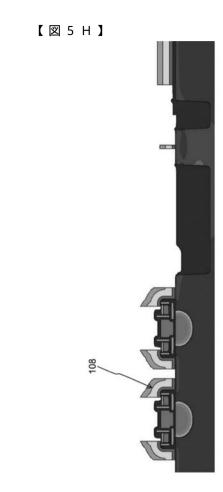

#### [0032]

図5A~5Hは、HKMG層が(ワード線電流を増加させるために)ワード線ゲートの一部として含まれる代替実施形態を例証する。これは、消去ゲートエリア内でのHKMG層の形成を依然として回避しながら行われ、消去ゲートがトンネル酸化物をHKMG加いの依然として保護する。この処理は、図4Cに示される(図5Aに再度示される)に、で通じて同じである。上述の酸化物エッチングの代わりに、図5Bに示されるように、がではつれる。ポリCMPエッチング及びポリエッチングバック処理が行われ、図5Cに対けされる。ポリCMPエッチング及びポリエッチングが行われ、図5Cに残す。NNIIを使用して、消去ゲート62bをメモリ積層体S1とS2との間に残す。NNII注のおいるように、又は後に行われ得る。マスキング工程を使用して、内側領域(及びその消去ゲート62b)をフォトレジスト100で被覆するが、フォトレジスト100を残の消去ゲート62b)をフォトレジスト100で被覆するが、フォトレジスト100を残ちの消去が一ト62b)をフォトレジスト100で被覆するが、フォトレジスト100を残るがのエリアから除去する。その後、ポリエッチングが行われ、図5Dに示されるように、基板上の酸化物層の露出された部分を除去する。

#### [0033]

IO及びコアマスク/注入が行われ、その後、HVOXマスク及びZMOS注入並びに酸化物エッチングが(HVデバイスエリア29内の残りの酸化物を除去するために)行われる。HV酸化物堆積を使用して、HVデバイスエリア29のために酸化物層102を形成し、その後、(IOエリアのみのために)LVOXマスク及び酸化物エッチングが行われる。その後、酸化物層形成工程がIOエリアに行われる。LLVOXマスク及び酸化物エッチングがコアデバイスエリア28及びメモリセルエリア27内の(積層体S1及びS2の)外側領域に行われて、基板上の酸化物を除去する。その後、図5Eに示されるように、酸化物層104の形成に加えて、上述のIL/HKMG/ポリ形成工程が3つ全ての領域27、28、29に行われる。

#### [ 0 0 3 4 ]

構造がフォトレジストでマスキングされ、これが選択的に除去されて、STI酸化物エリア並びにコアデバイスエリア及びHVデバイスエリアの部分を露出された状態で残す。その後、エッチングが行われて、図5Fに示されるように、酸化物128、ポリ78、金属76、高K層74、及びIL層72の露出された部分を除去する。構造がフォトレジスト106で再度マスキングされ、これがメモリ積層体とSTIエリア128の部分との間の内側領域から選択的に除去される。その後、エッチングが行われて、図5Gに示されるように、酸化物128、ポリ78、金属76、高K層74、及びIL層72の露出されたまうに、酸化物128、ポリ78、金属76、高K層74、及びIL層72の露出されたらされ、論理エリアゲートもメモリセルエリアワード線108もいずれも、IL層72の上方のHKMG層(金属76及び高K酸化物74)の上方のポリ層78から形成される。この加工が継続されて、メモリセルドレイン領域、論理エリアソース/ドレイン領域、及び接触線の形成が完了する。

# [ 0 0 3 5 ]

本発明は、上述の、及び本明細書に例示の実施形態(複数可)に限定されないことが理解されよう。例えば、本明細書で本発明に言及することは、任意の請求項又は請求項の用語の範囲を限定することを意図されておらず、その代わり、単に、1つ以上の請求項によって網羅され得る1つ以上の特徴に言及するものである。上述の材料、プロセス、及び数値例は、単なる例示であり、請求項を限定するものと見なされるべきではない。更に、特許請求の範囲及び明細書から明らかであるように、全ての方法工程が例証又は特許請求される正確な順序で行われる必要はないが、本発明のメモリセルの適切な形成を可能にする任意の順序で行われる。単一の材料層は、複数のそのような又は類似の材料層として形成することができ、そして、逆もまた同様である。本明細書で使用される、用語「形成」及

び「形成される」とは、材料堆積、材料化成、又は開示又は特許請求される材料を提供する際の任意の他の技法を含むものとする。

#### [0036]

本明細書で使用される、用語「~の上方に(over)」及び「~の上に(on)」はともに、「直接的に~の上に」(中間材料、要素、又は間隙がそれらの間に配設されていない)及び「間接的に~の上に」(中間材料、要素、又は間隙がそれらの間に配設されている)を包括的に含むことに留意されるべきである。同様に、用語「隣接する」は、「直接的に隣接する」(中間の材料、要素、又は間隙が間に配設されていない)及び「間接的に隣接する」(中間の材料、要素、又は間隙が間に配設されている)を含む。例えば、「基板の上方に」要素を形成することは、中間材料/要素が介在せずに直接的に基板の上にその要素を形成することも含む可能性がある。

【図4A】

【図4B】

【図4C】

【図4D】

S III

【図4M】

【図5A】

【図4N】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

#### 【国際調査報告】

# INTERNATIONAL SEARCH REPORT international application No PCT/US2016/037436 A. CLASSIFICATION OF SUBJECT MATTER INV. H01L29/423 H01L29/66 H01L29/788 H01L27/115 ADD. According to International Patent Classification (IPC) or to both national classification and IPC B. FIELDS SEARCHED Minimum documentation searched (classification system followed by classification symbols) H01L Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) EPO-Internal, WPI Data C. DOCUMENTS CONSIDERED TO BE RELEVANT Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. Category\* US 6 861 698 B2 (WANG CHIH HSIN [US]) 1 March 2005 (2005-03-01) 1-5 paragraphs [0090] - [0095], [0140] -[0154]; figures 3Q-3U, 23A-23R US 2015/072489 A1 (BAKER JR FRANK K [US] 1-9 ET AL) 12 March 2015 (2015-03-12) paragraphs [0006], [0048] - [0051]; figures 14-17 US 2014/264538 A1 (YU TEA-KWANG [KR] ET 6-9 AL) 18 September 2014 (2014-09-18) paragraphs [0154] - [0200]; figures 19-32 X See patent family annex. Further documents are listed in the continuation of Box C. Special categories of cited documents : later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention "A" document defining the general state of the art which is not considered to be of particular relevance "E" earlier application or patent but published on or after the international "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as epecified) document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art "O" document referring to an oral disclosure, use, exhibition or other document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of the actual completion of the international search Date of mailing of the international search report 17/10/2016 6 October 2016 Name and mailing address of the ISA/ Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016 Ley, Marc

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No PCT/US2016/037436

|                                           |    |                     | PCT/US2016/037436 |                                              |                   |                                                      |

|-------------------------------------------|----|---------------------|-------------------|----------------------------------------------|-------------------|------------------------------------------------------|

| Patent document<br>cited in search report |    | Publication<br>date |                   | Patent family<br>member(s)                   |                   | Publication<br>date                                  |

| US 6861698                                | B2 | 01-03-2005          | NONE              |                                              |                   |                                                      |

| US 2015072489                             | A1 | 12-03-2015          | NONE              |                                              |                   |                                                      |

| US 2014264538                             | A1 | 18-09-2014          | KR 20<br>TW       | 10405134<br>14011299<br>20143622<br>01426453 | 8 A<br>6 A<br>4 A | 17-09-2014<br>24-09-2014<br>16-09-2014<br>18-09-2014 |

|                                           |    |                     |                   | U1420453                                     |                   | 18-09-2014                                           |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

|                                           |    |                     |                   |                                              |                   |                                                      |

Form PCT/ISA/210 (patent family annex) (April 2005)

#### フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,ST,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,RS,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(74)代理人 100067013

弁理士 大塚 文昭

(74)代理人 100086771

弁理士 西島 孝喜

(74)代理人 100109070

弁理士 須田 洋之

(74)代理人 100109335

弁理士 上杉 浩

(74)代理人 100120525

弁理士 近藤 直樹

(74)代理人 100121979

弁理士 岩崎 吉信

(72)発明者 ス チエン・シェン

アメリカ合衆国 カリフォルニア州 95070 サラトガ カークモント ドライヴ 2030 ο

(72)発明者 ヤン ジェン・ウェイ

台湾 302 シンジュー カウンティー チューペイ シティー チュアンジン サード ロード ナンバー 48 1エフ

(72)発明者 チョウ フェン

アメリカ合衆国 カリフォルニア州 94536 フリーモント ベルデン テラス 3238 アパートメント #124

F ターム(参考) 5F083 EP02 EP23 EP30 EP33 EP36 ER18 GA11 GA27 JA03 JA06

JA56 KA01 KA05 MA06 MA16 MA19 MA20 NA01 PR07 PR40

5F101 BA01 BB05 BB09 BD02 BD22 BD35 BE02 BE06 BF02 BH21