**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) . Int. Cl.

*G05F 3/04* (2006.01)

(11) 공개번호 10-2007-0009703

(43) 공개일자 2007년01월18일

(21) 출원번호 10-2006-7023739

(22) 출원일자 2006년11월13일

심사청구일자     없음

번역문 제출일자 2006년11월13일

(86) 국제출원번호 PCT/US2005/012390

국제출원일자 2005년04월13일

(87) 국제공개번호 WO 2005/114350

국제공개일자 2005년12월01일

(30) 우선권주장 10/843,805     2004년05월12일     미국(US)

(71) 출원인     프리스케일 세미컨덕터, 인크.

미합중국 텍사스 (우편번호 78735) 오스틴 월리암 캐논 드라이브 웨스트 6501

(72) 발명자     밀러, 아이라 쥐.

미국 85283 아리조나조 템피 사우쓰 헤더 드라이브 5630

톰센, 브래트 제이.

미국 75214 텍사스주 달拉斯 윈스테드 드라이브 넘버4302 2208

밸라르드, 주니어., 에드아르도

미국 85225 아리조나주 챔들러 이스트 휘튼 플레이스 1405

(74) 대리인     주성민

이종희

백만기

전체 청구항 수 : 총 21 항

**(54) 전압 조정을 수행하는 회로**

**(57) 요약**

회로(10, 100)는 전압 조정을 수행하는데 사용된다. 일 실시예에서, 전압 조정기(11)는 제1 노드(30)로부터 제2 노드(28)로의 전압 강하를 조정하기 위해 동작하는 회로(10)를 형성하기 위해 출력 트랜지스터(24)와 함께 사용된다. 이러한 제2 노드(28)는 회로(27)에 전력을 제공하기 위해 사용될 수 있다. 회로(10) 내의 몇몇 트랜지스터(20-25)의 면적은 음 및 양의 온도 계수가 균형을 이루어 회로(10)가 전압 및 온도의 범위에 대해 원하는대로 동작하도록 조정될 수 있다. 일 실시예에서, 회로(100)는 2 단자 장치이다.

**대표도**

도 1

**특허청구의 범위**

### 청구항 1.

제1 출력 단자를 갖는 회로에 있어서,

전력 공급 단자에 연결된 입력과, 출력을 갖는 제1 전류 소스와,

상기 전력 공급 단자에 연결된 입력과, 출력을 갖는 제2 전류 소스와,

상기 제1 전류소스의 출력에 연결되는 제1 전류 전극 및 제어 전극과, 상기 제1 출력 단자에 연결된 제2 전류 전극을 갖는 제1 트랜지스터와,

상기 제2 전류 소스의 출력에 연결된 제1 전류 전극과, 상기 제1 트랜지스터의 제어 전극에 연결된 제어 전극과, 제2 전류 전극을 갖는 제2 트랜지스터와,

상기 제2 트랜지스터의 제2 전류 전극에 연결된 제1 단자와, 상기 제1 출력 단자에 연결된 제2 단자를 갖는 임피던스와,

전력 공급 단자에 연결된 제1 전류 전극과, 상기 제2 트랜지스터의 제1 전류 전극에 연결된 제어 전극, 및 상기 제1 출력 단자에 연결된 제2 전류 전극을 갖는 제3 트랜지스터

를 포함하는 회로.

### 청구항 2.

제1항에 있어서,

상기 제1, 제2, 및 제3 트랜지스터는 MOS 트랜지스터인 회로.

### 청구항 3.

제2항에 있어서,

상기 제1, 제2, 및 제3 트랜지스터는 N 채널 트랜지스터인 회로.

### 청구항 4.

제1항에 있어서,

상기 제1, 제2, 및 제3 트랜지스터는 바이폴라 트랜지스터인 회로.

### 청구항 5.

제4항에 있어서,

상기 바이폴라 트랜지스터는 NPN 트랜지스터인 회로.

### 청구항 6.

제1항에 있어서,

상기 제1 및 제2 전류 소스는 MOS 트랜지스터인 회로.

### 청구항 7.

제1항에 있어서,

상기 제1 전류 소스는 상기 전력 공급 단자에 연결된 제1 전류 전극을 갖는 제1 전류 소스 트랜지스터와, 상기 제1 트랜지스터의 제1 전류 소스에 연결된 제2 전류 소스와, 상기 제1 출력 단자에 연결된 제어 전극을 포함하고,

상기 제2 전류 소스는 상기 전력 공급 단자에 연결된 제1 전류 전극을 갖는 제2 전류 트랜지스터와, 상기 제2 트랜지스터의 제1 전류 소스에 연결된 제2 전류 소스와, 상기 제1 출력 단자에 연결된 제어 전극을 포함하는 회로.

### 청구항 8.

제1항에 있어서,

상기 제1 및 제2 전류 소스는, 상기 제1 출력 단자에서의 전압 감소에 응답하여, 더 많은 전류를 공급하는 회로.

### 청구항 9.

제1항에 있어서,

상기 임피던스는 MOS 트랜지스터를 포함하는 회로.

### 청구항 10.

제9항에 있어서,

상기 MOS 트랜지스터는 상기 제2 트랜지스터의 제2 전류 전극에 연결된 제1 단자로서의 제1 전류 전극과, 상기 제1 출력 단자에 연결된 제2 단자로서의 제2 전류 전극과, 접지 단자에 연결된 게이트를 포함하는 회로.

### 청구항 11.

제1항에 있어서,

상기 제3 트랜지스터의 제어 전극에 연결된 제1 단자 및 상기 제1 출력 단자에 연결된 제2 단자를 갖는 용량성 소자를 더 포함하는 회로.

### 청구항 12.

제1항에 있어서,

제2 출력 단자를 가지고,

제1 출력 단자에 연결된 입력과, 출력을 갖는 제3 전류 소스와,

상기 제1 출력 단자에 연결된 입력과, 출력을 갖는 제4 전류 소스와,

상기 제3 전류 소스의 출력에 연결된 제1 전류 전극 및 제어 전극과, 상기 제2 출력 단자에 연결된 제2 전류 전극을 갖는 제4 트랜지스터와,

상기 제4 전류 소스의 출력에 연결된 제1 전류 전극, 상기 제4 트랜지스터의 제어 전극에 연결된 제어 전극과, 제2 전류 전극을 갖는 제5 트랜지스터와,

상기 제5 트랜지스터의 제2 전류 전극에 연결된 제1 단자와, 상기 제2 출력 단자에 연결된 제2 단자를 갖는 제2 임피던스와,

상기 제1 출력 단자에 연결된 제1 전류 전극과, 상기 제4 트랜지스터의 제1 전류 전극에 연결된 제어 전극과, 상기 제2 출력 단자에 연결된 제2 전류 전극을 갖는 제6 트랜지스터

를 포함하는 회로.

### 청구항 13.

제1 출력 단자를 갖는 회로에 있어서,

전력 공급 단자와 상기 출력 단자 사이에 연결되어 기준 전압을 제공하는 조정기 회로와,

전력 공급 단자에 연결된 제1 전류 전극과, 상기 기준 전압을 수신하는 제어 전극과, 상기 제1 출력 단자에 연결된 제2 전류 전극을 갖는 출력 트랜지스터

를 포함하고,

상기 조정기 회로에 의해 수신되는 모든 전류는 상기 제1 출력 단자를 통과하는 회로.

### 청구항 14.

제13항에 있어서,

상기 조정기는 동일한 전류를 각각 제공하는 한 쌍의 전류 소스를 포함하는 회로.

### 청구항 15.

제14항에 있어서,

상기 동일한 전류는 상기 제1 출력 단자에서의 전압의 감소에 응답하여 증가하는 회로.

### 청구항 16.

제13항에 있어서,

상기 조정기는 상기 제1 출력 단자에서의 전압의 감소에 응답하여 상기 기준 전압을 증가시키는 회로.

### 청구항 17.

제13항에 있어서,

상기 조정기는,

전력 공급 단자에 연결된 입력과, 출력을 갖는 제1 전류 소스와,

상기 전력 공급 단자에 연결된 입력과, 출력을 갖는 제2 전류 소스와,

상기 제1 전류 소스의 출력에 연결된 제1 전류 전극 및 제어 전극과, 상기 출력 단자에 연결된 제2 전류 전극을 갖는 제1 트랜지스터와,

상기 제2 전류 소스의 출력에 연결되어 상기 기준 전압을 제공하는 제1 전류 전극과, 상기 제1 트랜지스터의 제어 전극에 연결된 제어 전극과, 제2 전류 전극을 갖는 제2 트랜지스터와,

제2 트랜지스터의 제2 전류 전극에 연결된 제1 단자와 상기 제1 출력 단자에 연결된 제2 단자를 갖는 임피던스

를 포함하는 회로.

### 청구항 18.

제13항에 있어서,

제2 출력 단자를 갖고,

상기 제1 출력 단자와 상기 제2 출력 단자 사이에 연결되어 제2 기준 전압을 제공하는 제2 조정기 회로와,

상기 제1 출력 단자에 연결되는 제1 전류 전극과, 상기 제2 기준 전압을 수신하는 제어 전극과, 상기 제2 출력 단자에 연결된 제2 전류 전극을 갖는 제2 출력 트랜지스터

를 더 포함하고,

상기 제2 조정기 회로에 의해 수신된 모든 전류는 상기 제2 출력 단자를 통과하는 회로.

### 청구항 19.

제1 단자를 갖는 회로에 있어서,

기준 전압을 구축하기 위해 기준 전류 - 상기 기준 전류는 출력 단자에서의 전압의 감소에 응답하여 증가함 - 를 구축하는 전류 미러와,

상기 기준 전류를 전달하고 온도의 증가와 함께 크기가 감소되는 임피던스와,

상기 기준 전압을 수신하고 상기 출력 단자에서 출력 전류를 제공하는 출력 트랜지스터

를 포함하는 회로.

## 청구항 20.

제19항에 있어서,

상기 전류 미러는,

전력 공급 단자에 연결된 입력과, 출력을 갖는 제1 전류 소스와,

상기 전력 공급 단자에 연결된 입력과, 출력을 갖는 제2 전류 소스와,

상기 제1 전류 소스의 출력에 연결되는 제1 전류 전극 및 제어 전극과, 상기 제1 출력 단자에 연결되는 제2 전류 전극을 갖는 제1 트랜지스터와,

상기 기준 전압을 제공하기 위해 상기 전류 소스의 출력에 연결되는 제1 전류 전극과, 상기 제1 트랜지스터의 제어 전극에 연결된 제어 전극과, 상기 임피던스에 연결된 제2 전류 전극을 갖는 제2 트랜지스터

를 포함하는 회로.

## 청구항 21.

제19항에 있어서,

제2 기준 전압을 구축하기 위해 제2 기준 전류 – 상기 제2 기준 전류는 상기 제2 출력 단자에서의 전압의 감소에 응답하여 증가함 – 를 구축하는 제2 전류 미러와,

상기 제2 기준 전류를 전달하고, 온도의 감소와 함께 크기가 감소하는 제2 임피던스와,

상기 제2 기준 전압을 수신하고 상기 제2 출력 단자에서 제2 출력 전류를 제공하는 제2 출력 트랜지스터

를 더 포함하는 회로.

### 명세서

#### 기술분야

본 발명은 전반적으로 회로에 관한 것으로, 특히, 전압 조정(voltage regulation)을 수행하는 회로에 관한 것이다.

#### 배경기술

레이아웃 밀도(layout density)의 증가로 인해 전자 회로의 동작 전압이 감소함에 따라, 전력 공급 전압(power supply voltage)은 동일하게 유지되지만 전자 회로의 동작 전압(operating voltage)은 낮추어져야만 하는 어플리케이션의 수가 점점 증가하게 되었다. 그러나, 어플리케이션이 배터리 전력에 점점 더 의존하게 될수록, 전자 회로에 의해 사용되는 전력도 낮아져야 한다. 따라서, 가능한 낮은 전력을 사용하여 전압 조정을 수행하는 회로가 요구된다.

#### 발명의 상세한 설명

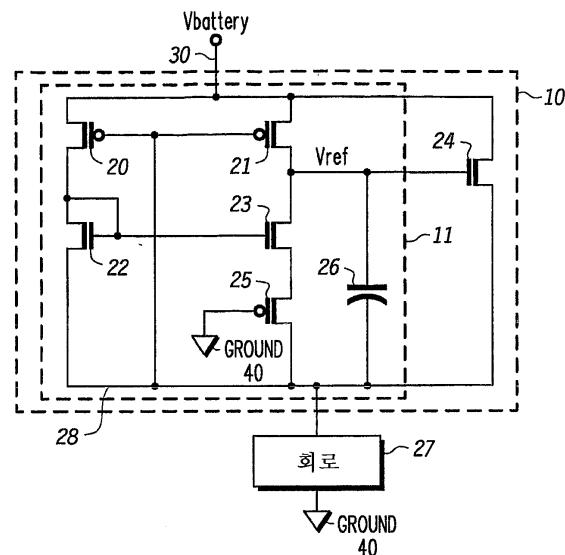

도 1은 전계 효과 트랜지스터(field effect transistors)(20–25)를 포함하는 본 발명의 일 실시예에 따른 회로(10)를 구성 도 형태로 나타낸 것이다. 회로(10)의 제1 단자는 노드(30)에 연결되고, 회로(10)의 제2 단자는 노드(28)에 연결된다. 제1 전력 공급 전압(예를 들어, Vbattery)은 노드(30)에 연결되고, 회로(27)는 노드(28)에 연결된다. 또한, 회로(27)는 제2 전력 공급 전압(40)(예를 들어, 접지(ground))에 연결된다. p 채널 트랜지스터(20)의 제1 전류 전극, p 채널 트랜지스터(21)의 제1 전류 전극, n 채널 트랜지스터(24)의 제1 전류 전극은 모두 노드(30)에 연결된다. 트랜지스터(20)의 제어 전극 및 트랜지스터(21)의 제어 전극은 모두 노드(28)에 연결된다. 트랜지스터(20)의 제2 전류 전극은 n 채널 트랜지스터(22)의

제1 전류 전극, 트랜지스터(22)의 제어 전극, 및 n 채널 트랜지스터(23)의 제어 전극에 연결된다. 트랜지스터(21)의 제2 전류 전극은 트랜지스터(23)의 제1 전류 전극, n 채널 트랜지스터(24)의 제어 전극, 및 용량성 소자(capacitive element)(26)의 제1 단자에 연결된다. 트랜지스터(23)의 제2 전류 전극은 p 채널 트랜지스터(25)의 제1 전류 전극에 연결된다. 트랜지스터(25)의 제어 전극은 제2 전력 공급 전압에 연결되고, 트랜지스터(25)의 제2 전류 전극은 노드(28)에 연결된다. 또한, 노드(28)는 트랜지스터(22)의 제2 전류 전극, 용량성 소자(26)의 제2 단자, 및 트랜지스터(24)의 제2 전류 전극에 연결된다.

도 1을 참조하면, 회로(10)는 트랜지스터(20, 21, 22, 23 및 25)를 도통하는 모든 전류 대략 같도록 동작된다. 트랜지스터(23)는 트랜지스터(22)보다 더 넓은 에리어와이즈(area-wise)를 가지기 때문에, 트랜지스터(23)는 트랜지스터(22)보다 더 작은  $V_{gs}$ 를 가질 것이다. 이는  $\Delta V_{gs}$ 가 트랜지스터(22 및 23) 사이에서 발현되도록 행해진다. 동일한 전류에 있어서, 트랜지스터(22)의  $V_{gs}$ 는 트랜지스터(23)의  $V_{gs}$ 보다 더 클 것이다. 또한, 여기에 사용된 바와 같이,  $\Delta V_{gs}$ 는 트랜지스터(22)의 게이트-소스 전압과 트랜지스터(23)의 게이트-소스 전압의 차를 나타낼 것이다. 또한,  $\Delta V_{gs}$ 는 트랜지스터(25) 양단에 나타나는 전압일 것이다. 트랜지스터(25)의 면적은 트랜지스터(25)를 도통하는 전류가 대략 트랜지스터(20, 21, 22 및 23)을 도통하는 전류와 같도록 조정될 것이다.

트랜지스터(21) 양단에 나타나는 전압(이하, 'V21')은 ( $\Delta V_{gs}$ /트랜지스터(25)의 채널 저항)\*(트랜지스터(21)의 채널 저항)과 거의 같을 것이다.  $V_{21+}$ (트랜지스터(24)의  $V_{gs}$ )는  $V_{battery}$ 와 노드(28)에서의 전압 사이의 전압과 대략 같을 것이라는 점을 유의해야 한다.  $V_{battery}$ 와 노드(28)에서의 전압 사이의 전압(이하, 'Vdrop')은 회로(10)를 제조하는데 사용되는 반도체 재료의 밴드갭 전압과 대략 같을 것이다. 실리콘의 경우, 밴드갭 전압은 대략 1.1V이다. 따라서, 실리콘 내에 형성되는 회로(10)에 대한  $V_{drop}$ 은 대략 1.1V이다. 회로(10)를 형성하기 위해 사용되는 제조 공정의 특성과 회로(10)의 희망 전압 및 온도 특성에 기인한 회로(10)의 동작을 조정하기 위해  $V_{drop}$ 은 밴드갭 전압과는 의도적으로 다르게 될 수 있다. 또한,  $V_{drop}$ 은 트랜지스터(24) 양단에 나타나는 전압 강하임에 유의해야 한다.

따라서, 회로(10)는  $V_{battery}$ 와 회로(27) 사이에 전압 강하를 생성한다. 이것은 회로(27)에 대한 안전한 동작 전압이  $V_{battery}$  전압 미만인 어플리케이션에 매우 유용하다. 예를 들어, 많은 스마트 카드 어플리케이션(smart card application) 및 핸드헬드 게임(handheld game)은 안전한 회로(27)의 동작 전압보다 더 높은 1V 이상의 고가 배터리를 사용한다. 따라서, 전력 공급 전압(가령,  $V_{battery}$ )과 회로(27)의 동작 전압 사이에 원하는 양만큼의 전압 강하를 제공하는 회로(10)를 사용할 필요성이 있다. 전력 공급 전압  $V_{battery}$ 를 배터리 전압으로서 나타내긴 했지만, 본 발명의 다른 실시 예에서는 전력 공급 전압을 제공하는 임의의 소스를 사용할 수도 있다. 배터리는 단지 가능한 전력 공급 소스의 일 예이다. 회로(27)는  $V_{battery}$  이하의 전력 공급 전압에서 동작할 수 있는 임의의 유형의 회로일 수 있다. 몇몇 실시 예에서, 회로(27)는  $V_{battery}$ 보다 높은 전압에서 기능할 수 있지만, 회로(27)에 의해 사용되는 전력을 줄이기 위해 또는 회로(27)에 의해 분산되는 열을 줄이기 위해, 노드(28)에서의  $V_{battery}$  또는 그보다 작은 전압이 전력 회로(27)에 사용될 수 있다.

본 발명의 일 실시 예에서, 캐패시터(26)는 회로(10)를 안정화시키는데 사용된다. 트랜지스터(24)의 게이트에서의 전압이 감소할 경우, 트랜지스터(24)의  $V_{gs}$ 는 감소한다는 점에 유의해야 한다. 그리고 나면, 노드(28)에서의 전압은 증가(즉,  $V_{battery}$ 를 향해 이동)하여 할 것이다. 그 결과, 트랜지스터(23)는 보다 적은 전류를 전도할 것이고, 이에 따라, 보다 적은 전류가 트랜지스터(21)를 도통할 것이다. 결과적으로, 트랜지스터(24)의 게이트에서의 전압은 증가할 것이다. 따라서, 트랜지스터(24)의 게이트에서의 전압은, 트랜지스터(23, 24, 25)를 통한 위상이  $180^\circ$ 를 향해 증가할 경우, 천천히 진동하거나 감쇠될 것이다. 트랜지스터(24)의 게이트에서의 전압의 이러한 진동은 일반적으로는 바람직하지 못한 것이고, 특히 고주파수(예를 들어, 1MHz 이상)에서 잘 나타날 수 있다. 회로(10)는 일반적으로 1MHz 미만의 주파수에서 DC(Direct Current) 까지 아래로 동작하도록 의도되었다. 본 발명의 또 다른 실시 예는 캐패시터(26)를 사용하지 않을 수 있다. 본 발명의 다른 실시 예는 회로(10)의 동작을 안정화시키기 위해서 다른 방법 및 회로 소자를 사용할 수 있다.

도 1에 도시된 회로(10)의 일 실시 예에 있어서, 트랜지스터(22, 23, 24)는 게이트-소스 전압이 트랜지스터의 스레시홀드 전압(threshold voltage) 미만인 서브스레시홀드 범위(subthreshold range) 내에서 동작한다. 트랜지스터의 스레시홀드 전압( $V_t$ )은 트랜지스터가 "턴 온(turn on)"되어 전도 가능한 상태가 되는 전압이다. 일 실시 예에서, 트랜지스터(20, 21)는 서브스레시홀드 범위 내에서 동작하는 것은 아니다. 그러나, 다른 실시 예는 서브스레시홀드 범위 내에서 트랜지스터(20, 21)를 동작시킬 수 있다. 전계 효과 트랜지스터(가령, 22, 23, 24)를 서브스레시홀드 범위 내에서 동작시키는 것은, 전계 효과 트랜지스터의 게이트-소스 전압이 바이폴라 트랜지스터의 베이스-에미터 전압과 유사한 방식으로 동작하도록 한다.

노드(28)에서의 전압을 광범위한 온도의 범위에서 비교적 일정하게 유지하는 것이 종종 바람직하다. 따라서,  $V_{drop}(28)$ 을 광범위한 온도의 범위에서 비교적 일정하게 유지하는 것이 바람직하다. 일 실시 예에서, 이는 회로(10)의 제1 부분이 양의 온도 계수를 가지고도록 하는 반면, 회로(10)의 제2 부분은 음의 온도 계수를 가지고도록 함으로써 달성될 수 있다. 회로(10)의 일 실시 예에 있어서, 트랜지스터(24)의 게이트-소스 전압은 음의 온도 계수를 가진다(즉, 트랜지스터(24)의  $V_{gs}$ 는 온도가

증가함에 따라 감소함). 이를 오프셋(offset)하기 위해, 트랜지스터(21)의 소스-드레인 전압은 양의 온도 계수를 가진다 (즉, 트랜지스터(21)의  $V_{sd}$ 는 온도가 증가함에 따라 증가함). 트랜지스터(22, 23)의 게이트-소스 전압 사이의 차( $\Delta V_{gs}$ )는 대략  $(KT/q) * \ln(\text{트랜지스터}(23)/\text{트랜지스터}(22))$ 이고, 여기서 T는 켈빈 온도이고 K 및 q는 공지된 상수이다. 트랜지스터(21)의  $V_{sd}$ 의 양의 온도 계수는 트랜지스터(23, 22) 사이의  $\Delta V_{gs}$ 의 함수임을 유의해야 한다. 따라서, 음과 양의 온도 계수의 결합은 서로를 오프셋시키고, 회로(10)에 대한 실효과(net effect)는 온도에 대해 안정적이다.

희망 범위 내에 있는, 노드(30)로부터 노드(28)로의 전압 강하( $V_{drop}$ )를 달성하기 위해, 트랜지스터(22, 23)의 면적 비(area ratios), 트랜지스터(21, 25)의 면적 비, 및 트랜지스터(24)의 면적이 조정될 수 있다. 이러한 희망 범위는 통상 밴드갭 전압(실리콘의 경우 1.1V) 주변에 집중된다. 본 발명의 다른 실시예는, 밴드갭 전압보다 상당히 많거나 적은 전압을 포함하는,  $V_{drop}$ 에 대한 소정의 희망 범위를 사용할 수 있다. 따라서, 트랜지스터(22, 23)의 면적 비, 트랜지스터(21, 25)의 면적 비, 및 트랜지스터(24)의 면적을 변경시킴으로써, 온도에 대한 회로(10)의 동작이 변경될 수 있다.

본 발명의 일 실시예에 있어서, 트랜지스터(25)는 회로(10)에 대해 임피던스를 제공하도록 기능한다. 트랜지스터(20, 21)는 각각 회로(10)에 대한 전류 소스로서 기능한다. 트랜지스터(24)는, 회로(27)가 더 높은 양의 전류를 유입하는 경우, 회로(27)에 상당한 양의 전류를 제공할 수 있는 출력 트랜지스터로서 기능한다. 트랜지스터(24)의 게이트에서의 전압은 기준 전압으로 지칭될 수 있다. 조정기 회로(11)와 출력 트랜지스터(24)는 함께 전압 조정 회로(10)를 형성한다. 조정기 회로(11)는 트랜지스터(20, 21, 22, 23, 25)뿐만 아니라, 용량성 소자(26)도 포함한다. 트랜지스터(24)의 제어 전극에서의 전압은  $V_{ref}$ 로 명명되고 출력 트랜지스터(24)에 기준 전압을 제공한다.

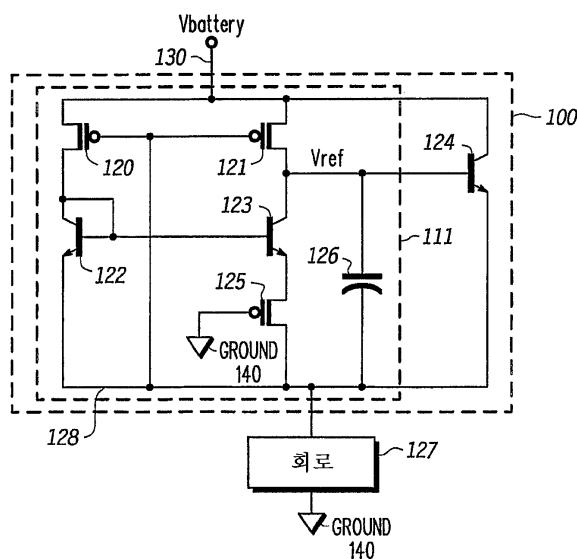

도 2는 본 발명의 다른 실시예에 따른 회로(100)를 구성도 형태로 나타내고 있다. 회로(100)의 제1 단자는 노드(130)에 연결되고, 회로(100)의 제2 단자는 노드(128)에 연결된다. 제1 전력 공급 전압(예를 들어,  $V_{battery}$ )은 노드(130)에 연결되고, 회로(127)는 노드(128)에 연결된다. 또한, 회로(127)는 제2 전력 공급 전압(40)(예를 들어, 접지(ground))에 연결된다. p 채널 트랜지스터(120)의 제1 전류 전극, p 채널 트랜지스터(121)의 제1 전류 전극, 및 바이폴라 트랜지스터(124)의 제1 전류 전극은 모두 노드(130)에 연결된다. 트랜지스터(120)의 제어 전극과 트랜지스터(121)의 제어 전극은 모두 노드(128)에 연결된다. 트랜지스터(120)의 제2 전류 전극은 바이폴라 트랜지스터(122)의 제1 전류 전극, 트랜지스터(122)의 제어 전극, 및 바이폴라 트랜지스터(123)의 제어 전극에 연결된다. 트랜지스터(121)의 제2 전류 전극은 트랜지스터(123)의 제1 전류 전극, 바이폴라 트랜지스터(124)의 제어 전극, 및 용량성 소자(126)의 제1 단자에 연결된다. 트랜지스터(123)의 제2 전류 전극은 p 채널 트랜지스터(125)의 제1 전류 전극에 연결된다. 트랜지스터(125)의 제어 전극은 제2 전력 공급 전압에 연결되고, 트랜지스터(125)의 제2 전류 전극은 노드(128)에 연결된다. 또한, 노드(128)는 트랜지스터(122)의 제2 전류 전극, 용량성 소자(126)의 제2 단자, 및 트랜지스터(124)의 제2 전류 전극에 연결된다.

본 발명의 일 실시예에 있어서, 트랜지스터(125)는 회로(100)에 임피던스를 제공하는 기능을 한다. 트랜지스터(120, 121)는 각각 회로(100)에 대한 전류 소스로서 기능한다. 트랜지스터(124)는, 회로(127)가 더 높은 양의 전류를 유입하는 경우, 상당한 양의 전류를 회로(127)에 제공할 수 있는 출력 트랜지스터로서 기능한다. 트랜지스터(124)의 게이트에서의 전압은 기준 전압으로 지칭될 수 있다. 조정기 회로(111) 및 출력 트랜지스터(124)는 함께 전압 조정 회로(100)를 형성한다. 조정기 회로(111)는 트랜지스터(120, 121, 122, 123, 125)뿐만 아니라, 용량성 소자(126)를 포함한다. 트랜지스터(124)의 제어 전극에서의 전압은  $V_{ref}$ 라 명명되고 출력 트랜지스터(124)에 기준 전압을 제공한다.

도 1 및 도 2를 참조하여, 일 실시예에 있어서, 회로(100)는, 회로(10)의 전계 효과 트랜지스터(22, 23, 24)가 바이폴라 트랜지스터(122, 123, 124)로 대체되었다는 점에서, 회로(10)와 상이하다. 본 발명의 일 실시예에서, 바이폴라 트랜지스터(122-125)는 npn 바이폴라 트랜지스터로 구현될 수 있다. 본 발명의 다른 실시예는, 대안적으로 선택된 n 채널 트랜지스터 대신에 p 채널 트랜지스터를 사용고, 선택된 p 채널을 위해 n 채널 트랜지스터를 사용하고, 및/또는 선택된 npn 바이폴라 트랜지스터 대신에 pnp 바이폴라 트랜지스터를 사용할 수 있다. 본 발명의 몇몇 실시예에서, 회로(10)는 회로(27)와 제2 전력 공급 전압(40, 140)(가령, ground) 사이에 사용될 수 있다. 도 2의 회로(100)는 도 1의 회로(10)와 유사한 방식으로 동작하는데, 여기서 바이폴라 트랜지스터(122-124)는 통상의 npn 바이폴라 트랜지스터와 같이 동작한다. 바이폴라 트랜지스터(122-124)의  $V_{be}$ 는 도 1의 트랜지스터(22-24)의 전계 효과 트랜지스터의  $V_{gs}$ 의 서브스레시홀드와 유사하게 동작한다.

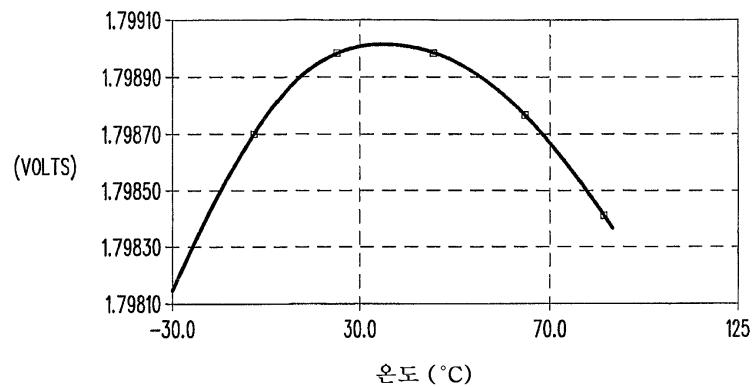

도 3은 본 발명의 일 실시예에 따른 도 1의 회로에 있어서의 전압-온도 곡선을 그래프 형태로 나타낸 것이다(제조 공정 파라미터에 어떤 변화도 없다고 가정함). 도시된 전압은 제2 전력 공급 전압(가령, ground)에 대한 노드(28)에서의 전압(도 1 참고)이다. 전압은 매우 넓은 온도 범위(-30°C 내지 125°C)에 대해 거의 변하지 않는다(도시된 그래프에서 대략 1mV만 변함). 다른 실시예는, 어떤 온도 범위가 요구되더라도, 노드(28)의 전압을 변경시키기 위해 회로(10)의 파라미터(가령, 트랜지스터의 크기, 제조 공정 파라미터)를 변화시킬 수 있다.

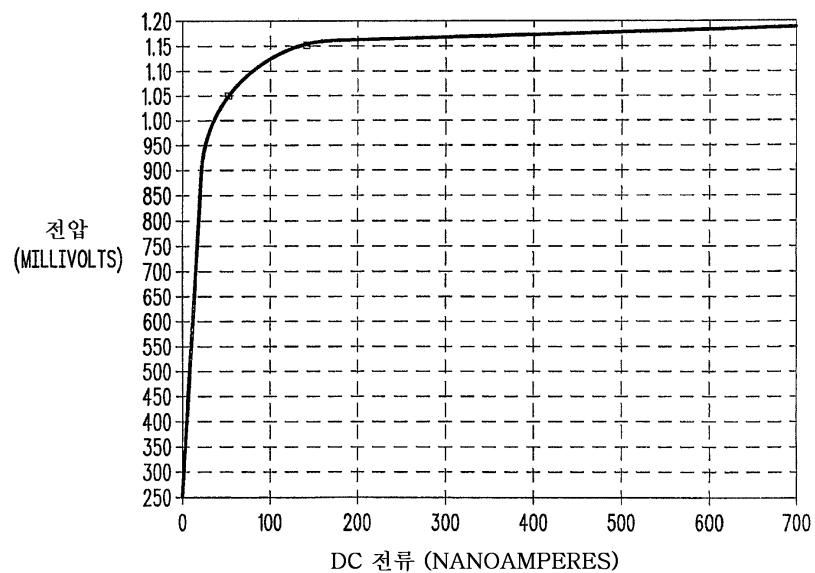

도 4는 본 발명의 일 실시예에 따른 도 1의 회로에 대한 전압-전류 곡선을 그래프 형태로 나타낸 것이다. 도시된 전압은 노드(30)로부터 노드(28)까지의 전압 강하 Vdrop이다(도 1 참고). 도시된 전류는 회로(10)로부터 회로(27)로 제공되는 전류이다. Vdrop은 매우 안정되어 있고 150nm의 전류 레벨에 도달하고 나면 거의변화가 없다. 따라서, 회로(10)는 제1 전력 공급 전압(Vbattery)과 노드(28)에서의 회로(27)에 제공되는 전압 사이에 안정된 전압 강하를 제공한다.

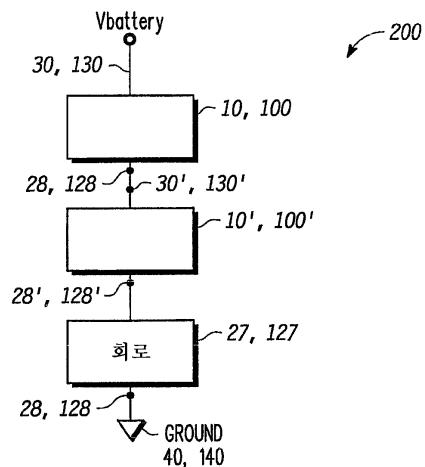

도 5는 본 발명의 일 실시예에 따른 회로(200)의 블럭도이다. 제1 전력 공급 전압(Vbattery)(30, 130)과 회로(27, 127) 사이에 보다 넓은 전압 강하를 제공하기 위해 복수의 회로(10) 또는 회로(100)는 직렬로 배치될 수 있다. 임의의 수의 회로(10, 100)가 직렬로 배치될 수 있다. 또한, 임의의 조합의 회로(10, 100)가 직렬로 사용될 수 있다. 참조 번호 10', 30' 및 28'은 도 1의 회로(10)의 제2 예를 나타낸다. 참조 번호 100', 130', 및 128은 도 2의 회로(100)의 제2 예를 나타낸다. 또한, 다른 실시예는 회로(10, 100)의 복수의 예가 회로(27, 127)와 제2 전력 공급 전압(40, 140)(가령, ground) 사이에 배치되도록 이동할 수 있다.

비록 본 발명이 특정 전도성 유형(conductivity types) 또는 포텐셜의 극성(polarity of potentials)에 대해 기술되었지만, 당업자는 전도성 유형 및 포텐셜의 극성이 반대로 될 수 있음을 이해할 것이다.

상술한 명세서에서, 본 발명은 특정 실시예에 대하여 기술하였다. 그러나, 당업자는 이하의 청구범위에 개시된 본 발명의 범주를 벗어남이 없이 다양한 변형 및 변경이 이루어질 수 있다는 점을 이해할 것이다. 따라서, 명세서 및 도면은 제한적인 의미라기보다는 설명을 위한 것이며, 그러한 모든 변경은 본 발명의 범주 내에 포함되도록 의도되었음이 이해되어야 할 것이다.

이점, 다른 이익, 및 문제에 대한 해결책은 특정 실시예에 대해 상술되었다. 그러나, 이점, 이익, 문제에 대한 해결책과, 임의의 이익, 이점 또는 해결책이 보다 분명히 되도록 하는 임의의 소자는 청구항의 일부 또는 전부의 중요한, 요구되는, 필수의 특징 또는 요소로서 해석될 수 있다. 여기서 사용된, "포함한다", "포함하는"이라는 용어 또는 임의의 다른 방법, 아티클, 또는 소자의 리스트를 포함하는 장치는 이들 소자뿐만 아니라 그러한 공정, 방법, 아티클, 또는 장치에 명시적으로 리스트되지 않은 다른 소자를 포함할 수 있다.

#### 부가 텍스트

##### [청구항 1]

제1 출력 단자를 갖는 회로에 있어서,

전력 공급 단자에 연결된 입력과, 출력을 갖는 제1 전류 소스와,

상기 전력 공급 단자에 연결된 입력과, 출력을 갖는 제2 전류 소스와,

상기 제1 전류소스의 출력에 연결되는 제1 전류 전극 및 제어 전극과, 상기 제1 출력 단자에 연결된 제2 전류 전극을 갖는 제1 트랜지스터와,

상기 제2 전류 소스의 출력에 연결된 제1 전류 전극과, 상기 제1 트랜지스터의 제어 전극에 연결된 제어 전극과, 제2 전류 전극을 갖는 제2 트랜지스터와,

상기 제2 트랜지스터의 제2 전류 전극에 연결된 제1 단자와, 상기 제1 출력 단자에 연결된 제2 단자를 갖는 임피던스와,

전력 공급 단자에 연결된 제1 전류 전극과, 상기 제2 트랜지스터의 제1 전류 전극에 연결된 제어 전극, 및 상기 제1 출력 단자에 연결된 제2 전류 전극을 갖는 제3 트랜지스터

를 포함하는 회로.

##### [청구항 2]

제1항에 있어서,

상기 제1, 제2, 및 제3 트랜지스터는 MOS 트랜지스터인 회로.

[청구항 3]

제2항에 있어서,

상기 제1, 제2, 및 제3 트랜지스터는 N 채널 트랜지스터인 회로.

[청구항 4]

제1항에 있어서,

상기 제1, 제2, 및 제3 트랜지스터는 바이폴라 트랜지스터인 회로.

[청구항 5]

제4항에 있어서,

상기 바이폴라 트랜지스터는 NPN 트랜지스터인 회로.

[청구항 6]

제1항에 있어서,

상기 제1 및 제2 전류 소스는 MOS 트랜지스터인 회로.

[청구항 7]

제1항에 있어서,

상기 제1 전류 소스는 상기 전력 공급 단자에 연결된 제1 전류 전극을 갖는 제1 전류 소스 트랜지스터와, 상기 제1 트랜지스터의 제1 전류 소스에 연결된 제2 전류 소스와, 상기 제1 출력 단자에 연결된 제어 전극을 포함하고,

상기 제2 전류 소스는 상기 전력 공급 단자에 연결된 제1 전류 전극을 갖는 제2 전류 트랜지스터와, 상기 제2 트랜지스터의 제1 전류 소스에 연결된 제2 전류 소스와, 상기 제1 출력 단자에 연결된 제어 전극을 포함하는 회로.

[청구항 8]

제1항에 있어서,

상기 제1 및 제2 전류 소스는, 상기 제1 출력 단자에서의 전압 감소에 응답하여, 더 많은 전류를 공급하는 회로.

[청구항 9]

제1항에 있어서,

상기 임피던스는 MOS 트랜지스터를 포함하는 회로.

[청구항 10]

제9항에 있어서,

상기 MOS 트랜지스터는 상기 제2 트랜지스터의 제2 전류 전극에 연결된 제1 단자로서의 제1 전류 전극과, 상기 제1 출력 단자에 연결된 제2 단자로서의 제2 전류 전극과, 접지 단자에 연결된 게이트를 포함하는 회로.

[청구항 11]

제1항에 있어서,

상기 제3 트랜지스터의 제어 전극에 연결된 제1 단자 및 상기 제1 출력 단자에 연결된 제2 단자를 갖는 용량성 소자를 더 포함하는 회로.

[청구항 12]

제1항에 있어서,

제2 출력 단자를 가지고,

제1 출력 단자에 연결된 입력과, 출력을 갖는 제3 전류 소스와,

상기 제1 출력 단자에 연결된 입력과, 출력을 갖는 제4 전류 소스와,

상기 제3 전류 소스의 출력에 연결된 제1 전류 전극 및 제어 전극과, 상기 제2 출력 단자에 연결된 제2 전류 전극을 갖는 제4 트랜지스터와,

상기 제4 전류 소스의 출력에 연결된 제1 전류 전극, 상기 제4 트랜지스터의 제어 전극에 연결된 제어 전극과, 제2 전류 전극을 갖는 제5 트랜지스터와,

상기 제5 트랜지스터의 제2 전류 전극에 연결된 제1 단자와, 상기 제2 출력 단자에 연결된 제2 단자를 갖는 제2 임피던스와,

상기 제1 출력 단자에 연결된 제1 전류 전극과, 상기 제4 트랜지스터의 제1 전류 전극에 연결된 제어 전극과, 상기 제2 출력 단자에 연결된 제2 전류 전극을 갖는 제6 트랜지스터

를 포함하는 회로.

[청구항 13]

제1 출력 단자를 갖는 회로에 있어서,

전력 공급 단자와 상기 출력 단자 사이에 연결되어 기준 전압을 제공하는 조정기 회로와,

전력 공급 단자에 연결된 제1 전류 전극과, 상기 기준 전압을 수신하는 제어 전극과, 상기 제1 출력 단자에 연결된 제2 전류 전극을 갖는 출력 트랜지스터

를 포함하고,

상기 조정기 회로에 의해 수신되는 모든 전류는 상기 제1 출력 단자를 통과하는 회로.

[청구항 14]

제13항에 있어서,

상기 조정기는 동일한 전류를 각각 제공하는 한 쌍의 전류 소스를 포함하는 회로.

[청구항 15]

제14항에 있어서,

상기 통일한 전류는 상기 제1 출력 단자에서의 전압의 감소에 응답하여 증가하는 회로.

[청구항 16]

제13항에 있어서,

상기 조정기는 상기 제1 출력 단자에서의 전압의 감소에 응답하여 상기 기준 전압을 증가시키는 회로.

[청구항 17]

제13항에 있어서,

상기 조정기는,

전력 공급 단자에 연결된 입력과, 출력을 갖는 제1 전류 소스와,

상기 전력 공급 단자에 연결된 입력과, 출력을 갖는 제2 전류 소스와,

상기 제1 전류 소스의 출력에 연결된 제1 전류 전극 및 제어 전극과, 상기 출력 단자에 연결된 제2 전류 전극을 갖는 제1 트랜지스터와,

상기 제2 전류 소스의 출력에 연결되어 상기 기준 전압을 제공하는 제1 전류 전극과, 상기 제1 트랜지스터의 제어 전극에 연결된 제어 전극과, 제2 전류 전극을 갖는 제2 트랜지스터와,

제2 트랜지스터의 제2 전류 전극에 연결된 제1 단자와 상기 제1 출력 단자에 연결된 제2 단자를 갖는 임피던스.

[청구항 18]

제13항에 있어서,

제2 출력 단자를 갖고,

상기 제1 출력 단자와 상기 제2 출력 단자 사이에 연결되어 제2 기준 전압을 제공하는 제2 조정기 회로와,

상기 제1 출력 단자에 연결되는 제1 전류 전극과, 상기 제2 기준 전압을 수신하는 제어 전극과, 상기 제2 출력 단자에 연결된 제2 전류 전극을 갖는 제2 출력 트랜지스터

를 더 포함하고,

상기 제2 조정기 회로에 의해 수신된 모든 전류는 상기 제2 출력 단자를 통과하는 회로.

[청구항 19]

제1 단자를 갖는 회로에 있어서,

기준 전압을 구축하기 위해 기준 전류 - 상기 기준 전류는 출력 단자에서의 전압의 감소에 응답하여 증가함 - 를 구축하는 전류 미러와,

상기 기준 전류를 전달하고 온도의 증가와 함께 크기가 감소되는 임피던스와,

상기 기준 전압을 수신하고 상기 출력 단자에서 출력 전류를 제공하는 출력 트랜지스터

를 포함하는 회로.

[청구항 20]

제19항에 있어서,

상기 전류 미러는,

전력 공급 단자에 연결된 입력과, 출력을 갖는 제1 전류 소스와,

상기 전력 공급 단자에 연결된 입력과, 출력을 갖는 제2 전류 소스와,

상기 제1 전류 소스의 출력에 연결되는 제1 전류 전극 및 제어 전극과, 상기 제1 출력 단자에 연결되는 제2 전류 전극을 갖는 제1 트랜지스터와,

상기 기준 전압을 제공하기 위해 상기 전류 소스의 출력에 연결되는 제1 전류 전극과, 상기 제1 트랜지스터의 제어 전극에 연결된 제어 전극과, 상기 임피던스에 연결된 제2 전류 전극을 갖는 제2 트랜지스터

를 포함하는 회로.

[청구항 21]

제19항에 있어서,

제2 기준 전압을 구축하기 위해 제2 기준 전류 - 상기 제2 기준 전류는 상기 제2 출력 단자에서의 전압의 감소에 응답하여 증가함 - 를 구축하는 제2 전류 미러와,

상기 제2 기준 전류를 전달하고, 온도의 감소와 함께 크기가 감소하는 제2 임피던스와,

상기 제2 기준 전압을 수신하고 상기 제2 출력 단자에서 제2 출력 전류를 제공하는 제2 출력 트랜지스터

를 더 포함하는 회로.

### 도면의 간단한 설명

본 발명은 예로서 설명되며 동일 참조번호가 유사 구성 요소를 나타내는 첨부의 도면에 의해 한정되는 것은 아니다.

도 1은 본 발명의 일 실시예에 따른 회로를 구성도 형태로 나타낸 것이다.

도 2는 본 발명의 다른 실시예에 따른 회로를 구성도 형태로 것이다.

도 3은 본 발명의 일 실시예에 따른 도 1의 회로에 대한 전압-온도 곡선을 그래픽 형태로 나타낸 것이다.

도 4는 본 발명의 일 실시예에 따른 도 1의 회로에 대한 전압-전류 곡선을 그래픽 형태로 나타낸 것이다.

도 5는 본 발명의 일 실시예에 따른 회로를 블럭도로 나타낸 것이다.

당업자는 도면에서의 구성 요소가 간단 명료하게 도시되었고 반드시 본래 크기로 도시된 것은 아니라는 점을 이해할 것이다. 예를 들어, 본 발명의 실시예들에 대한 이해를 향상시키는 것을 돋기 위해, 도면에서의 몇몇 구성 요소들의 치수는 다른 구성 요소들보다 상대적으로 과장되게 도시되어 있을 수 있다.

도면

도면1

도면2

도면3

도면4

도면5