(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5149881号

(P5149881)

(45) 発行日 平成25年2月20日(2013.2.20)

(24) 登録日 平成24年12月7日(2012.12.7)

(51) Int.Cl.

F 1

H01L 21/56 (2006.01)

H01L 25/00 (2006.01)H01L 21/56

H01L 25/00T

B

請求項の数 5 (全 39 頁)

(21) 出願番号 特願2009-226679 (P2009-226679)

(22) 出願日 平成21年9月30日 (2009.9.30)

(65) 公開番号 特開2011-77267 (P2011-77267A)

(43) 公開日 平成23年4月14日 (2011.4.14)

審査請求日 平成24年4月25日 (2012.4.25)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 平井 達也

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 橋本 知明

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 菊池 阜

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

以下の工程を含むことを特徴とする半導体装置の製造方法：

(a) 第1面を有する第1金型、および凹部が形成され、前記第1面と対向する第2面を有する第2金型を備えた成型金型を準備する工程；

(b) 第1主面、前記第1主面に形成された複数の第1電極パッド、前記複数の第1電極パッドとそれぞれ接続された複数の第1配線、前記複数の第1配線とそれぞれ接続された複数の第1ランド、および前記第1主面とは反対側の第1裏面を有する第1基材を、前記第1主面が前記第2金型の前記凹部と対向するように、前記第2金型の前記凹部内に配置する工程；

(c) 前記(b)工程の後、第2主面、前記第2主面に形成された複数の第2電極パッド、前記複数の第2電極パッドとそれぞれ接続された複数の第2配線、前記複数の第2配線とそれぞれ接続された複数の第2ランド、および前記第2主面とは反対側の第2裏面を有し、前記第2主面に半導体チップが搭載された第2基材を、前記第2主面が前記第1基材の前記第1裏面と対向するように、前記第1金型と前記第2金型との間に配置する工程；

(d) 前記(c)工程の後、前記第2基材を前記第1金型と前記第2金型でクランプする工程；

(e) 前記(d)工程の後、前記第1基材と前記第2基材との間に樹脂を供給し、前記第1基材と前記第2基材との間に封止体を形成する工程；

10

20

(f) 前記(e)工程の後、前記第1金型と前記第2金型との間から、前記封止体が形成された前記第1基材および前記第2基材を取り出す工程；

(g) 前記(f)工程の後、前記第1基材の前記第1ランドから前記第2基材の前記第2ランドに向かって貫通孔を形成し、前記第2ランドを露出させる工程；

(h) 前記(g)工程の後、前記貫通孔の内部に導電性部材を形成する工程。

#### 【請求項2】

請求項1において、

前記第1基材は、前記第1主面から前記第1裏面に向かって形成された第1孔部を有し、

前記(b)工程では、前記第2金型の前記凹部に形成された第1ピンが前記第1基材の前記第1孔部内に位置するように、前記第1基材を前記第2金型の前記凹部内に配置し、

前記第2基材は、前記第2主面から前記第2裏面に向かって形成された第2孔部を有し、

前記(c)工程では、前記第2金型の前記第2面に形成された第2ピンが前記第2基材の前記第2孔部内に位置するように、前記第2基材を前記第1金型と第2金型との間に配置することを特徴とする半導体装置の製造方法。 10

#### 【請求項3】

請求項2において、

前記第1基材の前記第1主面、および前記第2基材の前記第2主面は、それぞれ四角形の平面形状を成し、

前記第1孔部は、前記第1主面の4辺のうち、第1の辺に近づけて配置され、

前記第2孔部は、前記第2主面の4辺のうち、前記第1の辺に沿って配置される第2の辺に近づけて配置されていることを特徴とする半導体装置の製造方法。 20

#### 【請求項4】

請求項3において、

前記第1孔部は、前記第1の辺に沿って複数形成され、前記第2孔部は前記第2の辺に沿って複数形成されていることを特徴とする半導体装置の製造方法。

#### 【請求項5】

請求項4において、

前記第1孔部は、前記第1の辺の中央に配置される第1中央孔部と、前記第1の辺に沿って前記第1中央孔部の両サイドに配置される第1サイド孔部を有し、

前記第2孔部は、前記第2の辺の中央に配置される第2中央孔部と、前記第2の辺に沿って前記第2中央孔部の両サイドに配置される第2サイド孔部を有し、

前記第1サイド孔部の開口面積は、前記第1中央孔部の開口面積よりも広く、

前記第2サイド孔部の開口面積は、前記第2中央孔部の開口面積よりも広いことを特徴とする半導体装置の製造方法。 30

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は半導体装置などの電子装置の製造技術に関し、特に、半導体チップなどの電子部品が搭載された基材の主面上にさらに別の配線基板を積層する電子装置(半導体装置)に適用して有効な技術に関する。 40

##### 【背景技術】

##### 【0002】

近年、半導体装置などの電子装置に対する小型化の要求がより一層強まっている。そのため、実装基板(マザーボード)上に搭載される半導体装置やチップ部品などの実装領域を低減するために、複数の電子部品を1つの半導体装置で構成することが有効とされている。

##### 【0003】

このような半導体装置の構成としては、例えば特開2008-288490号公報(特 50

許文献 1 ( 図 2 ( D ) ) に示すように、チップ部品が搭載された第 1 の基板上に第 2 の基板を積層し、この第 2 の基板上に電子部品を搭載するものがある。

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2008 - 288490 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本願発明者は、前記特許文献 1 のような半導体装置の製造方法について検討した結果、10

以下の問題があることを発見した。

【0006】

まず、前記特許文献 1 の製造方法は、チップ部品が搭載された第 1 の基板上に、第 1 の基板との対向面に基板間接続用の電極が設けられた第 2 の基板を積層し、この電極と第 1 の基板に形成された電極接続用パッドとを接合し、その後、各基板の離間部分に封止樹脂を充填するものである。

【0007】

しかしながら、半導体装置の高機能化、または高集積化に伴い、第 2 の基板に搭載される電子部品（半導体チップやチップ部品）の電極パッドの数、または第 2 の基板に搭載される電子部品の数が増加する傾向にある。そのため、第 2 の基板と第 1 の基板とを電気的に接続するための電極の数も増加する傾向にある。これにより、各基板間に配置された電極が障害となって、封止樹脂の供給経路が狭くなるため、供給された封止樹脂内に空気が巻き込まれ易くなり、この封止工程により形成される封止体の内部に空気が残る虞がある。封止体内に空気が残ると、製造された半導体装置の信頼性が低下する可能性がある。20

【0008】

本発明は、上記課題に鑑みてなされたものであり、その目的は、半導体装置の信頼性を向上させることができる技術を提供することにある。

【0009】

また、本発明の他の目的は、半導体装置を小型化または高集積化することができる技術を提供することにある。30

【0010】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

【0012】

すなわち、本発明の一つの実施の形態における半導体装置の製造方法は、それぞれ別個に準備した第 1 基材と第 2 基材の間に封止体を形成して一体化し、その後、前記第 1 基材と前記第 2 基材を電気的に接続するものである。また、前記第 1 基材と前記第 2 基材を電気的に接続する手段として、前記第 1 基材に形成された第 1 ランドと、前記第 2 基材に形成された第 2 ランドの位置を揃えて配置し、前記第 1 ランドから前記第 2 ランドに向かって貫通孔を形成した後、前記貫通孔内に導電性部材を形成するものである。40

【発明の効果】

【0013】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

【0014】

すなわち、半導体装置の信頼性を向上させることができる。50

**【図面の簡単な説明】****【0015】**

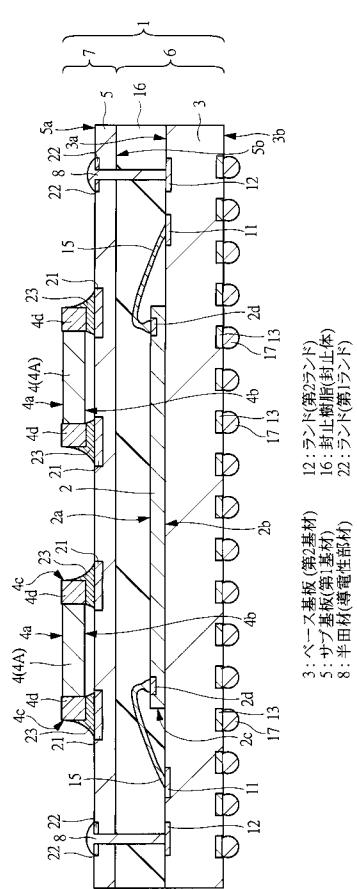

【図1】本発明の一実施の形態である半導体装置の全体構造を示す断面図である。

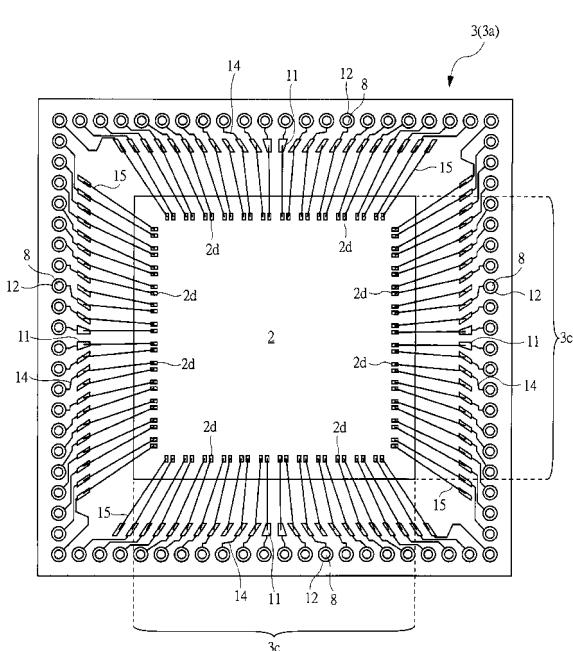

【図2】図1に示すベースパッケージの上面側の内部構造を示す透視平面図である。

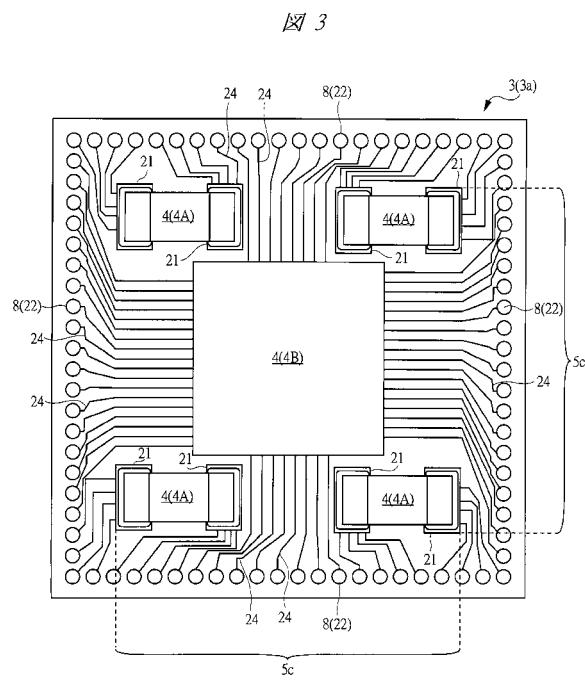

【図3】図1に示すサブパッケージの上面側を示す平面図である。

【図4】基材準備工程において準備する配線基板の正面の全体構造を示す平面図である。

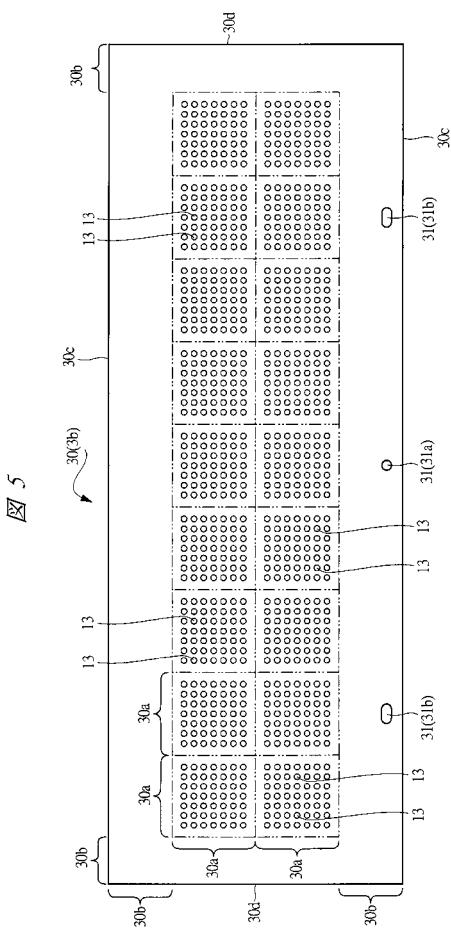

【図5】図4に示す配線基板の裏面の全体構造を示す平面図である。

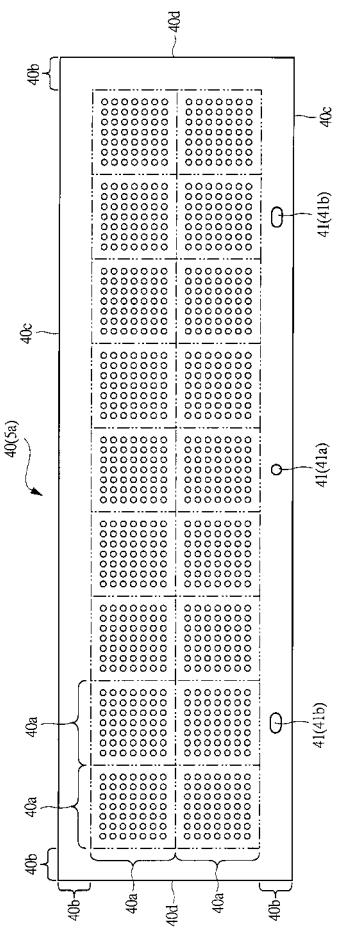

【図6】基板準備工程において準備する別の基板の正面の全体構造を示す平面図である。

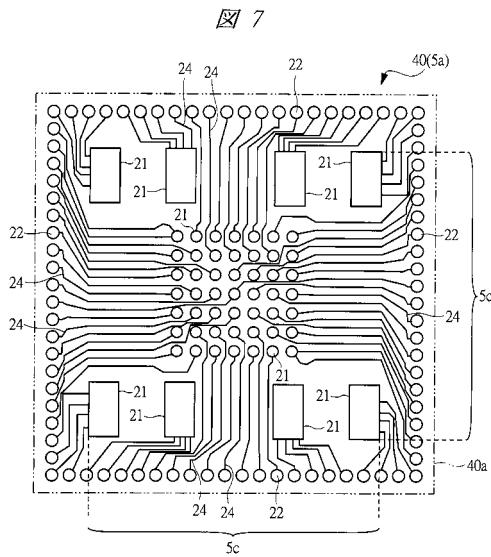

【図7】図6に示す配線基板の1つの製品形成領域を拡大して示す拡大平面図である。

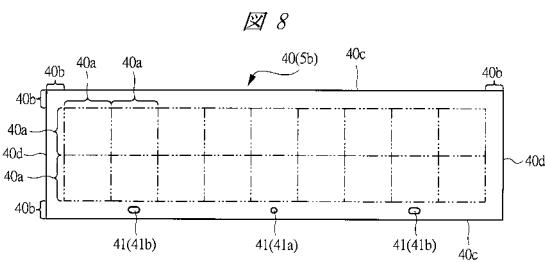

【図8】図6に示す配線基板の裏面の全体構造を示す平面図である。 10

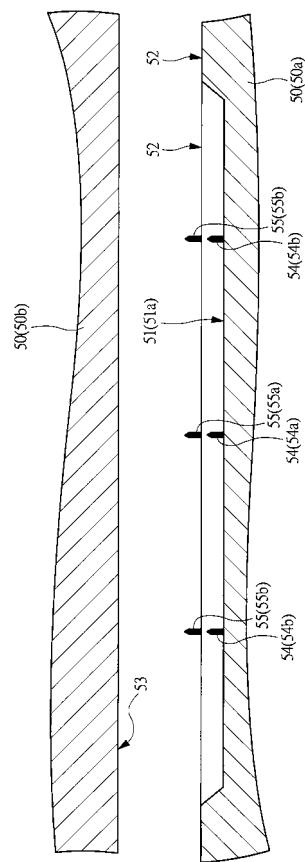

【図9】封止工程において準備する成型金型の要部を示す要部拡大断面図である。

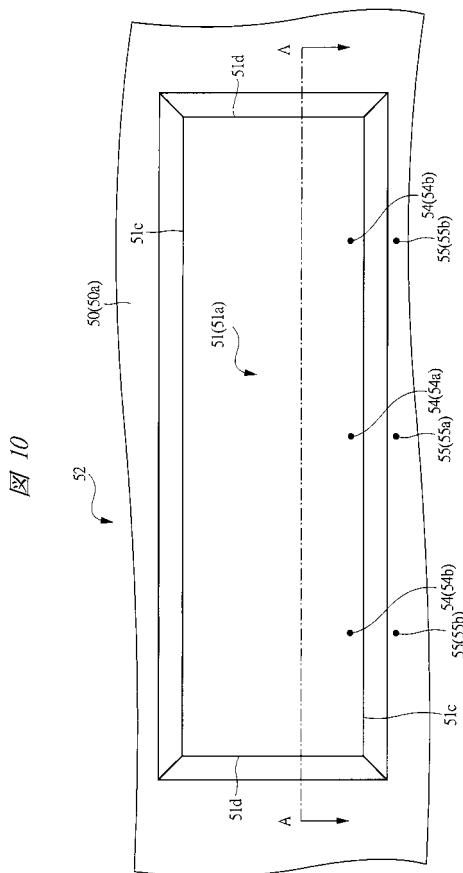

【図10】図9に示す下型の上面側の構造を示す要部拡大平面図である。

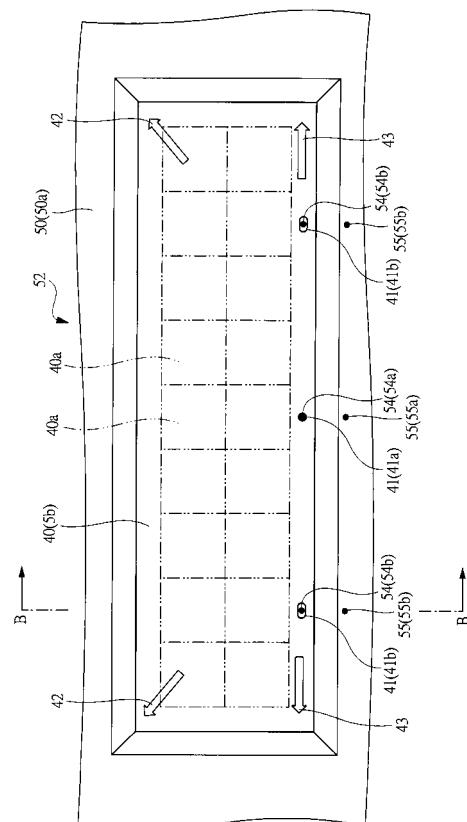

【図11】図10に示す成型金型のキャビティ内に図6および図8に示す配線基板を配置した状態を示す要部拡大平面図である。 20

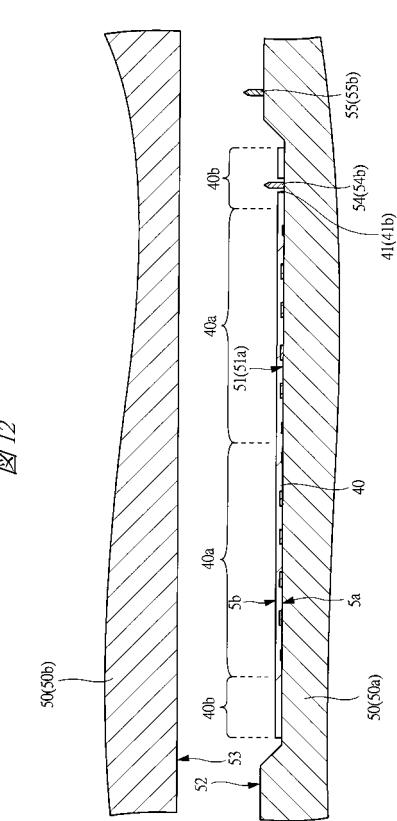

【図12】図11に示すB-B線に沿った要部拡大断面図である。

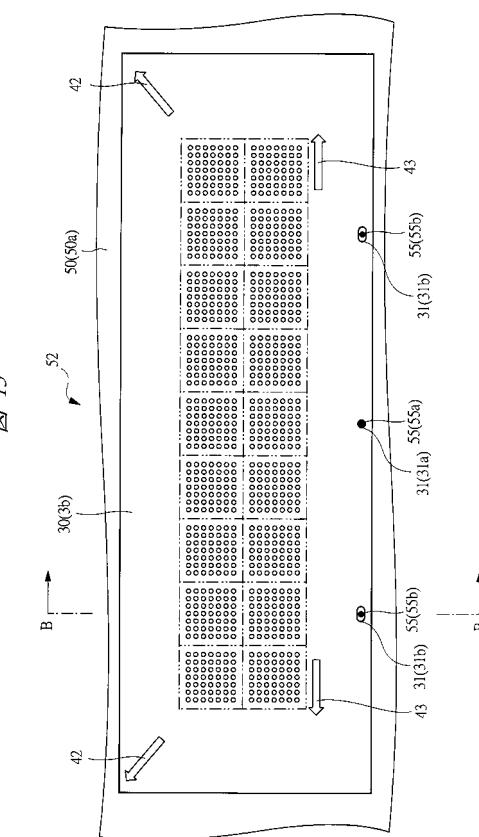

【図13】図11に示す成型金型の下型に図4および図5に示す配線基板を配置した状態を示す要部拡大平面図である。 20

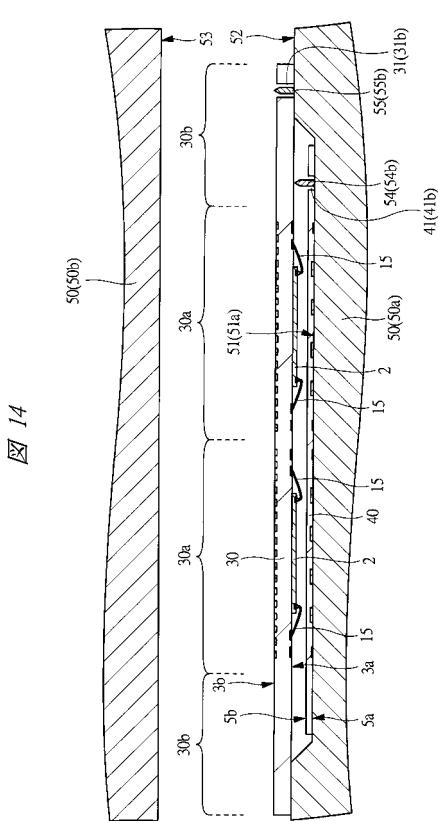

【図14】図13に示すB-B線に沿った要部拡大断面図である。

【図15】図14に示す配線基板(ベース基板)を成型金型で挟み込んでクランプした状態を示す要部拡大断面図である。 20

【図16】図15に示す2つの配線基板の間に、封止体を形成した状態を示す要部拡大断面図である。

【図17】図11あるいは図13に示す配線基板の膨張を制御する基準点周辺を拡大して示す要部拡大平面図である。

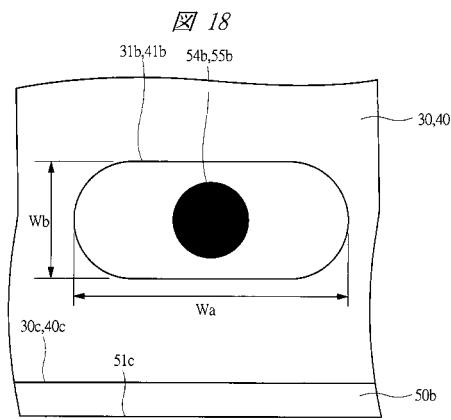

【図18】図11あるいは図13に示す配線基板の膨張を制御する補助点周辺を拡大して示す要部拡大平面図である。

【図19】図16に示す成型金型から取り出して上下を反転させた一括封止構造体を示す断面図である。 30

【図20】図19に示す一括封止構造体に複数の貫通孔を形成した状態を示す断面図である。 30

【図21】図19に示す貫通孔を形成した後の一括封止構造体の上面を、1つの製品形成領域について拡大して示す拡大平面図である。

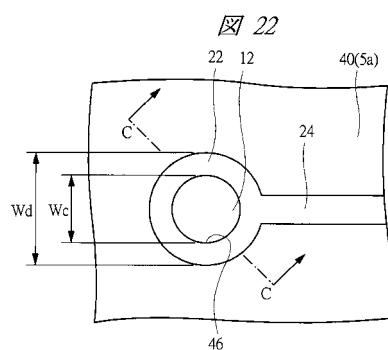

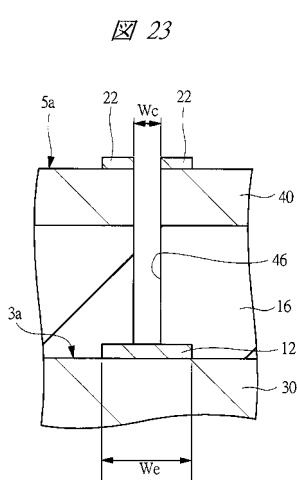

【図22】図21に示す貫通孔の1つを拡大して示す要部拡大平面図である。

【図23】図22に示すC-C線に沿った要部拡大断面図である。

【図24】図21に示す貫通孔内に導電性部材を形成した状態を示す断面図である。

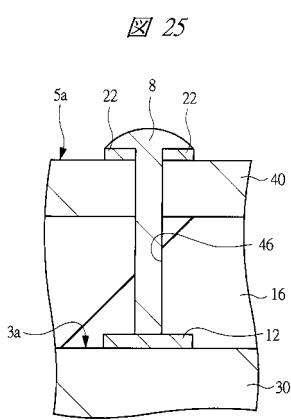

【図25】図24に示す1つの貫通孔周辺を拡大して示す要部拡大断面図である。

【図26】図24に示す一括封止構造体の裏面側に半田ボールを搭載した状態を示す断面図である。

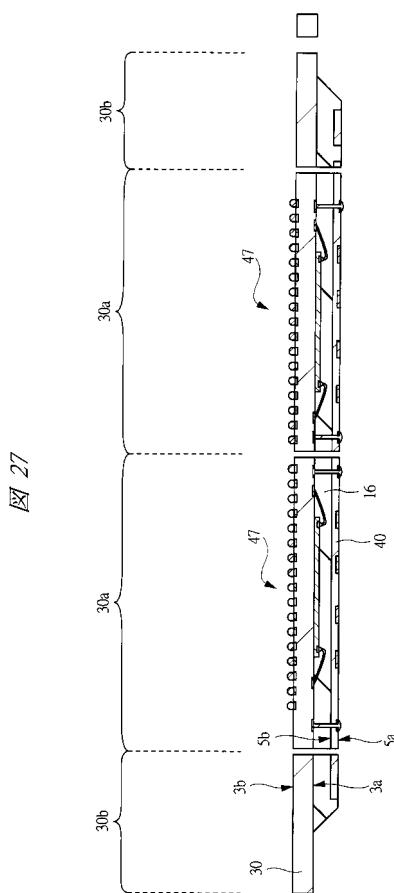

【図27】図26に示す一括封止構造体を切断した状態を示す断面図である。

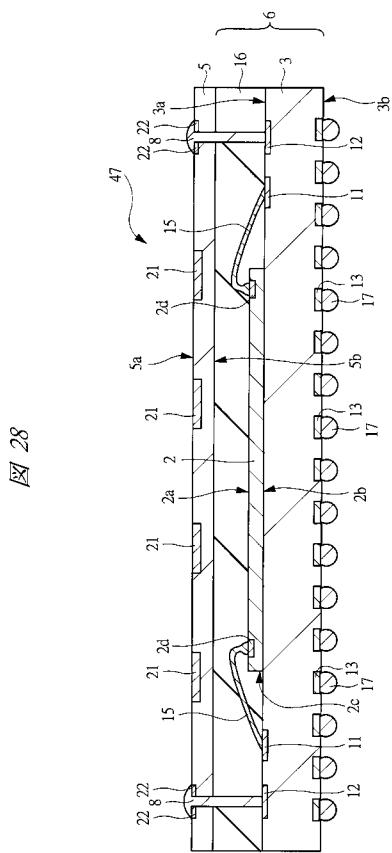

【図28】図26に示す個片化された配線基板の1個を示す断面図である。 40

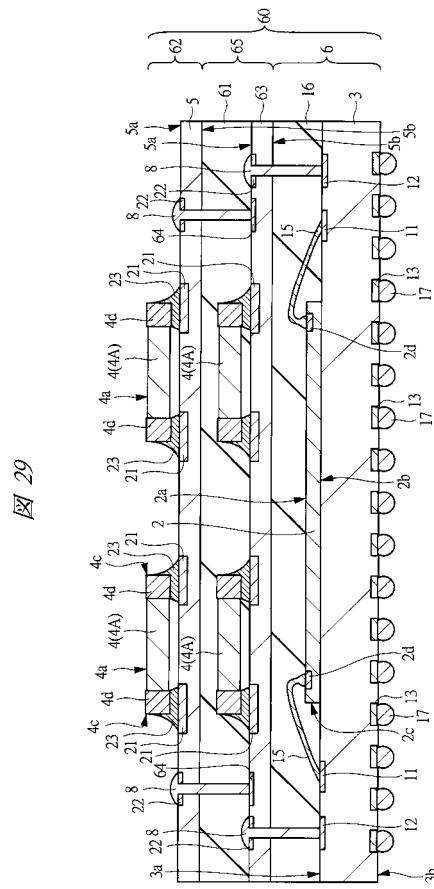

【図29】本発明の他の実施の形態である半導体装置の全体構造を示す断面図である。

【図30】本発明の他の実施の形態である半導体装置の製造方法における第3の基板配置工程を示す要部拡大断面図である。

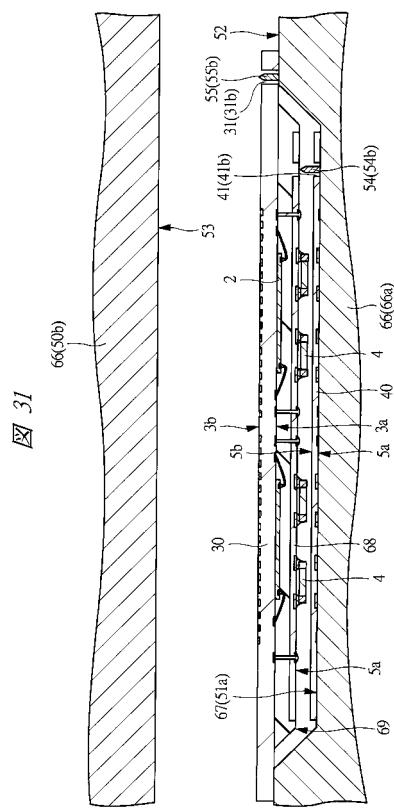

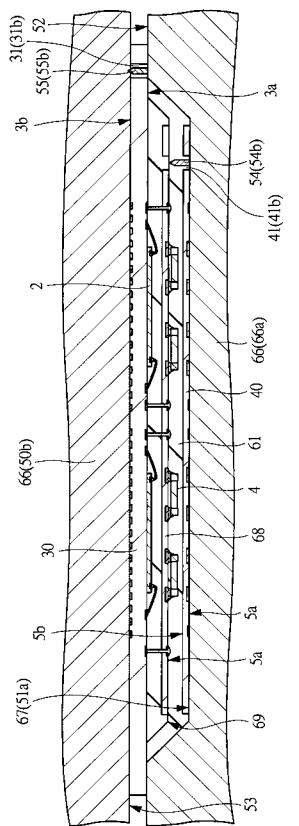

【図31】図30に示す配線基板上に一括封止構造体を配置した状態を示す要部拡大断面図である。

【図32】図31に示す一括封止構造体と配線基板の間に第2の封止体を形成した状態を示す要部拡大断面図である。

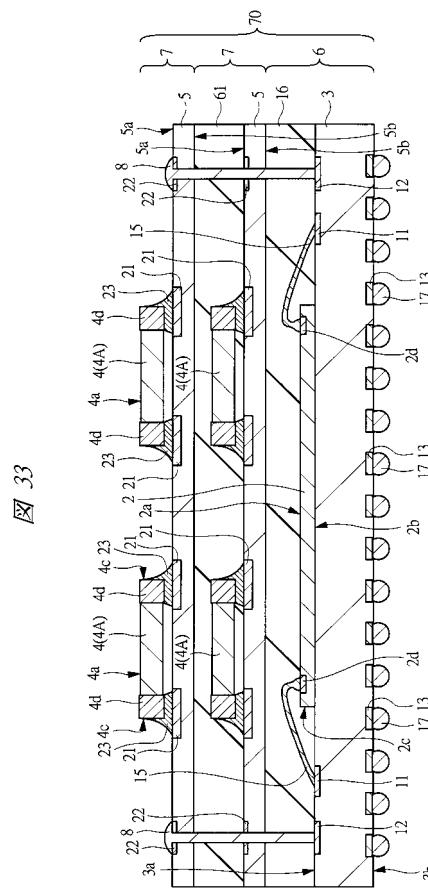

【図33】本発明の第1の変形例である半導体装置の全体構造を示す断面図である。

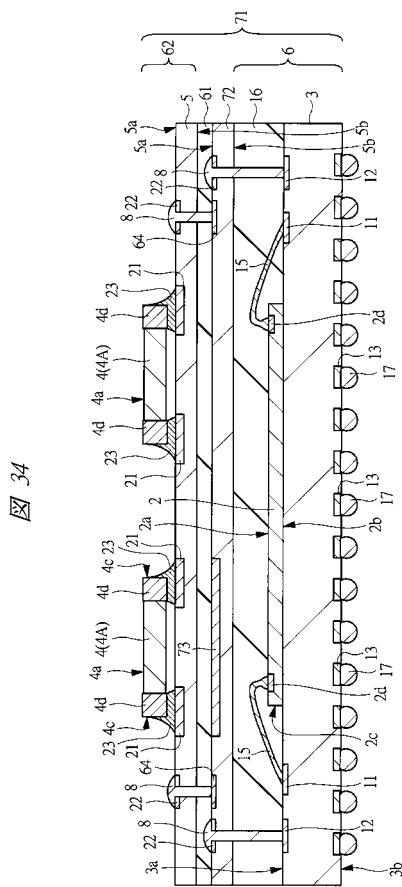

【図34】本発明の第2の変形例である半導体装置の全体構造を示す断面図である。

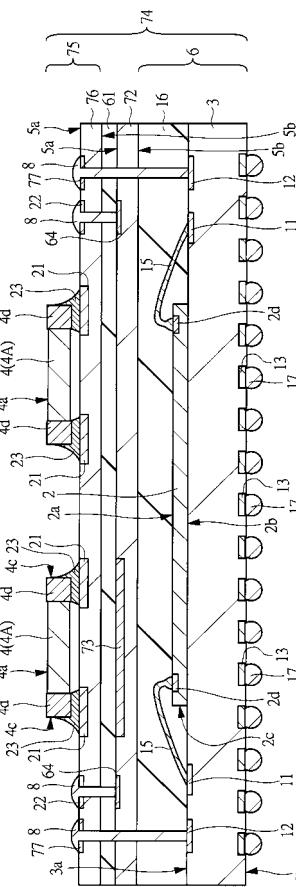

【図35】本発明の第3の変形例である半導体装置の全体構造を示す断面図である。 50

【図36】本発明の製造方法の変形例の第1の基材配置工程において、成型金型のキャビティ内に複数枚の配線基板を配置した状態を示す要部拡大断面図である。

【図37】図36に示す下型の上面を示す要部拡大平面図である。

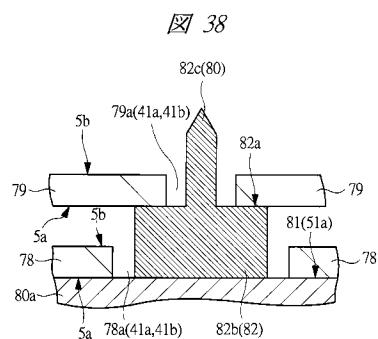

【図38】図36に示す位置決めピン周辺を拡大して示す要部拡大断面図である。

【図39】図36に示す支持台周辺を示す要部拡大断面図である。

【図40】図36で説明した第4の変形例に対する変形例を示す要部拡大断面図である。

#### 【発明を実施するための形態】

##### 【0016】

(本願における記載形式・基本的用語・用法の説明)

本願において、実施の態様の記載は、必要に応じて、便宜上複数のセクション等に分けて記載するが、特にそうでない旨明示した場合を除き、これらは相互に独立別個のものではなく、記載の前後を問わず、単一の例の各部分、一方が他方の一部詳細または一部または全部の変形例等である。また、原則として、同様の部分は繰り返しの説明を省略する。また、実施の態様における各構成要素は、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、必須のものではない。

##### 【0017】

同様に実施の態様等の記載において、材料、組成等について、「AからなるX」等といつても、特にそうでない旨明示した場合および文脈から明らかにそうでない場合を除き、A以外の要素を主要な構成要素のひとつとするものを排除するものではない。たとえば、成分についていえば、「Aを主要な成分として含むX」等の意味である。たとえば、「シリコン部材」等といつても、純粋なシリコンに限定されるものではなく、SiGe(シリコン・ゲルマニウム)合金やその他シリコンを主要な成分とする多元合金、その他の添加物等を含む部材も含むものであることはいうまでもない。また、金めっき、Cu層、ニッケル・めっき等といつても、そうでない旨、特に明示した場合を除き、純粋なものだけでなく、それぞれ金、Cu、ニッケル等を主要な成分とする部材を含むものとする。

##### 【0018】

さらに、特定の数値、数量に言及したときも、特にそうでない旨明示した場合、理論的にその数に限定される場合および文脈から明らかにそうでない場合を除き、その特定の数値を超える数値であってもよいし、その特定の数値未満の数値でもよい。

##### 【0019】

(実施の形態1)

<半導体装置の構造概要>

本実施の形態では電子部品がそれぞれ搭載された複数の配線基板を積層した半導体装置の例として、半導体チップが搭載された配線基板(基材)上に、電子部品が搭載された別の配線基板(基材)が積層されるパッケージオンパッケージ(Package on Package:POP)型半導体装置(以下、単にPOPと記載する)を取り上げて説明する。

##### 【0020】

POPは、例えば、半導体チップなどの電子部品が搭載された下段側の配線基板と、別の半導体チップなどの電子部品が搭載された上段側の配線基板とで構成され、上段側の配線基板と下段側の配線基板とを、導電性部材を介して電気的に接続することにより、上段、下段の電子部品を電気的に接続し、システムを構成する。またPOPは、例えば下段側の配線基板の下面に設けられた外部端子を介して外部電子機器のマザーボード(実装基板)などに実装される。

##### 【0021】

他方、POPと異なる形態の半導体パッケージとして、一枚の配線基板上に種類の異なる複数の半導体チップ(例えばコントローラ系チップとメモリ系チップ)を実装して、1つの半導体パッケージ内にシステムを構成するシステム・イン・パッケージ(System In Package: SIP)型半導体装置(以下、単にSIPと記載する)がある。

##### 【0022】

10

20

30

40

50

P O P は、複数枚の配線基板を備えているので、システムの多機能化に伴って半導体チップの入出力端子数が増加した場合でも、同一実装面積の S I P に比べて信号配線の量を増やすことができる利点がある。また、S I P と比較してシステムの少量・多品種化にも柔軟に対応できる。

#### 【 0 0 2 3 】

図 1 は本実施の形態の半導体装置の全体構造を示す断面図である。図 1 において、P O P ( 半導体装置 ) 1 は、半導体チップ 2 が搭載されたベース基板 ( 配線基板、基材、下段側基材 ) 3 の上部に、チップ部品 ( 電子部品、半導体チップ、半導体装置 ) 4 が搭載されたサブ基板 ( 配線基板、基材、上段側基材 ) 5 を重ね合わせた 2 層構造の積層型パッケージである。つまり、P O P 1 は、ベース基板 3 の正面 ( 表面、上面 ) 3 a に半導体チップ 2 が搭載されたベースパッケージ ( 下段側パッケージ ) 6 、およびサブ基板 5 の正面 ( 表面、上面 ) 5 a にチップ部品 4 が搭載されたサブパッケージ ( 上段側パッケージ ) 7 を有し、これら複数のパッケージを、導電性部材である半田材 8 を介して電気的に接続することにより、システムを構成している。

#### 【 0 0 2 4 】

なお、本実施の形態では、図 1 に示すようにベース基板 3 の裏面 3 b から封止樹脂 1 6 の上面までをベースパッケージ 6 と定義して説明する。しかし、ベースパッケージの定義は、これに限定されるものではない。例えば、図 1 に示すベース基板 3 の裏面 3 b からサブ基板 5 の正面 5 a までをベースパッケージとして考えることもできる。この場合のベースパッケージは、積層される複数の配線基板 ( ベース基板 3 およびサブ基板 5 ) の間に半導体チップ 2 が内蔵された半導体装置となる。また、例えば、外部端子である半田ボール 1 7 をベースパッケージに含めることもできる。

#### 【 0 0 2 5 】

##### < ベースパッケージ >

次に、図 1 に示すベースパッケージ 6 の構造について説明する。図 2 は図 1 に示すベースパッケージの上面側の内部構造を示す透視平面図である。なお、図 2 では、正面側の各部材の配置を示すため、図 1 に示す封止樹脂 1 6 を取り除いた状態で示している。

#### 【 0 0 2 6 】

ベースパッケージ 6 が有するベース基板 3 は、例えばビルドアップ工法によって製造された 4 層の配線層 ( 表面配線層、裏面配線層および 2 層の内層配線 ) を有する多層配線基板である。また、各配線層同士を電気的に絶縁する絶縁層は、例えば、ガラス繊維または炭素繊維に樹脂を含浸させたプリプレグによって構成されている。また、4 層の配線は、例えば銅 ( C u ) を主体とする導電膜によって構成されている。図 1 では、これらの配線の図示が省略されており、ベース基板 3 の正面 3 a に形成された端子 ( 電極パッド、ボンディングリード ) 1 1 、ランド ( 端子、基板間接続端子 ) 1 2 と、ベース基板 3 の下面 ( 裏面 ) 3 b に形成された外部入出力用のランド ( 端子、電極パッド ) 1 3 のみが示されている。

#### 【 0 0 2 7 】

図 2 に示すように、ベース基板 3 の正面 3 a は、平面形状が四角形からなり、本実施の形態では、正方形である。また、ベース基板 3 の正面 3 a には、複数の端子 ( 電極パッド、ボンディングリード ) 1 1 、端子 1 1 とそれぞれ電気的に接続される複数の配線 1 4 、および複数の配線 1 4 を介して端子 1 1 と電気的に接続される複数のランド 1 2 が形成されている。端子 1 1 は、正面 3 a において、チップ搭載領域 3 c の周囲 ( すなわち、半導体チップ 2 の周囲 ) に配置されている。本実施の形態では、四角形の平面形状をなす半導体チップ 2 の各辺に沿ってそれぞれ複数の端子 1 1 が形成されている。また、複数のランド 1 2 は、端子 1 1 よりも正面 3 a の周縁部側、すなわち、半導体チップ 2 よりも外側に配置されている。本実施の形態では、ランド 1 2 は、四角形の平面形状をなすベース基板 3 の正面 3 a の各辺に沿ってそれぞれ複数配置されている。また、複数のランド 1 2 には、それぞれ複数の半田材 8 が接合し、半田材 8 を介してベース基板 3 とサブ基板 5 は電気的に接続されている。なお、半田材 8 の詳細については後述する。

10

20

30

40

50

## 【0028】

一方、図1に示すベース基板3の下面(裏面)3bは、平面形状が四角形からなり、本実施の形態では、例えば、主面3aと等しい大きさの正方形である。裏面3bには、ベース基板3の図示しない配線層を介して、主面3aに形成された端子11、あるいはランド12と電気的に接続される複数のランド13が形成されている。複数のランド13には、POP1を図示しない実装基板に搭載する際の接合材となる複数の半田ボール17がそれぞれ配置(接合)されている。

## 【0029】

半田ボール17は、Pb(鉛)を実質的に含まない、所謂、鉛フリー半田であり、例えばSn(錫)のみ、Sn(錫)-Bi(ビスマス)、またはSn(錫)-Ag(銀)-Cu(Cu)などである。ここで、鉛フリー半田とは、鉛(Pb)の含有量が0.1wt%以下のものを意味し、この含有量は、RoHS(Restriction of Hazardous Substances)指令の基準として定められている。以下、本実施の形態において、半田、あるいは半田ボールについて説明する場合には、特にそうでない旨明示した場合を除き、鉛フリー半田を指す。

10

## 【0030】

ベース基板3の主面3aのチップ搭載領域3cには、チップ部品として半導体チップ2が搭載されている。半導体チップ2は、図1に示すように主面2a、主面2aと反対側に位置する裏面2b、および主面2aと裏面2bの間に位置する側面2cを有している。主面2aおよび裏面2bは、平面形状が四角形からなり、本実施の形態では、例えば、正方形である。

20

## 【0031】

また、半導体チップ2の主面2aには、トランジスタやダイオードなどの複数の半導体素子が形成され、各半導体素子は図示しない配線(チップ内配線)を介して電気的に接続され、集積回路を構成している。また、主面2a上には、主面2aの外縁を構成する各辺に沿って集積回路と電気的に接続される複数のパッド(電極パッド)2dが形成されている。パッド2dは、集積回路が形成される回路形成領域を囲むように配置され、集積回路と前記したチップ内配線を介して電気的に接続されている。

## 【0032】

また、図1に示すように半導体チップ2は、裏面2bがベース基板3の主面3aと対向するように図示しない接着材を介してベース基板3上に固定する、所謂、フェイスアップ実装方式によりベース基板3上に搭載されている。

30

## 【0033】

また、半導体チップ2の主面2aに形成された複数のパッド2dは、ベース基板3の主面3aに形成された複数の端子11と、例えば、金(Au)からなる複数のワイヤ(導電性部材)15を介してそれぞれ電気的に接続されている。

## 【0034】

また、ベース基板3の主面3aとサブ基板5の裏面5bとの間には、封止樹脂(封止体)16が配置され、半導体チップ2および複数のワイヤ15は、この封止樹脂16により封止されている。

40

## 【0035】

## &lt;サブパッケージ&gt;

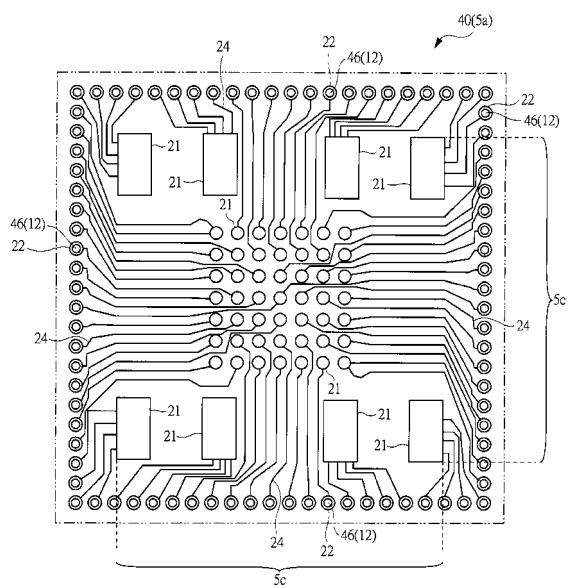

次に、図1に示すサブパッケージ7の構造について説明する。図3は図1に示すサブパッケージの上面側を示す平面図である。

## 【0036】

サブパッケージ7が有するサブ基板5は、例えば、ガラスエポキシ樹脂などを絶縁層とする樹脂基板からなる。図3に示すように、サブ基板5の主面5aは、平面形状が四角形からなり、例えば、図2に示すベース基板3の主面3aと同じ大きさである。また、サブ基板5の主面5aには、複数の端子(ボンディングリード、電極パッド)21、端子21とそれ電気的に接続される複数の配線24、および複数の配線24を介して端子21

50

と電気的に接続される複数のランド 2 2 が形成されている。また、図 1 に示すようにベース基板 3 の厚さはサブ基板 5 の厚さよりも厚い。ベース基板は P O P 1 の外部端子を有する基板であり、多数の配線を引き回すためにはサブ基板 5 よりも広い配線引き回しスペースが必要となる。このため、ベース基板 3 では、例えば 4 層、あるいはそれ以上の配線層を形成し、平面積の増大を抑制しつつ、配線引き回しスペースを確保しているため、厚くなる。一方、サブ基板 5 は、ベース基板 3 上に搭載される基板なので、配線引き回しスペースはベース基板 3 よりも小さくすることができる。したがって、サブ基板 5 はベース基板 3 よりも配線層数が少なく、例えば本実施の形態では、主面 5 a に 1 層の配線層を有するシンプルな配線基板としている。

## 【 0 0 3 7 】

10

また、サブ基板 5 の端子 2 1 は、主面 5 a において、チップ部品搭載領域 5 c に、チップ部品 4 のレイアウトに応じて複数配置されている。本実施の形態では、複数のチップ部品 4 を搭載する例を示しているので、各チップ部品 4 について、それぞれ複数の端子 2 1 が形成されている。この複数の端子 2 1 には、それぞれチップ部品 4 が搭載され、チップ部品 4 が有する複数の端子（電極）4 d は、導電性部材である半田材 2 3 を介して端子 2 1 と電気的に接続されている。

## 【 0 0 3 8 】

ここで、チップ部品 4 は、受動素子、能動素子、あるいは集積回路などが形成された電子部品であって、被搭載基材である配線基板上に形成された端子（ボンディングリード）に導電性部材を介して面実装される電極端子を有している。チップ部品 4 の例としては、チップ抵抗、チップコンデンサ、インダクタなどの受動素子部品、增幅器、整流器などの能動素子部品、あるいは半導体チップや半導体装置など、集積回路部品などを挙げることができる。図 1 では、上面 4 a、上面 4 a と反対側に位置する下面 4 b、および上面 4 a と下面 4 b の間に位置する側面 4 c を有し、対向する 2 つの側面 4 c 側に端子 4 d が形成されたチップ部品 4 A を例示的に示している。また、図 3 では、チップ部品 4 A に加え、主面および主面の反対側に位置する裏面、および主面側に形成される複数の電極パッド（図示は省略）を有し、主面とサブ基板 5 の主面 5 a とが対向した状態で、半田材などの導電性部材を介してサブ基板 5 の主面 5 a に形成された端子（ボンディングリード、電極パッド：図示は省略）と電気的に接続する、所謂フェイスダウン実装方式により実装されたチップ部品 4 B を例示的に示している。なお、チップ部品 4 B の例としては、例えば、主面、および主面の反対側に位置する裏面、主面上に形成された複数の電極パッド、および主面上に形成された再配線層を介して電極パッドと電気的に接続される外部端子を有する、所謂 W P P (Wafer Process Package) を例示することができる。しかし、チップ部品 4 の形状や実装態様は図 1 や図 3 に示す態様には限定されず、チップ部品 4 の種類に応じて種々の変形例を適用することができる。例えば、チップ部品 4 として、配線基板の主面に半導体チップが搭載され、この主面とは反対側の裏面に外部端子である半田ボールが形成された、所謂、B G A (Ball Grid Array) 型の半導体装置（半導体パッケージ）、あるいはリードフレームのチップ搭載部に半導体チップが搭載され、封止体からリードの一部が露出する Q F P (Quad Flat Package) をサブ基板 5 の主面 5 a に搭載してもよい。

## 【 0 0 3 9 】

30

複数の端子 2 1 とそれぞれ電気的に接続される複数のランド 2 2 は、端子 2 1 よりも主面 3 a の周縁部側、すなわち、チップ部品搭載領域 5 c よりも外側に配置されている。本実施の形態では、ランド 2 2 は、四角形の平面形状をなすサブ基板 5 の主面 5 a の各辺に沿ってそれぞれ複数配置されている。このランド 2 2 は、下段側の配線基板であるベース基板 3 に形成されたランド 1 2 と厚さ方向に重なる位置に形成されている。また、複数のランド 2 2 には、それぞれ複数の半田材 8 が接合し、半田材 8 を介してベース基板 3 とサブ基板 5 は電気的に接続されている。

## 【 0 0 4 0 】

40

一方、サブ基板 5 の下面（裏面）5 b は、平面形状が四角形からなり、例えば、図 2 に示すベース基板 3 の主面 3 a と同じ大きさである。一般に、P O P 型半導体装置では、上

50

段側に配置する配線基板の下面側に、上面と電気的に接続されたランドを形成し、該ランドと下段側の配線基板に形成されたランドとを、半田ボールを介して電気的に接続する（例えば前記特許文献1参照）。

#### 【0041】

しかし、本実施の形態では、図1に示すようにサブ基板5の正面5aからベース基板3の正面3aに向かって（詳しくはサブ基板5の正面5aに形成されたランド22からベース基板3の正面3aに形成されたランド12に向かって）形成された貫通孔の内部に、導電性部材として半田材8を埋め込んで形成している。このため、裏面5bには配線やランドを形成していない。すなわち、前記したようにサブ基板5は正面5aに配線層を有し、裏面5bには配線層を有しない1層（単層）配線基板である。このようにサブ基板5の配線構造を単純な構造とすることにより、サブ基板5の製造工程を効率化することができる。また、サブ基板5の材料コスト、加工コストを低減することができる。10

#### 【0042】

ただし、サブ基板5の配線レイアウトによっては、配線の引き回しスペースを確保する観点から、裏面5bにも配線層を形成し、2層基板、あるいはそれ以上の多層基板とする方が好ましい場合もある。この場合にはサブ基板5を单層基板とせず、複数層基板としても良い。

#### 【0043】

また、本実施の形態ではサブ基板5の裏面5bは、封止樹脂16と密着して固定されている。つまり、サブ基板5は封止樹脂16に接着固定され、これによりベースパッケージ6と一体の構造物となっている。前記した裏面5bに配線層を形成しないことは、封止樹脂16とサブ基板5との密着性を向上させる観点からも好ましい。POP1を構成するベースパッケージ6とその上段に配置されるサブ基板5は、このように一体構造となっているので、これを半導体チップ（チップ部品、電子部品）2が内蔵された配線基板として用いることもできる。20

#### 【0044】

##### <半導体装置の製造方法>

次に本実施の形態の半導体装置の製造方法について説明する。本実施の形態の半導体装置の製造方法は、ベースパッケージ6（封止樹脂16を除く）、およびサブ基板5に相当する基材をそれぞれ準備する基材準備工程を有している。また、ベースパッケージ6およびサブ基板5を離間した状態で配置して、ベース基板3の正面3aとサブ基板5の裏面5bの間に樹脂を供給して封止樹脂16を形成する封止工程を有している。また、封止樹脂16を形成した後、サブ基板5の正面5a側からベース基板3の上面側に向かって貫通孔を形成し、貫通孔内に導電性部材を形成してサブ基板5とベース基板3を電気的に接続する電気的接続工程を含んでいる。30

#### 【0045】

本実施の形態の半導体装置の製造方法の一つの特徴は、それぞれ別個に準備したベース基板とサブ基板の間に封止体を形成して一体化し、その後、ベース基板とサブ基板を電気的に接続する点である。また、本実施の形態の別の特徴は、ベース基板とサブ基板を電気的に接続する手段として、サブ基板の端子（ランド）とベース基板の端子（ランド）の位置を揃えて配置し、サブ基板の端子からベース基板の端子に向かって貫通孔を形成した後、該貫通孔内に導電性部材を形成する点である。40

#### 【0046】

前記特許文献1のように、電極をはんだで電極接続用パッドと接続する場合、洗浄工程が必要になる。しかし、予め第1の基板にチップ部品（または、半導体チップ）が搭載されており、そしてこのチップ部品がワイヤを介して第1の基板と電気的に接続されている場合には、この洗浄工程によりワイヤが変形し、隣のワイヤとショートする虞がある。

#### 【0047】

一方、本実施の形態によれば、半導体チップおよびこれに電気的に接続されるワイヤは、封止体により保護されているので、洗浄工程を実施する必要がなく、ワイヤが変形する50

ことを防止することができる。

#### 【0048】

また、ガラスエポキシ系の樹脂基板を用いると、電極をバンプ接続用パッドに接合するための熱の影響により、基板からアウトガスが発生し、基板の表面を汚染してしまう。このアウトガスは、例えばプラズマを汚染された表面に照射することで清浄化できる。しかし、前記特許文献1のように、電極を介して第1の基板と第2の基板を接合した後にアウトガスが発生すると、間に封止樹脂を供給する対向面（前記特許文献1の図1（E）における第1の基板の上面と第2の基板の下面）にプラズマを照射することが困難である。これにより、各基板間に供給される封止樹脂と基板との密着性が低下し、この封止工程により形成される封止体と基板の表面と間に隙間が生じ、半導体装置の信頼性が低下してしまう。10

#### 【0049】

一方、本実施の形態によれば、ベース基板とサブ基板とを電気的に接続する工程は、封止工程の後で行う。このため、ベース基板とサブ基板の対向面の汚染を防止することができる。また、仮に、ベース基板とサブ基板を準備する基材準備工程において、熱影響によるアウトガスの発生により、ベース基板の主面あるいはサブ基板裏面が汚染された場合であっても、封止体を形成する前であれば、汚染面に容易にプラズマを照射して清浄化することができる。

#### 【0050】

また、第1の基板と第2の基板を予め電気的に接続した状態で、各基板の間に封止体を形成する場合、熱影響により一方の基板に生じた反りが他方の基板に影響を与えることとなる。この結果、それぞれの基板に生じる反りの影響により、反りの程度が大きくなり、各基板の平面的位置関係にズレが生じ易くなる。20

#### 【0051】

一方、本実施の形態では、ベース基板とサブ基板の間に封止体を形成する工程までは、両基板は独立しているので、一方の基板に生じた反りは他方の基板に影響を与えない。したがって、その程度を低減することができるので、各基板の平面的位置関係をずれ難くすることができる。

#### 【0052】

以下本実施の形態の半導体装置の製造方法が有する各工程の詳細について順に説明する。30

。

#### 【0053】

まず、基材準備工程では、主面（上面）に半導体チップ（電子部品）6が搭載されたベース基板3に相当する基材と、サブ基板5に相当する配線基板（基材）をそれぞれ準備する。図4は、基材準備工程において準備する配線基板の主面の全体構造を示す平面図、図5は図4に示す配線基板の裏面の全体構造を示す平面図である。また、図6は基板準備工程において準備する別の基板の主面の全体構造を示す平面図、図7は図6に示す配線基板の1つの製品形成領域を拡大して示す拡大平面図、図8は図6に示す配線基板の裏面の全体構造を示す平面図である。

#### 【0054】

図4～図8に示すように、本工程で準備するベース基板（基材、配線基板、多数個取り配線基板）30およびサブ基板（基材、配線基板、多数個取り配線基板）40は、それぞれ複数の製品形成領域30a、40aが、例えば行列状に配置されたマトリクス基板（多数個取り基板）である。ベース基板30の各製品形成領域30aは、図2に示すベース基板3に、サブ基板40の各製品形成領域40aは図3に示すサブ基板5に相当する。また、ベース基板30およびサブ基板40は、複数の製品形成領域30a、40aが配置される領域の周囲を取り囲む枠部30b、40bを有している。換言すれば、各製品形成領域30a、40aは、主面3a、5a、あるいは裏面3b、5bの平面において、枠部30b、40bよりも内側に配置されている。40

#### 【0055】

10

20

30

40

50

ベース基板 3 0 が有する各製品形成領域 3 0 a は、図 1 あるいは図 2 を用いて説明した、上面（主面）3 a、主面 3 a に形成された複数の端子（ボンディングリード、電極パッド）1 1、主面 3 a に形成され複数の端子 1 1 とそれぞれ電気的に接続された複数の配線 1 4、複数の端子 1 1 よりも製品形成領域 3 0 a の周縁部側に配置され複数の配線 1 4 と電気的に接続されたランド 1 2、主面 3 a と反対側に位置する下面（裏面）3 b および裏面 3 b に形成され、ランド 1 2 あるいは端子 1 1 と電気的に接続されるランド 1 3 を有している。また、主面 3 a には半導体チップ 2 が裏面 2 b と主面 3 a とを対向させた状態で図示しない接着材を介して接着する、所謂フェイスアップ実装方式により搭載され、半導体チップ 2 の主面 2 a に形成された複数のパッド 2 d（図 2 参照）と、複数の端子 1 1（図 2 参照）は複数のワイヤ 1 5 を介してそれぞれ電気的に接続されている。主面 3 a 上に半導体チップ 2 を搭載するダイボンディング工程、および複数のパッド 2 d と複数の端子 1 1 とを複数のワイヤ 1 5 を介してそれぞれ電気的に接続するワイヤボンディング工程については、公知の方法を用いることができるので、詳細な説明は省略する。10

#### 【 0 0 5 6 】

なお、本工程の段階では、図 1 に示す封止樹脂 1 6 は形成されておらず、ベース基板 3 の主面 3 a は露出している。また、図 1 および図 2 に示す半田材 8 も形成されていない。また、図 1 および図 2 に示す半田ボール 1 7 も形成されておらず、裏面 3 b 側にはランド 1 3 が露出している。

#### 【 0 0 5 7 】

また、ベース基板 3 0 の枠部 3 0 b には、複数の孔部 3 1 が形成されている。ベース基板 3 0 の主面 3 a および裏面 3 b の平面形状は四角形（本実施の形態では長方形）であって、それぞれ対向する長辺 3 0 c と短辺 3 0 d を有している。本実施の形態では複数の孔部 3 1 は、4つの辺のうち、1つの長辺 3 0 c に沿って配置されている。この孔部 3 1 は、後述する封止工程において、ベース基板 3 0 とサブ基板 4 0 との位置合わせを行うための孔であり、本実施の形態では、主面 3 a から裏面 3 b に向かってベース基板 3 0 を貫通する貫通孔である。なお、孔部 3 1 の配置や形状については封止工程を説明する際に詳細に説明する。20

#### 【 0 0 5 8 】

一方、サブ基板 4 0 が有する各製品形成領域 4 0 a は、図 6 ~ 図 8 に示すように、上面（主面）5 a、主面 5 a に形成された複数の端子（ボンディングリード、電極パッド）2 1、主面 5 a に形成され複数の端子 2 1 とそれぞれ電気的に接続された複数の配線 2 4、複数の端子 2 1 よりも製品形成領域 4 0 a の周縁部側に配置され複数の配線 2 4 と電気的に接続されたランド 2 2、および主面 5 a と反対側に位置する下面（裏面）5 b を有している。30

#### 【 0 0 5 9 】

なお、本工程の段階では、図 7 に示すようにサブ基板 4 0 の主面 5 a にはチップ部品 4（図 1 参照）は搭載されておらず、各端子 2 1 が露出している。また、図 8 に示すように本実施の形態のサブ基板 5 の裏面 5 b は、配線や端子などが形成されず、絶縁材料で覆われている。

#### 【 0 0 6 0 】

また、前記したベース基板 3 0 と同様に、サブ基板 4 0 の枠部 4 0 b には、複数の孔部 4 1 が形成されている。サブ基板 4 0 の主面 5 a および裏面 5 b の平面形状は四角形（本実施の形態では長方形）であって、それぞれ対向する長辺 4 0 c と短辺 4 0 d を有している。本実施の形態では複数の孔部 4 1 は、4つの辺のうち、1つの長辺 4 0 c に沿って配置されている。この孔部 4 1 は、後述する封止工程において、ベース基板 3 0 とサブ基板 4 0 との位置合わせを行うための孔であり、本実施の形態では、主面 5 a から裏面 5 b に向かってサブ基板 4 0 を貫通する貫通孔である。なお、孔部 4 1 の配置や形状については封止工程を説明する際に詳細に説明する。40

#### 【 0 0 6 1 】

なお、前記したように、例えばダイボンディング工程やワイヤボンディング工程などの50

熱影響によりベース基板30からアウトガスが発生し、ベース基板30の主面が汚染される場合がある。この場合には、ベース基板30を準備した後、かつ、後述する封止工程の前に、主面3a側にプラズマを照射し、主面3aを清浄化しておくことが好ましい。これにより、封止工程において主面3aと封止樹脂との密着性の低下を抑制することができる。同様にサブ基板40の封止樹脂との密着面となる裏面5bについても、本工程において、プラズマを照射し、清浄化しておくことが好ましい。

#### 【0062】

次に、封止工程について説明する。封止工程は成型金型を準備する金型準備工程を有している。図9は封止工程において準備する成型金型の要部を示す要部拡大断面図、図10は図9に示す下型の上面側の構造を示す要部拡大平面図である。なお、図9は図10に示すA-A線に沿った断面に対応し、成型金型に形成されるピンの位置関係（高さ方向の位置関係）を示すため、ピンおよび上面の位置を示している。本実施の形態では、1つのキャビティ内に行列配置された複数の製品形成領域を有する配線基板を配置して、複数の製品形成領域について一括して封止する、所謂MAP（Mold Alay Package）と呼ばれる封止方式について説明する。

#### 【0063】

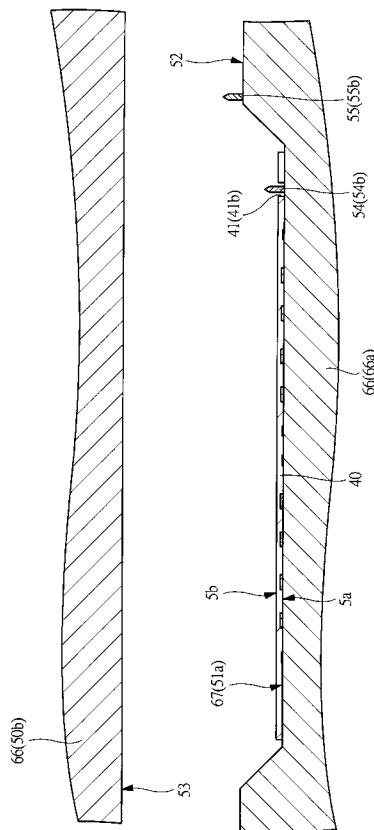

本工程で準備する成型金型50は、下面53を有する上型（金型）50b、および下面53と対向する上面52を有し、上面52側にキャビティ（凹部、窪み部）51が形成された下型（金型）50aを備えている。

#### 【0064】

また、下型50aは、複数のピン（突起、位置合わせピン）54、55を有している。ピン54、55は、封止工程において図4～図8のいずれかに示すベース基板30とサブ基板40の位置合わせを行うために用いる突起であり、キャビティ51の底面51a、あるいは上面52から、上型50bの下面53に向かって突出するように形成されている。

#### 【0065】

封止工程では、ピン54、55を図4あるいは図6に示す孔部31、41に挿入することにより、位置合わせを行う。このため、ピン54、55は、それぞれ孔部31、41と対応する位置に形成されている。換言すれば、ベース基板30、サブ基板40が有する孔部31、41は、ピン54、55の位置に対応して形成されている。詳しくは、キャビティ51の底面51aは、四角形（本実施の形態では長方形）の平面形状を有し、それぞれ対向する長辺51cと短辺51dを有している。本実施の形態では複数のピン54は、4つの辺のうち、1つの長辺51cに沿って、底面51a内に配置されている。また、複数のピン55は、4つの辺のうち、1つの長辺51cに沿って、上面52上に配置されている。

#### 【0066】

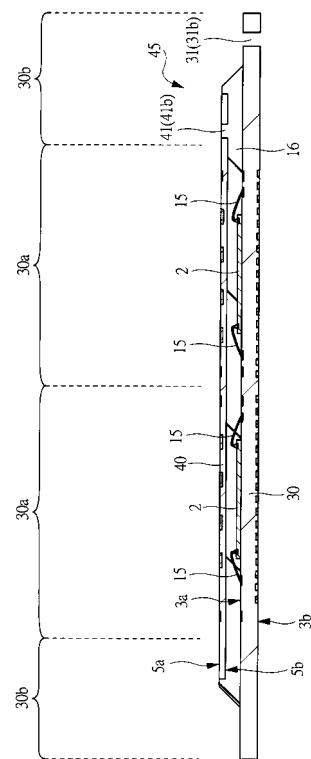

また、封止工程は、前記した基材準備工程で準備したサブ基板40を成型金型50のキャビティ51内に配置する第1の基材配置工程を有している。図11は図10に示す成型金型のキャビティ内に図6および図8に示す配線基板を配置した状態を示す要部拡大平面図、図12は図11に示すB-B線に沿った要部拡大断面図である。

#### 【0067】

本工程では、サブ基板40の主面5aが、下型50aのキャビティ51と対向するよう（詳しくは、キャビティ51の底面51aと対向するように）キャビティ51内に配置する。つまり、サブ基板40の上下を反転して、主面5aを下向きにした状態でキャビティ51内に配置する。この時、キャビティ51内に形成されたピン54がサブ基板40の孔部41内に位置するようにサブ基板40を配置する。詳しくは、ピン54をサブ基板40に形成された位置合わせ用の貫通孔である孔部41に挿入して、サブ基板40とキャビティ51の平面的位置関係を調整する。

#### 【0068】

なお、サブ基板40の位置合わせを行う観点からは、少なくとも、1組のピン54と孔部41を設ければ良い。しかし、より高精度で位置合わせを行う観点からは、本実施の形

10

20

30

40

50

態のように複数のピン 5 4 と複数の孔部 4 1 をそれぞれ設けることが好ましい。

#### 【 0 0 6 9 】

また、本工程では、サブ基板 4 0 をキャビティ 5 1 の底面 5 1 a 上に載置するが、底面 5 1 a 側からサブ基板 4 0 の正面 5 a 側を吸引するなどの作業は特に行っていない。サブ基板 4 0 の正面 5 a には、図 1 に示すチップ部品 4 はこの段階では搭載されておらず、略平坦である。また、正面 5 a の外形寸法は、底面 5 1 a の外形寸法よりも小さい。また、後述する封止体形成工程では、封止用の樹脂をベース基板 3 0 とサブ基板 4 0 の間に供給する。また、本実施の形態では、ベース基板 3 0 とサブ基板 4 0 をそれぞれ別個に準備して、本封止工程において封止樹脂を形成することにより一体化するので、サブ基板 4 0 の裏面 5 b 側から封止用の樹脂を供給すると、この供給圧力によりサブ基板 4 0 は底面 5 1 a の方向に押圧されることとなる。したがって、正面 5 a を吸着しなくても、後述する封止体形成工程においては、正面 5 a と底面 5 1 a を密着させることができる。

10

#### 【 0 0 7 0 】

次に、封止工程は、前記した基材準備工程で準備したベース基板 3 0 を成型金型 5 0 に配置する第 2 の基材配置工程を有している。図 1 3 は図 1 1 に示す成型金型の下型に図 4 および図 5 に示す配線基板を配置した状態を示す要部拡大平面図、図 1 4 は図 1 3 に示す B - B 線に沿った要部拡大断面図である。

#### 【 0 0 7 1 】

本工程では、ベース基板 3 0 の正面 3 a が、サブ基板 4 0 の裏面 5 b と対向するように、ベース基板 3 0 を上型 5 0 b と下型 5 0 a の間（詳しくは上型 5 0 b とサブ基板 4 0 の間）に配置する。つまり、ベース基板 3 0 の上下を反転して、正面 3 a を下向きにした状態で、下型 5 0 a に配置する。また、ベース基板 3 0 の正面 3 a は、下型 5 0 a の上面 5 2 の平面におけるキャビティ 5 1 の開口面積よりも広い面積を有し、ベース基板 3 0 の枠部 3 0 b の正面 3 a 側と下型 5 0 a の上面 5 2 とが当接する。このため、ベース基板 3 0 とサブ基板 4 0 の厚さ方向の位置関係は、キャビティ 5 1 の深さにより規定される。具体的には、ベース基板 3 0 、サブ基板 4 0 の厚さ、およびベース基板 3 0 の正面 3 a からワイヤ 1 5 のワイヤループの頂点までの高さの合計よりもキャビティ 5 1 の深さ（上面 5 2 から底面 5 1 a までの高低差）を深くすることにより、ワイヤ 1 5 をサブ基板 4 0 の裏面 5 b に接触させることなく離間して配置することができる。

20

#### 【 0 0 7 2 】

また、本工程では、下型 5 0 a の上面 5 2 上に形成されたピン 5 5 がベース基板 3 0 の孔部 3 1 内に位置するようにベース基板 3 0 を配置する。詳しくは、ピン 5 5 をベース基板 3 0 に形成された位置合わせ用の貫通孔である孔部 3 1 に挿入して、ベース基板 3 0 と下型 5 0 a の平面的位置関係を調整する。

30

#### 【 0 0 7 3 】

ところで、本実施の形態では、ベース基板 3 0 とサブ基板 4 0 をそれぞれ別個に準備して、これらの平面的な位置関係の調整は、成型金型 5 0 を介して位置合わせを行うことにより行う。本実施の形態では、後述する電気的接続工程で、各基板に形成された複数の端子（ランド 1 2 、 2 2 ）同士をそれぞれ接続する必要があるため、各基板に形成された製品形成領域 3 0 a 、 4 0 a の平面的位置関係を高い精度で合わせる必要がある。したがって、本実施の形態では、より高精度で位置合わせを行う観点から、サブ基板 4 0 については、複数のピン 5 4 と複数の孔部 4 1 をそれぞれ設けて位置合わせを行い、ベース基板 3 0 については、複数のピン 5 5 と複数の孔部 3 1 をそれぞれ設けて位置合わせを行っている。これにより、位置合わせ用のピン 5 4 、 5 5 と孔部 4 1 、 3 1 を設けない場合、あるいはそれぞれ 1 組の位置合わせ用のピン 5 4 、 5 5 と孔部 4 1 、 3 1 を設けた場合と比較して位置合わせ精度を向上させることができる。

40

#### 【 0 0 7 4 】

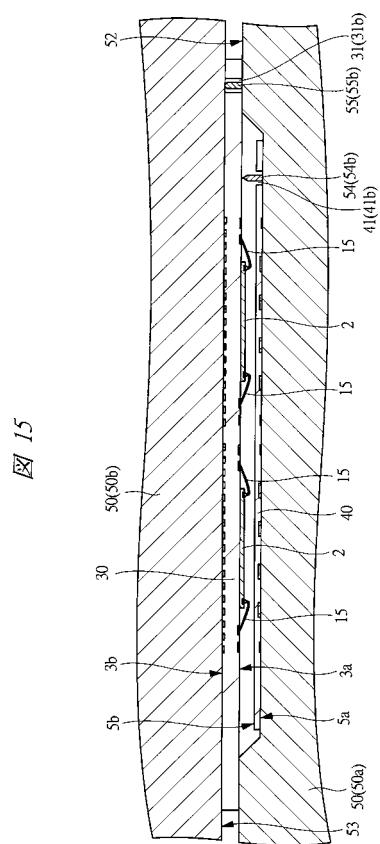

次に、封止工程は、前記した第 2 の基板配置工程の後、ベース基板 3 0 を上型 5 0 b と下型 5 0 a で挟み込んでクランプするクランプ工程を有している。図 1 5 は、図 1 4 に示す配線基板（ベース基板）を成型金型で挟み込んでクランプした状態を示す要部拡大断面

50

図である。

**【0075】**

本工程では、上型50bの下面53側をベース基板30の裏面3bに、下型50aの上面52側をベース基板30の主面3aに押しつけてベース基板30をしっかりと固定する。

**【0076】**

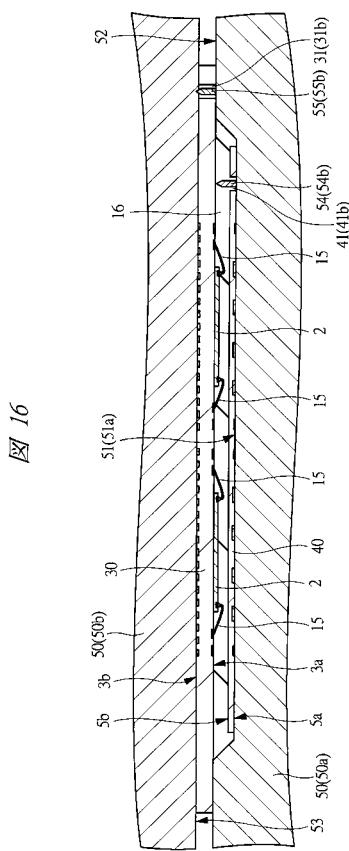

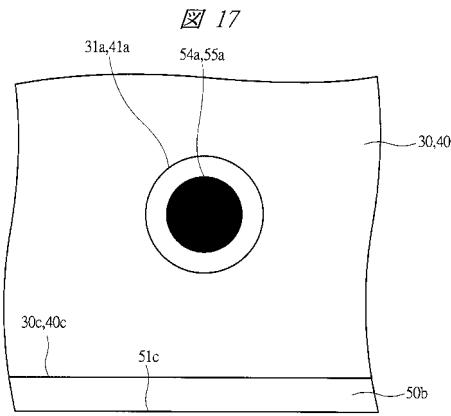

次に、封止工程は、前記したクランプ工程後、サブ基板40とベース基板30との間に樹脂を供給し、サブ基板40とベース基板30との間に封止体を形成する封止体形成工程を有している。図16は図15に示す2つの配線基板の間に、封止体を形成した状態を示す要部拡大断面図である。また、図17は、図11あるいは図13に示す配線基板の膨張を制御する基準点周辺を拡大して示す要部拡大平面図、図18は、図11あるいは図13に示す配線基板の膨張を制御する補助点周辺を拡大して示す要部拡大平面図である。

10

**【0077】**

本工程では、ベース基板30の主面3aとサブ基板40の裏面5bの間の空間内に、図示しないゲート部から封止用の樹脂を供給する。供給する樹脂は、ゲート部とは反対側に位置するエアベント部（図示は省略）の方向に流れ、ベース基板30の主面3aとサブ基板40の裏面5bの間の空間は封止樹脂で満たされる。

**【0078】**

その後、供給した樹脂を加熱硬化させると、図16に示す封止樹脂16が形成される。この封止樹脂16が形成されると、ベース基板30の主面3aとサブ基板40の裏面5bとは封止樹脂16を介して接着され、別個の構造物であったベース基板30とサブ基板40とが一体化される。

20

**【0079】**

なお、加熱硬化について詳しく説明すると、成型金型50内で供給された封止用の樹脂は、例えば180程度に加熱され、樹脂中の硬化成分の半分以上（例えば約70%程度）が硬化する、所謂、仮硬化と呼ばれる状態となる。この仮硬化の状態では、樹脂中の全ての硬化成分が硬化している訳ではないが、半分以上の硬化成分が硬化しているため、図16に示す封止樹脂16と密着するベース基板30とサブ基板40は固定される。しかし、封止樹脂の強度の安定性などの観点からは全ての硬化成分を完全に硬化させることができないので、後述する取り出し工程の後で、封止樹脂16が仮硬化したベース基板30およびサブ基板40を有する一括封止構造体を加熱炉に移動させて再度加熱する、所謂本硬化を行う。

30

**【0080】**

ここで、本実施の形態では、本工程を行う段階では、ベース基板30とサブ基板40を電気的に接続する導電性部材（図1に示す半田材8）は形成されていない。このため、ベース基板30とサブ基板40を電気的に接続する電極（すなわち、図4に示すランド12と図6に示すランド22）の数が増加しても、封止用の樹脂を供給する際に樹脂の流れを阻害する障害物とはならない。したがって、予めベース基板30とサブ基板40を電気的に接続した後で封止体を形成する場合と比較して、樹脂を安定的に供給することができる。また、本工程において、注入される封止用の樹脂内に空気を巻き込んで、封止樹脂16の内部に空気が残留することを防止することができる。このため、信頼性の高い半導体装置を得ることができる。また、本実施の形態のように、複数の製品形成領域30a、40a（図11または図13参照）を1つのキャビティ51内に配置してこれら複数の製品形成領域30a、40aを一括して封止する場合、各製品形成領域30a、40a毎に封止する場合と比較して、1個のキャビティ51内の空間が広い。このため、封止用の樹脂を供給する際の空気の巻き込みをより防止することができる。

40

**【0081】**

また、本工程では、供給する樹脂の流動性を向上させる目的、あるいは供給した樹脂を硬化（仮硬化）させる目的で、成型金型50のキャビティ51内の空間を加熱した状態で行う。ところが、この熱影響により、ベース基板30およびサブ基板40がそれぞれ熱膨

50

張する。前記したように、本実施の形態では、ベース基板30の製品形成領域30a(図4参照)とサブ基板40の製品形成領域40a(図6参照)の平面的な位置関係を高精度で位置合わせすることが重要である。しかし、ベース基板30とサブ基板40とがそれぞれ無秩序に膨張すると、位置関係がずれてしまうという新たな課題が生じる。

#### 【0082】

熱膨張による製品形成領域の位置ズレを防止する観点からは、配線基板(ベース基板30あるいはサブ基板40)の熱膨張を防止することが好ましい。しかし、配線基板の熱膨張を完全に防止することは困難であり、また、熱膨張を防止するために、配線基板の材料や構成部材のレイアウトなどを限定し過ぎると、設計の自由度が大幅に低下する。そこで、本願発明者は、前記したピン54、55と孔部31、41を設けることにより膨張方向を制御して製品形成領域30a、40aの平面的位置関係のズレを防止ないしは抑制する必要がある。10

#### 【0083】

具体的には、本実施の形態ではピン54、55をキャビティ51の底面の外形を構成する4辺のうちの1辺(本実施の形態では図10に示す長辺51c)に寄せて(対向配置される辺よりも近づけて)配置する。また、孔部31、41はピン54、55の位置に対応して、ベース基板30およびサブ基板40の外形を構成する4辺のうちの1辺(本実施の形態では図4に示す長辺30cあるいは図6に示す長辺40c)に寄せて配置している。これにより、ピン54、55と孔部31、41が重なった位置が固定されるため、固定された位置を基準点として膨張方向を制御することができる。20

#### 【0084】

なお、基準点の位置としては、本実施の形態のように1辺に寄せて配置する他、各基板の略中央に配置することも考えられる。例えば、図10において、キャビティ51内に形成されるピン54を底面51aの略中央に配置する方法が考えられる。しかしこの場合、図6に示すサブ基板40の孔部41もこれに対応して略中央に配置することとなるため、製品形成領域40a内に、孔部41を形成することとなるので、孔部41を形成した領域を取り除く工程が別途必要となり製造効率が低下してしまう。そこで、本実施の形態のように、位置合わせ用のピン54と孔部41をサブ基板40が有する製品形成領域40aよりも外側に位置する枠部40b(あるいは枠部40bと重なる位置)に形成することが好ましい。枠部40bは各製造工程において、サブ基板40に加工を施す際の作業用のスペースであり、位置合わせ用のピンの有無に係らず、最終的に切断して取り除くスペースである。したがって、この枠部40bに形成することにより、製造効率の低下を抑制することができる。また、スペースの有効活用という観点からも好ましい。30

#### 【0085】

また、基準点となるピンおよび孔部は、寄せて配置する辺の中央部に配置されている。本実施の形態では、図10に示すピン54a、55a、図4に示す孔部31a、および図6に示す孔部41aがこれに相当する。このように基準となるピン54a、55aおよび孔部31a、41aを寄せて配置する辺の中央部に配置すると、基準点から各基板(ベース基板30あるいはサブ基板40)の端部までの距離が短くなる。各基板の熱膨張を考慮すると、基準点からの距離が長くなる程、ズレの程度は大きくなる。したがって、基準点から端部までの距離を短くすることにより、ズレの程度を低減することができる。40

#### 【0086】

また、基準点から最も遠い端部までの距離を短くするという観点からは、基準点となるピン54a、55aおよび孔部31a、41aはそれぞれ長辺51c、30c、40cに寄せて配置することが好ましい。

#### 【0087】

また、前記の通り基準点からの距離が遠くなる程ズレの程度は大きくなる。つまり、図11あるいは図13に示す基準点となるピン54a、55aのみを設けた場合には、矢印42の方向にズレが大きくなる。そこで、本実施の形態では、図10に示すように基準点となるピン54a、55aが寄せて配置される長辺51cに沿って基準点となるピン54

10

20

30

40

50

a、55aの両サイドに熱膨張の制御を補助する補助点としてピン54b、55bをそれぞれ配置している。

#### 【0088】

また、これに対応して、図4に示すベース基板30では、基準点となる孔部31aが寄せて配置される長辺30cに沿って基準点となる31aの両サイドに熱膨張の制御を補助する補助点として孔部31bを配置している。同様に、図6に示すサブ基板40では、基準点となる孔部41aが寄せて配置される長辺40cに沿って基準点となる41aの両サイドに熱膨張の制御を補助する補助点として孔部41bを配置している。また、サブ基板40、ベース基板30を配置する工程では、孔部41bがピン54bと、孔部31bがピン55bと、重なるように配置している。これにより、図11あるいは図13に示す矢印42の方向のズレを抑制することができる。10

#### 【0089】

また、本実施の形態では膨張方向を制御する基準点として用いている孔部31a、41aと、膨張方向の制御する補助点となる孔部31b、41bとでは、異なる開口形状をしている。具体的には、図17に示すように、孔部31a、41aの開口形状は、挿入するピン54a、55aの外形（平面形状）に沿って形成している。本実施の形態では、円形の外形を有するピン54a、55aに沿って、孔部31a、41aの開口形状も円形に形成している。一方、図18に示すように、孔部31b、41bの開口形状は、細長く形成している。詳しくは、配線基板（ベース基板30あるいはサブ基板40）の長辺30c、40cに沿う方向の開口幅Waが長辺30c、40cと交差する方向（図4あるいは図6に示す短辺30d、40dに沿う方向）の開口幅Wbよりも長くなるように形成している。このため、長辺30c、40cについては基準点となる孔部31a、41aとピン54a、55aとの間の隙間（クリアランス）よりも、補助点となる孔部31b、41bとピン54b、55bとの間の隙間（クリアランス）の方が広い。20

#### 【0090】

このように基準点と補助点とで、孔部31、41を異なる開口形状とするのは、以下の観点からである。すなわち、配線基板の熱膨張を制御するためには、基準点のズレを小さくすることが重要である。このため、基準点となる孔部31a、41aの開口形状は、挿入するピン54a、55aの外形（平面形状）に沿って形成し、孔部31a、41aにピン54a、55aを挿入する観点から必要な最低限のクリアランスとしている。30

#### 【0091】

一方、補助点である孔部31b、41bとピン54b、55bとのクリアランスを基準点と同様に狭くすると、配線基板（ベース基板30あるいはサブ基板40）が熱膨張した際にピン54b、55bから配線基板に強い応力が印加され、応力の強さによっては配線基板が変形、あるいは損傷する場合がある。そこで、図18に示すように補助点である孔部31b、41bは基準点である孔部31a、41aよりもクリアランスを広くすることにより、ピン54b、55bから印加される応力を逃がすことができるので、応力を緩和することができる。また、長辺30c、40cに沿う方向の開口幅Waを開口幅Wbよりも広くすることにより、配線基板が膨張する方向を図11や図13に示す矢印43の方向に制御することができる。40

#### 【0092】

また、本実施の形態では、膨張を制御する基準点（ピン54a、55a、孔部31a、41a）および補助点（ピン54b、55b、孔部31b、41b）をそれぞれ同じ辺側に寄せて（対向配置される辺よりも近づけて）配置している。換言すれば、サブ基板40の孔部41は4つの辺のうち長辺40cに近づけて配置され、ベース基板30の孔部31は、4つの辺のうち、長辺40cに沿って配置される長辺30cに近づけて配置されている。これにより配線基板が熱膨張する際の膨張方向を揃えることができる。

#### 【0093】

なお、配線基板が熱膨張する際の膨張方向は、材料の物性値（熱膨張係数）によりある程度予測することができる。したがって、封止樹脂16が硬化し、ベース基板30とサブ50

基板 4 0 が固定された状態で、各配線基板の複数の製品形成領域の位置がそれぞれ揃っていれば、膨張方向は揃っていないとも良い。つまり、例えば、ベース基板 3 0 の基準点（ピン 5 5 a、孔部 3 1 a）および補助点（ピン 5 5 b、孔部 3 1 b）と、サブ基板 4 0 の基準点（ピン 5 4 a、孔部 4 1 a）および補助点（ピン 5 4 b、孔部 4 1 b）とを異なる辺に寄せて配置することができる。

#### 【0094】

しかし、この場合には、各配線基板の膨張速度や封止樹脂 1 6 の硬化速度など、複雑な要素を考慮する必要がある。したがって、本実施の形態のように膨張方向を揃えることは、容易に各配線基板の製品形成領域の位置を揃えることができるという観点から特に好ましい。

10

#### 【0095】

また、本実施の形態では、前記したように孔部 3 1、4 1 は正面 3 a、5 a から裏面 3 b、5 b まで貫通する貫通孔としている。また、ピン 5 4、5 5 はそれぞれサブ基板 4 0 の裏面 5 b、あるいはベース基板 3 0 の裏面 3 b の上側まで突出する長さを有している。すなわち、ピン 5 4 の長さはサブ基板 4 0 の厚さよりも長く、ピン 5 5 の長さはベース基板 3 0 の厚さよりも長い。前記した第 1 あるいは第 2 の基材配置工程で、ベース基板 3 0 やサブ基板 4 0 の位置合わせを行うのみであれば、孔部 3 1、4 1 を貫通孔とせず、それぞれ正面 3 a、5 a に形成された穴（窪み部、凹部）とすれば良い。しかし、本実施の形態では、ピン 5 4、5 5 および孔部 3 1、4 1 を、配線基板の熱膨張方向を制御する基準点あるいは補助点として用いている。このように膨張方向を制御する観点からは、より強固な力で配線基板とピンとの位置関係を保持する必要がある。このため、孔部 3 1、4 1 を貫通孔とし、ピン 5 4、5 5 の長さをベース基板 3 0 あるいはサブ基板 4 0 の厚さよりも厚くすることがより好ましい。

20

#### 【0096】

次に、封止工程は、前記した封止工程で用いた成型金型 5 0 から封止樹脂 1 6 が形成されたベース基板 3 0 およびサブ基板 4 0 を取り出す取り出し工程を有している。図 1 9 は図 1 6 に示す成型金型から取り出して上下を反転させた一括封止構造体を示す断面図である。

#### 【0097】

本工程では、図 1 6 に示す上型 5 0 b の下面 5 3 と下型 5 0 a の上面 5 2 を引き離し、封止樹脂 1 6 が形成され、ベース基板 3 0 とサブ基板 4 0 が封止樹脂 1 6 を介して固定された一括封止構造体 4 5 を取り出す。この段階では、ベース基板 3 0 とサブ基板 4 0 は、接着固定はされているが、電気的には接続されていない。また、本工程では、必要に応じて前記した封止工程で発生した樹脂バリなどの除去を行う。

30

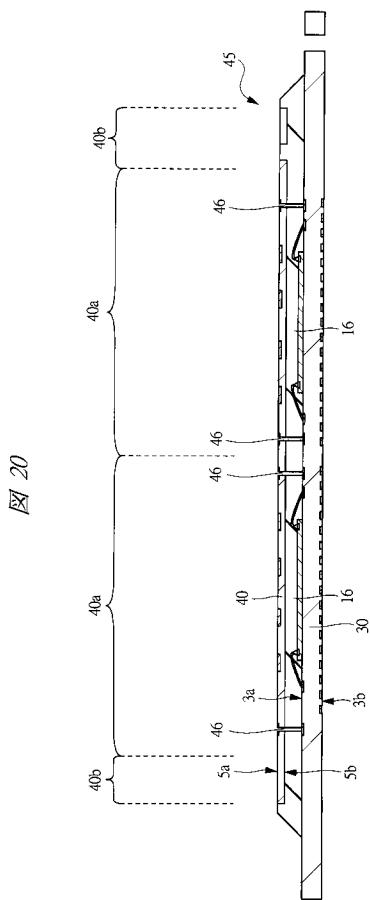

#### 【0098】

次に、一括封止構造体 4 5 が有するベース基板 3 0 とサブ基板 4 0 とを電気的に接続する電気的接続工程について説明する。電気的接続工程には、取り出した一括封止構造体のサブ基板 4 0 のランドからベース基板 3 0 のランドに向かって貫通孔を形成する貫通孔形成工程と、該貫通孔内に導電性部材を形成する導電性部材形成工程とを有している。図 2 0 は、図 1 9 に示す一括封止構造体に複数の貫通孔を形成した状態を示す断面図、図 2 1 は、図 1 9 に示す貫通孔を形成した後の一括封止構造体の上面を、1 つの製品形成領域について拡大して示す拡大平面図、図 2 2 は、図 2 1 に示す貫通孔の 1 つを拡大して示す要部拡大平面図、図 2 3 は図 2 2 に示す C - C 線に沿った要部拡大断面図である。

40

#### 【0099】

まず、貫通孔形成工程では、サブ基板 4 0 の正面 5 a に形成されたランド 2 2 からベース基板 3 0 の正面 3 a に形成されたランド 1 2 に向かって貫通孔 4 6 を形成し、ランド 1 2 を露出させる。本工程では、図 2 0 あるいは図 2 1 に示すように各製品形成領域 4 0 a のそれぞれに形成された複数のランド 2 2 に対して複数の貫通孔 4 6 を形成する。

#### 【0100】

ここで、貫通孔 4 6 の「貫通」とは、サブ基板 4 0 および封止樹脂 1 6 を厚さ方向に貫

50

通することを指す。前記した封止工程で説明したように、本実施の形態ではベース基板30とサブ基板40の平面的位置関係を高精度で位置合わせすることができる。このため、ランド22からランド12に向かって、下方向に封止樹脂16などの各部材を取り除くことにより、ランド12を露出させることができる。

#### 【0101】

また、図22に示すように貫通孔46の開口径Wcは、ランド22の幅Wdよりも狭い。換言すれば、貫通孔46の開口面積はランド22の表面の面積よりも狭い。このため、本工程において、図22に示すように貫通孔46の周囲を環状のランド22が取り囲んだ状態となる。また、図23に示すように開口径Wcはランド12の幅Weよりも狭い。換言すれば、貫通孔46の開口面積はランド12表面の面積よりも狭い。つまり、後述する導電性材料形成工程において、貫通孔46内に形成する導電性部材とランド12との接合面の面積は、ランド12の表面の面積よりも狭い。このため、位置合わせ精度や加工精度等の影響により、ランド12とランド22の平面的位置関係が僅かにずれた場合であっても確実にランド12およびランド22を接続することができる。10

#### 【0102】

本工程において、ランド22の表面からランド12の表面に至るまでに積層されている封止樹脂16などの各部材を取り除く手段、すなわち、貫通孔形成手段としては、レーザ加工法やエッティング法など種々の方法を挙げることができる。しかし、本実施の形態では、封止樹脂16を厚さ方向に貫通する必要があり、かつ、貫通孔46の開口径Wcは前記したように狭くする必要がある。このように狭く長い貫通孔46を形成するためには、加工精度や加工効率の観点からレーザ加工により行うことが好ましい。具体的には、サブ基板40の正面5a側、詳しくはランド22の表面側からレーザ光を照射して、サブ基板40および封止樹脂16を取り除き、ランド12を露出させる。これにより貫通孔46を形成することができる。なお、本実施の形態では、サブ基板40の正面5aにランド22を形成する段階で、ランド22を予め環状(ドーナツ状)に形成している。つまり、貫通孔46を形成する領域にはランド22が形成されず、サブ基板40の絶縁層が露出している。このため、レーザ加工により貫通孔46を形成する際に、レーザの出力を低減することができる。ただし、予め形成するランド22は、例えば円形のベタパターンとして形成することともできる。この場合、本工程において、レーザの出力などを調整することにより、ベタパターンのランド22の略中央を取り除き、貫通孔46を形成する。20

#### 【0103】

次に、導電性部材形成工程では、貫通孔46の内部に導電性部材を形成してベース基板30とサブ基板40とを電気的に接続する。図24は図21に示す貫通孔内に導電性部材を形成した状態を示す断面図、図25は、図24に示す1つの貫通孔周辺を拡大して示す要部拡大断面図である。

#### 【0104】

本工程では、図24に示すように複数の貫通孔46(図19参照)それぞれの内部に導電性部材である半田材8を形成し、ベース基板30とサブ基板40を電気的に接合する。詳しくは、半田材8をランド22とランド12にそれぞれ接合することによりこれらを電気的に接続する。40

#### 【0105】

また、半田材8は、少なくともランド12とランド22の両方に接触していれば、電気的に接続することが可能であるが、半田材8とランド22との接触面積を拡大させて、接続信頼性を向上させる観点からは、図25に示すように、半田材8を貫通孔46よりも外側にまで形成し、ランド22の表面を半田材8で覆うように形成することが好ましい。

#### 【0106】

また、本実施の形態のように、ランド12とランド22を、半田材8を用いて電気的に接続する場合には、半田材8として融点の高い材料を用いることが好ましい。後述するボールマウント工程や、サブ基板上に電子部品を実装する工程、あるいは完成した図1に示50

す P O P 1 を実装基板に搭載する工程などの加熱工程において、半田材 8 が再溶融することを防止するためである。一方、融点が極端に高い材料を用いると、半田材 8 を形成する際に必要な温度が高くなりすぎてしまう。そこで、半田材 8 の融点は、後述するボールマウント工程でベース基板 30 の裏面側に搭載する半田ボール 17 (図 1 参照) の融点よりも高くすることが好ましい。具体的には、融点がリフロー温度よりも高い約 300 度の融点の材料を用いることが好ましい。このような材料としては、例えば、Sn - 10 Agなどを例示することができる。

#### 【 0 1 0 7 】

また、半田材 8 を形成する手段としては、所謂ソルダシューと呼ばれる溶融半田の滴下装置を用いて溶融した半田を貫通孔 46 内に滴下して埋め込む方法、あるいは貫通孔 46 内に半田をめっき形成する方法を挙げることができる。これらの方法の場合、開口径が狭く、ランド 12 までの距離が長い貫通孔 46 であっても、確実に貫通孔 46 内に導電性部材を形成することができる点で好ましい。

#### 【 0 1 0 8 】

また、半田材 8 の変形例として、ペースト状の樹脂に、例えば Ag などの金属粒子を分散させた導電性ペーストと呼ばれる材料を用いることもできる。この場合、導電性ペーストを貫通孔 46 内に埋め込んで、その後硬化させることとなる。導電性ペーストの場合、金属粒子を分散させる樹脂成分により粘度を調整することができる。また、樹脂成分として、熱硬化性の樹脂材料を用いることにより、一度硬化させればその後加熱しても再溶融しないので、安定してランド 12 とランド 22 の電気的接続を確保することができる。

#### 【 0 1 0 9 】

また、半田材 8 の別の変形例として、半田と異なる金属材料（例えば銅など）をめっき法により形成することもできる。この場合には、開口径が狭く、ランド 12 までの距離が長い貫通孔 46 であっても、確実に貫通孔 46 内に導電性部材を形成することができる。また、図 1 に示す半田ボール 17 よりも融点が高い金属材料をめっき形成することにより、その後の加熱工程による再溶融を防止することができるので、安定してランド 12 とランド 22 の電気的接続を確保することができる。

#### 【 0 1 1 0 】

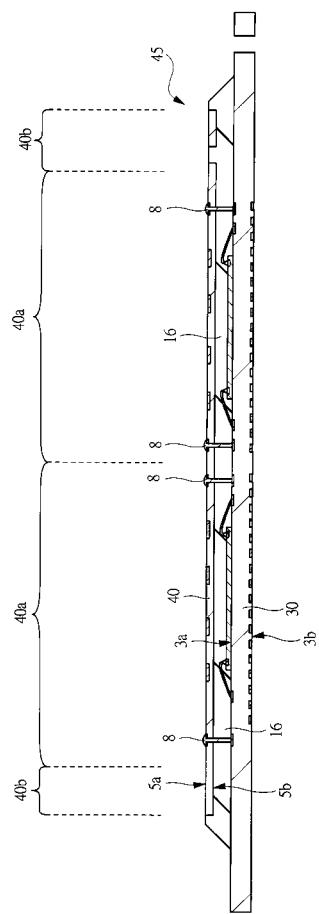

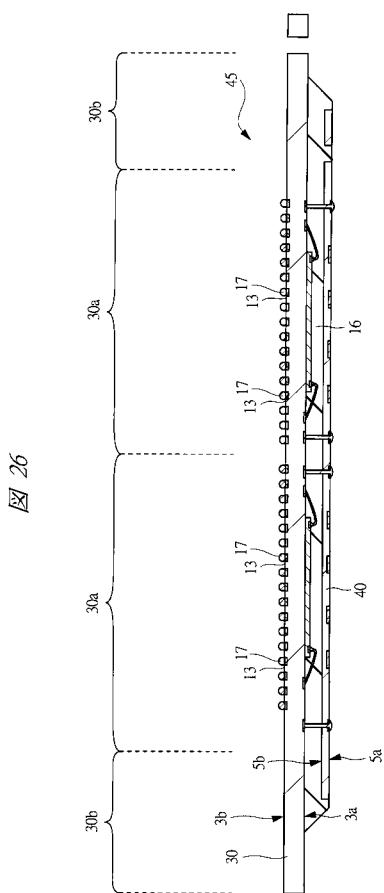

次に、ボールマウント工程として、図 24 に示すベース基板 30 の裏面側に形成された複数のランドのそれぞれに複数の半田ボールを搭載する。図 26 は、図 24 に示す一括封止構造体の裏面側に半田ボールを搭載した状態を示す断面図である。

#### 【 0 1 1 1 】

本工程では、図 26 に示すように一括封止構造体 45 の上下を反転させて、ベース基板の裏面 3b 側に形成された複数のランド 13 に複数の半田ボール 17 をそれぞれ搭載（接合）する。

#### 【 0 1 1 2 】

本実施の形態では、ボールマウント工程を電気的接続工程の後で行っているが、ボールマウント工程を実施する工程順序は、これには限定されない、例えば、半田材 8 を前記したソルダシューにより滴下して行う場合、あるいは半田材 8 に代えて導電性ペーストを用いる場合には、ボールマウント工程を先に実施し、その後、前記した電気的接続工程を実施することもできる。ただし、半田材 8 をめっき形成する場合、あるいは半田以外の金属材料をめっき形成する場合には、めっき工程の時点では、半田ボール 17 が形成されていない事が好ましいので、本工程は、電気的接続工程の後で行うことが好ましい。また、本工程は、後述する個片化工程、あるいは電子部品搭載工程の後で行うこともできる。

#### 【 0 1 1 3 】

次に、個片化工程として、図 26 に示す一括封止構造体 45 を製品形成領域毎に切断し、個々のパッケージに分割（個片化）する。図 27 は、図 26 に示す一括封止構造体を切断した状態を示す断面図、図 28 は図 26 に示す個片化された配線基板の 1 個を示す断面図である。

#### 【 0 1 1 4 】

10

20

30

40

50

本工程では、例えば、ダイシングブレードと呼ばれる切断治具を、製品形成領域 30 a に沿って走査して一括封止構造体 45 (図 26 参照) を切断し、図 27 あるいは図 28 に示す積層配線基板 (電子装置、半導体装置) 47 を複数個取得する。

#### 【0115】

積層配線基板 47 は、図 28 に示すようにベース基板 3 とサブ基板 5 が積層された配線基板である。ベース基板 3 とサブ基板 5 は封止樹脂 16 を介して接着固定され、半田材 8 を介して電気的に接続されている。サブ基板 5 の正面 5 a には複数の端子 21 が形成され、この複数の端子 21 は半田材 8 を介してベース基板 3 の裏面 3 b に形成された外部端子であるランド 13 と電気的に接続されている。また、ベース基板 3 とサブ基板 5 の間には、半導体チップ (電子部品) 2 が搭載され、封止樹脂 16 により封止されている。つまり、積層配線基板 47 は、半導体チップ 2 を内蔵する配線基板である。また、換言すれば、積層配線基板 47 は、ベースパッケージ 6 上にサブ基板 5 が接着固定され、サブ基板とベースパッケージ 6 が電気的に接続された半導体装置 (電子装置) であるとも言える。

#### 【0116】

この積層配線基板 47 は、ベースパッケージ 6 を含んでいるので、サブ基板 5 の正面 5 a 上に図 1 に示すようなチップ部品 4 を搭載しなくても、電気的に駆動させることができある。したがって、この積層配線基板 47 の状態で完成品とすることもできる。この場合、必要に応じて電気的検査や外観検査を行い良品について出荷する。なお、この場合、サブ基板 5 の正面 5 a に形成された複数の端子 21 は、別の場所で、必要に応じてチップ部品 4 (図 1 参照) を実装するための拡張用の端子となる。

#### 【0117】

また、図 1 に示す P O P 1 を完成品とする場合には、電子部品搭載工程として、正面 5 a 上に図 1 あるいは図 2 に示す複数のチップ部品 4 を搭載する。チップ部品 4 が有する複数の端子 4 d は、例えば、クリーム半田と呼ばれるペースト状の半田、あるいは半田ボールなどの半田材 23 (図 1 参照) を介して複数の端子 21 とそれぞれ電気的に接続する。

#### 【0118】

以上説明したように、本実施の形態によれば、ベース基板 30 とサブ基板 40 の間に封止樹脂 16 を形成した後でこれらを電気的に接続するので、封止体形成工程において、封止体内への空気残留抑制などが可能となり、信頼性の高い半導体装置を得ることができる。

#### 【0119】

また、ベース基板 30 と半導体チップ 2 を、ワイヤ 15 を介して電気的に接続する場合であっても、ベース基板 30 とサブ基板 40 を電気的に接続する際には、ワイヤ 15 は封止樹脂 16 により保護されているので、洗浄工程などを実施する必要がないため、洗浄によりワイヤ 15 が変形することはない。

#### 【0120】

また、本実施の形態によれば、それぞれ別個に準備したベース基板 30 とサブ基板 40 を成型金型 50 内で一体化するので、仮に、ベース基板 30 とサブ基板 40 の対向させる面 (正面 3 a および裏面 5 b ) のいずれか一方、あるいは両方がアウトガスにより汚染された場合であっても、成型金型 50 に配置する前にプラズマを照射して容易に清浄化することができる。このため、各配線基板と封止樹脂の密着性の低下を防止することができる。

#### 【0121】

また、一般に P O P は下段側のパッケージと上段側のパッケージを個別に準備して、これらを積層する。しかし、本実施の形態によれば、M A P により複数の P O P を一括して形成することができるので、製造効率を向上させることができる。

#### 【0122】

##### (実施の形態 2)

前記実施の形態 1 では、2 枚の配線基板 (基材) を積層した半導体装置の実施態様について説明したが、積層する配線基板の数は 2 枚に限定されない。本実施の形態 2 では、3

10

20

30

40

50

枚以上の配線基板（基材）を積層する実施態様について説明する。なお、本実施の形態では、前記実施の形態1との相違点を中心に説明し、前記実施の形態1と重複する説明は原則として省略する。

#### 【0123】

図29は本実施の形態の半導体装置の全体構造を示す断面図である。図29に示す本実施の形態2のPOP60と前記実施の形態1で説明したPOP1との相違点は、ベース基板3上に搭載されるサブ基板63の正面5aが、封止樹脂61により封止され、さらにその上にサブパッケージ62が搭載されている点である。サブパッケージ62は例えば、前記実施の形態1で説明したサブパッケージ7と同じ構造のパッケージであり、前記実施の形態1で説明したサブ基板5を有している。ただし、ランド22のレイアウトは、中段に配置されるサブ基板63の有するランド22と重ならない位置に形成されている。またサブパッケージ62の裏面5bは、封止樹脂61と密着し、サブ基板63と一体化されている。また、中段に配置されるサブパッケージ65およびサブパッケージ65が有するサブ基板63は、最上段に配置されるサブ基板5と区別するために、別の符号を付している。しかし、封止樹脂61が形成されている点、およびサブ基板63の正面5aに、複数のランド22に加えて、サブ基板5との基板間接続用の電極である複数のランド64が形成されている点を除き、前記実施の形態1で説明したサブパッケージ7、サブ基板5と同じ構造である。

10

#### 【0124】

サブ基板63の正面5aに形成されたランド（端子、基板間接続端子）64は、サブ基板5に形成されたランド22と厚さ方向に重なる位置に配置され、半田材8を介して電気的に接続されている。またランド64は、図示しない配線を介してサブ基板63の正面5aに形成された端子21あるいはランド22と電気的に接続されている。つまり、中段に配置されたサブ基板63とサブ基板63よりも上段側に配置されたサブ基板5とが、半田材8を介して電気的に接続されている。また、サブ基板5は、サブ基板63を介してベース基板3と電気的に接続されている。このように前記実施の形態1で説明した技術を応用して、3枚以上の配線基板を積層することもできる。なお、サブ基板63とサブ基板5を電気的に接続する半田材8には、前記実施の形態1で説明したように、種々の変形例を適用することができることは言うまでもない。

20

#### 【0125】

30

図29に示すPOP60のような3枚以上の配線基板を積層した半導体装置は、前記実施の形態1で説明した製造方法を応用して製造することができる。以下、前記実施の形態1との相違点を中心に説明する。図30は本実施の形態2の半導体装置の製造方法における第3の基板配置工程を示す要部拡大断面図、図31は、図30に示す配線基板上に一括封止構造体を配置した状態を示す要部拡大断面図、図32は図31に示す一括封止構造体と配線基板の間に第2の封止体を形成した状態を示す要部拡大断面図である。

#### 【0126】

本実施の形態2の半導体装置の製造方法では、前記実施の形態1で説明した基材準備工程、封止工程、電気的接続工程、電子部品搭載工程を行った後、さらに第2の封止工程を行う。

40

#### 【0127】

この第2の封止工程は、前記実施の形態1で説明した封止工程（第1の封止工程）と同様に、所謂MAPにより行う。まず、成型金型準備工程では、図30に示す上型（金型）50bと下型（金型）66aとを備える成型金型66を準備する。なお、前記実施の形態1で説明した成型金型50（図10参照）と本実施の形態2の成型金型66は、下型66aが有するキャビティ67の深さ、すなわち上面52から底面51aまでの高低差、および上面52におけるキャビティ67の開口面積を除き同じ構造である。

#### 【0128】

キャビティ67は前記実施の形態1で説明したキャビティ51（図9参照）よりも深く形成されている。これは、図31に示すように、サブ基板68とサブ基板40を離間して

50

配置するためである。

**【0129】**

また、上面52におけるキャビティ67の開口面積は、キャビティ51の開口面積よりも広く形成されている。これは、前記実施の形態1で説明した封止工程で形成した封止樹脂16をキャビティ67内に収納し、上面52とベース基板30の枠部を密着させるためである。

**【0130】**

次に、第3の基材配置工程として、図30に示すように3枚目の基材となるサブ基板40を配置する。本工程では、前記実施の形態1で説明した第1の基材配置工程と同様に、サブ基板40の正面5aが、下型66aのキャビティ67と対向するように(詳しくは、キャビティ67の底面51aと対向するように)キャビティ67内に配置する。なお、この時、キャビティ67の底面51aに形成されたピン54をサブ基板40に形成された孔部41に挿入する点については、前記実施の形態1と同様である。

10

**【0131】**

次に、第4の基材配置工程として、図31に示すように、ベース基板30とサブ基板68とが積層され、封止樹脂16を介して固定された一括封止構造体69を配置する。なお、サブ基板68は、サブ基板40と区別するために別の符号を付している。しかし、正面5aに、複数のランド22(図29参照)に加えて、サブ基板40との基板間接続用の電極である複数のランド64(図29参照)が形成されている点を除き、前記実施の形態1で説明したサブ基板40と同じ構造である。また、一括封止構造体69は、前記実施の形態1で説明した図24に示す一括封止構造体45に電子部品搭載工程を行い、各製品形成領域40aにそれぞれチップ部品4(図31参照)を搭載したものである。

20

**【0132】**

本工程では、ベース基板30の正面3a側、すなわちサブ基板68の正面5aをサブ基板40の裏面5bと対向させた状態で、一括封止構造体69を上型50bと下型66aの間(詳しくは上型50bとサブ基板40の間)に配置する。この時、ベース基板30の正面3aと下型66aの上面を当接させることにより、チップ部品4とサブ基板40を離間して配置する。またこの時、キャビティ67の上面52に形成されたピン55をベース基板30に形成された孔部31に挿入する点については、前記実施の形態1と同様である。孔部31は、前記実施の形態1で説明した第1の封止工程において、キャビティ51よりも外側に位置するように配置されている。このため、孔部31内には封止樹脂16を形成する際の余剰の樹脂が埋め込まれていないので、孔部31はそのまま位置決め用の孔部あるいは配線基板の膨張を制御するための孔部として利用することができる。

30

**【0133】**

次に封止体形成工程として、図32に示すように、ベース基板30とサブ基板40の間に封止用の樹脂を供給して硬化されることにより、第2の封止樹脂となる封止樹脂61を形成する。本工程は、前記実施の形態1で説明した封止工程と同様に、サブ基板68とサブ基板40を電気的接続する電気的接続工程よりも前に行うので、基板間接続電極などの障害物がない状態で行うことができる。したがって、前記実施の形態1で説明した封止体形成工程と同様に封止樹脂61内に空気が残留することを防止することができる。

40

**【0134】**

次に、第2の電気的接続工程として、サブ基板68とサブ基板40を電気的に接続する。詳しくは、サブ基板40の正面5aに形成されたランド22(図29参照)と、サブ基板68の正面5aに形成されたランド64(図29参照)とを、半田材8(図29参照)などの導電性部材を介して電気的に接続する。本工程は、前記実施の形態1で説明した電気的接続工程(第1の電気的接続工程)のランド12をランド64に、ベース基板30をサブ基板68に読み替えて適用することができるので、重複する説明は省略する。

**【0135】**

また、ボールマウント工程、電子部品搭載工程、個片化工程については、前記実施の形態1で説明した各工程を適用することができるので、重複する説明は省略する。なお、本

50

実施の形態 2 では、封止樹脂 6 1 を形成する封止工程（第 2 の封止工程）において、ベース基板 3 0 を成型金型 6 6 でしっかりとクランプする観点から、ボールマウント工程は、封止工程（第 2 の封止工程）の後で行うことが好ましい。

#### 【 0 1 3 6 】

< 第 1 の変形例 >

次に、ベース基板上に複数枚の配線基板を積層する第 1 の変形例について説明する。図 3 3 は第 1 の変形例である半導体装置の全体構造を示す断面図である。図 3 3 に示す P O P 7 0 と図 2 9 に示す P O P 6 0 の相違点は、基板間接続用のランド（端子）の配置である。

#### 【 0 1 3 7 】

P O P 7 0 では、基板間接続端子であるランド 1 2 、 2 2 がそれぞれ厚さ方向に重なる位置に配置され、半田材 8 が、複数のサブ基板 5 および複数の封止樹脂 1 6 、 6 1 を貫通し、ベース基板 3 0 のランド 1 2 と接合している。このように、複数のサブ基板 5 を貫通させて各サブ基板 5 をベース基板 3 と電気的に接続する場合、電気的接続工程を一括して行うことができるので、製造工程を簡略化することができる。

#### 【 0 1 3 8 】

すなわち、前記実施の形態 1 で説明した封止工程（第 1 の封止工程）および図 2 9 ～図 3 2 を用いて説明した第 2 の封止工程を行った後で、前記実施の形態 1 で説明した電気的接続工程を行う。電気的接続工程では、最上段に配置されるサブ基板 4 0 の主面 3 a に配置されたランド 2 2 から最下段に配置されるベース基板 3 0 の主面 3 a に形成されたランド 1 2 に向かって、複数のサブ基板 5 （詳しくはサブ基板 5 に相当する多数個取り基板）および複数の封止樹脂 1 6 、 6 1 を貫通する貫通孔を形成し、ランド 1 2 を露出させる。その後、貫通孔内に各段のランド 1 2 、 2 2 を電気的に接続するための導電性部材（半田材 8 ）を形成することにより、各基板間を電気的に接続することができる。本変形例は、複数枚の同じ配線基板を並列接続で積層する半導体装置に適用して特に有効である。

#### 【 0 1 3 9 】

< 第 2 の変形例 >

次に、ベース基板上に複数枚の配線基板を積層する第 2 の変形例について説明する。図 3 4 は第 2 の変形例である半導体装置の全体構造を示す断面図である。図 3 4 に示す P O P 7 1 と図 2 9 に示す P O P 6 0 の相違点は、中段に配置されるサブ基板 7 2 の主面 5 a 上にチップ部品 4 が搭載されていない点である。また、サブ基板 7 2 の主面 5 a には、上段に配置されるサブ基板 5 と電気的に接続される配線 7 3 が形成されている。

#### 【 0 1 4 0 】

前記実施の形態 1 で説明したように、ベース基板 3 上に積層されるサブ基板 5 は主面 5 a 側にのみ配線が形成される単層の配線基板としている。しかし、サブ基板 5 の配線レイアウトによっては、配線の引き回しスペースを確保する観点から、複数層の配線層を有する配線基板とする方が好ましい場合もある。そこで、本変形例のように、主面 5 a 側に電子部品が搭載されていないサブ基板 7 2 を中段に配置し、これをサブ基板 5 と電気的に接続することにより、配線引き回しのスペースを拡大することができる。

#### 【 0 1 4 1 】

本変形例の P O P 7 1 の製造方法は、図 2 9 ～図 3 2 で説明した P O P 6 0 の製造方法において、第 1 の電子部品搭載工程を省略して適用することができる。したがって、重複する説明は省略する。

#### 【 0 1 4 2 】

< 第 3 の変形例 >

次に、複数枚の配線基板を積層する第 3 の変形例について説明する。図 3 5 は第 3 の変形例である半導体装置の全体構造を示す断面図である。図 3 5 に示す P O P 7 4 と図 3 4 に示す P O P 7 1 との相違点は、基板間の接続構造である。P O P 7 4 の最上段に搭載されるサブパッケージ 7 5 が有するサブ基板 7 6 は主面 5 a に中段に配置されるサブ基板 7 2 と電気的に接続される複数のランド 2 2 に加え、ベース基板 3 と電気的に接続される複

10

20

30

40

50

数のランド 7 7 を有している。詳しくは、ランド 2 2 は半田材 8 を介してサブ基板 7 2 の正面 5 a に形成されたランド 6 4 と電気的に接続されている。また、ランド 7 7 は、複数のサブ基板 5 および複数の封止樹脂 1 6、6 1 を貫通して形成される半田材 8 を介してベース基板 3 0 のランド 1 2 と電気的に接続されている。また、ランド 2 2 およびランド 7 7 は、それぞれ図示しない配線を介してサブ基板 7 6 に搭載されたチップ部品 4 と電気的に接続されている。前記した第 2 の変形例と同様に、図 3 5 に示す第 3 の変形例の場合にも、正面 5 a 側に電子部品が搭載されていないサブ基板 7 2 を中段に配置し、これをサブ基板 5 と電気的に接続することにより、配線引き回しのスペースを拡大することができる。

#### 【 0 1 4 3 】

本変形例の P O P 7 4 は、例えば、前記した第 1 の変形例の製造方法を応用して製造することができる。すなわち、前記実施の形態 1 で説明した封止工程（第 1 の封止工程）および図 2 9 ~ 図 3 2 を用いて説明した第 2 の封止工程を行った後で、前記実施の形態 1 で説明した電気的接続工程を行う。この場合、電気的接続工程では、最上段に配置されるサブ基板 7 6（詳しくはサブ基板 7 6 に相当する多数個取り基板）の正面 3 a に配置されたランド 7 7 から最下段に配置されるベース基板 3 0 の正面 3 a に形成されたランド 1 2 に向かって、複数のサブ基板 7 6、7 2 および複数の封止樹脂 1 6、6 1 を貫通する貫通孔を形成し、ランド 1 2 を露出させる。また、ランド 2 2 からは、その下層に配置されるサブ基板 7 2（詳しくはサブ基板 7 2 に相当する多数個取り基板）の正面 5 a に形成されたランド 6 4 向かって、サブ基板 7 6 および複数の封止樹脂 6 1 を貫通する貫通孔を形成し、ランド 6 4 を露出させる。その後、各貫通孔内にランド 1 2 とランド 7 7、ランド 2 2 とランド 6 4 をそれぞれ電気的に接続するための導電性部材（半田材 8）を形成することにより、各基板間を電気的に接続することができる。本変形例によれば、各段の基板間接続端子をそれぞれ個別に接続することができるので、配線レイアウトの自由度が向上する。なお、本変形例を、前記した第 1 の変形例に適用しても良いことは言うまでもない。

#### 【 0 1 4 4 】

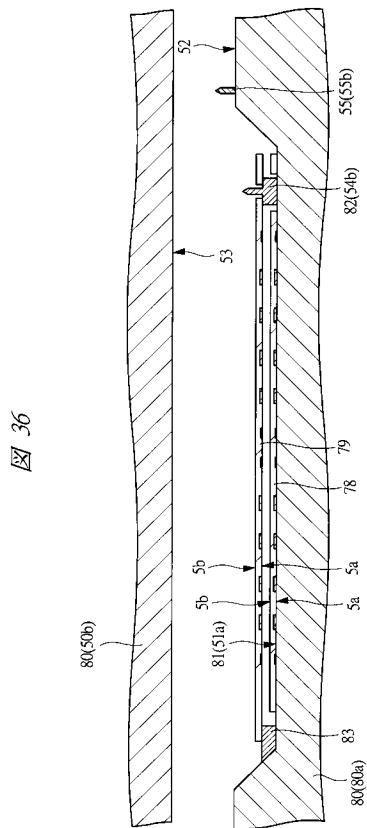

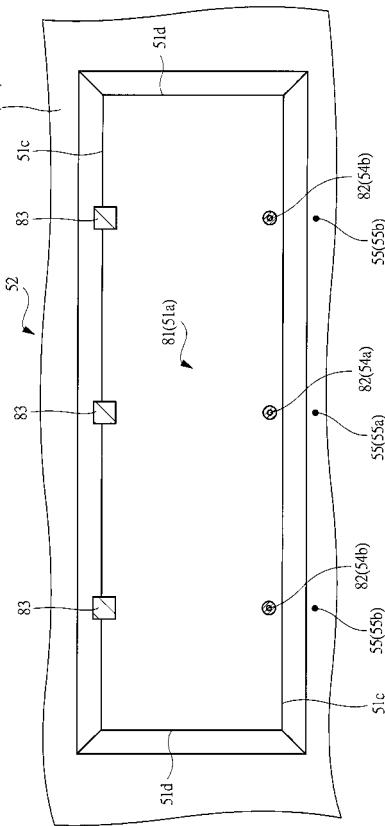

##### < 第 4 の変形例 >

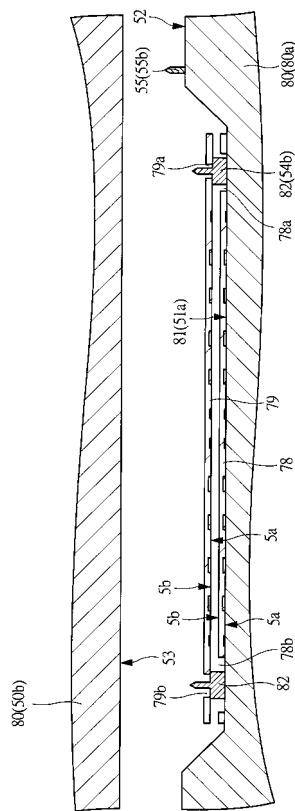

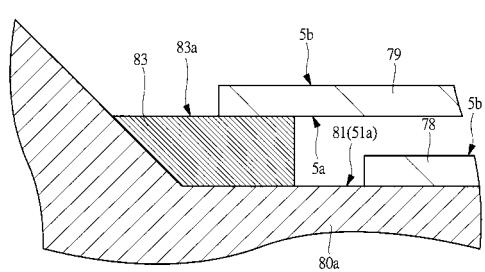

図 3 5 に示す P O P 7 4 は、前記実施の形態 1 で説明した製造方法を応用し、前記第 3 の変形例とは別の製造方法によっても製造することができる。以下別の製造方法について、第 4 の変形例として説明する。図 3 6 は本変形例の第 1 の基材配置工程において、成型金型のキャビティ内に複数枚の配線基板を配置した状態を示す要部拡大断面図、図 3 7 は図 3 6 に示す下型の上面を示す要部拡大平面図、図 3 8 は図 3 6 に示す位置決めピン周辺を拡大して示す要部拡大断面図、図 3 9 は図 3 6 に示す支持台周辺を示す要部拡大断面図である。

#### 【 0 1 4 5 】

以下に説明する本変形例の製造方法と前記実施の形態 1 で説明した製造方法の相違点は、封止工程において、ベース基板を配置する前に複数枚のサブ基板（基材）を配置して、複数枚のサブ基板を一括して封止する点である。つまり、実施の形態 2、あるいは第 1 ~ 第 3 の変形例において説明したように、対向配置される一対の配線基板（基材）の間に順次封止樹脂を形成していく方法ではなく、予め 3 枚以上の配線基板（基材）を積層配置し、各配線基板の間に一括して封止樹脂を形成する。

#### 【 0 1 4 6 】

本変形例では、前記実施の形態 1 で説明した封止工程に含まれる第 1 の基材配置工程において、複数の配線基板、すなわち図 3 6 に示すサブ基板 7 8 およびサブ基板 7 9 を成型金型 8 0 の下型（金型）8 0 a 内に順次配置する。なお、サブ基板 7 8 および 7 9 は、基板間接続端子であるランドの配置、正面 5 a に形成される配線のレイアウト、外形寸法、および孔部の開口径を除き、前記実施の形態 1 で説明したサブ基板 4 0 と同じ構造の多数個取り配線基板である。

#### 【 0 1 4 7 】

本変形例の封止工程で用いる成型金型 8 0 は、前記実施の形態 1 で説明した成型金型 5

10

20

30

40

50

0（図10参照）と、以下の点が相違する。まず、本変形例の成型金型80は、下型80aが有するキャビティ81の深さ、すなわち上面52から底面51aまでの高低差が深くなっている。これは、3枚以上の配線基板（基材）をそれぞれ離間して配置するためである。また、キャビティ81の底面51aに配置されるピン82の形状が前記実施の形態1で説明したピン54とは異なる。また、ピン54が寄せて配置される長辺51cの対向側には、上層に配置されるサブ基板79を支持するための支持台83が配置されている。ピン54とは異なる形状のピン82を設け、支持台83を設けているのは、サブ基板78、79を離間して配置するためである。

#### 【0148】

詳しく説明すると、図38に示すようにピン82は、キャビティ81の底面51aと反対側に位置する受け面82aを有する受け部82bを有している。また、ピン82は、受け面82a上の略中央に配置され、底面51aと反対方向に向かって突出する突出部（突起部）82cを有している。一方、図39に示す支持台83は、キャビティ81の底面51aと反対側に位置する受け面83aを有している。この受け面82aと受け面83aは、キャビティ81の底面51aからの高さが同じとなっており、上段に配置されるサブ基板79は、主面5aがこの受け面82a、83aと当接することにより、サブ基板78と離間した状態で支持される。

#### 【0149】

本変形例の第1の基材配置工程では、まず、図35に示すサブ基板76に相当する多数個取り配線基板であるサブ基板78を、主面5aが底面51aと対向するようにキャビティ81内に配置する。ここで、サブ基板78に形成されている孔部78aは受け面82aの径よりも広い開口径を有しており、サブ基板78を配置する際には受け部82bが孔部78aに挿入される。したがって、サブ基板78の主面5aは、底面51aと当接する。本変形例の封止工程では、サブ基板78に対してはこの受け部82bが前記実施の形態1で説明したピン54の機能を果たすこととなる。なお、孔部78aのその他の特徴は、前記実施の形態1で説明した孔部41と同様であるため、重複する説明は省略する。

#### 【0150】

次に、図35に示すサブ基板72に相当する多数個取り配線基板であるサブ基板79を、主面5aがサブ基板78の裏面5bと対向するようにキャビティ81内に配置する。ここで、サブ基板79に形成されている孔部79aは突出部82cよりも広く、かつ、受け面82aよりも狭い開口径を有している。このため、サブ基板79を配置する際には突出部82cが孔部78aに挿入され、サブ基板79は受け面82a上に配置される。また、サブ基板79はサブ基板78と比較して短辺が長く形成されている。このため、ピン82が配置される長辺51c（図37参照）と対向する長辺51c側では、図39に示すように、サブ基板79の主面5aが支持台83の受け面83aと当接している。このため、サブ基板79はサブ基板78と略平行に離間した状態で配置される。本変形例の封止工程では、サブ基板79に対してはこの突出部82cが前記実施の形態1で説明したピン54の機能を果たすこととなる。なお、孔部79aのその他の特徴は、前記実施の形態1で説明した孔部41と同様であるため、重複する説明は省略する。

#### 【0151】

次に、前記実施の形態1で説明した第2の基材配置工程、クランプ工程、封止体形成工程、取り出し工程を行い、3枚の配線基板が封止樹脂を介して一体に形成された一括封止構造体を得る。なお、本変形例における封止体形成工程では、最下層に配置されるサブ基板78とベース基板30（図14参照）の間にサブ基板79が配置されているため、前記実施の形態1よりも、封止用の樹脂を供給する際の抵抗が大きくなる。しかし、本変形例では、ピン82及び支持台83により略平行となるように離間して配置しているので、サブ基板78とサブ基板79の間にもしっかりと封止用の樹脂を供給することができる。このため、形成された封止樹脂61に空気が残留することを防止することができる。

#### 【0152】

また、サブ基板78およびサブ基板79の孔部78a、79aの開口径を変えることによ

10

20

30

40

50

より、孔部 7 8 a と受け部 8 2 b、孔部 7 9 a と突出部 8 2 c のクリアランスを適正に調整することができる。この結果、サブ基板 7 8 とサブ基板 7 9 、さらにはベース基板 3 0 との平面的位置関係を高精度で合わせるので、電気的接続工程において、図 3 5 に示す基板間接続端子であるランド 2 2 とランド 6 4 、ランド 7 7 とランド 1 2 をそれぞれ確実に接続することができる。

#### 【 0 1 5 3 】

また、本変形例では、電気的接続工程に加えて封止工程も一括して行うことができるの 10

で、前記した 3 の変形例の製造方法と比較して、製造工程をさらに簡略化することができる。

#### 【 0 1 5 4 】

なお、本変形例に対するさらに別の実施態様として、図 3 7 に示す支持台 8 3 を配置する辺にもピン 8 2 を配置し、孔部 7 8 a 、 7 9 a を対向する長辺に沿ってそれぞれ配置することも考えられる。しかし、封止工程における配線基板の熱膨張の方向を制御する観点から 10

は、本変形例のように一方の辺に寄せて配置することが特に好ましい。

#### 【 0 1 5 5 】

以上、本願発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

#### 【 0 1 5 6 】

例えば、前記実施の形態 1 、 2 では、ベース基板に搭載される半導体チップとして、フェイスアップ実装方式で実装し、ワイヤを介してベース基板と電気的に接続する半導体チップを例示して説明した。しかし、半導体チップの実装態様はこれに限定されず、例えば、半導体チップの主面を配線基板の主面と対向させた状態でバンプ電極を介して配線基板上に搭載する、所謂フリップチップ接続により搭載するフェイスダウン実装方式の半導体チップを用いることもできる。一般にフェイスダウン実装方式で半導体チップを搭載する場合には、半導体チップの裏面側は露出させた状態で行うが、本願で説明した技術を適用する場合には、半導体チップの裏面側も封止樹脂で覆うこととなる。半導体チップの裏面側にも封止樹脂を形成することにより、各配線基板の間隔を略一定とすることができる。この結果、各基板の平面的位置関係を高精度で合わせることができる。また、各基板の間を封止樹脂で埋めることにより、完成した半導体装置の強度、耐湿性などを向上させることができるので、信頼性を向上させることができる。 30

#### 【 0 1 5 7 】

また、前記実施の形態 1 、 2 では、半導体チップを有する半導体装置、あるいは半導体チップを内蔵する配線基板について説明した。しかし、半導体チップが搭載されていない電子装置にも適用することができる。例えば、前記実施の形態 1 、 2 で説明した半導体チップ 2 、あるいはチップ部品 4 を、全て半導体チップ以外の電子部品とすることもできる。

#### 【 0 1 5 8 】

また、前記実施の形態 1 、 2 で説明したベース基板やサブ基板についても種々の変形例を適用することができる。例えば、前記実施の形態 1 ではサブ基板 5 、 4 0 として、ガラスエポキシ系の樹脂基板を例示して説明した。しかし、これに代えてセラミック基板とすることもできる。また、例えばポリイミド樹脂などで構成されるテープ基板（フィルム基板）などを用いることもできる。また、前記実施の形態 1 では、ベース基板 3 0 として、プリプレグからなる配線基板を例示して説明した。しかしこれに代えてセラミック基板を用いることもできる。あるいは、ベース基板 3 0 として、チップ搭載部とチップ搭載部の周囲に配置される複数のリードを有するリードフレームを用いることもできる。ただし、前記実施の形態 1 で説明したように封止工程では、下型 5 0 a の上面 5 2 をベース基板 3 0 の枠部 3 0 b に当接させて支持するので、ベース基板 3 0 にはある程度の剛性が要求される。一方、下型にキャビティを形成した成型金型を用いて封止樹脂を形成する場合、最下層に配置する配線基板は、自重あるいは封止用樹脂の供給圧力により底面に押しつけら 40

50

れるので、テープ基板など剛性の低い材料を用いることができる。

#### 【0159】

また、前記第4の変形例では、成形金型50に支持台83を設けておき、サブ基板78、79を離間する方法について説明したが、サブ基板78、79を離間する手段はこれに限定されない。図40は図36で説明した第4の変形例に対する変形例を示す要部拡大断面図である。図40では、図36に示す支持台83に代えて、ピン82を配置している。つまり、サブ基板78、79において、複数の孔部78a、79aが形成された長辺と対向するもう一方の長辺に沿ってピン82を配置している。このように、対向辺に沿ってそれぞれピン82を配置すると、サブ基板78、79が膨張、または収縮した場合にピン82と接触すると、サブ基板78、79の膨張や収縮を妨げる可能性がある。

10

#### 【0160】

そこで、図40に示す変形例では、サブ基板78、79において複数の孔部78a、79aが形成された長辺と対向するもう一方の長辺に沿って、この孔部78a、79aの径よりも大きい径からなる孔部78b、79bをそれぞれ形成している。すなわち、孔部78b、79bとピン82の間の隙間は孔部78a、79aとピン82の間の隙間よりも広い。これにより、小さい径からなる孔部78a、79aを基点に、サブ基板79が膨張、または収縮したとしても、ピン82がサブ基板79の膨張、または収縮を妨げることを防止ないしは抑制することができる。

#### 【産業上の利用可能性】

#### 【0161】

20

本発明は、半導体チップなどの電子部品が搭載された基材の主面上にさらに別の配線基板を積層する電子装置（半導体装置）に利用可能である。

#### 【符号の説明】

#### 【0162】

1、60、70、71、74 P O P

2 半導体チップ

2 a 主面

2 b 裏面

2 c 側面

2 d パッド

30

3 ベース基板

3 a 主面

3 b 裏面

3 c チップ搭載領域

4、4A、4B チップ部品

4 a 上面

4 b 下面

4 c 側面

4 d 端子

5 サブ基板

40

5 a 主面

5 b 裏面

5 c チップ部品搭載領域

6 ベースパッケージ

7 サブパッケージ

8 半田材

1 1 端子

1 2 ランド

1 3 ランド

1 4 配線

50

|                                 |         |    |

|---------------------------------|---------|----|

| 1 5                             | ワイヤ     |    |

| 1 6                             | 封止樹脂    |    |

| 1 7                             | 半田ボール   |    |

| 2 1                             | 端子      |    |

| 2 2                             | ランド     |    |

| 2 3                             | 半田材     |    |

| 2 4                             | 配線      |    |

| 3 0                             | ベース基板   |    |

| 3 0 a                           | 製品形成領域  |    |

| 3 0 b                           | 枠部      | 10 |

| 3 0 c                           | 長辺      |    |

| 3 0 d                           | 短辺      |    |

| 3 1、3 1 a、3 1 b                 | 孔部      |    |

| 4 0                             | サブ基板    |    |

| 4 0 a                           | 製品形成領域  |    |

| 4 0 b                           | 枠部      |    |

| 4 0 c                           | 長辺      |    |

| 4 0 d                           | 短辺      |    |

| 4 1、4 1 a、4 1 b                 | 孔部      |    |

| 4 2                             | 矢印      | 20 |

| 4 3                             | 矢印      |    |

| 4 5                             | 一括封止構造体 |    |

| 4 6                             | 貫通孔     |    |

| 4 7                             | 積層配線基板  |    |

| 5 0                             | 成型金型    |    |

| 5 0 a                           | 下型      |    |

| 5 0 b                           | 上型      |    |

| 5 1                             | キャビティ   |    |

| 5 1 a                           | 底面      |    |

| 5 1 c                           | 長辺      | 30 |

| 5 1 d                           | 短辺      |    |

| 5 2                             | 上面      |    |

| 5 3                             | 下面      |    |

| 5 4、5 4 a、5 4 b、5 5、5 5 a、5 5 b | ピン      |    |

| 6 1                             | 封止樹脂    |    |

| 6 2、6 5、7 5                     | サブパッケージ |    |

| 6 3、6 8、7 2、7 6、7 8、7 9         | サブ基板    |    |

| 6 4、7 7                         | ランド     |    |

| 6 6、8 0                         | 成型金型    |    |

| 6 6 a、8 0 a                     | 下型      | 40 |

| 6 7、8 1                         | キャビティ   |    |

| 6 9                             | 一括封止構造体 |    |

| 7 3                             | 配線      |    |

| 7 8 a                           | 孔部      |    |

| 7 8 b                           | 孔部      |    |

| 7 9 a                           | 孔部      |    |

| 7 9 b                           | 孔部      |    |

| 8 2                             | ピン      |    |

| 8 2 a                           | 受け面     |    |

| 8 2 b                           | 受け部     | 50 |

8 2 c 突出部

8 3 支持台

8 3 a 受け面

W a、W b 開口幅

Wc 開口径

W d 、 W e 帧

【図1】

【 図 2 】

【図3】

【 四 4 】

【図5】

【図6】

【 义 7 】

【 义 8 】

【図 10】

【 义 9 】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

図21

【図22】

【図23】

【図24】

図24

【図26】

【図25】

【図27】

【図28】

【図30】

【図29】

【図31】

31

【図32】

【図34】

四三二

【図33】

33

【図35】

35

【図36】

【図37】

【図38】

【図40】

【図39】

---

フロントページの続き

(72)発明者 安永 雅敏

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72)発明者 杉山 道昭

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

審査官 坂本 薫昭

(56)参考文献 特開昭63-316446(JP,A)

特表2000-505248(JP,A)

特開2001-007130(JP,A)

特開2006-269861(JP,A)

特開2008-288490(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/56

H01L 25/00-18

H05K 3/46