(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년01월07일

(11) 등록번호 10-1219035

(24) 등록일자 2012년12월31일

(51) 국제특허분류(Int. Cl.)

*H05B 33/00* (2006.01) *H05B 33/10* (2006.01)

*H05B 33/22* (2006.01)

(21) 출원번호 10-2005-0037082

(22) 출원일자 2005년05월03일

심사청구일자 2010년05월03일

(65) 공개번호 10-2006-0114889

(43) 공개일자 2006년11월08일

(56) 선행기술조사문현

US06413790 B1\*

US20040119073 A1\*

JP2001244467 A

JP2004260057 A

\*는 심사관에 의하여 인용된 문현

(73) 특허권자

삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성2로 95 (농서동)

(72) 발명자

김보성

서울특별시 서초구 청두곶길 4, 3층 (방배동)

홍문표

경기도 성남시 분당구 내정로 94, 청구아파트 10

7동 1103호 (정자동, 한솔마을)

이우재

경기도 용인시 기흥구 구성로 90, 삼성래미안2차

아파트 205동604호 (언남동)

(74) 대리인

팬코리아특허법인

전체 청구항 수 : 총 23 항

심사관 : 추장희

(54) 발명의 명칭 유기 박막 트랜지스터 표시판 및 그 제조 방법

### (57) 요 약

본 발명은, 기판, 어느 한 방향으로 뻗은 복수의 게이트선, 상기 게이트선과 절연되어 교차하는 복수의 데이터선, 상기 데이터선과 연결되어 있는 소스 전극, 상기 소스 전극과 마주보는 드레인 전극, 상기 드레인 전극과 연결되어 있는 화소 전극, 그리고 상기 소스 전극과 상기 드레인 전극과 연결되어 있으며 감광성을 가지는 유기 물질로부터 형성되는 유기 반도체를 포함하는 유기 박막 트랜지스터 표시판 및 그 제조 방법을 제공한다.

**대 표 도** - 도2

## 특허청구의 범위

### 청구항 1

기판,

어느 한 방향으로 뻗은 복수의 케이트선,

상기 케이트선과 절연되어 교차하는 복수의 데이터선,

상기 데이터선과 연결되어 있는 소스 전극,

상기 소스 전극과 마주보는 드레인 전극,

상기 드레인 전극과 연결되어 있는 화소 전극, 그리고

상기 소스 전극과 상기 드레인 전극과 연결되어 있으며 감광성을 가지는 유기 물질로부터 형성되는 유기 반도체 그리고

상기 유기 반도체 위에 위치하는 절연 패턴을 포함하고,

상기 절연 패턴은 파릴렌(parylene), 불소계 탄화수소 화합물 및 폴리비닐알코올(poly vinyl alcohol) 중 적어도 어느 하나를 포함하는 유기 박막 트랜지스터 표시판.

### 청구항 2

제1항에서,

상기 유기 물질은 가용성(soluble) 유기 물질인 유기 박막 트랜지스터 표시판.

### 청구항 3

제1항 또는 제2항에서,

상기 유기 물질은 공액 구조(conjugated structure)를 가지는 유기 박막 트랜지스터 표시판.

### 청구항 4

제1항에서,

상기 유기 물질은 산 분해기(acid-labile group)를 가지는 유기 박막 트랜지스터 표시판.

### 청구항 5

제1항에서,

상기 유기 물질은 산 분해기를 가지는 가용성 펜타센 유도체(soluble pentacene derivative)인 유기 박막 트랜지스터 표시판.

### 청구항 6

제5항에서,

상기 산분해기는 t-부틸옥소카보닐기(t-butyloxocarbonyl group)인 유기 박막 트랜지스터 표시판.

### 청구항 7

삭제

### 청구항 8

삭제

**청구항 9**

제1항에서,

상기 소스 전극, 상기 드레인 전극 및 상기 화소 전극은 동일한 재료로 이루어지는 유기 박막 트랜지스터 표시판.

**청구항 10**

제9항에서,

상기 소스 전극과 상기 데이터선 사이에 도전성 접촉 패턴을 더 포함하는 유기 박막 트랜지스터 표시판.

**청구항 11**

제1항에서,

상기 유기 반도체 하부에 광자단막을 더 포함하는 유기 박막 트랜지스터 표시판.

**청구항 12**

기판 위에 게이트선을 형성하는 단계,

상기 게이트선 위에 게이트 절연막을 형성하는 단계,

상기 게이트 절연막 위에 소스 전극을 가지는 데이터선 및 드레인 전극을 형성하는 단계,

상기 데이터선 및 상기 드레인 전극 위에 감광성 유기 물질을 형성하는 단계,

상기 감광성 유기 물질을 노광하여 유기 반도체를 형성하는 단계,

상기 유기 반도체를 덮는 절연 패턴을 형성하는 단계,

상기 드레인 전극과 연결되는 화소 전극을 형성하는 단계 그리고

상기 감광성 유기 물질을 노광하는 단계는 수소(H<sup>+</sup>) 촉매의 존재 하에 수행하는 유기 박막 트랜지스터 표시판의 제조 방법.

**청구항 13**

제12항에서,

상기 감광성 유기 물질은 가용성 유기 물질인 유기 박막 트랜지스터 표시판의 제조 방법.

**청구항 14**

제12항에서,

상기 감광성 유기 물질을 형성하는 단계는 인쇄, 스플 코팅 및 잉크젯 방법 중 어느 하나로 수행하는 유기 박막 트랜지스터 표시판의 제조 방법.

**청구항 15**

삭제

**청구항 16**

제12항에서,

상기 감광성 유기 물질은 펜타센과 t-부틸옥소카보닐기를 가지는 화합물을 반응시켜 형성하는 유기 박막 트랜지스터 표시판의 제조 방법.

**청구항 17**

제12항에서,

상기 유기 반도체를 형성하는 단계는 상기 감광성 유기 물질을 노광한 후 열처리하는 단계를 포함하는 유기 박막 트랜지스터 표시판의 제조 방법.

### 청구항 18

제12항에서,

상기 절연 패턴을 형성하는 단계는 건식 저온 공정으로 수행하는 유기 박막 트랜지스터 표시판의 제조 방법.

### 청구항 19

기판 위에 복수의 데이터선을 형성하는 단계,

상기 데이터선 위에 절연막을 형성하는 단계,

상기 절연막 위에 게이트선을 형성하는 단계,

상기 게이트선 위에 상기 데이터선을 노출시키는 접촉구를 포함하는 게이트 절연막을 형성하는 단계,

상기 게이트 절연막 위에 상기 접촉구를 통하여 상기 데이터선과 연결되는 소스 전극 및 상기 소스 전극과 마주하는 드레인 전극을 포함하는 화소 전극을 형성하는 단계,

상기 소스 전극 및 상기 화소 전극 위에 감광성 유기 물질을 형성하는 단계,

상기 감광성 유기 물질을 노광하여 유기 반도체를 형성하는 단계,

상기 유기 반도체를 덮는 절연 패턴을 형성하는 단계 그리고

상기 감광성 유기 물질을 노광하는 단계는 수소(H<sub>2</sub>) 촉매의 존재 하에 수행하는 유기 박막 트랜지스터 표시판의 제조 방법.

### 청구항 20

제19항에서,

상기 감광성 유기 물질은 가용성 유기 물질인 유기 박막 트랜지스터 표시판의 제조 방법.

### 청구항 21

제19항에서,

상기 감광성 유기 물질을 형성하는 단계는 인체, 스픈 코팅 및 잉크젯 방법 중 어느 하나로 수행하는 유기 박막 트랜지스터 표시판의 제조 방법.

### 청구항 22

삭제

### 청구항 23

제19항에서,

상기 감광성 유기 물질은 펜타센과 t-부틸옥소카보닐기를 가지는 화합물을 반응시켜 형성하는 유기 박막 트랜지스터 표시판의 제조 방법.

### 청구항 24

제19항에서,

상기 유기 반도체를 형성하는 단계는 상기 감광성 유기 물질을 노광한 후 열처리하는 단계를 포함하는 유기 박막 트랜지스터 표시판의 제조 방법.

### 청구항 25

제19항에서,

상기 절연 패턴을 형성하는 단계는 건식 저온 공정으로 수행하는 유기 박막 트랜지스터 표시판의 제조 방법.

## 청구항 26

제19항에서,

상기 소스 전극 및 상기 화소 전극을 형성하는 단계는 ITO를 상온에서 형성하는 단계 및 상기 ITO를 사진 식각하는 단계를 포함하는 유기 박막 트랜지스터 표시판의 제조 방법.

## 청구항 27

제26항에서,

상기 ITO를 사진 식각하는 단계는 염기성 성분을 포함하는 식각액으로 식각하는 단계를 포함하는 유기 박막 트랜지스터 표시판의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0018]

본 발명은 유기 박막 트랜지스터 표시판 및 그 제조 방법에 관한 것이다.

[0019]

차세대 표시 장치의 구동 소자로서 유기 박막 트랜지스터(organic thin film transistor, O-TFT)에 대한 연구가 활발히 이루어지고 있다.

[0020]

유기 박막 트랜지스터는 박막 트랜지스터를 이루는 반도체를 기준의 규소(Si)와 같은 무기 물질 대신 유기 물질로 바꾸어 형성한 것으로, 저온에서 단일 공정으로 제작 가능하기 때문에 공정상 이점이 크고, 섬유(fiber) 또는 필름(film)과 같은 형태로 제작 가능하기 때문에 가요성 표시 장치(flexible display)의 핵심 소자로 주목받고 있다.

[0021]

유기 박막 트랜지스터를 이루는 유기 반도체는 증착, 스픈 코팅, 슬릿 코팅 또는 인쇄(printing) 등의 방법으로 형성할 수 있다.

[0022]

그러나, 이 중 어느 방법도 유기 반도체 패턴을 형성하기 위하여 감광성 수지막을 이용한 사진 식각 공정 또는 격벽 형성 공정이 별도로 요구된다.

#### 발명이 이루고자 하는 기술적 과제

[0023]

따라서, 본 발명은, 유기 박막 트랜지스터의 제조 공정을 줄이면서도 고해상도 유기 반도체를 실현할 수 있는 유기 박막 트랜지스터 표시판 및 그 제조 방법을 제공한다.

#### 발명의 구성 및 작용

[0024]

본 발명에 따른 유기 박막 트랜지스터 표시판은, 기판, 어느 한 방향으로 뻗은 복수의 게이트선, 상기 게이트선과 절연되어 교차하는 복수의 데이터선, 상기 데이터선과 연결되어 있는 소스 전극, 상기 소스 전극과 마주보는 드레인 전극, 상기 드레인 전극과 연결되어 있는 화소 전극, 그리고 상기 소스 전극과 상기 드레인 전극과 연결되어 있으며 감광성을 가지는 유기 물질로부터 형성되는 유기 반도체를 포함한다.

[0025]

또한, 본 발명에 따른 유기 박막 트랜지스터 표시판의 제조 방법은, 기판 위에 게이트선을 형성하는 단계, 상기 게이트선 위에 게이트 절연막을 형성하는 단계, 상기 게이트 절연막 위에 소스 전극을 가지는 데이터선 및 드레인 전극을 형성하는 단계, 상기 데이터선 및 상기 드레인 전극 위에 감광성 유기 물질을 형성하는 단계, 상기 감광성 유기 물질을 노광하여 유기 반도체를 형성하는 단계, 상기 유기 반도체를 덮는 절연 패턴을 형성하는 단계, 그리고 상기 드레인 전극과 연결되는 화소 전극을 형성하는 단계를 포함한다.

[0026]

또한, 본 발명에 따른 유기 박막 트랜지스터 표시판의 제조 방법은, 기판 위에 복수의 데이터선을 형성하는 단계, 상기 데이터선 위에 절연막을 형성하는 단계, 상기 절연막 위에 게이트선을 형성하는 단계, 상기 게이트선

위에 상기 데이터선을 노출시키는 접촉구를 포함하는 게이트 절연막을 형성하는 단계, 상기 게이트 절연막 위에 상기 접촉구를 통하여 상기 데이터선과 연결되는 소스 전극 및 상기 소스 전극과 마주하는 드레인 전극을 포함하는 화소 전극을 형성하는 단계, 상기 소스 전극 및 상기 화소 전극 위에 감광성 유기 물질을 형성하는 단계, 상기 감광성 유기 물질을 노광하여 유기 반도체를 형성하는 단계, 그리고 상기 유기 반도체를 덮는 절연 패턴을 형성하는 단계를 포함한다.

[0027] 이하, 첨부한 도면을 참고로 하여 본 발명의 실시예에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다. 그러나 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 여기에서 설명하는 실시예에 한정되지 않는다.

[0028] 도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 명세서 전체를 통하여 유사한 부분에 대해서는 동일한 도면 부호를 붙였다. 층, 막, 영역, 판 등의 부분이 다른 부분 위에 있다고 할 때, 이는 다른 부분 바로 위에 있는 경우뿐 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 바로 위에 있다고 할 때에는 중간에 다른 부분이 없는 것을 뜻한다.

[0029] [실시예 1]

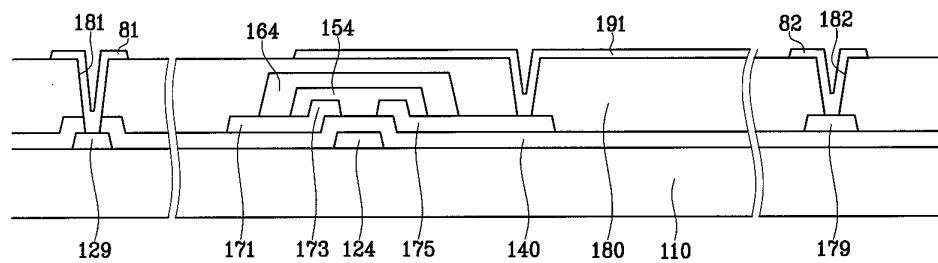

[0030] 먼저, 도 1 및 도 2를 참조하여 본 발명의 한 실시예에 따른 유기 박막 트랜지스터 표시판에 대하여 상세하게 설명한다.

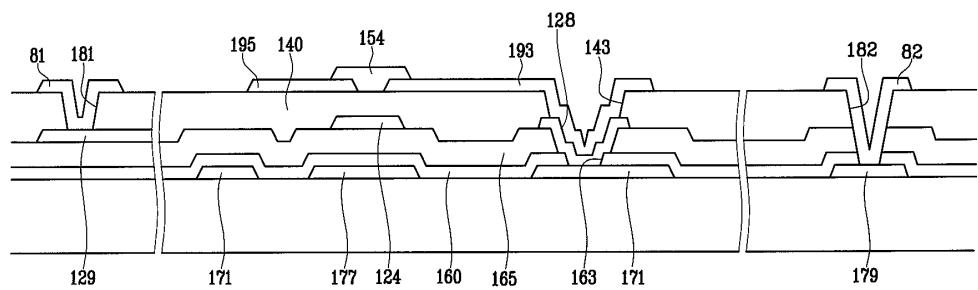

[0031] 도 1은 본 발명의 한 실시예에 따른 유기 박막 트랜지스터 표시판의 배치도이고, 도 2는 도 1의 유기 박막 트랜지스터 표시판을 II-II선을 따라 잘라 도시한 단면도이다.

[0032] 도면에서 보는 바와 같이, 투명한 유리 또는 플라스틱 따위로 만들어진 절연 기판(110) 위에 복수의 게이트선 (gate line)(121)이 형성되어 있다.

[0033] 게이트선(121)은 게이트 신호를 전달하며 주로 가로 방향으로 뻗어 있다. 각 게이트선은 위로 돌출한 복수의 게이트 전극(gate electrode)(124)과 다른 층 또는 외부 구동 회로와의 접속을 위하여 면적이 넓은 끝 부분(129)을 포함한다. 게이트 신호를 생성하는 게이트 구동 회로(도시하지 않음)는 기판(110) 위에 부착되는 가요성 인쇄 회로판(flexible printed circuit)(도시하지 않음) 위에 장착되거나, 기판(110) 위에 직접 장착되거나, 기판(110)에 접적될 수 있다. 게이트 구동 회로가 기판(110) 위에 접적되어 있는 경우 게이트선(121)이 연장되어 이와 직접 연결될 수 있다.

[0034] 게이트선(121)은 알루미늄(Al)과 알루미늄 합금 등의 알루미늄 계열의 금속, 은(Ag)과 은 합금 등의 은 계열의 금속, 금(Au)과 금 합금 등의 금 계열 금속, 구리(Cu)와 구리 합금 등의 구리 계열의 금속, 몰리브덴(Mo)과 몰리브덴 합금 등의 몰리브덴 계열의 금속, 크롬(Cr), 티타늄(Ti), 탄탈륨(Ta) 따위로 이루어지는 것이 바람직하다. 그러나 게이트선(121)은 물리적 성질이 다른 두 개의 도전막(도시하지 않음)을 포함하는 다중막 구조를 가질 수 있다. 이 중 한 도전막은 신호 지연이나 전압 강하를 줄일 수 있도록 낮은 비저항(resistivity)의 금속으로 만들어진다. 이와는 달리, 다른 도전막은 다른 물질, 특히 ITO(indium tin oxide) 및 IZO(indium zinc oxide)와의 물리적, 화학적, 전기적 접촉 특성이 우수한 물질로 만들어진다. 그러나 게이트선(121)은 여러 가지 다양한 금속과 도전체로 만들어질 수 있다.

[0035] 게이트선(121)의 측면은 기판(110) 면에 대하여 경사져 있으며 그 경사각은 약 30° 내지 80° 인 것이 바람직하다.

[0036] 게이트선(121) 위에는 게이트 절연막(gate insulating layer)(140)이 형성되어 있다. 게이트 절연막(140)은 무기 절연물 또는 유기 절연물로 만들어질 수 있다. 무기 절연물의 예로는 질화규소( $\text{SiN}_x$ ) 및 산화규소( $\text{SiO}_2$ )를 들 수 있으며, 산화규소의 경우 OTS(octadecyl-trichlorosilane)로 표면 처리될 수 있다. 유기 절연물의 예로는 말레이미드스티렌(maleimide-styrene), 폴리비닐페놀(Polyvinylalcohol, PVA) 및 모디파이드 시아노에틸풀루란(Modified Cyanoethylpullulan, m-CEP)을 들 수 있다.

[0037] 게이트 절연막(140) 위에는 복수의 데이터선(data line)(171)과 복수의 드레인 전극(drain electrode)(175)이 형성되어 있다.

[0038] 데이터선(171)은 데이터 신호를 전달하며 주로 세로 방향으로 뻗어 게이트선(121)과 교차한다. 각 데이터선(171)은 게이트 전극(124)을 향하여 뻗은 복수의 소스 전극(source electrode)(173)과 다른 층 또는 외부 구동 회로와의 접속을 위하여 면적이 넓은 끝 부분(179)을 포함한다. 데이터 신호를 생성하는 데이터 구동 회로(도시

하지 않음)는 기판(110) 위에 부착되는 가요성 인쇄 회로판(도시하지 않음) 위에 장착되거나, 기판(110) 위에 직접 장착되거나, 기판(110)에 접적될 수 있다. 데이터 구동 회로가 기판(110) 위에 접적되어 있는 경우, 데이터선(171)이 연장되어 이와 직접 연결될 수 있다.

[0039] 드레인 전극(175)은 데이터선(171)과 분리되어 있고 게이트 전극(124)을 중심으로 소스 전극(173)과 마주 본다.

[0040] 데이터선(171) 및 드레인 전극(175)은 알루미늄(Al)이나 알루미늄 합금 등 알루미늄 계열 금속, 은(Ag)이나 은 합금 등 은 계열 금속, 금(Au)이나 금 합금 등 금 계열 금속, 구리(Cu)나 구리 합금 등 구리 계열 금속, 몰리브덴이나 몰리브덴 합금 등 몰리브덴 계열 금속, 니켈(Ni), 크롬, 탄탈륨(Ta), 티타늄(Ti) 및 ITO(indium tin oxide) 따위로 만들어질 수 있다. 그러나 이들은 물리적 성질이 다른 두 개의 도전막(도시하지 않음)을 포함하는 다중막 구조를 가질 수도 있다. 이 중 한 도전막은 신호 지연이나 전압 강하를 줄일 수 있도록 비저항(resistivity)이 낮은 금속으로 만들어진다. 이와는 달리, 다른 도전막은 다른 물질, 특히 유기 반도체, ITO 및 IZO(indium zinc oxide)와의 물리적, 화학적, 전기적 접촉 특성이 우수한 물질로 만들어진다. 그러나 데이터선(171) 및 드레인 전극(175)은 이외에도 여러 가지 다양한 금속 또는 도전체로 만들어질 수 있다.

[0041] 데이터선(171) 및 드레인 전극(175) 또한 그 측면이 기판(110) 면에 대하여  $30^{\circ}$  내지  $80^{\circ}$  정도의 경사각으로 기울어진 것이 바람직하다.

[0042] 소스 전극(173), 드레인 전극(175) 및 게이트 절연막(140) 위에는 복수의 섬형 유기 반도체(154)가 형성되어 있다. 유기 반도체(154)는 게이트 전극(124) 위에 위치하며 소스 전극(173) 및 드레인 전극(175)과 접촉한다.

[0043] 유기 반도체(154)는 공액계(conjugated system)와 같이 전자를 쉽게 이동시킬 수 있는 구조를 가진 올리고머(oligomer) 또는 중합체(polymer)로 이루어질 수 있다. 유기 반도체(154)는 저분자 화합물 또는 수용액이나 유기 용매에 용해되는 고분자 화합물로 이루어질 수 있으며, 용해성이 낮은 저분자 화합물을 용액 공정에 적용하기 위하여 저분자 공액계 화합물에 친수성(hydrophilic) 또는 소수성(hydrophobic) 작용기를 결합시킨 유도체(derivatives)를 이용하여 형성할 수 있다.

[0044] 유기 반도체(154)로는, 예컨대 테트라센(tetracene) 또는 펜타센(pentacene)의 치환기를 포함하는 유도체이거나, 티오펜 링(thiophene ring)의 2, 5 위치를 통하여 4 내지 8개가 연결된 올리고티오펜(oligothiophene), 폴리티닐렌비닐렌(polythienylenevinylene), 폴리-3-헥실티오펜(poly-3-hexylthiophene), 프탈로시아닌(phthalocyanine) 또는 티오펜(thiophene) 등에서 선택될 수 있다.

[0045] 또한, 유기 반도체(154)는 감광성을 가지는 유기 물질로부터 형성된다. 감광성 유기 물질은 노광에 의해 소정의 패턴으로 형성될 수 있으며, 노광 후의 생성물은 반도체 특성을 가져야 한다. 이러한 유기 물질로는, 분자 구조 내에 반도체 특성을 나타낼 수 있는 부분(moiety)과 일정 조건 하에 노광에 의해 분해될 수 있는 산분해기(acid-labile group)를 동시에 가지는 화합물을 들 수 있다. 이러한 유기 물질이 광산발생제(photo-acid generator)의 존재 하에 노광되는 경우, 광산발생제에서 방출한 산 촉매(acid-catalyst)( $H^+$ )에 의해 산분해기가 분해되면서 반도체 특성을 나타내는 유기 물질이 생성될 수 있다.

[0046] 이러한 감광성 유기 물질은 증착(evaporation), 스판 코팅(spin coating), 오프셋 인쇄(off-set printing), 스크린 인쇄(screen printing), 미세접촉 인쇄(micro-contact printing) 또는 잉크젯 인쇄(inkjet printing) 등의 방법으로 전면 또는 부분적으로 형성된 후 노광하여 유기 반도체로 형성될 수 있다. 이 경우, 비교적 낮은 해상도를 나타내는 인쇄 또는 스판 코팅 등의 간편한 방법으로 형성한 유기 반도체를 별도의 추가 공정없이 사전 식각으로 패터닝함으로써 고해상도의 유기 반도체를 실현할 수 있다.

[0047] 하나의 게이트 전극(124), 하나의 소스 전극(173) 및 하나의 드레인 전극(175)은 유기 반도체(154)와 함께 하나의 박막 트랜지스터(thin film transistor, TFT)를 이루며, 박막 트랜지스터의 채널(channel)은 소스 전극(173)과 드레인 전극(175) 사이의 유기 반도체(154)에 형성된다.

[0048] 유기 반도체(154) 위에는 절연 패턴(164)이 형성되어 있다.

[0049] 절연 패턴(164)은 유기 반도체(154)가 외부의 열, 플라스마 또는 화학 물질에 의하여 영향을 받는 것을 방지하기 위한 것으로, 파릴렌(parylene), 불소계 탄화수소 화합물 또는 폴리비닐알코올(poly vinyl alcohol) 등으로 형성될 수 있다.

[0050] 데이터선(171), 드레인 전극(175) 및 절연 패턴(164) 위에는 보호막(passivation layer)(180)이 형성되어 있다. 보호막(180)은 질화규소( $SiN_x$ ) 또는 산화규소( $SiO_2$ ) 따위의 무기 절연물, 폴리이미드(poly imide) 또는

폴리아크릴(poly acryl) 따위의 유기 절연물, 저유전율 절연물 따위로 만들어진다. 저유전율 절연물의 유전 상부는 4.0 이하인 것이 바람직하며, 플라스마 화학 기상 증착(plasma enhanced chemical vapor deposition, PECVD)으로 형성되는 a-Si:C:O, a-Si:O:F 등이 그 예이다. 그러나 보호막(180)은 유기막의 우수한 절연 특성을 살리면서도 노출된 반도체(154) 부분에 해가 가지 않도록 하부 무기막과 상부 유기막의 이중막 구조를 가질 수도 있으며, 경우에 따라 보호막(180)이 생략될 수도 있다.

[0051] 보호막(180)에는 데이터선(171)의 끝 부분(179) 및 드레인 전극(175)을 각각 드러내는 복수의 접촉 구멍(contact hole)(182, 185)이 형성되어 있고, 보호막(180)과 게이트 절연막(140)에는 게이트선(121)의 끝 부분(129)을 드러내는 복수의 접촉 구멍(181)이 형성되어 있다.

[0052] 보호막(180) 위에는 복수의 화소 전극(pixel electrode)(191) 및 복수의 접촉 보조 부재(contact assistant)(81, 82)가 형성되어 있다. 이들은 ITO 또는 IZO 등의 투명한 도전 물질이나 알루미늄, 은 또는 그 합금 등의 반사성 금속으로 만들어질 수 있다.

[0053] 화소 전극(191)은 접촉 구멍(185)을 통하여 드레인 전극(175)과 물리적·전기적으로 연결되어 있으며, 드레인 전극(175)으로부터 데이터 전압을 인가 받는다. 데이터 전압이 인가된 화소 전극(191)은 공통 전압(common voltage)을 인가 받는 다른 표시판(도시하지 않음)의 공통 전극(common electrode)(도시하지 않음)과 함께 전기장을 생성함으로써 두 전극 사이의 액정층(도시하지 않음)의 액정 분자의 방향을 결정한다. 화소 전극(191)과 공통 전극은 축전기[이하 “액정 축전기(liquid crystal capacitor)”라 함]를 이루어 박막 트랜지스터가 된 오프된 후에도 인가된 전압을 유지한다.

[0054] 화소 전극(191)은 게이트선(121) 및 데이터선(171)과 중첩되어 개구율(aperture ratio)을 높인다.

[0055] 접촉 보조 부재(81, 82)는 각각 접촉 구멍(181, 182)을 통하여 게이트선(121)의 끝 부분(129) 및 데이터선(171)의 끝 부분(179)과 연결된다. 접촉 보조 부재(81, 82)는 데이터선(171) 및 게이트선(121)의 끝 부분(179, 129)과 외부 장치와의 접착성을 보완하고 이들을 보호한다.

[0056] 그러면, 도 1 및 도 2에 도시한 유기 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조하는 방법에 대하여 도 3 내지 도 13과 도 1 및 도 2를 참조하여 상세하게 설명한다.

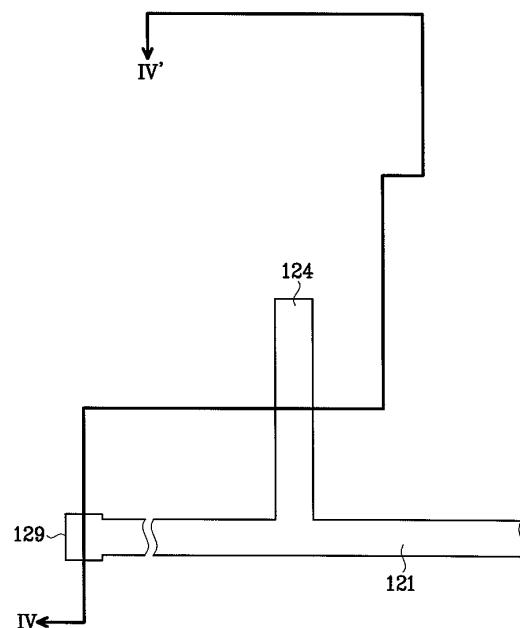

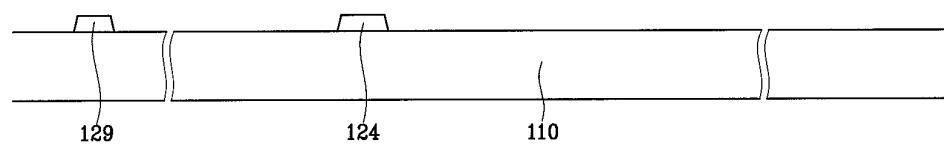

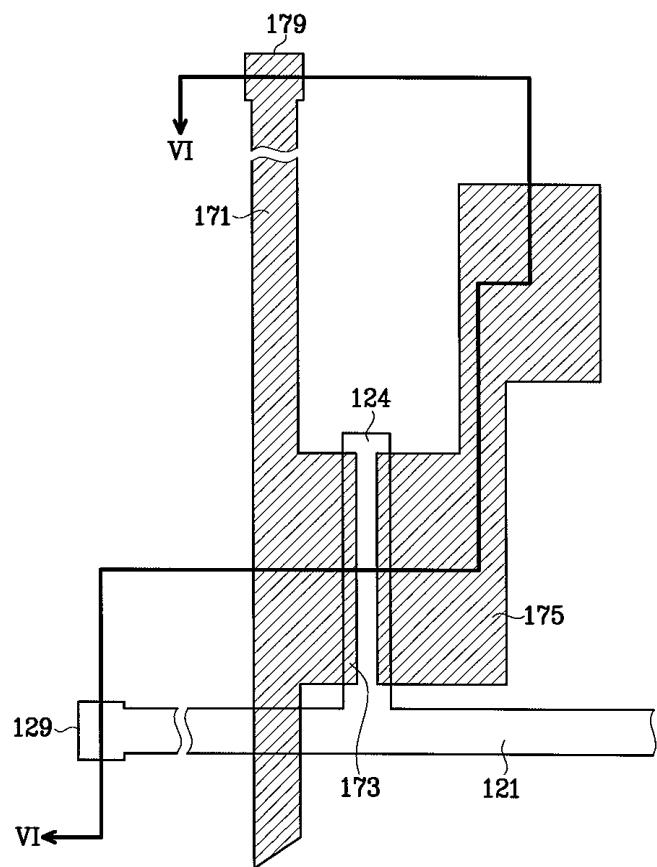

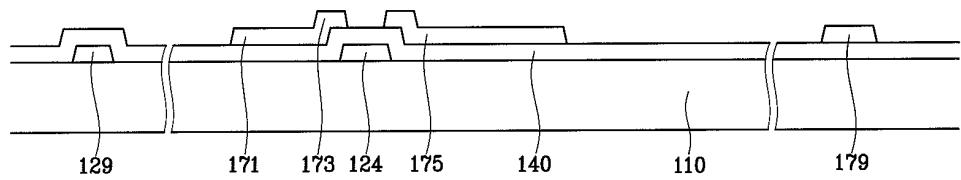

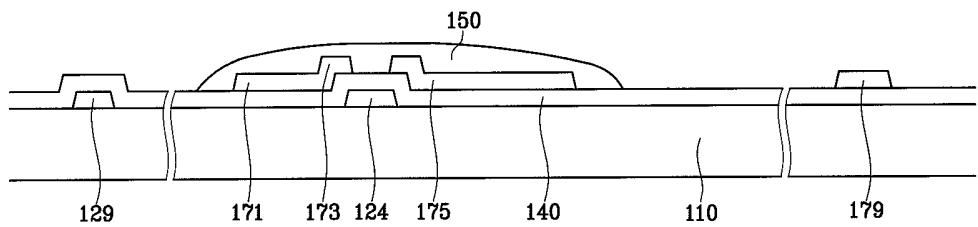

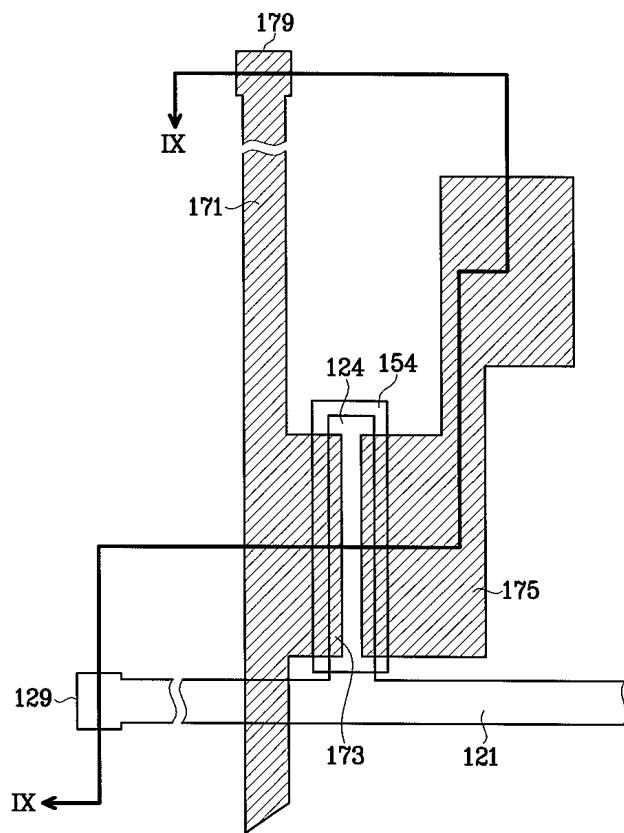

[0057] 도 3, 도 5, 도 8, 도 10 및 도 12는 도 1 및 도 2의 유기 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조하는 방법의 중간 단계에서의 배치도이고, 도 4는 도 3의 유기 박막 트랜지스터 표시판을 IV-IV선을 따라 잘라 도시한 단면도이고, 도 6은 도 5의 유기 박막 트랜지스터 표시판을 VI-VI선을 따라 잘라 도시한 단면도이고, 도 7은 도 5 및 도 6에 연속되는 공정을 나타내는 단면도이고, 도 9는 도 8의 유기 박막 트랜지스터 표시판을 IX-IX선을 따라 잘라 도시한 단면도이고, 도 11은 도 10의 유기 박막 트랜지스터 표시판을 XI-XI선을 따라 잘라 도시한 단면도이고, 도 13은 도 12의 유기 박막 트랜지스터 표시판을 XIII-XIII선을 따라 잘라 도시한 단면도이다.

[0058] 먼저, 도 3 및 도 4에서 보는 바와 같이, 투명 유리 또는 플라스틱 따위의 절연 기판(110) 위에 게이트 전극(124)과 끝 부분(129)을 포함하는 복수의 게이트선(121)을 형성한다.

[0059] 그 다음, 도 5 및 도 6에서 보는 바와 같이, 화학 기상 증착(chemical vapor deposition)으로 게이트 절연막(140)을 형성한다. 게이트 절연막(140)은 약 500 내지 3000Å의 두께를 가질 수 있으며, OTS용액에 담가 표면 처리할 수도 있다.

[0060] 이어서, 게이트 절연막(140) 위에 금(Au) 등의 저저항 도전층을 형성한 후 사진 식각 방법으로 패터닝하여 소스 전극(173) 및 끝 부분(179)을 포함하는 복수의 데이터선(171) 및 복수의 드레인 전극(175)을 형성한다.

[0061] 그 다음, 도 7에서 보는 바와 같이, 데이터선(171) 및 드레인 전극(175) 위의 전면 또는 부분에, 감광성 유기 물질로 이루어진 유기막(150)을 형성한다. 여기서, 감광성 유기 물질은 분자 구조 내에 반도체 특성을 나타내는 부분(moiety)과 노광에 의해 분해될 수 있는 산분해기(acid-labile group)를 동시에 가지는 것으로, 예컨대 분자 구조 내에 t-부틸옥소카르보닐기(t-butyloxocarbonyl group, t-BOC)를 가지는 펜타센 유도체(pentacene derivatives)일 수 있다.

[0062] 상기 펜타센 유도체는 펜타센(pentacene)과 N-설피닐-t-부틸카바메이트(N-sulfinyl-tert-butyloxocarbonyl)를 팔라듐(palladium) 촉매의 존재하에 반응시킬 수 있다. 상기 반응은 딜스-알더 반응(Diels-Alder reaction)을 통해 펜타센 구조 내에 t-부틸옥소카르보닐기(t-BOC)를 결합시킨다.

[0063] 상기 펜타센 유도체를 증착(evaporation), 스판 코팅(spin coating), 오프셋 인쇄법(off-set printing), 스크린 인쇄법(screen printing), 미세접촉 인쇄법(micro-contact printing) 또는 잉크젯 인쇄법(inkjet printing) 등의 방법으로 형성한다.

[0064] 그 다음, 수소(H<sup>+</sup>) 촉매를 공급하기 위한 광발생제로 예컨대 디-터-부틸-페닐아이오도늄 퍼플루오로부탄설포네이트(di-tert-butyl-phenyliodonium perfluorobutanesulfonate)의 존재 하에 상기 펜타센 유도체를 UV로 노광하고 약 110 내지 150°C에서 약 5분간 열처리한다. 이 경우, 광산발생제에서 생성된 수소(H<sup>+</sup>) 촉매에 의하여 펜타센 유도체 내의 터-부틸옥소카르보닐기(t-BOC group)가 분해되면서, 도 8 및 도 9에서 보는 바와 같이, 펜타센(pentacene)으로 이루어진 소정 패턴의 유기 반도체(154)가 형성된다.

[0065] 그 다음, 도 10 및 도 11에서 보는 바와 같이, 상온 또는 저온에서 건식 공정(dry process)으로 파릴렌, 불소계 탄화수소 화합물 또는 폴리비닐알코올 등으로 이루어진 절연층을 형성한다. 이어서, 절연층을 사진 식각 공정으로 패터닝하여 유기 반도체(154)를 충분히 덮는 절연 패턴(164)을 형성한다.

[0066] 이어서, 도 12 및 도 13에서 보는 바와 같이, 데이터선(171), 드레인 전극(175) 및 절연 패턴(164)을 덮는 보호막(180)을 적층하고 패터닝하여 게이트선(121)의 끝 부분(129), 데이터선(171)의 끝 부분(179) 및 드레인 전극(175)을 각각 노출하는 복수의 접촉 구멍(181, 182, 185)을 형성한다.

[0067] 마지막으로, 도 1 및 도 2에서 보는 바와 같이, 보호막(180) 위에 복수의 화소 전극(191)과 복수의 접촉 부재(81, 82)를 형성한다.

[0068] [실시예 2]

[0069] 이하에서는, 본 발명의 다른 한 실시예에 따른 유기 박막 트랜지스터 표시판에 대하여 상세하게 설명한다.

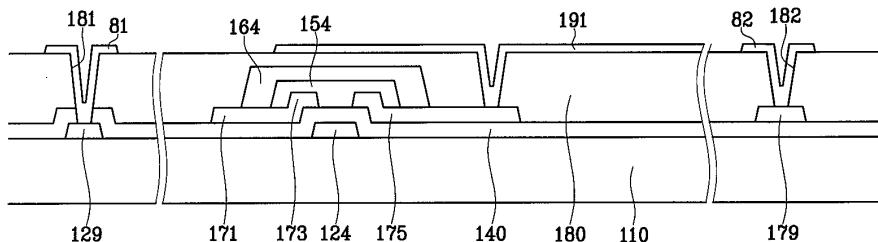

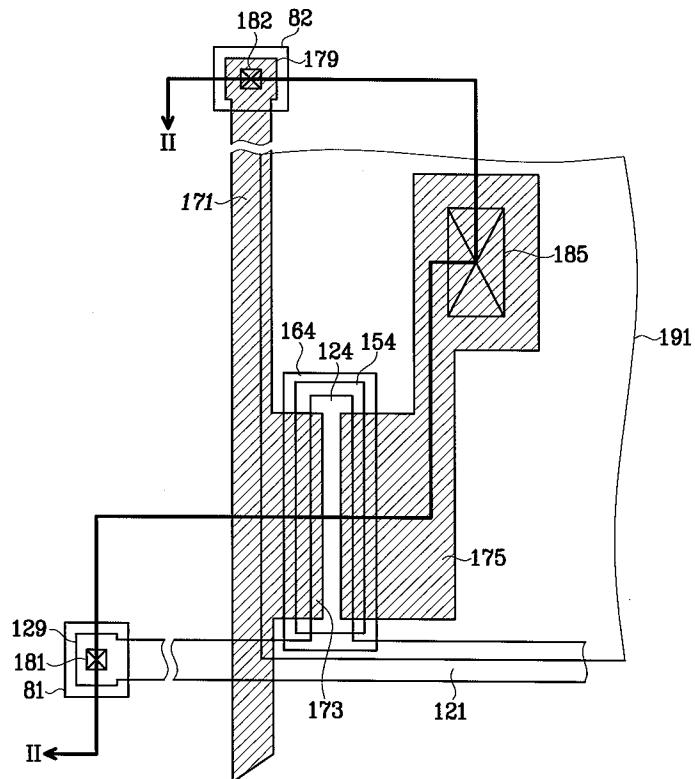

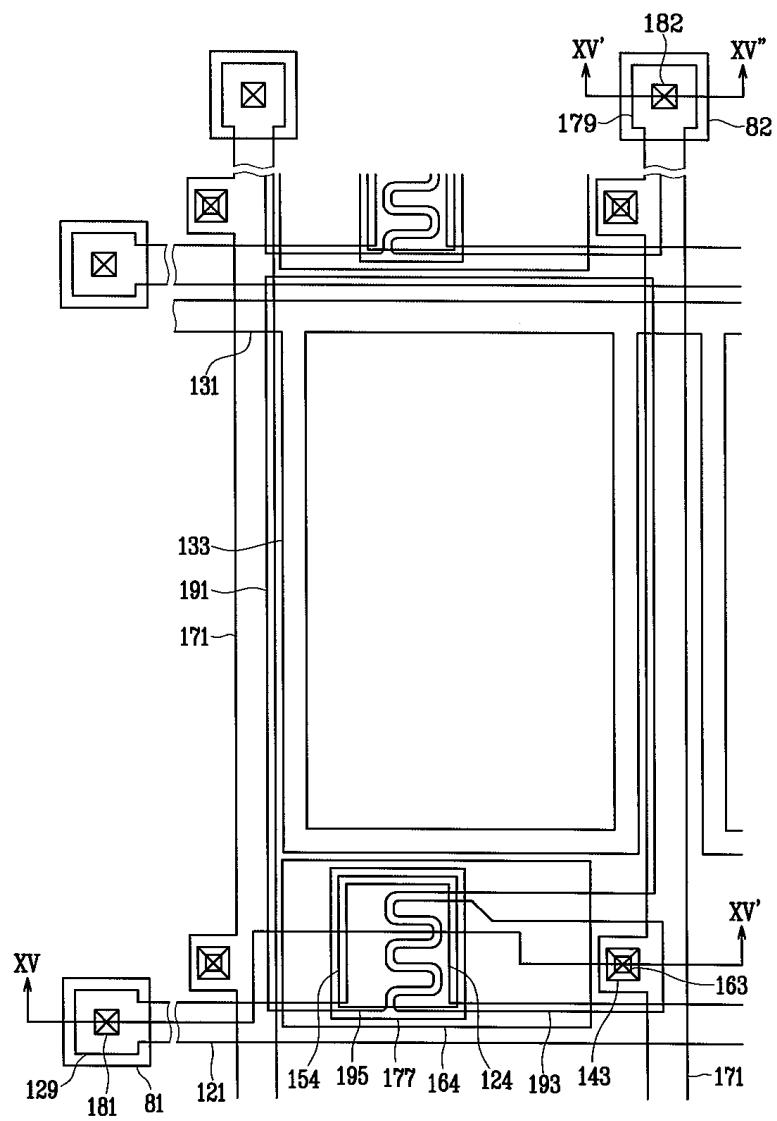

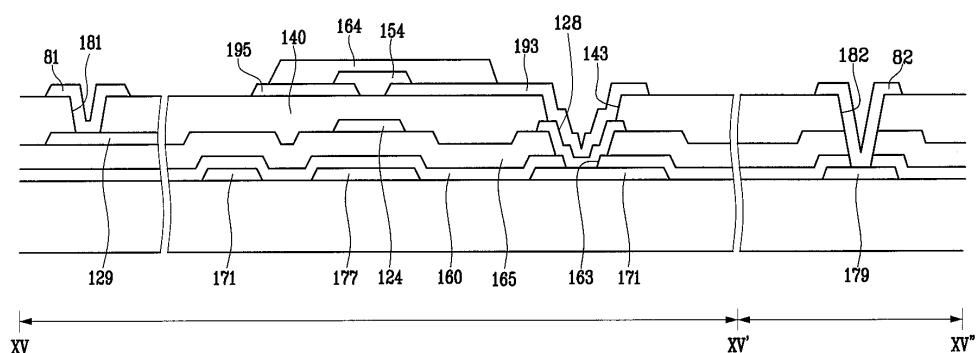

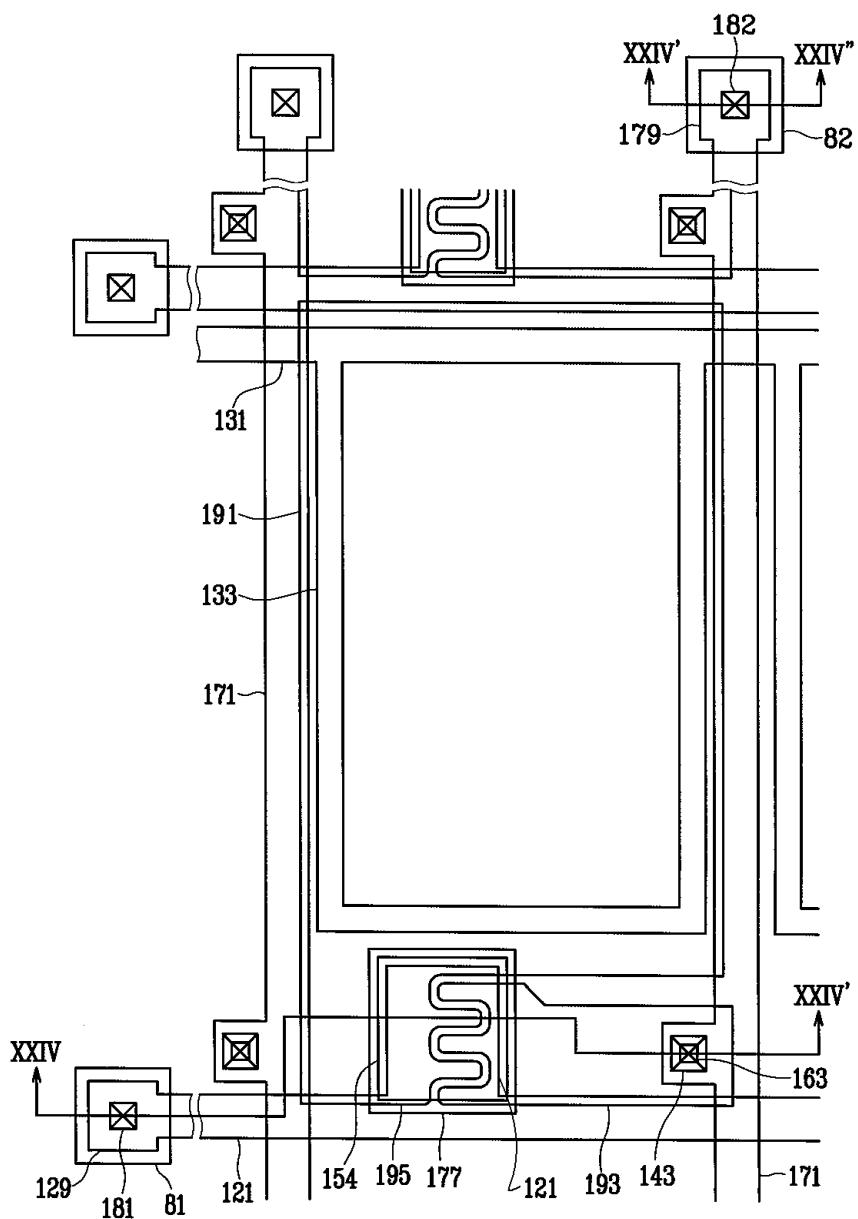

[0070] 도 14는 본 발명의 다른 한 실시예에 따른 유기 박막 트랜지스터 표시판의 배치도이고, 도 15는 도 14의 유기 박막 트랜지스터 표시판을 XV-XV'-XV 선을 따라 잘라 도시한 단면도이다.

[0071] 투명 유리 또는 플라스틱 따위로 만들어진 절연 기판(110) 위에 복수의 데이터선(171) 및 광차단막(177)이 형성되어 있다.

[0072] 데이터선(171)은 데이터 신호를 전달하며 주로 세로 방향으로 뻗어있으며, 각 데이터선(171)의 한쪽 끝 부분(179)은 외부 회로 또는 다른 층과의 연결을 위하여 폭이 확장되어 있다.

[0073] 데이터선(171) 및 광차단막(177)은 신호 지연이나 전압 강하를 줄일 수 있도록 낮은 비저항(resistivity)의 금속, 예컨대 금(Au), 은(Ag), 구리(Cu), 알루미늄(Al) 또는 이들의 합금으로 이루어진 도전막으로 이루어질 수 있다. 또한, 물리적 성질이 다른 둘 이상의 도전막을 포함할 수 있으며, 이 경우 하나의 도전막은 저저항의 도전 물질로 이루어지며, 다른 도전막은 다른 물질, 특히 IZO(indium zinc oxide) 또는 ITO(indium tin oxide)와의 물리적, 화학적 및 전기적 접촉 특성이 우수한 물질, 이를테면 몰리브덴(Mo), 몰리브덴 합금[보기: 몰리브덴-텅스텐(MoW) 합금] 또는 크롬(Cr) 등의 도전 물질로 이루어진 것이 바람직하다.

[0074] 데이터선(171) 및 광차단막(177)은 약 1000 내지 3000Å의 두께로 형성되어 있다.

[0075] 데이터선(171) 및 광차단막(177)의 측면은 각각 경사져 있으며 그 경사각은 기판(110)면에 대하여 약 30 내지 80°인 것이 바람직하다.

[0076] 데이터선(171) 및 광차단막(177) 위에는 질화규소(SiN<sub>x</sub>) 또는 산화규소(SiO<sub>2</sub>) 따위의 무기 절연 물질로 이루어진 하부 층간 절연막(160)과, 내구성이 우수한 폴리아크릴(polyacryl), 폴리이미드(polyimide) 및/또는 벤조사이클로부틴(benzocyclobutene, C<sub>10</sub>H<sub>8</sub>) 등을 포함하는 유기 절연 물질로 이루어진 상부 층간 절연막(165)이 순차적으로 형성되어 있다. 또는, 경우에 따라, 하부 층간 절연막(160) 및 상부 층간 절연막(165) 중 어느 하나를 생략할 수도 있다.

[0077] 하부 층간 절연막(160) 및 상부 층간 절연막(165)에는 데이터선(171)을 노출시키는 접촉 구멍(163) 및 데이터선(171)의 끝부분(179)을 노출시키는 복수의 접촉 구멍이 형성되어 있다.

[0078] 상부 층간 절연막(165) 위에는 게이트 신호를 전달하는 복수의 게이트선(gate line)(121), 데이터선(171) 상부에 형성되어 있는 접촉 패턴(128) 및 복수의 유기 전극선(131)이 형성되어 있다.

[0079] 게이트선(121)은 게이트 신호를 전달하며 주로 세로 방향으로 뻗은 데이터선(171)과 교차한다. 또한, 게이트선

(121)의 일부는 위로 돌출되어 복수의 게이트 전극(gate electrode)(124)을 이루며, 게이트선(121)의 한쪽 끝 부분(129)은 외부 회로 또는 다른 층과의 연결을 위하여 폭이 확장되어 있다.

[0080] 접촉 패턴(128)은 하부에서 상부 층간 절연막(165) 및 하부 층간 절연막(160)에 형성된 접촉구(163)를 통하여 데이터선(171)과 연결되어 있고, 상부에서 게이트 절연막(140)에 형성된 접촉구(143)를 통하여 소스 전극(193)에 연결되어 있다. 데이터선(171)과 소스 전극(193) 사이에는 상부 층간 절연막(165) 및 게이트 절연막(140)을 포함한 복수의 유기막이 포함되어 있기 때문에, 유기막에 의하여 데이터선(171)과 소스 전극(193) 사이에 접촉 불량을 일으킬 수 있다. 따라서, 데이터선(171)과 소스 전극(193) 사이에 접촉 패턴(128)을 개재함으로써 데이터선(171)과 소스 전극(193) 사이의 접촉 불량을 방지할 수 있다.

[0081] 유지 전극선(131) 각각은 주로 가로 방향으로 뻗어 있으며, 게이트선(121)과 데이터선(171)으로 둘러싸인 영역의 가장자리에 배치되어 있는 유지 전극(133)을 포함한다.

[0082] 게이트선(121), 접촉 패턴(128) 및 유지 전극선(131)은 신호의 지연이나 전압 강하를 줄일 수 있도록 낮은 비저항(resistivity)의 금속, 예컨대 금(Au), 은(Ag), 알루미늄(Al) 또는 이들의 합금 등으로 이루어진 도전막을 포함할 수 있다. 또는, 물리적 성질이 다른 둘 이상의 도전막을 포함할 수 있는데, 이 경우 하나의 도전막은 저저항의 도전 물질로 이루어지며, 다른 도전막은 다른 물질, 특히 IZO(indium zinc oxide) 또는 ITO(indium tin oxide)와의 물리적, 화학적 및 전기적 접촉 특성이 우수한 물질, 이를테면 몰리브덴(Mo), 몰리브덴 합금[보기: 몰리브덴-텅스텐(MoW) 합금] 또는 크롬(Cr) 등의 도전 물질로 이루어질 수 있다.

[0083] 게이트선(121), 접촉 패턴(128) 및 유지 전극선(131)의 측면은 각각 경사져 있으며 그 경사각은 기판(110)면에 대하여 약 30 내지 80°인 것이 바람직하다.

[0084] 게이트선(121), 접촉 패턴(128) 및 유지 전극선(131)을 포함한 전면에는 질화규소(SiNx) 따위의 무기 절연 물질 또는 유기 절연 물질로 이루어진 게이트 절연막(gate insulating layer)(140)이 형성되어 있다. 여기서, 게이트 절연막(140)은 유기 물질로 이루어지는 것이 바람직하며, 예컨대 옥타데실 트리클로로 실란(octadecyl trichloro silane, OTS)으로 표면처리된 산화규소(SiO<sub>2</sub>) 또는 진공 중에서 화학 기상 증착(CVD) 공정에 의해 형성되는 파릴렌(parylene) 또는 불소(F) 함유의 탄화수소계열의 고분자 화합물로 이루어질 수 있다.

[0085] 특히, 파릴렌은 코팅 균일도(coating uniformity)가 매우 우수하고, 1000Å 내지 수  $\mu\text{m}$ 까지 코팅 두께(coating thickness)를 조절하는 것이 용이하고, 유전율이 매우 낮아 절연막으로서의 특성이 우수하다. 또한, 파릴렌이 고분자화되는 경우 현준하는 모든 유기 용매에 거의 용해되지 않으며, 상온에서 증착 가능하므로 열 스트레스가 없는 이점이 있다. 또한, 건식 공정으로 형성되어 별도의 용제가 필요하지 않기 때문에 환경친화적이다.

[0086] 게이트 절연막(140)은 약 6000Å 내지 1.2 $\mu\text{m}$ 의 두께로 형성되어 있다.

[0087] 게이트 절연막(140)에는 게이트선(121)의 끝 부분(129)을 노출시키는 접촉 구멍(181)과, 층간 절연막(160, 165)의 접촉 구멍(163)과 함께 게이트 전극(124)에 인접한 데이터선(171) 및 데이터선(171)의 끝 부분(179)을 각각 노출시키는 복수의 접촉 구멍(143, 182)이 형성되어 있다.

[0088] 게이트 절연막(140)에 게이트선(121) 및 데이터선(171)의 끝 부분(129, 179)을 노출하는 접촉구(181, 182)가 형성되어 있는 경우는 외부의 구동 회로를 이방성 도전막을 이용하여 게이트선(121) 및 데이터선(171)에 연결하기 위해 게이트선(121) 및 데이터선(171)이 접촉부를 가지는 구조이다. 또한, 기판(110)의 상부에 직접 게이트 구동 회로가 유기 박막 트랜지스터와 동일한 층으로 형성될 수 있으며, 이 경우 게이트선(121) 및 데이터선(171)의 끝 부분(129, 179)은 구동 회로의 출력단에 전기적으로 연결된다.

[0089] 게이트 절연막(140) 위에는 복수의 소스 전극(source electrode)(193) 및 복수의 화소 전극(pixel electrode)(190)과, 복수의 접촉 보조 부재(contact assistant)(81, 82)가 형성되어 있다.

[0090] 소스 전극(193), 화소 전극(190) 및 접촉 보조 부재(81, 82)는 IZO 또는 ITO 등과 같은 투명한 도전 물질 또는 반사도가 높은 도전 물질로 이루어질 수 있으며, 약 300 내지 800Å의 두께로 형성되어 있다.

[0091] 화소 전극(190) 중 게이트 전극(124)의 상부에 위치하는 일부는 드레인 전극(195)을 이루며, 데이터 신호를 인가 받는다.

[0092] 소스 전극(193)은 게이트 전극(124)을 중심으로 드레인 전극(195)과 마주하며, 접촉구(143, 163)를 통하여 데이터선(171)과 연결되어 있다.

[0093] 소스 전극(193)과 드레인 전극(195)은 서로 평행하게 마주하는 경계선을 가지는데, 단위 면적에서 길이를 극대

화하기 위해 굴곡되어 있다.

[0094] 화소 전극(190)은 또한 이웃하는 게이트선(121) 및 데이터선(171)과 중첩되어 개구율(aperture ratio)을 높이고 있으나, 중첩되지 않을 수도 있다.

[0095] 접촉 보조 부재(81, 82)는 접촉 구멍(181, 182)을 통하여 게이트선(121) 및 데이터선(171)의 끝 부분(129, 179)과 각각 연결된다. 접촉 보조 부재(81, 82)는 게이트선(121) 및 데이터선(171)의 각 끝 부분(129, 179)과 구동 접적 회로와 같은 외부 장치와의 접착성을 보완하고 이들을 보호하는 역할을 하는 것으로 필수적인 것은 아니며, 이들의 적용 여부는 선택적이다.

[0096] 화소 전극(190) 및 소스 전극(193) 위에는 복수의 섬형 유기 반도체(154)가 형성되어 있다. 유기 반도체(154)는 게이트 전극(124) 위에 위치하며 소스 전극(193) 및 드레인 전극(195)과 접촉한다. 유기 반도체(154)의 하부에는 광차단막(177)이 형성되어 있다. 광차단막(177)은 유기 반도체(154)에서 광에 의한 누설 전류(photoleakage current)가 급격히 증가하는 것을 방지하는 역할을 한다.

[0097] 유기 반도체(154)는 공액계(conjugated system)와 같이 전자를 쉽게 이동시킬 수 있는 구조를 가진 올리고머(oligomer) 또는 중합체(polymer)로 이루어질 수 있다. 유기 반도체(154)는 저분자 화합물 또는 수용액이나 유기 용매에 용해되는 고분자 화합물로 이루어질 수 있으며, 용해성이 낮은 저분자 화합물을 용액 공정에 적용하기 위하여 저분자 공액계 화합물에 친수성(hydrophilic) 또는 소수성(hydrophobic) 작용기를 결합시킨 유도체(derivatives)를 이용하여 형성할 수도 있다.

[0098] 유기 반도체(154)로는, 예컨대 테트라센(tetracene) 또는 펜타센(pentacene)의 치환기를 포함하는 유도체이거나, 티오펜 링(thiophene ring)의 2, 5 위치를 통하여 4 내지 8개가 연결된 올리고티오펜(oligothiophene), 폴리티닐렌비닐렌(polythienylenevinylene), 폴리-3-헥실티오펜(poly-3-hexylthiophene), 프탈로시아닌(phthalocyanine) 또는 티오펜(thiophene) 등에서 선택될 수 있다.

[0099] 또한, 유기 반도체(154)는 감광성을 가지는 유기 물질로부터 형성된다. 감광성 유기 물질은 노광에 의해 소정의 패턴으로 형성될 수 있으며, 노광 후의 생성물은 반도체 특성을 가져야 한다. 이러한 유기 물질로는, 분자 구조 내에 반도체 특성을 나타낼 수 있는 부분(moiety)과 일정 조건 하에 노광에 의해 분해될 수 있는 산 분해기(acid-labile group)를 동시에 가지는 화합물을 들 수 있다. 이러한 유기 물질은 광산발생제(photo-acid generator)의 존재 하에 노광되는 경우, 광산발생제에서 방출된 산 촉매(acid-catalyst)(H<sup>+</sup>)에 의해 산 분해기가 분해되면서 반도체 특성을 나타내는 유기 물질이 생성될 수 있다.

[0100] 이러한 감광성 유기 물질은 증착(evaporation), 스픬 코팅(spin coating), 오프셋 인쇄법(off-set printing), 스크린 인쇄법(screen printing), 미세접촉 인쇄법(micro-contact printing) 또는 잉크젯 인쇄법(inkjet printing) 등의 방법으로 전면 또는 부분적으로 형성된 후 노광하여 유기 반도체로 형성될 수 있다. 이 경우, 비교적 낮은 해상도를 나타내는 인쇄 또는 스픬 코팅 등의 간편한 방법으로 형성한 유기 반도체를 별도의 추가 공정없이 사진 식각으로 패터닝함으로써 고해상도의 유기 반도체를 실현할 수 있다.

[0101] 유기 반도체(154)는 약 300 내지 1000Å의 두께로 형성될 수 있다.

[0102] 하나의 게이트 전극(124), 하나의 소스 전극(193) 및 하나의 드레인 전극(195)은 유기 반도체(154)와 함께 하나의 박막 트랜지스터(thin film transistor, TFT)를 이루며, 박막 트랜지스터의 채널(channel)은 소스 전극(193)과 드레인 전극(195) 사이의 유기 반도체(154)에 형성된다.

[0103] 유기 반도체(154) 위에는 절연 패턴(164)이 형성되어 있다.

[0104] 절연 패턴(164)은 유기 반도체(154)가 외부의 열, 플라스마 또는 화학 물질에 의하여 영향을 받는 것을 방지하기 위한 것으로, 파릴렌(parylene), 불소계 탄화수소 화합물 또는 폴리비닐알코올(poly vinyl alcohol) 등으로 형성될 수 있다.

[0105] 그러면, 도 14 및 도 15에 도시한 유기 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조하는 방법에 대하여 도 16 내지 도 24를 참조하여 상세하게 설명한다.

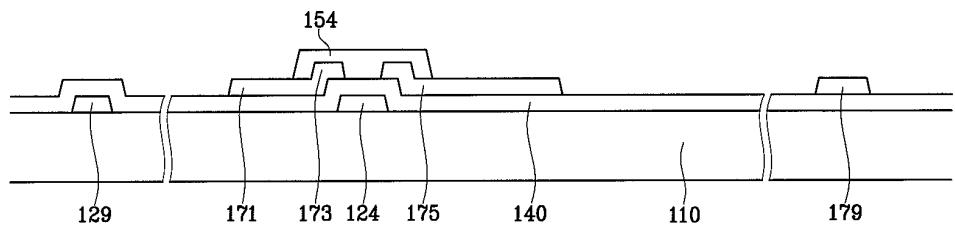

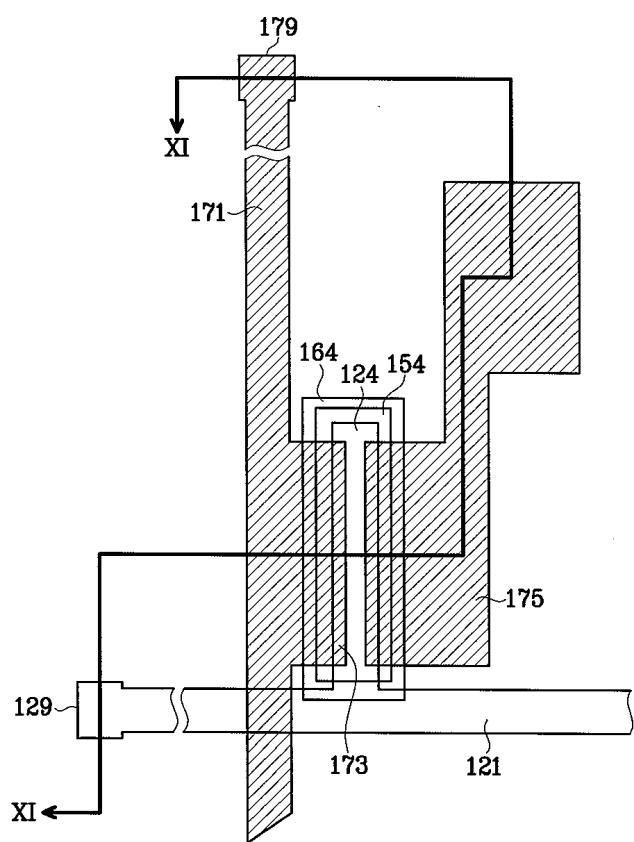

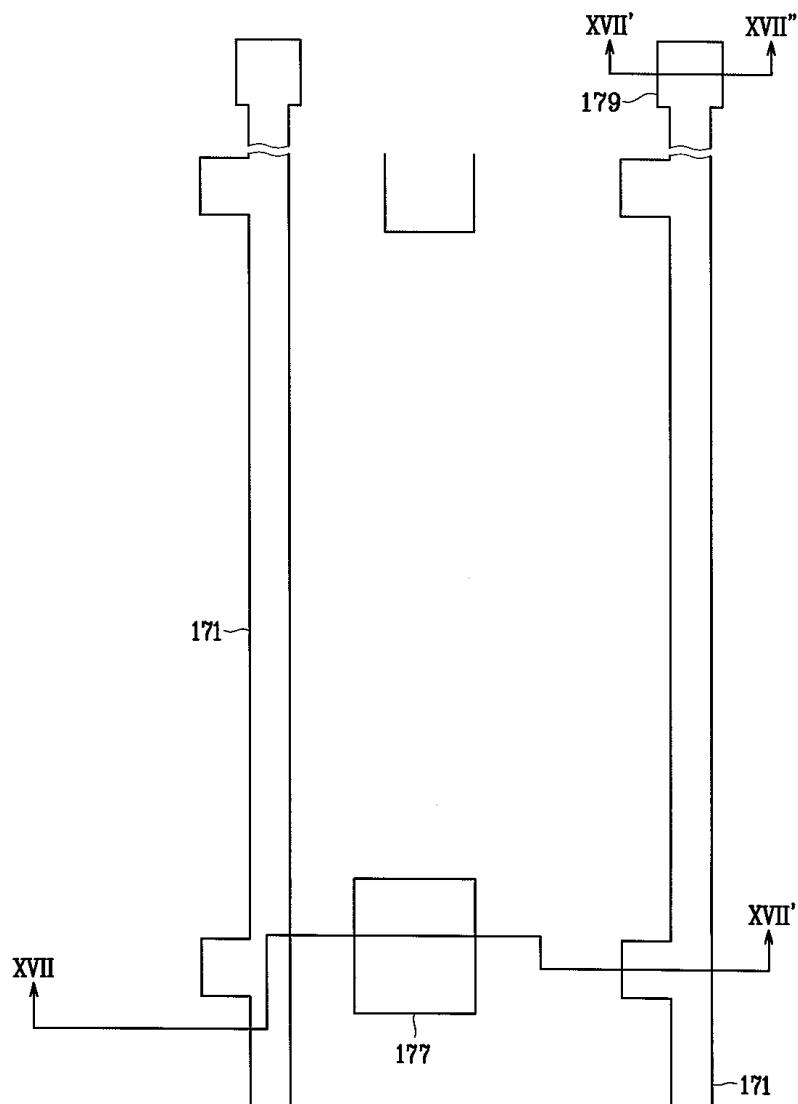

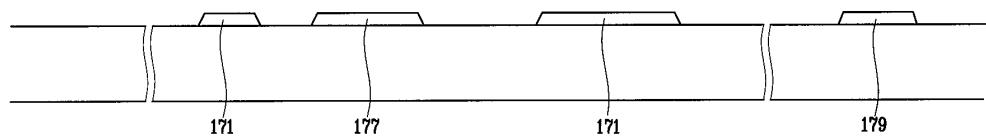

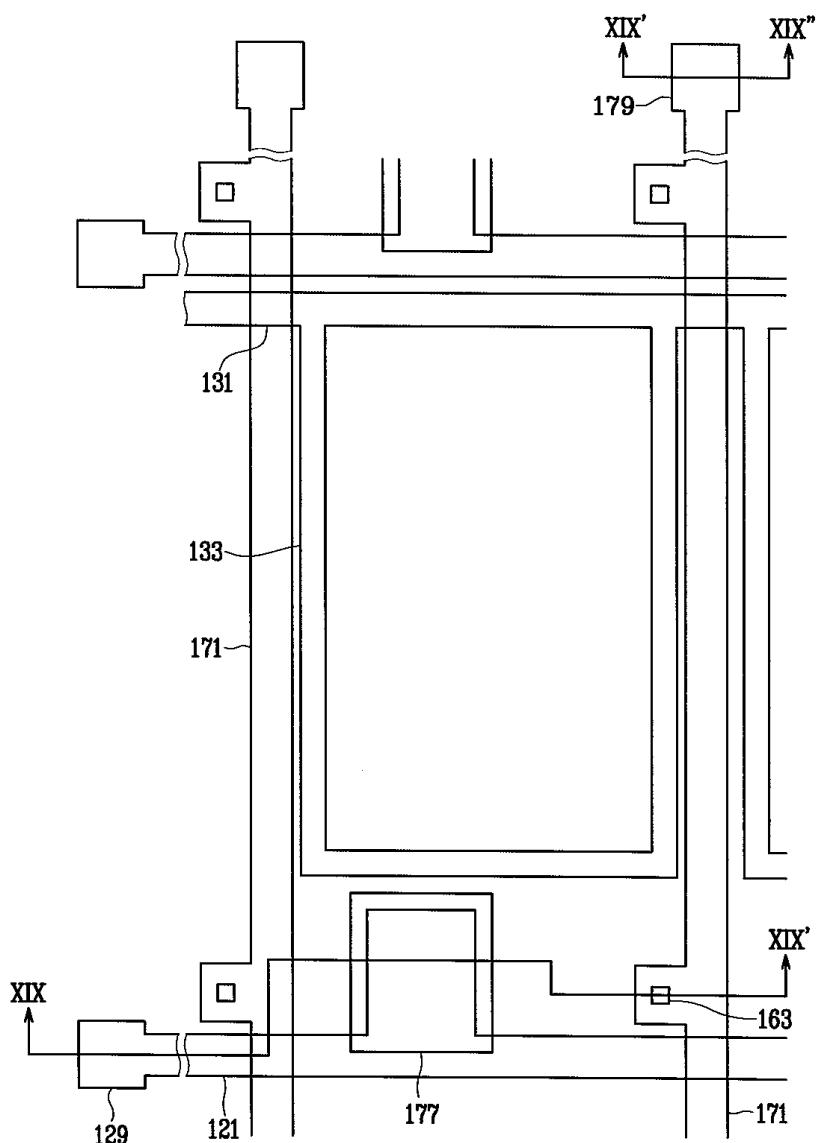

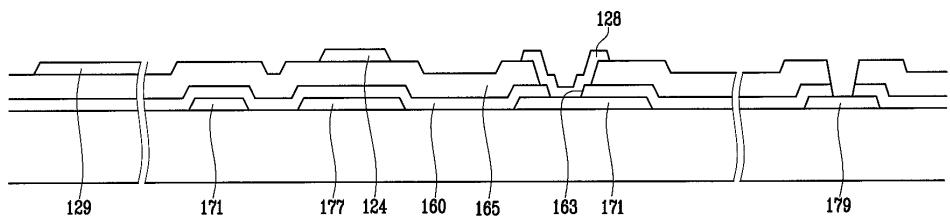

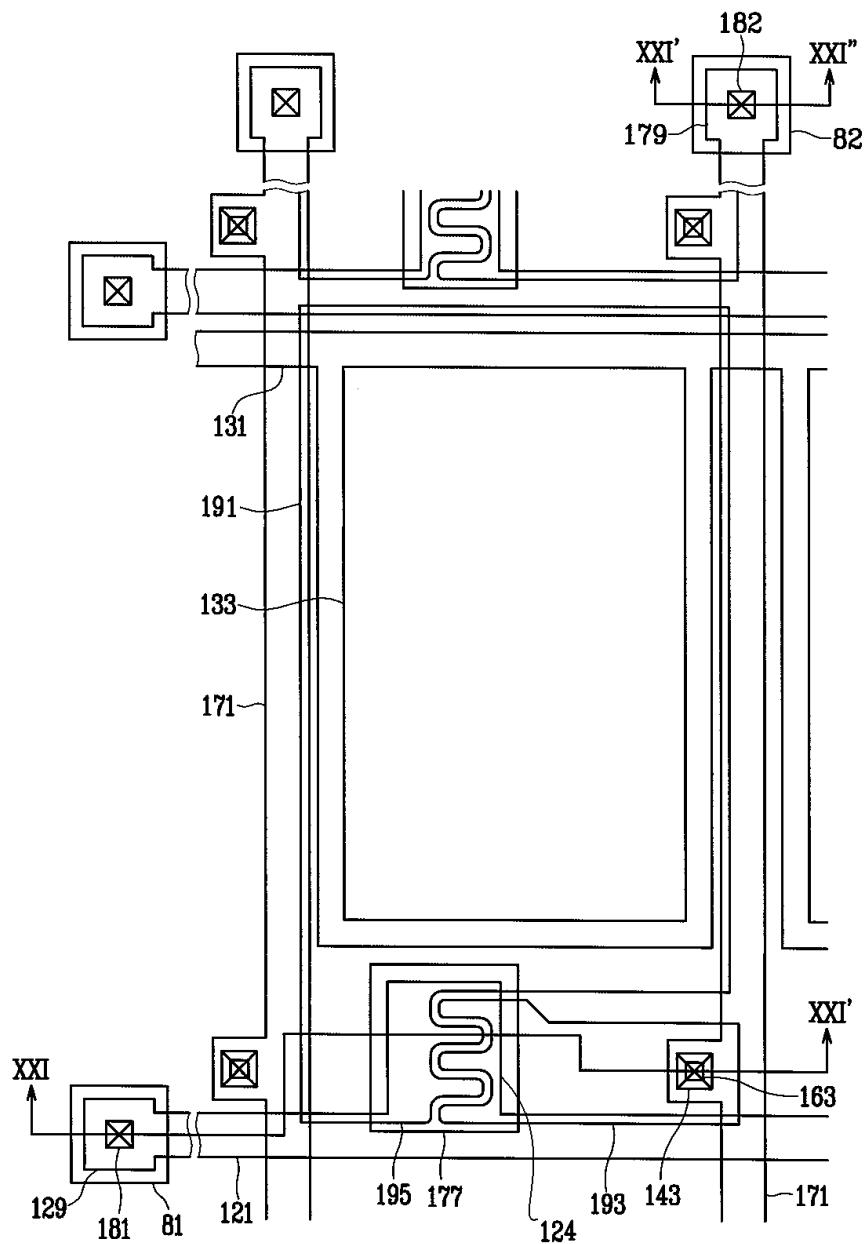

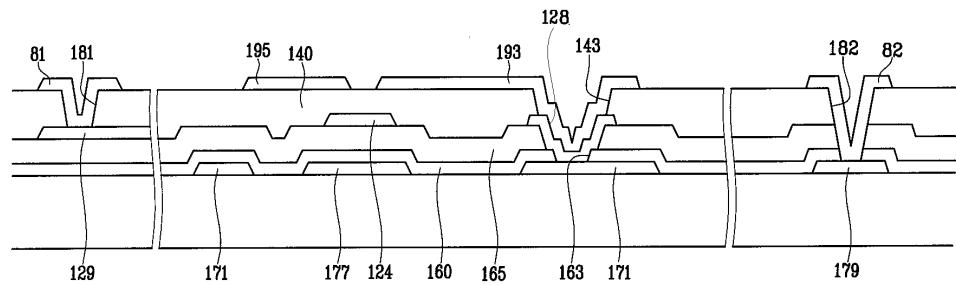

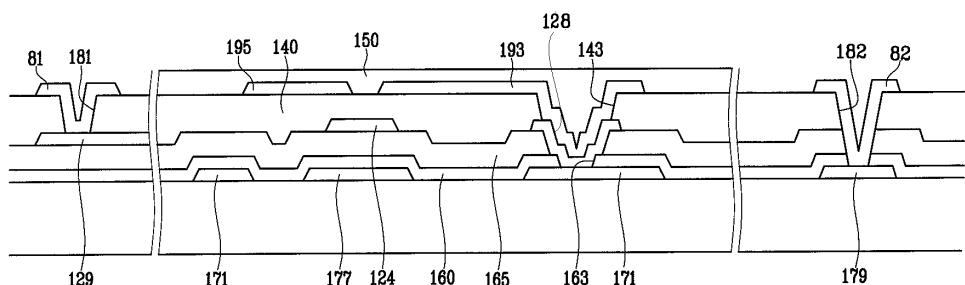

[0106] 도 16, 도 18, 도 20 및 도 23은 도 14 및 도 15의 유기 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조하는 방법의 중간 단계에서의 배치도이고, 도 17은 도 16의 유기 박막 트랜지스터 표시판을 XVII-XVII'-XVII 선을 따라 잘라 도시한 단면도이고, 도 19는 도 18의 XIX-XIX'-XIX 선을 따라 잘라 도시한 단면도이고, 도 21은 도 20의 XXI-XXI'-XXI 선을 따라 잘라 도시한 단면도이고, 도 22는 도 21에 연속되는 공정을 도시한 단면

도이고, 도 24는 도 23의 유기 박막 트랜지스터 표시판을 XXIV-XXIV'-XXIV 선을 따라 잘라 도시한 단면도이다.

[0107] 먼저, 도 16 및 도 17에서 보는 바와 같이, 투명 유리 또는 플라스틱 따위의 절연 기판(110) 위에 스퍼터링(sputtering)으로 금속층을 형성한다.

[0108] 여기서 금속층은 낮은 저저항(resistivity)의 금속, 예컨대 금(Au), 은(Ag), 구리(Cu), 알루미늄(Al) 또는 이들의 합금으로 이루어진 도전체로 이루어질 수 있으며, 저저항 특성 및 접착성(adhesion) 등을 고려하여 다층으로 형성할 수도 있다.

[0109] 그 다음, 금속층을 사진 식각하여, 데이터선(171) 및 광차단막(177)을 형성한다.

[0110] 이어서, 도 18 및 도 19에서 보는 바와 같이, 데이터선(171) 및 광차단막(177)을 포함한 기판 전면에 질화규소(SiNx) 따위의 무기 물질로 이루어진 하부 층간 절연막(160)과 감광성 유기 물질로 이루어진 상부 층간 절연막(165)을 순차적으로 형성한다. 여기서, 하부 층간 절연막(160)은 약 250 내지 400°C의 온도에서 화학 기상 증착(chemical vapor deposition, CVD) 방법으로 형성하고, 상부 층간 절연막(165)은 용액 상태로 스픈 코팅(spin coating)하여 형성할 수 있다. 경우에 따라 하부 층간 절연막(160) 및 상부 층간 절연막(165) 중 어느 하나를 생략할 수도 있다.

[0111] 그 다음, 감광성 유기 물질로 이루어진 상부 층간 절연막(165)을 노광하여 데이터선(171) 및 데이터선의 끝부분(179)을 각각 노출시키는 접촉 구멍을 형성한 후, 상부 층간 절연막(165)을 마스크로 하여 하부 층간 절연막(160)을 건식 식각(dry etching)한다.

[0112] 이어서, 상부 층간 절연막(165) 위에 금속층을 형성한다. 금속층은, 예컨대 금(Au), 은(Ag), 구리(Cu), 알루미늄(Al) 또는 이들의 합금으로 이루어진 도전체로 이루어질 수 있으며, 저저항 특성 및 접착성(adhesion) 등을 고려하여 다층으로 형성할 수도 있다.

[0113] 그 다음, 금속층을 사진 식각하여, 게이트 전극(124)을 포함하는 게이트선(121), 접촉 패턴(128) 및 유지 전극(133)을 포함하는 유지 전극선(131)을 형성한다.

[0114] 이어서, 도 20 및 도 21에서 보는 바와 같이, 게이트선(121), 접촉 패턴(128) 및 유지 전극선(131)을 포함한 전면에 무기 물질 또는 감광성 유기 물질로 이루어진 게이트 절연막(140)을 형성한다.

[0115] 그 다음, 게이트 절연막(140)을 노광하여 접촉 패턴(128) 및 데이터선의 끝부분(179)을 노출시키는 접촉구(143, 181)를 형성한다.

[0116] 이어서, 게이트 절연막(140)의 전면에 ITO를 스퍼터링(sputtering)한다. 이 때, 스퍼터링은 상온(room temperature)에서 수행하여 비정질 ITO막을 형성한다. 그 다음, 상기 비정질 ITO막을 아민(NH<sub>2</sub>)성분이 함유되어 있는 약염기성 식각액을 이용하여 패터닝하여 드레인 전극(195)을 포함하는 화소 전극(191), 소스 전극(193) 및 접촉 보조 부재(81, 82)를 형성한다. 이와 같이 비정질 ITO로 형성하는 경우 약염기성 식각액으로 용이하게 식각할 수 있기 때문에, 다른 도전체 또는 결정질 ITO와 같이 강산 식각액을 필요로 하지 않다. 강산(strong acid) 식각액을 이용하여 패터닝하는 경우, 식각액이 하부의 게이트 절연막(140)과 접촉하여 불량을 유발할 수 있을 뿐만 아니라, 게이트 절연막(140)에 발생한 크랙(crack)으로 침투하여 하부 도전층을 침식시킬 수 있기 때문이다.

[0117] 그 다음, 비정질 ITO를 그대로 이용할 수도 있고, 비정질 ITO를 결정화하여 결정질 ITO를 형성할 수도 있다.

[0118] 또한, 상기에서는 ITO에 대해서만 설명하였지만, IZO와 같은 다른 투명 전극 또는 금(Au), 알루미늄(Al)과 같은 반사성 전극으로 형성할 수도 있다.

[0119] 이어서, 도 22에서 보는 바와 같이, 소스 전극(193) 및 화소 전극(191)을 포함한 전면에, 감광성 유기 물질로 이루어진 유기막(150)을 형성한다. 여기서, 감광성 유기 물질은 분자 구조 내에 반도체 특성을 나타내는 부분(moiety)과 노광에 의해 분해될 수 있는 산분해기(acid-labile group)를 동시에 가지는 것으로, 예컨대 분자 구조 내에 t-부틸옥소카르보닐기(t-butyloxocarbonyl group, t-BOC)을 가지는 펜타센 유도체(pentacene derivatives)일 수 있다.

[0120] 상기 펜타센 유도체는 펜타센(pentacene)과 N-설피닐-t-부틸카바메이트(N-sulfinyl-tert-butyloxocarbonyl carbamate)를 팔라듐(palladium) 촉매 존재하에 반응시킬 수 있다. 상기 반응은 딜스-알더 반응(Diels-Alder reaction)을 통해 펜타센 구조 내에 t-부틸옥소카르보닐기(t-BOC)를 결합시킨다.

[0121] 상기 펜타센 유도체를 증착(evaporation), 스판 코팅(spin coating), 오프셋 인쇄법(off-set printing), 스크린 인쇄법(screen printing), 미세접촉 인쇄법(micro-contact printing) 또는 잉크젯 인쇄법(inkjet printing) 등의 방법으로 형성한다.

[0122] 그 다음, 수소(H<sup>+</sup>) 촉매를 공급하기 위한 광발생제로 예컨대 디-*t*-부틸-페닐아이오도늄 퍼플루오로부탄설포네이트(di-*t*-butyl-phenyliodonium perfluorobutanesulfonate)의 존재 하에 상기 펜타센 유도체를 UV로 노광하고 약 110 내지 150°C에서 약 5분간 열처리한다. 이 경우, 광산발생제에서 생성된 수소(H<sup>+</sup>) 촉매에 의하여 펜타센 유도체 내의 *t*-부틸옥소카르보닐기(*t*-BOC group)가 분해되면서, 도 23 및 도 24에서 보는 바와 같이, 펜타센(pentacene)으로 이루어진 소정 패턴의 유기 반도체(154)가 형성된다.

[0123] 마지막으로, 도 14 및 도 15에서 보는 바와 같이, 상온 또는 저온에서 건식 공정(dry process)으로 파릴렌, 불소계 탄화수소 화합물 또는 폴리비닐알코올 등의 절연층을 형성한다. 이어서, 절연층을 사진 식각 공정으로 패터닝하여 유기 반도체(154)를 충분히 덮는 절연 패턴(164)을 형성한다.

[0124] 상기 실시예에서는 액정 표시 장치용 박막 트랜지스터 표시판의 경우만 설명하였지만, 예컨대 유기 발광 표시 장치(organic light emitting device, OLED) 및 전자 종이(e-paper)와 같이 박막 트랜지스터에 의해 구동될 수 있는 다른 표시 장치에도 동일하게 적용할 수 있음을 당연하다.

[0125] 이상에서 본 발명의 바람직한 실시예들에 대하여 상세하게 설명하였지만 본 발명의 권리범위는 이에 한정되는 것은 아니고 다음의 청구 범위에서 정의하고 있는 본 발명의 기본 개념을 이용한 당업자의 여러 변형 및 개량 형태 또한 본 발명의 권리범위에 속하는 것이다.

### 발명의 효과

[0126] 상기와 같이, 감광성을 가지는 유기 물질을 이용하여 반도체를 형성함으로써 반도체 패턴을 형성하기 위한 감광막 또는 격벽을 별도로 형성할 필요가 없어서 제조 공정을 줄일 수 있을 뿐만 아니라 비교적 해상도가 낮은 용액 공정 후에 사진 공정을 이용하여 반도체 패터닝을 수행함으로써 고해상도를 실현할 수 있다.

### 도면의 간단한 설명

[0001] 도 1은 본 발명의 한 실시예에 따른 유기 박막 트랜지스터 표시판의 배치도이고,

[0002] 도 2는 도 1의 유기 박막 트랜지스터 표시판을 II-II선을 따라 잘라 도시한 단면도이고,

[0003] 도 3, 도 5, 도 8, 도 10 및 도 12는 도 1 및 도 2의 유기 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조하는 방법의 중간 단계에서의 배치도이고,

[0004] 도 4는 도 3의 유기 박막 트랜지스터 표시판을 IV-IV선을 따라 잘라 도시한 단면도이고,

[0005] 도 6은 도 5의 유기 박막 트랜지스터 표시판을 VI-VI선을 따라 잘라 도시한 단면도이고,

[0006] 도 7은 도 5 및 도 6에 연속되는 공정을 나타내는 단면도이고,

[0007] 도 9는 도 8의 유기 박막 트랜지스터 표시판을 IX-IX선을 따라 잘라 도시한 단면도이고,

[0008] 도 11은 도 10의 유기 박막 트랜지스터 표시판을 XI-XI선을 따라 잘라 도시한 단면도이고,

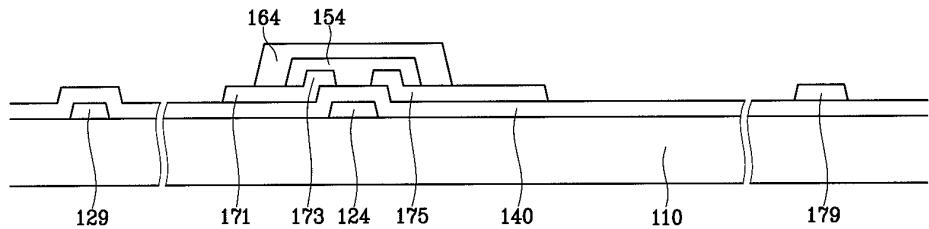

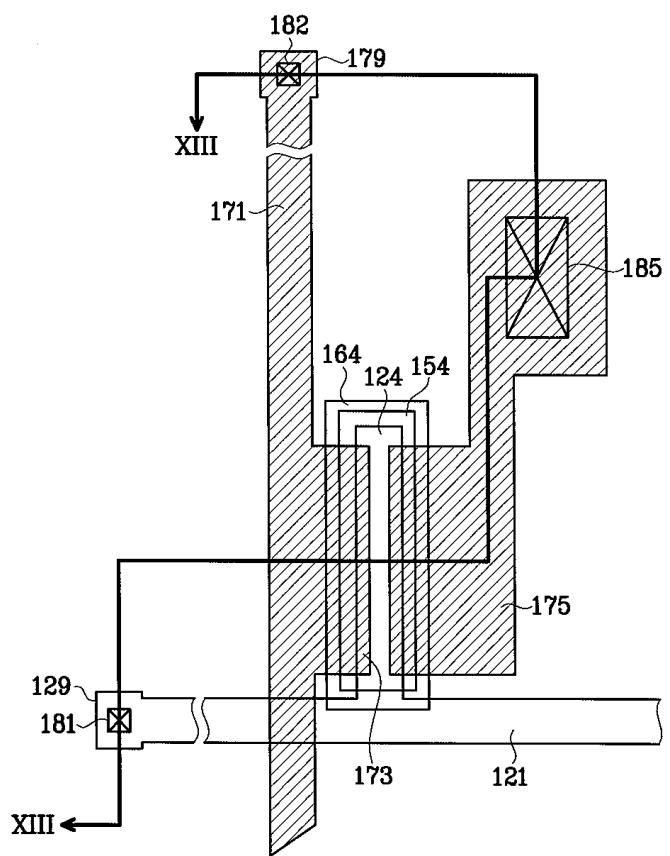

[0009] 도 13은 도 12의 유기 박막 트랜지스터 표시판을 XIII-XIII선을 따라 잘라 도시한 단면도이고,

[0010] 도 14는 본 발명의 다른 한 실시예에 따른 유기 박막 트랜지스터 표시판의 배치도이고,

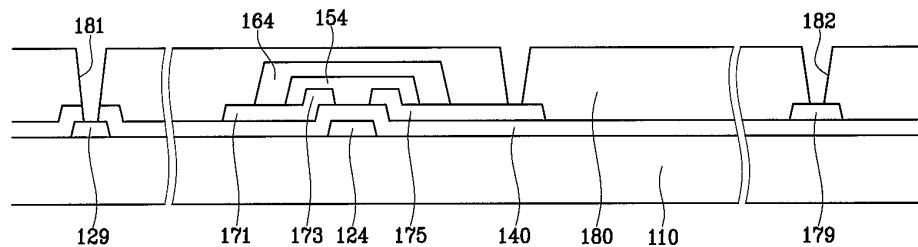

[0011] 도 15는 도 14의 유기 박막 트랜지스터 표시판을 XV-XV 선을 따라 잘라 도시한 단면도이고,

[0012] 도 16, 도 18, 도 20 및 도 23은 도 14 및 도 15의 유기 박막 트랜지스터 표시판을 본 발명의 한 실시예에 따라 제조하는 방법의 중간 단계에서의 배치도이고,

[0013] 도 17은 도 16의 유기 박막 트랜지스터 표시판을 XVII-XVII 선을 따라 잘라 도시한 단면도이고,

[0014] 도 19는 도 18의 XIX-XIX 선을 따라 잘라 도시한 단면도이고,

[0015] 도 21은 도 20의 XXI-XXI 선을 따라 잘라 도시한 단면도이고,

[0016]

도 22는 도 21에 연속되는 공정을 도시한 단면도이고,

[0017]

도 24는 도 23의 유기 박막 트랜지스터 표시판을 XXIV-XXIV 선을 따라 잘라 도시한 단면도이다.

## 도면

## 도면1

## 도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19

도면20

도면21

도면22

도면23

도면24