(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7465200号

(P7465200)

(45)発行日 令和6年4月10日(2024.4.10)

(24)登録日 令和6年4月2日(2024.4.2)

(51)国際特許分類

H 0 3 K 5/13 (2014.01)F I

H 0 3 K 5/13

請求項の数 6 (全14頁)

(21)出願番号 特願2020-190639(P2020-190639)

(22)出願日 令和2年11月17日(2020.11.17)

(65)公開番号 特開2022-79823(P2022-79823A)

(43)公開日 令和4年5月27日(2022.5.27)

審査請求日 令和5年4月18日(2023.4.18)

(73)特許権者 715010864

エイブリック株式会社

長野県北佐久郡御代田町大字御代田 4 1

0 6 番地 7 3

(72)発明者 岡部 茂行

東京都港区三田三丁目 9 番 6 号 エイブ

リック株式会社内

審査官 工藤 一光

最終頁に続く

(54)【発明の名称】 遅延回路

## (57)【特許請求の範囲】

## 【請求項 1】

入力端子に接続されるゲートと、第1の電源電圧を供給する電源端子に接続されるソースと、ドレインとを有する第1のトランジスタと、

前記第1の電源電圧を供給する電源端子に接続される第1端と、前記第1のトランジスタのドレインに接続される第2端とを有する容量と、

前記第1のトランジスタのゲート及び前記入力端子に接続されるゲートと、前記第1のトランジスタのドレイン及び前記容量の第2端に接続されるドレインと、ソースとを有する第2のトランジスタと、

前記第2のトランジスタのソースと、前記第1の電源電圧とは異なる第2の電源電圧を供給する電源端子との間に接続され、前記第2のトランジスタを介して接続される前記容量を充電する定電流を供給する第1の定電流源と、

前記第1のトランジスタのドレインと、前記第2のトランジスタのドレインと、前記容量の第2端との節点に接続されるゲートと、前記第2の電源電圧を供給する電源端子に接続されるソースと、ドレインとを有する第3のトランジスタと、

前記節点及び前記第3のトランジスタのゲートに接続されるゲートと、前記第3のトランジスタのドレイン及び出力端子に接続されるドレインと、ソースとを有する第4のトランジスタと、

前記第1の電源電圧を供給する電源端子と前記第4のトランジスタのソースとを通電可能に接続し、前記容量の充電が開始された後に電圧降下を生じる抵抗体と、を備え、

10

20

前記第1のトランジスタと前記第4のトランジスタとは、p型及びn型の一方である第1の導電型のMOSトランジスタであり、

前記第2のトランジスタ及び前記第3のトランジスタは、p型及びn型の他方である第2の導電型のMOSトランジスタであることを特徴とする遅延回路。

【請求項2】

前記第4のトランジスタのドレインと前記出力端子との間にさらに接続される第5のトランジスタ及び第6のトランジスタと、

第1端及び第2端を有する抵抗と、を備え、

前記第5のトランジスタは、前記第4のトランジスタのドレインと接続されるゲートと、前記第1の電源電圧を供給する電源端子に接続されるソースと、前記抵抗の第1端と接続されるドレインと、を有する前記第1の導電型のMOSトランジスタであり、

前記第6のトランジスタは、前記第5のトランジスタのゲート及び前記第4のトランジスタのドレインと接続されるゲートと、前記第2の電源電圧を供給する電源端子に接続されるソースと、前記抵抗の第2端及び前記出力端子と接続されるドレインと、を有する前記第2の導電型のMOSトランジスタである請求項1に記載の遅延回路。

【請求項3】

前記抵抗体は、前記第4のトランジスタのソースと接続される第1端と、前記第1の電源電圧を供給する電源端子と接続される第2端とを有するダイオードであって、

前記第6のトランジスタのドレインと前記抵抗の第2端と前記出力端子とに接続されるゲートと、前記第1の電源電圧を供給する電源端子に接続されるソースと、前記第4のトランジスタのソース及び前記ダイオードの第1端に接続されるドレインとを有する第7のトランジスタを備える請求項2に記載の遅延回路。

【請求項4】

前記抵抗体は、前記第4のトランジスタのソースと接続される第1端と、前記第1の電源電圧を供給する電源端子と接続される第2端とを有するダイオードであって、

ゲートと、前記第1の電源電圧を供給する電源端子に接続されるソースと、前記第4のトランジスタのソース及び前記ダイオードの第1端に接続されるドレインとを有する第7のトランジスタと、

前記第4のトランジスタのドレインと接続される入力端と、前記第7のトランジスタのゲートと接続される出力端とを有するインバータと、

を備える請求項1に記載の遅延回路。

【請求項5】

前記抵抗体は、前記第4のトランジスタのソースと接続される第1端と、前記第1の電源電圧を供給する電源端子と接続される第2端とを有するダイオードであって、

ゲートと、前記第1の電源電圧を供給する電源端子に接続されるソースと、前記第4のトランジスタのソース及び前記ダイオードの第1端に接続されるドレインとを有する第7のトランジスタを備え、

前記第7のトランジスタのゲートには、前記第4のトランジスタのドレインから出力される電圧に基づく電圧が供給される請求項1又は2に記載の遅延回路。

【請求項6】

前記第4のトランジスタのドレインと前記第3のトランジスタのドレインとの間に接続される第2の定電流源を備える請求項1から5の何れか一項に記載の遅延回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、遅延回路に関する。

【背景技術】

【0002】

容量を備え、この容量の容量値に応じた遅延時間を発生させる遅延回路が知られている（例えば、特許文献1参照）。

10

20

30

40

50

【先行技術文献】

【特許文献】

【0003】

【文献】特開2010-219661号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上述した遅延回路では、発生させたい遅延時間が大きくなるほど、容量値が大きくなってしまう。容量値の増大は、容量のサイズ増大、ひいては遅延回路全体のサイズ増大につながる。

10

【0005】

本発明は、上述した事情を考慮し、従来と同じ遅延時間を、従来よりもコンパクトなサイズで発生可能な遅延回路を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の実施形態に係る遅延回路は、入力端子に接続されるゲートと、第1の電源電圧を供給する電源端子に接続されるソースと、ドレインとを有する第1のトランジスタと、前記第1の電源電圧を供給する電源端子に接続される第1端と、前記第1のトランジスタのドレインに接続される第2端とを有する容量と、前記第1のトランジスタのゲート及び前記入力端子に接続されるゲートと、前記第1のトランジスタのドレイン及び前記容量の第2端に接続されるドレインと、ソースとを有する第2のトランジスタと、前記第2のトランジスタのソースと、前記第1の電源電圧とは異なる第2の電源電圧を供給する電源端子との間に接続され、前記第2のトランジスタを介して接続される前記容量を充電する定電流を供給する第1の定電流源と、前記第1のトランジスタのドレインと、前記第2のトランジスタのドレインと、前記容量の第2端との節点に接続されるゲートと、前記第2の電源電圧を供給する電源端子に接続されるソースと、ドレインとを有する第3のトランジスタと、前記節点及び前記第3のトランジスタのゲートに接続されるゲートと、前記第3のトランジスタのドレイン及び出力端子に接続されるドレインと、ソースとを有する第4のトランジスタと、前記第1の電源電圧を供給する電源端子と前記第4のトランジスタのソースとを通電可能に接続し、前記容量の充電が開始された後に電圧降下を生じる抵抗体と、を備え、前記第1のトランジスタと前記第4のトランジスタとは、p型及びn型の一方である第1の導電型のMOSトランジスタであり、前記第2のトランジスタ及び前記第3のトランジスタは、p型及びn型の他方である第2の導電型のMOSトランジスタであることを特徴とする。

20

【発明の効果】

【0007】

本発明によれば、従来と同じ遅延時間を、従来よりもコンパクトなサイズで発生させることができる。

30

【図面の簡単な説明】

【0008】

40

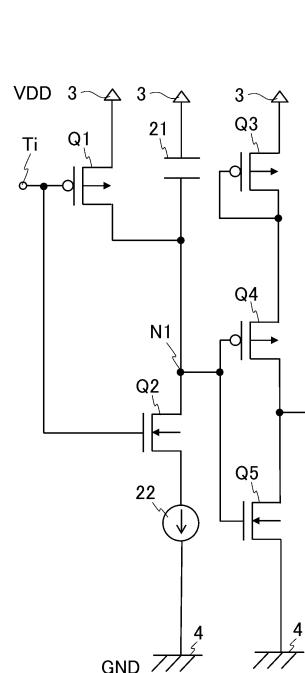

【図1】本発明の第1の実施形態に係る遅延回路の回路図である。

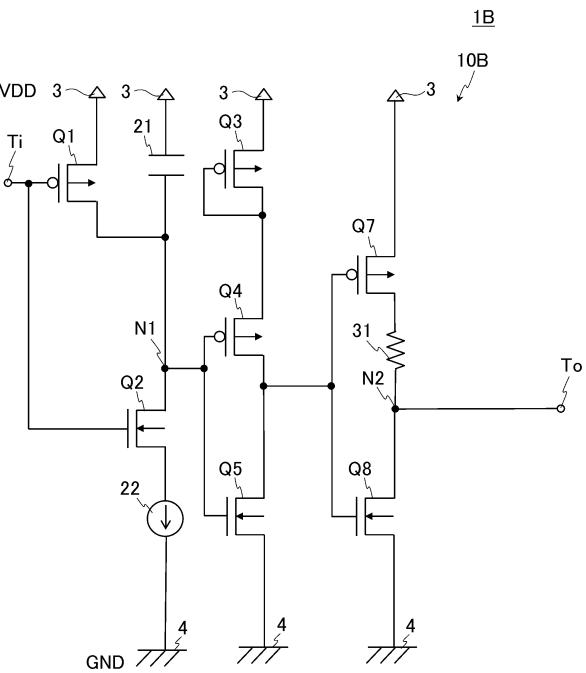

【図2】本発明の第2の実施形態に係る遅延回路の回路図である。

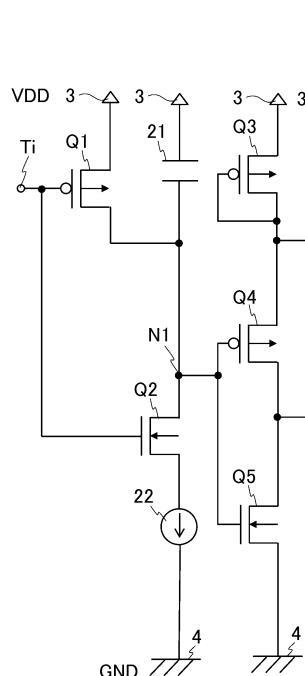

【図3】本発明の第3の実施形態に係る遅延回路の回路図である。

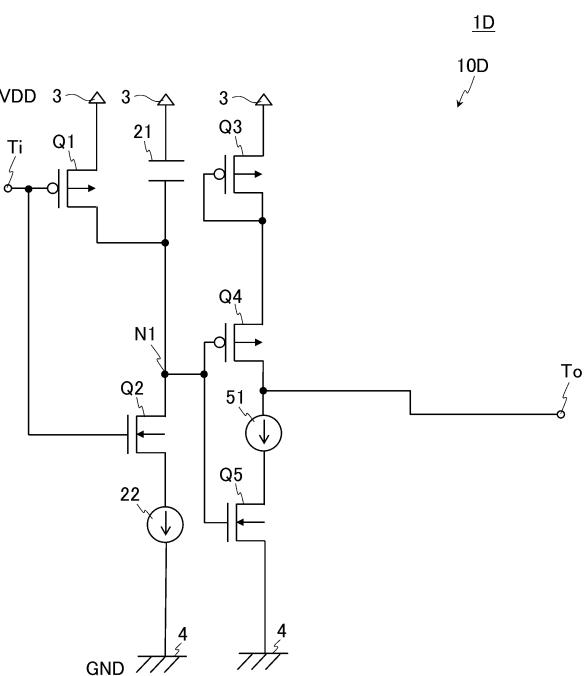

【図4】本発明の第4の実施形態に係る遅延回路の回路図である。

【図5】本発明の実施形態に係る遅延回路の第1変形例を示す回路図である。

【図6】本発明の実施形態に係る遅延回路の第2変形例を示す回路図である。

【図7】本発明の実施形態に係る遅延回路の第3変形例を示す回路図である。

【発明を実施するための形態】

【0009】

【第1の実施形態】

50

図1は、本発明の第1の実施形態に係る遅延回路の一例である遅延回路10Aの回路図である。

【0010】

遅延回路10Aは、例えば、半導体基板上に形成され、半導体装置1Aに具備されている。遅延回路10Aは、例えば、p型のMOSトランジスタ（以下、「PMOSトランジスタ」とする。）Q1, Q3, Q4と、n型のMOSトランジスタ（以下、「NMOSトランジスタ」とする。）Q2, Q5と、容量21と、定電流源22と、を備えている。

【0011】

第1のトランジスタとしてのPMOSトランジスタQ1は、入力端子Tiに接続されるゲートと、電源端子3に接続されるソースと、ドレインとを有する。電源端子3は、電源電圧としての電圧VDDを供給する電源端子である。

10

【0012】

容量21は、電源端子3とPMOSトランジスタQ1のドレインとの間に接続されている。すなわち、容量21は、電源端子3に接続される第1端と、PMOSトランジスタQ1のドレインに接続される第2端とを有している。

【0013】

第2のトランジスタとしてのNMOSトランジスタQ2は、PMOSトランジスタQ1のゲート及び入力端子Tiに接続されるゲートと、PMOSトランジスタQ1のドレイン及び容量21の第2端に接続されるドレインと、ソースとを有している。

20

【0014】

第1の定電流源としての定電流源22は、NMOSトランジスタQ2のソースと、電源端子としての接地端子4との間に接続されている。接地端子4は、接地電圧GNDを供給する電源端子である。電源電圧としての接地電圧GNDは、例えば、0V等の基準となる電圧であり、電圧VDDと異なる電圧である。

【0015】

第3のトランジスタとしてのNMOSトランジスタQ5は、節点N1に接続されるゲートと、接地端子4に接続されるソースと、ドレインとを有している。節点N1は、PMOSトランジスタQ1のドレインと、NMOSトランジスタQ2のドレインと、容量の第2端との接続点である。

【0016】

第4のトランジスタとしてのPMOSトランジスタQ4は、節点N1及びNMOSトランジスタQ5のゲートに接続されるゲートと、NMOSトランジスタQ5のドレイン及び出力端子Toに接続されるドレインと、ソースとを有している。

30

【0017】

抵抗体としてのPMOSトランジスタQ3は、ゲートとドレインとが接続（短絡）されており、例えば、互いに接続されたゲート及びドレインである第1端と、ソースである第2端とを備える抵抗体として機能する。いわゆるダイオード接続されたPMOSトランジスタQ3は、第4のトランジスタのソースと接続される第1端としてのゲート及びドレインと、電源端子3と接続される第2端としてのソースと、を有している。

【0018】

ここで、本実施形態に係る遅延回路における第1～4のトランジスタの導電型の関係は、第1のトランジスタ及び第4のトランジスタは、p型及びn型の一方である第1の導電型である。一方、第2のトランジスタ及び第3のトランジスタは、p型及びn型の他方で第1の導電型とは異なる第2の導電型である。図1に例示される遅延回路10Aでは、第1の導電型がp型、第2の導電型がn型の一例である。

40

【0019】

次に、遅延回路10Aの動作について説明する。

入力端子Tiにローレベル（以下、「Lレベル」とする。）の電圧が入力されると、PMOSトランジスタQ1はオンし、NMOSトランジスタQ2はオフするため、PMOSトランジスタQ4のゲート及びNMOSトランジスタQ5のゲートには、電圧VDD、す

50

なわちハイレベル（以下、「Hレベル」とする。）の電圧が供給される。従って、PMOSトランジスタQ4はオフし、NMOSトランジスタQ5はオンし、出力端子Toから出力される電圧の電圧レベルはLレベルとなる。

#### 【0020】

ここで、入力端子Tiに入力される電圧の電圧レベルがLレベルからHレベルに遷移すると、PMOSトランジスタQ1はオンからオフに遷移し、NMOSトランジスタQ2はオフからオンに遷移する。PMOSトランジスタQ1がオフし、NMOSトランジスタQ2がオンすると、定電流源22の定電流によって容量21に電荷のチャージが開始される。容量21は入力端子Tiに入力される電圧の電圧レベルが遷移したタイミングから出力端子Toから出力される電圧の電圧レベルが遷移するまでの遅延時間を発生させる。従って、容量21に電荷のチャージが開始される時点では、出力端子Toから出力される電圧の電圧レベルはLレベルが維持されている。

10

#### 【0021】

その後、電荷のチャージが進行するにつれて容量21の両端の電圧が上昇し節点N1の電圧が下降する。やがて、節点N1の電圧がPMOSトランジスタQ3とPMOSトランジスタQ4とNMOSトランジスタQ5とで構成される回路（インバータ）から出力される電圧の電圧レベルが遷移する閾値（以下、単に「閾値」とする。）を下回ると、出力される電圧の電圧レベルはLレベルからHレベルに遷移し、出力端子ToからHレベルの電圧が供給される。

20

#### 【0022】

遅延回路10Aは、遅延回路10Aにおける容量21とPMOSトランジスタQ3を備えない遅延回路における容量とが同じ容量値であった場合、PMOSトランジスタQ3を備えない遅延回路と比べて、PMOSトランジスタQ4及びNMOSトランジスタQ5で構成される回路の閾値を低くすることができる。従って、遅延時間に着目すれば、遅延回路10Aは、同じサイズのPMOSトランジスタQ3を備えない遅延回路よりも大きな遅延時間を発生させることができる。

30

#### 【0023】

一方、PMOSトランジスタQ3を備えない遅延回路の遅延時間と、遅延回路10Aの遅延時間とを同じにした場合、遅延回路10Aにおける容量21の容量値は、PMOSトランジスタQ3を備えない遅延回路の容量の容量値よりも小さくすることができる。従って、回路サイズに着目すれば、遅延回路10Aは、遅延時間が同じであって、PMOSトランジスタQ3を備えない遅延回路に対して、全体的な回路サイズを小さくすることができる。

40

#### 【0024】

なお、本実施形態では、抵抗体として1段のダイオード接続されたPMOSトランジスタQ3が適用された例を説明したが、抵抗体はこれに限定されない。

#### 【0025】

抵抗体は、所定の電圧降下を発生させる单一又は複数の素子を有していればよく、ダイオードや抵抗が適用されていてもよい。ダイオードには、ダイオード素子のみならず、ダイオード接続されたMOSトランジスタが含まれる。また、抵抗体は、ダイオード接続されたMOSトランジスタ、ダイオード素子及び抵抗が複数個縦続接続されて構成されてもよい。

40

#### 【0026】

##### [第2の実施形態]

図2は、本発明の第2の実施形態に係る遅延回路の一例である遅延回路10Bの回路図である。

#### 【0027】

遅延回路10Bは、遅延回路10Aに対して、抵抗体としてのPMOSトランジスタQ3の代わりにダイオードとしてのPMOSトランジスタQ3を備える点と、PMOSトランジスタQ7と、NMOSトランジスタQ8と、抵抗31とをさらに備える点とで相違し

50

ているが、その他の点については実質的に相違しない。そこで、本実施形態では、遅延回路 10 A と相違する構成要素、作用及び効果を中心に説明するとともに、遅延回路 10 A と実質的に相違しない構成要素については、同じ符号を付して説明を省略する。

#### 【0028】

遅延回路 10 B は、例えば、半導体基板上に形成され、半導体装置 1 B に具備されている。遅延回路 10 B は、抵抗体としての PMOS トランジスタ Q3、PMOS トランジスタ Q1, Q4、NMOS トランジスタ Q2, Q5、容量 21 及び定電流源 22 と、例えば、PMOS トランジスタ Q7 と、NMOS トランジスタ Q8 と、抵抗 31 とをさらに備えている。

#### 【0029】

第 5 のトランジスタとしての PMOS トランジスタ Q7 は、PMOS トランジスタ Q4 のドレインと接続されるゲートと、電源端子 3 に接続されるソースと、抵抗 31 の第 1 端と接続されるドレインとを有している。

#### 【0030】

第 6 のトランジスタとしての NMOS トランジスタ Q8 は、PMOS トランジスタ Q7 のゲート及び PMOS トランジスタ Q4 のドレインと接続されるゲートと、接地端子 4 に接続されるソースと、抵抗 31 の第 2 端及び出力端子 To と接続されるドレインとを有している。ここで、NMOS トランジスタ Q8 のドレインと抵抗 31 の第 2 端との接続点を節点 N2 と呼称する。遅延回路 10 B では、出力端子 To が節点 N2 に接続されている。

#### 【0031】

PMOS トランジスタ Q7 と、NMOS トランジスタ Q8 と、抵抗 31 とを備えて構成される回路の閾値は、PMOS トランジスタ Q4 及び NMOS トランジスタ Q5 のドレインと接続する経路に流れる貫通電流と PMOS トランジスタ Q3 で決まる電圧に対して低いものとする。すなわち、PMOS トランジスタ Q4 のドレイン及び NMOS トランジスタ Q5 のドレインとの節点から出力される電圧の電圧レベルが L レベルから H レベルに遷移した際に、NMOS トランジスタ Q8 がオンするように構成される。

#### 【0032】

PMOS トランジスタ Q7 と、NMOS トランジスタ Q8 と、抵抗 31 とを備えて構成される回路（インバータ）の閾値は、抵抗 31 の抵抗値の大小を変えることで、所望の閾値に調整可能である。

#### 【0033】

ここで、本実施形態に係る遅延回路における第 1 ~ 6 のトランジスタの導電型の関係は、第 1, 4, 5 のトランジスタは、p 型及び n 型の一方である第 1 の導電型である。一方、第 2, 3, 6 のトランジスタは、p 型及び n 型の他方で第 1 の導電型とは異なる第 2 の導電型である。図 2 に例示される遅延回路 10 B では、第 1 の導電型が p 型、第 2 の導電型が n 型の一例である。

#### 【0034】

続いて、遅延回路 10 B の動作について説明する。なお、遅延回路 10 A と重複する構成要素についての動作は実質的に同じであるため、当該動作については説明を簡略又は省略する。

#### 【0035】

入力端子 Ti に L レベルの電圧が入力されると、PMOS トランジスタ Q4 のドレイン及び NMOS トランジスタ Q5 のドレインとの節点からは L レベルの電圧が出力される。PMOS トランジスタ Q7 のゲート及び NMOS トランジスタ Q8 のゲートには L レベルの電圧が印加され、PMOS トランジスタ Q7 がオンし、NMOS トランジスタ Q8 がオフする。従って、PMOS トランジスタ Q7 のドレインと NMOS トランジスタ Q8 のドレインとの節点から出力端子 To へ供給される電圧は H レベルの電圧となる。

#### 【0036】

入力端子 Ti に入力される電圧の電圧レベルが L レベルから H レベルに遷移すると、遅延時間が発生する。当該遅延時間経過後、PMOS トランジスタ Q4 のドレイン及び NM

10

20

30

40

50

O SトランジスタQ 5のドレインとの節点から出力される電圧の電圧レベルは、L レベルからH レベルに遷移する。

【 0 0 3 7 】

遅延時間経過直後は、PMOSトランジスタQ 4のドレイン及びNMOSトランジスタQ 5のドレインとの節点から出力される電圧は、PMOSトランジスタQ 4及びNMOSトランジスタQ 5のドレインと接続する経路に流れる貫通電流とPMOSトランジスタQ 3で決まる電圧までしか上昇しない。しかしながら、遅延時間経過直後のPMOSトランジスタQ 4のドレイン及びNMOSトランジスタQ 5のドレインとの節点から出力される電圧の電圧上昇は、NMOSトランジスタQ 8をオフ状態からオン状態へ遷移させる。

【 0 0 3 8 】

NMOSトランジスタQ 8がオフ状態からオン状態に遷移する一方、PMOSトランジスタQ 7は、PMOSトランジスタQ 4のドレイン及びNMOSトランジスタQ 5のドレインとの節点から出力される電圧の上昇が十分でない段階では、オン状態からオフ状態に遷移しない。しかしながら、PMOSトランジスタQ 7がオン状態のままでも、PMOSトランジスタQ 7のドレインとNMOSトランジスタQ 8のドレインと間に抵抗31が接続されているので、抵抗31の両端に電圧降下が生じる。

【 0 0 3 9 】

従って、NMOSトランジスタQ 8がオフ状態からオン状態に遷移すれば、抵抗31の両端に電圧降下が生じることによって、PMOSトランジスタQ 7のドレインとNMOSトランジスタQ 8のドレインとの節点から出力端子T oへ供給される電圧は、H レベルからL レベルへ遷移する。なお、PMOSトランジスタQ 7がオフ状態に遷移した場合、PMOSトランジスタQ 7のドレインとNMOSトランジスタQ 8のドレインとの節点から出力端子T oへ供給される電圧はL レベルの電圧である。

【 0 0 4 0 】

このように、NMOSトランジスタQ 8がオフ状態からオン状態に遷移すれば、PMOSトランジスタQ 7のオン／オフ状態にかかわらず、PMOSトランジスタQ 7のドレインとNMOSトランジスタQ 8のドレインとの節点から出力端子T oへ供給される電圧はL レベルの電圧となる。

【 0 0 4 1 】

遅延回路10Bによれば、遅延回路10Aと同様の効果を得ることができる。すなわち、回路サイズに着目すれば、遅延回路10Bは、従来と同じ遅延時間を、従来よりもコンパクトなサイズで発生させることができる。また、遅延時間に着目すれば、遅延回路10Bは、従来の遅延回路と同じサイズで、従来よりも大きな遅延時間を発生させができる。

【 0 0 4 2 】

また、遅延回路10Bによれば、PMOSトランジスタQ 4のドレイン及びNMOSトランジスタQ 5のドレインから出力される電圧が十分に上昇していない遅延時間経過直後においても電圧レベルを確実に遷移させることができる。

【 0 0 4 3 】

【 第3の実施形態 】

図3は、本発明の第3の実施形態に係る遅延回路の一例である遅延回路10Cの回路図である。

【 0 0 4 4 】

遅延回路10Cは、遅延回路10Aに対して、PMOSトランジスタQ 9と、インバータ41とをさらに備える点で相違しているが、その他の点については実質的に相違しない。そこで、本実施形態では、遅延回路10Aと相違する構成要素、作用及び効果を中心に説明するとともに、遅延回路10Aと実質的に相違しない構成要素については同じ符号を付し説明を省略する。

【 0 0 4 5 】

遅延回路10Cは、例えば、半導体基板上に形成され、半導体装置1Cに具備されてい

10

20

30

40

50

る。遅延回路 10C は、ダイオードとしての PMOS トランジスタ Q3、PMOS トランジスタ Q1, Q4、NMOS トランジスタ Q2, Q5、容量 21 及び定電流源 22 と、例えば、PMOS トランジスタ Q9 と、インバータ 41 と、をさらに備えている。ダイオードとしての PMOS トランジスタ Q3 は、抵抗を利用する場合と比べて、リーク電流が流れる場合においても所望の電圧降下を得つつ消費電流を抑える観点から接続されている。

#### 【0046】

第 7 のトランジスタとしての PMOS トランジスタ Q9 は、ゲートと、電源端子 3 に接続されるソースと、PMOS トランジスタ Q4 のソース及びダイオード接続された PMOS トランジスタ Q3 のゲート及びドレインに接続されるドレインとを有している。

#### 【0047】

インバータ 41 は、PMOS トランジスタ Q4 のドレインと接続される入力端と、PMOS トランジスタ Q9 のゲートと接続される出力端とを有している。ここで、インバータ 41 の入力端と出力端子 Ti との接続点を、節点 N3 と呼称する。遅延回路 10C では、PMOS トランジスタ Q4 のドレイン及び NMOS トランジスタ Q5 のドレインが、節点 N3 と接続されている。

#### 【0048】

ここで、本実施形態に係る遅延回路における第 1 ~ 7 のトランジスタの導電型の関係は、第 1, 4, 5, 7 のトランジスタは、p 型及び n 型の一方である第 1 の導電型である。一方、第 2, 3, 6 のトランジスタは、p 型及び n 型の他方で第 1 の導電型とは異なる第 2 の導電型である。図 3 に例示される遅延回路 10C では、第 1 の導電型が p 型、第 2 の導電型が n 型の一例である。

#### 【0049】

続いて、遅延回路 10C の動作について説明する。なお、遅延回路 10A と重複する構成要素についての動作は実質的に同じであるため、当該動作については説明を簡略又は省略する。

#### 【0050】

入力端子 Ti に L レベルの電圧が入力されると、PMOS トランジスタ Q4 のドレイン及び NMOS トランジスタ Q5 のドレインとの節点からは L レベルの電圧が output される。ここで、PMOS トランジスタ Q9 は、PMOS トランジスタ Q4 のドレインから出力される電圧に基づく電圧をゲートに受ける。遅延回路 10C では、PMOS トランジスタ Q4 のドレイン及び NMOS トランジスタ Q5 のドレインとの節点から出力される電圧が、インバータ 41 を経由して PMOS トランジスタ Q9 のゲートに供給される。このとき、PMOS トランジスタ Q9 のゲートには、H レベルの電圧が供給されるため、PMOS トランジスタ Q9 はオフ状態である。

#### 【0051】

入力端子 Ti に入力される電圧の電圧レベルが L レベルから H レベルに遷移すると、遅延時間が発生する。PMOS トランジスタ Q4 のドレイン及び NMOS トランジスタ Q5 のドレインとの節点から出力される電圧の電圧レベルは、L レベルから H レベルに遷移する。PMOS トランジスタ Q9 は、そのゲートに、インバータ 41 を介して L レベルの電圧が入力されるため、オンする。

#### 【0052】

PMOS トランジスタ Q9 がオンに遷移すると、PMOS トランジスタ Q3 に比べて PMOS トランジスタ Q9 のオン抵抗は極めて小さいことから、PMOS トランジスタ Q4 のドレインと PMOS トランジスタ Q3 を介して電源端子 3 と接続される経路は無視することができる。すなわち、PMOS トランジスタ Q4 のドレインは、オン状態の PMOS トランジスタ Q9 を介して電源端子 3 と接続される。

#### 【0053】

従って、入力端子 Ti に入力される電圧の電圧レベルが L レベルから H レベルに遷移すると、遅延時間経過後には、PMOS トランジスタ Q4 のドレイン及び NMOS トランジスタ Q5 のドレインとの節点の電圧を、電圧 VDD に上昇させることができる。

10

20

30

40

50

## 【0054】

遅延回路10Cによれば、消費電流を増加させることなく、遅延回路10Aと同様の効果を得ることができる。すなわち、回路サイズに着目すれば、遅延回路10Cは、従来と同じ遅延時間を、消費電流を増加させることなく、かつ従来よりもコンパクトなサイズで発生させることができる。また、遅延時間に着目すれば、遅延回路10Cは、従来の遅延回路と同じサイズで、従来よりも大きな遅延時間を、消費電流を増加させることなく発生させることができる。

## 【0055】

また、遅延回路10Cによれば、遅延時間経過後に、電源端子3からPMOSトランジスタQ4へ流れる電流の経路を、PMOSトランジスタQ3を経由する経路からPMOSトランジスタQ9を経由する経路に切り替えることで、PMOSトランジスタQ4及びNMOSトランジスタQ5のドレインの電圧を電圧VDDに上昇させる。PMOSトランジスタQ4及びNMOSトランジスタQ5のドレインの電圧を電圧VDDに上昇させることによって、外部回路が output 端子Toに接続されている場合に、当該外部回路へ流れる貫通電流の影響を抑制することができる。

10

## 【0056】

なお、本実施形態では、ダイオードとして1段のダイオード接続されたPMOSトランジスタQ3が適用された例を説明したが、ダイオードはこれに限定されない。

## 【0057】

ダイオードは、ダイオード接続されたMOSトランジスタに限らず、ダイオード素子が適用されていてもよい。また、ダイオードは、ダイオード接続されたMOSトランジスタ又はダイオード素子が複数個縦続接続されて構成されていてもよい。

20

## 【0058】

## [第4の実施形態]

図4は、本発明の第4の実施形態に係る遅延回路の一例である遅延回路10Dの回路図である。

## 【0059】

遅延回路10Dは、例えば、半導体基板上に形成され、半導体装置1Dに具備されている。遅延回路10Dは、遅延回路10Aに対して、定電流源51をさらに備える点で相違しているが、その他の点については実質的に相違しない。そこで、本実施形態では、遅延回路10Aと相違する構成要素、作用及び効果を中心にして説明するとともに、遅延回路10Aと実質的に相違しない構成要素については同じ符号を付し説明を省略する。

30

## 【0060】

遅延回路10Dは、抵抗体としてのPMOSトランジスタQ3、PMOSトランジスタQ1, Q4、NMOSトランジスタQ2, Q5、容量21及び定電流源22と、例えば、定電流源51と、をさらに備えている。第2の定電流源としての定電流源51は、PMOSトランジスタQ4のドレインとNMOSトランジスタQ5のドレインとの間に接続されている。

## 【0061】

ここで、本実施形態に係る遅延回路における第1～7のトランジスタの導電型の関係は、第3の実施形態に係る遅延回路における第1～7のトランジスタの導電型の関係と同じである。すなわち、第1, 4, 5, 7のトランジスタは第1の導電型であり、第2, 3, 6のトランジスタは第2の導電型である。図4に例示される遅延回路10Dでは、第1の導電型がp型、第2の導電型がn型の一例である。

40

## 【0062】

続いて、遅延回路10Dの動作について説明する。なお、遅延回路10Aと重複する構成要素についての動作は実質的に同じであるため、当該動作については説明を簡略又は省略する。

## 【0063】

入力端子TiにLレベルの電圧が入力されると、PMOSトランジスタQ4のドレイン

50

及び定電流源 5 1との節点からは L レベルの電圧が出力される。また、定電流源 5 1は、所定の定電流を N M O S トランジスタ Q 5 のドレインに供給する。

【 0 0 6 4 】

入力端子 T i に入力される電圧の電圧レベルが L レベルから H レベルに遷移すると、遅延時間が発生する。当該遅延時間経過後、P M O S トランジスタ Q 4 のドレイン及び定電流源 5 1との節点から出力される電圧の電圧レベルは、L レベルから H レベルに遷移する。

【 0 0 6 5 】

ここで、P M O S トランジスタ Q 3 、P M O S トランジスタ Q 4 、定電流源 5 1 及び N M O S トランジスタ Q 5 を備える回路の閾値は、定電流源 5 1 が供給する所定の定電流と P M O S トランジスタ Q 3 で決まる電圧と、P M O S トランジスタ Q 4 のゲート・ソース間電圧とで決定される。一方、P M O S トランジスタ Q 4 のドレインと N M O S トランジスタ Q 5 のドレインとの間に接続される定電流源 5 1 を備えず、P M O S トランジスタ Q 3 、P M O S トランジスタ Q 4 及び N M O S トランジスタ Q 5 を備える回路の閾値は、P M O S トランジスタ Q 4 の閾値電圧と N M O S トランジスタ Q 5 の閾値電圧と P M O S トランジスタ Q 3 によって降下する電圧とで決定される。

10

【 0 0 6 6 】

従って、定電流源 5 1 を備えていない遅延回路では、発生させる遅延時間が、電源端子 3 の電圧 V D D の影響を受けてしまう。すなわち、P M O S トランジスタ Q 4 のドレインと N M O S トランジスタ Q 5 のドレインとの間に接続される定電流源 5 1 を備えていない遅延回路では、発生させる遅延時間の電圧 V D D に対する依存性が大きい。

20

【 0 0 6 7 】

これに対して、遅延回路 1 0 D のような P M O S トランジスタ Q 4 のドレインと N M O S トランジスタ Q 5 のドレインとの間に接続される定電流源 5 1 を備える遅延回路は、発生させる遅延時間が電源端子 3 の電圧 V D D の影響を受けない。すなわち、電圧 V D D に依存しない遅延時間を発生させる。

【 0 0 6 8 】

遅延回路 1 0 D によれば、遅延回路 1 0 A と同様の効果を得ることができる。すなわち、回路サイズに着目すれば、遅延回路 1 0 D は、従来と同じ遅延時間を、従来よりもコンパクトなサイズで発生させることができる。また、遅延時間に着目すれば、遅延回路 1 0 D は、従来の遅延回路と同じサイズで、従来よりも大きな遅延時間を発生させることができる。

30

【 0 0 6 9 】

また、遅延回路 1 0 D によれば、定電流源 5 1 を備えることによって、電圧 V D D に依存しない遅延時間を発生させることができる。

【 0 0 7 0 】

なお、本発明は、上述した実施形態そのままに限定されるものではなく、実施段階では、上述した例以外にも様々な形態で実施することが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更をすることができる。例えば、上述した構成例の他、後述する遅延回路 1 0 E , 1 0 F , 1 0 G のように、遅延回路 1 0 A ~ 1 0 D の構成要素を適宜組み合わせた構成（第 1 , 2 , 3 变形例）への変形が可能である。

40

【 0 0 7 1 】

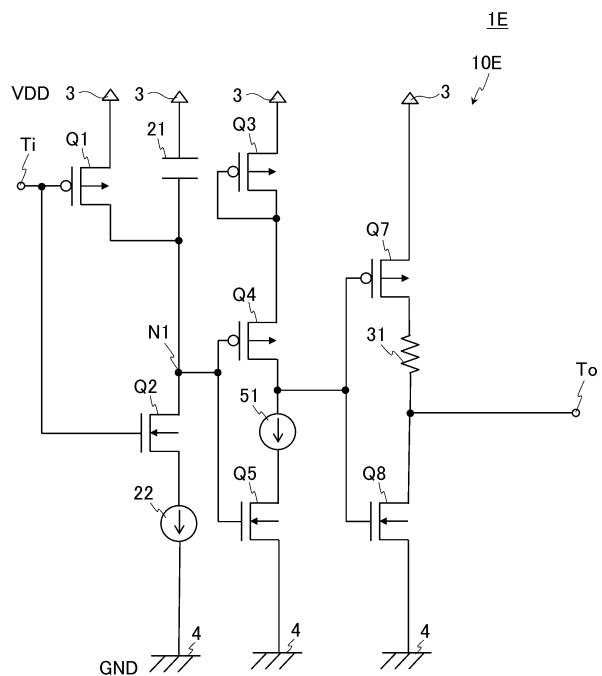

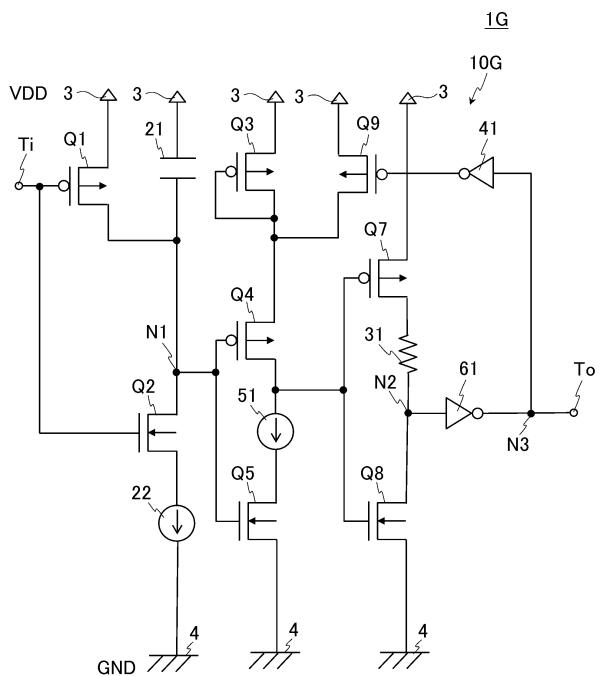

図 5 、図 6 及び図 7 は、それぞれ、本発明の実施形態に係る遅延回路の第 1 变形例、第 2 变形例及び第 3 变形例である遅延回路 1 0 E 、遅延回路 1 0 F 及び遅延回路 1 0 G の回路図である。

【 0 0 7 2 】

遅延回路 1 0 E , 1 0 F , 1 0 G は、例えば、上述した遅延回路 1 0 A ~ 1 0 D と同様に、半導体基板上に形成され、半導体装置 1 E , 1 F , 1 G に具備されている。遅延回路 1 0 E は、遅延回路 1 0 B に対して、定電流源 5 1 をさらに備えて構成されている。すなわち、遅延回路 1 0 E は、遅延回路 1 0 A に対して、P M O S トランジスタ Q 7 と、N M O S トランジスタ Q 8 と、抵抗 3 1 と、定電流源 5 1 とをさらに備えて構成されている。

50

遅延回路 10 E によれば、遅延回路 10 A, 10 B, 10 D と同様の効果を得ることができる。

【0073】

遅延回路 10 F は、遅延回路 10 C に対して、定電流源 51 をさらに備えて構成されている。すなわち、遅延回路 10 F は、遅延回路 10 A に対して、PMOS ドランジスタ Q9 と、インバータ 41 と、定電流源 51 とをさらに備えて構成されている。遅延回路 10 F によれば、遅延回路 10 A, 10 C, 10 D と同様の効果を得ることができる。

【0074】

遅延回路 10 G は、遅延回路 10 E に対して、PMOS ドランジスタ Q9 と、インバータ 41 と、インバータ 61 とをさらに備えて構成されている。すなわち、遅延回路 10 G は、遅延回路 10 A に対して、PMOS ドランジスタ Q7 と、NMOS ドランジスタ Q8 と、抵抗 31 と、定電流源 51 と、PMOS ドランジスタ Q9 と、インバータ 41 と、インバータ 61 とをさらに備えて構成されている。インバータ 61 は、節点 N2 に接続される入力端と、節点 N3 に接続される出力端とを有している。遅延回路 10 G によれば、遅延回路 10 A, 10 B, 10 C, 10 D と同様の効果を得ることができる。

10

【0075】

なお、この遅延回路 10 G から、2 個のインバータ 41, 61 及び定電流源 51 の少なくとも一方を省略して遅延回路が構成されていてもよい。遅延回路 10 G から 2 個のインバータ 41, 61 が省略された遅延回路では、PMOS ドランジスタ Q4 のドレインから出力される電圧が、PMOS ドランジスタ Q4 のドレインから出力される電圧に基づく電圧として、PMOS ドランジスタ Q9 のゲートに直接印加される。

20

【0076】

また、上述した本実施形態に係る遅延回路において、入力端子 Ti に入力される電圧を、その電圧レベルを反転させて出力端子 To から出力する構成としてもよい。この場合、例えば、遅延回路 10 G において、インバータ 41 又はインバータ 61 の接続位置を変更することによる変形が可能である。具体的に説明すれば、遅延回路 10 G において、インバータ 61 を節点 N3 と PMOS ドランジスタ Q9 のゲートとを接続する経路上に設けたり、インバータ 41 を節点 N2 と節点 N3 とを接続する経路上に設けたりしてもよい。

【0077】

さらに、実施形態に係る遅延回路の他の構成例として、上述した遅延回路に対して、半導体素子の導電型 (p 型及び n 型) 並びに端子及び各素子の接続関係を反転させた構成としてもよい。

30

【0078】

上述した実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0079】

1A ~ 1G 半導体装置

10A ~ 10G 遅延回路

21 容量

22 定電流源 (第 1 の定電流源)

40

31 抵抗

41 インバータ

51 定電流源 (第 2 の定電流源)

Q1 PMOS ドランジスタ (第 1 のトランジスタ)

Q2 NMOS ドランジスタ (第 2 のトランジスタ)

Q3 PMOS ドランジスタ (抵抗体、ダイオード)

Q4 PMOS ドランジスタ (第 4 のトランジスタ)

Q5 NMOS ドランジスタ (第 3 のトランジスタ)

Q7 PMOS ドランジスタ (第 5 のトランジスタ)

50

Q 8 N M O Sトランジスタ (第6のトランジスタ)Q 9 P M O Sトランジスタ (第7のトランジスタ)

【図面】

【図1】

1A

10A

【図2】

1B

10B

10

20

【図3】

1C

10C

【図4】

1D

10D

30

40

40

50

【図 5】

【図 6】

10

20

【図 7】

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開2002-124858 (JP, A)

- 特開2010-4526 (JP, A)

- 特開平5-110396 (JP, A)

- 特開平5-304464 (JP, A)

- 特開2003-273712 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- H03K5/13-5/145

- H03K19/0175-19/0185