(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4989931号

(P4989931)

(45) 発行日 平成24年8月1日(2012.8.1)

(24) 登録日 平成24年5月11日(2012.5.11)

(51) Int.Cl.

F 1

H04B 3/04 (2006.01)

H04L 25/03 (2006.01)H04B 3/04

H04L 25/03A

C

請求項の数 25 (全 20 頁)

(21) 出願番号 特願2006-193262 (P2006-193262)

(22) 出願日 平成18年7月13日 (2006.7.13)

(65) 公開番号 特開2007-28625 (P2007-28625A)

(43) 公開日 平成19年2月1日 (2007.2.1)

審査請求日 平成21年7月3日 (2009.7.3)

(31) 優先権主張番号 11/182,658

(32) 優先日 平成17年7月14日 (2005.7.14)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 597154922

アルテラ コーポレイション

Altera Corporation

アメリカ合衆国 95134 カリフォルニア州 サンホセ イノベーション ドライヴ 101

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100062409

弁理士 安村 高明

(74) 代理人 100113413

弁理士 森下 夏樹

最終頁に続く

(54) 【発明の名称】プログラム可能な、レシーバの等化回路および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

伝送媒体を介してドライバによって伝送されるデータ信号を受信するレシーバ回路であつて、該レシーバ回路は、

少なくとも 1 つの制御デバイスと、

該データ信号に対する等化をプログラム可能に提供する等化回路であつて、該データ信号は該等化回路の入力部において受信され、該等化されたデータ信号は該等化回路の出力部において提供され、

該等化回路は、複数のステージを備え、各ステージは、該少なくとも 1 つの制御デバイスから送信される第 1 の制御信号を用いて制御され、該第 1 の制御信号は、n ビット制御信号を含み、

該第 1 の制御信号は、該ステージが、該ステージに関連付けられている周波数範囲内で、該等化回路によって提供されるゲインの傾きを増大させるかどうかを決定し、該ステージが該ゲインの傾きを増大させるように決定された場合に、該第 1 の制御信号は、該ステージに関連付けられている該周波数範囲内の  $2^n - 1$  個の選択可能な周波数からの第 1 の周波数を示し、該データ信号に提供される該ゲインの傾きは、該第 1 の周波数で増大し、

該第 1 の周波数は、該少なくとも 1 つの制御デバイスによってプログラム可能に制御され、それによって、該等化回路は、該伝送媒体によって起こる減衰を補償するために、該データ信号にゲインを提供する、等化回路と、

10

20

入力部および出力部を有するバッファであって、該バッファの該入力部は、該等化回路の該出力部に結合されることにより、該バッファに結合された他の回路のインピーダンスを、該等化回路の該出力部インピーダンスから分離し、該バッファの該出力部は、該等化回路の該入力部に結合されることにより、該等化回路にネガティブフィードバック信号を提供し、該等化回路は、該ネガティブフィードバック信号に基づいて、該データ信号に適用されるゲインを調整する、バッファと

を備える、レシーバ回路。

【請求項 2】

前記複数のステージの各々は、前記少なくとも 1 つの制御デバイスから送信される第 2 の制御信号によって制御されることにより、第 2 の周波数で前記ゲインの傾きを減少させるようにさらに構成され、該第 2 の制御信号は該第 2 の周波数を示す、請求項 1 に記載のレシーバ回路。 10

【請求項 3】

前記第 2 の周波数はプログラム可能に制御され、それによって、前記等化回路は前記データ信号における高周波ノイズをフィルタする、請求項 2 に記載のレシーバ回路。

【請求項 4】

前記複数のステージの各々は、前記データ信号に、所望される量の DC ゲインを提供するようにさらに構成される、請求項 1 に記載のレシーバ回路。

【請求項 5】

前記第 1 の周波数がプログラム可能に制御されることにより、前記ゲインの傾きを、前記伝送媒体によって起こる前記減衰の傾きと大きさが等しく、かつ、該減衰の傾きと符号が反対になるようにする、請求項 1 に記載のレシーバ回路。 20

【請求項 6】

前記複数のステージのステージが直列に結合される、請求項 1 に記載のレシーバ回路。

【請求項 7】

前記複数のステージのステージがカスケード化される、請求項 1 に記載のレシーバ回路。 。

【請求項 8】

前記等化回路の入力部に結合されたバイアス回路をさらに備え、該バイアス回路は、前記データ信号への DC バイアシングを提供して前記伝送媒体とマッチングするインピーダンスを提供するように構成される、請求項 1 に記載のレシーバ回路。 30

【請求項 9】

前記他の回路のうちの 1 つは信号検出回路である、請求項 1 に記載のレシーバ回路。

【請求項 10】

前記他の回路のうちの 1 つはオフセット消去回路である、請求項 1 に記載のレシーバ回路。

【請求項 11】

前記第 1 の周波数は、ネガティブフィードバック信号に少なくとも部分的にに基づいてプログラム可能に制御される、請求項 1 に記載のレシーバ回路。

【請求項 12】

伝送媒体を介してドライバによって伝送されるデータ信号を受信するレシーバ回路であって、該レシーバ回路は、

少なくとも 1 つの制御デバイスと、

該データ信号に対する等化をプログラム可能に提供する等化回路であって、該等化回路は、複数のステージを備え、各ステージは、該少なくとも 1 つの制御デバイスから送信される制御信号を用いて制御され、該制御信号は、n ビット制御信号を含み、

該制御信号は、該ステージが、該ステージに関連付けられている周波数範囲内で、該等化回路によって提供されるゲインの傾きを増大させるかどうかを決定し、該ステージが周波数応答の該ゲインの傾きを増大させるように決定された場合に、該制御信号は、該ステージに関連付けられている該周波数範囲内の  $2^n - 1$  個の選択可能な周波数からの第 1 50

の周波数を示し、該ゲインの傾きは、該第1の周波数で増大し、

該第1の周波数は、該少なくとも1つの制御デバイスによってプログラム可能に制御され、それによって、該等化回路は、該伝送媒体によって起こる減衰を補償するために、該データ信号にゲインを提供する、等化回路と、

該等化回路の出力部に結合されたスライサであって、該スライサに複数のクロックサイクルを提供するデジタルクロックに結合され、該スライサは、該複数のクロックサイクルのうちの1つ内の該データ信号が高い場合にデジタル高信号を割り当て、該複数のクロックサイクルのうちの1つ内の該データ信号が低い場合にデジタル低信号を割り当てることによって、該データ信号をデジタル信号へ変換し、該スライサは、該データ信号からクロックおよびデータ情報を抽出するクロックデータリカバリ回路を備える、スライサと

10

を備える、レシーバ回路。

【請求項13】

伝送媒体を介して伝送されるデータ信号に対する等化を提供する方法であって、該方法は、

第1および第2のステージを有する等化器を提供することと、

該第1および第2のステージの各々に対する少なくとも1つの制御デバイスが、該ステージによって該データ信号に提供されるゲインの傾きが、該ステージに関連付けられている周波数範囲内で増大するかどうかを決定するために該ステージに制御信号を送信することであって、該制御信号は、 $n$ ビット制御信号を含み、該制御信号は、該ステージに関連付けられている該周波数範囲内の $2^{n-1}$ 個の選択可能な周波数から1つの周波数を決定するためのものであり、該ゲインの傾きが増大すると決定された場合に、該ゲインの傾きは該1つの周波数で増大する、ことと、

20

該第1のステージに対して、該ゲインの傾きが増大可能な第1の周波数範囲を規定すること、および、該第2のステージに対して、該ゲインの傾きが増大可能な第2の周波数範囲を規定することであって、該第1の周波数範囲が該第2の周波数範囲とオーバーラップし、それによって、該オーバーラップする該第1の周波数範囲と該第2の周波数範囲とは、一緒に、該第1の周波数範囲および該第2の周波数範囲のうちのいずれの1つよりも広い連続的な周波数範囲をカバーする、ことと、

該少なくとも1つの制御デバイスが、該1つの周波数をプログラム可能に制御することであって、それによって、該第1のステージと該第2のステージとが該伝送媒体によって起こる減衰を補償するために十分なゲインを提供する、ことと、

30

等化されたデータ信号を生成するために、該第1のステージと該第2のステージとに該データ信号を適用することと

を包含する、方法。

【請求項14】

前記等化回路が前記データ信号に結合された望まれない高周波ノイズをフィルタするよう、前記少なくとも1つの制御デバイスが第2の周波数をプログラム可能に制御することであって、前記ゲインの傾きは、該第2の周波数で減少する、ことをさらに包含する、請求項13に記載の方法。

【請求項15】

伝達関数に所望される量のDCゲインを提供することをさらに包含する、請求項13に記載の方法。

【請求項16】

前記データ信号が高い場合にデジタル高信号を割り当て、該データ信号が低い場合にデジタル低信号を割り当てることによって、デジタル信号を生成するように、前記等化されたデータ信号を処理することをさらに包含する、請求項13に記載の方法。

【請求項17】

前記1つの周波数は、ユーザの入力に基づいて、プログラム可能に制御される、請求項13に記載の方法。

【請求項18】

10

20

30

40

50

前記1つの周波数がプログラム可能に制御されることにより、前記ゲインの傾きを、前記伝送媒体によって起こる前記減衰の傾きと大きさが等しく、かつ、該減衰の傾きと符号が反対になるようにする、請求項13に記載の方法。

【請求項19】

前記1つの周波数は、ネガティブフィードバックループ信号に少なくとも部分的に基づいてプログラム可能に制御される、請求項13に記載の方法。

【請求項20】

受信されたデータ信号に対する等化を提供する等化回路であって、該データ信号は伝送媒体を介して等化回路の入力部において受信され、該等化回路は、

制御デバイスから送信される制御信号を用いて制御されるステージを備え、

該制御信号は、該ステージが、該ステージに関連付けられている周波数範囲内で、該等化回路によって提供されるゲインの傾きを増大させるかどうかを決定し、該制御信号は、nビット制御信号を含み、該ステージが該ゲインの傾きを増大させることが決定された場合に、該制御信号は、該ステージに関連付けられている該周波数範囲内の $2^n - 1$ 個の選択可能な周波数からの第1の周波数を示し、該ゲインの傾きは、該第1の周波数で増大し、

該第1の周波数は、該制御デバイスによってプログラム可能に制御され、それによって、該等化回路は、該伝送媒体によって起こる減衰を補償するために、該データ信号にゲインを提供する、等化回路。

【請求項21】

前記第1および第2のステージのうちの少なくとも1つが、前記少なくとも1つの制御デバイスから前記制御信号を受信することをさらに包含し、

前記1つの周波数をプログラム可能に制御することは、該ステージが前記ゲインの傾きを増大させるように決定された場合に、該1つの周波数で該ステージによって提供される該ゲインの傾きを増大させることを包含する、請求項13に記載の方法。

【請求項22】

伝送媒体を介してドライバによって伝送されるデータ信号を受信するレシーバ回路であって、該レシーバ回路は、

少なくとも1つの制御デバイスと、

該データ信号に対する等化をプログラム可能に提供する等化回路であって、該データ信号は該等化回路の入力部において受信され、該等化されたデータ信号は該等化回路の出力部において提供され、

該等化回路は、複数のステージを備え、各ステージは、該少なくとも1つの制御デバイスから送信される制御信号を用いて制御され、該制御信号は、nビット制御信号を含み、

該制御信号は、該ステージが、該ステージに関連付けられている周波数範囲内で、該等化回路によって提供されるゲインの傾きを増大させるかどうかを決定し、該ステージが該ゲインの傾きを増大させるように決定された場合に、該制御信号は、該ステージに関連付けられている該周波数範囲内の $2^n - 1$ 個の選択可能な周波数からの第1の周波数を示し、該データ信号に提供される該ゲインの傾きは、該第1の周波数で増大し、

該制御信号によって示される該第1の周波数は、該少なくとも1つの制御デバイスによってプログラム可能に制御され、それによって、該ステージが該第1の周波数で該ゲインの傾きを増大する場合に、該等化回路は、該伝送媒体によって起こる減衰を補償するために、該データ信号にゲインを提供する、等化回路と、

入力部および出力部を有するバッファであって、該バッファの該入力部は、該等化回路の該出力部に結合されることにより、該バッファに結合された他の回路のインピーダンスを、該等化回路の該出力部インピーダンスから分離し、該バッファの該出力部は、該等化回路の該入力部に結合されることにより、該等化回路にネガティブフィードバック信号を提供し、該等化回路は、該ネガティブフィードバック信号に基づいて、該データ信号に提供されるゲインを調整する、バッファと

該等化回路の入力部に結合されたバイアス回路であって、該バイアス回路は、該データ

10

20

30

40

50

信号に D C バイアシングを提供して該伝送媒体とマッチングするインピーダンスを提供するように構成される、バイアス回路と

を備える、レシーバ回路。

【請求項 2 3】

伝送媒体を介してドライバによって传送されるデータ信号を受信するレシーバ回路であって、該レシーバ回路は、

少なくとも 1 つの制御デバイスと、

該データ信号に対する等化をプログラム可能に提供する等化回路であって、

該等化回路は、複数のステージを備え、各ステージは、該少なくとも 1 つの制御デバイスから送信される制御信号を用いて制御され、

10

該制御信号は、該ステージが、該ステージに関連付けられている周波数範囲内で、該等化回路によって提供されるゲインの傾きを増大させるかどうかを決定し、該制御信号は、n ビット制御信号を含み、該ステージが周波数応答の該ゲインの傾きを増大させるように決定された場合に、該制御信号は、該ステージに関連付けられている該周波数範囲内の  $2^{n-1}$  個の選択可能な周波数からの第 1 の周波数を示し、該データ信号に提供される該ゲインの傾きは、該第 1 の周波数で増大し、

該制御信号によって示される該第 1 の周波数は、該少なくとも 1 つの制御デバイスによってプログラム可能に制御され、それによって、該等化回路は、該伝送媒体によって起こる減衰を補償するために、該データ信号にゲインを提供する、等化回路と、

20

該等化回路の出力部に結合されたスライサであって、該スライサに複数のクロックサイクルを提供するデジタルクロックに結合され、該スライサは、該複数のクロックサイクルのうちの 1 つ内の該データ信号が高い場合にデジタル高信号を割り当て、該複数のクロックサイクルのうちの 1 つ内の該データ信号が低い場合にデジタル低信号を割り当てることによって、該データ信号をデジタル信号へ変換し、該スライサは、該データ信号からクロックおよびデータ情報を抽出するクロックデータリカバリ回路を備える、スライサと

該等化回路の入力部に結合されたバイアス回路であって、該バイアス回路は、

該データ信号に D C バイアシングを提供して該伝送媒体とマッチングするインピーダンスを提供するように構成される、バイアス回路と

を備える、レシーバ回路。

【請求項 2 4】

30

伝送媒体を介して传送されたデータ信号に対する等化を提供する方法であって、該方法は、

該データ信号への D C バイアシングを提供して該伝送媒体とマッチングするインピーダンスを適用することと、

第 1 および第 2 のステージを有する等化器を提供することと、

該第 1 および第 2 のステージの各々に対する制御デバイスが、該ステージによって該データ信号に提供されるゲインの傾きが、該ステージに関連付けられている周波数範囲内で増大するかどうかを決定するために該ステージに制御信号を送信することであって、該制御信号は、n ビット制御信号を含み、該制御信号は、該ステージに関連付けられている該周波数範囲内の  $2^{n-1}$  個の選択可能な周波数から 1 つの周波数を決定するためのものであり、該ゲインの傾きが増大すると決定された場合に、該ゲインの傾きは該 1 つの周波数で増大する、ことと、

40

該第 1 のステージに対して、該ゲインの傾きが増大可能な第 1 の周波数範囲を規定すること、および、該第 2 のステージに対して、該ゲインの傾きが増大可能な第 2 の周波数範囲を規定することであって、該第 1 の周波数範囲が該第 2 の周波数範囲とオーバーラップし、それによって、該オーバーラップする該第 1 の周波数範囲と該第 2 の周波数範囲とは、該第 1 の周波数範囲および該第 2 の周波数範囲のうちのいずれの 1 つよりも広い連続的な周波数範囲をカバーする、ことと、

該制御デバイスが、該 1 つの周波数を制御することであって、それによって、該第 1 のステージと該第 2 のステージとが該伝送媒体によって起こる減衰を補償するために十分な

50

ゲインを提供することと、

等化されたデータ信号を生成するために、該第1のステージと該第2のステージとに該データ信号を適用することと

を包含する、方法。

#### 【請求項25】

前記複数のステージのうちの第1のステージに対し、該ステージは複数の容量性ロードを備え、前記第2の制御信号はデジタル信号であり、前記少なくとも1つの制御デバイスは、複数の選択可能な周波数から前記第2の周波数を選択するように構成されており、該複数の選択可能な周波数の各々は、所定の周波数範囲内にあり、かつ、該複数の容量性ロードのうちの1つに関連付けられている、請求項2に記載のレシーバ回路。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、デジタルデータ通信に関し、より詳細には、そのような通信における回路を自動的に調整するための方法および装置であり、それによって、ドライバ回路からレシーバ回路へ送信されたデジタルデータ信号のロスを補償する。

##### 【背景技術】

##### 【0002】

異なる信号の伝送媒体は、異なる信号の送信特性を有する傾向にある。例えば、ケーブルは、プリント回路基板のバックプレーンとは異なる送信特性を有し得る。さらに、伝送媒体の任意の所定のタイプの各場合が、伝送媒体のそのタイプにとって典型的である範囲内において、多少異なる特性を有し得る。また、通信媒体が、時間を経て変化する、または、他の環境要因の結果として変化することも起こり得る。

20

##### 【0003】

伝送媒体のパフォーマンスに不利益に特に影響する特性は、減衰および位相シフトである。減衰および位相シフトの量が周波数に依存することは、一般的なことである。典型的に、減衰および位相シフトの両方が、周波数の増加と共に増大する。本明細書中において、利便性のために、減衰、位相シフト、および他の形の信号の低下は、時折、総称的に、「ロス」として示される。

##### 【0004】

30

デジタルデータ信号の満足のいく送信を達成するために、特に、高データレートまたは高周波数において、送信されている間における信号にてロスを補償する必要性があり得る。さらに、そのようなロスが、場合、場合によって、または、時と共に変化し得るため、そのような補償が、少なくとも部分的に自動的または適応的であることが、所望され得る。そのような補償に対してしばし、用いられる用語は、等化である。用語、プリエンファシス (pre-emphasis) もまた、時折、補償または等化に対して用いられる。ここにおいて、補償または等化は、ドライバにおいて行われる、すなわち、それは、発生するであろうロスを予想し、信号が送信される前に、その信号を修正することによってこれらのロスを補償することである。用語のプリエンファシスが用いられる場合、等化は、レシーバにおいて行われた補償に対する用語として用いられ得る。等化が、レシーバにおいて最初に行われたものとして記載されても、本発明の一部の局面が、ドライバにおいて行われる等化 (プリエンファシス) に適用もされ得ることは、認識されるべきである。

40

##### 【0005】

一般的に、等化は、特定の周波数に対して固定量のゲインを有するプログラム不可能な回路によって提供される。そのような回路は、識別され得、適切な減衰特性を有する伝送媒体と共に用いられ得る。例えば、2 dBのゲインを100 MHzの信号に提供する等化は、100 MHzを2 dB分を減衰させるバックプレーンと共に用いられ得る。

##### 【0006】

プログラマブルロジックデバイス (「PLD」) 回路のようなプログラム可能回路は、適応的な等化をサポートする際に有用であり得る性能を有し得る。例えば、PLDまたは

50

P L D 回路は、適応的な等化を必要とする信号の送信または受信に関わる構成要素のうちの1つであり得、または、そのような回路は、そのような信号の送受信、または、そのような信号の送信もしくは受信をする回路の特定の局面を制御するために用いられ得る。プログラム可能度 ( p r o g r a m m a b i l i t y ) が、起こり得る異なった送信口ス特性を扱うために、異なったパラメータおよび / または手順を提供するのを援助する故、そのようなプログラム可能回路 ( 例えば、P L D 回路 ) は、本発明の実施において特に有用であり得る。

**【発明の開示】**

**【課題を解決するための手段】**

**【 0 0 0 7 】**

10

プログラム可能レシーバ等化回路は、伝送媒体によって起こる受信されたデータ信号の減衰に対して補償するために提供され得る。等化回路は、同一のステージのカスケードとして実施され得る。

**【 0 0 0 8 】**

各ステージは、別々にプログラム可能であり得る。各ステージは、パラメータと共にステージを提供する構成可能なデバイス ( 例えば、構成 R A M ) に結合され得る。ここにおいて、デバイスは、パラメータによって動作する。等化回路の全体的な周波数応答は、各ステージの周波数応答の集まりであり得る。

**【 0 0 0 9 】**

20

各ステージの D C ゲインは、プログラム可能であり得る。例えば、受信されたデータ信号のピークツーピーク電圧が低すぎる場合、1つ以上のステージは、その受信されたデータ信号のピークツーピーク電圧を高くするためにプログラム可能なように制御され得る。

**【 0 0 1 0 】**

各ステージは、伝達関数にゼロを挿入することによって、受信されたデータ信号に A C ゲインをも提供し得る。ステージがゼロを挿入するかどうかは、プログラム可能なように制御され得る。挿入されたゼロは、ステージの周波数応答の大きさが、そのゼロを挿入した周波数において 2 0 d B / d e c a d e のレートで大きくなるようにし得る。

**【 0 0 1 1 】**

30

特定の周波数 ( 例えば、データ信号のデータレートに対応する周波数 ) において所望のゲインを得るために、各ステージは、プログラム可能なように制御され得、それによって、挿入されたゼロの周波数位置が選択される。一部の実施形態において、挿入されたゼロの周波数位置は、周波数範囲に制限され得る。

**【 0 0 1 2 】**

1つより多いステージが、ゼロを挿入するように構成される場合、周波数範囲は、高域の周波数範囲をカバーするように調整され得る。ここにおいて、その周波数範囲においてステージがゼロを挿入し得る。ゼロの周波数位置が散在する場合、等化回路によって提供されるゲインの傾きは、広域の周波数範囲に渡って増加する ( すなわち、傾きは、各ゼロの周波数位置において、2 0 d B / d e c a d e 大きくなる )。これは、等化回路の周波数応答が、伝送媒体の周波数応答により適合することを可能にする。ここにおいて、伝送媒体の周波数応答の傾きは、周波数が増加するにつれより負になる。

40

**【 0 0 1 3 】**

各ステージの伝達関数はまた、極をも含み得る。ステージの伝達関数における極は、ステージのゲインが 2 0 d B / d e c a d e において減少するようにさせる。各ステージはまた、極の周波数位置をプログラム可能なように制御し得、それによって、高周波ノイズが減少し、クロストーク消去を可能にする。

**【 0 0 1 4 】**

本発明はさらに以下の手段を提供する。

**( 項目 1 )**

伝送媒体を介して受信されるデータ信号へ等化をプログラム可能なように提供する等化回路であって、該等化回路は、

50

1つ以上のステージを備え、各ステージが、

該等化回路の伝達関数にゼロを挿入するように、および

挿入されたゼロの周波数位置を制御するように構成され、

挿入されたゼロの各々の該周波数位置が、該データ信号に十分なゲインを適用するよう

に制御され、それによって、該伝送媒体によって起こる減衰に対して補償する、等化回路

。

(項目2)

上記1つ以上のステージの各々が、さらに、上記等化回路の該伝達関数における極の周

波数位置を制御するように構成される、項目1に記載の等化回路。

(項目3)

上記極の上記周波数位置が、上記データ信号における高周波ノイズをフィルタするよう

に選択される、項目2に記載の等化回路。

(項目4)

上記1つ以上のステージの各々が、さらに、上記データ信号に、所望される量のDCゲ

インを提供するように構成される、項目1に記載の等化回路。

(項目5)

挿入されたゼロの各々の上記周波数位置が制御され、それによって、上記ゲインの傾き

が、上記伝送媒体によって起こる上記減衰の傾きの大きさと同一になり、該減衰の傾きの

符号と反対になる、項目1に記載の等化回路。

(項目6)

上記1つ以上のステージのステージが直列に結合される、項目1に記載の等化回路。

(項目7)

上記1つ以上のステージのステージがカスケード化される、項目1に記載の等化回路。

(項目8)

伝送媒体を介してドライバによって送信されるデータ信号を受信するレシーバ回路であ

って、該レシーバ回路は、

項目1に記載の等化回路を備える、レシーバ回路。

(項目9)

上記データ信号へのDCバイアシングと上記伝送媒体とマッチングするインピーダン

スとを提供するように構成されるバイアス回路をさらに備える、項目8に記載のレシーバ

回路。

(項目10)

上記等化回路の出力部に結合されるバッファをさらに備え、それによって、該バッファ

に結合される他の回路の上記インピーダンスを、該等化回路の出力インピーダンスから分

離する、項目8に記載のレシーバ回路。

(項目11)

上記他の回路のうちの1つが信号検出回路である、項目10に記載のレシーバ回路。

(項目12)

上記他の回路のうちの1つがオフセット消去回路である、項目10に記載のレシーバ回

路。

(項目13)

挿入されたゼロの各々のそれぞれの周波数位置は、ネガティブフィードバックループを

用いて、上記等化回路の上記出力部によって少なくとも部分的に制御される、項目10に

記載のレシーバ回路。

(項目14)

上記データ信号をフルスケールデジタル信号へ変換するために、上記等化回路の上記出

力部に結合されるスライサをさらに備える、項目8に記載のレシーバ回路。

(項目15)

伝送媒体を介して送信されるデータ信号へ等化を提供する方法であって、該方法は、

伝達関数に1つ以上のゼロを挿入することと、

10

20

30

40

50

該伝送媒体によって起こる減衰に対して補償するのに十分なゲインを提供するために、該1つ以上の挿入されたゼロのそれぞれの周波数位置を制御することと、

等化データ信号を生成するために、該伝達関数に該データ信号を適用することとを包含する、方法。

(項目16)

上記データ信号に結合される望まれない高周波ノイズをフィルタするために、1つ以上の極の上記それぞれの周波数位置を制御することをさらに包含する、項目15に記載の方法。

(項目17)

ゼロが挿入され得る周波数範囲を規定することをさらに包含する、項目15に記載の方法。

10

(項目18)

ゼロが挿入され得る該周波数範囲を規定することをさらに包含し、該周波数範囲は、オーバーラップし、広域および連続的な周波数範囲を共にカバーする、項目15に記載の方法。

(項目19)

上記伝達関数に所望される量のDCゲインを提供することをさらに包含する、項目15に記載の方法。

(項目20)

フルスケールデジタル信号を生成するために、上記等化されたデータ信号を処理することをさらに包含する、項目15に記載の方法。

20

(項目21)

上記1つ以上の挿入されたゼロの上記それぞれの周波数位置を制御することが、ユーザの入力に基づく、項目15に記載の方法。

(項目22)

上記挿入されたゼロの上記それぞれの周波数位置が制御され、それによって、上記ゲインの傾きが、上記伝送媒体によって起こる上記減衰の傾きの大きさと同一になり、該減衰の傾きの符号と反対になる、項目15に記載の方法。

(項目23)

上記挿入されたゼロの上記それぞれの周波数位置は、ネガティブフィードバックループを用いて、少なくとも部分的に制御される、項目15に記載の方法。

30

【0015】

(摘要)

伝送媒体を介して送信されるデータ信号は、その伝送媒体によって起こる減衰をこうむる。等化回路は、伝送媒体によって起こる減衰に対して補償するために提供される。等化回路は、直列に配列される複数のステージを含み、それによって、ステージの周波数応答を共に統合することを可能にする。各ステージは、ゼロを挿入するようにプログラム可能であり得、それによって、ステージの周波数応答の大きさは、20dB/decade大きくなる。ゼロの周波数位置はまた、プログラム可能であり得、それによって、各ステージが、特定の周波数に対する特定の量のゲインを与えることを可能にする。各ステージは、高周波ノイズの低減およびクロストーク消去に対する極の位置を決定するようにプログラム可能もあり得る。

40

【0016】

本発明のさらなる特徴、その性質、および様々な利点は、添付の図面、および後述される好ましい実施形態の記載からより明確になるであろう。

【発明を実施するための最良の形態】

【0017】

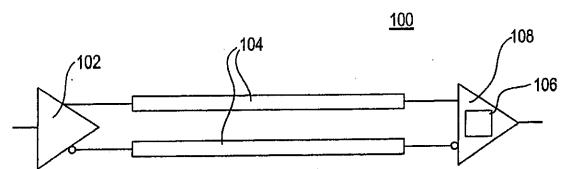

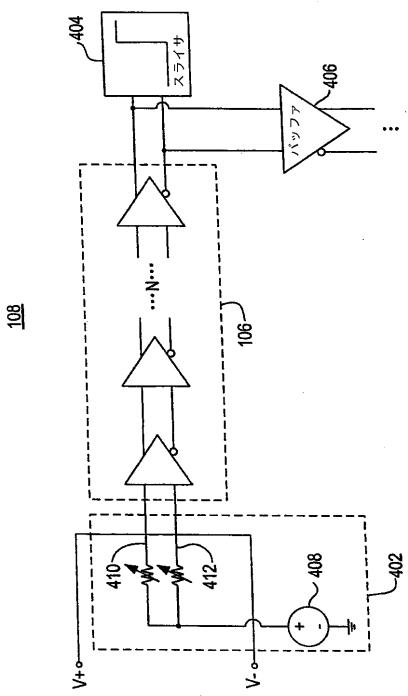

図1は、本発明に従う、データ転送システム100のブロック図である。図1に示されるように、データ転送システム100は、ドライバ102、伝送媒体104、等化回路106、およびレシーバ108を含む。

50

## 【0018】

ドライバ102は、高データレートにおいてデータを送信するように構成されるデバイスの一部であり得る。例えば、ドライバ102は、プログラマブルロジックデバイス、トランシーバ、特定用途向けIC(AVIC)、または任意の他の適切なデバイス、の構成要素であり得る。ドライバ102は、例えば、データ送信における、低電圧差動伝送(LVDS)のような、任意の適切なシリアル通信プロトコルを利用し得る。一部の実施形態において、ドライバ102は、トライステート可能であり得、それによって、複数のドライバ(図示せず)が、複数のレシーバ(図示せず)に接続されることが可能である。

## 【0019】

伝送媒体104は、ドライバ102によって送信されたデータをレシーバ108へ伝え得る。伝送媒体104は、任意の適切な媒体であり得、それらは、例えば、プリント回路基板バックプレーン、送信ライン、ケーブル、空気(すなわち、無線アプリケーションに対して)、または任意の他の適切な媒体である。

10

## 【0020】

データ信号が伝送媒体104を越えて送信された場合、データ信号のパワーは、減衰の結果、低減し得る。伝送媒体104によって起こる減衰の量は、例えば、抵抗率、表皮効果、キャパシタンスロス、および誘導性の干渉のような伝送媒体104の特性に依存し得る。伝送媒体によって起こる減衰の量は、媒体のそれぞれによって異なり得る。例えば、銅ワイヤは、2.5GHz光ファイババックプレーンの減衰特性とは異なる減衰特性を有する。さらに、所定の伝送媒体に対して、減衰の量は、異なったデータレートにおいて送信されるデータによって異なり得る。一般的に、その媒体によって起こる減衰の量は、周波数またはデータレートが増加すると同時に増大する。さらに、減衰の傾きもまた、周波数またはデータレートの増加に伴い、より負に傾く。

20

## 【0021】

レシーバ108は、伝送媒体104を越えてドライバ102によって送信されたデータを受信し、処理するように構成され得る。レシーバ108は、例えば、プログラマブルロジックデバイス、トランシーバ、特定用途向けIC(AVIC)、または任意の他の適切なデバイスのようなデバイスの構成要素であり得る。レシーバ108は、受信した信号をフルスケールデジタル信号に回復するための回路を含み得る。

## 【0022】

30

等化回路106は、データ信号のパワーをブーストし、伝送媒体104によって起こる減衰を補償するために提供され得る。例えば、1Gbpsのデータ信号が、伝送媒体104を越えて伝わる間、10dB分減衰する場合、等化回路106は、1GHz信号を10dB分增幅するように構成され得る。

## 【0023】

一部の実施形態において、等化回路106は、レシーバ108において実施され得る。一部の実施形態において、等化回路106は、レシーバ108とは別の構成要素として実施され得る。

## 【0024】

40

等化回路106は、減衰の様々な量に対する補償をするためにプログラム可能であり得る。一部の実施形態において、等化回路106は、ユーザがパラメータを入力することを可能にし、それによって、等化回路106によって提供される等化の量を特定する。例えば、所定のバックプレーンが1GHz信号を10dB分減衰させると既知の場合、等化回路102は、その所定のバックプレーンを越えて伝わる1GHzのデータ信号へ、10dBのゲインを提供するようにプログラム可能であり得る。一部の実施形態において、等化回路106は、提供する等化の量を自動的に決定し得る。例えば、等化回路106は、入力信号へ適用するゲインの適切なレベルを自動的に決定するために、フィードバックを用い得る。他の実施形態において、等化回路106は、増幅された信号のパワーが所望のレベルに到達するまで、ゲインを自動的に上げる。

## 【0025】

50

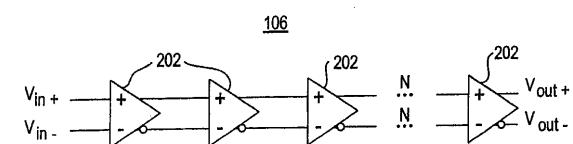

図2は、本発明に従う、等化回路106のブロック図である。図2に示されるように、等化回路106は、「N」個のステージのカスケード202として実施され得る。均等か回路106において実施されるステージの実際の数は、例えば、伝送媒体104によって維持されるデータレート、および、伝送媒体104より予期される減衰量のような要素に依存し得る。例えば、3ステージ等化回路は、6.5 Gbpsバックプレーンによって起こる減衰に対して十分に補償し得る。しかし、4ステージ等化回路は、10 Gbpsバックプレーンによって起こる減衰に対して補償することを必要とし得る。さらに、一部の実施形態において、等化回路106は、単一のステージ202を有して実施され得る。

#### 【0026】

図2に示されるように、等化回路106の各ステージ202は、差動入力を受信し、差動出力を出力する。等化回路106が、差動またはシングルエンドであるかは、ドライバ102およびレシーバ108(図1)によって利用されるシリアル通信のタイプによる。例えば、低電圧差動伝送(LVDS)は、差動伝送を利用するシリアル通信規格である。他の実施例において、RS-232は、シングルエンド信号を利用するシリアル通信規格である。本発明は、差動信号を用いるシステムに関連して論議されるが、本発明の原理が、シングルエンド信号を用いるシステムに適用もされ得ることは、当業者によって理解されるべきである。

#### 【0027】

等化回路106の各ステージ202は、周波数応答に従い、入力信号を形付け得る。各ステージ202の周波数応答は、帯域制限型高域フィルター(band-limited high pass filter)の周波数応答と似得る。例えば、等化回路106のステージの周波数応答の大きさは、DCゲインレベルにおいて最初は一定である。第1の「カットオフ」周波数(ここで、ゼロが位置する)において、周波数応答の大きさは、20dB/decadeの速さにおいて増加し始める。等化サーキット106の各ステージ202が、1つのゼロのみを有するように論議されるが、各ステージ202が1つよりも多いゼロを有するように実施され得ることは、当業者によって留意されるべきである。

#### 【0028】

ステージ202の周波数応答は、1つ以上の極が位置する第2の「カットオフ」周波数において減少し得る。減少のレートは、その周波数に存在する極の数に依存し得、周波数応答の大きさは、存在する各極に対して20dB/decadeの速さにおいて小さくなる。

#### 【0029】

等化回路106にある全ステージ202をカスケードすることは、それらのステージの周波数応答特性が一緒に統合することを引き起こす。例えば、2ステージ等化回路の第1のステージが、1GHzにおいて10dBのゲインを提供し、第2のステージが、1GHzにおいて15dBのゲインを提供する場合、1GHz信号に対する2ステージ等化回路の全体的なゲインは、25dBである。

#### 【0030】

等化回路106の各々のステージ202は、完全にプログラム可能になり得る。ステージ202は、例えば、構成RAMセル、ヒューズベースのデバイス、アンチヒューズ、プログラマブル消去可能読み取り専用メモリ(PROMS)、消去可能PROMS(EPROMS)、電気的消去可能PROMS(EEPROMS)、フラッシュメモリ、および任意の他の適したデバイスのような構成可能(configurable)デバイスによってプログラム的に制御され得る。一部の実施形態においては、構成可能デバイスは、ステージを制御するために制御信号を格納し得る。

#### 【0031】

一部の実施形態においては、ステージ202のDCゲインは、プログラム可能になり得る。各々のステージのための構成デバイスは、提供するDCゲインの量をステージに示すために制御信号を格納し得る。DCゲインは、データ信号のピーク間電圧が増えるように

10

20

30

40

50

する。例えば、3 dBのDCゲインを提供するようにプログラムされているステージが、1 GHz信号および10 GHz信号を受信した場合、両方の信号のピーク間電圧は、3 dB増やされる。

#### 【0032】

一部の実施形態においては、ステージ202のACゲインは、プログラム可能になり得る。ACゲインは、特定の周波数において、そのステージの伝達関数にゼロを挿入することによって提供され得る。ステージ202は、ゼロを挿入するようにプログラム的に制御され得、挿入されたゼロの周波数位置も、プログラム的に制御され得る。

#### 【0033】

上述されたように、ステージ202は、ゼロを挿入するようにプログラム的に制御され得る。等化回路106のあらゆるステージが、ゼロを与える必要はない。例えば、4ステージの等化回路が、低データレートにおいて送信されるデータを等化するために使用された場合、等化回路106が減衰を補償するために、2つのゼロだけが必要になり得る。この実施例においては、4ステージのうちの2つは、ゼロを与えるためにプログラム的に制御され得る。他の2ステージは、ゼロを与えないようにプログラム的に制御され得る。

#### 【0034】

ステージ202がゼロを挿入するようにプログラム的に制御されている場合、周波数応答の大きさは、ゼロの周波数位置から20dB/decade増える。例えば、ゼロが1GHzにおいて挿入された場合、周波数応答の大きさは、1GHzから開始し、20dB/decadeのレートにおいて増える。1GHzにおいて、2つのゼロが挿入された場合、周波数応答の大きさは、1GHzから開始し、40dB/decadeのレートにおいて増える。挿入されるあらゆる追加のゼロは、ゲインが追加の20dB/decade増える、レートを上げる。複数のゼロを挿入することは、等化回路106が、伝送媒体104(図1)に起因する多大の量の減衰を補償することを可能にする。

#### 【0035】

ステージ202によって挿入されるゼロの周波数位置も、プログラム的に制御され得る。ゼロを与える各々のステージ202は、ゼロが他のステージから独立して配置される場所を制御し得る。例えば、ゼロが、ゲインが20dB/decade増えるようにするために、20dBゲインが10GHzにおいて所望された場合、ゼロは、1GHzにおいて挿入され得る。20dBより少ないゲインが所望された場合、ゼロの周波数位置は、10GHzにおけるゲインを減らすために増やされ得る。他の実施例においては、ユーザがバックプレーンの周波数応答を測定し、2.5GHzにおいて極を観測した場合、等化回路106は、極による減衰を消去するために、2.5GHzにおいてゼロを挿入するようにプログラムされ得る。

#### 【0036】

一部の実施形態においては、ステージ202は、所定の周波数範囲内にてゼロを挿入することに制限され得る。一部の実施形態において、周波数範囲はプログラム的に制御され得、すなわち、各々のステージに対する周波数上限および下限は、構成可能デバイスによって設定され得る。例えば、ステージ202は、1と1.5GHzとの間にゼロを挿入することに制限され得る(すなわち、1と1.5GHzとの間にゼロを挿入することは、例えば、2GHzのような所望された周波数位置におけるゲインの量を十分に制御する)。ステージ202が、任意の周波数、特に、データ信号を送信するために通常使用される周波数より大きい周波数において、ゼロを挿入することを可能にするのは実用的ではない。

#### 【0037】

構成可能デバイスは、そのステージの所定の周波数範囲内にて $2^n$ の均等に間隔された(evenly-spaced)周波数の1つを選択するために、nビット制御信号をステージに適用し得る。例えば、3ビット制御信号が1と1.5GHzとの間の周波数位置を選択するために使用された場合、制御信号は、1と1.5GHzとの間の8の均等に間隔された周波数から選択し得る。他の実施例においては、4ビット制御信号は、ステージが16の周波数から選択することを可能にする。より多くの制御ビットを提供すること

10

20

30

40

50

は、周波数を選択するのにより高い精度を可能にし得、従って、ステージ 202 のゲインのより大きな制御を可能にし得る。

【0038】

一部の実施形態においては、所定の制御信号値は、周波数値を選択すること以外の機能のためにリザーブされ得る。例えば、一制御信号値は、ゼロが挿入されるべきではないときを示すためにリザーブされ得る。この実施例においては、残りの  $2^n - 1$  値は、ゼロを挿入することに対して周波数を選択するためにリザーブされ得る。

【0039】

一部の実施形態においては、等化回路 106 が複数のステージ 202 を含む場合、周波数範囲の間にいくつかのオーバラップがあるように、ステージ 202 の周波数範囲をスタガーラップすることは有益である。これは、ゼロが、広く、連続的な周波数範囲に渡って挿入されることを可能にする。例えば、第 1 のステージは、2 と 3.25 GHz との間にゼロを挿入するように構成され得、第 2 のステージは、2.75 と 4 GHz との間にゼロを挿入するように構成され得る。

10

【0040】

更に、ゼロの周波数位置を分散させることは、周波数が増えることによって、周波数応答のスロープを増やし、それによって、等化回路の周波数応答が、周波数が増えることによってスロープがよりネガティブになり、伝送媒体の周波数応答によりきっちりと反対になる (closely counter) ことを可能にする。

【0041】

20

異なる周波数位置において複数のゼロを挿入することも、等化回路 106 の周波数応答のスロープのより大きな制御を提供する。例えば、等化回路 106 が、その両方が 1 GHz における、2 つのゼロを有する場合、等化回路 106 は、10 GHz における 40 dB のゲインを与える。10 GHz において、35 dB のゲインだけが所望された場合、両方のゼロの周波数を増やす代わりに、1 つのゼロの周波数だけが増やされ得、従って、等化回路 106 の帯域幅を保存する。

【0042】

等化回路 106 は、容量性ローディングも含み得る。一部の実施形態においては、容量性ローディングは、等化回路 106 の各々のステージに存在し得る。各々のステージ 202 の容量性ローディングの量は、プログラム的に制御可能になり得る。一部の実施形態においては、容量性ローディングは、等化回路 106 の出力において存在し得る。等化回路 106 における容量性ローディングの量は、プログラム的に制御可能になり得る。容量性ローディングの量は、周波数応答がどこでロールオフを開始するかを決定する、等化回路 106 の伝達関数において、1 つ以上の極の周波数位置を決定する。

30

【0043】

極の周波数位置は、クロストークの減少および / または消去を支援し得る。一部の実施形態においては、極の周波数位置は、データ信号の周波数に設定され得る (例、1 Gbps データ信号に対して 1 GHz)。これは、データ信号の周波数以上の周波数を有する信号が、抑制されるようにする (または少なくとも更にブーストされないように)。一部の実施形態においては、極の周波数位置は、高周波信号が増えることから防ぐために、十分に低く設定され得る。クロストーク減少 / 消去は、高周波ノイズが伝送媒体 104 (図 1) に結合し得た、低周波アプリケーションに使用され得る。

40

【0044】

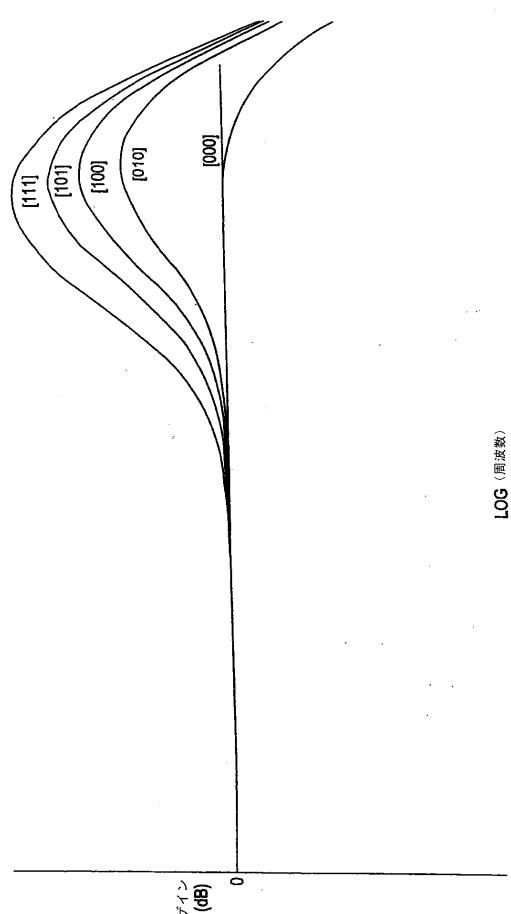

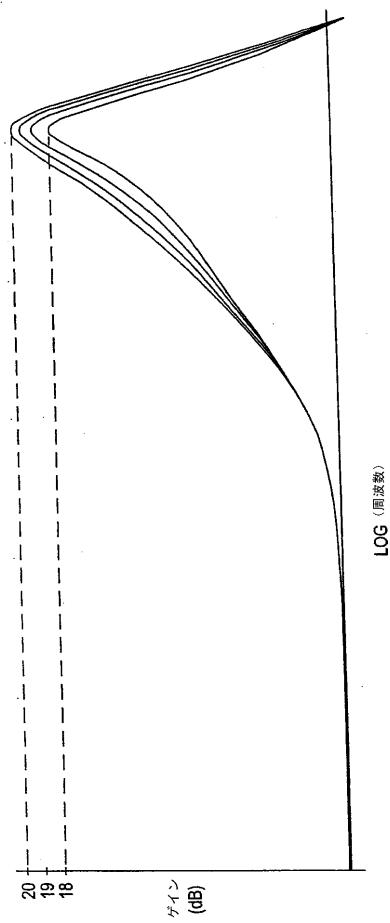

図 3a は、本発明に従って、等化回路 106 におけるステージ 202 の 1 つによって提供されるプログラム可能ゲイン機能性を示すボード (Board) 図である。一部の実施形態においては、ステージ 202 によって提供されるゲインの量は、n ビット制御信号によって制御される。図 3a に示されるように、3 ビット制御信号は、等化回路の周波数応答を変化させるために使用される。

【0045】

一部の実施形態においては、制御信号は、ステージ 202 がゼロを挿入するのかどうか

50

を決定し、もし挿入するならば、ゼロが挿入される周波数も決定する。例えば、[ 0 0 0 ] 制御信号がステージ 2 0 2 に適用された場合、ステージ 2 0 2 は、その伝達関数にゼロを全く挿入しない。この実施例においては、図 3 a に示されるように、ステージ 2 0 2 は、[ 0 0 0 ] 制御信号を用いてゲインを全く生成しない。

**【 0 0 4 6 】**

[ 0 0 0 ] 以外の制御信号は、ゼロが挿入される周波数を決定し得る。一部の実施形態においては、ステージ 2 0 2 は、周波数の所定の範囲内だけにおいて、ゼロを挿入するように構成され得る。例えば、図 3 a において、ゼロの周波数位置は、5 M H z と 5 0 M H z の間である。制御信号は、周波数範囲内において、どこにゼロが挿入されるかを決定し得る。一部の実施形態においては、制御信号のバイアス値が低い場合、ゼロは、周波数範囲の下端の方へ挿入され得る。一部の実施形態においては、制御信号のバイアス値が低い場合、ゼロは、周波数範囲の上端の方へ挿入され得る。この実施例においては、制御信号は、ゼロを挿入する均等に間隔された周波数の 7 つのうちの 1 つを選択し得る。10

**【 0 0 4 7 】**

一般に、ゼロが低周波において挿入された場合、ステージ 2 0 2 は、より多くのゲインを生成する。図 3 a に示されるように、[ 1 1 1 ] 入力は、[ 1 0 1 ] 入力より多くゲインを生成し、[ 1 1 1 ] カーブのゼロ挿入ポイントは、[ 1 0 1 ] カーブのゼロ挿入ポイントより低い周波数にある。

**【 0 0 4 8 】**

どの制御信号をステージ 2 0 2 に適用するかを決定するにおいて、ユーザは、5 G H z における伝送媒体 1 0 4 ( 図 1 ) による減衰の量を考慮する。例えば、ユーザが、伝送媒体 1 0 4 の周波数応答を測定し、3 G H z データ信号が 6 d B 減衰することが伝送媒体 1 0 4 に起因することを知った場合、ユーザは、データ信号に 6 d B のゲインを提供するために、[ 1 0 1 ] の制御信号を選択し得る。20

**【 0 0 4 9 】**

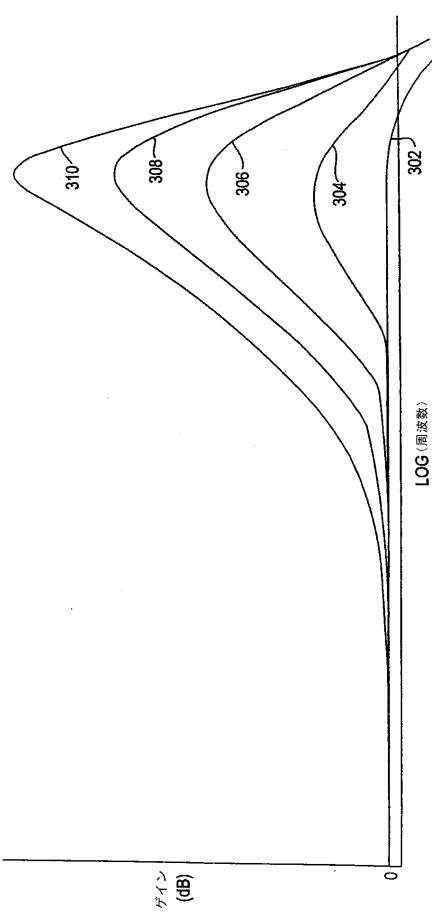

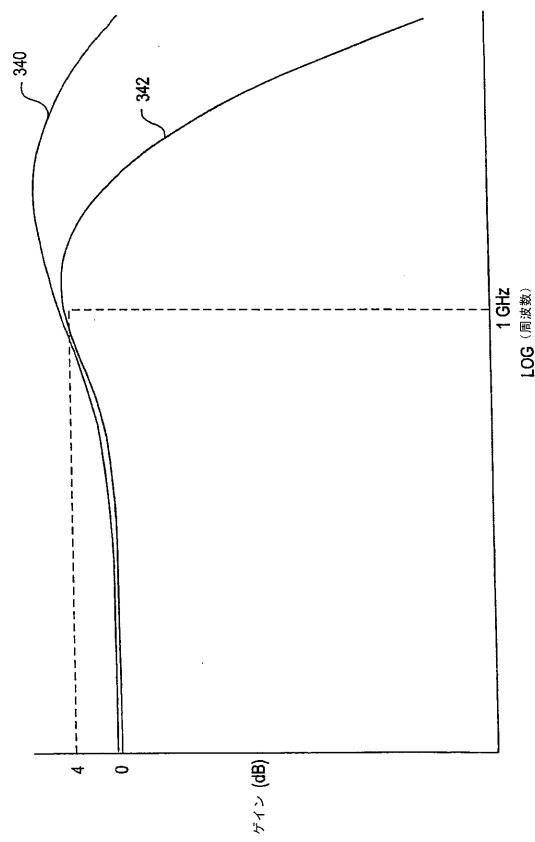

図 3 b および図 3 c は、本発明に従って、等化回路 1 0 6 のプログラム可能スロープ機能性を示すボード図である。

**【 0 0 5 0 】**

図 3 b は、各々のカーブが異なるスロープを有する、カーブ 3 0 2 、 3 0 4 、 3 0 6 、 3 0 8 および 3 1 0 と同様な周波数応答を生成するようにプログラム的に制御され得る、等化回路 1 0 6 を示す。ステージ 2 0 2 は、ゼロを与えるまたはゼロを与えないのどちらかをするように、プログラム的に制御され得る。ゼロを与えるあるゆるステージ 2 0 2 に対して、等化回路 1 0 6 のゲインは、ゼロが追加される周波数から追加の 2 0 d B / d e c a d e 増える。例えば、4 ステージ等化回路において、0 、 2 0 、 4 0 、 6 0 および 8 0 d B / d e c a d e のスロープは、ゼロを与えるステージの数によって、達成され得る。

**【 0 0 5 1 】**

カーブ 3 0 2 のような周波数応答カーブは、等化回路における全てのステージがゼロを与えるようにプログラムされていない場合、達成され得る。カーブ 3 0 4 のような周波数応答は、等化回路におけるステージの 1 つが、1 G H z においてゼロを与えるようにプログラムされている場合、達成され得る。同様に、カーブ 3 0 6 、 3 0 8 または 3 1 0 のような周波数応答カーブは、等化回路における 2 つ、 3 つまたは 4 つのステージのそれぞれが、1 G H z においてゼロを与えるようにプログラムされている場合、達成され得る。40

**【 0 0 5 2 】**

図 3 b に示されるように、より大きなスロープを有する周波数応答カーブは、より大きなゲインを達成できる。等化回路 1 0 6 の周波数応答のスロープをプログラム的に制御することは、等化回路 1 0 6 の A C ゲインの追加の制御を提供する。特に、等化回路 1 0 6 が大きなスロープ ( すなわち、複数のゼロ ) を有するようにプログラムすることは、等化回路 1 0 6 が、通常複数の極を有し、多大な量の減衰を受ける、伝送媒体 1 0 4 ( 図 1 ) を通じてのデータの高速送信による減衰を補償することを可能にする。50

## 【0053】

図3cは、複数のステージを有する等化回路106のゲインをプログラム的に制御することに対するアプローチを示す。図3bに示されるように、等化回路106におけるステージ202は、ゼロを挿入するようにプログラム的に制御され得る。周波数応答のスロープにおける複数のゼロの効果を示すために、図3bの中の全てのゼロの周波数位置は、同等の周波数に設定されている。図3cに示されるように、ゼロの周波数位置を変更することは、周波数応答カーブの形においてより大きな制御を提供する。

## 【0054】

特に、図3cに示されるように、周波数応答カーブ320、322、324、および326は、全て非常に類似している。しかしながら、周波数応答カーブの大きさには明らかな差異がある。例えば、カーブ326の最大ゲインは、20dBを越えるが、カーブ320の最大ゲインは、18dBを越える。他の実施例においては、カーブ320は、2GHzをちょうど越える周波数応答において顕著(noticeable)なペンドを有する。カーブ間のこれらの差異は、異なる周波数位置において挿入されるゼロによるものである。

10

## 【0055】

等化回路が1つよりも多いゼロを与える場合、任意の所定の周波数におけるゲインは、個別のゼロの周波数位置を変更することによって、微同調され得る。ゼロの周波数位置が低くなった場合、全体的なゲインが増える。その一方、そのゼロの周波数位置が増えた場合、全体的なゲインは減る。例えば、図3に示されるように、カーブ320およびカーブ326の両方は、第1の周波数における第1のゼロを有する。カーブ320および326は、第2のゼロも有する。カーブ320の第2のゼロが、カーブ326の第2のゼロより高い周波数位置にあるため、カーブ320はカーブ326より低いゲインを有する。

20

## 【0056】

ゼロが異なる周波数位置に挿入されることを可能にすることは、1つの周波数における周波数応答のゲインの制御および周波数応答全体としての形のより高い精度を可能にする。

## 【0057】

異なる周波数位置にゼロ挿入することは、等化回路106が、異なる周波数位置に渡って分散される複数の極を有する、伝送媒体104(図1)の減衰をよりきっちりと反対にすることを可能にする。理論的に、等化回路106(図2)は、ゼロが伝送媒体104にある極の周波数位置において挿入された場合、伝送媒体104による全ての周波数に渡る減衰を正確に補償し得る。

30

## 【0058】

図3dは、本発明に従って、等化回路によって提供されるクロストークフィルタリング機能性を示す、例示的なボード図である。クロストークは、1つの信号経路からの信号が近くの信号経路に電磁的に結合された場合、生じる。

## 【0059】

等化回路106(図2)の2つの例示的な周波数応答カーブ340および342は、図3dに示される。カーブ340は、クロストークフィルタリングなしの等化回路に対応し、カーブ342は、クロストークフィルタリングを用いた等化回路に対応する。両方のカーブは、1GHzのデータ信号に対して同等の量のゲインを提供する。例えば、1GHzのデータ信号が、4dBの減衰を発生させる伝送媒体を通じて送信された場合、等化回路106は、データ信号をその本来の強さに復帰させるために、周波数応答を有するように構成され得る。

40

## 【0060】

しかしながら、等化回路106がカーブ340に対応する周波数応答を有するように構成されている場合、近くの信号経路から結合される高周波干渉は、増幅される。これは、近くの信号経路を移動している信号が、ほぼ確実に高周波において送信され、そうでない場合においても、帯域内にない低周波信号は、増幅されないため、低周波アプリケーショ

50

ンにおいては、特に有害である。その一方、等化回路 106 が、カーブ 342 に対応する周波数応答を有するように構成されている場合、高周波信号は、かなり減衰される。このアプローチは、クロストークフィルタリングと言及され、等化回路のカットオフ周波数がプログラム的に選択されることを可能にする。一部の実施形態においては、カットオフ周波数は、データ信号が送信される周波数において選択される。これは、等化回路の周波数応答が、データ信号の送信周波数において、頂点に達することを可能にする。

#### 【0061】

クロストークフィルタリングは、ステージ 202 (図 2) の容量性ロードまたは等化回路 106 の出力におけるステージ 202 からの別々の容量性ロードとして実施され得る。容量性ローディングの量はプログラム的に制御され得、カットオフ周波数の位置を決定する。一般に、高い容量性ロードが、低いカットオフ周波数という結果になる。容量性ローディングは、周波数の所定の範囲においてロールオフを生成することに制限され得る。

#### 【0062】

一部の実施形態においては、 $m$  ビット制御信号は、等化回路 106 (図 2) が所定の周波数範囲内における  $2^m$  の周波数から選択することを可能にするために提供され得る。一部の実施形態においては、 $m$  ビット制御信号は、等化回路 106 の周波数応答にロールオフを生成することに対して、 $2^m$  の容量性ロード値から選択するために提供され得る。

#### 【0063】

図 4 は、本発明に従って、等化回路 106 を有するレシーバ 108 のブロック図である。図 4 に示されるように、等化回路 106 は、伝送媒体 (例、伝送媒体 104 (図 1)) を通じて送信されるデータ信号を受信する、レシーバ 108 に実施される。レシーバ 108 は、等化回路 106 の入力に結合されるバイアス回路 402、等化回路 106 の出力に結合されるスライサ 404、および等化回路 106 の出力にも結合されるバッファ 406 を含み得る。

#### 【0064】

バイアス回路 402 は、バイアス等化回路 106 に DC 電圧を供給する、電圧源 408 を含み得る。電圧源 408 は、AC 接地 (ground) を送信されたデータ信号に提供し得る。バイアス回路 402 は、抵抗 410 および 412 の一致する組も含み得る。一致する抵抗 410 および 412 は、等化回路 106 のインピーダンスを、データがその媒体を通じて送信される伝送媒体 104 (図 1) と一致させるために選択され得る。例えば、伝送媒体 104 が、50 Ω 送信ラインである場合、一致するレジスタ 410 および 412 の抵抗値は、50 Ω に設定されるべきである。設定されない場合、伝送媒体 104 を通じて送信されるデータ信号は、反射およびパワーロスを受けやすい。一部の実施形態においては、一致するレジスタ 410 および 412 の抵抗値は、インピーダンス一致を提供するために、プログラム的に制御され得る。

#### 【0065】

等化回路 106 がデータ信号を処理した (すなわち、減衰を補償する) 後、スライサ 404 は、フルスケールのデジタル信号を生成するために、等化回路 106 の出力を処理し得る。スライサ 404 がクロックサイクル内にて、等化回路 106 の出力がロジックハイ (logic high) またはロジックロー (logic low) のどちらを示すのかを決定するように、スライサ 404 は、デジタルクロックに接続され得る。したがって、スライサ 404 は、等化回路 106 の出力からのアナログ信号を、レシーバ 108 においてデジタル回路によって使用され得るデジタル信号に、本質的に変換する。例えば、レシーバ 108 がプログラマブルロジックデバイスの一部である場合、スライサ 404 の出力は、更なる処理のために、プログラマブルロジックデバイスにルートされ得る。

#### 【0066】

一部の実施形態においては、スライサ 404 は、送信されたデータ信号からクロックおよびデータ情報を回復するために、クロックデータ回復 (CDR) 回路を含み得る。CDR 回路は、正しい量の位相を用いてクロック情報を回復するために、位相ロックループ (PLL) を含み得る。

10

20

30

40

50

P L L ) を使用し得る。クロック情報は、次いで、データ信号からデータをサンプリングするために使用され得る。

#### 【 0 0 6 7 】

レシーバ 108 は、バッファ 406 をも含み得る。バッファ 406 は、等化回路 106 の出力を用いて他の回路をドライブするために使用され得る。バッファ 406 の入力抵抗は無限であり、従って、等化回路 106 の出力抵抗に影響しない。バッファ 406 の出力は、等化回路 106 の出力抵抗からのその抵抗を絶縁させるために、無限ではない入力抵抗を用いて他の回路に結合され得る。バッファ 406 なしには、等化回路 106 の帯域幅は、他の回路の入力における任意の容量性ローディングによって影響され得る。そのような容量性ローディングは、等化回路 106 の周波数応答における極の位置を影響し得る。

10

#### 【 0 0 6 8 】

一部の実施形態においては、バッファ 406 は、信号検出回路（図示せず）に結合され得る。信号検出回路は、レシーバ 108 によってデータ信号が受信されているかどうかを検出するために使用され得る。信号検出回路が、入力が受信されていることを検出すると、信号検出回路は、出力信号を生成し得る。出力信号は、スライサ 404 が受信されたデータ信号を処理できるようにし得る。

#### 【 0 0 6 9 】

一部の実施形態においては、バッファ 406 は、ループバックバッファ（図示せず）に結合され得る。ループバックバッファは、処理のためにレシーバ 108 の出力を、他の回路に再度導き得る。例えば、ループバックバッファは、オシロスコープによる観測のために出力をピンにドライブし得る、送信ドライバに、レシーバ 108 の出力を再度導き得る。他の実施例においては、ループバックバッファは、受信されたデータの有効性（例、ピットエラーレート）を検出するために、レシーバ 108 の出力を回路に再度導き得る。

20

#### 【 0 0 7 0 】

一部の実施形態においては、バッファ 406 の出力は、ネガティブフィードバックを等化回路 106（図示せず）に提供するために、等化回路 106 の入力に結合され得、それによって、等化回路 106 が、出力信号にゲインを適用する（例、フィードバック率に基づいて）ことを可能にする。

#### 【 0 0 7 1 】

30

一部の実施形態においては、バッファ 406 の出力は、オフセット消去回路（図示せず）に結合され得る。オフセットは、例えば、ステージ 202 の 1 つの入力がアンバランスな場合、生じる。例えば、ステージの 1 つが、差動入力がゼロのときにおいても出力を生成する場合、オフセットは、存在し得る。オフセットは、ステージからステージへと蓄積され得、従って、全てのステージの出力においてオフセットを消去することが好ましい。これは、等化回路 106 の出力を訂正し、訂正された信号を等化回路 106 の入力にフィードバックすることによって、達成され得る。

#### 【 0 0 7 2 】

上述のものは、本発明の原理を単に例示しているだけであり、様々な修正は、本発明の範囲および精神から逸脱せずに、当業者によって行われ得る。

40

#### 【 図面の簡単な説明 】

#### 【 0 0 7 3 】

【 図 1 】本発明に従う例示的なデータ転送システムのブロック図である。

【 図 2 】本発明に従う例示的な等化回路のブロック図である。

【 図 3 a 】本発明に従う、1 つのステージの等化回路によって提供されたプログラム可能ゲイン機能性を示すボード図である。

【 図 3 b 】本発明に従う、マルチステージの等化回路のプログラム可能傾き機能性を示すボード図である。

【 図 3 c 】本発明に従う、マルチステージの等化回路のプログラム可能傾き機能性を示すボード図である。

50

【図3d】本発明に従う、等化回路によって提供されるクロストークフィルタリング機能性を示すボード図である。

【図4】本発明に従う、例示的な等化回路を有する例示的なレシーバのブロック図である。

【符号の説明】

【0074】

102 ドライバ

104 伝送媒体

106 等化回路

108 レシーバ回路

202 ステージ

404 スライサ

406 パッファ

10

【図1】

【図3a】

【図2】

LOG (周波数)

【図3 b】

【図3 c】

【図3 d】

【図4】

---

フロントページの続き

- (72)発明者 シマルディープ マンガト

アメリカ合衆国 カリフォルニア 94086, サニーベール, コルテス ドライブ 121

2 ナンバー3

- (72)発明者 セルゲイ シュマライエフ

アメリカ合衆国 カリフォルニア 94579, サン リアンドロ, ロッキー ポイント コ

ート 2328

- (72)発明者 ウィルソン ウォン

アメリカ合衆国 カリフォルニア 94134, サンフランシスコ, フェルトン ストリート

301

- (72)発明者 トウンゴック トラン

アメリカ合衆国 カリフォルニア 95133, サン ホセ, クリーク ポイント ドライブ

2960

審査官 廣川 浩

- (56)参考文献 特開平09-331363 (JP, A)

国際公開第2005/029797 (WO, A1)

特開平01-170123 (JP, A)

特開昭61-062241 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04B 3/04 - 3/18

H04L 25/03