(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6549451号

(P6549451)

(45) 発行日 令和1年7月24日(2019.7.24)

(24) 登録日 令和1年7月5日(2019.7.5)

(51) Int.Cl.

H02M 1/08 (2006.01)

F 1

H02M 1/08 ZHVA

請求項の数 6 (全 14 頁)

(21) 出願番号 特願2015-172625 (P2015-172625)

(22) 出願日 平成27年9月2日 (2015.9.2)

(65) 公開番号 特開2017-50984 (P2017-50984A)

(43) 公開日 平成29年3月9日 (2017.3.9)

審査請求日 平成30年5月24日 (2018.5.24)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

東京都江東区豊洲三丁目2番24号

(74) 代理人 110000350

ポレール特許業務法人

(72) 発明者 鶴丸 誠

東京都江東区豊洲三丁目2番24号 ルネ

サスエレクトロニクス株式会社内

審査官 麻生 哲郎

最終頁に続く

(54) 【発明の名称】半導体集積回路装置および電子装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電力用半導体装置を駆動する駆動回路と、

前記駆動回路の駆動能力を制御する駆動能力制御回路と、

前記電力用半導体装置のセンス電流に基づいて異常電流検出用電圧を出力する第1の電流検出回路と、

前記電力用半導体装置の前記センス電流に基づいて通常電流検出用電圧を出力する第2の電流検出回路と、

前記電力用半導体装置の異常電流検出用抵抗を外部に接続するための第1の端子と、

前記電力用半導体装置の通常電流検出用抵抗を外部に接続するための第2の端子と、

を備え、

前記駆動回路は、前記電力用半導体装置の前記センス電流から検出した異常電流に基づいて前記電力用半導体装置の駆動を停止するよう構成され、

前記駆動能力制御回路は、前記電力用半導体装置の前記センス電流から検出した通常電流に基づいて前記駆動回路の駆動能力を制御するよう構成され、

前記第1の電流検出回路および前記第2の電流検出回路はカレントミラー回路で構成される半導体集積回路装置。

## 【請求項 2】

電力用半導体装置を駆動する駆動回路と、

前記駆動回路の駆動能力を制御する駆動能力制御回路と、

10

20

前記電力用半導体装置のセンス電流に基づいて異常電流検出用電圧を出力する第1の電流検出回路と、

前記電力用半導体装置の前記センス電流に基づいて通常電流検出用電圧を出力する第2の電流検出回路と、

を備え、

前記駆動回路は、前記電力用半導体装置の前記センス電流から検出した異常電流に基づいて前記電力用半導体装置の駆動を停止するよう構成され、

前記駆動能力制御回路は、前記電力用半導体装置の前記センス電流から検出した通常電流に基づいて前記駆動回路の駆動能力を制御するよう構成され、

前記駆動能力制御回路は、

10

前記通常電流検出用電圧に基づいた電圧を生成する回路と、

前記電圧に基づいて前記駆動回路の電圧または電流を制御する制御回路と、

を備え、

前記回路は、

オペアンプとループ抵抗を有する增幅回路と、

基準電圧を生成する回路と、

を備え、

前記ループ抵抗の抵抗値または前記基準電圧は制御信号に基づいて変更することが可能な半導体集積回路装置。

**【請求項3】**

20

請求項2の半導体集積回路装置において、さらに、

前記通常電流検出用電圧を変換するA/D変換回路と、

前記A/D変換回路の出力を出力する端子と、

前記A/D変換回路の出力に基づいて生成された前記制御信号を入力する端子と、

を備える半導体集積回路装置。

**【請求項4】**

電力用半導体装置と、

第1の半導体集積回路装置と、

第2の半導体集積回路装置と、

を備え、

30

前記電力用半導体装置は、

負荷を駆動するための電流を供給する第1の端子と、

駆動電流をモニタするための電流を供給する第2の端子と、

を備え、

前記第1の半導体集積回路装置は、

前記電力用半導体装置を駆動する駆動回路と、

前記駆動回路の駆動能力を制御する駆動能力制御回路と、

前記第2の端子からの電流に基づいて異常電流検出用電圧を出力する第1の電流検出回路と、

前記第2の端子からの電流に基づいて通常電流検出用電圧を出力する第2の電流検出回路と、

前記電力用半導体装置の異常電流検出用抵抗を外部に接続するための第4の端子と、

前記電力用半導体装置の通常電流検出用抵抗を外部に接続するための第5の端子と、

を備え、

前記駆動回路は、前記電力用半導体装置のセンス電流から検出した異常電流に基づいて前記電力用半導体装置の駆動を停止するよう構成され、

前記駆動能力制御回路は、前記電力用半導体装置のセンス電流から検出した通常電流に基づいて前記駆動回路の駆動能力を制御するよう構成され、

前記第1の電流検出回路および前記第2の電流検出回路は、カレントミラー回路で構成され、

40

50

前記カレントミラー回路は前記第4の端子および第5の端子に接続される電子装置。

【請求項5】

電力用半導体装置と、

第1の半導体集積回路装置と、

第2の半導体集積回路装置と、

を備え、

前記電力用半導体装置は、

負荷を駆動するための電流を供給する第1の端子と、

駆動電流をモニタするための電流を供給する第2の端子と、

を備え、

前記第1の半導体集積回路装置は、

前記電力用半導体装置を駆動する駆動回路と、

前記駆動回路の駆動能力を制御する駆動能力制御回路と、

前記第2の端子からの電流に基づいて異常電流検出用電圧を出力する第1の電流検出回路と、

前記第2の端子からの電流に基づいて通常電流検出用電圧を出力する第2の電流検出回路と、

を備え、

前記駆動回路は、前記電力用半導体装置のセンス電流から検出した異常電流に基づいて前記電力用半導体装置の駆動を停止する構成され、

前記駆動能力制御回路は、前記電力用半導体装置のセンス電流から検出した通常電流に基づいて前記駆動回路の駆動能力を制御する構成され、

前記駆動能力制御回路は、

前記通常電流検出用電圧に基づいた電圧を生成する回路と、

前記電圧に基づいて前記駆動回路の電圧または電流を制御する制御回路と、

を備え、

前記回路は、

オペアンプとループ抵抗を有する增幅回路と、

基準電圧を生成する回路と、

を備え、

前記ループ抵抗の抵抗値または前記基準電圧は制御信号に基づいて変更することが可能である電子装置。

【請求項6】

請求項5の電子装置において、

前記第1の半導体集積回路装置は、さらに前記通常電流検出用電圧を変換するA/D変換回路を備え、

前記第2の半導体集積回路装置は、前記前記A/D変換回路の出力に基づいて前記制御信号を生成するCPUを備える電子装置。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は半導体集積回路装置に関し、例えば絶縁ゲートバイポーラトランジスタ(IGBT)等の電力用半導体装置を駆動する半導体集積回路装置に適用可能である。

【背景技術】

【0002】

電動機(モータ)は、例えば内燃機関(ガソリンエンジン)と組み合わせたハイブリッド自動車(HEV)または電気自動車(EV)等の動力源として用いられる。電動機を駆動する際、所定のトルク、電源周波数を得るのに直流-交流変換を行う電力変換装置(インバータ)が用いられる。インバータにおいて、モータの駆動電流を電流検出器によってモニタしながら駆動信号を制御している(例えば、特開2011-97812号公報)。

10

20

30

40

50

## 【先行技術文献】

## 【特許文献】

## 【0003】

【特許文献1】特開2011-97812号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

各位相のモータ駆動電流を変流器等の電流検出器および制御回路のA/D変換器などを使って通常電流を検出してモータ駆動制御に利用する場合、電流検出は変流器の出力電圧を制御回路でA/D変換し、その結果に基づくドライブ制御調整というループ時間がかかるため高速処理が難しい。

その他の課題と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

## 【課題を解決するための手段】

## 【0005】

本開示のうち、代表的なものの概要を簡単に説明すれば、下記のとおりである。

すなわち、半導体集積回路装置は電力用半導体装置のセンス電流から検出した通常電流に基づいて駆動回路の駆動能力を制御する駆動能力制御回路を備える。

## 【発明の効果】

## 【0006】

上記半導体集積回路装置によれば、高速処理が可能になる。

## 【図面の簡単な説明】

## 【0007】

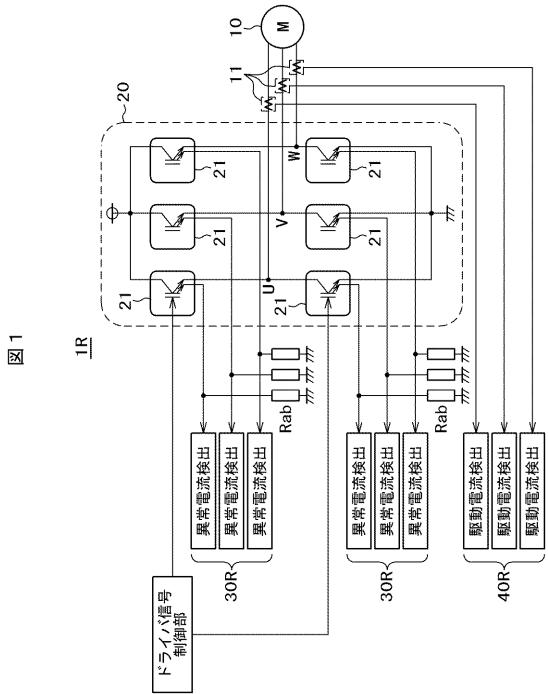

【図1】比較例に係る電動機システムを説明するためのブロック図。

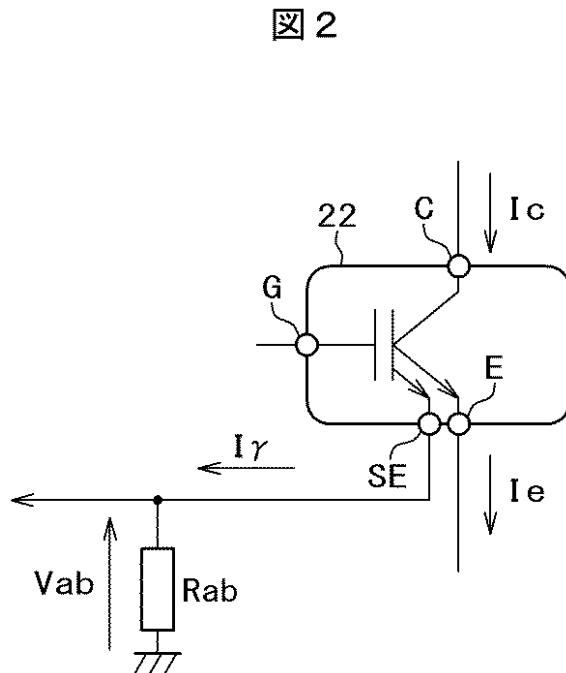

【図2】IGBTのセンス電流を説明するための図。

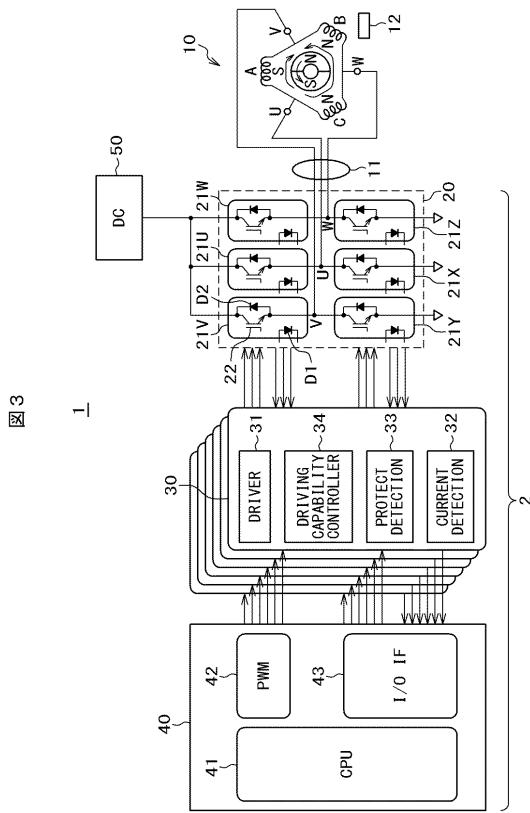

【図3】実施例1に係る電動機システムを説明するためのブロック図。

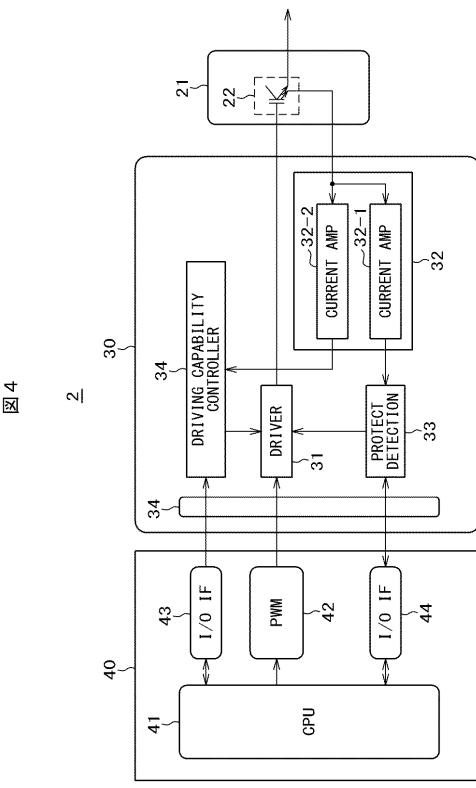

【図4】図3の電動機システムの一部である電子装置を示すブロック図。

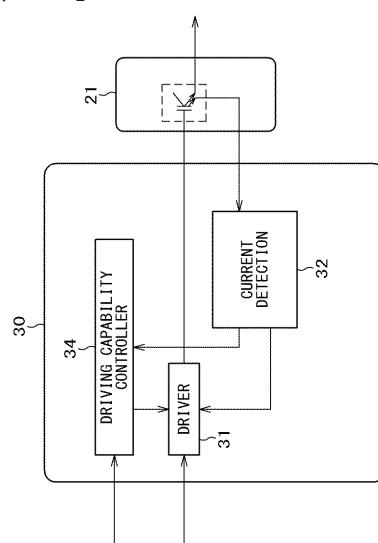

【図5】図4のドライバICを説明するためのブロック図。

【図6】図5のカレントミラー回路を説明するための回路図。

【図7】図5のドライブ能力制御部の構成を説明するためのブロック図。

【図8】図5のドライブ能力制御部の制御を説明するためのタイミング図。

【図9】実施例2に係るIGBTおよびドライバICを説明するためのブロック図。

【図10】図9のIGBTを説明するための図。

【図11】実施例3に係るドライバICおよび制御回路を説明するためのブロック図。

【図12】図11のドライブ能力制御部を説明するためのブロック図。

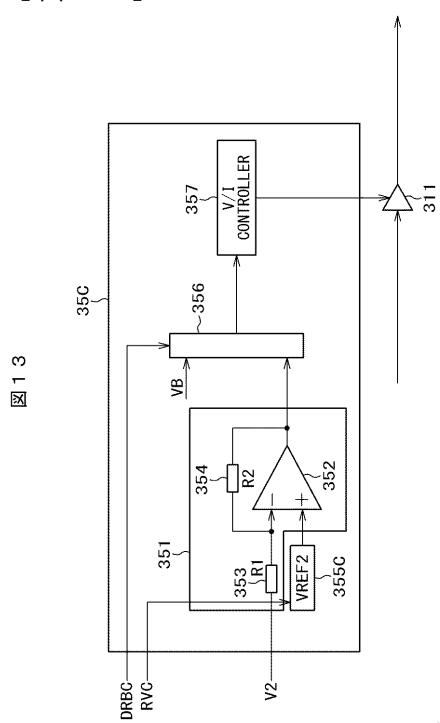

【図13】図11のドライブ能力制御部を説明するためのブロック図。

【図14】実施形態に係る半導体集積回路装置を説明するためのブロック図。

## 【発明を実施するための形態】

## 【0008】

以下、実施形態、実施例および変形例について、図面を用いて説明する。ただし、以下の説明において、同一構成要素には同一符号を付し繰り返しの説明を省略することがある。

## 【0009】

まず、本開示に先立って本願発明者が検討した技術（以下、比較例という。）について説明する。

図1は比較例に係る電動機システムの一部を示すブロック図である。図2はIGBTのセンス電流を説明するための図である。電動機システム1Rは三相モータ10とインバータ回路20とドライバIC30Rと制御回路40Rとを備える。三相モータ10は3個の変流器（コイル）11を備える。なお、2つの位相電流検出ができれば、各相の電流計算は可能があるので、変流器は2個でもよい。インバータ回路20は6個の電力用半導体装

10

20

30

40

50

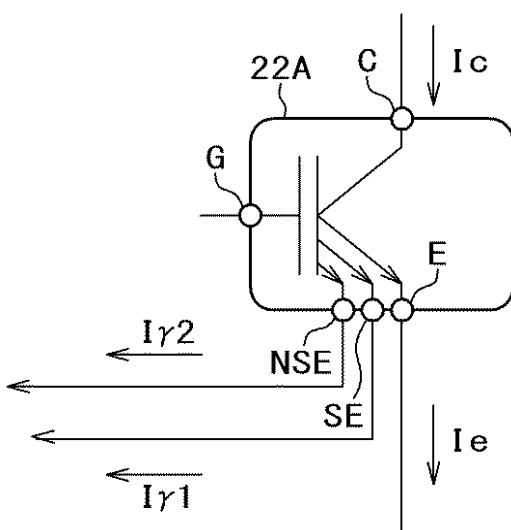

置 2 1 によって三相ブリッジ構成する。図 2 に示すように、電力用半導体装置 2 1 はスイッチングトランジスタである IGBT 2 2 を備え、IGBT 2 2 はゲート端子 G とコレクタ端子 C と駆動電流を流すエミッタ端子 E とセンス電流を流す電流検出端子 S E とを備える。ドライバ I C 3 0 R は電力用半導体 2 1 を駆動し、制御回路 4 0 はドライバ I C 3 0 を制御する。

【 0 0 1 0 】

IGBT 2 2 を使ったインバータ回路において、モータ駆動を行うためには、駆動する電流をモニタしながら IGBT 2 2 を駆動するドライブ信号 ( PWM 信号 ) を制御する必要がある。電流のモニタは下記の 2 つを行う。

( 1 ) 各位相のモータ駆動電流を変流器 1 1 、制御回路 4 0 の A / D 変換器などを使ってモニタし、通常電流検出用としてモータ駆動制御に利用する。 10

( 2 ) センス電流をドライバ I C 3 0 での電圧比較回路や A / D 変換器などを使ってモニタし、主に過電流検出用として異常電流時にドライバ信号を遮断するために利用する。

【 0 0 1 1 】

IGBT 2 2 の駆動電流はエミッタ電流 ( I e ) であり、センス電流は IGBT 2 2 内のカレントミラー回路の電流であるのでカレントミラー電流 ( I ) ともいう。エミッタ電流 ( I e ) とカレントミラー電流 ( I ) との比 ( I e / I ) カレントミラー比という。カレントミラー比は 1 0 0 0 ~ 1 0 0 0 0 程度が選択される。モータの通常駆動電流を 4 0 0 A 程度とすると、定格電流は 1 6 0 0 A 程度である。したがって、定格電流値を超える異常判断にセンス電流を利用する場合、カレントミラー比を 4 0 0 0 、電流検出用抵抗 ( R a b ) を 5 とすると、異常電流検出における電流検出電圧 ( V a b ) は、下記のとおりである。 20

$$V_{a b} = ( 1 6 0 0 A / 4 0 0 0 ) \times 5 = 2 V$$

一方で通常動作における電流検出電圧 ( V n ) は、下記のとおりである。

$$V_n = ( 4 0 0 / 4 0 0 0 ) \times 5 = 0.5 V$$

さらに、モータの低速領域では駆動電流は小さくなるためダイナミックレンジは非常に小さいものになる。

【 0 0 1 2 】

モータの回転立ち上がりや低速回転時は、より駆動能力を高めるためには、ドライブ信号である PWM 信号だけではなく、ドライブ信号の電流を増やしたりしたいが、上記 ( 1 ) のような電流検出は変流器の出力電圧を制御回路 4 0 R で A / D 変換し、その結果に基づくドライブ制御調整というループ時間がかかるため高速処理が難しい。また、上記 ( 2 ) のようなセンス電流で制御する場合にも異常電流検出用に適したループバックにしているため、充分なゲインが得られない。 30

【 0 0 1 3 】

< 実施形態 >

図 1 4 は実施形態に係る半導体集積回路装置を説明するためのブロック図である。半導体集積回路装置 3 0 は、電力用半導体装置 2 1 を駆動する駆動回路 3 1 と、駆動回路 3 1 の駆動能力を制御する駆動能力制御回路 3 4 と、を備える。駆動回路 3 1 は、電力用半導体装置 2 1 のセンス電流から検出した異常電流に基づいて電力用半導体装置 2 1 の駆動を停止する。駆動能力制御回路 3 4 は、電力用半導体装置 2 1 のセンス電流から検出した通常電流に基づいて駆動回路 3 1 の駆動能力を制御する。 40

電力用半導体装置の駆動能力が向上し、例えばモータを高トルクで駆動することが可能になる。

【 実施例 1 】

【 0 0 1 4 】

( 電動機システム )

図 3 は実施例 1 に係る電動機システムの構成を示すブロック図である。図 3 の電動機システム 1 は三相モータ 1 0 と電力用半導体装置を 6 個用いたインバータ回路 2 0 と 6 個のドライバ I C 3 0 と制御回路 4 0 と直流電源 5 0 とを備える。インバータ回路 2 0 、 6 個 50

のドライバ I C 3 0 および制御回路 4 0 で構成される部分を電子装置 2 という。インバータ回路 2 0 は、車両等の駆動時には直流電源 ( D C ) 5 0 の電圧から、三相モータ 1 0 の各相に電流を流すように、インバータ回路 2 0 内部のスイッチングトランジスタ 2 2 を O N / O F F 制御し、このスイッチングの周波数により車両等の速度を変化させる。また、車両等の制動時には、三相モータ 1 0 の各相に生じる電圧に同期してスイッチングトランジスタ 2 2 を O N / O F F 制御し、いわゆる整流動作を行い、直流電圧に変換して回生を行う。

#### 【 0 0 1 5 】

三相モータ 1 0 は回転子が永久磁石で、電機子がコイルで構成され、三相 ( U 相、 V 相、 W 相 ) の電機子巻き線は 120 度間隔に配置される。コイルはデルタ結線され、常に U 相、 V 相、 W 相の 3 つのコイルに電流が流れる。三相モータ 1 0 は変流器等の電流検出器 1 1 と角速度および位置検出器 1 2 を備える。

#### 【 0 0 1 6 】

インバータ回路 2 0 は、電力用半導体装置により U 相、 V 相、 W 相のブリッジ回路を構成している。 U 相のブリッジ回路は電力用半導体装置 2 1 U と電力用半導体装置 2 1 X の接続点が三相モータ 1 0 に接続されている。 V 相のブリッジ回路は電力用半導体装置 2 1 V と電力用半導体装置 2 1 Y の接続点が三相モータ 1 0 に接続されている。 W 相のブリッジ回路は電力用半導体装置 2 1 W と電力用半導体装置 2 1 Z の接続点が三相モータ 1 0 に接続されている。ここで、電力用半導体装置 2 1 U , 2 1 V , 2 1 W , 2 1 X , 2 1 Y , 2 1 Z の構成は同じであるので、これらを総称して電力用半導体装置 2 1 ということもある。電力用半導体装置 2 1 は I G B T で構成されるスイッチングトランジスタ ( 以下、 I G B T という。 ) 2 2 および温度検出用ダイオード D 1 を備えた半導体チップと、 I G B T 2 2 のエミッタとコレクタ間に並列に接続された還流ダイオード D 2 を備えた半導体チップとで構成される。還流ダイオード D 2 は、 I G B T 2 2 に流れる電流とは逆方向で電流を流すように接続されている。 I G B T 2 2 と温度検出用ダイオード D 1 とが形成される半導体チップと還流ダイオード D 2 が形成される半導体チップとは同一のパッケージに封入するのが好ましい。還流ダイオード D 1 は I G B T 2 2 と温度検出用ダイオード D 1 とが形成された半導体チップと同一チップに形成されてもよい。

#### 【 0 0 1 7 】

第 1 の半導体集積回路装置であるドライバ I C 3 0 は I G B T 2 2 のゲートを駆動する信号を生成する駆動回路 ( DRIVER ) 3 1 と電流検出回路 ( CURRENT DETECTION ) 3 2 と保護検出回路 ( PROTECT DETECTION ) 3 3 とドライブ能力制御回路 ( DRIVING CAPABILITY C O N TROLLER ) 3 4 を 1 つの半導体基板に備える。第 2 の半導体集積回路装置である制御回路 4 0 は C P U 4 1 と P W M 回路 ( P W M ) 4 2 と I / O インタフェース ( I / O I F ) 4 3 とを 1 つの半導体基板に備え、例えばマイクロコンピュータユニット ( M C U ) で構成される。 C P U 4 1 は図示している flaッシュメモリ等の電気的に消去および書き換えが可能な不揮発性メモリに格納されるプログラムに従って動作する。

#### 【 0 0 1 8 】

##### ( ドライバ I C 、制御回路 )

図 4 は図 3 の電動機システムの一部である電子装置を示すブロック図である。ドライバ I C 3 0 は駆動回路 3 1 と電流検出回路 3 2 と保護検出回路 3 3 とアイソレータ 3 4 とドライブ能力制御回路 3 5 とを備える。電流検出回路 3 2 は異常電流を検出する電流增幅回路 ( CURRENT AMP ) 3 2 - 1 と通常電流を検出する電流增幅回路 3 2 - 2 を備える。電流增幅回路 ( CURRENT AMP ) 3 2 - 1 はセンス電流を電圧 ( V 1 ) に変換し、保護検出回路 3 3 はその電圧に基づいて異常電流を検出して駆動回路 3 1 に送られ I G B T 2 2 の駆動信号を遮断するとともに、アイソレータ 3 4 、制御回路 4 0 の I / O インタフェース 4 4 を介して C P U 4 1 に送られる。電流增幅回路 3 2 - 2 は通常電流を電圧 ( V 2 ) に変換し、ドライブ能力制御回路 3 5 に送られ駆動回路 3 1 の駆動能力を制御する。なお、アイソレータ 3 4 はドライバ I C 3 0 と制御回路 4 0 との間を伝送する信号を磁気結合によって伝達する。アイソレータ 3 4 は配線で形成されたオンチップトランジスタを層間膜で絶縁す

10

20

30

40

50

ることにより構成される。

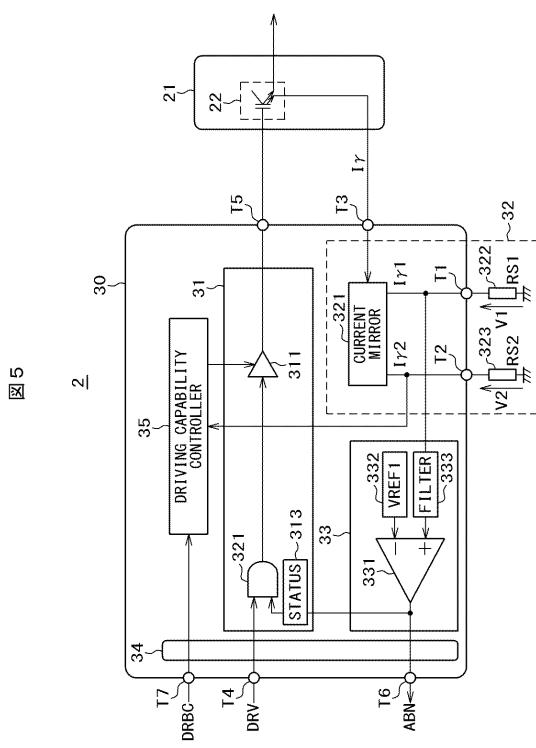

【0019】

図5は図4のドライバICを示すブロック図である。電流検出回路32はカレントミラー回路(CURRENT MIRROR)321と端子T1、T2に接続される抵抗322、323などで構成される。IGBT22の電流検出端子NEから端子T3を介して流れ込む電流(I1)をカレントミラー回路321により異常電流(I1)と通常電流(I2)とに分流する。異常電流検出と通常電流検出に適正なカレントミラービー、検出用抵抗が設定される。異常電流を検出する抵抗322の抵抗値をRS1とし、通常電流を検出する抵抗323の抵抗値をRS2とし、異常電流検出用電圧をV1とし、通常電流検出用電圧をV2とすると、

$$V1 = I1 \times RS1$$

$$V2 = I2 \times RS2$$

となる。

【0020】

保護検出回路33はコンパレータ331と基準電圧生成回路332とフィルタ333を備える。コンパレータ331は反転入力端子にフィルタ(FILTER)333を介して入力する異常電流検出電圧(V1)と非反転入力端子に入力する基準電圧生成回路332の基準電圧(VREF1)とを比較し、V1がVREF1よりも大きいときに異常電流として検出し、異常電流信号(ABN)を出力する。

【0021】

駆動回路31はドライバ311とANDゲート312と状態保持回路313とを備える。状態保持回路313は保護検出回路33で検出した異常電流信号(ABN)を保持し、異常電流信号(ABN)が異常であることを示している場合はANDゲート312の出力をLOWにして、端子T4から入力されるドライブ信号(DRV)を遮断する。異常電流信号(ABN)が異常でないことを示している場合はANDゲート312にドライブ信号(DRV)を通過させる。ドライバ311はドライブ信号(DRV)をドライブ能力制御回路35の電圧制御または電流制御に基づいて端子T5を介してIGBT22のゲート端子Gに送る。異常電流信号(ABN)は端子T6を介して制御回路40に送られる。

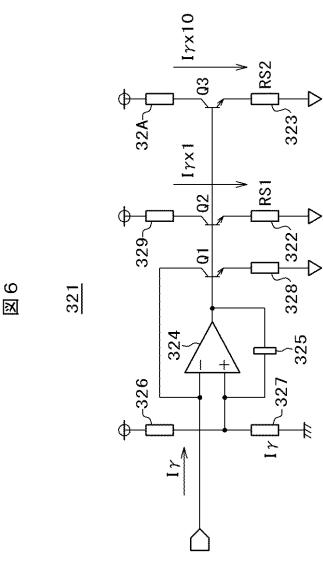

【0022】

図6は図5のカレントミラー回路を示す回路図である。カレントミラー回路321はオペアンプ324とフィルタコンデンサ325とトランジスタQ1、Q2、Q3と抵抗322、323、326、327、328、329、32Aとを備える。IGBT22のカレントミラーレ電流(I1)が流れ込む入力オペアンプ324とトランジスタQ1で受けるバッファ回路を組み、トランジスタQ1のベース電圧と同じ電圧を別のトランジスタQ2、Q3に入力し、トランジスタQ2、Q3の電流増幅設計を期待の値にすることで、例えば、

トランジスタQ2の電流をI1 × 1

トランジスタQ3の電流をI1 × 10

とすることができます。

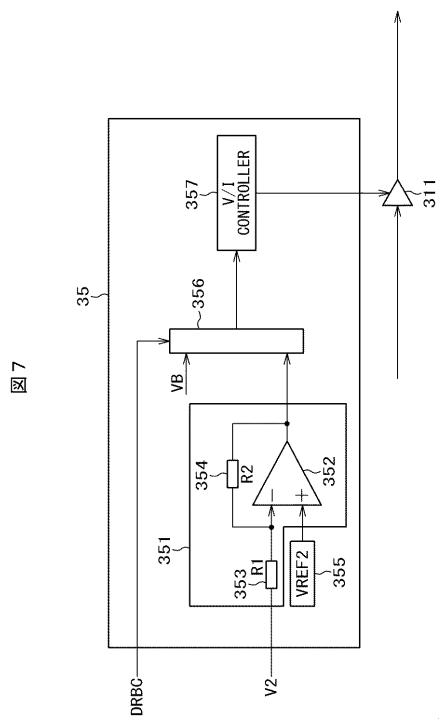

【0023】

図7は図5のドライブ能力制御回路を示すブロック図である。ドライブ能力制御回路35は増幅回路351、基準電圧生成回路352、切替回路356、電圧または電流制御回路(V/I CONTROLLER)357を備える。増幅回路351はオペアンプ352と抵抗353、354などで構成される反転差動増幅回路であり、基準電圧生成回路352の基準電圧(VREF2)と通常電流検出電圧(V2)との差に、抵抗352の抵抗値(R2)と抵抗351の抵抗値(R1)との比を掛けた電圧(V3)に増幅する。

【0024】

$$V3 = (VREF2 - V2) \times R2 / R1$$

V3はV2が小さいときはV3が大きくなり、V2が大きいときはV3が小さくなる。

【0025】

10

20

30

40

50

切替回路 356 は、制御回路 40 から端子 T7 を介して入力されるドライブ能力制御信号 (DRBC) に基づいて基本設定電圧 (VB) と電圧 (V3) とを切り替えて、電圧または電流制御回路 357 に電圧を供給する。

【0026】

電圧または電流制御回路 357 はドライバ 311 の電圧または電流を制御し、ドライバ 311 の出力電圧または電流を制御する。電圧 (V3) は基本設定電圧 (VB) よりも高い電圧であり、電圧 (V3) に切り替えたときはドライバ 311 の出力電圧または電流は増加する。

【0027】

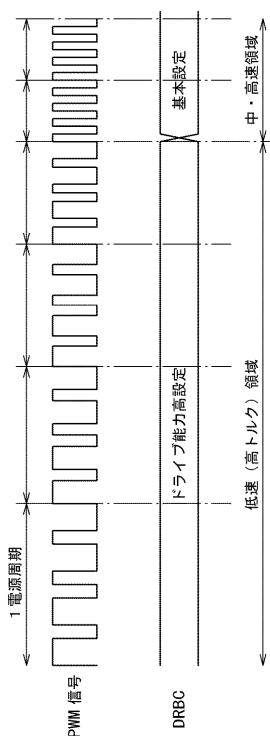

図 8 は図 5 のドライブ能力制御回路の制御を説明するためのタイミング図である。モータの低速 (高トルク) 領域では、中高速領域よりも 1 電源周期を長くし、かつ PWM 信号のデューティを大きくすると共に、ドライバ 311 のドライブ能力を高く設定するため、端子 T7 から入力されるドライブ能力制御信号 (DRBC) によって電圧 (V3) に切り替える。中高速領域では、ドライブ能力制御信号 (DRBC) によって基本設定電圧 (VB) に切り替える。

10

【0028】

本実施例によれば、モータの回転立ち上がりや低速回転時に、より駆動能力を高めるために、ドライブ信号である PWM 信号だけではなく、ドライブ信号の電流を増やすことが可能である。また、センス電流で電流を検出し、電流検出に変流器を使用ないので、変流器の出力電圧を制御回路 40 で A/D 変換し、その結果に基づくドライブ制御調整というループ時間がかかるってしまうことがないので、高速処理が容易になる。また、異常電流検出用に適したループバックと通常電流検出用に適したループバックとの両方があるので、充分なゲインが得られる。

20

【実施例 2】

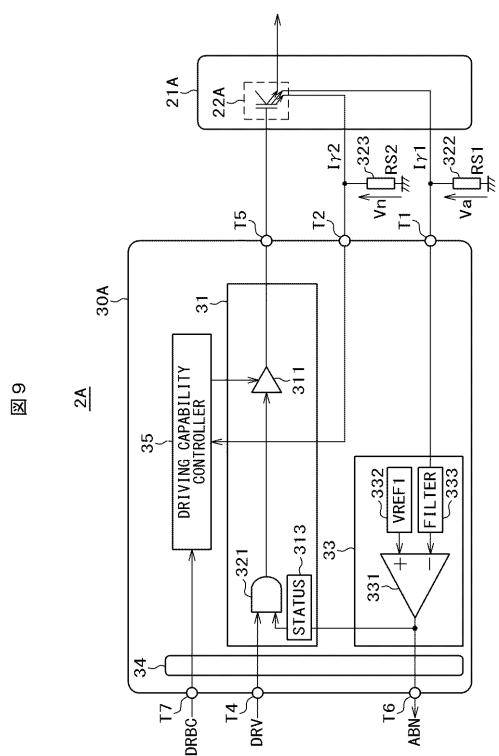

【0029】

図 9 は実施例 2 に係る電子装置を示すブロック図である。実施例 2 に係る電子装置は IGBT に 2 つのカレントミラーを備え、実施例 1 のドライバ I/C のカレントミラー回路を省略するものであり、その他の構成は実施例 1 と同様である。

【0030】

実施例 1 の IGBT 22 は同一構造からなる数千～数万個のセルから構成されている。このうちの一部をセンス電流 (異常電流) 検出用のセルとして利用し、またセンス電流検出用の一部のセルからなる領域を「異常電流検出領域」、その他のセルからなる領域を「メイン領域」という。そしてメイン領域のセル数 (Nm : 整数) と異常電流検出領域のセル数 (Ns : 整数) の比 (Nm / Ns) は数千倍となるように設定する。実施例 2 の IGBT 22A は、さらにセンス電流 (通常電流) 検出用のセルを有し、このセルからなる領域を通常電流検出領域という。通常電流検出領域のセル数 (Nns : 整数) とすると、Nns / Ns を例えば 10 に設定する。

30

【0031】

図 10 に示すように、IGBT 22A においてメイン領域と異常電流検出領域と通常電流検出領域のコレクタ端子は共通であり、エミッタ端子はメインエミッタ端子 E (以下、メイン端子という。) と異常電流検出用エミッタ端子 SE (以下、センス端子という。) と通常電流検出用エミッタ端子 NSE (以下、通常センス端子という。) に分離されている。また、各領域を駆動するためのゲート端子 G は共通である。

40

【0032】

センス端子 SE からのカレントミラー電流 (I1) は端子 T1 に接続される異常電流検出用抵抗 322 により異常電流検出電圧 (V1) を生成し、IGBT 22A のカレントミラー回路と異常電流検出用抵抗 322 は異常電流検出回路を構成する。通常センス端子 NSE からのカレントミラー電流 (I2) は端子 T2 に接続される通常電流検出用抵抗 323 により通常電流検出電圧 (V2) を生成し、IGBT 22A のカレントミラー回路と通常電流検出用抵抗 323 は通常電流検出回路を構成する。

50

## 【0033】

本実施例ではドライバIC内にカレントミラー回路を設ける必要がないので、実施例1よりもドライバICを簡単な構成にすることができ、チップ面積を小さくすることが可能となる。

## 【実施例3】

## 【0034】

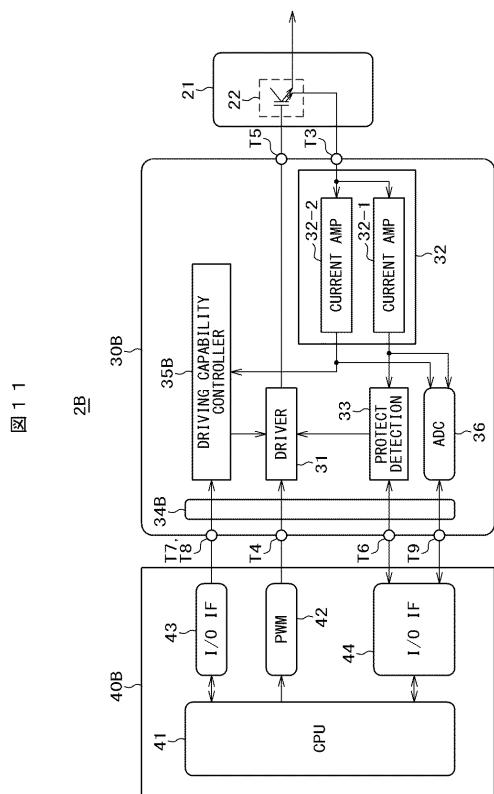

図11は実施例3に係る電子装置を示すブロック図である。実施例3に係る電子装置は実施例1のドライバICにさらにA/D変換器を備え、ドライバ能力制御回路にフィードバックできるものであり、その他の構成は実施例1と同様である。

## 【0035】

ドライバIC30Bは電流検出回路32（電流増幅回路32-1、32-2）の出力である異常電流検出用電圧（Va）および通常電流検出用電圧（Vn）を制御回路40Bに通知するためのA/D変換器（ADC）36を備える。A/D変換器36の出力はアイソレータ34Bおよび端子T9を介して制御回路40Bに送られる。

## 【0036】

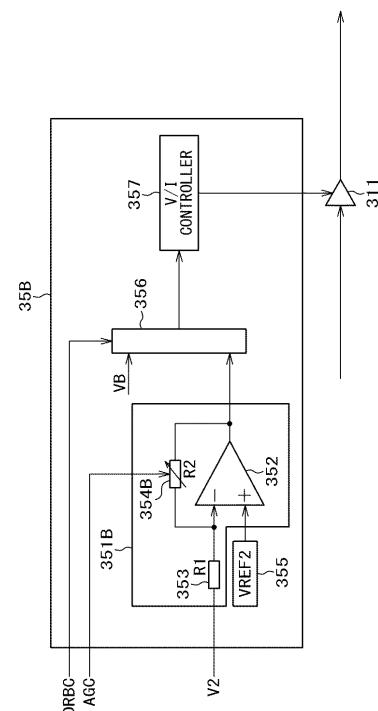

図12は図11のドライブ能力制御回路を説明するためのブロック図である。実施例1のドライブ能力制御回路は増幅回路のループ抵抗の抵抗値を調整可能な機能を有し、その他の構成は実施例1と同様である。制御回路40BはA/D変換器36を経由して得られた電圧（Vn）に基づいて制御信号（AGC）を生成する。ドライブ能力制御回路35Bの増幅回路351Bの抵抗354Bは可変抵抗であり、端子T8から入力される制御信号（AGC）に基づいて抵抗値の調整が可能とされる。通常電流検出用電圧（Vn）のフィードバックゲインを調整できる機能（増幅回路351Bのループ抵抗354Bを調整できる機能）を有することで、通常電流検出用抵抗322の抵抗値（RS2）のバラツキにあわせて、当該ゲインを調整することで、精度の高い駆動能力制御が可能となる。

## 【0037】

## &lt;変形例&gt;

図13は図11のドライブ能力制御部を説明するためのブロック図である。実施例1の基準電圧（VREF2）を調整可能な機能を有し、その他の構成は実施例1と同様である。制御回路40BはA/D変換器36を経由して得られた電圧（Vn）に基づいて制御信号（RVC）を生成する。ドライブ能力制御回路35Cの基準電圧生成回路355Cの基準電圧（VREF2）は可変であり、端子T8から入力される制御信号（RVC）に基づいて基準電圧の調整が可能とされる。通常電流検出用電圧（Vn）のフィードバックゲインを調整できる機能（基準電圧生成回路355Cの基準電圧（VREF2）を調整できる機能）を有することで、通常電流検出用抵抗322の抵抗値（RS2）のバラツキにあわせて、当該ゲインを調整することで、精度の高い駆動能力制御が可能となる。

## 【0038】

以上、本発明者によってなされた発明を実施形態、実施例および変形例に基づき具体的に説明したが、本発明は、上記実施形態、実施例および変形例に限定されるものではなく、種々変更可能であることはいうまでもない。

## 【符号の説明】

## 【0039】

- 1・・・電動機システム

- 10・・・三相モータ

- 11・・・変流器

- 20・・・インバータ回路

- 21・・・電力用半導体装置

- 22・・・IGBT

- 30・・・ドライバIC

- 31・・・駆動回路

- 311・・・ドライバ

10

20

30

40

50

- |       |             |    |

|-------|-------------|----|

| 3 1 2 | ANDゲート      | 10 |

| 3 1 3 | 状態保持回路      |    |

| 3 2   | 電流検出回路      |    |

| 3 2 1 | カレントミラー回路   |    |

| 3 2 2 | 異常電流検出抵抗    |    |

| 3 2 3 | 通常電流検出抵抗    |    |

| 3 3   | 保護検出回路      |    |

| 3 3 1 | コンパレータ      |    |

| 3 3 2 | 基準電圧        |    |

| 3 3 3 | フィルタ回路      |    |

| 3 4   | アイソレータ      |    |

| 3 5   | ドライブ能力制御回路  |    |

| 3 5 1 | 增幅回路        |    |

| 3 5 2 | オペアンプ       |    |

| 3 5 3 | 抵抗          |    |

| 3 5 4 | 抵抗          |    |

| 3 5 5 | 基準電圧生成回路    |    |

| 3 5 6 | 切替回路        |    |

| 3 5 7 | 電圧または電流制御回路 |    |

| 4 0   | 制御回路        | 20 |

| 4 1   | CPU         |    |

| 4 2   | PWM回路       |    |

| 4 3   | I/Oインターフェース |    |

| 4 4   | I/Oインターフェース |    |

【 図 1 】

【 図 2 】

【 义 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図9】

【 四 8 】

【図10】

10

【図11】

【 図 1 2 】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開2006-187101(JP,A)

特開2013-219910(JP,A)

特開2000-323974(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 02 M 1 / 08