(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2010-534897

(P2010-534897A)

(43) 公表日 平成22年11月11日(2010.11.11)

(51) Int.Cl.

G 11 C 11/406 (2006.01)

G 06 F 12/00 (2006.01)

F 1

G 11 C 11/34

G 06 F 12/00

G 06 F 12/00

G 11 C 11/34

テーマコード(参考)

5 B 0 6 0

5 M 0 2 4

審査請求 有 予備審査請求 未請求 (全 16 頁)

(21) 出願番号 特願2010-518407 (P2010-518407)

(86) (22) 出願日 平成20年7月25日 (2008.7.25)

(85) 翻訳文提出日 平成22年3月26日 (2010.3.26)

(86) 國際出願番号 PCT/US2008/071153

(87) 國際公開番号 WO2009/015324

(87) 國際公開日 平成21年1月29日 (2009.1.29)

(31) 優先権主張番号 11/828,569

(32) 優先日 平成19年7月26日 (2007.7.26)

(33) 優先権主張国 米国(US)

(71) 出願人 595020643

クアアルコム・インコーポレイテッド

Q U A L C O M M I N C O R P O R A T

E D

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】有効データインジケータの使用によってダイナミックRAM電力消費を減らすシステムおよび方法

## (57) 【要約】

DRAMまたはSDRAMのコンポーネントは、行のような、DRAMアレイの独立してリフレッシュ可能なメモリ装置が有効データを含むかどうか示すインジケータを維持する。リフレッシュ操作が関連するメモリに導かれるとき、メモリが有効データを含んでいない場合にリフレッシュ操作が抑えられる。著しい省電力は無効データに向けられたリフレッシュ操作を抑えることにより実現されるかもしれない。

FIG. 4

**【特許請求の範囲】****【請求項 1】**

それぞれ独立してリフレッシュ可能なメモリ装置にインジケータを関連させることと、独立してリフレッシュ可能なメモリ装置にデータを書き込むことで、有効データを反映させるために関連するインジケータをセットすることと、その関連するインジケータがメモリ装置に記憶された有効データを反映する、独立してリフレッシュ可能なメモリ装置だけをリフレッシュすることとを具備するダイナミックメモリをリフレッシュすることの方法。

**【請求項 2】**

前記独立してリフレッシュ可能なメモリ装置が行である請求項 1 の方法。 10

**【請求項 3】**

前記独立してリフレッシュ可能なメモリ装置が 2 つ以上のメモリバンクを通して行を具備する請求項 1 の方法。

**【請求項 4】**

前記インジケータが有効ビットである請求項 1 の方法。

**【請求項 5】**

前記有効ビットがDRAMアレイに記憶される請求項 4 の方法。

**【請求項 6】**

前記有効ビットがスタティックメモリに記憶される請求項 4 の方法。 20

**【請求項 7】**

前記有効ビットがレジスタに記憶される請求項 4 の方法。

**【請求項 8】**

有効データを反映させるために前記関連するインジケータをセットすることは、前記関連する独立してリフレッシュ可能なメモリ装置にデータを書き込むことで前記インジケータを自動的にセットすることを具備する請求項 1 の方法。

**【請求項 9】**

有効データを反映させるために前記関連するインジケータをセットすることは、メモリコントローラからのコマンドで前記インジケータをセットすることを具備する請求項 1 の方法。

**【請求項 10】**

有効データを反映するためにセットしたインジケータはリセットでクリアされる請求項 1 の方法。 30

**【請求項 11】**

有効データを反映するためにセットしたインジケータは、メモリコントローラからのコマンドでクリアされる請求項 1 の方法。

**【請求項 12】**

その関連するインジケータがメモリ装置に記憶された有効データを反映する、前記独立してリフレッシュ可能なメモリ装置だけをリフレッシュすることは、

その関連するインジケータがそこに記憶された有効データを反映する、前記独立してリフレッシュ可能なメモリ装置だけをセルフリフレッシュすることを具備する請求項 1 の方法。 40

**【請求項 13】**

その関連するインジケータがメモリ装置に記憶された有効データを反映する、前記独立してリフレッシュ可能なメモリ装置だけをリフレッシュすることは、

その関連するインジケータがそこに記憶された有効データを反映する、前記独立してリフレッシュ可能なメモリ装置だけをオートリフレッシュすることを具備する請求項 1 の方法。

**【請求項 14】**

その関連するインジケータがメモリ装置に記憶された有効データを反映する、前記独立してリフレッシュ可能なメモリ装置だけをリフレッシュすることは、 50

不連続の独立してリフレッシュ可能なメモリ装置を連続してリフレッシュすることを具備する請求項 1 の方法。

【請求項 1 5】

その関連するインジケータがメモリ装置に記憶された有効データを反映する、前記独立してリフレッシュ可能なメモリ装置だけをリフレッシュすることは、

リフレッシュコマンドを受け取ることと、

現在のリフレッシュアドレスに関連した前記インジケータを検査することと、

前記インジケータが有効データを反映する場合で、前記アドレスされた、独立してリフレッシュ可能なメモリ装置をリフレッシュすることを具備する請求項 1 の方法。

【請求項 1 6】

前記インジケータが無効データを反映する場合で、リフレッシュサイクルを抑えることをさらに具備する請求項 1 4 の方法。

【請求項 1 7】

前記インジケータが有効データを反映する場合で、有効データを反映する前記インジケータをもつ、前記次の独立してリフレッシュ可能なメモリ装置へのリフレッシュアドレスをインクリメントすることをさらに具備する請求項 1 4 の方法。

【請求項 1 8】

スキップされたリフレッシュアドレスの数に比例してリフレッシュ回数を縮小することをさらに具備する請求項 1 6 の方法。

【請求項 1 9】

データを記憶するのに作用し、複数の独立してリフレッシュ可能なメモリ装置として組織された D R A M アレイと、

各々独立してリフレッシュ可能なメモリ装置に関係していて、有効データが前記独立してリフレッシュ可能なメモリ装置に記憶されるかどうか示した複数のインジケータと、

前記インジケータを検査し、かつ有効データを記憶する独立してリフレッシュ可能なメモリ装置だけをリフレッシュするために制御信号とオペレイティヴ (operative) を受け取るコントローラと

を具備する D R A M コンポーネント。

【請求項 2 0】

前記 D R A M アレイの中の前記独立してリフレッシュ可能なメモリ装置のアドレスを生成するのに作用するリフレッシュカウンタをさらに具備する請求項 1 9 の D R A M コンポーネント。

【請求項 2 1】

データが、関連する独立してリフレッシュ可能なメモリ装置に書き込まれている場合にインジケータをセットするのに作用する回路をさらに具備する請求項 1 9 の D R A M コンポーネント。

【請求項 2 2】

前記インジケータが初期設定中にクリアされる請求項 1 9 の D R A M コンポーネント。

【請求項 2 3】

前記コントローラは、制御信号に応じて前記インジケータをセットするかクリアするのにさらに作用する請求項 1 9 の D R A M コンポーネント。

【請求項 2 4】

前記インジケータは、1 つ以上の独立してリフレッシュ可能なメモリ装置に記憶される請求項 1 9 の D R A M コンポーネント。

【請求項 2 5】

前記インジケータは、前記 D R A M アレイとは異なるメモリに記憶される請求項 1 9 の D R A M コンポーネント。

【請求項 2 6】

タスクにメモリを割り付けるソフトウェアタスクからのリクエストを受け取ることと、メモリ装置中の1つ以上の独立してリフレッシュ可能なメモリ装置からのタスクにメモ

10

20

30

40

50

リを割り付けることと、

前記独立してリフレッシュ可能なメモリ装置に向けられたリフレッシュ操作を抑えないために前記メモリ装置に向けられた、それぞれ独立してリフレッシュ可能なメモリ装置に関連したインジケータをセットすることとのステップを行なうのに作用する1つのメモリマネージャコンピュータプログラムを少なくとも含むコンピュータ読取可能媒体。

#### 【請求項27】

前記メモリマネージャコンピュータプログラムは、

以前にタスクに割り付けられたメモリを開放するためにソフトウェアタスクからリクエストを受け取ることと、

以前に前記タスクに割り付けられたメモリを開放することと、

10

前記独立してリフレッシュ可能なメモリ装置中のメモリがすべて開放されている場合、その独立してリフレッシュ可能なメモリ装置に向けられた、リフレッシュ操作を抑えるようにメモリ装置に命令するために前記関連するインジケータをクリアすることとのステップを行なうのにさらに作用する請求項26のコンピュータ読取可能媒体。

#### 【請求項28】

シングルプロセッサ上で実行する複数のソフトウェアタスクに前記メモリマネージャコンピュータプログラムがメモリを割り付ける請求項26のコンピュータ読取可能媒体。

#### 【請求項29】

異なるプロセッサ上で各々実行する、2つ以上のソフトウェアタスクに前記メモリマネージャコンピュータプログラムがメモリを割り付ける請求項26のコンピュータ読取可能媒体。

20

#### 【請求項30】

前記メモリマネージャコンピュータプログラムは、前記関連する独立してリフレッシュ可能なメモリ装置に最初にデータを書き込むことで、独立してリフレッシュ可能なメモリ装置インジケータをセットする請求項26のコンピュータ読取可能媒体。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、メモリの分野に一般に関係があり、システムへダイナミックRAM電力消費を減らすためのシステム及び方法に特に関係がある。

30

#### 【背景技術】

#### 【0002】

ソリッドステートダイナミックランダムアクセスメモリ(DRAM)は、携帯用電子機器を含む、多くの現代のコンピューティングシステムのための資金効率の良い大容量メモリ装置ソリューションである。同期DRAM(SDRAM)を含むDRAMは、高位ビット密度、およびファスター(faster)と比較してビットあたりの比較的低いコスト、レジスタ、スタティックRAMなど(SRAM)のようなオンチップメモリ構造、および、ハードディスク、CD-ROMなどのような電気的、磁気的、または光学的・機械的大容量ストレージより劇的に速いアクセス速度を提供する。

#### 【0003】

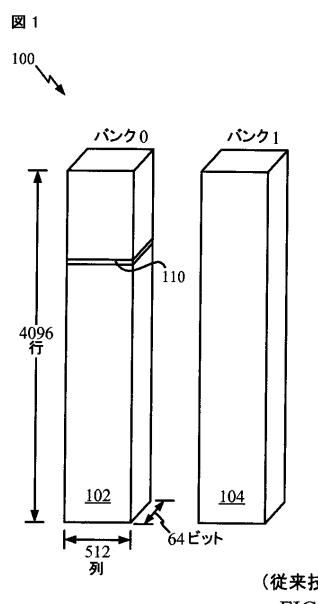

図1は、代表的な512メガビットのDRAMアレイ100の論理的な見方を描く。アレイ100は、別々にアドレス指定できる複数のバンク102, 104, 106, 108として組織される。それぞれのバンクは、行(row)110の多数、例えば4096に分割される。それぞれの行110は、複数の列(column)(例えば512列)に分割され、また、それぞれの列はバイト群(例えば8バイト)として典型的に組織されて、多くのデータビットを含む。いくつかのデータアドレッシングスキームは従来から知られている。例えば、バンク、行、列(BRC)アドレッシングで、メモリアドレスは

40

【表1】

表1

| 31-26 | 25-24 | 23-12    | 11-3        | 2-0   |

|-------|-------|----------|-------------|-------|

| チップ選択 | バンク選択 | 行(row)選択 | 列(column)選択 | バイト選択 |

10

【0004】

として解釈されるかもしれない。行、バンク、列（RBC）アドレッシングのような代替アドレスシングスキームでは、メモリアドレスは

【表2】

表2

| 31-26 | 25-14    | 13-12 | 11-3        | 2-0   |

|-------|----------|-------|-------------|-------|

| チップ選択 | 行(row)選択 | バンク選択 | 列(column)選択 | バイト選択 |

20

【0005】

として解釈されるかもしれない。

【0006】

D R A M メモリアレイは揮発性であり、その保全性を維持するためにD R A M アレイに記憶されたデータは周期的にリフレッシュされなければならない。D R A M リフレッシュ動作中に、多くのデータ保存場所は、アレイ100から同時に除かれ、充電される。因習的に、D R A M アレイは一行ずつリフレッシュされる。すなわち、行が、あるいは、いくつかのインプリメンテーションで、あらゆるバンクの中で同時に同じ行が選択され、また、行の内の全てのデータは单一の操作でリフレッシュされる。ここに使用されるように、用語“独立してリフレッシュ可能なメモリ装置”すなわちI R M Uは、単一のリフレッシュ操作でリフレッシュされるデータの量を指す。本発明は一行ずつのリフレッシュ操作に制限されていないが、D R A M アレイのためのI R M Uは典型的に行である。

30

【0007】

I R M Uに向けられたリフレッシュ操作は、メモリアクセスで因習的に散りばめられ、また、時間が計られる、帯電減衰(charge decay)により失われた任意のデータに先立って全D R A M アレイがリフレッシュされるそのようなものである。もともとは、リフレッシュアドレス、すなわちそれぞれ独立してリフレッシュ可能なメモリ装置のアドレスは、プロセッサのようなメモリコントローラによって供給され、それは制御信号の個性的なコンビネーションによってリフレッシュ操作を指定する。現代のS D R A M コンポーネントは2つの付加的なリフレッシュモードである、セルフリフレッシュおよびオートリフレッシュを含むかもしれない。両方のモードにおいて、S D R A M コンポーネントは内部リフレッシュアドレスカウンタを含んでいる。セルフリフレッシュは、電力を保持するために“スリープ”モードを使用する、電池式の電子装置のような多くのシステムで利用される。セルフリフレッシュモードでは、S D R A M コンポーネントは保存またはデータ検索へアクセス可能ではなく、しかしながら、S D R A M は、記憶データの保全性を保証するために内部でリフレッシュ操作を行なう。オートリフレッシュモードでは、メモリコントローラはリフレッシュ操作を指定するが、リフレッシュアドレスを提供しない。もっと正確に言えば、S D R A M コンポーネントは、それは連続的な独立してリフレッシュ可能なメモリアドレスを提供する。

40

50

リ装置（例えば行）アドレスを提供する内部リフレッシュアドレスカウンタをインクリメントする。

【0008】

データがDRAMアレイから読まれ充電されるとともに、リフレッシュ操作はそれぞれ電力を消費する。しかしながら、特に下記パワーオンあるいはシステムリセット、DRAMアレイの中のほとんどのメモリ装置場所(locations)は有効データを含んでいない。

【発明の概要】

【0009】

ここに示されてクレームされた1つ以上の実施形態によれば、メモリのリフレッシュ可能なセグメントが有効データを含むかどうか示すインジケータが維持される。リフレッシュ操作が関連するメモリに向けられる際、メモリが有効データを含んでいない場合、リフレッシュ操作が抑えられる。著しい省電力は無効データに向けられたリフレッシュ操作を抑えることにより実現されるかもしれない。

10

【0010】

1つの実施形態はダイナミックメモリをリフレッシュする方法に関係がある。インジケータはそれぞれ独立してリフレッシュ可能なメモリ装置に関係している。独立してリフレッシュ可能なメモリ装置にデータを書き込む際、関連するインジケータは、有効データを反映する準備ができている。独立してリフレッシュ可能なメモリ装置だけがリフレッシュされ、その関連するインジケータは、そのメモリ装置に記憶した有効データを反映したものである。

20

【0011】

1つの実施形態はDRAMコンポーネントに関係がある。DRAMコンポーネントは、データを記憶するのに作用して、複数の独立してリフレッシュ可能なメモリ装置として組織されたDRAMアレイを含んでいる。DRAMコンポーネントは、各々独立してリフレッシュ可能なメモリ装置に関係していて、独立してリフレッシュ可能なメモリ装置に有効データが保存されるかどうか示した複数のインジケータをさらに含んでいる。DRAMコンポーネントは、インジケータを検査するため、かつ有効データを記憶する独立してリフレッシュ可能なメモリ装置のみをリフレッシュするために制御信号とオペレーティブ(operative)を受け取るコントローラをさらに含んでいる。

30

【図面の簡単な説明】

【0012】

【図1】図1は、DRAMアレイの中のデータ組織の機能ブロック図である。

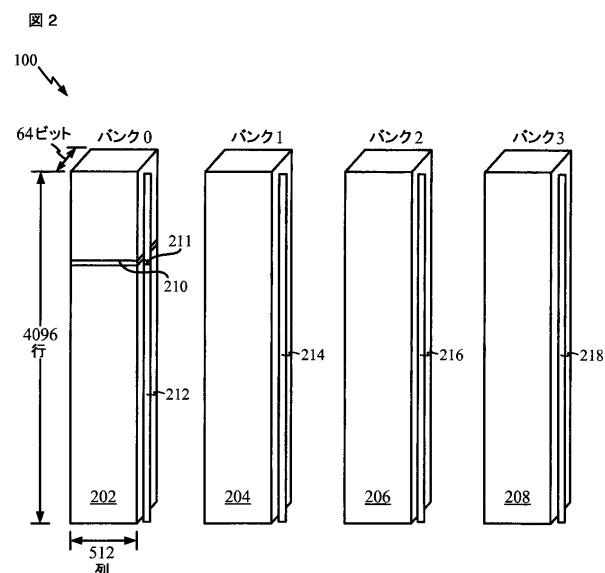

【図2】図2は、それぞれ独立してリフレッシュ可能なメモリ装置に関連した、有効なインジケータあるいはビットを伴うDRAMアレイの中のデータ編成の機能ブロック図である。

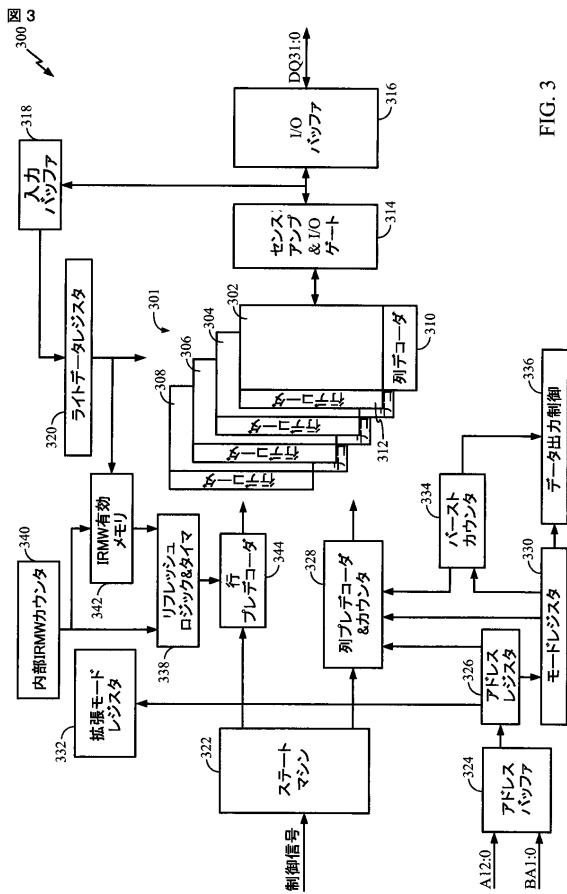

【図3】図3はSDRAMコンポーネントの機能ブロック図である。

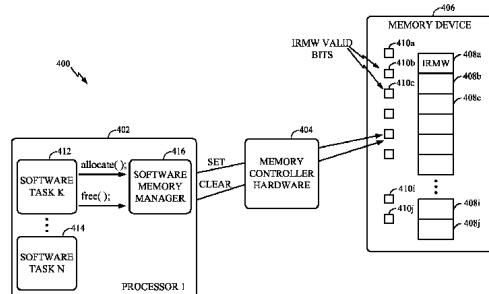

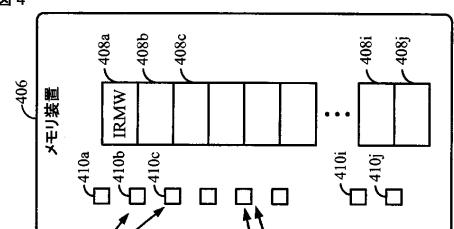

【図4】図4はシングルプロセッサコンピューティングシステムの機能ブロック図である。

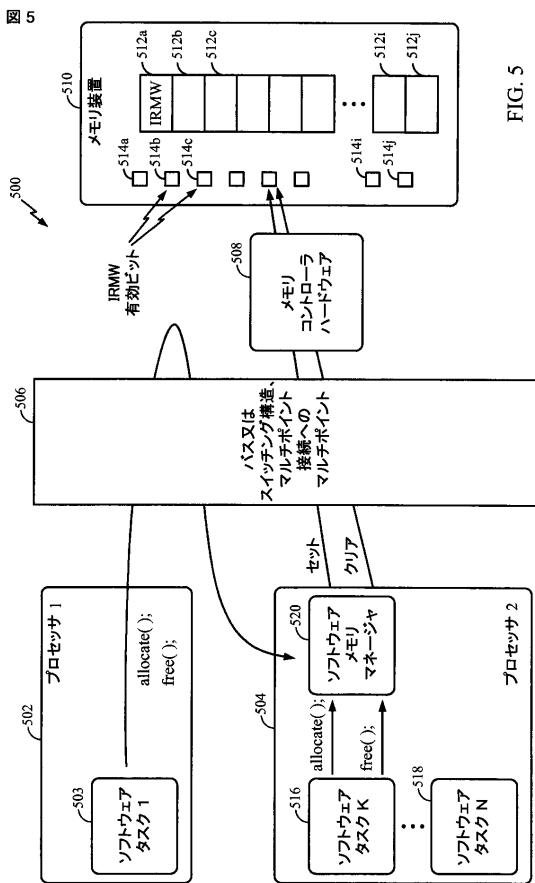

【図5】図5は多重プロセッサコンピューティングシステムの機能ブロック図である。

40

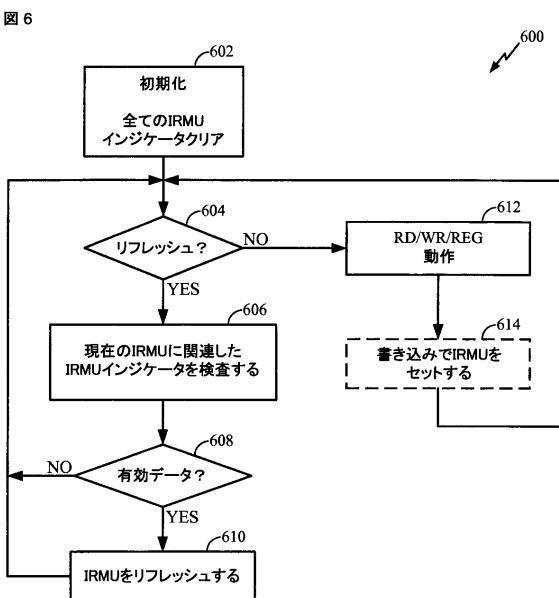

【図6】図6はDRAMアレイをリフレッシュする方法のフローチャートである。

【発明を実施するための形態】

【0013】

図2は、1つの実施形態によるDRAMアレイ200組織の論理的な視界を描く。アレイ200は、4つのバンク202, 204, 206, 208として論理上組織され、各バンクは4096行を含む。代表的な行は210として描かれる。この実施形態では、行210は最も小さな独立してリフレッシュ可能なメモリ装置である。アレイ200内で行210に関係していたものは、行210が有効データを含んでいても含んでいなくても反映するインジケータ211である。描かれた実施形態では、それぞれのインジケータ211は、各行に関係する、有効ビットとしてここに参照されるシングルビットを具備する。図2は、それぞれ、バンク202, 204, 206, 208で行に関連した各インジケータ

50

ビットである、インジケータビット 212, 214, 216, 218 のセットを描く。最も小さな独立してリフレッシュ可能なメモリ装置が 4 つのバンク 202, 204, 206, 208 すべてにまたがる行を具備する実施形態では、インジケータビット 212 の 1 つのセットのみが必要だろう。

【0014】

リフレッシュ操作中に、例えば IRMU210 といった、現在アドレス指定された独立してリフレッシュ可能なメモリ装置に関連した、例えばインジケータ 211 といった、インジケータあるいは有効ビットは検査される。インジケータビットがセットされる場合、関連する IRMU が有効データを含むことを示して、リフレッシュ操作はデータを維持するために IRMU 上で行なわれる。インジケータビットがセットされない場合、関連する IRMU を示すことは有効データを含まず、1 つの実施形態では、リフレッシュ操作は IRMU をリフレッシュする際にさもなければ消費される電力を保存することで抑えられる。したがって、有効データを含んでいる IRMU のみがリフレッシュされるだろう、そして初期化されなかった、あるいは“don't care”状態でのアレイ中の IRMU はリフレッシュされない。リフレッシュアドレスはメモリコントローラによって供給されるかもしれない、あるいは例えばオートリフレッシュあるいはセルフリフレッシュの期間のように内部アドレスカウンタによって生成されるかもしれない。

10

【0015】

インジケータビットは様々な方法で維持されるかもしれない。1 つの実施形態では、インジケータビットはメモリアレイ 200 の固定のまたはプログラム可能な部分で記憶される。この場合、アレイ 200 の使用可能なサイズは 0.003 % 減らされる。別の実施形態では、インジケータビットは、例えばスタティック RAM ストラクチャ中やレジスタ中などのように、DRAM アレイ 200 以外のメモリ中の DRAM / SDRAM コンポーネントで記憶される。1 つの実施形態では、IRMU 有効インジケータメモリは、SDRAM コンポーネントのモードレジスタと拡張モードのレジスタアクセスシーケンスに似ている 2 サイクルシーケンスによってアクセスされる。

20

【0016】

図 3 は、1 つの実施形態による SDRAM コンポーネント 300 の機能ブロック図である。SDRAM 300 は、4 つのバンク 302, 304, 306, 308 として組織される DRAM アレイ 301 を含んでいる。それぞれのバンクは行デコーダ 312, 列デコーダ 310 を含む。センスアンプ 314 は、I/O バッファ 316 に DRAM アレイ 301 からの読まれたデータを供給する。I/O バッファ 316 からの書き込みデータ (write data) は入力バッファ 318 を通り、DRAM アレイ 301 に書き込む前にライトデータレジスタ 320 に保存される。

30

【0017】

SDRAM コンポーネント 300 の動作はステートマシン 322 によって制御される。バンクとメモリアドレスはアドレスバッファ 324 へ入力されてアドレスレジスタ 326 に記憶され、するとそこで、それらが列プレデコーダ & カウンタ回路 (column pre-decoder and counter circuit) 328 を制御する。モードレジスタ 330 および拡張モードレジスタ 332 は、例えばカラム・アドレス・ストローブ (CAS) 遅れ、バースト長などのようなモード選択ビットを記憶し、そしてそれはバーストカウンタ 334 およびデータ出力制御回路 336 の動作を制御する。

40

【0018】

リフレッシュロジック & タイマ回路 (refresh logic and timer circuit) 338 は、内部カウンタ 340 からの IRMU アドレス、および IRMU 有効メモリ 342 からの IRMU 有効ビットを受け取る。リフレッシュロジックは、行プレデコーダ (row pre-decoder) 344 に IRMU アドレスを出力する。IRMU 有効メモリ 342 が DRAM アレイ 301 から分離して区別された機能ブロックとして図 3 に描かれている間に、IRMU 有効インジケータの記憶装置に物理的に専用のメモリは、DRAM アレイ 301 の一部かもしれないし、あるいは個別の DRAM, SDRAM、レジスタあるいは他のメモリかもし

50

れないことに注意されたい。

【0019】

1つの実施形態中で、SDRAMコンポーネント300は、書き込みアドレス(write addresses)を自動的に監視し、また、それぞれの書き込み操作(write operation)が向けられるIRMUに対応するIRMU有効インジケータをセットする。その後、リフレッシュロジック338は、各リフレッシュ操作でのIRMU有効メモリ342を検査し、有効データを含んでいないあらゆるIRMUに向けられたリフレッシュサイクルを抑える。これは、SDRAMコンポーネント300の電力消費を最小化するが、リフレッシュ抑制知識あるいはメモリコントローラまたはプロセッサによる関与を要求しない。DRAMアレイ301が、有効データの大部分が中身がない場合、主要な省電力化は、パワーオンあるいはリセットに続いておそらく生じる。DRAMアレイ301の中のより多くのIRMUへのメモリコントローラ書き込みデータ(memory controller writes data)として、より多くのIRMU有効ビットがセットされ、また、より少数のリフレッシュサイクルが抑えられる。この実施形態では、IRMUメモリ342は、電源投入からリセットに続くSDRAMコンポーネント300初期設定の部分として自動的にクリアされる。精巧なメモリ管理機能性を含んでいない既存のメモリコントローラおよびソフトウェアを利用している間、この実施形態は、システム設計者がSDRAMコンポーネント300のより低い電力消費を利用することを可能にする。

10

【0020】

1つの実施形態では、IRMUメモリ342は、例えば定義済みのモードレジスタ330あるいは拡張モードレジスタ332書き込み操作かビットパターンのような、メモリコントローラからのコマンドによってクリアされるかもしれない。この実施形態は、ソフト(例えばソフトウェア初期化)リセットに続く、減らされたSDRAMコンポーネント300電力消費を考慮に入れ、しかしメモリコントローラがIRMUメモリ342クリアコマンドを出すことを要求する。

20

【0021】

図4は、DRAM電力消費を制御して減らすコンピューティングシステム400を描く。システム400は、例えばプロセッサ402、メモリコントローラハードウェア404(それはプロセッサに統合されてもよい)、およびSDRAMコンポーネント406のようなメモリ装置のようなメモリコントローラを含んでいる。SDRAMコンポーネント406内部のDRAMアレイは、独立してリフレッシュ可能なメモリ装置408a, 408b, 408c, ..., 408jに論理的に分割される。例えばビット410a, 410b, 410c, ..., 410jのようなIRMU有効インジケータが各IRMUに関係しており、そしてそれは関連するIRMUが有効データを含むかどうかを示す。

30

【0022】

複数のソフトウェアタスク412, 414はプロセッサ402で実行する。それぞれのソフトウェアタスクはデータ記憶のためにメモリを割り付けるかもしれない、また、もはや必要とされないメモリを開放するかもしれない。ソフトウェアメモリマネージャ416は、プロセッサ402用メモリを管理するソフトウェアモジュールである。ソフトウェアメモリマネージャ416はソフトウェアタスク412, 414からのメモリ“allocate”および/または“free”リクエストを受け取る。レスポンスで、ソフトウェアメモリマネージャ416は、タスク412, 414間のメモリを割り当てる、1以上の独立してリフレッシュ可能なメモリ装置408a, 408b, 408c, ..., 408j(例えば行)に割り当てられたメモリを位置づけ、また、現在IRMU408a, 408b, 408c, ..., 408jの中のデータのステータスを反映する、対応するIRMU有効インジケータ410a, 410b, 410c, ..., 410jをセットしクリアする。1つの実施形態では、実際のメモリコントローラは独立したハードウェア要素404であり、別の実施形態では、メモリコントローラ機能はプロセッサ402へ統合される。SDRAMコンポーネント406は、無効データを含んでいるIRMU408a, 408b, 408c, ..., 408jに向けられたリフレッシュ操作をすべて抑える。

40

50

## 【0023】

図5は、メモリ割当てを制御して、SDRAM電力消費を最小化するマルチプロセッサシステム500を描く。プロセッサ502, 504はシステムバス506を通って互いおよびメモリコントローラハードウェア508と通信する。既に知られているように、バス506も、スイッチング構成(fabric)、クロスバースイッチなどとして実施されるかもしれない。1つ以上のソフトウェアタスク503, 516, 518は、プロセッサ502, 504上で実行する。システム全体のソフトウェアメモリマネージャ520は、システムで実行するすべてのソフトウェアタスク503, 516, 518間でメモリを割り当てて、1つのプロセッサ504上で実行する。プロセッサ502上で実行するいくつかのソフトウェアタスク503は、メモリ割り当て、バス506を通ったソフトウェアメモリマネージャ520へのフリーリクエストを送るかもしれない。上に述べられたように、ソフトウェアメモリマネージャ520は、タスク503, 516, 518間にメモリを割り当て、1以上の独立してリフレッシュ可能なメモリ装置512a, 512b, 512c, ..., 512jに割り当てられたメモリを位置づけ、また、IRMU514a, 514b, 514c, ..., 512jに現在保存されたデータのステータスを反映するメモリコントローラハードウェア508による対応するIRMU有効インジケータ514a, 514b, 514c, ..., 514jをセットしクリアする。SDRAMコンポーネント510は、無効データを含んでいるIRMU512a, 512b, 512c, ..., 512jに向けられたリフレッシュ操作を抑える。

10

## 【0024】

20

従来のリフレッシュモード、オートリフレッシュモードあるいはセルフリフレッシュモードでは、SDRAMコンポーネント300, 406, 510はリフレッシュアドレス(メモリコントローラまたは内部カウンタによって供給された)をIRMU有効メモリ342, 410, 514と比較し、有効データを含んでいないIRMU408, 512に向けられたリフレッシュ操作を抑える。1つの実施形態では、ソフトウェアメモリマネージャ416, 520は活発にメモリを管理し、IRMU有効ビット410, 514をセットする又はクリアし、システムはメモリリフレッシュをさらに最適化するかもしれない、物理メモリが割り当てからソフトウェアタスクまで開放されて“pool,”に返されるとともに、IRMUへのリフレッシュコマンドをダイナミックに抑えることにより、電力消費を最小化し、その場合には、そのデータ内容は適切ではない。

30

## 【0025】

30

従来のリフレッシュモードでは、ソフトウェアメモリマネージャ416, 520は、有効データを含んでいるIRMU408, 512にのみにリフレッシュアドレスを提供するかもしれない。オートリフレッシュあるいはセルフリフレッシュモードでは、SDRAMコンポーネント300, 406, 510は、各リフレッシュ操作に続いて、有効データを含んでいる次のIRMU408, 512への、そのリフレッシュアドレスカウンタをインクリメントすることにより、無効のメモリを“スキップ”するかもしれない。いずれの場合も、メモリコントローラ404, 508は、リフレッシュ操作間の遅れを増加させるかもしれない、それは、有効データを含んでいるIRMU408, 512だけが最大のリフレッシュ周期ですべてリフレッシュされるほどのものである。この実施形態では、リフレッシュコマンドはSDRAMコンポーネント300, 406, 510によって抑えられない。これは、不必要的メモリコマンドサイクルの回避により、電力消費をさらに最適化し(さらにバス輻輳を減らす)、また、進行中のメモリアクセスに乘じる遅れリフレッシュコマンドを減らす。

40

## 【0026】

図6は、1つ以上の実施形態によるリフレッシュするDRAMの方法600を描く。初期設定に際して、すべてのIRMUインジケータはクリアされる(ブロック602)。その後、その方法は、リフレッシュ操作が行なわれることになっているかどうかチェックする(ブロック604)。従来のリフレッシュモードでは、リフレッシュ操作は、メモリコントローラからのDRAMコンポーネントへ送られる制御信号によって示され、また、リ

50

フレッシュされるIRMUはアドレスバス上で示される。オートリフレッシュモードでは、リフレッシュ操作はメモリコントローラによって命令され、また、内部カウンタはIRMUリフレッシュアドレスを提供する。セルフリフレッシュモードでは、リフレッシュタイマーの終了は、リフレッシュ操作が必要であることを示し、また、内部カウンタはIRMUアドレスを提供する。

#### 【0027】

リフレッシュ操作が示される場合(ブロック604)、現在のIRMUアドレス(例えば行アドレスのような)に関連したIRMUインジケータは検査される(ブロック606)。IRMUが有効データを含むことをIRMUインジケータが示す場合(ブロック608)、リフレッシュ操作はアドレス指定されたIRMU上で行なわれる(ブロック610)。IRMUが有効データを含まないことをIRMUインジケータが示す場合(ブロック608)、リフレッシュ操作は、無効の(あるいは、“don't care”)データのリフレッシュにより、さもなければ消費されると推測される電力を節約することで抑えられる。

#### 【0028】

セルフリフレッシュモードでは、SDRAMコンポーネントはリフレッシュアドレスカウンタの次の終了に関してブロック604で待機する。他のリフレッシュモード中で、リフレッシュ操作が命令されない場合(ブロック604)、DRAM(あるいはSDRAM)コンポーネントは、またはメモリコントローラによって命令されるような、読み、書き、および/又はレジスタアクセス操作を実行する(ブロック612)。1つの実施形態で、メモリ管理ソフトウェアモジュールがメモリブロックを割り付け、開放する場合には、メモリあるいはレジスタアクセス操作が、IRMUインジケータを読み、セットし、クリアするIRMUメモリに向けられた動作を含むかもしれない。1つの実施形態では、IRMUインジケータは、関連するIRMUに向けられた書き込み操作で自動的にセットされる(ブロック614)。この実施形態では、IRMUインジケータは初期設定で単にクリアされ(ブロック602)、しかし有効データが多くのIRMUに少なくとも一度書き込まれるまで著しい省電力を提供するかもしれない。

#### 【0029】

[0032] DRAMアレイの物理的なリフレッシュ操作に、メモリ管理のソフトウェアパラダイム(paradigm)(ここで、メモリは、タスクに割り付けられて、割り付けより前に又は開放された後に“don't care”状態を仮定する場合に単に該当する)を適用することによって、著しい省電力は、有効データを保持しないメモリのセグメントに向けられた不要なリフレッシュ操作を除くことにより実現されるかもしれない。1つの実施形態では、有効データのトラッキングは、関連するIRMUビットのセットによって、自動的である。この実施形態では、本発明の省電力の利点は、選択的にリフレッシュ操作を抑える能力のソフトウェアメモリ管理か知識のないシステムにおいて有効である。他の実施形態では、IRMUメモリの直接制御は、精巧なメモリ管理および最大電力節約を考慮に入る。

#### 【0030】

ここに使用されるように、用語“独立してリフレッシュ可能なメモリ装置”すなわちIRMUは単一のリフレッシュ操作でリフレッシュされるデータの量を参照する。本発明はそのように制限されていないが、DRAMアレイのためのIRMUは典型的に行である。ここに使用されるように、用語“セット”は、データ(例えば0、または1、マルチビットパターン)の値にかかわらず、有効データが関連するIRMUに記憶されることを示すためにIRMUインジケータにデータを書き込むことを参照する。“クリア”は、データ(例えば0、または1、マルチビットパターン)の値にかかわらず、有効データが関連するIRMUに記憶されないことを示すためにIRMUインジケータにデータを書き込むことを指す。ここに使用されるように、“DRAMアレイ”はダイナミックランダムアクセスメモリアレイを参照し、それはDRAMおよびSDRAM集積回路コンポーネントの両方にデータを記憶する。ここに使用されるように、用語“DRAM”だけ、あるいは“DRAMコンポーネント”的範囲は、同期DRAMメモリコンポーネントおよびSDRAMコンポーネントの両方を含む。ここに使用されるように、用語“allocate”はソフ

10

20

30

40

50

トウェアタスクに一連のメモリアドレスを割り当てる参考を参照し、また、用語“free”は割り当てを解除されたメモリのプール(pool)に、前に割り当てられたメモリアドレスを返す参考を参照する。

【0031】

本発明は、その具体的特徴、局面および実施形態についてここに記述されたが、多数の変形、改良および他の実施形態が本発明の広い範囲内で可能であることは明白であろうし、また、従って、全ての変形、改良および実施例は本発明の範囲内にみなされることである。したがって、現在の実施形態は、実例となり、限定的でないものとして、すべての局面の中で解釈されることであり、また、追加された請求項の意味および同等の範囲内に来る全ての変更は、そこに包含されるように意図される。

10

【図1】

【図2】

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/US2008/071153            |

|                                     |

|-------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER |

| INV. G11C11/406                     |

According to International Patent Classification (IPC) or to both national classification and IPC

|                    |

|--------------------|

| B. FIELDS SEARCHED |

|--------------------|

Minimum documentation searched (classification system followed by classification symbols)

G06F G11C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

|                                        |

|----------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT |

|----------------------------------------|

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                        | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2003/023825 A1 (WOO STEVEN C [US] ET AL) 30 January 2003 (2003-01-30)<br>paragraphs [0047] - [0056]; figures 3,4                                                                       | 1-17,<br>19-30<br>18  |

| X         | US 2002/191467 A1 (MATSUMOTO JUNKO [JP] ET AL) 19 December 2002 (2002-12-19)<br>paragraphs [0101] - [0121], [0176] - [0183]; claims 1-4; figures 1-6,22,24                                | 1,19,26<br>18         |

| X         | US 2003/217246 A1 (KUBOTA KENICHI [JP] ET AL) 20 November 2003 (2003-11-20)<br>paragraphs [0013], [0025] - [0027], [0048] - [0055], [0059] - [0061], [0066] - [0075], [0080]; figures 3,4 | 1,19,26               |

|           |                                                                                                                                                                                           | -/-                   |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the international filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

\*&\* document member of the same patent family

|                                                                                                                                                                      |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search                                                                                                            | Date of mailing of the international search report |

| 24 October 2008                                                                                                                                                      | 12/11/2008                                         |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Stocken, Christian       |

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2008/071153

| C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                        |                       |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category*                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                                     | Relevant to claim No. |

| X                                                    | US 2004/093461 A1 (KIM TAE YUN [KR])<br>13 May 2004 (2004-05-13)<br>paragraphs [0022] - [0037], [0055] -<br>[0068]; figures 1,3,5                      | 1,19,26               |

| X                                                    | US 2006/133173 A1 (JAIN SANDEEP K [US] ET<br>AL) 22 June 2006 (2006-06-22)<br>paragraphs [0004], [0005], [0017] -<br>[0020], [0026] - [0029]; figure 1 | 1,19,26               |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2008/071153

| Patent document cited in search report |    | Publication date |                            | Patent family member(s)                                               |  | Publication date                                                   |

|----------------------------------------|----|------------------|----------------------------|-----------------------------------------------------------------------|--|--------------------------------------------------------------------|

| US 2003023825                          | A1 | 30-01-2003       | US                         | 2004193829 A1                                                         |  | 30-09-2004                                                         |

| US 2002191467                          | A1 | 19-12-2002       | CN<br>DE<br>JP<br>KR<br>TW | 1392565 A<br>10221651 A1<br>2002373489 A<br>20030009125 A<br>224337 B |  | 22-01-2003<br>02-01-2003<br>26-12-2002<br>29-01-2003<br>21-11-2004 |

| US 2003217246                          | A1 | 20-11-2003       | EP                         | 1408510 A2                                                            |  | 14-04-2004                                                         |

| US 2004093461                          | A1 | 13-05-2004       | KR                         | 20040040579 A                                                         |  | 13-05-2004                                                         |

| US 2006133173                          | A1 | 22-06-2006       | JP<br>KR<br>US<br>WO       | 2008524774 T<br>20070086472 A<br>2008056047 A1<br>2006069356 A2       |  | 10-07-2008<br>27-08-2007<br>06-03-2008<br>29-06-2006               |

## フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MT,NL,NO,PL,PT,RO,SE,SI,SK,T

R),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,

BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,K

G,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT

,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 ミカラック、ジェラルド・ポール

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 ウォルフォード、バリー・ジョー

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

F ターム(参考) 5B060 AA02 AA14

5M024 AA15 BB22 BB39 EE05 EE09 EE17 EE24 LL01 PP01