(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7584512号

(P7584512)

(45)発行日 令和6年11月15日(2024.11.15)

(24)登録日 令和6年11月7日(2024.11.7)

(51)国際特許分類

H 04 L 25/03 (2006.01)

F I

H 04 L 25/03

C

H 04 L 27/01 (2006.01)

H 04 L 27/01

H 04 B 3/06 (2006.01)

H 04 B 3/06

C

請求項の数 18 (全22頁)

(21)出願番号 特願2022-523803(P2022-523803)

(86)(22)出願日 令和2年9月29日(2020.9.29)

(65)公表番号 特表2023-501908(P2023-501908

A)

(43)公表日 令和5年1月20日(2023.1.20)

(86)国際出願番号 PCT/IB2020/059102

(87)国際公開番号 WO2021/084341

(87)国際公開日 令和3年5月6日(2021.5.6)

審査請求日 令和5年2月24日(2023.2.24)

(31)優先権主張番号 16/667,872

(32)優先日 令和1年10月29日(2019.10.29)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 390009531

インターナショナル・ビジネス・マシ

ンズ・コーポレーション

INTERNATIONAL BUSI

NESS MACHINES CORPO

RATION

アメリカ合衆国 10504 ニューヨー

ク州 アーモンク ニュー オーチャード

ロード

New Orchard Road, A

rmonk, New York 105

04, United States of

America

(74)代理人 100112690

弁理士 太佐 種一

最終頁に続く

(54)【発明の名称】 データ伝送システムのための時間依存ライン等化器

## (57)【特許請求の範囲】

## 【請求項1】

クロック信号を受け取るように構成されたデータ・クロック入力部と、

前記クロック信号と同期して状態を変化させる传送シンボルのデータ信号を受け取るよ

うに動作する入力ノードと、

前記入力ノードに結合された第1のタップと、

前記データ信号のバリエーションを受け取るように構成された第2のタップであって、

前記第1のタップの重みまたは前記第2のタップの重みの少なくとも一方が、各传送シン

ボルと同期して繰り返す動的制御パラメータによって調整される、前記第2のタップと

を含み、

前記第1および第2のタップが、複数のタップの一部であり、

前記複数のタップのうちの少なくとも1つが、各传送シンボルにより静的に制御される

タップ重みを有する、

データ等化システム。

## 【請求項2】

前記データ信号の前記バリエーションが前記データ信号の時間遅延である、請求項1に

記載のデータ等化システム。

## 【請求項3】

前記動的制御パラメータが、前記传送シンボルの入力時間シーケンスの時間依存関数変

換を提供する、請求項1に記載のデータ等化システム。

**【請求項 4】**

前記データ等化システムがフィード・フォワード等化器（FFE）である、請求項1に記載のデータ等化システム。

**【請求項 5】**

前記データ等化システムが送信器回路の一部である、請求項1に記載のデータ等化システム。

**【請求項 6】**

前記データ等化システムが受信器回路の一部である、請求項1に記載のデータ等化システム。

**【請求項 7】**

前記動的制御パラメータが時間の軸について直線傾斜である、請求項1に記載のデータ等化システム。

10

**【請求項 8】**

前記動的制御パラメータが時間の変数について非線形関数である、請求項1に記載のデータ等化システム。

**【請求項 9】**

前記第1のタップが、各传送シンボルに対して一定であるタップ重みを有するプレカーソル・タップであり、

前記第2のタップが、前記動的制御パラメータによって調整されるタップ重みを有する第1のポストカーソル・タップである、

請求項1に記載のデータ等化システム。

20

**【請求項 10】**

等化の方法であって、前記方法が、

第1のタップおよび第2のタップを有する等化システムを用意することと、

データ・クロックを受け取ることと、

前記データ・クロックと同期して状態を変化させる传送シンボルのデータ入力を受け取ることと、

前記データ・クロックの各传送シンボルと同期して繰り返す動的制御パラメータにより前記第1のタップまたは前記第2のタップの少なくとも一方のタップ重みを調整することと、

30

前記等化システムにおけるすべてのタップの重みを合計することと、

前記システムにおける前記すべてのタップの合計された重みに基づいて出力データを提供することと

を含み、

前記第1および第2のタップが、複数のタップの一部であり、

前記複数のタップのうちの少なくとも1つが、各传送シンボルにより静的に制御されるタップ重みを有する、方法。

**【請求項 11】**

前記第2のタップが、前記データ入力の時間遅延バージョンを受け取る、請求項10に記載の方法。

40

**【請求項 12】**

前記動的制御パラメータが、前記传送シンボルの入力時間シーケンスの時間依存関数変換を提供する、請求項10に記載の方法。

**【請求項 13】**

前記等化システムがフィード・フォワード等化器（FFE）である、請求項10に記載の方法。

**【請求項 14】**

前記動的制御パラメータが時間の軸について直線傾斜である、請求項10に記載の方法。

**【請求項 15】**

50

前記動的制御パラメータが時間の変数について非線形関数である、請求項 10 に記載の方法。

【請求項 16】

各伝送シンボルに対して前記第 1 のタップの重みを一定に保持することと、前記第 2 のタップの重みを前記動的制御パラメータにより調整することとをさらに含む、請求項 10 に記載の方法。

【請求項 17】

プロセッサと、ネットワークを介した通信を可能にするために前記プロセッサに結合されたネットワーク・インターフェースと、

前記プロセッサに結合され、請求項 10 ないし 16 のいずれか一項に記載の方法の動作を実行するように構成された等化エンジンとを含むコンピューティング・デバイス。

【請求項 18】

実行されたとき、請求項 10 ないし 16 のいずれか一項に記載の方法をコンピュータ・デバイスに実行させるコンピュータ可読命令を有するコンピュータ可読プログラム・コードを記憶するコンピュータ可読ストレージ媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、電気通信システムに関し、より詳細には、高速データ伝送システムにおける等化に関する。

【背景技術】

【0002】

ネットワーキングおよびコンピューティング・システムの最新の電気データ伝送システムは、一般に、チャネル時間分散およびその結果として生じるシンボル間干渉 ( ISI ) から生じる歪みを低減するための等化技術を使用する。既知のシステムでは、これらの等化技術は、一般に、送信器デバイスまたは受信器デバイスあるいはその両方でのフィード・フォワード等化 ( FFE ) の使用に基づき、システムによっては、受信器連続時間等化 ( CTE ) および判定帰還等化 ( DFE ) と組み合わされる。等化システムの目標には、受信器のデータ・サンプル時に可能な限り多くの ISIを取り除いて、回復可能なビット誤り率 ( BER ) を改善することが含まれる。最新のシステムのデータ・レートは 100 Gb / s 以上に上昇し続けているので、実際の実施態様で達成可能なクロック精度が、システム性能を著しく制限し始める可能性がある。これらの高データ・レートでは、完全な伝送シンボル期間は 20 ps 以下になる可能性がある。FFE / CTE / DFE の使用に基づく既知の等化システムは、この 20 ps 間隔内の 1 つの特定の時点に ISI を取り除いている。達成可能なクロック精度の事実上の制限のために、所与の受信器サンプルは、等化される特定の時点よりも遅くまたは早く等化信号をサンプリングする可能性があり、それにより、BER の劣化がもたらされ、最終的に、達成可能なクロック精度の事実上の制限に起因して達成可能な最大データ・レートが制限される。

【発明の概要】

【0003】

1 つの実施形態によれば、データ等化システムが提供される。データ・クロック入力部が、クロック信号を受け取るように構成される。クロック信号と同期して状態を変化させる伝送シンボルのデータ信号を受け取るように動作する入力ノードがある。第 1 のタップが、入力ノードに結合される。第 2 のタップが、データ信号のバリエーションを受け取るように構成される。第 1 のタップの重みまたは第 2 のタップの重みの少なくとも一方が、各伝送シンボルと同期して繰り返す制御パラメータによって動的に調整される。

【0004】

1 つの実施形態において、データ信号のバリエーションは、データ信号の時間遅延であ

10

20

30

40

50

る。

【0 0 0 5】

1つの実施形態において、動的制御パラメータは、伝送シンボルの入力時間シーケンスの時間依存関数変換 (time dependent functional transformation) を提供する。

【0 0 0 6】

1つの実施形態において、データ等化システムは、フィード・フォワード等化器 (FFE) である。

【0 0 0 7】

1つの実施形態において、データ等化システムは送信器回路の一部である。

【0 0 0 8】

1つの実施形態において、データ等化システムは受信器回路の一部である。

10

【0 0 0 9】

1つの実施形態において、動的制御パラメータは直線傾斜 (linear ramp) である。

【0 0 1 0】

1つの実施形態において、動的制御パラメータは非線形関数である。

【0 0 1 1】

1つの実施形態において、第1および第2のタップは、複数のタップの一部である。複数のタップのうちの少なくとも1つは、各伝送シンボルにより静的に制御されるタップ重みを有する。

【0 0 1 2】

1つの実施形態において、第1のタップは、各伝送シンボルに対して一定であるタップ重みを有するプレカーソル・タップ (precursor tap) である。第2のタップは、動的制御パラメータによって調整されるタップ重みを有する第1のポストカーソル・タップ (postcursor tap) である。

20

【0 0 1 3】

1つの実施形態において、動的制御パラメータは差動である。

【0 0 1 4】

様々な実施形態によれば、信号を等化するための方法、コンピューティング・デバイス、および非一過性コンピュータ可読ストレージ媒体が提供される。第1のタップおよび第2のタップを有する等化システムが提供される。データ・クロックが受け取られる。データ・クロックと同期して状態を変化させる伝送シンボルのデータ入力が受け取られる。第1のタップまたは第2のタップの少なくとも一方のタップ重みが、データ・クロックの各伝送シンボルと同期して繰り返す動的制御パラメータにより調整される。等化システムにおけるすべてのタップの重みが合計される。出力データが、システムにおけるすべてのタップの合計された重みに基づいて提供される。

30

【0 0 1 5】

1つの実施形態において、第2のタップが、データ入力の時間遅延バージョンを受け取る。

【0 0 1 6】

1つの実施形態において、動的制御パラメータが、伝送シンボルの入力時間シーケンス (input time sequence) の時間依存関数変換を提供する。

40

【0 0 1 7】

1つの実施形態において、データ等化システムは、フィード・フォワード等化器 (FFE) である。

【0 0 1 8】

1つの実施形態において、動的制御パラメータは直線傾斜である。

【0 0 1 9】

1つの実施形態において、動的制御パラメータは非線形関数である。

【0 0 2 0】

1つの実施形態において、第1および第2のタップは、複数のタップの一部であり、複

50

数のタップのうちの少なくとも 1 つは、各伝送シンボルにより静的に制御されるタップ重みを有する。

【 0 0 2 1 】

1 つの実施形態において、第 1 のタップの重みは、各伝送シンボルに対して一定に保持される。

【 0 0 2 2 】

1 つの実施形態において、第 2 のタップの重みが、動的制御パラメータにより調整される。

【 0 0 2 3 】

1 つの実施形態において、第 1 のタップまたは第 2 のタップの少なくとも一方の重みは、動的制御パラメータによって差動的に制御される。

【 0 0 2 4 】

本明細書で論じる特徴によって、長距離 ( 2 5 d B + 損失 ) チャネルを介した頑健な 1 0 0 G b / s 4 レベル・データ伝送が、H E Y E マージンを 3 倍まで改善することによって提供される。1 0 0 G b / s システムを含む様々な伝送システムが、より低いビット誤り率 ( B E R ) によりさらに確実に機能することができる。一般に、本明細書の教示は、静的等化器と比較して、H E Y E マージンを 2 倍、3 倍、またはそれを超えて向上させる。それに加えてさらに、通信システムのジッタ許容範囲 ( J T O L ) が改善されるとともに、システム・クロックのジッタへの要件が緩和される。

【 0 0 2 5 】

これらのおよび他の特徴は、添付の図面に関連して読むことができるその例示的な実施形態の以下の詳細な説明から明らかになるであろう。

【 0 0 2 6 】

図面は、例示的な実施形態のものである。それらは、すべての実施形態を示しているわけではない。他の実施形態が、加えてまたは代わりに使用されてもよい。明白であるかまたは不要である可能性がある詳細は、スペースを節約するために、またはより効果的な例証のために省略されることがある。いくつかの実施形態は、追加の構成要素またはステップを用いて、または図示された構成要素またはステップのすべてを用いずに、あるいはその両方で実践され得る。同じ数字が異なる図面に現われる場合、それは、同じまたは同様の構成要素またはステップを指す。

【 図面の簡単な説明 】

【 0 0 2 7 】

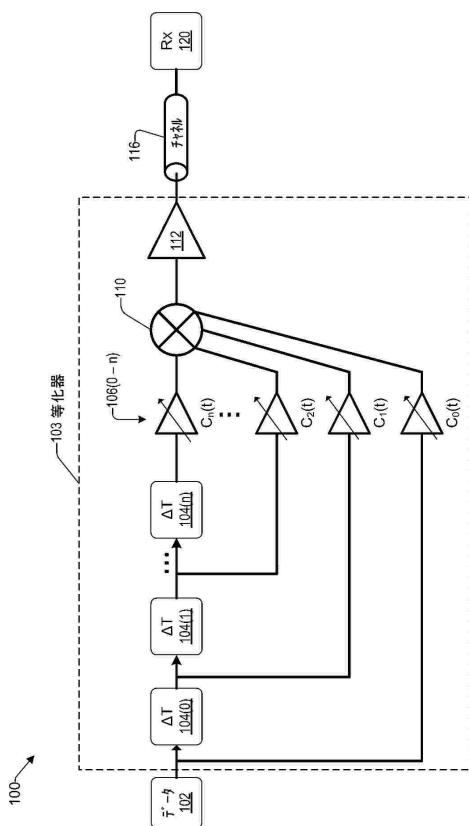

【 図 1 】一実施形態と一致する、データ伝送システムのブロック図である。

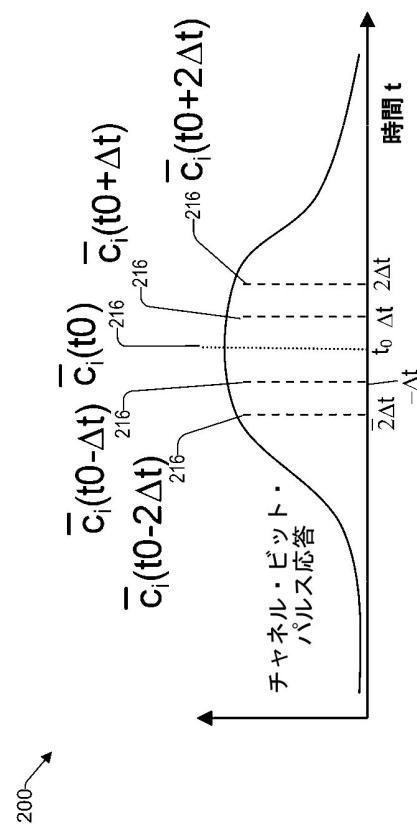

【 図 2 】図 1 のタップのうちの少なくとも 1 つの時変等化 ( time variant equalization ) の状況におけるチャネル・ビット・パルス応答を示す図である。

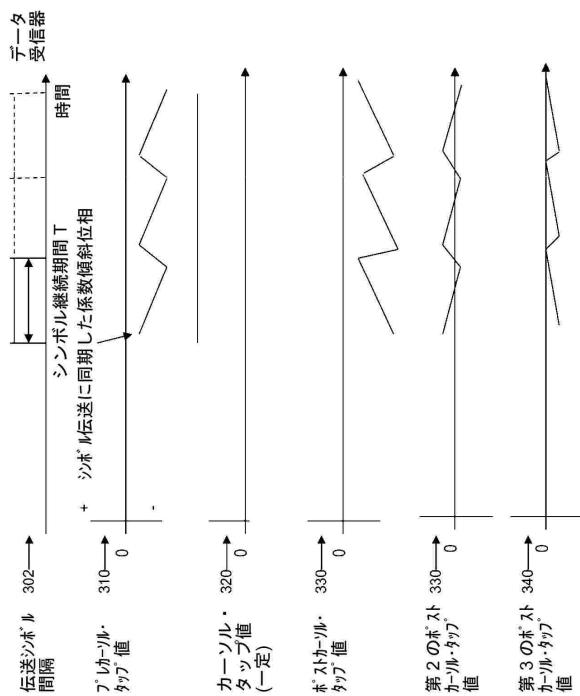

【 図 3 】異なるデータ・シンボルに対する異なるタップのタップ値の波形を示す図である。

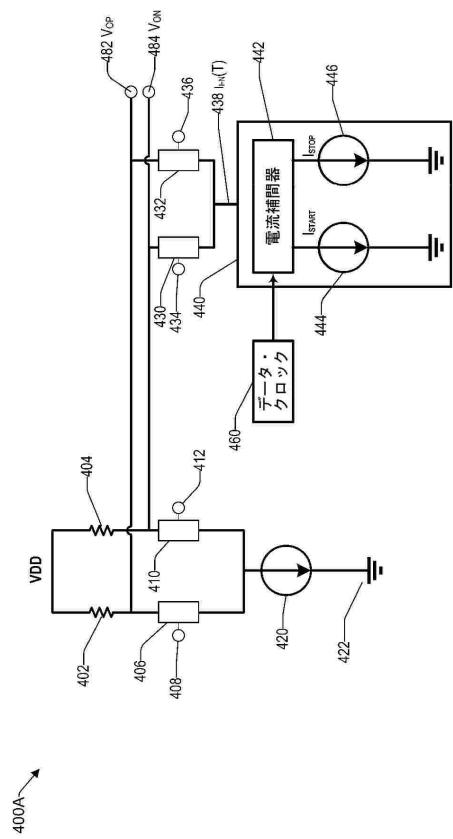

【 図 4 A 】電流モード論理を使用する例示のフィード・フォワード等化器回路を示す図である。

【 図 4 B 】一実施形態と一致する、C M O S 回路を使用する動的タップ重み発生器 ( dynamic tap weight generator ) のハードウェア実施態様を示す図である。

【 図 4 C 】図 4 B のタップ重み発生器回路の例示の波形を示す図である。

【 図 5 】異なるシンボルに対する異なるタップのタップ値の波形を示す図である。

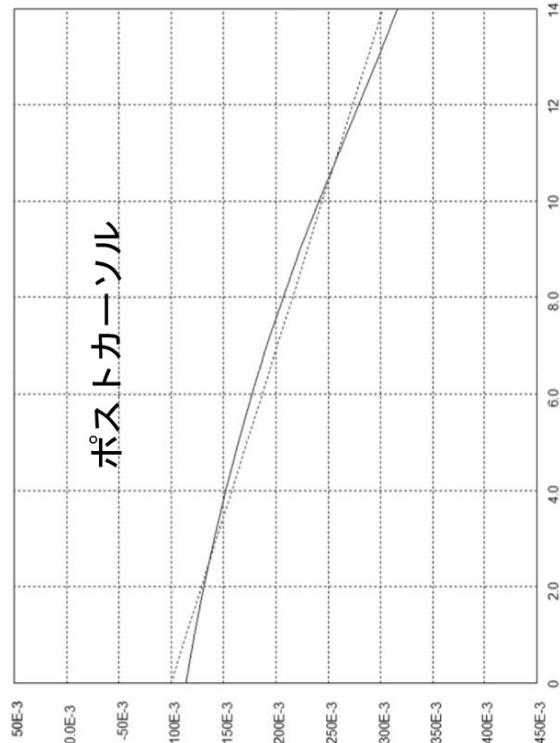

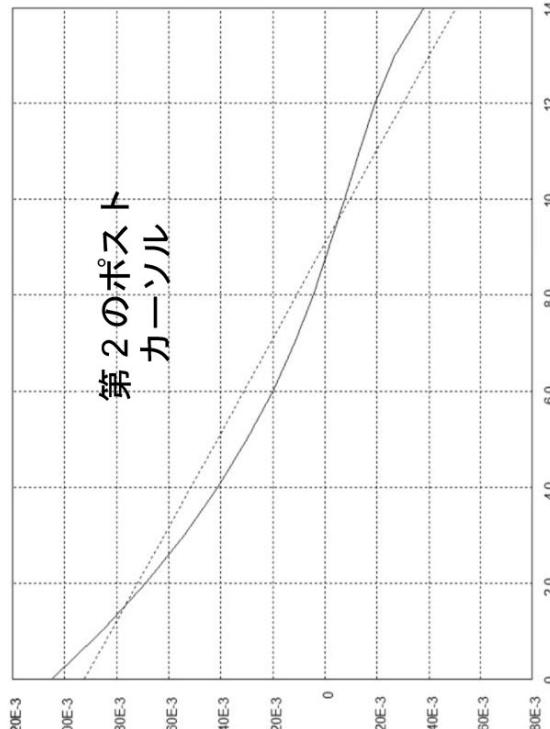

【 図 6 A 】例示の 5 タップ F F E のブレカーソルのタップ重みを示す図である。

【 図 6 B 】例示の 5 タップ F F E のポストカーソルのタップ重みを示す図である。

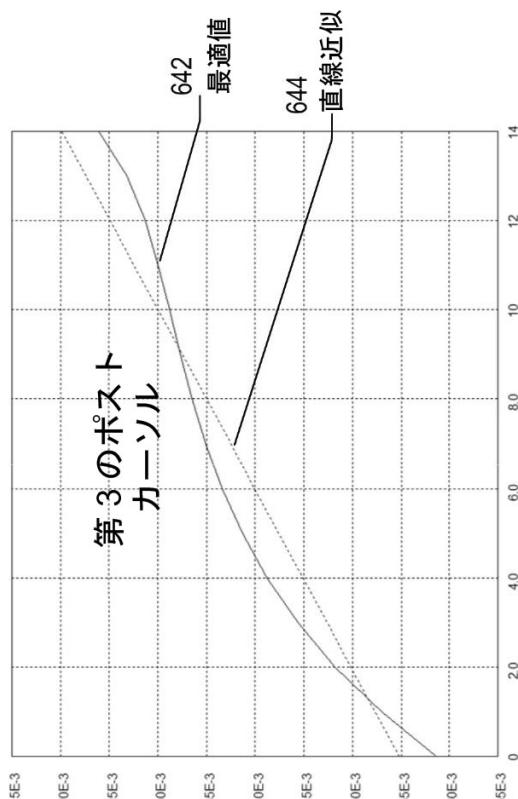

【 図 6 C 】例示の 5 タップ F F E の第 2 のポストカーソルのタップ重みを示す図である。

【 図 6 D 】例示の 5 タップ F F E の第 3 のポストカーソルのタップ重みを示す図である。

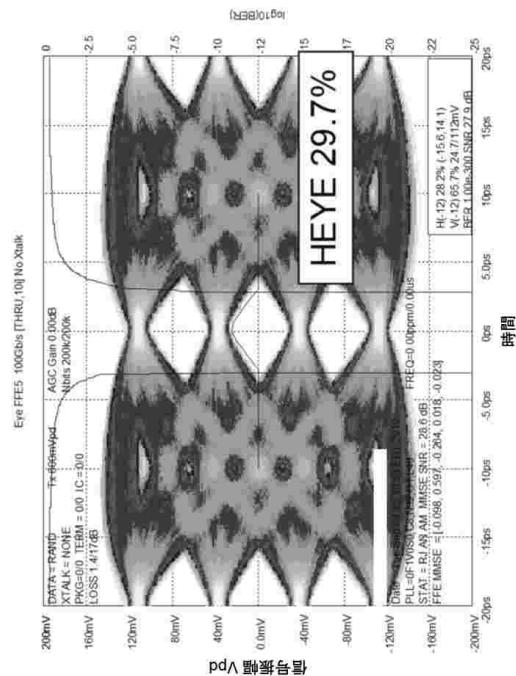

【 図 7 A 】タップ重みが固定された H E Y E マーキングを示す図である。

【 図 7 B 】一実施形態により達成された改善された H E Y E マージンを示す図である。

【 図 8 A 】タップ重みが固定された例示の時変フィード・フォワード・ライン等化器のアイ・ダイアグラムを示す図である。

10

20

30

40

50

【図 8 B】一実施形態と一致する、タップ重みが調整された例示の時変フィード・フォワード・ライン等化器のアイ・ダイアグラムを示す図である。

【図 9 A】タップ重みが固定された別の例示の時変フィード・フォワード・ライン等化器のアイ・ダイアグラムを示す図である。

【図 9 B】一実施形態と一致する、タップ重みが調整された、図 9 A で使用されたフィード・フォワード・ライン等化器のアイ・ダイアグラムを示す図である。

【図 10 A】タップ重みが固定されたさらなる別の例示の時変フィード・フォワード・ライン等化器のアイ・ダイアグラムを示す図である。

【図 10 B】例示の実施形態と一致する、タップ重みが調整された、図 10 A で使用されたフィード・フォワード・ライン等化器のアイ・ダイアグラムを示す図である。

【図 11】一実施形態と一致する、データ信号の等化を実行するためのプロセスを提示する図である。

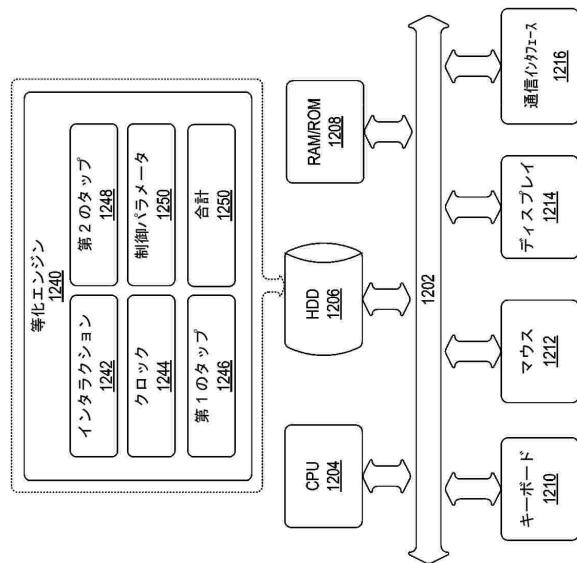

【図 12】様々なネットワーク化構成要素と通信することができるコンピュータ・ハードウェア・プラットホームのブロック図である。

【発明を実施するための形態】

【0028】

概要

以下の詳細な説明において、多数の特定の詳細が、関連する教示の完全な理解を提供するために例として記載される。しかしながら、本教示はそのような詳細なしに実践することができる事が当業者には明らかであろう。他の例では、よく知られている方法、手順、構成要素、または回路、あるいはその組合せは、本教示の態様を必要に不明瞭にしないために、詳細なしに比較的高レベルで説明されている。

【0029】

本明細書で使用される等化は、チャネルを通して伝送される信号によって引き起こされる歪みの除去のことを言う。本明細書の教示は、時間依存等化に基づく強化された等化システムおよび方法を提供し、等化の時間依存は、等化器が各伝送シンボルの伝送間隔の全体にわたって等化の変更を適用できるように、データ伝送間隔と同期される。本明細書で論じる等化アーキテクチャによって、I S I は、シンボル伝送期間の継続期間の間名目上一定であるタップ重みを使用する既知のフィード・フォワード等化 ( F F E ) 技術と比較して、シンボル伝送期間内に広い時間スパンにわたって低下する。その結果として、これにより、データ伝送システムは、一般に避けられないシステム・クロックのジッタの存在下で、より低い B E R で動作することができる。現在の議論を容易にするために、フィード・フォワード等化 F F E アーキテクチャが、限定としてではなく、単に例として、説明される。

【0030】

例示のアーキテクチャ

図 1 を参照すると、データ伝送システム 100 は、データ・ソース 102、等化器 103、送信チャネル 116、およびデータ受信器 120 を含む。1 つの実施形態では、等化器 103 は、伝送シンボル・シーケンスの時間遅延値の加重合計を作り出すトランスパーサル F F E である。等化器 103 は、データ・ソース 102 によって提供されるデータ信号の異なる段階に結合される複数のタップ 106 ( 0 ) から 106 ( n ) を含む。例えば、データ・ソース 102 は、クロック信号 ( 図示せず ) と同期して状態を変化させる伝送シンボルを供給するように動作する。その信号は、信号調整要素 104 ( 0 ) から 104 ( n ) によって異なる段階で調整される。1 つの実施形態では、信号調整要素は、受け取った信号を各々対応する期間だけ遅延させるように動作する遅延要素である。

【0031】

データ・ソース 102 からのデータは、( 限定しないが ) N R Z ( 非ゼロ復帰 )、4 - P A M ( パルス振幅変調 )、8 - P A M、または 32 - Q A M ( 直交振幅変調 ) などの様々な様々な技術を使用して、伝送シンボル上に符号化することができ、ここで、数字は、情報を搬送するために使用されるコンステレーション・ポイントの別個の数を示す。合計

10

20

30

40

50

ノード 110 は、タップ 106(0) から 106(n) のすべてを受け取り、出力をバッファ 112 に供給するように動作する。1 つの実施形態では、電流モード論理を使用して、異なるタップ 106(0) から 106(n) の出力部の電流を合計する。代替として、他の既知の合計回路を使用して、異なる経路の信号の合計を実行することができる。

#### 【0032】

重要なことには、トランスバーサル等化器 103 によって作り出される加重合計の重みのうちの 1 つまたは複数は、より広い時間スパンにわたる改善された等化を遂行するために、シンボル伝送間隔内で変化させることができる。概念的には、重みの変化は、図 1 に示されるように、端から端までのチャネル応答からのタップ重みに由来することが分かる。別の言い方をすれば、一定である（すなわち、シンボル伝送間隔中に変化しない）タップ重みを有する従来の FFE と異なり、タップ 106(0) から 106(n) のうちの少なくとも 1 つが、各传送シンボルと同期して繰り返す動的制御パラメータによって調整される。したがって、既知の FFE タップ重み決定方法は、端から端までのチャネル応答の時点  $t_0$  で FFE タップ重みを見いだすことができるが、一方、本明細書の教示は、クロック・サイクル中時間とともに動的に変化することができる少なくとも 1 つのタップ重みを用意する。この概念は、以下の議論を考慮してよりよく理解することができる。

#### 【0033】

次に、図 1 のタップ 160(0) から 160(n) のうちの少なくとも 1 つの時間依存等化の状況におけるチャネル・ビット・パルス応答 200 を示す図 2 を参照する。より広い時間間隔にわたって等化を達成するために適切なタップ重み変化を決定するのに、タップ重みを特定のタップ重みに固定する代わりに、名目上の  $t_0$  等化点の近くの時間 ( $t_0 - 2t, t_0 - t, t_0, t_0 + t, t_0 + 2t$  など) を考慮することができ、ここで、 $t$  は、シンボル伝送間隔の期間内の（例えば、任意の）小さい時間ステップである。これらの時間の各々において、等化 FFE 係数  $c_i$  の新しいセットが見いだされる。次いで、改善された等化が、時間依存係数重みを FFE に適用することによって達成され、時間依存係数重みは、計算されたタップ重みを時間経過とともに経る。1 つの実施形態では、時間依存等化器の実際の実現を簡単にするために、時間の関数としての係数タップ重みの変化を、ビット・パルス応答 200 に示されるような最適値を通過する直線傾斜で近似することができる。そのような実施形態において、FFE の 1 つまたは複数のタップは 2 つのパラメータ、すなわち、( $i$ ) タップ重みおよび ( $i i$ ) タップ傾斜値もしくは変化率、または代わりに ( $i$ ) 開始タップ重みおよび ( $i i$ ) 停止タップ重みにより構成することができる。各传送シンボルと同期して繰り返すタップ重みの調整の概念は、以下で論じるタイミング図の例示の波形を考慮してよりよく理解することができる。

#### 【0034】

##### 例示のタイミング図

次に、異なるデータ・シンボルに対する異なるタップのタップ値の波形を示す図 3 を参照する。限定としてではなく、単に例として、図 3 は、例示のチャネルに対して、5 タップ FFE のタップ重みが、時間とともにどのように変化するかを示しており、ここで、タップ重みプロットの x 軸は、シンボル伝送間隔の 1/32 の時間増分に対応する単位で与えられる。本議論を容易にするために、図 3 の例では、タップ重みの線形変化率近似が使用されるが、任意の他の関数が本明細書の教示によって同様にサポートされることが理解されるであろう。波形 302 は、传送シンボル間隔を示す。時には本明細書においてタップ重みと呼ばれるタップ値は、传送シンボル間隔と同期する。例えば、プレカーソル・タップ値の波形 310 は、传送シンボル 302 と同期した係数傾斜位相を有する。この係数傾斜位相 310 は、传送シンボル 302 と同期して繰り返すタップの動的制御パラメータである。いくつかの実施形態では、動的制御パラメータは、传送シンボル 302 間で変化する。

#### 【0035】

すべてのタップが動的制御パラメータに従う必要があるとは限らないことに留意されたい。様々な実施形態において、1 つまたは複数のタップは動的制御パラメータを有するこ

とができる、一方、残りのタップは、シンボル伝送間隔を通して静的または一定である。これに関して、例として、図3は、各传送シンボルに対して一定であるカーソル・タップ値320を示す。このように、図3の例のFFEカーソル・タップ320は固定されているが、プレカーソル310、ポストカーソル330、第2のポストカーソル330、および第3のポストカーソル340のタップ値は、データ传送間隔302と時間的に同期して調整される。このようにして、より広い時間間隔にわたって改善された ISI補償が達成される。

#### 【0036】

##### 例示の回路図

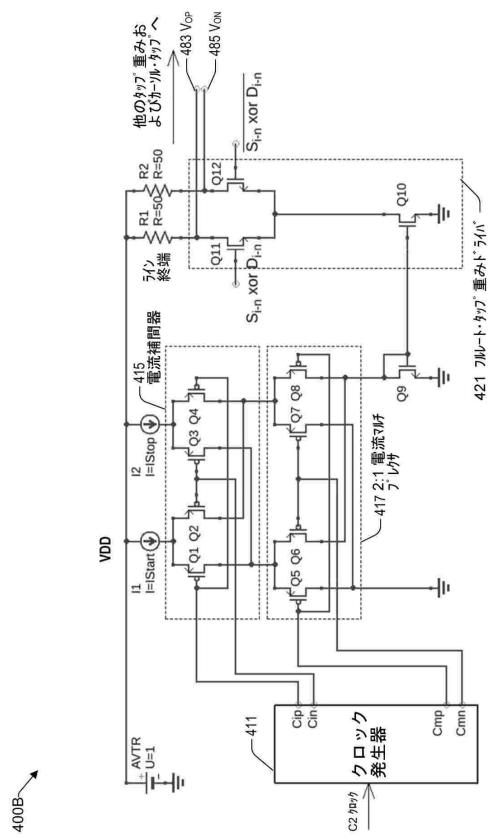

等化システムの理論的な動作および波形の前述の説明とともに、図1の等化器を実現するために使用できる例示の回路図を説明することは有用であり得る。これに関して、図4Aは、例示の実施形態と一致する、電流モード論理を使用する例示のFFE等化器回路400を示す。回路400は、抵抗器とすることができる差動負荷402および404を含み、各々は、本例ではVDDである第1の基準ノードに結合された第1のノードを有する。図4の例では、2つのタップがあり、第1のタップは、電流源420に結合された差動トランジスタ406および410によって表され、第2のタップは、同期時間依存タップ発生器440に結合された差動トランジスタ430および432によって表される。

10

#### 【0037】

様々な実施形態において、トランジスタ406、410、430、および432は、nチャネル電界効果トランジスタ(NFET)またはpチャネル電界効果トランジスタ(PFET)あるいはその両方などの相補型金属酸化膜半導体(CMOS)技術に基づくことができる。いくつかの実施形態では、バイポーラ・トランジスタ(例えば、PNPまたはNPN)が、MOSトランジスタの代わりに使用されてもよい。トランジスタ対406および410は、電流源420に結合された共通エミッタ(またはソース)を有する。電流源は、接地422とすることができる第2の基準ノードに結合される。例えば、第1のトランジスタ対406および410の入力部は、それぞれ、データ信号を差動的に受け取るように動作する制御入力部408および412を(例えば、ゲート入力部またはベース入力部)有する。例えば、入力部408は、データ信号D1を受け取ることができ、一方、入力部412は、その補完(例えば、

20

#### 【数1】

30

D1

)を受け取る。1つの実施形態では、非ゼロ復帰(NRZ)シグナリングが使用される。図4Aの例では、第1のタップは定電流源420を有する。別の言い方をすれば、タップ重みの大きさは、传送シンボルの間時間とともに変化しない。入力部434および436は、データ履歴およびタップ符号に応じて、適用されるタップ重みの極性を制御する。

#### 【0038】

固定重みカーソル・タップは、データ・シンボル符号に基づく固定電流420を出力負荷402および404に切り替えることによって形成され、それによって、VOP482およびVON484により差動的に表される伝送出力信号Voが形成される。1つの実施形態では、インデクス「i」をもつカーソル・タップの固定重みは、インデクス「i」のデータ(Si)の符号によって切り替えられた固定重み電流を電流合計することにより形成される。

40

#### 【0039】

対照的に、第2のタップは、一定であるタップ重みを提供しない。むしろ、それは、各传送シンボルの全体にわたってタップ重みを変化させることができる。その目的のために、1つの実施形態では、同期時間依存タップ重み発生器440は、クロック・サイクル中の異なる時点に選択することができる複数の電流源に結合された電流補間器442を有することができる。例えば、第1の電流源(START)444および第2の電流源(INS

50

$T_{OP}$ ) 446 があり得る。その結果、差動出力  $V_{OP482}$  および  $V_{ON484}$  の合計に、同期時間依存タップ重み発生器を使用する少なくとも 1 つの所与のタップ・インデクス「i」を有する可変重み電流が供給される。1 つの実施形態では、同期動的タップ重み発生器 440 は、シンボル伝送間隔にわたって電流  $I_{START444}$  から電流  $I_{STOP446}$  に向かって補間することができる電流補間器 442 を使用して実現され、ここで、 $I_{START444}$  および  $I_{STOP446}$  の値は、適応等化制御システムなどの他のシステムによってプログラム的に事前構成されるかまたは自動的に適合されてもよく、少なくとも 2 つのタップ設定パラメータ（例えば、 $I_{start}$  および  $I_{stop}$ ）を制御して、より広い時間スパンにわたってシンボル間干渉を最小にする新しい能力が与えられる。

#### 【0040】

図 4B は、限定としてではなく、単に例として、CMOS 回路を使用する動的タップ重み発生器のハードウェア実施態様を示す。1 つの実施形態では、ハーフレートまたは C2 のクロックが、クロック発生器ブロック 460 を駆動する。クロック発生器は、2 つの差動出力クロック  $C_{i1}$ （または補間器クロック）および  $C_m$ （またはマルチプレクサ・クロック）を作る。1 つの実施形態では、同期時間依存タップ重み発生器 440 は、シンボル伝送間隔にわたって開始電流および停止電流の値を制御することによって傾斜勾配と傾斜オフセットの両方を構成できるようにする設定パラメータに応答する。

#### 【0041】

例えば、カーソル・タップから取り除かれた単位シンボル間隔において、FFE 回路 400A は、FFE タップの符号にデータ（NRZ 伝送の）の符号を乗じたものに基づいて、FFE タップ電流 420 を出力信号  $V_{OP} / V_{ON}$  (482, 484) に切り替える。FFE 回路 400A は、同期動的タップ重み発生器 440 を使用することによって第 2 の FFE タップの電流を動的に変化させる。同期動的タップ重み発生器 440 は、シンボル伝送間隔およびプログラム制御に関連する入力クロック 460 に応答し、これにより、開始電流  $I_{START444}$  および停止電流  $I_{STOP446}$  の構成が可能になる。1 つの実施形態では、各データ伝送間隔を通して、タップ重み電流は、名目上、 $I_{START444}$  の値で始まり、シンボル伝送間隔の終了の  $I_{STOP446}$  の値に向かって傾斜し、それにより、適用される等化の所望の変化が時間の関数として提供される。同期動的タップ重み発生器 440 は、少なくとも 1 つのシステム・クロックに応答して、動的タップ重み発生器 440 がデータ伝送間隔に同期した電流傾斜 438 を作ることを可能にする。図 4A は、差動アーキテクチャを有する例として回路 400 を説明しているが、シングル・エンド手法が、本明細書の教示によって同様にサポートされることが理解されるであろう。

#### 【0042】

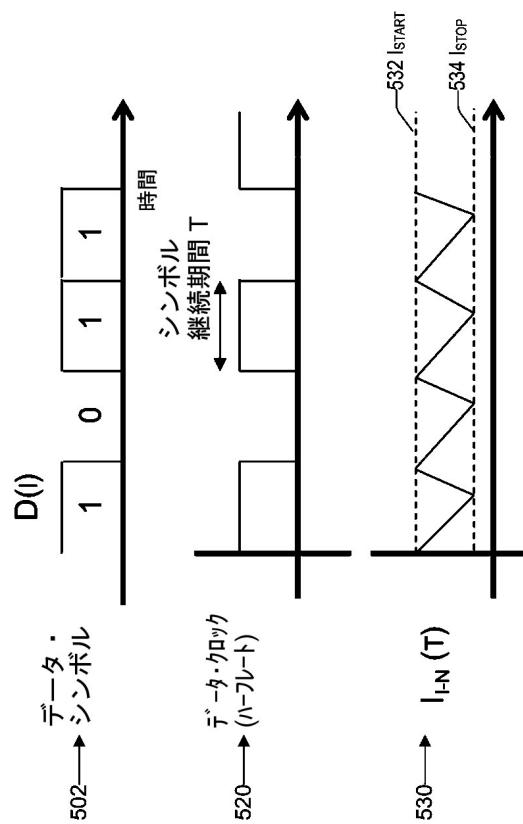

図 4A の回路図は、例示の波形を考慮してよりよく理解することができる。その目的のために、図 5 は、異なるシンボルに対する異なるタップのタップ値の波形を示す。2 進値「0」および「1」によって表されるデータ・シンボルが、波形 502 によって示される。波形 520 は、データ・シンボル 502 が同期するデータ・クロックを表す。図 4A のノード 438 の動的タップ重み電流は、 $I_{START}$  と  $I_{STOP}$  との間で変化し、データ・クロック 520 と同期する。1 つの実施形態では、タップ電流は、直線傾斜  $I_{START532}$  および  $I_{STOP534}$  である。

#### 【0043】

次に、例示的な実施形態と一致する、動的タップ重み発生器回路 400B を示す図 4B を参照する。限定としてではなく、単に例として、回路 400B は、CMOS 技術を使用して示される。タップ重み発生器回路 400B は、電流補間器回路 415 に結合される差動出力  $C_{ip} / C_{ip}$  の第 1 のセットを有するクロック発生器回路 411 を含む。クロック発生器ブロック 411 は、2:1 電流マルチプレクサ 417 の差動入力に結合される差動出力  $C_{mp}$  および  $C_{mn}$  の第 2 のセットを有する。

#### 【0044】

電流補間器 415 は、第 1 の電流の  $I_{start}$  を供給するように動作する第 1 の電流源（I1）に結合された共通ソースを有する 2 つの PFTS\_Q1 および Q2 を含む。

10

20

30

40

50

電流補間器は、第2の電流  $I_{stop}$  を供給するように動作する第2の電流源  $I_2$  に結合された共通ソースを有する2つのPFETs  $Q_3$  および  $Q_4$  をさらに含む。PFETs  $Q_1$  および  $Q_4$  のゲートは、正端子  $C_{ip}$  に結合され、一方、トランジスタ  $Q_2$  および  $Q_3$  のゲートは、第1の差動クロック出力の負端子  $C_{in}$  に結合される。

#### 【0045】

2 : 1電流マルチプレクサ回路417は、電流補間器のものと同様の構造を有しており、それゆえに、簡潔にするためにここでは繰り返されない。電流補間器回路415の（すなわち、PFETs  $Q_1$  および  $Q_3$  の共通ドレインの）第1の出力は、回路417のPFETs  $Q_5$  および  $Q_6$  の共通ソースに結合される。電流補間器回路415の（すなわち、PFETs  $Q_2$  および  $Q_4$  の共通ドレインの）第2の出力は、回路417のPFETs  $Q_7$  および  $Q_8$  の共通ソースに結合される。PFETs  $Q_5$  および  $Q_8$  のゲートは、正端子  $C_{mp}$  に結合され、一方、トランジスタ  $Q_6$  および  $Q_7$  のゲートは、第2の差動クロック出力の負端子  $C_{mn}$  に結合される。PFETs  $Q_5$  および  $Q_7$  のドレインは共通レベル（例えば、接地）に結合される。PFETs  $Q_6$  および  $Q_8$  のドレインは、ゲートがドレインに結合されたNFT  $Q_9$  によって表される電流源に結合される。ドライバ回路があり、それは、NFT  $Q_{10}$  で表された電流源に結合された共通ソースを有する2つのNFTs  $Q_{11}$  および  $Q_{12}$  を含むフルレート・タップ重みドライバ（full-rate tap weight driver）421であり得る。

#### 【0046】

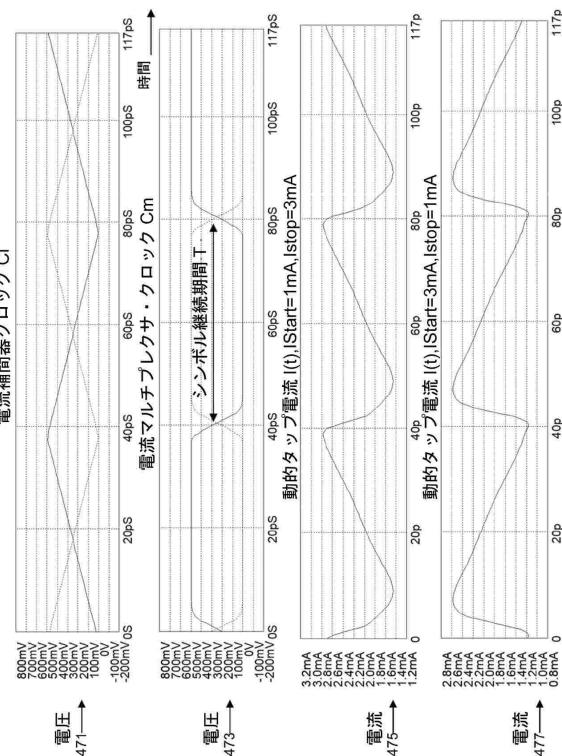

動的タップ重み発生器回路400Bの動作は、波形を考慮してよりよく理解することができる。その目的のために、図4Cは、図4Bのタップ重み発生器回路400Bの例示の波形を示す。その結果、タップ重み発生器回路400Bの動作は、図4Cの波形を参照して論じられる。

#### 【0047】

図4Bの実施形態において、同期動的タップ重み発生器400Bは、シンボル伝送間隔にわたって電流  $I_{start}$  から電流  $I_{stop}$  に向かって補間することができる電流補間器415を使用して実現され、ここで、 $I_{start}$  および  $I_{stop}$  の値は、以前に論じたように、プログラム的に事前構成されるかまたは自動的に適合されてもよい。1つの実施形態では、ハーフレートまたはC2のクロックが、クロック発生器ブロック411を駆動する。クロック発生器ブロック411は、図4Cにおいて、それぞれ、波形471および473で示される2つの差動出力クロック、すなわち、 $C_i$  または補間器クロック、および  $C_m$  またはマルチプレクサ・クロックを作る。1つの実施形態では、補間器クロック  $C_{i471}$  は、PMOSデバイス  $Q_1$ 、 $Q_2$ 、 $Q_3$ 、および  $Q_4$  を含む電流補間器回路415を駆動するのに適切な振幅（swinging）をもつ、図4Bの入力  $C_2$  クロックと同じ周波数の三角波形である。図4Cに示された例示の波形では、補間器三角波形471は、図4BのPMOS電流補間器デバイス  $Q_1$  から  $Q_4$  のゲートを駆動するために0から0.5Vまで変化する。PMOS電流補間器415は、PMOSデバイス  $Q_5$ 、 $Q_6$ 、 $Q_7$ 、および  $Q_8$  によって形成されたPMOS 2 : 1電流マルチプレクサ417に出力を供給する。

#### 【0048】

波形473で示された電流補間器クロック  $C_m$  は、電流マルチプレクサ417の電流スイッチを駆動して、ゲートとドレインが一緒に結合されたNFTとして構成されたNMOSキャッチ・ダイオード  $Q_9$  に2 : 1多重化電流を供給し、それにより、所望のフルレート電流傾斜波形を作りタップの重みを制御する。図4Cに示された例示の波形では、補間器クロック  $C_{m473}$  は、名目上の矩形波形状により0から0.5Vまで変化して、電流マルチプレクサ417の状態を迅速に切り替える。ティル電流デバイス  $Q_{10}$  と組み合わされたキャッチ・ダイオード  $Q_9$  は、電流ミラーを形成して、動的タップ重み電流  $I(t)$  を作り、次いで、動的タップ重み電流  $I(t)$  は、タップ重み  $S_{i-n}$  の符号にデータ（NRZ伝送の） $D_{i-n}$  の符号を乗じたものに基づいて、NMOSトランジスタ  $Q_{11}$  および  $Q_{12}$  を通してライン・ドライバ端子出力483および485に切り替えられ

10

20

30

40

50

る。

#### 【0049】

2つの例示の動的電流発生器構成が、図4Cの波形に示されている。より詳細には、波形475は、シンボル伝送間隔を通して時間的に増加するタップ重み電流の生成を示しており、一方、波形477は、シンボル伝送間隔を通して時間的に減少するタップ重み電流の生成を示している。1つの実施形態では、クロックC<sub>i</sub>471およびC<sub>m</sub>473の位相を調節して、動的電流の過渡部分（動的電流がI<sub>stop</sub>からI<sub>start</sub>に切り替わるとき）を、シンボル伝送間隔内の所望の場所に、例えば、データ波形の移行エッジの近くに集中させることができる。データ波形自体は、図4Cに示されていないが、C<sub>m</sub>クロック473と名目上同期していることが理解されるであろう。

10

#### 【0050】

メインまたはカーソル・タップが10mA固定電流によりプログラムされた一例では、正規化された動的タップ重みは、名目上、0.1から0.3まで変化する。回路の帯域幅制限のために、実際のプログラムされた開始および停止電流は、1mAおよび3mAに正確に対応しないことがあるが、シンボル伝送にわたる0.1から0.3までのタップ重みの変化に対応する電流傾斜勾配は良好な表示を提供することが理解されるであろう。

#### 【0051】

いくつかのシナリオでは、所望の傾斜勾配が、データ伝送間隔を通してタップ符号の変化を引き起こし、それが、負電流へのタップ重み構成を含むことがある。それは、図4Bの説明された電流補間器回路で十分に提供されないことがある。1つの実施形態では、実施態様を簡単にするために、タップ重み変化がI<sub>start</sub>からI<sub>stop</sub>までに符号を変化させる（すなわち、正のI<sub>start</sub>および負のI<sub>stop</sub>）場合、I<sub>stop</sub>は、小さい値に飽和される。代わりに、I<sub>stop</sub>が、絶対値でI<sub>start</sub>よりも著しく大きい場合、タップ重みS<sub>i</sub>の符号を反転させて、I<sub>stop</sub>を正にし、I<sub>start</sub>を小さい値に飽和させることができる。別の実施形態では、動的等化器タップと組み合わされた第2の静的等化器タップを使用することによって、極性交差を達成することができ、静的等化器タップと動的等化器タップとが、出力の反対極性に適用される。一例として、一方の極性の静的タップ値の正規化重み0.2を、他方の極性の0.1から0.3まで変化する傾斜の正規化重みと組み合わせることにより、組み合わされた静的タップと動的タップの正味の0.1から-0.1の正規化された重みがもたらされる。

20

#### 【0052】

##### 例示の結果

本明細書に記載のシステムおよび方法の利点は、いくつかの実際のシミュレーション結果でよりよく理解することができる。その目的のために、異なる等化タップ波形と、対応する等化データ信号の「アイ・ダイアグラム」が、図6から図10に各々提供される。図の「アイ・ダイアグラム」は、水平アイ（HEY）および垂直アイ（VEY）動作マージン・メトリックを作るための様々な既知の統計技術を使用して分析することができる。

#### 【0053】

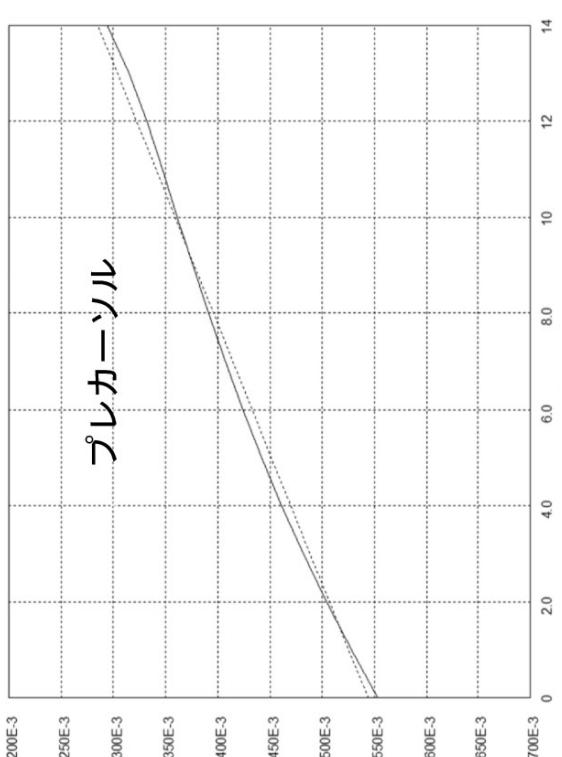

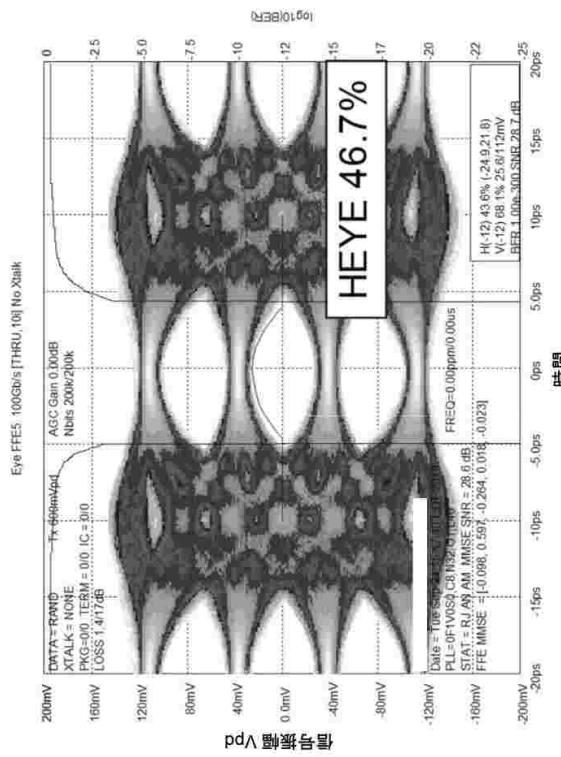

図6Aから図6Dは、17dBの損失チャネルを有する例示の5タップFFE100G b/s 4レベル伝送のプレカーソル（すなわち、図6A）、ポストカーソル（すなわち、図6B）、第2のポストカーソル（すなわち、図6C）、および第3のポストカーソル（すなわち、図6D）のタップ重みを示す。最適値（642などの実線）と直線近似（644などの破線）の両方が示される。したがって、図6Aから図6Dは、経時的なタップ重みの時間変化の計算、およびそれらのタップ重みの直線近似を示す。図7Aは、先行技術（タップ重みが固定されている）の29.7%のHEYマーキングを示し、一方、図7Bは、本発明の適用により達成された、その結果の改善されたHEYマージンを示す。この例では、HEYは、名目上17dBの損失チャネルの4レベル・データ伝送を使用して、約30%HEYから47%HEYに改善した。

40

#### 【0054】

図8Aおよび図8Bは、先行技術（タップ重みが固定されている）と例示の実施形態の

50

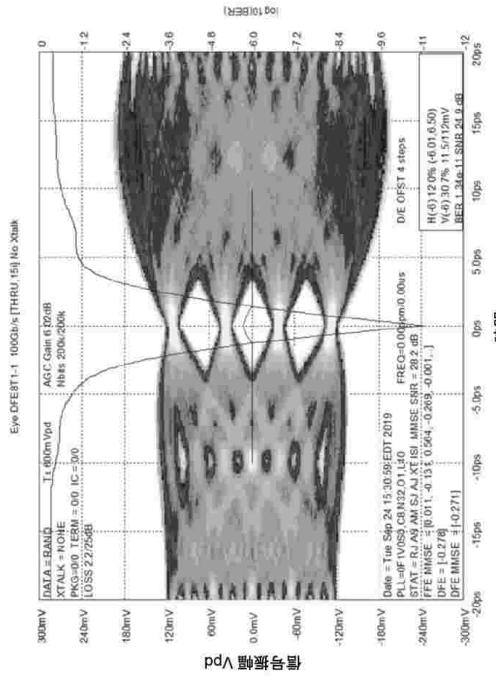

両方について、2つのプレカーソルをもつ8タップF F E、R x D F E 1、1 0 0 G b / s 4 レベル伝送、2 5 d B 損失チャネルを有する別の例示の時変フィード・フォワード・ライン等化器のアイ・ダイアグラムを示す。この例は、F F E 等化とD F E 等化の両方を使用するより高い損失のチャネルに基づき、さらに、クロック・ジッタ（すなわち、2 0 0 f s R M S のランダム・クロック・ジッタ）および振幅雑音（すなわち、3 m V R M S 振幅雑音）からの劣化を加えている。図8 A および図8 B の比較のアイ・ダイアグラム・プロットで示されるように、H E Y E は、1 2 . 5 % マージンから3 9 % マージンに改善される（すなわち、3倍以上の改善）。

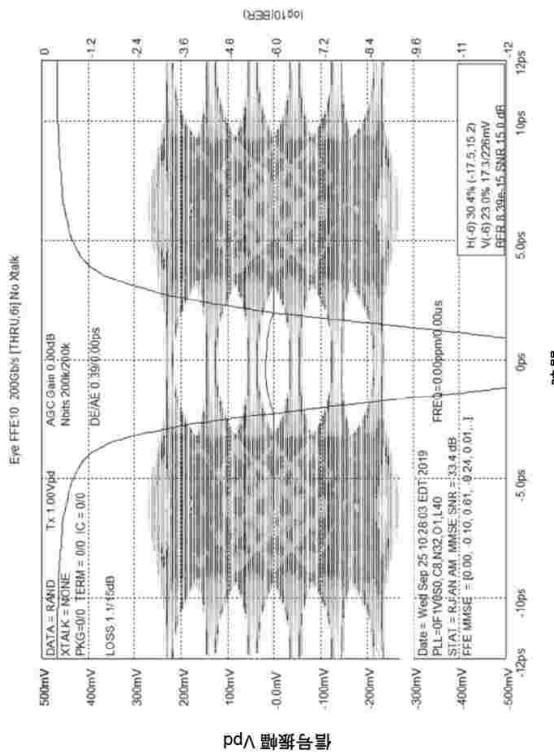

#### 【0 0 5 5】

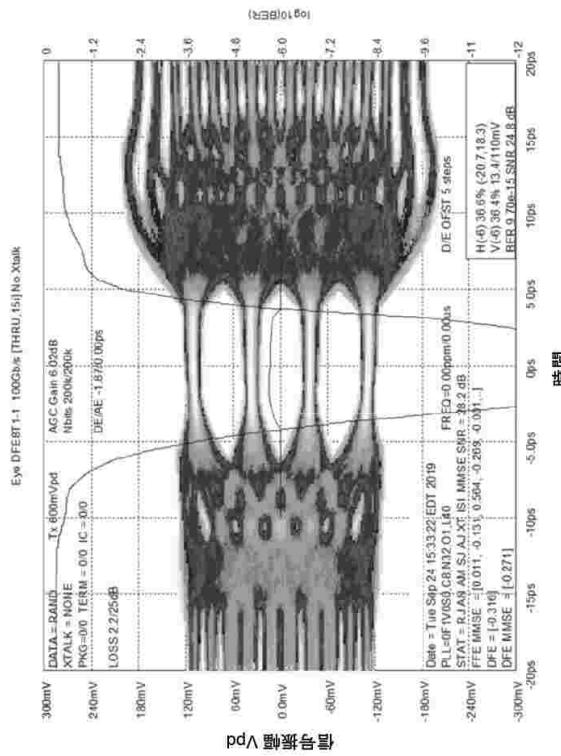

図9 A および図9 B は、6 レベル伝送をもたらす3 2 Q A M 变調を使用する、2 0 0 f s R M S クロックR J および5 m V R M S 振幅雑音をもつ1 5 d B 損失チャネルによる2 0 0 G b / s データ伝送を有する別の例示の時変フィード・フォワード・ライン等化器のアイ・ダイアグラムを示す。この例では、B E R フロアは、図9 A の先行技術の3 E - 1 1 から本開示の一実施形態の図9 B の8 E - 1 5 に改善され、1 e - 6 信頼度のH E Y E は1 2 . 5 % から3 2 . 7 % に向上している。

10

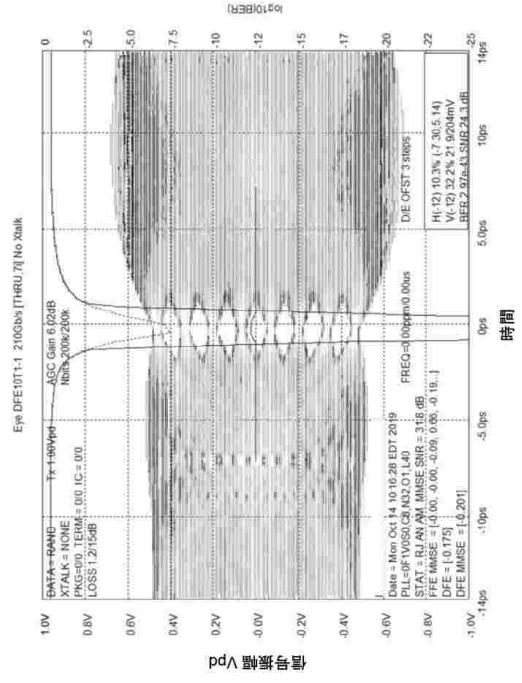

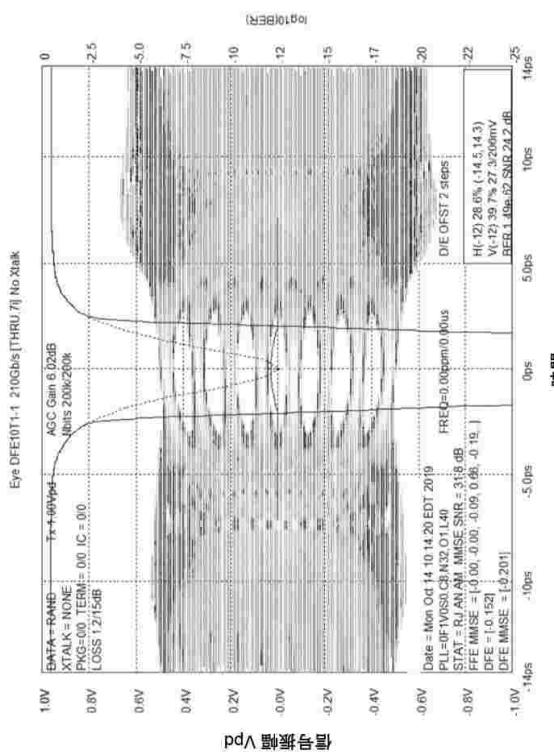

#### 【0 0 5 6】

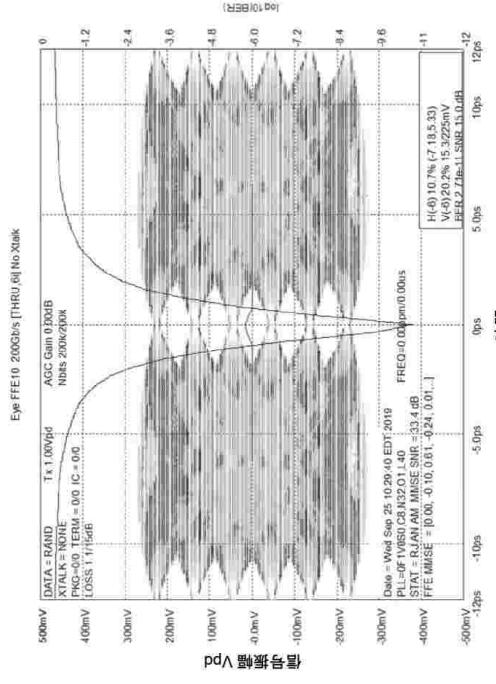

図10 A および図10 B は、2 0 0 f s R M S クロック・ジッタおよび5 m V R M S 振幅雑音をもつ1 5 d B 損失チャネルによる2 1 0 G b / s 8 レベル信号伝送を有するさらなる別の例示の時変フィード・フォワード・ライン等化器のアイ・ダイアグラムを示す。この例では、リード・ソロモン誤り訂正コードを適用した後、H E Y E は、本開示の一実施形態と一致する、時間依存等化器を使用して、1 2 . 4 %（すなわち、タップ重みが固定されている図10 A の先行技術）から2 8 . 8 %（すなわち、図10 B ）に改善されている。

20

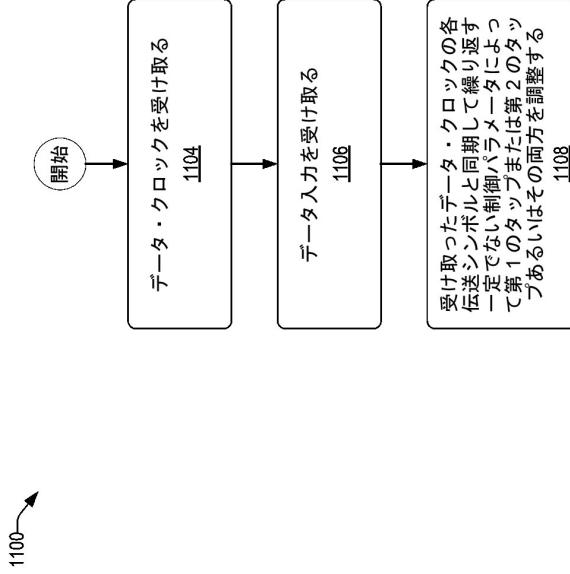

#### 【0 0 5 7】

##### 例示のプロセス

例示の等化器システム1 0 0 、例示の波形3 0 2 から3 4 0 、および例示の回路実施態様4 0 0 の前述の概要を用いて、ここで、例示のプロセスの高レベルの議論を考えることは有用であり得る。その目的のために、図11は、例示的な実施形態と一致する、データ信号の等化を実行するためのプロセス1 1 0 0 を提示する。プロセス1 1 0 0 は、論理流れ図におけるプロセスの集合として示され、各ブロックは、ハードウェア、ソフトウェア、またはそれらの組合せで実施することができる操作のシーケンスを表す。ソフトウェアのコンテキストにおいて、プロセスは、1つまたは複数のプロセッサによって実行されたとき、列挙された操作を実行するコンピュータ実行可能命令を表す。一般に、コンピュータ実行可能命令は、機能を実行するか、または抽象データ型を実施するルーチン、プログラム、オブジェクト、コンポーネント、データ構造などを含むことができる。操作が記載されている順序は、限定として解釈されることを意図しておらず、任意の数の記載されたプロセスは、任意の順序で組み合わされてもよく、またはプロセスを実施するために並行して実行されてもよく、あるいはその両方であってもよい。議論の目的で、プロセス1 1 0 0 は、図4を参照して説明される。

30

#### 【0 0 5 8】

限定としてではなく、単に例として、データ信号を受け取るように動作する入力ノード、データ・クロック入力部、第1のタップ、および第2のタップを含むF F E システムを考える。ブロック1 1 0 4 において、クロック信号が受け取られる。ブロック1 1 0 6 において、データ信号が、受け取ったクロック信号と同期して状態を変化させる传送シンボルの入力ノードで受け取られる。ブロック1 1 0 8 において、第1のタップ重みまたは第2のタップ重みの少なくとも一方が、各传送シンボルと同期して繰り返す動的制御パラメータによって調整される。

40

#### 【0 0 5 9】

##### 例示のコンピュータ・プラットフォーム

上述で論じたように、データ信号の等化に関連する機能、ならびに本明細書で論じられ

50

る他の機能は、コントローラまたはコンピューティング・デバイスを使用することによって実行することができる。図12は、本明細書で論じられる1つまたは複数の機能ブロックを実装するために使用することができる、様々なネットワーク化構成要素と通信することができるコンピュータ・ハードウェア・プラットホームの機能ブロック図の例である。

#### 【0060】

コンピュータ・プラットフォーム1200は、中央処理装置(CPU)1204、ハード・ディスク・ドライブ(HDD)1206、ランダム・アクセス・メモリ(RAM)または読み出し専用メモリ(ROM)1208、あるいはその両方、キーボード1210、マウス1212、ディスプレイ1214、および通信インターフェース1216を含むことができ、それらは、システムバス1202に接続される。

10

#### 【0061】

1つの実施形態では、HDD1206は、本明細書に記載された方法で等化エンジン1240などの様々なプロセスを実行することができるプログラムを格納することを含む機能を有する。等化エンジン1240は、様々な機能を実行するように構成された様々なモジュールを有することができる。例えば、ネットワークを介して様々なソースからのデータ信号を受け取るように動作するインターラクション・モジュール(interaction module)1242があってもよく、ここで、データは、等化エンジン1240によって等化され得る。

#### 【0062】

クロック・モジュール1244があってもよく、クロック・モジュール1244は、入力データが同期するクロック信号を受け取るかまたはそれ自体のクロック信号を生成するかあるいはその両方を行うように動作する。2つ以上のタップがあり、例として、第1のタップ・モジュール1245および第2のタップ・モジュール1248として表される。2つのタップ・モジュールが示されているが、様々な実施形態において、本明細書で論じられた概念によってサポートされるタップの数には制限はない。第1のタップ1246または第2のタップ1248の少なくとも一方のタップ重みを制御するように動作する制御パラメータ・モジュール1250があってもよい。制御パラメータ・モジュール1250は、クロックの各伝送シンボルと同期して繰り返す動的制御パラメータを提供することによってタップ重みを調整する。第1のタップおよび第2のタップのタップ重みを合計するように動作する合計モジュール1250があってもよい。

20

#### 【0063】

1つの実施形態では、Apache(商標)などのプログラムが、システムをWebサーバとして操作するために格納され得る。1つの実施形態では、HDD1206は、JVM(Java(R))(商標)仮想マシン)を実現するためのJava(R)(商標)実行時環境プログラム用のものなどの1つまたは複数のライブラリ・ソフトウェア・モジュールを含む実行アプリケーションを格納することができる。

30

#### 【0064】

##### 結論

様々な実施形態の記載は、例証の目的のために提示されたが、網羅的であること、または開示された実施形態に限定されることを意図していない。多くの変形および変更が、本発明の範囲から逸脱することなく、当業者には明らかであろう。本明細書で使用される用語は、本発明の原理、実際の適用、または市場で見いだされる技術を超える技術的改善を最もよく説明するように、あるいは他の当業者が本明細書で開示される実施形態を理解できるように選ばれた。

40

#### 【0065】

前述は、最良の状態または他の例あるいはその両方であると考えられるものを説明したが、様々な変形がその中で行われてもよく、本明細書で開示された主題が様々な形態および例で実現されてもよく、教示が多数の用途に適用されてもよく、それらの一部のみが本明細書で説明されていることを理解されたい。以下の特許請求の範囲により、本教示の真の範囲内にある任意のすべての用途、変形、および変更を特許請求することが意図されて

50

いる。

#### 【 0 0 6 6 】

本明細書で論じられた構成要素、ステップ、特徴、目的、利益、および利点は単に例示である。それらのどれも、またそれらに関連する議論も、保護の範囲を限定するように意図されていない。様々な利点が本明細書で論じられたが、すべての実施形態が必ずしもすべての利点を含むとは限らないことが理解されるであろう。特に明記しない限り、以下の特許請求の範囲を含めて本明細書に記載されるすべての測定、値、定格、位置、大きさ、サイズ、および他の仕様は、近似であり、正確ではない。それらは、それらが関連する機能と、それらが関係する技術分野において慣例であるものと一致する妥当な範囲を有するように意図されている。

10

#### 【 0 0 6 7 】

多数の他の実施形態も考慮される。これらには、より少ない、追加の、または異なる、あるいはその組合せの構成要素、ステップ、特徴、目的、利益、および利点を有する実施形態が含まれる。これらには、構成要素またはステップあるいはその両方が異なるように配列されるかまたは順序づけられるかあるいはその両方である実施形態がさらに含まれる。例えば、本明細書で論じられた任意の信号は、基礎をなす制御方法を実質的に変更することなしに、スケーリングされ、バッファされ、スケーリングおよびバッファされ、別の状態（例えば、電圧、電流、電荷、時間など）に変換され、または別の状態に（例えば、ハイからローに、およびローからハイに）変換され得る。

#### 【 0 0 6 8 】

N F E T S および P F E T S が、本明細書の例のうちのいくつかに図示されているかまたは論じられているかあるいはその両方であるが、これらのトランジスタは、限定ではなく、単に例として、提供された。本明細書で開示された概念に基づいて、相補型論理による他のタイプの絶縁ゲート電界効果トランジスタ（ I G F E T ）が、同様に使用されてもよいことが理解されるであろう。例えば、カーボン・ナノチューブ F E T S を含む周期律表の列 I I I - V からの任意の F E T S が、本明細書で説明された構造を実現するために同様に使用されてもよい。いくつかの実施形態では、バイポーラ・トランジスタ（例えば、 P N P または N P N ）または B i C M O S あるいはその両方が、 M O S トランジスタの代わりに使用されてもよい。

20

#### 【 0 0 6 9 】

本発明の態様は、本出願の実施形態による方法、装置（システム）、およびコンピュータ・プログラム製品の流れ図またはブロック図あるいはその両方を参照して本明細書に記載されている。流れ図またはブロック図あるいはその両方の各ブロック、および流れ図またはブロック図あるいはその両方のブロックの組合せは、コンピュータ可読プログラム命令によって実現され得ることが理解されるであろう。

30

#### 【 0 0 7 0 】

これらのコンピュータ可読プログラム命令は、コンピュータまたは他のプログラマブル・データ処理装置のプロセッサを介して実行される命令が流れ図またはブロック図あるいはその両方の 1 つまたは複数のブロックにおいて指定された機能 / 動作を実施するための手段を作り出すように、汎用コンピュータ、専用コンピュータ、またはマシンを作るための他のプログラマブル・データ処理装置のプロセッサに提供され得る。これらのコンピュータ可読プログラム命令はまた、命令が格納されたコンピュータ可読ストレージ媒体が流れ図またはブロック図あるいはその両方の 1 つまたは複数のブロックにおいて指定された機能 / 動作の態様を実施する命令を含む製品を構成するように、コンピュータ、プログラマブル・データ処理装置、または他のデバイス、あるいはその組合せに、特定の方法で機能するように指示することができるコンピュータ可読ストレージ媒体に格納されてもよい。

40

#### 【 0 0 7 1 】

コンピュータ可読プログラム命令はまた、コンピュータ、他のプログラマブル装置、または他のデバイスで実行される命令が流れ図またはブロック図あるいはその両方の 1 つまたは複数のブロックにおいて指定された機能 / 動作を実施するように、コンピュータ、他

50

のプログラマブル・データ処理装置、または他のデバイスにロードされて、一連の動作ステップをコンピュータ、他のプログラマブル装置、または他のデバイスで実行させて、コンピュータ実装プロセスを生じさせることができる。

【 0 0 7 2 】

図における流れ図およびブロック図は、本発明の様々な実施形態によるシステム、方法、およびコンピュータ・プログラム製品の可能な実施態様のアーキテクチャ、機能、および動作を示す。これに関しては、流れ図またはブロック図の各ブロックは、指定された論理機能を実施するための1つまたは複数の実行可能命令を含む命令のモジュール、セグメント、または一部を表すことができる。いくつかの代替の実施態様では、ブロックに記された機能は、図に記された順序から外れて行われてもよい。例えば、連続して示された2つのブロックは、実際には、実質的に同時に実行されてもよく、またはブロックは、時には、関連する機能に応じて逆の順序で実行されてもよい。ブロック図または流れ図あるいはその両方の各ブロック、およびブロック図または流れ図あるいはその両方のブロックの組合せは、指定された機能または動作を実行するかあるいは専用ハードウェア命令とコンピュータ命令の組合せを実行する専用ハードウェア・ベース・システムで実施され得ることにも留意されたい。

10

【 0 0 7 3 】

前述は例示的な実施形態に関連して説明されたが、「例示的な」という用語は、最良または最適ではなく単に一例としてのものを意味していることを理解されたい。すぐ上に記載されている場合を除き、記載または図示されているものは、特許請求の範囲に詳述されているか否かに関係なく、いかなる構成要素、ステップ、特徴、目的、利益、利点、または等価物も一般の人々に提供することを意図したものではなく、またはそのように解釈されるべきでない。

20

【 0 0 7 4 】

本明細書で使用される用語および表現は、特定の意味が本明細書において別に記載されている場合を除いて、それらの対応する調査および研究のそれぞれの分野に関してそのような用語および表現に与えられるような通常の意味を有することが理解されるであろう。第1の、第2などの関係語は、そのようなエンティティまたはアクション間の実際の任意のそのような関係または順序を必ずしも必要とするかまたは意味することなく、あるエンティティまたはアクションを別のものから区別するためにもっぱら使用され得る。「備える、含む ( c o m p r i s e s ) 」、「備えている、含んでいる ( c o m p r i s i n g ) 」という用語、またはその任意の他の変形例は、要素のリストを含むプロセス、方法、物品、または装置が、それらの要素のみを含むのではなく、そのようなプロセス、方法、物品、または装置に明確にリストされずまたは固有でない他の要素を含むことができるよう、非排他的な包括を包含することが意図される。「 a 」または「 a n 」に続く要素は、さらなる制約なしに、その要素を含むプロセス、方法、物品、または装置における追加の同様の要素の存在を排除しない。

30

【 0 0 7 5 】

読者が技術的な開示の性質を速やかに確認できるように、「本開示の要約」が提供される。その要約は、特許請求の範囲の範囲または意味を解釈または限定するために使用されないという理解の下に提示される。加えて、前述の「詳細な説明」において、本開示を簡素化する目的で、様々な特徴が様々な実施形態において一緒にグループ化されていることを理解することができる。開示のこの方法は、特許請求される実施形態が、各請求項に明確に列挙されているものよりも多くの特徴を必要とするという意図を反映するものと解釈されるべきでない。むしろ、以下の特許請求の範囲が反映するように、発明の主題は、単一の開示された実施形態のすべての特徴よりも少ない特徴に存在する。したがって、以下の特許請求の範囲は、本明細書によって、「詳細な説明」に組み込まれ、各請求項は、別々に特許請求される主題として自立している。

40

50

【図面】

【図 1】

【 図 2 】

【 义 3 】

### 【図 4 A】

【図4B】

### 【図4C】

【図5】

【図 6 A】

### 【図 6 B】

### 【図 6 D】

### 【図 6 C】

### 【図7A】

先行技術

【図 7 B】

【図 8 A】

先行技術

【図 8 B】

【図 9 A】

先行技術

【図 9 B】

【図 10 A】

先行技術

【図 10 B】

【図 11】

【図 1 2】

10

20

30

40

50

---

フロントページの続き

(72)発明者 ブッケマ、トロイ

アメリカ合衆国 10598 ニューヨーク州ヨークタウン・ハイツ キッチャワン・ロード 1101

審査官 川口 貴裕

(56)参考文献 特開 2000-295148 (JP, A)

特表 2002-519895 (JP, A)

特開 2002-280941 (JP, A)

特開 2008-288653 (JP, A)

特開 2019-022051 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04L 25/00 - 25/66

H04L 27/01

H04B 3/04 - 3/18