(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5314949号

(P5314949)

(45) 発行日 平成25年10月16日(2013.10.16)

(24) 登録日 平成25年7月12日(2013.7.12)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 301W |

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 301V |

| HO1L 23/522 | (2006.01) | HO1L 21/90 | D    |

| HO1L 21/768 | (2006.01) |            |      |

請求項の数 4 (全 8 頁)

(21) 出願番号 特願2008-174498 (P2008-174498)

(22) 出願日 平成20年7月3日 (2008.7.3)

(65) 公開番号 特開2009-54999 (P2009-54999A)

(43) 公開日 平成21年3月12日 (2009.3.12)

審査請求日 平成23年5月11日 (2011.5.11)

(31) 優先権主張番号 特願2007-195493 (P2007-195493)

(32) 優先日 平成19年7月27日 (2007.7.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 橋谷 雅幸

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

審査官 井上 弘亘

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板を用意する工程と、

前記半導体基板のチャネル領域となる領域の一部を表面から内部にかけて除去し、側面と底面を有するトレンチを形成してプレーナー部とトレンチ部を配置する工程と、

前記トレンチ部および前記プレーナー部の表面に酸化膜を形成する工程と、

レジスト材を塗布し、前記トレンチのソース領域およびドレイン領域方向の上面から底面にかけて不純物が導入できるようにパターニングする工程と、

前記半導体基板を回転させながら第1のソース領域およびドレイン領域を形成する不純物をイオン注入する工程と、

前記レジスト材および前記酸化膜を除去し、ゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜を形成した後に、多結晶シリコンを堆積し、ゲート電極を形成する工程と、

前記ゲート電極を挟んで第2のソース領域およびドレイン領域を形成する工程とからなる半導体装置の製造方法。

## 【請求項 2】

前記トレンチ部上面から底部にかけて形成される前記第1のソース領域およびドレイン領域は、 $1 \times 10^{13} \text{ atoms/cm}^2$  から  $1 \times 10^{16} \text{ atoms/cm}^2$  のドーズ量でイオン注入されることを特徴とする請求項1に記載の半導体装置の製造方法。

## 【請求項 3】

10

20

前記トレンチ部上面から底部にかけて形成される前記第1のソース領域およびドレイン領域の不純物拡散と活性化は、前記ゲート絶縁膜の形成工程と同時に行われることを特徴とする請求項1に記載の半導体装置の製造方法。

【請求項4】

前記トレンチ部上面から底部にかけて形成される前記第1のソース領域およびドレイン領域の不純物導入工程は、前記ゲート絶縁膜の形成工程の前後のどちらにおいても実施可能であることを特徴とする請求項1に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、高駆動能力を要するMOSトランジスタを含む半導体装置およびその製造方法に関する。

【背景技術】

【0002】

MOSトランジスタは電子技術において中核を担う電子素子であって、MOSトランジスタの小型化と高駆動能力化は、重要である。MOSトランジスタを高駆動能力化する方法の1つとして、ゲート幅を長くしてオン抵抗を低減させる方法があるが、ゲート幅を広くするとMOSトランジスタの占有面積が大きくなるという問題があった。その解決のために、横型MOS構造のMOSトランジスタの専有面積の増加を抑えながらゲート幅を広くする技術が提案されている。(例えば、特許文献1参照)

20

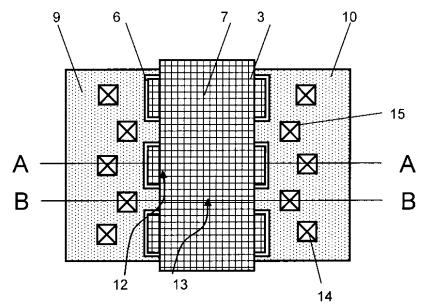

以下、図4を用いて、従来の半導体装置について説明する。図4(a)の斜視図は、ウェル11にトレンチ構造3を設け、ゲート絶縁膜6を介してトレンチ構造を有するトレンチ部の内部およびトレンチが形成されていないプレーナー部の上面にゲート電極7を形成したものである。ウェル11の表面部分において、ゲート電極7の一方の側にはソース領域9が設けられており、他方の側にはドレイン領域10が設けられている。図4(b)は、図4(a)のA-A断面図であり、プレーナー部を示している。図4(c)は、図4(a)のB-B断面図であり、チャネルに垂直な方向の断面図である。B-B断面図に示したように、トレンチ部3の内部にゲート電極7が形成されているため、ゲート電極7の下に位置するゲート絶縁膜6が形成する曲線の長さの総延長がゲート幅となる。

【0003】

30

このように、この技術では、ゲート部を凸部と凹部を有するトレンチ構造にすることによって、表面でのゲート電極7の長さに対して、実効的なゲート幅の長さを長くすることができ、これによって、MOSトランジスタの耐圧を低下させずに単位面積あたりのオン抵抗を低減することができる。

【特許文献1】特開2006-49826号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

以上述べた半導体装置の構造では、想定したよりも駆動能力が実際には得られないという問題があった。そして、ゲート長によって、駆動能力が異なり、ゲート長が短くなると、駆動能力が低下する傾向を示すということが分かった。

40

【0005】

これは、ソースドレイン間に生じたチャネルのうち、図4(d)に示した経路A(トレンチ部3が形成されていないプレーナー部)に電流が多く流れ、ソースとドレインを結ぶ向きであるチャネルに平行なトレンチ部8の側面を流れる経路Bやトレンチ部8の底面を介して流れる経路Cにはあまり電流が流れないことが原因であると推察できる。そのため、ゲート長が短いほど、経路Aに電流が集中するようになり、このことが、ゲート長が短くなると駆動能力が低下する原因であると考えられる。

【0006】

本発明の目的は、トレンチ構造を有する半導体装置の駆動能力を向上させることである

50

。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明は次の手段を用いた。

【0008】

(1) 第1導電型半導体基板に形成された、ゲート幅方向に断続的に深さが変化するトレンチ構造と、ゲート絶縁膜を介して前記トレンチ構造が定めるトレンチ部の内部およびプレーナー部の上面に形成されたゲート電極と、前記ゲート電極の一方の側に形成された第2導電型のソース領域と、前記ゲート電極の他方の側に形成された第2導電型のドレイン領域を備えた半導体装置において、前記ソース領域と前記ドレイン領域のうち、前記トレンチ部を挟んで向き合う部分は、当該トレンチ構造の上面から底部と同じあるいはそれ以上に達する深さを有することを特徴とする半導体装置とした。10

【0009】

(2) 第1導電型半導体基板と、前記第1導電型半導体基板の表面近傍に離間して配置された第2導電型のソース領域およびドレイン領域と、前記ソース領域およびドレイン領域の間に配置された第1のチャネル領域となる平坦なプレーナー部と、前記プレーナー部に沿って配置された、その側面および底面が第2のチャネル領域となる、一定の深さを有するトレンチ部と、前記プレーナー部および前記トレンチ部の表面に設けられたゲート絶縁膜と、前記ゲート絶縁膜の上に設けられたゲート電極とからなる半導体装置であって、前記ソース領域およびドレイン領域のうち前記トレンチ部を介して向き合う部分の拡散領域の深さは当該トレンチ構造の上面から底部と同じあるいはそれ以上に達する深さを有することを特徴とする半導体装置とした。20

【0010】

半導体基板を用意する工程と、前記半導体基板のチャネル領域となる領域の一部を表面から内部にかけて除去し、側面と底面を有するトレンチを形成してプレーナー部とトレンチ部を配置する工程と、前記トレンチ部および前記プレーナー部の表面に酸化膜を形成する工程と、レジスト材を塗布し、前記トレンチのソース領域およびドレイン領域方向の上面から底面にかけて不純物が導入できるようにパターニングする工程と、前記半導体基板を回転させながら第1のソース領域およびドレイン領域を形成する不純物をイオン注入する工程と、前記レジスト材および前記酸化膜を除去し、ゲート絶縁膜を形成する工程と、多結晶シリコンを堆積し、ゲート電極を形成する工程と、前記ゲート電極を挟んで第2のソース領域およびドレイン領域を形成する工程とからなる半導体装置の製造方法とした。30

【発明の効果】

【0011】

本発明によれば、上述の半導体装置のソース領域およびドレイン領域の一部において、ゲート電極形成前のトレンチ部にフォトレジスト膜を塗布しパターニングし、イオン注入をおこなうことでトレンチ部上面から底部にかけて深く拡散させた領域を形成することが可能である。これによって、トレンチ部トランジスタのゲート電極に対して深い位置までソース領域およびドレイン領域が形成されることになるため、ゲート幅方向に断続的に深さが変化する凹部上部への電流集中を緩和させ、電流をトレンチ部側面および底面にも流すことが可能となることから、半導体装置の駆動能力を向上させることが可能となる。40

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施の形態を図面に基づいて説明する。

【0013】

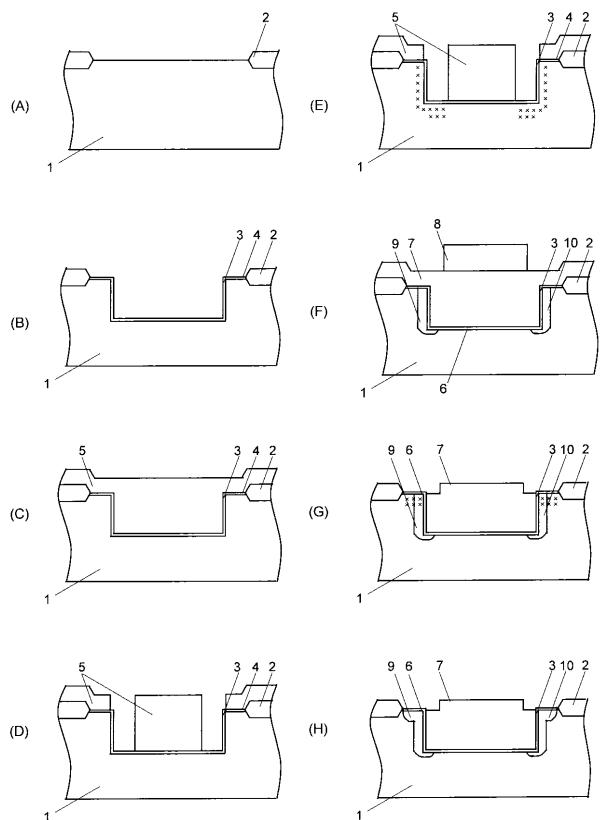

図1は本発明の半導体装置の製造方法の第1の実施例を示す模式的断面図による工程順のフローである。

【0014】

図1(A)は、第1導電型半導体基板である、例えばホウ素を添加した抵抗率20cmから30cmの不純物濃度を有するP型半導体基板1に、LOCOS法により厚膜酸化膜2とし50

て、例えば膜厚 500 nm から 1 μm の熱酸化膜を所望の領域に形成したものである。基板の導電型は本発明の本質とは関係ない。続いて図 1 (B) に示すように、第 1 導電型半導体基板にトレンチ構造 3 を例えば数百 nm から数 μm の深さに形成する。トレンチ構造 3 を形成する溝状の凹部は一つだけ配置されることもあるが、図面の紙面と垂直方向に平行に並んで複数個配置されることもある。その後、トレンチ構造 3 の内部を構成する半導体基板表面を含むおよび半導体基板表面に酸化膜 4 を例えば膜厚数百 nm で形成する。

#### 【0015】

その後、図 1 (C) に示すように、レジスト膜 5 を塗布し、図 1 (D) に示すように、ソース領域およびドレイン領域への不純物添加がトレンチ構造 3 の上面から底面と同じかそれ以上にかけて深く形成できるように、ソース領域およびドレイン領域のレジスト膜 5 をパターニングして不用部分を除去する。ここでレジスト膜に替え、窒化膜、多結晶シリコン膜をマスクとしてパターニングすることも可能である。その後、図 1 (E) に示すように不純物として、例えば砒素を好ましくは  $1 \times 10^{13} \text{ atoms/cm}^2$  から  $1 \times 10^{16} \text{ atoms/cm}^2$  のドーズ量でウェハをスピinn(回転)させながらイオン注入をおこなう。

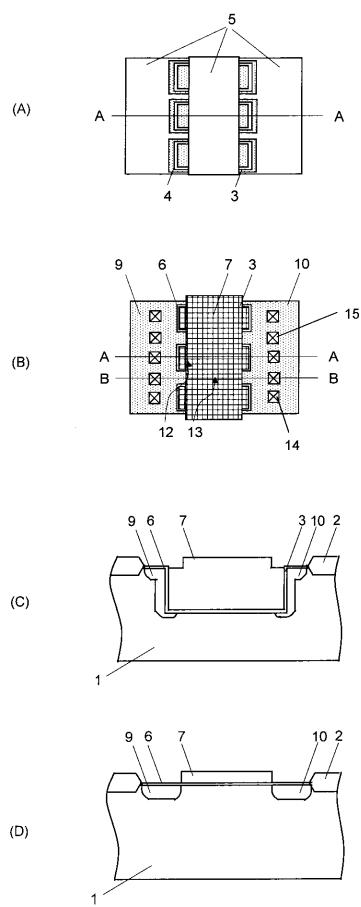

#### 【0016】

この工程については図 2 を用いて詳細に説明する。図 2 は図 1 (E) のトレンチ構造内へのイオン注入工程を示す模式図であり、図 2 (A) はソース領域側を示し、図 2 (B) は、図 2 (A) に対しウェハを 180° 回転させた時のドレイン領域側を示すものである。図 2 (A) に示すように、トレンチ構造 3 の側面から底面に不純物添加され、このウェハをスピinn(回転)させながら、低角度のイオン注入入射角度でのイオン注入をおこなうので、図 2 (B) に示すように、ソース領域側であるレジスト膜 5 の反対側に位置するドレイン領域にも側面から底部に不純物添加が可能となる。さらに、図 1 (E) を上から見た図が図 3 (A) であり、図 1 (E) は図 3 (A) に示す A-A 部の断面図となっている。その後、レジスト膜 5 および酸化膜 4 を除去する。

#### 【0017】

次に、図 1 (F) に示すように、ゲート絶縁膜 6 を、例えば膜厚十～数百 nm の熱酸化膜で形成した後、ゲート絶縁膜 6 上に多結晶シリコンゲート膜を好ましくは膜厚を 100 nm ~ 500 nm 堆積し、プリデポジションあるいはイオン注入法により不純物を導入してゲート電極 7 とする。ここで、熱酸化膜であるゲート絶縁膜 6 を形成するのに同じくして、イオン注入により添加した不純物の拡散および活性化をおこなう。この工程で、拡散したソース領域 9 およびドレイン領域 10 の双方は、トレンチ構造 3 の上面から底部と同じかそれ以上にかけて深い位置に拡散する。さらにここでは、上述のイオン注入による不純物添加が高濃度の場合、ソース領域 9 およびドレイン領域 10 のそれぞれの表面において熱酸化膜が厚くなることから、自動的にゲートとドレイン間での容量を低減することが可能である。

#### 【0018】

一方で、レジスト膜 8 でゲート電極 10 のパターニングをおこなうことで図 1 (G) に示すような構造が整う。引き続き、図 1 (G) に示すように、ゲート電極 10 に対しセルファーライン法でソース領域およびドレイン領域を形成するための不純物添加を行う。ソース領域およびドレイン領域の不純物添加は例えば砒素を好ましくは  $1 \times 10^{15} \text{ atoms/cm}^2$  から  $1 \times 10^{16} \text{ atoms/cm}^2$  のドーズ量でイオン注入する。この工程までで、トレンチ構造 3 を有する MOS ロジックの形態が整う。その後、800 ~ 1000 °C で数時間熱処理することで、図 1 (H) に示すように、ソース領域 9 およびドレイン領域 10 を形成する。

#### 【0019】

また、第 2 の実施例として、上述したようなトレンチ構造 3 の上面から底部と同じかそれ以上にかけて深く形成するためのソース領域 9 およびドレイン領域 10 の不純物添加を、ゲート絶縁膜 6 を形成後におこなうことが可能である。

#### 【0020】

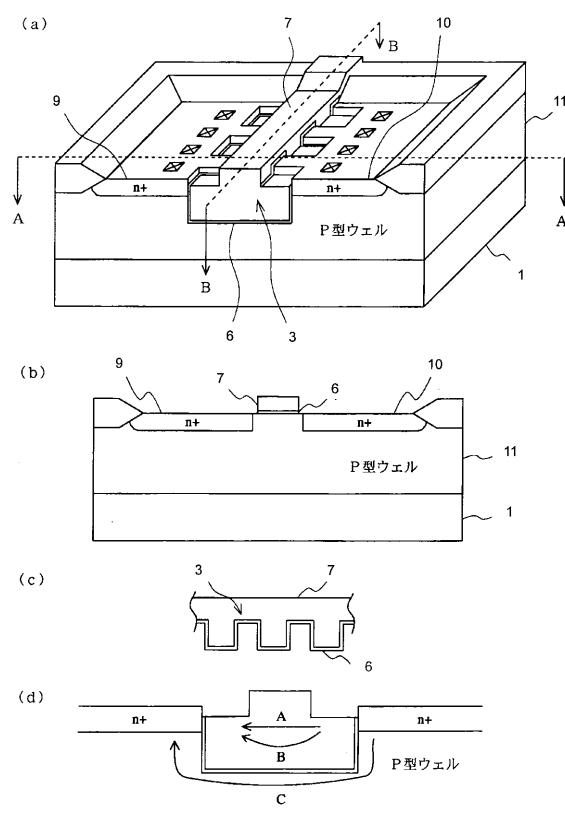

上述までの第 1 の実施例あるいは第 2 の実施例で得られる半導体装置の平面図は図 3 (

10

20

30

40

50

B) に示すとおりである。図3(B)のA-A断面図を図3(C)に、図3(B)のB-B断面図を図3(D)にそれぞれ示す。図3(C)より、トレンチ構造3を有するトレンチ部トランジスタ12において、ゲート電極7付近のソース領域9およびドレイン領域10においてトレンチ構造3の上面から底部と同じかそれ以上深くにかけて形成し、一方で、図3(D)からは、プレーナー部トランジスタ13ではゲート電極7付近においてもソース領域9およびドレイン領域10の全域において同程度の深さになるように形成させる。

【0021】

図5は、第3の実施例で得られる半導体装置の平面模式図である。図3(B)と異なる点はソース領域およびドレイン領域表面のコンタクトの位置である。図3(B)ではトレンチ部コンタクトとプレーナー部コンタクトが一列に並んで配置されているが、本実施例ではプレーナー部コンタクト15は寄生抵抗などを小さくするためにゲート電極7からの距離をトレンチ部コンタクト14とゲート電極との距離よりも短くした。

10

【0022】

以上のように、本発明においては、トレンチ構造を有するトレンチ部トランジスタ12においてトレンチ部3の上面から底部と同じかそれ以上にかけて深くすることで、ゲート幅方向に断続的に深さが変化する凹部上部への電流集中を緩和させ、電流をトレンチ部側面および底面にも流すことが可能となり、半導体装置の駆動能力を向上させることが可能となる。

【図面の簡単な説明】

【0023】

20

【図1】本発明の第1の実施例を示す模式的断面図フローである。

【図2】第1の実施例を示す模式的断面図フローにおけるイオン注入工程の模式図である。

【図3】第1の実施例および第2の実施例で得られる半導体装置の断面模式図および平面模式図である。

【図4】従来技術とその課題を示す断面図と模式図である。

【図5】第3の実施例で得られる半導体装置の平面模式図である。

【符号の説明】

【0024】

1 半導体基板

30

2、4 酸化膜

3 トレンチ構造

5、8 レジスト膜

6 ゲート絶縁膜

7 ゲート電極

9 ソース領域

10 ドレイン領域

11 ウェル

12 トレンチ部トランジスタ

13 プレーナー部トランジスタ

40

14 トレンチ部コンタクト

15 プレーナー部コンタクト

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開平05-160401(JP,A)

特開平02-023670(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 21/768

H01L 23/522

H01L 29/78