### (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2017-50489 (P2017-50489A)

(全 11 頁)

(43) 公開日 平成29年3月9日(2017.3.9)

(51) Int. Cl. FLテーマコード (参考) HO1L 23/48 (2006, 01) HO1L 5F136 23/48 L HO1L 23/34 (2006, 01) HO1L 23/34 Α

審査請求 未請求 請求項の数 14 OL

(21) 出願番号

(22) 出願日

特願2015-174622 (P2015-174622)

平成27年9月4日(2015.9.4)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100108062

弁理士 日向寺 雅彦

(72) 発明者 宮川 毅

東京都港区芝浦一丁目1番1号 株式会社

東芝内

F ターム(参考) 5F136 DA04 DA05 DA22

(54) 【発明の名称】半導体パッケージおよび半導体パッケージの製造方法

#### (57)【要約】 (修正有)

【課題】接続部の厚みを容易に調べることが可能な半導 体パッケージおよび半導体パッケージの製造方法を提供 する。

【解決手段】第1金属板1と、半導体チップ10と、第 2 金属板 2 と、を有する半導体パッケージにおいて、半 導体チップ10の第1電極は、第1接続部を介して第1 面を有する第1金属板1と接続する。第2金属板2は、 第2面S2および第3面S3を有し、第2面S2および 第3面S3は、第1面に平行な第1方向と交差する。第 3面53は、第2面52の反対側に設ける。第2面52 に、第2方向に延びる第1凹部41を形成し、第3面5 3に、第2方向に延びる第2凹部42を形成する。第2 金属板2は、第2接続部を介して半導体チップ10の第 2 電極 1 2 と接続する。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

第1面を有する第1金属板と、

前記第1面の上に設けられ、第1電極および第2電極を有し、前記第1電極が第1接続部を介して前記第1金属板と接続された半導体チップと、

前記第1面に平行な第1方向と交差する第2面と、前記第2面の反対側に設けられ、前記第1方向と交差する第3面と、を有し、前記第2面には、前記第2面と平行であり前記第1面と交差する第2方向に延びる第1凹部が形成され、前記第3面には、前記第2方向に延びる第2凹部が形成され、前記半導体チップの上に設けられ、第2接続部を介して前記第2電極と接続された第2金属板と、

を備えた半導体パッケージ。

### 【請求項2】

前記第1凹部は、前記第2面の前記第2方向における一端から他端に亘って形成され、前記第2凹部は、前記第3面の前記第2方向における一端から他端に亘って形成された請求項1記載の半導体パッケージ。

#### 【請求項3】

前記第1凹部の一部および前記第2凹部の一部は、前記第2方向において前記半導体チップと並ぶ請求項2記載の半導体パッケージ。

#### 【請求頃4】

前記第1凹部の前記一部および前記第2凹部の前記一部は、前記第2方向において前記半導体チップの角部と並ぶ請求項3記載の半導体パッケージ。

#### 【請求項5】

前記第1凹部および前記第2凹部は、前記第2方向において前記第2接続部と並ばない請求項3または4に記載の半導体パッケージ。

#### 【請求項6】

前記第3面には、第3凹部がさらに形成され、

前記第3凹部は、前記第3面の前記第2方向における一端から他端に亘って形成された 請求項2~5のいずれか1つに記載の半導体パッケージ。

### 【請求項7】

前記半導体チップは、第3電極をさらに有し、

前記第2電極および前記第3電極は、前記第1電極と反対側に設けられ、

前記第2電極と前記第3電極は、互いに離間して設けられた請求項1~6のいずれか1つに記載の半導体パッケージ。

### 【請求項8】

前記第3電極の上に設けられ、前記第3電極と接続された金属部材をさらに備え、

前記金属部材は、前記第1方向と、前記第1面に平行であり前記第1方向に対して垂直な第3方向と、において、前記第2金属板と離間して設けられた請求項7記載の半導体パッケージ。

### 【請求項9】

前記2金属板は、

第1部分と、

前記第1方向において前記第1部分と前記半導体チップとの間に位置する第2部分と

### を有し、

前記第1部分に形成された前記第1凹部の、前記第1方向に対して垂直であり前記第2面に沿う第3方向における長さは、前記第2部分に形成された前記第1凹部の前記第3方向における長さよりも長い請求項1~8のいずれか1つに記載の半導体パッケージ。

### 【請求項10】

前記第2方向は、前記第1面に対して垂直である請求項1~9のいずれか1つに記載の半導体パッケージ。

10

20

30

50

#### 【請求項11】

第1金属板の第1面の上に、第1接続部を介して半導体チップを配する工程と、

前記第1面に平行な第1方向と交差する第2面と、前記第2面の反対側に設けられ、前 記第1方向と交差する第3面と、を有し、前記第2面には、前記第2面と平行であり前記 第1面と交差する第2方向に延びる第1凹部が形成され、前記第3面には、前記第2方向 に延びる第2凹部が形成された第2金属板を、前記半導体チップの上に第2接続部を介し て配する工程と、

を備えた半導体パッケージの製造方法。

### 【請求項12】

前記第2金属板を配する工程において、前記第1凹部の一部および前記第2凹部の一部 を、前記第2方向において前記半導体チップと並ぶように、前記第2金属板を配する請求 項11記載の半導体パッケージの製造方法。

#### 【請求項13】

前記第2金属板を配する工程において、前記第1凹部の前記一部および前記第2凹部の 前記一部を、前記第2方向において前記半導体チップの角部と並ぶように、前記第2金属 板を配する請求項12記載の半導体パッケージの製造方法。

### 【請求項14】

前記第1凹部および前記第2凹部を通して、複数の箇所における前記半導体チップの前 記第1方向における位置を測定する工程をさらに備えた請求項11~13のいずれか1つ に記載の半導体パッケージの製造方法。

【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明の実施形態は、半導体パッケージおよび半導体パッケージの製造方法に関する。

#### 【背景技術】

### [00002]

2 つの金属板の間に接続部を介して半導体チップが設けられた半導体パッケージがある この半導体パッケージの放熱性を高めるためには、それぞれの金属板において露出して いる面積が大きいことが望ましい。一方で、接続部の厚みは、半導体パッケージの信頼性 に影響するため、組み立てられた半導体パッケージについて、接続部の厚みを調べること が望ましい。しかし、金属板の面積が増加すると、それぞれの金属板と半導体チップとの 間に設けられている接続部の厚みを調べることが困難となる。

【先行技術文献】

### 【特許文献】

### [0003]

【 特 許 文 献 1 】 特 開 2 0 0 6 - 2 1 6 6 4 1 号 公 報

#### 【発明の概要】

【発明が解決しようとする課題】

### [0004]

本発明が解決しようとする課題は、接続部の厚みを容易に調べることが可能な半導体パ ッ ケ ー ジ お よ び 半 導 体 パ ッ ケ ー ジ の 製 造 方 法 を 提 供 す る こ と で あ る 。

【課題を解決するための手段】

### [00005]

実 施 形 態 に 係 る 半 導 体 パ ッ ケ ー ジ は 、 第 1 金 属 板 と 、 半 導 体 チ ッ プ と 、 第 2 金 属 板 と 、 を有する。

前記第1金属板は、第1面を有する。

前 記 半 導 体 チ ッ プ は 、 前 記 第 1 面 の 上 に 設 け ら れ て い る 。 前 記 半 導 体 チ ッ プ は 、 第 1 電 極 お よ び 第 2 電 極 を 有 す る 。 前 記 半 導 体 チ ッ プ の 前 記 第 1 電 極 は 、 第 1 接 続 部 を 介 し て 前 記第1金属板と接続されている。

前記第2金属板は、第2面および第3面を有する。前記第2面は、前記第1面に平行な

10

20

30

40

第1方向と交差する。前記第3面は、前記第2面の反対側に設けられている。前記第3面は、前記第1方向と交差する。前記第2面には、前記第2面と平行であり前記第1面と交差する第2方向に延びる前記第1凹部が形成されている。前記第3面には、前記第2方向に延びる第2凹部が形成されている。前記第2金属板は、前記半導体チップの上に設けられている。前記第2金属板は、第2接続部を介して前記第2電極と接続されている。

### 【図面の簡単な説明】

- [0006]

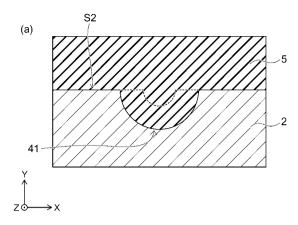

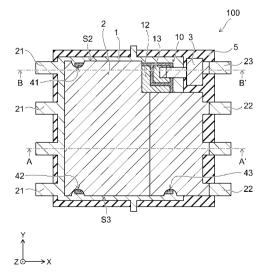

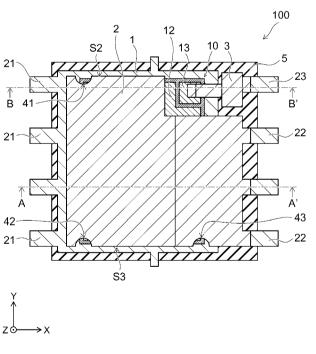

- 【図1】実施形態に係る半導体パッケージの平面図。

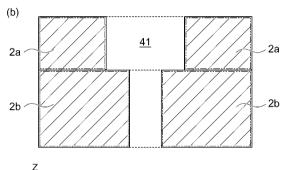

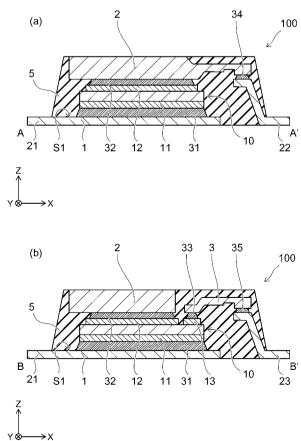

- 【図2】(a)は図1のA-A´断面図であり、(b)は図1のB-B´断面図である。

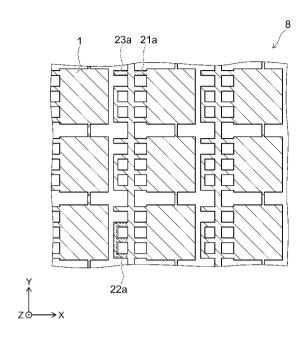

- 【 図 3 】 実 施 形 態 に 係 る 半 導 体 パ ッ ケ ー ジ の 製 造 工 程 を 表 す 工 程 平 面 図 で あ る 。

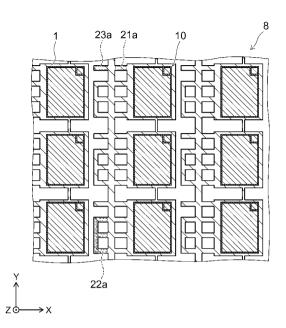

- 【 図 4 】 実 施 形 態 に 係 る 半 導 体 パ ッ ケ ー ジ の 製 造 工 程 を 表 す 工 程 平 面 図 で あ る 。

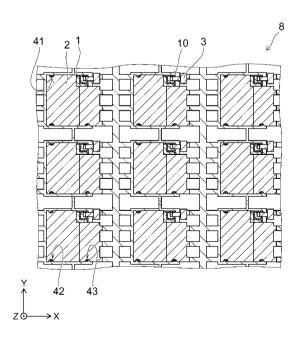

- 【図5】実施形態に係る半導体パッケージの製造工程を表す工程平面図である。

- 【図6】実施形態に係る半導体パッケージの製造工程を表す工程平面図である。

- 【図7】実施形態の変形例に係る半導体パッケージの一部を表す模式図である。

- 【発明を実施するための形態】

- [0007]

以下に、本発明の各実施形態について図面を参照しつつ説明する。

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

また、本願明細書と各図において、既に説明したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

各実施形態の説明には、XYZ直交座標系を用いる。第1金属板1が有する第1面S1に平行であり、互いに直交する2方向をX方向(第3方向)およびY方向(第1方向)とする。そして、X方向およびY方向に対して垂直な方向をZ方向(第2方向)とする。

- [0008]

- 図1および図2を用いて、実施形態に係る半導体パッケージについて説明する。

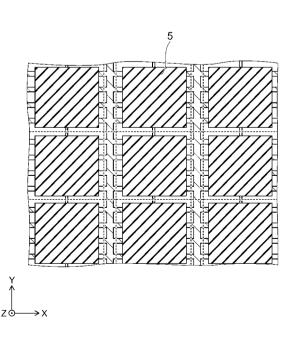

- 図1は、実施形態に係る半導体パッケージ100の平面図である。

- 図 2 ( a )は、図 1 の A A ´断面図であり、図 2 ( b )は、図 1 の B B ´断面図である。

なお、図1では、半導体パッケージ100の内部構造の説明のために、封止部5の一部 が省略されている。

[0009]

図1および図2に表すように、半導体パッケージ100は、第1金属板1と、第2金属板2と、金属部材3と、封止部5と、半導体チップ10と、第1リード端子21と、第2リード端子22と、第3リード端子23と、を有する。

[0010]

図2に表すように、半導体チップ10は、第1金属板1の第1面S1の上に設けられている。半導体チップ10は、例えば四角形であり、第1電極11、第2電極12、および第3電極13を有する。第2電極12および第3電極13は、第1電極11の反対側に設けられ、互いに離間している。第1電極11は、第1接続部31を介して第1金属板1と接続されている。

[0011]

図 2 ( a ) に表すように、第 2 金属板 2 は、半導体チップ 1 0 の上に設けられ、第 2 接続部 3 2 を介して第 2 電極 1 2 と接続されている。

図1および図2(b)に表すように、金属部材3は、半導体チップ10の上に、第2金属板2と離間して設けられている。金属部材3は、第3接続部33を介して第3電極13と接続されている。

[ 0 0 1 2 ]

第1リード端子21は、第1金属板1と接続されている。第1リード端子21はY方向

10

20

30

40

において複数設けられ、それぞれが X 方向に延びている。図 1 に表す例では、第 1 金属板 1 と第 1 リード端子 2 1 が一体に形成されているが、第 1 金属板 1 と第 1 リード端子 2 1 は、互いに異なる部材から構成されていてもよい。この場合、第 1 金属板 1 と第 1 リード端子 2 1 は、はんだやボンディングワイヤなどで接続される。

### [0013]

第2リード端子22は、第4接続部34を介して第2金属板2と接続されている。第2 リード端子22はY方向において複数設けられ、それぞれがX方向に延びている。

第3リード端子23は、第5接続部35を介して金属部材3と接続され、X方向に延びている。

図1および図2に表す例に限らず、第2金属板2と第2リード端子22は一体に形成されていてもよく、金属部材3と第3リード端子23も一体に形成されていてもよい。また、第2リード端子22および第3リード端子23は、第1リード端子21が延びている方向と異なる方向に延びていてもよい。

### [0014]

第 1 リード端子 2 1 の数、第 2 リード端子 2 2 の数、および第 3 リード端子 2 3 の数は、図 1 に表す例に限られず、任意である。

また、第1リード端子21、第2リード端子22、および第3リード端子23のそれぞれは、途中で屈曲した部分を有していてもよい。

### [0015]

封止部 5 は、第 1 金属板 1 の上および第 1 金属板 1 の周りに設けられ、半導体チップ 1 0、第 1 リード端子 2 1 ~第 3 リード端子 2 3 のそれぞれの一部、および第 2 金属板 2 の一部を覆っている。

### [0016]

次に、第2金属板2について、より具体的に説明する。

図1に表すように、第2金属板2は、互いに対向する第2面S2および第3面S3を有する。第2面S2および第3面S3は、Y方向と交差し、X方向およびZ方向に沿う面である。

#### [0017]

第2面S2には、第1凹部41が形成されており、第3面S3には、第2凹部42および第3凹部43が形成されている。第1凹部41と第2凹部42はY方向において並び、第2凹部42と第3凹部43はX方向において並んでいる。

### [0018]

第1凹部41~第3凹部43は、Z方向に延びている。より具体的には、第1凹部41は、第2面S2のZ方向の一端から他端に亘って形成されている。第2凹部42および第3凹部43は、第3面S3のZ方向の一端から他端に亘って形成されている。すなわち、第1凹部41は、第2面S2の上端から下端に亘って形成され、第2凹部42および第3凹部43は、第3面S3の上端から下端に亘って形成されている。

第1凹部41~第3凹部43は、封止部5で充填されている。

### [0019]

第1凹部41~第3凹部43のそれぞれの一部は、Z方向において、半導体チップ10 と並んでいる。他の表現によると、第1凹部41~第3凹部43のそれぞれを構成する面の一部が、Z方向において、半導体チップ10と並んでいる。

すなわち、第2金属板2は、封止部5を透過させてZ方向から半導体パッケージ100 を見た場合、第1凹部41~第3凹部43を通して半導体チップ10の上面が見えるよう に構成されている。

### [0020]

また、第2金属板2と金属部材3は、半導体チップ10の上に、X方向およびY方向において互いに離間して設けられている。このため、封止部5を透過させてZ方向から半導体パッケージ100を見た場合、第2金属板2と金属部材3との間の隙間から、半導体チップ10の上面を見ることができる。

10

20

30

00

40

#### [0021]

ここで、各構成要素の材料の一例について説明する。

第1金属板1、第2金属板2、金属部材3、および第1リード端子21~第3リード端子23は、銅などの金属を含む。

半導体チップ10は、シリコン、炭化シリコン、窒化ガリウム、またはガリウムヒ素を 主成分とする半導体素子を含む。

第 1 電極 1 1 ~ 第 3 電極 1 3 は、アルミニウムなどの金属材料を含む。

第1接続部31~第5接続部35は、はんだ材料を含む。

封止部5は、エポキシ樹脂などの絶縁性樹脂を含む。

### [0022]

次に、本実施形態に係る半導体パッケージの製造方法の一例について説明する。

図3~図6は、実施形態に係る半導体パッケージ100の製造工程を表す工程平面図である。

### [0023]

まず、図3に表すように、複数の第1金属板1を有するフレーム8を用意する。フレーム8は、さらに第1リード端子21~第3リード端子23のそれぞれに対応する、部分21a~23aを含んでいる。部分21aは第1金属板1と接しているのに対して、部分22aおよび部分23aは、X方向において第1金属板と離間している。フレーム8において、第1金属板1、部分21a~23aは、X方向およびY方向に配列されている。

### [0024]

次に、図4に表すように、それぞれの第1金属板1の上に半導体チップ10を配する。 このとき、半導体チップ10の第1電極11と、第1金属板1と、が第1接続部31によって接続される。

#### [0025]

次に、図5に表すように、それぞれの半導体チップ10の上に第2金属板2および金属部材3を配する。このとき、第2金属板2は、第2接続部32および第4接続部34によって、第2電極12と、部分22aと、に接続される。また、金属部材3は、第3接続部33および第5接続部35によって、第3電極13と、部分23aと、に接続される。

### [0026]

また、第2金属板2には、上述したように、第1凹部41~第3凹部43が形成されている。第2金属板2は、第1凹部41~第3凹部43のそれぞれの一部が、Z方向において半導体チップ10と並ぶように、配される。このとき、第1凹部41~第3凹部43が、Z方向において半導体チップ10のそれぞれの角部と並ぶように、第2金属板2を配することが望ましい。

第2金属板2を配した後は、第1凹部41~第3凹部43を通して、複数の個所で半導体チップ10の位置を測定する。

### [0027]

次に、図6に表すように、それぞれの半導体チップ10および第2金属板2を覆う封止部5を、互いに離間して配する。このとき、封止部5は、部分21a~部分23aのそれぞれの一部が露出するように、配される。

続いて、第2金属板2の上面が露出するまで、封止部5の上面を研削する。その後、図6に表す破線の位置でフレームを切断することで、図1および図2に表す半導体パッケージ100が得られる。

### [ 0 0 2 8 ]

ここで、本実施形態による作用および効果について説明する。

半導体パッケージ100において熱の発生と冷却が繰り返された場合、厚みが薄い部分で亀裂が生じやすい。これは、特に、各金属板および半導体チップ10との接触面積が大きい第1接続部31および第2接続部32において顕著である。これらの接続部で亀裂が生じると、導電性が低下するために、半導体パッケージの動作不良が起こる可能性がある

10

20

30

このため、接続部の厚みを測定し、接続部において局所的に薄い部分が存在しないか検査することが望ましい。一方で、放熱性を高めるために、第1金属板1の面積および第2金属板2の面積を大きくすると、接続部がこれらの金属板の間に隠れてしまい、接続部の厚みの測定が困難となる。

### [0029]

これに対して、本実施形態に係る半導体パッケージでは、第2金属板2に、第1凹部41および第2凹部42が形成されている。第2金属板2に、第1凹部41および第2凹部42が形成されていることで、これらの凹部を通して、半導体チップ10の上面の位置の測定が容易となる。

第1凹部41および第2凹部42を通して、少なくとも2か所の半導体チップ10の上面の位置を測定することで、半導体チップ10の傾きを求めることができる。半導体チップ10の傾きを求めることで、第1接続部31の厚みおよび第2接続部32の厚みの各点の厚みを推定することができる。

すなわち、本実施形態によれば、第2金属板2に、第1凹部41および第2凹部42が 形成されていることで、接続部の厚みを調べることが容易となる。

#### [0030]

また、第3面S3に、第2凹部42に加えて第3凹部43が形成されている場合、第1凹部41~第3凹部43を通して、3か所の半導体チップ10の上面の位置を検出することができる。このため、半導体チップ10のX-Z面内における傾きと、Y-Z面内における傾きと、を検出することが可能となる。この結果、第1接続部31の厚みおよび第2接続部32の厚みを、より精度よく調べることが可能となる。

#### 【 0 0 3 1 】

また、半導体チップ10の傾きをより精度よく求めるためには、第1凹部41~第3凹部43を通して、半導体チップ10のそれぞれの角部の位置を測定できることが望ましい。すなわち、第1凹部41~第3凹部43は、図1に表すように、2方向において、半導体チップ10のそれぞれの角部と並んでいることが望ましい。

### [0032]

なお、図2に表すように、半導体パッケージが金属部材3を有し、第2金属板2と金属部材3が離間して設けられている場合、第2金属板2と金属部材3との隙間を通して半導体チップ10の上面の位置を測定することができる。

従って、半導体パッケージが金属部材3を有する場合、第1凹部41および第2凹部42の少なくともいずれかが形成されていれば、第1接続部31の厚みおよび第2接続部32の厚みを調べることが可能となる。また、第1凹部41および第2凹部42の両方が形成されていれば、半導体チップ10のX-Z面内における傾きと、Y-Z面内における傾きと、を求めることが可能である。

### [0033]

ただし、その一方で、半導体チップ10が、反りを有する場合がある。この場合、半導体チップ10の傾きは一様ではない。従って、第1凹部41~第3凹部43に加えて、第2金属板2と金属部材3との隙間を通して半導体チップ10の上面の位置を測定し、各点における第1接続部31の厚みおよび第2接続部32の厚みを調べることが望ましい。

### [ 0 0 3 4 ]

また、半導体チップ10の上面の位置をより精度よく測定するためには、第1凹部41~第3凹部43のそれぞれの一部が、半導体チップ10と2方向において並んでおり、第2接続部32と2方向において並んでいないことが望ましい。

### [0035]

なお、図1および図2では、半導体チップ10が、第1電極11~第3電極13の3つの電極を有する場合の一例を表している。このような半導体チップ10として、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)や、IGBT(Insulated Gate Bipolar Transistor)がある。

本実施形態はこの例に限らず、半導体チップ10が、ダイオードなどの2つの電極を有

10

20

30

40

する場合についても適用可能である。この場合、半導体チップ10は、第3電極を有していなくても良く、半導体パッケージ100は、金属部材3および第3リード端子23を有していなくても良い。

#### [0036]

また、図1および図2に表す例では、第1凹部41~第3凹部43が、半円状に形成されていた。本実施形態に係る半導体パッケージはこれに限られず、第1凹部41~第3凹部43が、三角状や四角状など、半円以外の形状に形成されていてもよい。

また、第2金属板2には、第1凹部41~第3凹部43に加えて、さらに他の凹部が形成されていてもよい。

### [0037]

(変形例)

図 7 ( a ) は、実施形態の変形例に係る半導体パッケージの一部を表す平面図であり、図 7 ( b ) は、実施形態の変形例に係る半導体パッケージの一部を表す背面図である。

図 7 では、第 2 面 S 2 に設けられた第 1 凹部 4 1 近傍を拡大した様子が表されている。 また、図 7 ( a ) では、第 2 部分 2 b の一部を破線で表している。

#### [0038]

図7に表すように、変形例に係る半導体パッケージにおいて、第2金属板2は、第1部分2aおよび第2部分2bを有する。第1部分2aおよび第2部分2bは共に、第2面S2を有する部分である。第2部分2bは、第1部分2aと半導体チップ10との間に位置する。

[0039]

第1部分2aに形成された第1凹部41のX方向における長さは、第2部分2bに形成された第1凹部41のX方向における長さよりも、長い。

このため、第1部分2aにおいて第1凹部41の内側に設けられる封止部5の体積は、第2部分2bにおいて第1凹部41の内側に設けられる封止部5の体積よりも大きい。また、第2部分2bの一部は、Z方向において、封止部5の一部と他の一部との間に位置している。

#### [0040]

このような構成を採用することで、封止部 5 と第 2 金属板 2 の接触面積を大きくするとともに、第 2 金属板 2 を覆っている封止部 5 の面積を大きくすることができる。このため、封止部 5 によって第 2 金属板 2 をより強固に固定することが可能となる。

[0041]

ここでは、第1凹部41を例に挙げて説明したが、上述した第1凹部41の構造を、第2凹部42および第3凹部43に対して適用することも可能である。

[0042]

なお、半導体チップ10の上面の位置については、例えば、測定顕微鏡を用いて測定することが可能である。

[0043]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。実施形態に含まれる、例えば、第1金属板1、金属部材、封止部5、半導体チップ10、第1電極11、第2電極12、第3電極13、第1リード端子21、第2リード端子22、第3リード端子23、第1接続部31、第2接続部32、第3接続部334、第5接続部35などの各要素の具体的な構成に関しては、当業者が公知の技術から適宜選択することが可能である。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。また、前述の各実施形態は、相互に組み合わせて実施することができる。

### 【符号の説明】

20

10

30

40

### [0044]

1 0 0 … 半導体パッケージ 1 … 第 1 金属板 2 … 第 2 金属板 3 … 金属部材 5 … 封止部 1 0 … 半導体チップ 2 1 … 第 1 リード端子 2 2 … 第 2 リード端子 2 3 … 第 3 リード端子

## 【図1】

### 【図2】

【図3】 【図4】

## 【図5】

# 【図7】