(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5824135号

(P5824135)

(45) 発行日 平成27年11月25日(2015.11.25)

(24) 登録日 平成27年10月16日(2015.10.16)

(51) Int.Cl.

F 1

|                   |                  |                   |             |

|-------------------|------------------|-------------------|-------------|

| <b>H01L 25/07</b> | <b>(2006.01)</b> | <b>H01L 25/04</b> | <b>C</b>    |

| <b>H01L 25/18</b> | <b>(2006.01)</b> | <b>H01L 29/78</b> | <b>652T</b> |

| <b>H01L 29/12</b> | <b>(2006.01)</b> | <b>H01L 29/78</b> | <b>652Q</b> |

| <b>H01L 29/78</b> | <b>(2006.01)</b> |                   |             |

請求項の数 4 (全 43 頁)

|            |                                                                    |

|------------|--------------------------------------------------------------------|

| (21) 出願番号  | 特願2014-262313 (P2014-262313)                                       |

| (22) 出願日   | 平成26年12月25日 (2014.12.25)                                           |

| (62) 分割の表示 | 特願2013-535780 (P2013-535780)<br>の分割<br>原出願日 平成23年9月30日 (2011.9.30) |

| (65) 公開番号  | 特開2015-92609 (P2015-92609A)                                        |

| (43) 公開日   | 平成27年5月14日 (2015.5.14)                                             |

| 審査請求日      | 平成26年12月25日 (2014.12.25)                                           |

|           |                                                   |

|-----------|---------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>東京都江東区豊洲三丁目2番24号 |

| (74) 代理人  | 100080001<br>弁理士 筒井 大和                            |

| (74) 代理人  | 100113642<br>弁理士 菅田 篤志                            |

| (74) 代理人  | 100117008<br>弁理士 筒井 章子                            |

| (74) 代理人  | 100147430<br>弁理士 坂次 哲也                            |

| (72) 発明者  | 金澤 孝光<br>神奈川県川崎市中原区下沼部1753番地<br>ルネサスエレクトロニクス株式会社内 |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1面と、前記第1面とは反対側の第2面と、を有する第1金属プレートと、

第3面と、前記第3面とは反対側の第4面と、を有する第2金属プレートと、

前記第1金属プレートの前記第1面上に搭載された第1半導体チップと、

前記第2金属プレートの前記第3面上に搭載された第2半導体チップと、

第1リードと、

第2リードと、

前記第1金属プレートと連結された第3リードと、

前記第1半導体チップ、前記第2半導体チップ、前記第1リードの一部、前記第2リードの一部、および前記第3リードの一部を封止する封止体と、を有し、

前記第1半導体チップは、シリコンカーバイドを材料とし、第1ゲート電極と、第1ソースと、第1ドレインと、を有するノーマリオン型の接合FETを備え、且つ前記接合FETの前記第1ソースと電気的に接続された第1ソースパッド、および前記接合FETの前記第1ゲート電極と電気的に接続された第1ゲートパッドが形成された第1表面と、前記接合FETの前記第1ドレインと電気的に接続され、前記第1表面とは反対側の第1裏面と、を有し、

前記第2半導体チップは、シリコンを材料とし、第2ゲート電極と、第2ソースと、第2ドレインと、を有するノーマリオフ型のMOSFETを備え、且つ前記MOSFETの前記第2ソースと電気的に接続された第2ソースパッド、および前記MOSFETの前記

10

20

第2ゲート電極と電気的に接続された第2ゲートパッドが形成された第2表面と、前記MOSFETの前記第2ドレインと電気的に接続され、前記第2表面とは反対側の第2裏面と、を有し、

前記第1半導体チップの前記第1裏面が、第1導電性接着材を介して前記第1金属プレートの前記第1面上に搭載されていることにより、前記接合FETの前記第1ドレインは前記第3リードと電気的に接続され、

前記第2半導体チップの前記第2裏面が、第2導電性接着材を介して前記第2金属プレートの前記第3面上に搭載されていることにより、前記MOSFETの前記第2ドレインは前記第2金属プレートと電気的に接続され、

前記第1半導体チップの前記第1ゲートパッドは、第1ワイヤを介して前記第1リードと電気的に接続され、10

前記第2半導体チップの前記第2ソースパッドは、第2ワイヤを介して前記第1リードと電気的に接続されていることにより、前記第1半導体チップの前記第1ゲートパッドと電気的に接続され、

前記第2半導体チップの前記第2ゲートパッドは、第3ワイヤを介して前記第2リードと電気的に接続され、

前記第1半導体チップの前記第1ソースパッドは、第4ワイヤを介して前記第2金属プレートと電気的に接続され、

平面視において、前記第1半導体チップの前記第1ゲートパッドは、前記第2リードと前記第3リードより前記第1リードに近くなるように配置されている、半導体装置。20

### 【請求項2】

請求項1に記載の半導体装置において、

前記封止体は第1側面と、前記第1側面に対向する第2側面と、を有する直方体形状であって、

前記第1リード、前記第2リード、および前記第3リードのそれぞれの前記封止体に封止されていない部分は、前記第1側面から突出している、半導体装置。

### 【請求項3】

請求項2に記載の半導体装置において、

前記第1金属プレートの前記第2面、および前記第2金属プレートの前記第4面は封止体で覆われている、半導体装置。30

### 【請求項4】

請求項2に記載の半導体装置において、

前記第1金属プレートと前記第2金属プレートの間には封止体の一部が配置されている、半導体装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置に関し、特に、例えば、エアコンのインバータ、コンピュータ電源のDC/DCコンバータ、ハイブリッド自動車や電気自動車のインバータモジュールなどに使用されるパワー半導体装置に適用して有効な技術に関する。40

#### 【背景技術】

#### 【0002】

特表2000-506313号公報（特許文献1）には、低オン抵抗と高耐圧を両立させたスイッチング素子を提供する技術が記載されている。具体的に、特許文献1には、シリコンカーバイド（SiC）を材料とする接合FET（Junction Field Effect Transistor）と、シリコン（Si）を材料とするMOSFET（Metal Oxide Semiconductor Field Effect Transistor）をカスコード接続する構成が記載されている。

#### 【0003】

特開2008-198735号公報（特許文献2）には、低オン電圧で高耐圧の素子を提供するために、SiCを材料とするFETと、Siを材料とするダイオードとを直列接50

続する構成が記載されている。

#### 【0004】

特開2002-208673号公報（特許文献3）には、パワーモジュールの面積を削減するために、スイッチング素子と、ダイオードとを平板接続端子を挟んで積層する構造が記載されている。

#### 【0005】

特開2010-206100号公報（特許文献4）には、SiCを材料とするノーマリオフ型の接合FETのしきい値電圧を高くすることにより、誤点弧を防ぐ技術が記載されている。具体的には、SiC基板上に、接合FETとMOSFETとを配置し、接合FETのゲート電極に、MOSFETをダイオード接続するとしている。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】特表2000-506313号公報

【特許文献2】特開2008-198735号公報

【特許文献3】特開2002-208673号公報

【特許文献4】特開2010-206100号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

20

耐圧の向上とオン抵抗の低減の両立を図るスイッチング素子として、カスコード接続方式を使用したスイッチング素子がある。カスコード接続方式を使用したスイッチング素子は、例えば、シリコン(Si)よりもバンドギャップの大きな材料を使用したノーマリオン型の接合FET(Junction Field Effect Transistor)と、シリコン(Si)を使用したノーマリオフ型のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)とを直列接続した構成をしている。このカスコード接続方式のスイッチング素子によれば、絶縁耐圧の大きな接合FETにより耐圧を確保できるとともに、ノーマリオン型の接合FETによるオン抵抗の低減と、低耐圧なMOSFETによるオン抵抗の低減により、耐圧の向上とオン抵抗の低減を両立させたスイッチング素子を得ることができる。

#### 【0008】

30

このカスコード接続したスイッチング素子の実装構成においては、接合FETを形成した半導体チップと、MOSFETを形成した半導体チップとを、ボンディングワイヤで接続した構成が採用されている。この構成の場合、ボンディングワイヤに存在する寄生インダクタンスの影響や、接合FETのリーク電流の影響により、スイッチング時に、低耐圧であるMOSFETのソースとドレイン間に設計耐圧以上の大きさの電圧が印加されてしまうことを本発明者が新たに見出した。このように、低耐圧であるMOSFETに設計耐圧以上の電圧が印加されると、MOSFETが破壊されるおそれがあり、半導体装置の信頼性低下を招くことになる。

#### 【0009】

本発明の目的は、半導体装置の信頼性を向上できる技術を提供することにある。

40

#### 【0010】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【課題を解決するための手段】

#### 【0011】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0012】

一実施の形態における半導体装置は、接合FETを形成した半導体チップのゲートパッドが、他のリード(ゲートリードやドレインリード)よりもソースリードに近くなるよう

50

に配置されていることを特徴とするものである。

**【発明の効果】**

**【0013】**

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

**【0014】**

一実施の形態によれば、半導体装置の信頼性を向上できる。また、半導体装置の電気的特性の向上を図ることができる。

**【図面の簡単な説明】**

**【0015】**

10

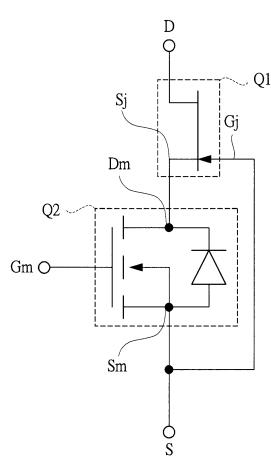

【図1】カスコード接続方式を採用したスイッチング素子の回路構成を示す図である。

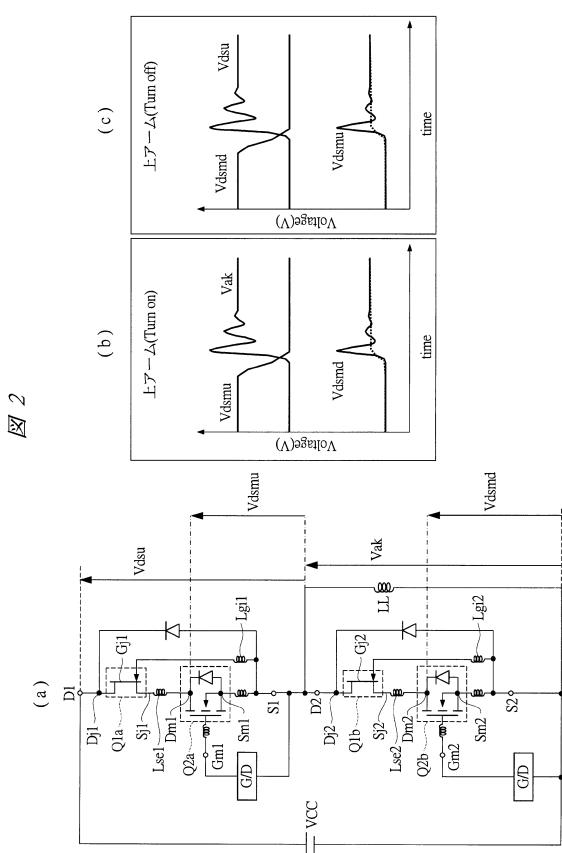

【図2】(a) カスコード接続した接合FETとMOSFETとをスイッチング素子として利用したインバータを示す回路図である。(b)は、上アームを構成するスイッチング素子をターンオンした場合の波形を示す図であり、(c)は、上アームを構成するスイッチング素子をターンオフした場合の波形を示す図である。

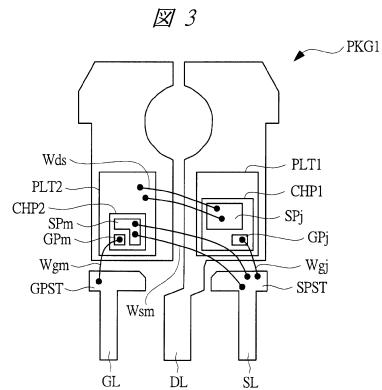

【図3】本発明の実施の形態1における半導体装置の実装構成を示す図である。

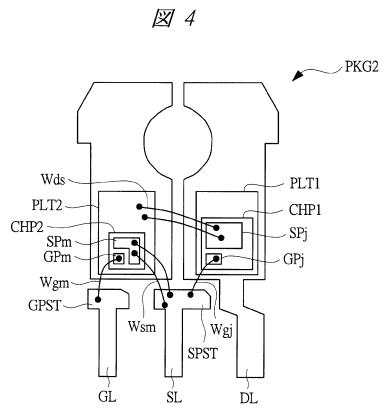

【図4】実施の形態1における他の半導体装置の実装構成を示す図である。

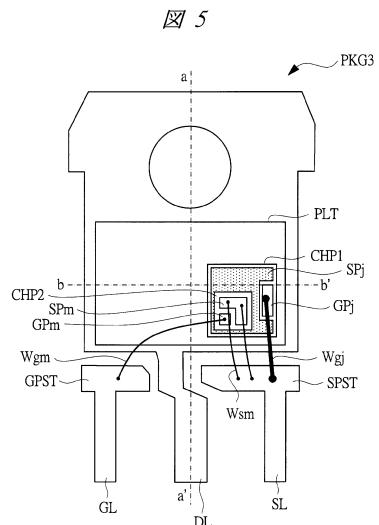

【図5】変形例1における半導体装置の実装構成を示す図である。

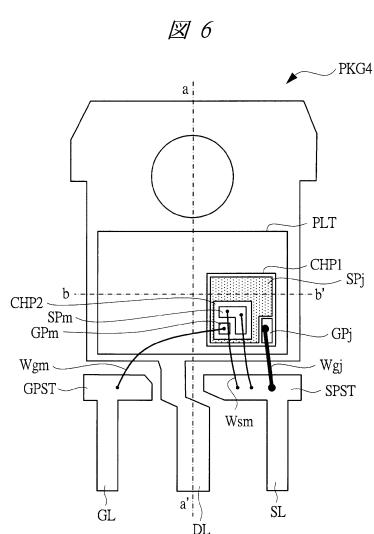

【図6】変形例1における他の半導体装置の実装構成を示す図である。

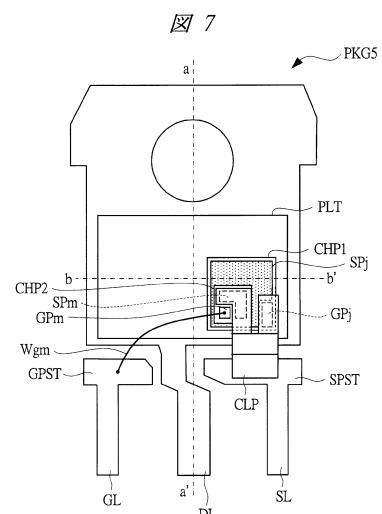

【図7】変形例1における他の半導体装置の実装構成を示す図である。

20

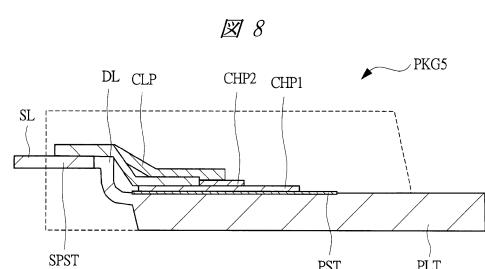

【図8】図7の一断面を示す断面図である。

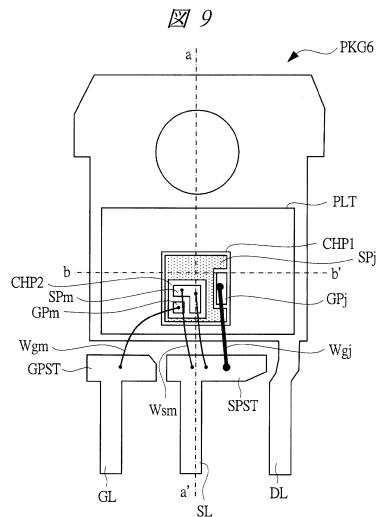

【図9】変形例1における他の半導体装置の実装構成を示す図である。

【図10】図9の一断面を示す断面図である。

【図11】変形例1における他の半導体装置の実装構成を示す図である。

【図12】(a)は、従来技術におけるスイッチング素子とともに寄生インダクタンスの存在位置を示す回路図であり、(b)は、実施の形態1におけるスイッチング素子とともに寄生インダクタンスの存在位置を示す回路図である。また、(c)は、本変形例1におけるスイッチング素子とともに寄生インダクタンスの存在位置を示す回路図である。

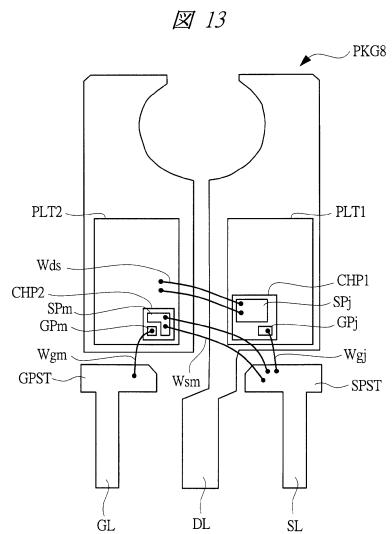

【図13】変形例2における半導体装置の実装構成を示す図である。

【図14】図13の一断面を示す断面図である。

30

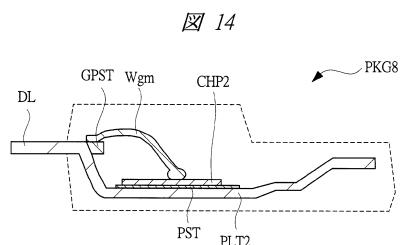

【図15】変形例2における他の半導体装置の実装構成を示す図である。

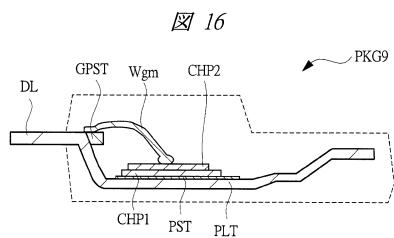

【図16】図15の一断面を示す断面図である。

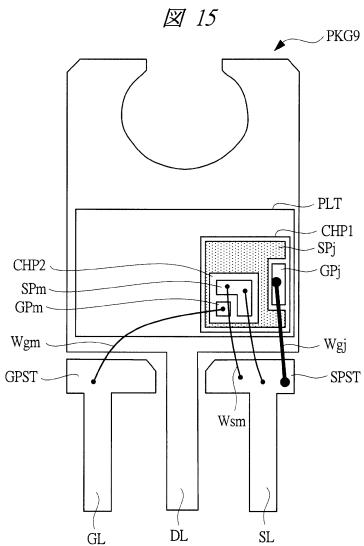

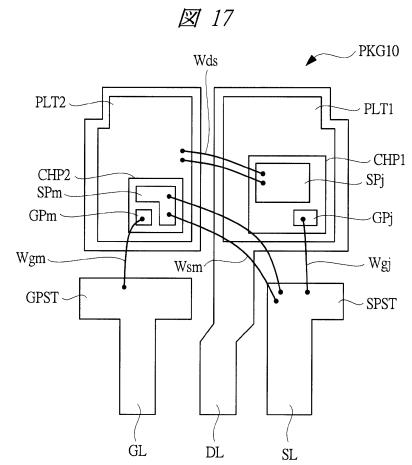

【図17】変形例3における半導体装置の実装構成を示す図である。

【図18】図17の一断面を示す断面図である。

【図19】変形例3における他の半導体装置の実装構成を示す図である。

【図20】図19の一断面を示す断面図である。

【図21】変形例4における半導体装置の実装構成を示す図である。

【図22】図21の一断面を示す断面図である。

【図23】変形例4における他の半導体装置の実装構成を示す図である。

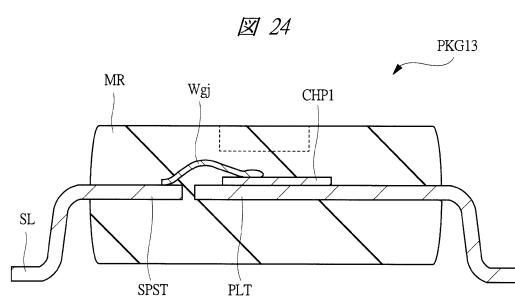

【図24】図23の一断面を示す断面図である。

40

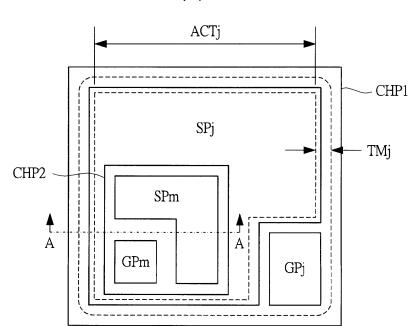

【図25】実施の形態2における積層半導体チップの構成を示す図である。

【図26】実施の形態2における積層半導体チップの他の構成を示す図である。

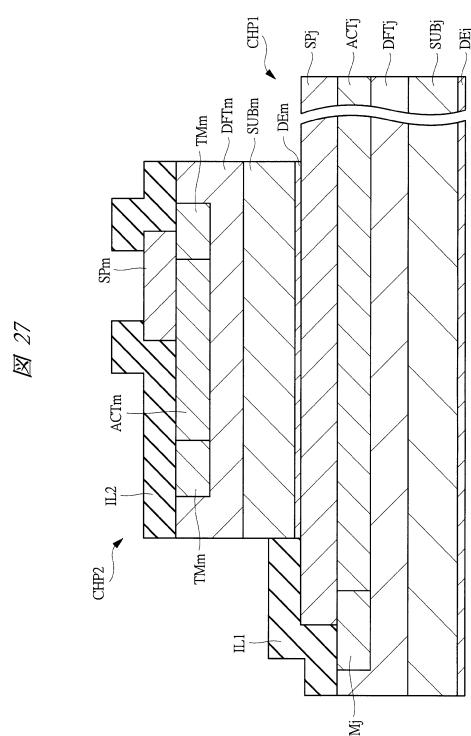

【図27】図25および図26のA-A線で切断した断面図である。

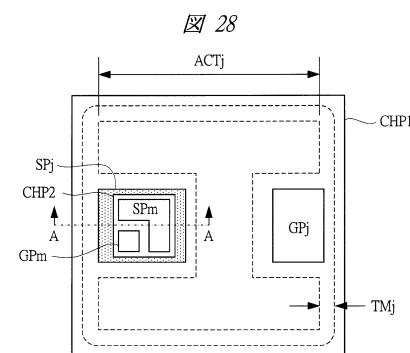

【図28】変形例における積層半導体チップの構成を示す図である。

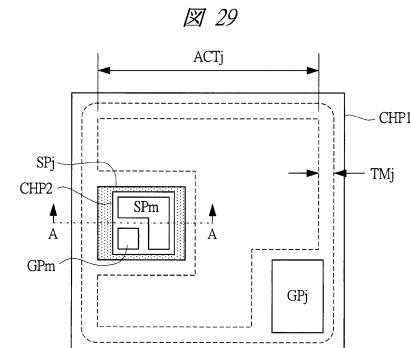

【図29】変形例における積層半導体チップの他の構成を示す図である。

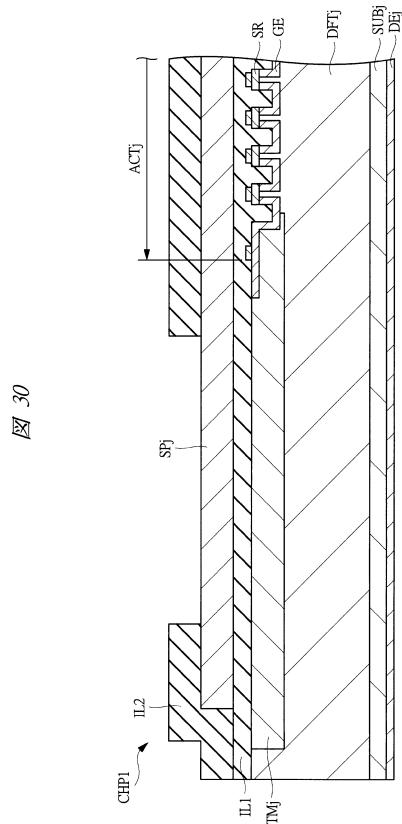

【図30】図28および図29のA-A線で切断した断面図である。

【図31】実施の形態2におけるMOSFETのデバイス構造を示す断面図である。

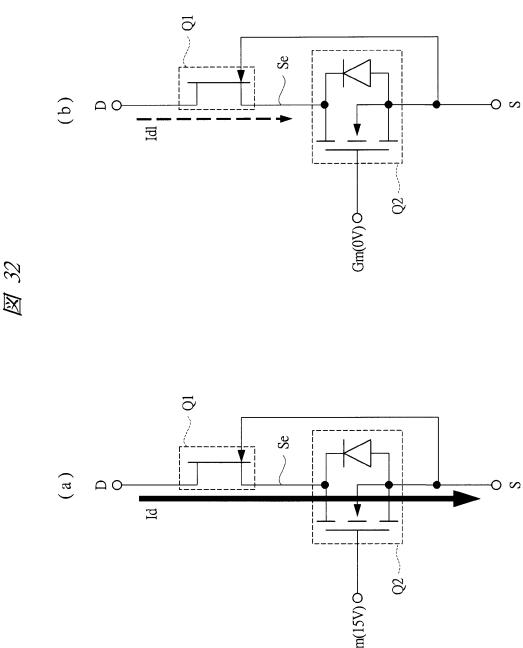

【図32】カスコード接続されたスイッチング素子における電流経路を示す図である。(a)は、オン時の電流経路を示す図であり、(b)は、オフ時に流れるリーク電流の電流経路を示す図である。

50

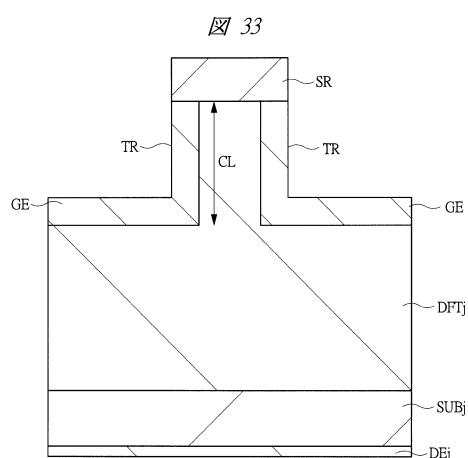

【図33】実施の形態2における接合FETのデバイス構造を示す断面図である。

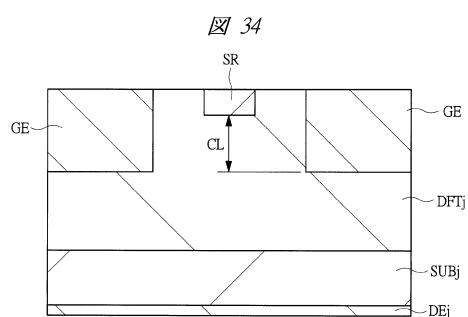

【図34】実施の形態2における接合FETの他のデバイス構造を示す断面図である。

【発明を実施するための形態】

【0016】

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

【0017】

また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

10

【0018】

さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。

【0019】

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

20

【0020】

また、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。なお、図面をわかりやすくするために平面図であってもハッチングを付す場合がある。

【0021】

（実施の形態1）

<本発明者が見出した課題の詳細>

地球環境保全という大きな社会潮流の中で、環境負荷を低減するエレクトロニクス事業の重要性が増している。中でもパワーデバイス（パワー半導体装置）は、鉄道車両、ハイブリッド自動車、電気自動車のインバータやエアコンのインバータ、パソコンなどの民生機器の電源に用いられており、パワーデバイスの性能改善は、インフラシステムや民生機器の電力効率改善に大きく寄与する。電力効率を改善するということは、システムの稼働に必要なエネルギー資源を削減できるということであり、言い換えれば、二酸化炭素の排出量削減、すなわち、環境負荷を低減できる。このため、パワーデバイスの性能改善に向けた研究開発が各社で盛んに行われている。

30

【0022】

一般的に、パワーデバイスは、大規模集積回路(LSI (Large Scale Integration))と同様に、シリコンを材料としている。しかし、近年では、シリコンよりもバンドギャップが大きいシリコンカーバイド(SiC)が注目されている。SiCは、バンドギャップが大きいため、絶縁破壊耐圧がシリコンの10倍程度ある。このことから、SiCを材料とするデバイスは、Siを材料とするデバイスよりも膜厚を薄くできる結果、導通時の抵抗値（オン抵抗値） $R_{on}$ を大幅に下げることができる。したがって、SiCを材料とするデバイスは、抵抗値 $R_{on}$ と導通電流*i*の積で表される導通損失( $R_{on} \times i^2$ )を大幅に削減することができ、電力効率の改善に大きく寄与できる。このような特徴に着目して、国内外で、SiCを使用したMOSFETやショットキーダイオードや接合FETの開発が進められている。

40

【0023】

特に、スイッチングデバイスに着目すると、SiCを材料とした接合FET(JFET)の製品化がいち早く進められている。この接合FETは、SiCを材料とするMOSFETと比較すると、例えば、酸化シリコン膜からなるゲート絶縁膜を必要としないため、酸

50

化シリコン膜とSiCとの界面における欠陥と、それに伴う素子特性の劣化に代表される問題を回避することができる。また、この接合FETは、pn接合による空乏層の伸びを制御してチャネルのオン／オフを制御できるため、ノーマリオフ型の接合FETと、ノーマリオン型の接合FETとを容易に作り分けることができる。このようにSiCを材料とした接合FETは、SiCを材料としたMOSFETと比較すると、長期信頼性にも優れています、また、デバイスを作りやすいという特徴を有する。

#### 【0024】

SiCを材料とした接合FETの中でも、ノーマリオン型の接合FETは、通常、チャネルがオンして電流が流れています、チャネルをオフする必要があるときにゲート電極に負電圧を印加してpn接合から空乏層を延ばしてチャネルをオフします。したがって、接合FETがなんらかの原因で壊れた場合、チャネルがオンしたまま電流が流れ続けることになります。通常、接合FETが壊れた場合には電流が流れないことが安全性（フェイルセーフ）の観点から望ましいが、ノーマリオン型の接合FETでは、接合FETが壊れた場合でも電流が流れ続けるので用途が限定されます。したがって、フェイルセーフの観点から、ノーマリオフ型の接合FETが望まれる。

10

#### 【0025】

しかしながら、ノーマリオフ型の接合FETは、次のような課題を有する。つまり、接合FETのゲート電極とソース領域は、それぞれp型半導体領域（ゲート電極）とn型半導体領域（ソース領域）とからなるpn接合ダイオード構造を有するため、ゲート電極とソース領域との間の電圧が3V程度になると、ゲート電極とソース領域との間の寄生ダイオードがオンします。この結果、ゲート電極とソース領域との間に大電流が流れることがあり、これによって、接合FETが過剰に発熱してしまい破壊するおそれがあります。このことから、接合FETをノーマリオフ型のスイッチング素子として利用するためには、ゲート電圧を2.5V程度の低い電圧に制限して、寄生ダイオードがオンしない状態、もしくは、ゲート電極とソース領域との間のダイオード電流が充分小さい状態で利用することが望ましい。なお、Siを材料とする通常のMOSFETでは0から15Vもしくは20V程度のゲート電圧を印加します。このため、ノーマリオフ型の接合FETを利用するためには、既存のMOSFETのゲート駆動回路に加えて、2.5V程度の電圧を生成する降圧回路（DC/DCコンバータ）や、レベル変換回路などを追加する必要があります。この設計変更、すなわち、部品の追加は、システム全体のコストを上昇させてしまうことがあります。このことから、長期信頼性に優れ、かつ、作りやすいという特徴を有する接合FETであるが、駆動するためのゲート電圧が一般的なMOSFETと大きく異なるため、接合FETを新たに利用する場合には、駆動回路等を含めた大きな設計変更が必要であり、そのため、システム全体のコストが上昇するという課題が存在します。

20

#### 【0026】

この問題を解決する方法として、カスコード接続方式があります。このカスコード接続方式は、SiCを材料としたノーマリオン型の接合FETと、Siを材料とした低耐圧MOSFETとを直列接続した方式です。このような接続方式を採用すると、ゲート駆動回路は低耐圧MOSFETを駆動することになりますので、ゲート駆動回路の変更は不要となります。一方、ドレインとソースとの間の耐圧は絶縁耐圧の高い接合FETの特性で決定することができます。さらには、カスコード接続した場合でも、接合FETの低いオン抵抗と、低耐圧MOSFETの低いオン抵抗の直列接続となるので、カスコード接続したスイッチング素子のオン抵抗も比較的小さく抑えることができる。このようにカスコード接続方式は、ノーマリオフ型の接合FETの問題点を解決できる可能性があります。

30

#### 【0027】

図1は、カスコード接続方式を採用したスイッチング素子の回路構成を示す図である。図1に示すように、カスコード接続方式を採用したスイッチング素子は、ソースSとドレインD間にノーマリオン型の接合FET Q1と、ノーマリオフ型のMOSFET Q2が直列接続された構成をしている。具体的には、ドレインD側に接合FET Q1が配置され、ソースS側にMOSFET Q2が配置されている。つまり、接合FET Q1のソースS側にMOSFET Q2が配置されています。

40

50

は、MOSFET Q2のドレインDmと接続されており、MOSFET Q2のソースSmがスイッチング素子のソースSと接続されている。また、接合FET Q1のゲート電極Gjは、スイッチング素子のソースSと接続されており、MOSFET Q2のゲート電極Gmがゲート駆動回路（図示せず）と接続されている。

#### 【0028】

なお、図1に示すように、MOSFET Q2と逆並列にフリーホイールダイオードが接続されている。このフリーホイールダイオードは、逆方向電流を還流させてインダクタンスに蓄積されるエネルギーを開放する機能を有している。すなわち、図1に示すスイッチング素子がインダクタンスを含む負荷に接続された場合、スイッチング素子をオフすると、負荷に含まれるインダクタンスによって、MOSFET Q2の電流が流れる方向と逆方向の逆方向電流が発生する。このことから、MOSFET Q2と逆並列にフリーホイールダイオードを設けることにより、逆方向電流を還流させてインダクタンスに蓄積されるエネルギーを開放している。10

#### 【0029】

このような接続方式がカスコード接続方式であり、カスコード接続方式が採用されたスイッチング素子によれば、まず、ゲート駆動回路（図示せず）がMOSFET Q2のゲート電極Gmを駆動することになるため、MOSFET 単体をスイッチング素子として利用する場合からのゲート駆動回路の変更が不要となる利点がある。

#### 【0030】

さらに、接合FET Q1が、シリコン(Si)よりもバンドギャップの大きなシリコンカーバイド(SiC)に代表される物質を材料として使用しているため、接合FET Q1の絶縁耐圧が大きくなる。このことから、カスコード接続されたスイッチング素子の耐圧は、主に、接合FET Q1の特性で決定される。したがって、接合FET Q1と直列接続されているMOSFET Q2に要求される絶縁耐圧を、MOSFET 単体を使用したスイッチング素子よりも低くすることができる。すなわち、スイッチング素子として絶縁耐圧が必要とされる場合であっても、MOSFET Q2として低耐圧（例えば、数十V程度）のMOSFETを使用することができる。このため、MOSFET Q2のオン抵抗を低減することができる。さらに、接合FET Q1がノーマリオン型の接合FETから構成されるため、接合FET Q1のオン抵抗も低減することができる。この結果、カスコード接続されたスイッチング素子によれば、ゲート駆動回路の設計変更が不要になる利点を有するとともに、絶縁耐性の確保とオン抵抗の低減の両立を図ることができ、これによって、半導体素子（スイッチング素子）の電気的特性の向上を図ることができる。2030

#### 【0031】

また、図1に示すように、カスコード接続された接合FET Q1は、ノーマリオン型の接合FET Q1であり、接合FET Q1のゲート電極Gjがスイッチング素子のソースSと電気的に接続されている。この結果、接合FET Q1のゲート電極GjとソースSとの間の電圧は、スイッチング時（オン時）でも順バイアスされない。このことから、カスコード接続では、接合FET Q1の寄生ダイオードによる大電流が流れないと、過剰な発熱によるスイッチング素子の破壊を抑制することができる。すなわち、ノーマリオフ型の接合FETでは、スイッチング時（オン時）に、ソースSに対してゲート電極Gjに正電圧を印加する。このとき、接合FET Q1のソース領域はn型半導体領域から形成され、ゲート電極Gjはp型半導体領域から形成されていることから、ソースSに対してゲート電極Gjに正電圧を印加するということは、ソース領域とゲート電極Gjの間に順方向電圧（順バイアス）が印加されることを意味する。このため、ノーマリオフ型の接合FETでは、順方向電圧をあまり大きくしすぎると、ソース領域とゲート電極Gjからなる寄生ダイオードがオンしてしまう。この結果、ゲート電極Gjとソース領域との間に大電流が流れる場合があり、接合FETが過剰に発熱して破壊に至る可能性がある。これに対し、カスコード接続されたスイッチング素子では、ノーマリオン型の接合FET Q1を使用しており、ゲート電極Gjがスイッチング素子のソースSと電気的に接続されている。このことから、接合FET Q1のゲート電極GjとソースSとの間の電圧は、スイッチング時4050

(オン時)でも順バイアスされない。したがって、カスコード接続では、接合FETQ1の寄生ダイオードによる大電流が流れないとため、過剰な発熱によるスイッチング素子の破壊を抑制することができる。

#### 【0032】

このようにカスコード接続されたスイッチング素子は、上述した様々な利点を有するが、本発明者が検討した結果、以下に示す課題を新たに見出した。すなわち、カスコード接続を実現するためには、接合FETQ1を形成した半導体チップと、低耐圧なMOSFETQ2を形成した半導体チップとをボンディングワイヤで接続する必要がある。このため、例えば、低耐圧なMOSFETQ2のドレインDmと、接合FETQ1のソースSjは、ボンディングワイヤを介して接続される。この場合、接合FETQ1のソースSjには、ボンディングワイヤによる寄生インダクタンスが付加されてしまう。このような寄生インダクタンスが付加されると、スイッチング時に大きなサージ電圧が発生し、これによって、低耐圧なMOSFETQ2に耐圧以上の電圧が印加されることになる。この結果、低耐圧なMOSFETQ2がアバランシェモードで動作して、ゲート電極Gmでは制御できない大電流が低耐圧なMOSFETQ2に流れて素子破壊に至るおそれがあることを本発明者が新たに見出したのである。以下に、このメカニズムについて、詳細に説明する。

#### 【0033】

##### <課題の発生するメカニズム>

図2(a)は、カスコード接続した接合FETとMOSFETとをスイッチング素子として利用したインバータを示す回路図である。図2(a)に示すインバータは、電源VCcに直列接続された上アームと下アームとを有している。上アームは、ドレインD1とソースS1との間に接続されたスイッチング素子から構成されている。上アームを構成するスイッチング素子は、カスコード接続された接合FETQ1aとMOSFETQ2aから構成されている。具体的には、接合FETQ1aのドレインDj1がスイッチング素子のドレインD1と接続され、接合FETQ1aのソースSj1がMOSFETQ2aのドレインDm1と接続されている。そして、MOSFETQ2aのソースSm1がスイッチング素子のソースS1と接続されている。また、接合FETQ1aのゲート電極Gj1は、スイッチング素子のソースS1と接続され、MOSFETQ2aのゲート電極Gm1と、スイッチング素子のソースS1との間にはゲート駆動回路(G/D)が接続されている。

#### 【0034】

ここで、接合FETQ1aのソースSj1と、MOSFETQ2aのドレインDm1との間にはボンディングワイヤに基づく寄生インダクタンスLse1が存在し、接合FETQ1aのゲート電極Gj1と、スイッチング素子のソースS1との間には、ボンディングワイヤに基づく寄生インダクタンスLgi1が存在する。なお、図2(a)において、スイッチング素子のソースS1と、スイッチング素子のドレインD1との間の電圧を電圧Vdsuと定義し、スイッチング素子のソースS1とMOSFETQ2aのドレインDm1との間の電圧を電圧Vdsmuと定義する。

#### 【0035】

同様に、図2(a)に示すように、下アームは、ドレインD2とソースS2との間に接続されたスイッチング素子から構成されている。下アームを構成するスイッチング素子は、カスコード接続された接合FETQ1bとMOSFETQ2bから構成されている。具体的には、接合FETQ1bのドレインDj2がスイッチング素子のドレインD2と接続され、接合FETQ1bのソースSj2がMOSFETQ2bのドレインDm2と接続されている。そして、MOSFETQ2bのソースSm2がスイッチング素子のソースS2と接続されている。また、接合FETQ1bのゲート電極Gj2は、スイッチング素子のソースS2と接続され、MOSFETQ2bのゲート電極Gm2と、スイッチング素子のソースS2との間にはゲート駆動回路(G/D)が接続されている。さらに、スイッチング素子のソースS2と、スイッチング素子のドレインD2の間には負荷インダクタンスLlが接続されている。

#### 【0036】

10

20

30

40

50

ここで、接合FETQ1bのソースSj2と、MOSFETQ2bのドレインDm2との間にはボンディングワイヤに基づく寄生インダクタンスLse2が存在し、接合FETQ1bのゲート電極Gj2と、スイッチング素子のソースS2との間には、ボンディングワイヤに基づく寄生インダクタンスLgi2が存在する。なお、図2(a)において、スイッチング素子のソースS2と、スイッチング素子のドレインD2との間の電圧を電圧Vakと定義し、スイッチング素子のソースS2とMOSFETQ2bのドレインDm2との間の電圧を電圧Vdsmdと定義する。

#### 【0037】

カスコード接続されたスイッチング素子を利用したインバータは上記のように構成されており、以下に、このインバータの動作を説明しながら、課題の発生するメカニズムについて説明する。まず、上アームを構成するスイッチング素子をターンオンする場合について説明する。すなわち、上アームを構成するスイッチング素子をオンする一方、下アームを構成するスイッチング素子をオフすることにより、負荷（負荷インダクタンスを含む）に電源電圧を印加する場合について説明する。

#### 【0038】

図2(b)は、上アームを構成するスイッチング素子をターンオンした場合の波形を示している。具体的に、上アームを構成するスイッチング素子をターンオンすると、上アームを構成する接合FETQ1aおよびMOSFETQ2aがオンするため、接合FETQ1aのドレインDj1から、MOSFETQ2aのドレインDm1およびソースSm1を経由して、負荷インダクタンスLLを通り、電源VCCに戻るという経路で還流電流が流れれる。このとき、図2(b)に示すように、電圧Vdsmuは、所定電圧から0V程度に変化する一方、電圧Vakは、上アームのスイッチング素子をオフしている際の0Vから電源電圧程度の電圧まで上昇する。この結果、下アームのMOSFETQ2bのドレイン電圧である電圧Vdsmdは、下アームの接合FETQ1bをカットオフする電圧まで上昇し、下アームの接合FETQ1bがオフした後は、ある一定の電圧を維持する。この電圧Vdsmdの変化は、寄生インダクタンスが無視できる理想状態の変化であり、図2(b)の破線で示されている。ところが、寄生インダクタンスLse2や寄生インダクタンスLgi2が大きくなると、図2(b)の実線で示すように、電圧Vdsmdは、上アームのスイッチング素子をターンオンした際、急激に大きく上昇する。

#### 【0039】

一方、図2(c)は、上アームを構成するスイッチング素子をターンオフした場合の波形を示している。具体的に、上アームを構成するスイッチング素子をターンオフすると、図2(c)に示すように、電圧Vdsmdは、所定電圧から0V程度に変化する一方、電圧Vdsuは、上アームのスイッチング素子をオンしている際の0Vから電源電圧程度の電圧まで上昇する。この結果、上アームのMOSFETQ2aのドレイン電圧である電圧Vdsmuは、上アームの接合FETQ1aをカットオフする電圧まで上昇し、上アームの接合FETQ1aがオフした後は、ある一定の電圧を維持する。この電圧Vdsmuの変化は、寄生インダクタンスが無視できる理想状態の変化であり、図2(c)の破線で示されている。ところが、寄生インダクタンスLse1や寄生インダクタンスLgi1が大きくなると、図2(c)の実線で示すように、電圧Vdsmuは、上アームのスイッチング素子をターンオフした際、急激に大きく上昇する。

#### 【0040】

このように、上アームのスイッチング素子をターンオンする場合には、ターンオフする下アームのMOSFETQ2bのドレイン電圧である電圧Vdsmdが急激に上昇する現象が生じ、上アームのスイッチング素子をターンオフする場合には、ターンオフする上アームのMOSFETQ2aのドレイン電圧である電圧Vdsmuが急激に上昇する現象が生じることがわかる。これらの現象が生じるメカニズムは同様であるため、以下では、上アームのスイッチング素子をターンオンする場合に着目して、ターンオフする下アームのMOSFETQ2bのドレイン電圧である電圧Vdsmdが急激に上昇する現象が生じるメカニズムについて説明する。この現象が生じるメカニズムとしては、次に示す3つのメ

10

20

30

40

50

カニズムが考えられる。

**【0041】**

第1のメカニズムは、下アームを構成する接合FETQ1bのソースSj2と、下アームを構成するMOSFETQ2bのドレインDm2の間に存在する寄生インダクタンスLse2に起因している。具体的に、上アームのスイッチング素子をターンオンする際、下アームのMOSFETQ2bはオフされる。このとき、電圧Vakは0V程度から増加し始め、この電圧Vakの増加に伴って、下アームのMOSFETQ2bのドレイン電圧である電圧Vdsmも増加し始める。しかしながら、電圧Vdsmが増加する初期段階においては、電圧Vdsmが、接合FETQ1bのゲート電極Gj2に印加されているゲート電圧よりも所定値以上大きくなっているため、接合FETQ1bはカットオフされず、接合FETQ1bのドレインDj2からソースSj2に向って電流が流れる。この結果、MOSFETQ2bのドレインDm2に電流が流れ込み、電荷が蓄積される。このことから、MOSFETQ2bのドレイン電圧である電圧Vdsmが上昇する。そして、この電圧Vdsmが上昇し続けて、接合FETQ1bのゲート電圧よりも所定値以上大きくなると、接合FETQ1bがカットオフされて、それ以上電流が流れなくなる。つまり、電圧Vdsmが増加する初期段階においては、接合FETQ1bのドレインDj2とソースSj2の間に電流が流れ、MOSFETQ2bのドレインDm2に電荷が蓄積されるため、電圧Vdsmが増加する。その後、電圧Vdsmが増加するにつれて、電圧Vdsmが、接合FETQ1bのゲート電圧よりも所定値以上の大きさになる状態に近づくため、接合FETQ1bのドレインDj2とソースSj2に流れる電流が次第に減少していく。そして、最終的に、電圧Vdsmが、接合FETQ1bのゲート電圧よりも所定値以上大きくなることによって、接合FETQ1bがカットオフされる。接合FETQ1bがカットオフされた後は、MOSFETQ2bのドレインDm2に流入する電荷がなくなるため、電圧Vdsmは、ほぼ一定となる。

**【0042】**

このように、上アームのスイッチング素子をターンオンする際、下アームのMOSFETQ2bはオフされるが、この段階で、下アームの接合FETQ1bは直ちにカットオフされず、接合FETQ1bのドレインDj2からソースSj2に電流が流れる。そして、接合FETQ1bのソースSj2に流れ込んだ電流は、寄生インダクタンスLse2を介して、MOSFETQ2bのドレインDm2に流れ込む。このとき、着目すべき点は、下アームの接合FETQ1bのドレインDj2からソースSj2に流れる電流が減少するという点である。このことは、寄生インダクタンスLse2に流れる電流も時間とともに減少することを意味している。この結果、寄生インダクタンスLse2においては、電流の減少を打ち消すような起電力が発生する。すなわち、寄生インダクタンスLse2は、接合FETQ1bのドレインDj2からソースSj2に流れる電流を増加させるように機能する。このため、寄生インダクタンスLse2が大きくなると、過渡的に、接合FETQ1bのドレインDj2からソースSj2に向って大きな電流が流れる。この結果、MOSFETQ2bのドレインDm2に流入する電荷が急激に増加し、これによって、電圧Vdsmが急激に増加するのである。これが第1のメカニズムである。

**【0043】**

続いて、第2のメカニズムは、下アームを構成する接合FETQ1bのゲート電極Gj2と、下アームのソースS2との間に存在する寄生インダクタンスLgi2に起因している。具体的に、上アームのスイッチング素子をターンオンする際、下アームのMOSFETQ2bはオフされる。このとき、電圧Vakは0V程度から増加し始めるが、例えば、図2(b)に示すように、上アームのスイッチング素子をターンオンした初期段階において、電圧Vakは電源電圧を超える範囲まで振動する。これは、インバータに接続されている負荷に含まれる負荷インダクタンスLLに起因する逆起電力に基づくものである。したがって、電圧Vakは、上アームをターンオンする際の初期段階で変動することになる。ここで、接合FETQ1bに着目すると、接合FETQ1bのドレインDj2とゲート電極Gj2の間に寄生容量が形成されており、電圧Vakが変動すると、この寄生容量に

10

20

30

40

50

印加される電圧も変動する。そして、この寄生容量の静電容量値は比較的大きな値となるため、寄生容量に印加される電圧変動に伴って発生する充放電電流も大きくなる。この充放電電流は、接合FETQ1bのゲート電極Gj2と下アームのソースS2との間に流れれる。このとき、充放電電流は、時間的に変化する電流である。このため、例えば、接合FETQ1bのゲート電極Gj2と下アームのソースS2との間に寄生インダクタンスLgi2が存在すると、時間的に変化する充放電電流が寄生インダクタンスLgi2を流れれるため、寄生インダクタンスLgi2の大きさと充放電電流の時間微分の積に比例した抵抗成分が、接合FETQ1bのゲート電極Gj2と下アームのソースS2の間に発生する。この結果、接合FETQ1bのゲート電極Gj2と下アームのソースS2が同電位にならず、接合FETQ1bのゲート電極Gj2が下アームのソースS2に対して正電圧方向に上昇するモードが発生する。この場合、接合FETQ1bのゲート電極Gj2が正電圧となるため、接合FETQ1bのゲート電極Gj2から伸びる空乏層が抑制されて、チャネル領域の幅が大きくなる。このため、過渡的に、接合FETQ1bのドレインDj2からソースSj2に向って流れる電流が大きくなる。この結果、MOSFETQ2bのドレインDm2に流入する電荷が急激に増加し、これによって、電圧Vdsmが急激に増加するのである。これが第2のメカニズムである。さらに、第2のメカニズムによれば、接合FETQ1bのゲート電極Gj2に正電圧が印加されることから、接合FETQ1bをカットオフするためには、ゲート電極Gj2に0Vが印加されている場合よりも大きな電圧が接合FETQ1bのソースSj2に印加されなくてはならないことになる。この観点からも、接合FETQ1bがカットオフされるまで上昇する電圧Vdsmが大きくなる。10

#### 【0044】

さらに、第3のメカニズムは、下アームを構成する接合FETQ1bのゲート電極Gj2と、下アームのソースS2との間に存在する寄生抵抗に起因している。第2のメカニズムで説明したように、接合FETQ1bのゲート電極Gj2と下アームのソースS2との間に充放電電流が流れれる。このことから、接合FETQ1bのゲート電極Gj2と、下アームのソースS2との間に寄生抵抗が存在すると、この寄生抵抗に充放電電流が流れ、電圧降下が生じる。この結果、接合FETQ1bのゲート電極Gj2と下アームのソースS2が同電位にならず、接合FETQ1bのゲート電極Gj2が下アームのソースS2に対して正電圧方向に上昇するモードが発生する。これにより、第3のメカニズムでも、第2のメカニズムと同様に、接合FETQ1bのゲート電極Gj2が正電圧となるため、接合FETQ1bのゲート電極Gj2から伸びる空乏層が抑制されて、チャネル領域の幅が大きくなる。したがって、過渡的に、接合FETQ1bのドレインDj2からソースSj2に向って流れる電流が大きくなる。この結果、MOSFETQ2bのドレインDm2に流入する電荷が急激に増加し、これによって、電圧Vdsmが急激に増加するのである。20

#### 【0045】

以上のように、寄生インダクタンスLse2、寄生インダクタンスLgi2および寄生抵抗に関する第1のメカニズムから第3のメカニズムによって、電圧Vdsmが急激に増加することがわかる。このように、寄生インダクタンスLse2、寄生インダクタンスLgi2および寄生抵抗が大きくなると、下アームのMOSFETQ2bのドレイン電圧である電圧Vdsmが、MOSFETQ2bの耐圧以上の電圧まで上昇し、これによって、下アームのMOSFETQ2bがアバランシェ動作し、最終的に、下アームのMOSFETQ2bが破壊されるおそれがあるのである。30

#### 【0046】

具体的には、MOSFETQ2bに耐圧以上の電圧が印加されると、MOSFETQ2bの内部に電界集中する領域が局所的に発生し、この領域でインパクトイオン化による正孔電子対が大量に発生する。この大量に発生した正孔電子対によって、ソース領域(n型半導体領域)、チャネル形成領域(p型半導体領域)およびドリフト領域(n型半導体領域)によって形成される寄生n-p-nバイポーラトランジスタがオンする。寄生n-p-nバイポーラトランジスタがオンしたセル(MOSFETQ2b)では、MOSFETQ2bの40

ゲート電極 G m 2 では制御することができない大電流が流れ発熱する。このとき、発熱による温度上昇により半導体領域の電気抵抗が小さくなるために、さらに大きな電流が流れるという正帰還が起こる。この結果、大電流が局的に流れ、MOSFET Q 2 b の破壊が起こる。この現象がアバランシェ破壊である。このようなアバランシェ破壊が発生すると、半導体装置の信頼性低下を招くことになる。

#### 【0047】

そこで、本実施の形態 1 では、アバランシェ破壊の原因となる MOSFET への絶縁耐圧以上の電圧印加を抑制するため、寄生インダクタンスおよび寄生抵抗を低減する工夫を施している。以下に、この工夫を施した本実施の形態 1 における技術的思想について説明する。本実施の形態 1 では、半導体装置の実装構成に工夫を施した点に特徴があり、この特徴点を含む半導体装置の実装構成について説明する。10

#### 【0048】

<本実施の形態 1 における半導体装置の実装構成>

図 3 は、本実施の形態 1 におけるパッケージ（半導体装置）PKG 1 の実装構成を示す図である。図 3 に示すように、本実施の形態 1 におけるパッケージ PKG 1 は、互いに電気的に絶縁された 2 つのチップ搭載部 PLT 1 とチップ搭載部 PLT 2 を有している。図 3 において、右側に配置されている金属プレートがチップ搭載部 PLT 1 を構成し、左側に配置されている金属プレートがチップ搭載部 PLT 2 を構成している。チップ搭載部 PLT 1 は、ドレインリード DL と連結されるように一体的に形成されており、チップ搭載部 PLT 1 とドレインリード DL とは電気的に接続されている。そして、このドレインリード DL を離間して挟むように、ソースリード SL とゲートリード GL が配置されている。具体的には、図 3 に示すように、ドレインリード DL の右側にソースリード SL が配置され、ドレインリード DL の左側にゲートリード GL が配置されている。これらのドレインリード DL、ソースリード SL、および、ゲートリード GL は、互いに電気的に絶縁されている。そして、ソースリード SL の先端部には、幅広領域からなるソースリードポスト部 SPS が形成され、ゲートリード GL の先端部には、幅広領域からなるゲートリードポスト部 GPS が形成されている。20

#### 【0049】

次に、チップ搭載部 PLT 1 上には、例えば、銀ペーストや半田からなる導電性接着材を介して、半導体チップ CHP 1 が搭載されている。この半導体チップ CHP 1 には、例えば、SiC を材料とした接合 FET が形成されている。そして、半導体チップ CHP 1 の裏面がドレイン電極となっており、半導体チップ CHP 1 の表面（正面）にソースパッド S P j とゲートパッド G P j が形成されている。つまり、半導体チップ CHP 1 には、カスコード接続方式をしたスイッチング素子の一部を構成する接合 FET が形成されており、この接合 FET のドレインと電気的に接続されるドレイン電極が半導体チップ CHP 1 の裏面に形成され、接合 FET のソースと電気的に接続されるソースパッド S P j 、および、接合 FET のゲート電極と電気的に接続されるゲートパッド G P j が半導体チップ CHP 1 の表面に形成されている。30

#### 【0050】

続いて、チップ搭載部 PLT 2 上には、例えば、銀ペーストや半田からなる導電性接着材を介して、半導体チップ CHP 2 が搭載されている。この半導体チップ CHP 2 には、例えば、Si を材料とした MOSFET が形成されている。このとき、半導体チップ CHP 2 の裏面がドレイン電極となっており、半導体チップ CHP 2 の表面（正面）にソースパッド S P m とゲートパッド G P m が形成されている。つまり、半導体チップ CHP 2 には、カスコード接続方式をしたスイッチング素子の一部を構成する MOSFET が形成されており、このMOSFET のドレインと電気的に接続されるドレイン電極が半導体チップ CHP 2 の裏面に形成され、MOSFET のソースと電気的に接続されるソースパッド S P m 、および、MOSFET のゲート電極と電気的に接続されるゲートパッド G P m が半導体チップ CHP 2 の表面に形成されている。40

#### 【0051】

50

そして、チップ搭載部 P L T 1 上に搭載された半導体チップ C H P 1 と、チップ搭載部 P L T 2 上に搭載された半導体チップ C H P 2 と、ボンディングワイヤで接続することにより、カスコード接続されたスイッチング素子を構成することができる。具体的には、図 3 に示すように、半導体チップ C H P 1 の表面に形成されているゲートパッド G P j と、ソースリード S L の先端部に形成されているソースリードポスト部 S P S T がワイヤ W g j で電気的に接続されている。また、半導体チップ C H P 1 の表面に形成されているソースパッド S P j と、チップ搭載部 P L T 2 がワイヤ W d s で電気的に接続されている。さらに、半導体チップ C H P 2 の表面に形成されているソースパッド S P m と、ソースリード S L の先端部に形成されているソースリードポスト部 S P S T がワイヤ W s m で電気的に接続されている。また、半導体チップ C H P 2 の表面に形成されているゲートパッド G P m と、ゲートリード G L の先端部に形成されているゲートリードポスト部 G P S T がワイヤ W g m で電気的に接続されている。ここで、ソースリードポスト部 S P S T のワイヤ W g j およびワイヤ W s m が接続されている領域と、ゲートリードポスト部 G P S T のワイヤ W g m が接続されている領域は、チップ搭載部 P L T 1 の上面やチップ搭載部 P L T 2 の上面よりも高い位置に位置するように構成されている。

10

#### 【 0 0 5 2 】

なお、半導体チップ C H P 1 は、導電性接着材を介してチップ搭載部 P L T 1 上に搭載されていることから、半導体チップ C H P 1 の裏面に形成されているドレイン電極は、チップ搭載部 P L T 1 と電気的に接続されている。また、半導体チップ C H P 2 は、導電性接着材を介してチップ搭載部 P L T 2 上に搭載されていることから、半導体チップ C H P 2 の裏面に形成されているドレイン電極は、チップ搭載部 P L T 2 と電気的に接続されていることになる。

20

#### 【 0 0 5 3 】

このように構成されているパッケージ P K G 1 においては、半導体チップ C H P 1 、半導体チップ C H P 2 、チップ搭載部 P L T 1 の一部、チップ搭載部 P L T 2 の一部、ドレンリード D L の一部、ソースリード S L の一部、ゲートリード G L の一部、および、ワイヤ W g j 、W d s 、W g m 、W s m が、少なくとも、封止体で封止されている。したがって、チップ搭載部 P L T 1 とチップ搭載部 P L T 2 との間には、封止体の一部が配置されていることになり、これによって、チップ搭載部 P L T 1 とチップ搭載部 P L T 2 が封止体によって電気的に絶縁されることになる。なお、チップ搭載部 P L T 1 の下面、および、チップ搭載部 P L T 2 の下面是、封止体から露出するように構成されていてもよい。この場合、半導体チップ C H P 1 や半導体チップ C H P 2 で発生した熱を、チップ搭載部 P L T 1 の下面やチップ搭載部 P L T 2 の下面から効率良く放散させることができる。

30

#### 【 0 0 5 4 】

この封止体は、例えば、直方体形状をしており、第 1 側面と、この第 1 側面と対向する第 2 側面とを有している。この場合、例えば、封止体の第 1 側面から、ドレンリード D L の一部、ソースリード S L の一部、ゲートリード G L の一部が突出している。これらの突出したドレンリード D L の一部、ソースリード S L の一部、ゲートリード G L の一部が外部接続端子として機能することになる。

#### 【 0 0 5 5 】

ここで、カスコード接続されたスイッチング素子では、半導体チップ C H P 1 と半導体チップ C H P 2 という 2 つの半導体チップを搭載するため、パッケージ内に 1 つのチップ搭載部しか有さない既存の汎用パッケージをそのまま流用することはできない。例えば、数 A 以上の大きな定格電流での使用も考慮して、半導体チップ C H P 1 に形成されている接合 F E T や、半導体チップ C H P 2 に形成されている M O S F E T は、いわゆる半導体チップの裏面にドレイン電極を有する縦型構造が採用されている。この場合、カスコード接続方式のスイッチング素子では、半導体チップ C H P 1 の裏面に形成されているドレイン電極と、半導体チップ C H P 2 の裏面に形成されているドレイン電極とを電気的に接続することはできない。このことから、パッケージ内に 1 つのチップ搭載部しか有さない既存の汎用パッケージにおいては、この 1 つのチップ搭載部に、半導体チップ C H P 1 と半

40

50

導体チップCHP2を配置すると、半導体チップCHP1の裏面に形成されているドレイン電極と、半導体チップCHP2の裏面に形成されているドレイン電極が電気的に接続されてしまいカスコード接続方式を実現することができなくなる。

#### 【0056】

そこで、本実施の形態1では、図3に示すように、外形形状が汎用パッケージと同等であることを前提として、封止体の内部に、互いに電気的に絶縁された2つのチップ搭載部PLT1およびチップ搭載部PLT2を設けるようにパッケージPKG1を構成している。そして、チップ搭載部PLT1上に半導体チップCHP1を搭載するとともに、チップ搭載部PLT2上に半導体チップCHP2を搭載するように、パッケージPKG1を構成している。つまり、電気的に絶縁された2つのチップ搭載部PLT1およびチップ搭載部PLT2をパッケージPKG1内に設け、半導体チップCHP1と半導体チップCHP2とを平面的に配置し、平面的に配置された半導体チップCHP1と半導体チップCHP2とをワイヤで接続することにより、カスコード接続を実現している。10

#### 【0057】

このため、本実施の形態1におけるパッケージPKG1によれば、例えば、電源回路などに利用されているスイッチング素子を実装している既存の汎用パッケージを、外形寸法の同等な本実施の形態1におけるパッケージPKG1に入れ替えることができる。特に、本実施の形態1におけるパッケージPKG1によれば、ドレンリードDL、ソースリードSL、および、ゲートリードGLの配置が汎用パッケージと同様であるため、汎用パッケージを本実施の形態1におけるパッケージPKG1に入れ替えることが可能であり、その他の駆動回路やプリント基板の配線などを設計変更する必要がない。したがって、本実施の形態1によれば、汎用パッケージを利用したスイッチング素子から、本実施の形態1のパッケージPKG1を利用した高性能なカスコード接続方式のスイッチング素子に変更することが容易であり、高性能な電源システムを大幅な設計変更することなく提供できるという利点を有している。20

#### 【0058】

以下に、本実施の形態1におけるパッケージPKG1の特徴点について説明する。まず、本実施の形態1における第1特徴点は、図3に示すように、接合FETを形成した半導体チップCHP1の表面に設けられているゲートパッドGpjと、ソースリードSLとができるだけ近づけるように配置する点にある。具体的に、本実施の形態1では、半導体チップCHP1を搭載するチップ搭載部PLT1をドレンリードDLに対してソースリードSLが配置されている側と同じ側に配置している。これにより、チップ搭載部PLT1をソースリードSLに近づけることができる。このことは、チップ搭載部PLT1上に搭載される半導体チップCHP1をソースリードSLに近づけるように配置できることを意味している。そして、本実施の形態1では、チップ搭載部PLT1上に搭載される半導体チップCHP1をチップ搭載部PLT1の中央部に配置するのではなく、チップ搭載部PLT1のソースリードSLに最も近い辺へ近づくように半導体チップCHP1を配置している。これにより、半導体チップCHP1をソースリードSLに最も近づくように配置することができる。さらに、本実施の形態1では、半導体チップCHP1をできるだけ、ソースリードSLに近づけるように配置するとともに、半導体チップCHP1の表面に形成されているゲートパッドGpjがソースリードSLに近づくように配置されている。このように本実施の形態1では、まず、接合FETが形成されている半導体チップCHP1が搭載されるチップ搭載部PLT1を、ソースリードSLに近い位置に配置し、さらに、チップ搭載部PLT1内の内部領域のうち、ソースリードSLに近い領域に半導体チップCHP1を搭載している。その上、本実施の形態1では、半導体チップCHP1の表面に形成されているゲートパッドGpjがソースリードSLに近づくように、ゲートパッドGpjを配置している。これにより、半導体チップCHP1の表面に形成されているゲートパッドGpjと、ソースリードSLとが近づくことになる。言い換えれば、本実施の形態1においては、半導体チップCHP1の表面に形成されているゲートパッドGpjが、他のリード(ドレンリードDLやゲートリードGL)よりもソースリードSLに近づく304050

ように配置されていることになる。この結果、本実施の形態1によれば、ゲートパッドG P jとソースリードS Lとの間の距離を短くすることができるため、ゲートパッドG P jとソースリードS Lとを接続するワイヤW g jの長さを短くすることができる。特に、本実施の形態1では、ソースリードS Lのうち、ゲートパッドG P jに近い先端部に存在する幅広のソースリードポスト部S P S TでワイヤW g jを接続する構成を取っているので、さらに、ワイヤW g jの長さを短くすることができる。ワイヤW g jの長さを短くできるということは、ワイヤW g jに存在する寄生インダクタンス(図2のL g i 1やL g i 2)を低減できることを意味する。つまり、本実施の形態1によれば、ワイヤW g jに存在する寄生インダクタンスを充分に低減できる。このことから、上述した第2のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本実施の形態1によれば、半導体装置の信頼性向上を図ることができる。

#### 【0059】

続いて、本実施の形態1における第2特徴点について説明する。本実施の形態1における第2特徴点は、図3に示すように、MOSFETを形成した半導体チップCHP2の表面に設けられているゲートパッドG P mと、ゲートリードG Lとができるだけ近づけるように配置する点にある。具体的に、本実施の形態1では、半導体チップCHP2を搭載するチップ搭載部PLT2をドレインリードDLに対してゲートリードGLが配置されている側と同じ側に配置している。これにより、チップ搭載部PLT2をゲートリードGLに近づけることができる。このことは、チップ搭載部PLT2上に搭載される半導体チップCHP2をゲートリードGLに近づけるように配置できることを意味している。そして、本実施の形態1では、チップ搭載部PLT2上に搭載される半導体チップCHP2をチップ搭載部PLT2の中央部に配置するのではなく、チップ搭載部PLT2のゲートリードGLに最も近い辺へ近づくように半導体チップCHP2を配置している。これにより、半導体チップCHP2をゲートリードGLに最も近づくように配置することができる。さらに、本実施の形態1では、半導体チップCHP2をできるだけ、ゲートリードGLに近づけるように配置するとともに、半導体チップCHP2の表面に形成されているゲートパッドG P mがゲートリードGLに近づくように配置されている。このように本実施の形態1では、まず、MOSFETが形成されている半導体チップCHP2が搭載されるチップ搭載部PLT2を、ゲートリードGLに近い位置に配置し、さらに、チップ搭載部PLT2内の内部領域のうち、ゲートリードGLに近い領域に半導体チップCHP2を搭載している。その上、本実施の形態1では、半導体チップCHP2の表面に形成されているゲートパッドG P mがゲートリードGLに近づくように、ゲートパッドG P mを配置している。これにより、半導体チップCHP2の表面に形成されているゲートパッドG P mと、ゲートリードGLとが近づくことになる。言い換えると、本実施の形態1においては、半導体チップCHP2の表面に形成されているゲートパッドG P mが、他のリード(ドレインリードDLやソースリードSL)よりもゲートリードGLに近づくように配置されていることになる。この結果、本実施の形態1によれば、ゲートパッドG P mとゲートリードGLとの間の距離を短くすることができるため、ゲートパッドG P mとゲートリードGLとを接続するワイヤW g mの長さを短くすることができる。特に、本実施の形態1では、ゲートリードGLのうち、ゲートパッドG P mに近い先端部に存在する幅広のゲートリードポスト部G P S TでワイヤW g mを接続する構成を取っているので、さらに、ワイヤW g mの長さを短くすることができる。これにより、本実施の形態1によれば、ワイヤW g mの寄生インダクタンスを低減することができる。このワイヤW g mの寄生インダクタンスを低減できることは、カスコード接続されたスイッチング素子の電気的特性の向上に寄与するが、MOSFETへの絶縁耐圧以上の電圧印加を抑制することとは直接関連していない。本実施の形態1における第2特徴点の構成によれば、直接的ではなく間接的に、MOSFETへの絶縁耐圧以上の電圧印加を抑制できるのである。

#### 【0060】

以下に、この点について説明する。図3に示すように、本実施の形態1における第2特

10

20

30

40

50

特徴点は、MOSFETが形成された半導体チップCHP2ができるだけ、ゲートリードGLに近づけるように配置する点にある。このことは、図3に示すように、チップ搭載部PLT2の手前側に偏って半導体チップCHP2が配置されることを意味し、言い換えれば、チップ搭載部PLT2の奥側に、半導体チップCHP2が搭載されていない大きなスペースができるることを意味する。このように、本実施の形態1では、チップ搭載部PLT2に、半導体チップCHP2が搭載されていない大きなスペースを確保できる点に間接的な特徴がある。具体的には、この特徴により、図3に示すように、チップ搭載部PLT1上に搭載された半導体チップCHP1の表面に形成されているソースパッドSPjと、チップ搭載部PLT2とを電気的に接続するワイヤ接続領域を充分に確保することができるものである。この結果、図3に示すように、ソースパッドSPjとチップ搭載部PLT2とを複数本のワイヤWdsで接続できることになる。ここで、チップ搭載部PLT2は、搭載されている半導体チップCHP2の裏面に形成されているドレイン電極と電気的に接続されていることから、本実施の形態1によれば、複数本のワイヤWdsによって、MOSFETのドレインと接合FETのソースが接続されることになる。このことは、MOSFETのドレインと接合FETのソースとを接続するワイヤWdsの寄生インダクタンス(図2のLse1、Lse2)を低減できることを意味する。つまり、本実施の形態1によれば、複数本のワイヤWdsを使用することにより、MOSFETのドレインと接合FETのソース間の寄生インダクタンスを充分に低減できる。

10

#### 【0061】

さらには、図3に示すように、半導体チップCHP1の表面に形成されているソースパッドSPjの形成位置を、なるべく、チップ搭載部PLT2に近づけるように配置することが望ましい。なぜなら、ソースパッドSPjを、このように配置することにより、ソースパッドSPjとチップ搭載部PLT2とを接続するワイヤWdsの長さをできるだけ短くすることができるからである。これによっても、MOSFETのドレインと接合FETのソースとを接続するワイヤWdsの寄生インダクタンス(図2のLse1、Lse2)を低減できる。

20

#### 【0062】

以上のことから、本実施の形態1における第2特徴点によれば、上述した第1のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本実施の形態1によれば、半導体装置の信頼性向上を図ることができる。

30

#### 【0063】

なお、本実施の形態1では、図3に示すように、ゲートパッドGPjは、ワイヤWgjによって、ソースリードSLと電気的に接続され、かつ、ゲートパッドGPMは、ワイヤWgmによって、ゲートリードGLと電気的に接続されている。このとき、ワイヤWgjの太さ(幅)は、ワイヤWgmの太さ(幅)よりも太く構成することが望ましい。なぜなら、ワイヤWgjに存在する寄生抵抗が大きくなると、第3のメカニズムによって、MOSFETへ絶縁耐圧以上の電圧が印加されることになってしまうからである。したがって、ワイヤWgjに存在する寄生抵抗を低減する観点から、ワイヤWgjの太さを他の他のワイヤよりも太くする構成を取ることが望ましい。これにより、接合FETのゲート電極とスイッチング素子のソース(MOSFETのソースということもできる)との間の寄生抵抗を低減できることから、上述した第3のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本実施の形態1によれば、半導体装置の信頼性向上を図ることができる。

40

#### 【0064】

次に、本実施の形態1における第3特徴点について説明する。本実施の形態1における第3特徴点は、図3に示すように、MOSFETを形成した半導体チップCHP2の表面に設けられているソースパッドSPmと、ソースリードSL(ソースリードポスト部SP

50

S T )とを複数本のワイヤW s mで接続する点にある。これにより、MOSFETのソースとソースリードS Lとの間の寄生抵抗および寄生インダクタンスを低減することができる。この結果、MOSFETのソースの電位がソースリードS Lから供給されるGND電位(基準電位)から変動することを抑制でき、MOSFETのソースをGND電位に確実に固定することができる。さらには、MOSFETのソースとソースリードS Lとの間の寄生抵抗が低減されることから、カスコード接続されたスイッチング素子のオン抵抗を低減することもできる。このように、本実施の形態1における第3特徴点によれば、パッケージPKG1に形成されているカスコード接続されたスイッチング素子の電気的特性の向上を図ることができる。

## 【0065】

10

以上のように、本実施の形態1におけるパッケージPKG1(半導体装置)によれば、上述した第1特徴点と第2特徴点を備えることにより、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、半導体装置の信頼性向上を図ることができる。さらには、本実施の形態1におけるパッケージPKG1(半導体装置)が上述した第3特徴点を備えることによっても、寄生抵抗および寄生インダクタンスの低減を図ることができることから、半導体装置の電気的特性の向上を図ることができる。

## 【0066】

また、本実施の形態1のパッケージPKG1に付随する具体的な効果として、本実施の形態1におけるパッケージPKG1は、接合FETを形成した半導体チップCHP1と、MOSFETを形成した半導体チップCHP2を平面的に配置する構成を採用しているので、半導体チップCHP1や半導体チップCHP2のチップ面積を自由に設計することができる。このことから、低オン抵抗の設計やオン電流密度の設計も容易となり、様々な仕様のスイッチング素子を実現することができる。

20

## 【0067】

続いて、本実施の形態1におけるスイッチング素子の他の実装形態の一例について説明する。図4は、本実施の形態1におけるパッケージPKG2の実装構成を示す図である。図4に示すパッケージPKG2と、図3に示すパッケージPKG1との相違点は、ソースリードS LとドレインリードD Lの形成位置が異なる点である。具体的に、図3に示すパッケージPKG1では、一番左側にゲートリードG Lが配置され、真中にドレインリードD Lが配置され、一番右側にソースリードS Lが配置されていた。これに対し、図4に示すパッケージPKG2では、一番左側にゲートリードG Lが配置され、真中にソースリードS Lが配置され、一番右側にドレインリードD Lが配置されている。この場合、図4に示すように、ソースリードS Lの配置位置が変更されていることに伴って、半導体チップCHP1の表面に形成されているゲートパッドGPjの形成位置も、他のリードよりもソースリードS Lに近くなるように変更されている。この結果、図4に示すパッケージPKG2においても、ゲートパッドGPjとソースリードS Lとの間の距離を短くすることができる。このため、ゲートパッドGPjとソースリードS Lとを接続するワイヤWgjの長さを短くすることができる。つまり、図4に示すパッケージPKG2においても、ワイヤWgjに存在する寄生インダクタンスを充分に低減できる。このことから、上述した第2のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、図4に示すパッケージPKG2においても、半導体装置の信頼性向上を図ることができる。

30

## 【0068】

40

さらに、図4に示すパッケージPKG2に特有な特徴点としては、半導体チップCHP2の表面に形成されているソースパッドSPmと、ソースリードS Lとを電気的に接続するワイヤW smの長さを、図3に示すパッケージPKG1に比べて充分に短くすることができる点である。このため、図4に示すパッケージPKG2によれば、ワイヤW smの寄生抵抗および寄生インダクタンスを低減できることから、本実施の形態1におけるスイッ

50

チング素子の電気的特性を向上させることができる。特に、ワイヤW s mの長さを短くすることによる効果は、本実施の形態1におけるスイッチング素子のオン抵抗を小さくなる点に顕在化する。

#### 【0069】

<変形例1>

次に、本変形例1におけるパッケージPKG3の実装構成について説明する。本変形例1では、接合FETを形成した半導体チップと、MOSFETを形成した半導体チップとを積層する構成について説明する。

#### 【0070】

図5は、本変形例1におけるパッケージPKG3の実装構成を示す図である。図5において、本変形例1におけるパッケージPKG3は、例えば、矩形形状をした金属プレートからなるチップ搭載部PLTを有している。このチップ搭載部PLTは、ドレインリードDLと連結されるように一体的に形成されており、チップ搭載部PLTとドレインリードDLとは電気的に接続されている。そして、このドレインリードDLを離間して挟むように、ソースリードSLとゲートリードGLが配置されている。具体的には、図5に示すように、ドレインリードDLの右側にソースリードSLが配置され、ドレインリードDLの左側にゲートリードGLが配置されている。これらのドレインリードDL、ソースリードSL、および、ゲートリードGLは、互いに電気的に絶縁されている。そして、ソースリードSLの先端部には、幅広領域からなるソースリードポスト部SPOSTが形成され、ゲートリードGLの先端部には、幅広領域からなるゲートリードポスト部GPOSTが形成されている。

10

#### 【0071】

次に、チップ搭載部PLT上には、例えば、銀ペーストや半田からなる導電性接着材を介して、半導体チップCHP1が搭載されている。この半導体チップCHP1には、例えば、SiCを材料とした接合FETが形成されている。そして、半導体チップCHP1の裏面がドレイン電極となっており、半導体チップCHP1の表面(正面)にソースパッドSPjとゲートパッドGPjが形成されている。つまり、半導体チップCHP1には、カスコード接続方式をしたスイッチング素子の一部を構成する接合FETが形成されており、この接合FETのドレインと電気的に接続されるドレイン電極が半導体チップCHP1の裏面に形成され、接合FETのソースと電気的に接続されるソースパッドSPj、および、接合FETのゲート電極と電気的に接続されるゲートパッドGPjが半導体チップCHP1の表面に形成されている。

20

#### 【0072】

続いて、この半導体チップCHP1上に、例えば、銀ペーストや半田からなる導電性接着材を介して、半導体チップCHP2が搭載されている。この半導体チップCHP2には、例えば、Siを材料としたMOSFETが形成されている。このとき、半導体チップCHP2の裏面がドレイン電極となっており、半導体チップCHP1の表面(正面)にソースパッドSPmとゲートパッドGPmが形成されている。つまり、半導体チップCHP2には、カスコード接続方式をしたスイッチング素子の一部を構成するMOSFETが形成されており、このMOSFETのドレインと電気的に接続されるドレイン電極が半導体チップCHP2の裏面に形成され、MOSFETのソースと電気的に接続されるソースパッドSPm、および、MOSFETのゲート電極と電気的に接続されるゲートパッドGPmが半導体チップCHP2の表面に形成されている。

30

#### 【0073】

このように、本変形例1では、半導体チップCHP1上に半導体チップCHP2が搭載されており、特に、半導体チップCHP1の表面に形成されているソースパッドSPj上に半導体チップCHP2が搭載されている。これにより、半導体チップCHP2の裏面に形成されているドレイン電極と、半導体チップCHP1の表面に形成されているソースパッドSPjとが電気的に接続されることになる。この結果、半導体チップCHP1に形成されている接合FETのソースと、半導体チップCHP2に形成されているMOSFET

40

50

のドレインとが電気的に接続されることになる。このことから、半導体チップCHP2は、平面視において、半導体チップCHP1の表面に形成されているソースパッドSPjに内包されるように形成されている必要がある。つまり、本変形例1においては、半導体チップCHP2のサイズは、半導体チップCHP1のサイズよりも小さくなっている必要があり、さらに言えば、半導体チップCHP2のサイズは、ソースパッドSPjのサイズよりも小さくなっている必要がある。

#### 【0074】

続いて、図5に示すように、半導体チップCHP1の表面に形成されているゲートパッドG P jと、ソースリードS Lの先端部に形成されているソースリードポスト部S P S TがワイヤW g jで電気的に接続されている。そして、半導体チップCHP2の表面に形成されているソースパッドS P mと、ソースリードS Lの先端部に形成されているソースリードポスト部S P S TがワイヤW s mで電気的に接続されている。また、半導体チップCHP2の表面に形成されているゲートパッドG P mと、ゲートリードG Lの先端部に形成されているゲートリードポスト部G P S TがワイヤW g mで電気的に接続されている。ここで、ソースリードポスト部S P S TのワイヤW g jおよびワイヤW s mが接続されている領域と、ゲートリードポスト部G P S TのワイヤW g mが接続されている領域は、チップ搭載部P L T 1の上面やチップ搭載部P L T 2の上面よりも高い位置に位置するように構成されている。

#### 【0075】

このように構成されているパッケージPKG3においては、半導体チップCHP1、半導体チップCHP2、チップ搭載部P L Tの一部、ドレインリードD Lの一部、ソースリードS Lの一部、ゲートリードG Lの一部、および、ワイヤW g j、W g m、W s mが、少なくとも、封止体で封止されている。なお、チップ搭載部P L Tの下面は、封止体から露出するように構成されていてもよい。この場合、半導体チップCHP1や半導体チップCHP2で発生した熱を、チップ搭載部P L Tの下面から効率良く放散させることができる。

#### 【0076】

この封止体は、例えば、直方体形状をしており、第1側面と、この第1側面と対向する第2側面とを有している。この場合、例えば、封止体の第1側面から、ドレインリードD Lの一部、ソースリードS Lの一部、ゲートリードG Lの一部が突出している。これらの突出したドレインリードD Lの一部、ソースリードS Lの一部、ゲートリードG Lの一部が外部接続端子として機能することになる。

#### 【0077】

本変形例1におけるパッケージPKG3は上記のように構成されており、以下に、本変形例1におけるパッケージPKG3の特徴点について説明する。まず、本変形例1における特徴点は、図5に示すように、接合F E Tを形成した半導体チップCHP1の表面に設けられているゲートパッドG P jと、ソースリードS Lとをできるだけ近づけるように配置する点にある。具体的に、本変形例1では、半導体チップCHP1をドレインリードD Lに対してソースリードS Lが配置されている側と同じ側に配置している。つまり、半導体チップCHP1は、図5に示す中心線a - a'に対して右側に偏って配置されている。これにより、半導体チップCHP1をソースリードS Lに近づけることができる。そして、本変形例1では、半導体チップCHP1をチップ搭載部P L Tの中央部に配置するのではなく、チップ搭載部P L TのソースリードS Lに最も近い辺へ近づくように半導体チップCHP1を配置している。つまり、半導体チップCHP1は、図5に示す中心線b - b'に対して手前側(下側)に偏って配置されている。これにより、半導体チップCHP1をソースリードS Lに最も近づくように配置することができる。言い換えれば、本変形例1においては、半導体チップCHP1の表面に形成されているゲートパッドG P jが、その他のリード(ドレインリードD LやゲートリードG L)よりもソースリードS Lに近づくように配置されていることになる。この結果、本変形例1によれば、ゲートパッドG P jとソースリードS Lとの間の距離を短くすることができるため、ゲートパッドG P jと

10

20

30

40

50

ソースリードS Lとを接続するワイヤW g jの長さを短くすることができる。特に、本変形例1では、ソースリードS Lのうち、ゲートパッドG P jに近い先端部に存在する幅広のソースリードポスト部S P S TでワイヤW g jを接続する構成を取っているので、さらに、ワイヤW g jの長さを短くすることができる。ワイヤW g jの長さを短くできるということは、ワイヤW g jに存在する寄生インダクタンス(図2のL g i 1やL g i 2)を低減できることを意味する。すなわち、本変形例1によれば、ワイヤW g jに存在する寄生インダクタンスを充分に低減できる。このことから、上述した第2のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本変形例1によれば、半導体装置の信頼性向上を図ることができる。

10

#### 【0078】

ここで、ゲートパッドG P jとソースリードS Lとを接続するワイヤW g jの長さを短くする観点からは、半導体チップC H P 1のソースリードS Lに最も近い辺側に、ゲートパッドG P jを偏って配置することが考えられる。ところが、本変形例1では、図5に示すように、半導体チップC H P 1の右辺側に沿うとともに、右辺中央部に対して対称となるように、ゲートパッドG P jが配置されている。これは、以下に示す理由による。すなわち、ゲートパッドG P jは、半導体チップC H P 1の内部に形成されている複数の接合FETの各ゲート電極とゲート配線によって接続されている。このことから、例えば、ゲートパッドG P jを右辺中央部に対して対称となるように配置することにより、複数の接合FETの各ゲート電極とゲートパッドG P jを接続するゲート配線の距離のばらつきを抑制できるのである。このことは、半導体チップC H P 1内に形成されている複数の接合FETの特性を揃えて利用できることを意味している。このような理由から、本変形例1では、半導体チップC H P 1の右辺中央部に対して対称となるように、ゲートパッドG P jを配置しているのである。

20

#### 【0079】

なお、本変形例1では、図5に示すように、ゲートパッドG P jは、ワイヤW g jによって、ソースリードS Lと電気的に接続され、かつ、ゲートパッドG P mは、ワイヤW g mによって、ゲートリードG Lと電気的に接続されている。このとき、ワイヤW g jの太さ(幅)は、ワイヤW g mの太さ(幅)よりも太く構成することが望ましい。なぜなら、ワイヤW g jに存在する寄生抵抗が大きくなると、第3のメカニズムによって、MOSFETへ絶縁耐圧以上の電圧が印加されることになってしまうからである。したがって、ワイヤW g jに存在する寄生抵抗を低減する観点から、ワイヤW g jの太さを他のワイヤよりも太くする構成を取ることが望ましい。これにより、接合FETのゲート電極とスイッチング素子のソース(MOSFETのソースということもできる)との間の寄生抵抗を低減できることから、上述した第3のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本変形例1によれば、半導体装置の信頼性向上を図ることができる。

30

#### 【0080】

次に、本変形例1におけるさらなる特徴点について説明する。本変形例1におけるさらなる特徴点は、図5に示すように、MOSFETを形成した半導体チップC H P 2の表面に設けられているソースパッドS P mと、ソースリードS L(ソースリードポスト部S P S T)とを複数本のワイヤW s mで接続する点にある。これにより、MOSFETのソースとソースリードS Lとの間の寄生抵抗および寄生インダクタンスを低減することができる。この結果、MOSFETのソースの電位がソースリードS Lから供給されるGND電位(基準電位)から変動することを抑制でき、MOSFETのソースをGND電位に確実に固定することができる。さらには、MOSFETのソースとソースリードS Lとの間の寄生抵抗が低減されることから、カスコード接続されたスイッチング素子のオン抵抗を低減することもできる。このように、本変形例1におけるさらなる特徴点によれば、パッケージPKG 3に形成されているカスコード接続されたスイッチング素子の電気的特性の向

40

50

上を図ることができる。

#### 【0081】

続いて、本変形例1に特有の特徴点について説明する。本変形例1に特有の特徴点は、図5に示すように、接合FETを形成した半導体チップCHP1上に、MOSFETを形成した半導体チップCHP2が搭載されている点である。これにより、半導体チップCHP1の表面に形成されているソースパッドSPjと、半導体チップCHP2の裏面に形成されているドレイン電極とを直接接続することができる。つまり、本変形例1によれば、接合FETのソースと、MOSFETのドレインとをワイヤを使用せずに、直接接続することができる。このことは、接合FETのソースと、MOSFETのドレインとの間に介在する寄生インダクタンスをほぼ完全に削除できることを意味する。すなわち、本変形例1に特有の特徴点は、半導体チップCHP1上に直接半導体チップCHP2を搭載している点にあり、この構成によって、接合FETのソースと、MOSFETのドレインとを接続するためにワイヤが不要となるのである。ワイヤを使用する場合、ワイヤに存在する寄生インダクタンスが問題となるが、本変形例1によれば、ワイヤを使用せずに、接合FETのソースと、MOSFETのドレインとを直接接続することができる。MOSFETのドレインと接合FETのソースとの間の寄生インダクタンス(図2のLse1、Lse2)をほぼ完全になくすことができる。以上のことから、本変形例1に特有の特徴点によれば、上述した第1のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本変形例1によれば、半導体装置の信頼性向上を図ることができる。10

#### 【0082】

本変形例1におけるパッケージPKG3によれば、チップ搭載部PLT上に半導体チップCHP1と半導体チップCHP2とを積層して配置している。このことから、本変形例1におけるパッケージPKG3では、パッケージ内に1つのチップ搭載部PLTを有する構造でもよく、したがって、パッケージ内に1つのチップ搭載部しか有さない既存の汎用パッケージをそのまま流用することができる。すなわち、本変形例1におけるパッケージPKG3によれば、いわゆる安価な汎用パッケージをそのまま流用することができるため、カスコード接続された高性能なスイッチング素子を安価に提供することができる。言い換えるれば、本変形例1によれば、カスコード接続された高性能なスイッチング素子を形成したパッケージPKG3のコスト削減を図ることができる。20

#### 【0083】

また、本変形例1によれば、接合FETを形成した半導体チップCHP1と、MOSFETを形成した半導体チップCHP2とを積層しているため、半導体チップの実装面積を低減できる利点も得られる。特に、この場合、図5に示すように、チップ搭載部PLTに大きなスペースを確保することができるため、半導体チップCHP1や半導体チップCHP2で発生した熱を効率良く放散することもできる。さらには、本変形例1によれば、スイッチング素子の実装面積を低減することができるため、従来は、パッケージ外部のプリント基板上に配置していたフリーホイールダイオード(還流ダイオード)を、スイッチング素子と一緒にパッケージに実装できる利点も得られる。この結果、本変形例1によれば、プリント基板の実装面積削減にも寄与することができ、これによって、電源システムに代表されるシステム全体のコスト削減を図ることができる。30

#### 【0084】

続いて、本変形例1におけるスイッチング素子の他の実装形態の一例について説明する。図6は、本変形例1におけるパッケージPKG4の実装構成を示す図である。図6に示すパッケージPKG4と、図5に示すパッケージPKG3との相違点は、半導体チップCHP1の表面に形成されているゲートパッドGPjの配置位置が異なる点である。具体的に、図5に示すパッケージPKG3では、半導体チップCHP1の右辺側に沿うとともに、右辺中央部に対して対称となるように、ゲートパッドGPjが配置されていた。これに対し、図6に示すパッケージPKG4では、半導体チップCHP1のソースリードSLに40

最も近い辺側に、ゲートパッド G P j が偏って配置されている。この場合、ゲートパッド G P j からソースリード S L までの距離を最短にすることができる。したがって、図 6 に示すパッケージ P K G 4 によれば、ゲートパッド G P j とソースリード S L とを接続するワイヤ W g j の長さを最短にすることができる、これによって、ワイヤ W g j に存在する寄生インダクタンスを最小化することができる。このことから、上述した第 2 のメカニズムによる M O S F E T への絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続された M O S F E T のアバランシェ破壊を効果的に抑制することができる。この結果、図 6 に示すパッケージ P K G 4 においても、半導体装置の信頼性向上を図ることができる。

## 【 0 0 8 5 】

10

本変形例 1 におけるスイッチング素子の他の実装形態の一例について説明する。図 7 は、本変形例 1 におけるパッケージ P K G 5 の実装構成を示す図である。図 7 に示すパッケージ P K G 5 では、ゲートパッド G P j とソースリード S L との接続、および、ソースパッド S P m とソースリード S L との接続に、例えば、銅板（金属板）からなるクリップ C L P を使用している。このように銅板を使用することにより、ワイヤよりも導体抵抗が小さくなるので、寄生インダクタンスの低減を図ることができる。つまり、金属板構造をしたクリップ C L P を使用することにより、ゲートパッド G P j とソースリード S L との間に存在する寄生インダクタンス、および、ソースパッド S P m とソースリード S L との間に存在する寄生インダクタンスを低減することができる。

## 【 0 0 8 6 】

20

特に、図 7 に示すパッケージ P K G 5 によれば、ゲートパッド G P j とソースリード S L との間に存在する寄生インダクタンスを低減できるため、上述した第 2 のメカニズムによる M O S F E T への絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続された M O S F E T のアバランシェ破壊を効果的に抑制することができる。この結果、図 7 に示すパッケージ P K G 5 によれば、半導体装置の信頼性向上を図ることができる。さらに、図 7 に示すパッケージ P K G 5 によれば、ソースパッド S P m とソースリード S L との間に存在する寄生インダクタンスも低減できるため、半導体装置の電気的特性の向上も図ることができる。

## 【 0 0 8 7 】

30

なお、図 8 は、本変形例 1 におけるパッケージ P K G 5 の一断面を示す図である。図 8 に示すように、チップ搭載部 P L T 上に、導電性接着材 P S T を介して、半導体チップ C H P 1 が搭載されており、この半導体チップ C H P 1 上に、導電性接着材（図示せず）を介して、半導体チップ C H P 2 が搭載されている。そして、半導体チップ C H P 1（ゲートパッド）とソースリード S L 、および、半導体チップ C H P 2（ソースパッド）とソースリード S L がクリップ C L P によって電気的に接続されている。なお、破線部は、封止体で覆われる部分を示している。

## 【 0 0 8 8 】

40

続いて、本変形例 1 におけるスイッチング素子の他の実装形態の一例について説明する。図 9 は、本変形例 1 におけるパッケージ P K G 6 の実装構成を示す図である。図 9 に示すパッケージ P K G 6 と、図 5 に示すパッケージ P K G 3 との相違点は、ソースリード S L とドレインリード D L の形成位置が異なる点である。具体的に、図 5 に示すパッケージ P K G 3 では、一番左側にゲートリード G L が配置され、真中にドレインリード D L が配置され、一番右側にソースリード S L が配置されていた。これに対し、図 9 に示すパッケージ P K G 6 では、一番左側にゲートリード G L が配置され、真中にソースリード S L が配置され、一番右側にドレインリード D L が配置されている。この場合、図 9 に示すように、ソースリード S L の配置位置が変更されていることに伴って、チップ搭載部 P L T に搭載される半導体チップ C H P 1 の搭載位置が変更されている。つまり、半導体チップ C H P 1 の配置位置が、他のリードよりもソースリード S L に近くなるように変更されている。具体的に、半導体チップ C H P 1 は、図 9 に示す中心線 a - a' に対して対称になるように配置され、かつ、中心線 b - b' に対して、手前側（下側）に偏るように配置され

50

ている。この結果、図9に示すパッケージPKG6においても、ゲートパッドGpjとソースリードSLとの間の距離を短くすることができる。このため、ゲートパッドGpjとソースリードSLとを接続するワイヤWgjの長さを短くすることができる。つまり、図9に示すパッケージPKG6においても、ワイヤWgjに存在する寄生インダクタンスを充分に低減できる。このことから、上述した第2のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、図9に示すパッケージPKG6においても、半導体装置の信頼性向上を図ることができる。

#### 【0089】

さらに、図9に示すパッケージPKG6に特有な特徴点としては、半導体チップCHP2の表面に形成されているゲートパッドGpmと、ゲートリードGLとを電気的に接続するワイヤWgmの長さを、図5に示すパッケージPKG3に比べて充分に短くすることができる点である。このため、図9に示すパッケージPKG6によれば、ワイヤWgmの寄生抵抗および寄生インダクタンスを低減できることから、本変形例1におけるスイッチング素子の電気的特性を向上させることができる。

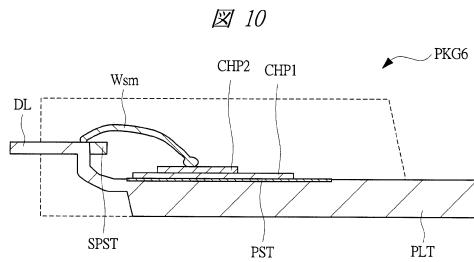

#### 【0090】

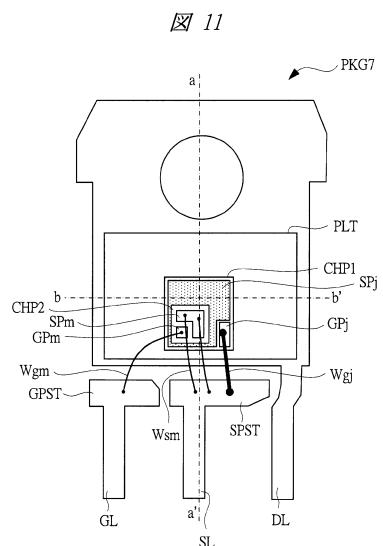

なお、図10は、本変形例1におけるパッケージPKG6の一断面を示す図である。図10に示すように、チップ搭載部PLT上に、導電性接着材PSTを介して、半導体チップCHP1が搭載されており、この半導体チップCHP1上に、導電性接着材(図示せず)を介して、半導体チップCHP2が搭載されている。そして、半導体チップCHP2(ソースパッド)とソースリードSLがワイヤWsmによって電気的に接続されている。なお、破線部は、封止体で覆われる部分を示している。

#### 【0091】

次に、本変形例1におけるスイッチング素子の他の実装形態の一例について説明する。図11は、本変形例1におけるパッケージPKG7の実装構成を示す図である。図11に示すパッケージPKG7と、図9に示すパッケージPKG6との相違点は、半導体チップCHP1の表面に形成されているゲートパッドGpjの配置位置が異なる点である。具体的に、図9に示すパッケージPKG6では、半導体チップCHP1の右辺側に沿うとともに、右辺中央部に対して対称となるように、ゲートパッドGpjが配置されていた。これに対し、図11に示すパッケージPKG7では、半導体チップCHP1のソースリードSLに最も近い辺側に、ゲートパッドGpjが偏って配置されている。この場合、ゲートパッドGpjからソースリードSLまでの距離を最短にすることができる。したがって、図11に示すパッケージPKG7によれば、ゲートパッドGpjとソースリードSLとを接続するワイヤWgjの長さを最短にすることができる、これによって、ワイヤWgjに存在する寄生インダクタンスを最小化することができる。このことから、上述した第2のメカニズムによるMOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、図11に示すパッケージPKG7においても、半導体装置の信頼性向上を図ることができる。

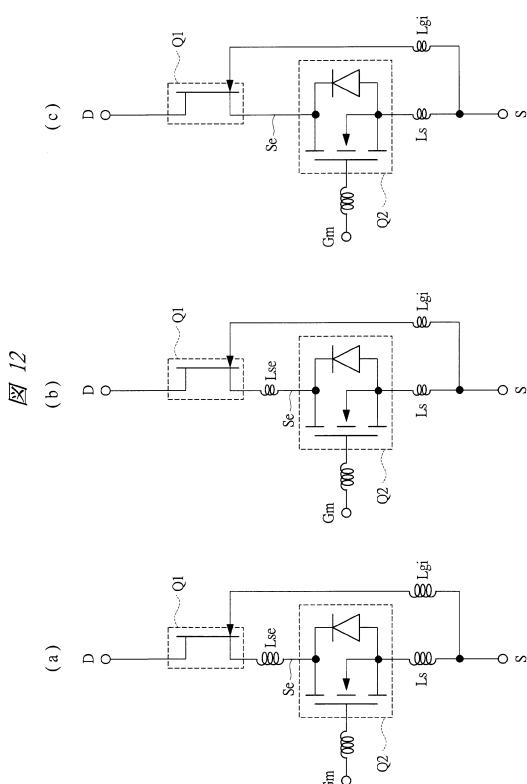

#### 【0092】

続いて、本実施の形態1におけるスイッチング素子、および、本変形例におけるスイッチング素子に存在する寄生インダクタンスについて、従来技術におけるスイッチング素子に存在する寄生インダクタンスと対比して説明する。図12は、カスコード接続されたスイッチング素子の回路図を寄生インダクタンスとともに示す図である。具体的に、図12(a)は、従来技術におけるスイッチング素子とともに寄生インダクタンスの存在位置を示す回路図であり、図12(b)は、本実施の形態1におけるスイッチング素子とともに寄生インダクタンスの存在位置を示す回路図である。また、図12(c)は、本変形例1におけるスイッチング素子とともに寄生インダクタンスの存在位置を示す回路図である。

#### 【0093】

まず、図12(a)からわかるように、従来技術のカスコード接続されたスイッチング

10

20

30

40

50

素子では、接合FETQ1のソースと、MOSFETQ2のドレインとを接続する中間ノードSeに寄生インダクタンスLseが存在し、MOSFETQ2のソースと、スイッチング素子のソースSとの間に寄生インダクタンスLsが存在する。また、接合FETのゲート電極と、スイッチング素子のソースSとの間に寄生インダクタンスLgiが存在し、MOSFETのゲート電極Gmに寄生インダクタンスが存在する。

#### 【0094】

これに対し、図12(b)に示すように、本実施の形態1のカスコード接続されたスイッチング素子では、寄生インダクタンスLse、寄生インダクタンスLs、および、寄生インダクタンスLgiが、図12(a)に示す従来技術のカスコード接続されたスイッチング素子に比べて低減されている。これは、例えば、図3に示すように、本実施の形態1では、チップ搭載部PLT1の配置位置と半導体チップCHP1の配置位置とゲートパッドGpjの配置位置を工夫することにより、ゲートパッドGpjとソースリードSLとを接続するワイヤWgjを短くする構成を取っている点と、ソースパッドSPjとチップ搭載部PLT2とを接続するワイヤWdsを複数本で構成している点に基づくものである。これにより、本実施の形態1によれば、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本実施の形態1によれば、半導体装置の信頼性向上を図ることができる。

#### 【0095】

また、図12(c)に示すように、本変形例1のカスコード接続されたスイッチング素子では、本実施の形態1と同様に、寄生インダクタンスLs、および、寄生インダクタンスLgiを、図12(a)に示す従来技術のカスコード接続されたスイッチング素子に比べて低減することができる。さらに、本変形例1では、接合FETQ1のソースと、MOSFETQ2のドレインとを接続する中間ノードSeに存在する寄生インダクタンスLseをほぼ完全に削除することができる。これは、例えば、図5に示すように、接合FETを形成した半導体チップCHP1上に、MOSFETを形成した半導体チップCHP2が搭載されているからである。これにより、半導体チップCHP1の表面に形成されているソースパッドSPjと、半導体チップCHP2の裏面に形成されているドレイン電極とを直接接続することができる。つまり、本変形例1によれば、接合FETのソースと、MOSFETのドレインとをワイヤを使用せずに、直接接続することができる。このため、本変形例1によれば、接合FETのソースと、MOSFETのドレインとの間に介在する寄生インダクタンスをほぼ完全に削除できるのである。これにより、本変形例1によれば、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本変形例1によれば、半導体装置の信頼性向上を図ることができる。

#### 【0096】

##### <変形例2>

次に、本変形例2におけるパッケージPKG8の実装構成について説明する。図13は、本変形例2におけるパッケージPKG8の実装構成を示す図である。図13に示すパッケージPKG8の構成は、図3に示すパッケージPKG1の構成とほぼ同様である。異なる点は、パッケージの外形形状である。このように本発明の技術的思想は、図3に示すパッケージPKG1に適用できるだけでなく、図13に示すようなパッケージPKG8にも適用することができる。つまり、スイッチング素子を実装構成するパッケージには、様々な種類の汎用パッケージがあり、本発明の技術的思想は、例えば、図3に示すパッケージPKG1や図13に示すパッケージPKG8に代表される多様な汎用パッケージを改良して実現することができる。具体的に、図13に示すパッケージPKG8においても、例えば、ゲートパッドGpjとソースリードSLとの間の距離を短くすることができるため、ゲートパッドGpjとソースリードSLとを接続するワイヤWgjの長さを短くすることができる。このことから、図13に示すパッケージPKG8においても、ワイヤWgjに存在する寄生インダクタンスを充分に低減できる。このことから、MOSFETへの絶縁

10

20

30

40

50

耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、図13に示すパッケージPKG8においても、半導体装置の信頼性向上を図ることができる。

#### 【0097】

なお、図14は、本変形例2におけるパッケージPKG8の一断面を示す図である。図14に示すように、チップ搭載部PLT2上に、導電性接着材PSTを介して、半導体チップCHP2が搭載されている。そして、例えば、半導体チップCHP2（ゲートパッド）とゲートリードGL（ゲートリードポスト部GPOST）が、ワイヤWgmによって電気的に接続されている。なお、破線部は、封止体で覆われる部分を示している。

#### 【0098】

続いて、本変形例2におけるスイッチング素子の他の実装形態の一例について説明する。図15は、本変形例2におけるパッケージPKG9の実装構成を示す図である。図15に示すパッケージPKG9の構成は、図5に示すパッケージPKG3の構成とほぼ同様である。異なる点は、パッケージの外形形状である。このように本発明の技術的思想は、図5に示すパッケージPKG3に適用できるだけでなく、図15に示すようなパッケージPKG9にも適用することができる。つまり、スイッチング素子を実装構成するパッケージには、様々な種類の汎用パッケージがあり、本発明の技術的思想は、例えば、図5に示すパッケージPKG3や図15に示すパッケージPKG9に代表される多様な汎用パッケージに適用することができる。具体的に、図15に示すパッケージPKG9によても、接合FETを形成した半導体チップCHP1上に、MOSFETを形成した半導体チップCHP2を搭載しているため、ソースパッドSPjと、半導体チップCHP2の裏面に形成されているドレイン電極とを直接接続することができる。このことから、図15に示すパッケージPKG9によても、ワイヤを使用せずに、接合FETのソースと、MOSFETのドレインとを直接接続することができるので、MOSFETのドレインと接合FETのソースとの間の寄生インダクタンス（図2のLse1、Lse2）をほぼ完全になくすことができる。したがって、図15に示すパッケージPKG9によても、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本変形例2によれば、半導体装置の信頼性向上を図ることができる。

#### 【0099】

なお、図16は、本変形例2におけるパッケージPKG9の一断面を示す図である。図16に示すように、チップ搭載部PLT上に、導電性接着材PSTを介して、半導体チップCHP1が搭載され、この半導体チップCHP1上に、導電性接着材（図示せず）を介して、半導体チップCHP2が搭載されている。そして、例えば、半導体チップCHP2（ゲートパッド）とゲートリードGL（ゲートリードポスト部GPOST）が、ワイヤWgmによって電気的に接続されている。なお、破線部は、封止体で覆われる部分を示している。

#### 【0100】

##### <変形例3>

次に、本変形例3におけるパッケージPKG10の実装構成について説明する。図17は、本変形例3におけるパッケージPKG10の実装構成を示す図である。図17に示すパッケージPKG10の構成は、図3に示すパッケージPKG1の構成とほぼ同様である。異なる点は、パッケージの外形形状である。このように本発明の技術的思想は、図3に示すパッケージPKG1に適用できるだけでなく、図17に示すようなパッケージPKG10にも適用することができる。つまり、スイッチング素子を実装構成するパッケージには、様々な種類の汎用パッケージがあり、本発明の技術的思想は、例えば、図3に示すパッケージPKG1や図17に示すパッケージPKG10に代表される多様な汎用パッケージを改良して実現することができる。具体的に、図17に示すパッケージPKG10においても、例えば、ゲートパッドGPjとソースリードSLとの間の距離を短くすることができるため、ゲートパッドGPjとソースリードSLとを接続するワイヤWgjの長さを

10

20

30

40

50

短くすることができる。このことから、図17に示すパッケージPKG10においても、ワイヤWgjに存在する寄生インダクタンスを充分に低減できる。このことから、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、図17に示すパッケージPKG10においても、半導体装置の信頼性向上を図ることができる。

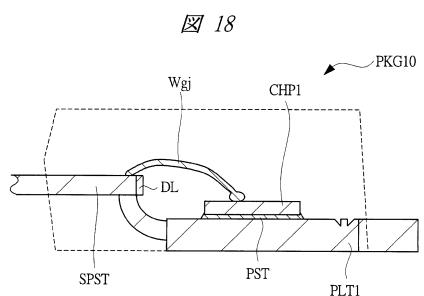

#### 【0101】

なお、図18は、本変形例3におけるパッケージPKG10の一断面を示す図である。図18に示すように、チップ搭載部PLT1上に、導電性接着材PSTを介して、半導体チップCHP1が搭載されている。そして、例えば、半導体チップCHP1（ゲートパッドGpj）とソースリードSL（ソースリードポスト部SPOST）が、ワイヤWgjによって電気的に接続されている。なお、破線部は、封止体で覆われる部分を示している。

#### 【0102】

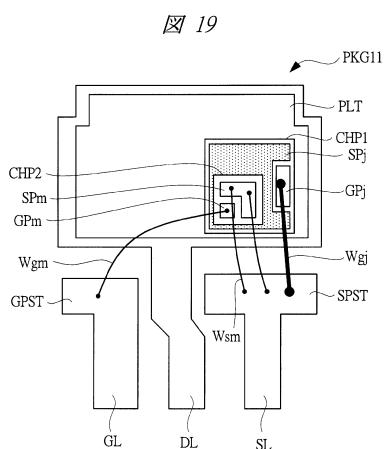

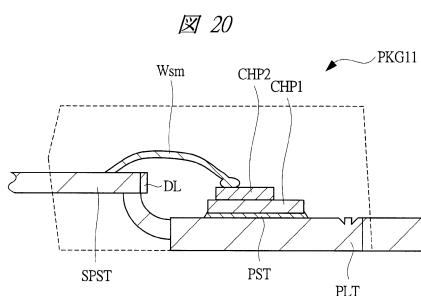

続いて、本変形例3におけるスイッチング素子の他の実装形態の一例について説明する。図19は、本変形例3におけるパッケージPKG11の実装構成を示す図である。図19に示すパッケージPKG11の構成は、図5に示すパッケージPKG3の構成とほぼ同様である。異なる点は、パッケージの外形形状である。このように本発明の技術的思想は、図5に示すパッケージPKG3に適用できるだけでなく、図19に示すようなパッケージPKG11にも適用することができる。つまり、スイッチング素子を実装構成するパッケージには、様々な種類の汎用パッケージがあり、本発明の技術的思想は、例えば、図5に示すパッケージPKG3や図19に示すパッケージPKG11に代表される多様な汎用パッケージに適用することができる。具体的に、図19に示すパッケージPKG11によつても、接合FETを形成した半導体チップCHP1上に、MOSFETを形成した半導体チップCHP2を搭載しているため、ソースパッドSPjと、半導体チップCHP2の裏面に形成されているドレイン電極とを直接接続することができる。このことから、図19に示すパッケージPKG11によつても、ワイヤを使用せずに、接合FETのソースと、MOSFETのドレインとを直接接続することができるので、MOSFETのドレインと接合FETのソースとの間の寄生インダクタンス（図2のLse1、Lse2）をほぼ完全になくすことができる。したがって、図19に示すパッケージPKG11によつても、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本変形例3によれば、半導体装置の信頼性向上を図ることができる。

#### 【0103】

なお、図20は、本変形例3におけるパッケージPKG11の一断面を示す図である。図20に示すように、チップ搭載部PLT上に、導電性接着材PSTを介して、半導体チップCHP1が搭載され、この半導体チップCHP1上に、導電性接着材（図示せず）を介して、半導体チップCHP2が搭載されている。そして、例えば、半導体チップCHP2（ゲートパッド）とゲートリードGL（ゲートリードポスト部GPOST）が、ワイヤWsmによって電気的に接続されている。なお、破線部は、封止体で覆われる部分を示している。

#### 【0104】

##### <変形例4>

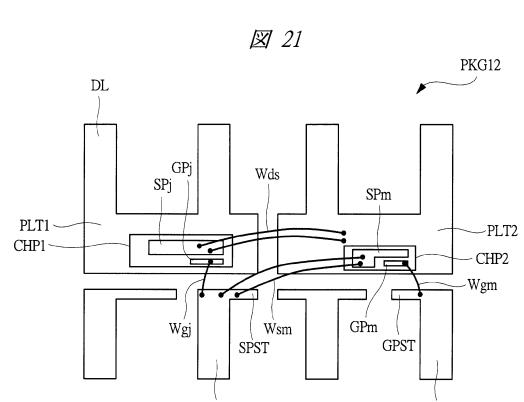

次に、本変形例4におけるパッケージPKG12の実装構成について説明する。図21は、本変形例4におけるパッケージPKG12の実装構成を示す図である。図21に示すパッケージPKG12の構成は、図3に示すパッケージPKG1の構成とほぼ同様である。異なる点は、パッケージの外形形状である。具体的に、本変形例4におけるパッケージPKG12のパッケージ形態は、SOP（Small Outline Package）となっている。このように本発明の技術的思想は、図3に示すパッケージPKG1に適用できるだけでなく、図21に示すようなパッケージPKG12にも適用することができる。つまり、スイッチング素子を実装構成するパッケージには、様々な種類の汎用パッケージがあり、本発明の

10

20

30

40

50

技術的思想は、例えば、図3に示すパッケージPKG1や図21に示すパッケージPKG12に代表される多様な汎用パッケージを改良して実現することができる。具体的に、図21に示すパッケージPKG12においても、例えば、ゲートパッドGpjとソースリードSLとの間の距離を短くすることができるため、ゲートパッドGpjとソースリードSLとを接続するワイヤWgjの長さを短くすることができる。このことから、図21に示すパッケージPKG12においても、ワイヤWgjに存在する寄生インダクタンスを充分に低減できる。このことから、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、図21に示すパッケージPKG12においても、半導体装置の信頼性向上を図ることができる。

10

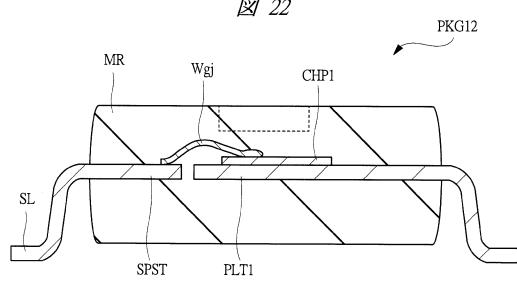

#### 【0105】

なお、図22は、本変形例4におけるパッケージPKG12の一断面を示す図である。図22に示すように、チップ搭載部PLT1上に、導電性接着材(図示せず)を介して、半導体チップCHP1が搭載されている。そして、例えば、半導体チップCHP1(ゲートパッドGpj)とソースリードSL(ソースリードポスト部SPOST)が、ワイヤWgjによって電気的に接続されている。なお、本変形例4においては、例えば、図22に示すように、チップ搭載部PLT1、半導体チップCHP1、ワイヤWgjやリードの一部分などが、樹脂からなる封止体MRによって封止されている。このとき、図21と図22から類推できるように、パッケージPKG12(SOPパッケージ)において、封止体MRは、略直方体形状をしており、第1側面と、この第1側面と対向する第2側面とを有する。そして、ゲートリードGL、および、ソースリードSLは、封止体MRの第1側面から突出するように構成され、ドレインリードDLは、封止体MRの第2側面から突出するように構成されている。

20

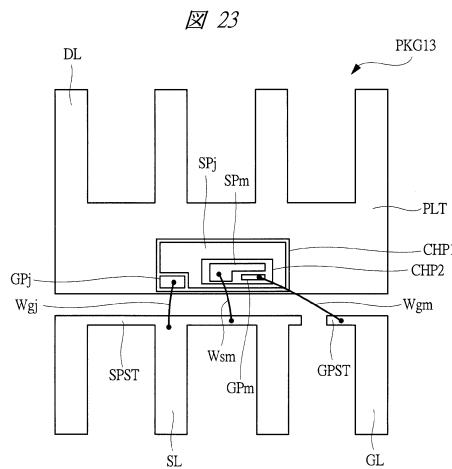

#### 【0106】

続いて、本変形例4におけるスイッチング素子の他の実装形態の一例について説明する。図23は、本変形例4におけるパッケージPKG13の実装構成を示す図である。図23に示すパッケージPKG13の構成は、図5に示すパッケージPKG3の構成とほぼ同様である。異なる点は、パッケージの外形形状である。具体的に、本変形例4におけるパッケージPKG13のパッケージ形態は、SOP(Small Outline Package)となっている。このように本発明の技術的思想は、図5に示すパッケージPKG3に適用できるだけでなく、図23に示すようなパッケージPKG13にも適用することができる。つまり、スイッチング素子を実装構成するパッケージには、様々な種類の汎用パッケージがあり、本発明の技術的思想は、例えば、図5に示すパッケージPKG3や図23に示すパッケージPKG13に代表される多様な汎用パッケージに適用することができる。具体的に、図23に示すパッケージPKG13によっても、接合FETを形成した半導体チップCHP1上に、MOSFETを形成した半導体チップCHP2を搭載しているため、ソースパッドSPjと、半導体チップCHP2の裏面に形成されているドレイン電極とを直接接続することができる。このことから、図23に示すパッケージPKG13によっても、ワイヤを使用せずに、接合FETのソースと、MOSFETのドレインとを直接接続することができるので、MOSFETのドレインと接合FETのソースとの間の寄生インダクタンス(図2のLse1、Lse2)をほぼ完全になくすことができる。したがって、図23に示すパッケージPKG13によっても、MOSFETへの絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続されたMOSFETのアバランシェ破壊を効果的に抑制することができる。この結果、本変形例4によれば、半導体装置の信頼性向上を図ることができる。

30

#### 【0107】

なお、図24は、本変形例4におけるパッケージPKG13の一断面を示す図である。図24に示すように、チップ搭載部PLT上に、導電性接着材(図示せず)を介して、半導体チップCHP1が搭載され、この半導体チップCHP1上に、導電性接着材(図示せず)を介して、半導体チップCHP2が搭載されている。そして、例えば、半導体チップ

40

50

C H P 1 (ゲートパッド G P j) とソースリード S L (ソースリードポスト部 S P S T) が、ワイヤ W g j によって電気的に接続されている。なお、本変形例 4においては、例えば、図 2 4に示すように、チップ搭載部 P L T、半導体チップ C H P 1、半導体チップ C H P 2、ワイヤ W g j やリードの一部分などが、樹脂からなる封止体 M R によって封止されている。このとき、封止体 M R の両側の側面からリードの一部が突出している。

#### 【0108】

##### (実施の形態 2)

前記実施の形態 1 では、パッケージ構造に関する工夫点について説明したが、本実施の形態 2 では、デバイス構造に関する工夫点について説明する。

#### 【0109】

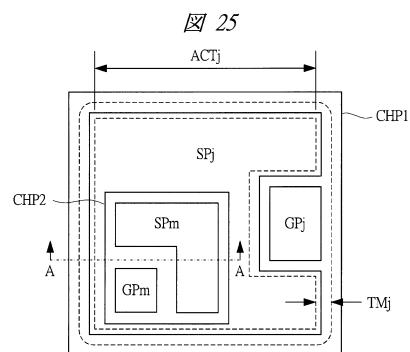

##### <積層半導体チップのレイアウト構成>

図 2 5 は、本実施の形態 2 における半導体チップのレイアウト構成を示す図である。以下に示す半導体チップのレイアウト構成は、例えば、シリコンカーバイド (S i) に代表されるシリコン (S i) よりもバンドギャップの大きな物質を材料とする接合 F E T を形成した半導体チップ C H P 1 上に、シリコン (S i) を材料とする M O S F E T を形成した半導体チップ C H P 2 を積層して搭載する例を示している。図 2 5 において、半導体チップ C H P 1 は矩形形状をしており、この矩形形状をした半導体チップ C H P 1 の外周領域にターミネーション領域 T M j が形成されている。このターミネーション領域 T M j は、耐圧を確保するために設けられている領域である。そして、ターミネーション領域 T M j の内側領域がアクティブ領域 A C T j となっている。このアクティブ領域 A C T j に複数の接合 F E T が形成されている。

#### 【0110】

半導体チップ C H P 1 の外周領域にターミネーション領域 T M j が設けられているが、ターミネーション領域 T M j の一部が内部に入り込むようになっており、この領域にゲートパッド G P j が形成されている。このゲートパッド G P j は、アクティブ領域 A C T j に形成される複数の接合 F E T の各ゲート電極とゲート配線を介して接続されている。ここで、図 2 5 では、ゲートパッド G P j が、半導体チップ C H P 1 の右辺中央部に配置されている。言い換れば、ゲートパッド G P j は、右辺に偏って配置されるとともに、左右に延在する中心線に対して対称となるように配置されている。これにより、複数の接合 F E T の各ゲート電極とゲートパッド G P j を接続するゲート配線の距離のばらつきを抑制できる。このため、図 2 5 に示すレイアウト構成によれば、半導体チップ C H P 1 内に形成されている複数の接合 F E T の特性を揃えて利用できる利点が得られる。

#### 【0111】

半導体チップ C H P 1 のアクティブ領域 A C T j 上には、ソースパッド S P j が形成されている。このソースパッド S P j は、アクティブ領域 A C T j に形成されている接合 F E T のソース領域と電気的に接続されている。そして、このソースパッド S P j 上に、矩形形状をした半導体チップ C H P 2 が搭載されている。この半導体チップ C H P 2 には、複数の M O S F E T が形成されており、半導体チップ C H P 2 の正面にソースパッド S P m と、ゲートパッド G P m が形成されている。ソースパッド S P m は、M O S F E T のソース領域と電気的に接続され、ゲートパッド G P j は、M O S F E T のゲート電極と電気的に接続されている。

#### 【0112】

図 2 6 は、本実施の形態 2 における積層半導体チップの他のレイアウト構成を示す図である。図 2 6 に示すレイアウト構成は、図 2 5 に示すレイアウト構成とほぼ同様である。図 2 6 と図 2 5 の異なる点は、図 2 5 に示すレイアウト構成では、ゲートパッド G P j が、右辺中央部に配置されているのに対し、図 2 6 に示すレイアウト構成では、ゲートパッド G P j が、半導体チップ C H P 1 の右下角部に偏って配置されている点である。このように図 2 6 では、半導体チップ C H P 1 の右下角部に配置することにより、例えば、図 6 に示すように、ゲートパッド G P j からソースリード S L までの距離を最短にすることができる。つまり、図 2 6 に示すレイアウト構成を採用することにより、ゲートパッド G P

10

20

30

40

50

$j$  とソースリード S L とを接続するワイヤ W g j の長さを最短にすることができ、これによって、ワイヤ W g j に存在する寄生インダクタンスを最小化することができる。

#### 【0113】

続いて、図 27 は、図 25 および図 26 の A - A 線で切断した断面図である。図 27 に示すように、半導体基板 S U B j の裏面にドレイン電極 D E j が形成されており、半導体基板 S U B j の主面(表面)にドリフト層 D F T j が形成されている。そして、ドリフト層 D F T j 上にアクティブ領域 A C T j が形成されており、このアクティブ領域 A C T j に接合 F E T のゲート電極およびソース領域が形成されている。アクティブ領域 A C T j の端部には、耐圧を確保するためのターミネーション領域 T M j が形成されており、アクティブ領域 A C T j 上にソースパッド S P j が形成されている。このソースパッド S P j の端部を覆うように、例えば、酸化シリコン膜からなる絶縁膜 I L 1 が形成されている。ここまで構成が、接合 F E T を形成した半導体チップ C H P 1 の構造であり、この接合 F E T を形成した半導体チップ C H P 1 上に、M O S F E T を形成した半導体チップ C H P 2 が搭載されている。

10

#### 【0114】

具体的には、露出しているソースパッド S P j 上に、例えば、導電性接着材(図示せず)を介して、ドレイン電極 D E m が接触している。このドレイン電極 D E m は、半導体基板 S U B m の裏面に形成されており、半導体基板 S U B m の裏面と反対側の主面(表面)には、ドリフト層 D F T m が形成されている。そして、ドリフト層 D F T m にアクティブ領域 A C T m が形成されており、アクティブ領域 A C T m の両端部に、耐圧を確保するためのターミネーション領域 T M m が形成されている。このアクティブ領域 A C T m には、M O S F E T のゲート電極およびソース領域が形成されている。アクティブ領域 A C T m とターミネーション領域 T M m に跨るようにソースパッド S P m が形成されている。このソースパッド S P m の端部を覆うように絶縁膜 I L 2 が形成されているが、ソースパッド S P m の大部分の表面領域は、絶縁膜 I L 2 から露出している。このようにして、接合 F E T を形成した半導体チップ C H P 1 上に、M O S F E T を形成した半導体チップ C H P 2 が搭載されている。

20

#### 【0115】

図 27 に示すように、ソースパッド S P j に内包されるように、半導体チップ C H P 2 が半導体チップ C H P 1 上に搭載されている。したがって、半導体チップ C H P 2 の裏面に形成されているドレイン電極 D E m が、半導体チップ C H P 1 の表面に形成されているソースパッド S P j と、ワイヤを介さず、導電性接着材(図示せず)で直接接触している。このことは、接合 F E T のソースと、M O S F E T のドレインとの間に介在する寄生インダクタンスをほぼ完全に削除できることを意味する。すなわち、図 27 に示すように、半導体チップ C H P 1 上に直接半導体チップ C H P 2 を搭載する構成によって、接合 F E T のソースと、M O S F E T のドレインとを接続するためにワイヤが不要となるのである。ワイヤを使用する場合、ワイヤに存在する寄生インダクタンスが問題となるが、本実施の形態 2 におけるレイアウト構成によれば、ワイヤを使用せずに、接合 F E T のソースと、M O S F E T のドレインとを直接接続することができる。このことから、M O S F E T のドレインと接合 F E T のソースとの間の寄生インダクタンス(図 2 の L s e 1、L s e 2)をほぼ完全になくすことができる。以上のことから、本実施の形態 2 によれば、M O S F E T への絶縁耐圧以上の電圧印加を抑制することができ、これによって、カスコード接続された M O S F E T のアバランシェ破壊を効果的に抑制することができる。この結果、本実施の形態 2 によれば、半導体装置の信頼性向上を図ることができる。

30

40

#### 【0116】

また、図 27 に示すように、本実施の形態 2 におけるレイアウト構成によれば、アクティブ領域 A C T j 上にソースパッド S P j を配置しているため、接合 F E T を流れる電流を大きくすることができる。そして、この場合、ソースパッド S P j の大面積化も可能であるため、ソースパッド S P j 上に搭載される半導体チップ C H P 2 の面積も大きくすることができます。すなわち、半導体チップ C H P 2 の面積を大きくすることができるという

50

ことは、半導体チップCHP2内に形成されるMOSFETの数を増加できることを意味し、この結果、複数のMOSFET全体を流れる電流を大きくすることができる。このように、本実施の形態2におけるレイアウト構成によれば、複数の接合FET全体を流れる電流、および、複数のMOSFET全体を流れる電流を大きくすることができるので、接合FETとMOSFETとをカスコード接続したスイッチング素子の大電流化を容易に実現することができる。さらに、本実施の形態2によれば、シリコンに比べて原理的に高耐圧および低オン抵抗を実現可能なシリコンカーバイドを利用した接合FETを使用しているため、大電流化、高耐圧化、および、低オン抵抗化を両立できるスイッチング素子を提供することができる。

## 【0117】

10

## &lt;レイアウト構成の変形例&gt;

続いて、本実施の形態2における積層半導体チップの他のレイアウト構成について説明する。図28は、本変形例における積層半導体チップのレイアウト構成を示す図である。図28に示すように、半導体チップCHP1は矩形形状をしており、この矩形形状をした半導体チップCHP1の外周領域にターミネーション領域TMjが形成されている。そして、ターミネーション領域TMjの内側領域に、アクティブ領域ACTj、ゲートパッドGPj、および、ソースパッドSPjが形成されている。ここで、本変形例の特徴は、アクティブ領域ACTj、ゲートパッドGPj、および、ソースパッドSPjが平面的に重ならないように配置されている点である。つまり、図28に示すように、接合FETが形成されるアクティブ領域ACTjは、ゲートパッドGPjやソースパッドSPjを避けるように配置されている。そして、ソースパッドSPj上に半導体チップCHP2が搭載されている。

20

## 【0118】

また、図29は、本変形例における積層半導体チップの他のレイアウト構成を示す図である。図29に示すレイアウト構成は、図28に示すレイアウト構成とほぼ同様である。図29と図28の異なる点は、図28に示すレイアウト構成では、ゲートパッドGPjが、右辺中央部に配置されているのに対し、図29に示すレイアウト構成では、ゲートパッドGPjが、半導体チップCHP1の右下角部に偏って配置されている点である。

## 【0119】

30

次に、図30は、図28および図29のA-A線で切断した断面図である。図30に示すように、半導体基板SUBjの裏面にドレイン電極DEjが形成されており、半導体基板SUBjの正面(表面)にドリフト層DFTjが形成されている。このドリフト層DFTjには、アクティブ領域ACTjが形成されており、アクティブ領域ACTjの外側領域にターミネーション領域TMjが形成されている。アクティブ領域ACTjには、接合FETのゲート電極GEやソース領域SRが形成されている。そして、アクティブ領域ACTj上およびターミネーション領域TMj上には、絶縁膜IL1が形成されており、この絶縁膜IL1上にソースパッドSPjが形成されている。ここで、本変形例において、重要な点は、ソースパッドSPjがアクティブ領域ACTjには形成されておらず、ターミネーション領域TMj上に形成されている点である。すなわち、本変形例では、平面視において、アクティブ領域ACTjとソースパッドSPjは重ならないように配置されており、ソースパッドSPjは、ターミネーション領域TMj上に配置される。なお、図30では、ソースパッドSPj上に配置される半導体チップCHP2の図示を省略している。つまり、図30においても、図27と同様に、ソースパッドSPjに半導体チップCHP2が搭載されるが、その構成は、同様であるため、図30では、ソースパッドSPj上に配置される半導体チップCHP2の図示を省略している。

40

## 【0120】

このように構成されている本変形例によれば、以下に示す効果を得ることができる。すなわち、ソースパッドSPj上には半導体チップCHP2が搭載される。この場合、ソースパッドSPjに応力がかかる。ところが、本変形例では、このソースパッドSPjの直下領域に、接合FETを形成したアクティブ領域ACTjが形成されていないため、アク

50

ティップ領域 A C T j に応力が印加されることを防止できる。つまり、本変形例によれば、アクティブ領域 A C T j に不必要的応力が印加されることを防止できることから、アクティブ領域 A C T j に形成されている接合 F E T の機械的な破壊を防止することができる。

#### 【 0 1 2 1 】

また、ソースパッド S P j 上に搭載される半導体チップ C H P 2 の表面には、ゲートパッド G P m やソースパッド S P m が形成されており、これらのパッドには、ワイヤボンディングによって、ワイヤが接続される。このワイヤボンディング工程でも応力が発生するが、本変形例では、半導体チップ C H P 2 とアクティブ領域 A C T j が平面的に重ならないように配置されているため、ワイヤボンディング工程で発生した応力が、アクティブ領域 A C T j に直接伝達されることを防止できる。この結果、本変形例における積層半導体チップのレイアウト構成によれば、半導体チップ C H P 2 の搭載時やワイヤボンディング時に発生する応力が、半導体チップ C H P 1 のアクティブ領域 A C T j に形成されている接合 F E T の特性に影響を与えることを抑制できる。すなわち、本変形例によれば、組み立て歩留まりが高く、信頼性の高い半導体装置を提供することができる。10

#### 【 0 1 2 2 】

##### < M O S F E T のデバイス構造 >

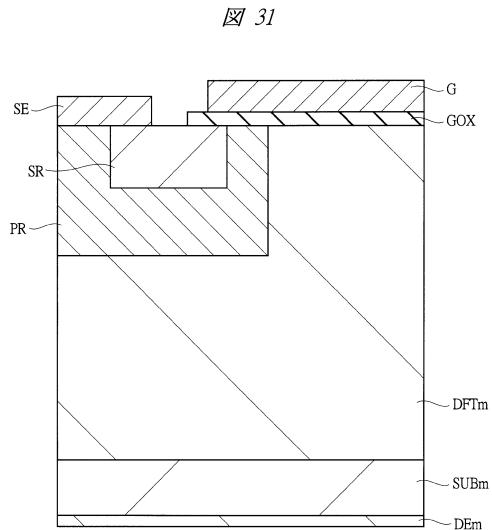

次に、半導体チップ C H P 2 に形成されている M O S F E T のデバイス構造の一例について説明する。図 3 1 は、本実施の形態 2 における M O S F E T のデバイス構造の一例を示す断面図である。図 3 1 に示すように、例えば、n 型不純物を導入したシリコンからなる半導体基板 S U B m の裏面には、例えば、金膜からなるドレイン電極 D E m が形成されている一方、半導体基板 S U B m の正面側には、n 型半導体領域からなるドリフト層 D F T m が形成されている。ドリフト層 D F T m には、p 型半導体領域からなるボディ領域 P R が形成されており、このボディ領域 P R に内包されるように、n 型半導体領域からなるソース領域 S R が形成されている。このソース領域 S R とドリフト層 D F T m で挟まれた、ボディ領域 P R の表面領域がチャネル形成領域として機能する。そして、ソース領域 S R とボディ領域 P R の両方に電気的に接続するようにソース電極 S E が形成されている。さらに、チャネル形成領域上を含むドリフト層 D F T m の表面には、例えば、酸化シリコン膜からなるゲート絶縁膜 G O X が形成されており、このゲート絶縁膜 G O X 上にゲート電極 G が形成されている。20

#### 【 0 1 2 3 】

このように構成されている M O S F E T では、例えば、ソース領域 S R から、ボディ領域 P R の表面に形成されたチャネル形成領域を通って、ドリフト層 D F T m から半導体基板 S U B m の裏面に形成されているドレイン電極 D E m へ電子が流れるよう構成されており、いわゆる縦型 M O S F E T と呼ばれる構造である。この縦型 M O S F E T の利点は、半導体チップ C H P 2 に高密度に形成できるため、電流密度の大きな M O S F E T となる点である。したがって、縦型 M O S F E T を本発明のスイッチング素子に利用することにより、電流密度の大きなスイッチング素子を実現することができる。30

#### 【 0 1 2 4 】

例えば、図 2 8 や図 2 9 に示すレイアウト構成の場合、アクティブ領域 A C T j に形成されている接合 F E T への応力に基づく特性劣化を効果的に防止できるが、その一方で、ソースパッド S P j の面積が比較的小さくなる。この場合、ソースパッド S P j 上に配置される M O S F E T を形成した半導体チップ C H P 2 の面積も比較的小さくなるが、半導体チップ C H P 2 に形成される M O S F E T として、図 3 1 に示す縦型 M O S F E T を使用すれば、小さなチップ面積でも、比較的大きな電流密度の M O S F E T を実現することができる。この結果、カスコード接続されたスイッチング素子全体の電流密度を大きくすることができる。つまり、特に、図 2 8 や図 2 9 に示すレイアウト構成を取ることにより、M O S F E T を形成した半導体チップ C H P 2 の面積が小さくなる場合であっても、図 3 1 に示す縦型 M O S F E T を使用することで、アクティブ領域 A C T j に形成されている接合 F E T への応力に基づく特性劣化を効果的に防止しながら、大電流を確保できる高性能なスイッチング素子を提供することができる。4050

**【0125】**

<本発明者が見出した課題>

次に、本発明者が見出した新たな課題について説明する。図32は、カスコード接続されたスイッチング素子における電流経路を示す図である。図32(a)は、オン時の電流経路を示す図であり、図32(b)は、オフ時に流れるリーク電流の電流経路を示す図である。図32(a)に示すように、オン時においては、定格電流 $I_d$ が接合FETQ1のドレインからMOSFETQ2のソースへ流れる。すなわち、カスコード接続されたスイッチング素子のドレインDからソースSに向って定格電流 $I_d$ が流れる。このとき、MOSFETQ2がカットオフされる前のMOSFETQ2のドレイン電圧(中間ノードSeの電圧)は、MOSFETQ2のオン抵抗と定格電流 $I_d$ の積から求めることができる。例えば、オン抵抗が10mΩで、定格電流 $I_d$ が40Aであれば、中間ノードSeの電圧は0.4Vである。この中間ノードSeの電圧は、MOSFETQ2のドレイン電圧であるとともに、接合FETQ1のソース電圧でもあるため、接合FETQ1のソース電圧を基準とした接合FETQ1のゲート電圧である電圧 $V_{gs}$ は、-0.4Vである。

**【0126】**

カスコード接続されたスイッチング素子をオン状態からオフ状態に遷移させる場合、図32(a)に示すように、MOSFETQ2のゲート電極Gmに15Vを印加した状態から、図32(b)に示すように、MOSFETQ2のゲート電極Gmに0Vを印加する。MOSFETQ2は、ノーマリオフ型のMOSFETであるため、ゲート電極Gmに0Vが印加されると、カットオフする。

**【0127】**

MOSFETQ2をカットオフする過程において、初期段階では、チャネルが徐々に消失するので、MOSFETQ2のドレインとソース間のオン抵抗は徐々に上昇する。カスコード接続されたスイッチング素子に使用されている接合FETQ1は、ノーマリオン型であり、MOSFETQ2をカットオフする初期段階においては、接合FETQ1の電圧 $V_{gs}$ は、-0.4Vであるため、接合FETQ1は、オン状態を維持する。このことから、接合FETQ1のドレイン(例えば、電源電圧300Vのアプリケーションでは、ドレイン電圧が300V程度)から接合FETQ1のソースに向って電流が流れる。したがって、MOSFETQ2のドレイン電圧(中間ノードSeの電圧)は、チャネルの消失に伴って増加するオン抵抗と、接合FETQ1のドレインから流れ込むドレイン電流の積となるため、MOSFETQ2のドレイン電圧(中間ノードSeの電圧)は、0.4Vから徐々に上昇する。

**【0128】**

その後、MOSFETQ2のチャネルが完全に消失して、MOSFETQ2が完全にカットオフされると、接合FETQ1から流れ込む電流により、中間ノードSeに電荷が蓄積されるため、MOSFETQ2のドレイン電圧(中間ノードSeの電圧)は、さらに上昇し、接合FETQ1のカットオフ電圧(例えば、5V~15V程度)まで上昇する。この状態になると、接合FETQ1がオフして、接合FETQ1のドレイン電流が流れなくなる。すなわち、MOSFETQ2のドレイン電圧(中間ノードSeの電圧)の上昇が止まり、この状態が維持される。

**【0129】**

しかしながら、カスコード接続されたスイッチング素子において、接合FETQ1の電圧 $V_{gs}$ が-5V~-15V程度になった場合でも、接合FETQ1のドレインとソースとの間にリーク電流 $I_{d1}$ が流れる場合があることを本発明者は見出した。このリーク電流 $I_{d1}$ が流れると、中間ノードSeに電荷が蓄積されるため、MOSFETQ2のドレイン電圧(中間ノードSeの電圧)は、上昇することになる。このことから、上述したりーク電流 $I_{d1}$ が大きくなると、MOSFETQ2のドレイン電圧(中間ノードSeの電圧)が、MOSFETQ2の耐圧以上(例えば、30V以上)の電圧になるおそれがある。この結果、MOSFETQ2がアバランシェ動作し、最終的に、MOSFETQ2が破壊されるおそれが生じる。この対策として、耐圧の高い高耐圧なMOSFETを使用す

れば、上述したMOSFETのアバランシェ破壊を防止できる可能性は高まるが、高耐圧なMOSFETを使用する場合、耐圧を確保するためにドリフト層を厚く設計する必要がある。このように低濃度のドリフト層の厚さが厚くなると、MOSFETのオン抵抗が増加してしまうため、カスコード接続されたスイッチング素子のオン時における導通損失が増加してしまう問題点が生じる。つまり、カスコード接続されたスイッチング素子の高性能化を確保しつつ、MOSFETのアバランシェ破壊を防止するためには、低濃度のドリフト層を厚くする構成以外の工夫を施す必要があるのである。そこで、本実施の形態2では、カスコード接続されたスイッチング素子の高性能化を確保しつつ、MOSFETのアバランシェ破壊を防止するために、接合FETのデバイス構造に工夫を施している。以下に、この工夫を施した本実施の形態2における接合FETのデバイス構造について説明する。10

### 【0130】

#### <接合FETのデバイス構造>

図33は、本実施の形態2における接合FETのデバイス構造を示す断面図である。図33に示すように、本実施の形態2における接合FETは、半導体基板SUBjを有し、この半導体基板SUBjの裏面にドレイン電極DEjが形成されている。一方、半導体基板SUBjの裏面とは反対側の正面側には、ドリフト層DFTjが形成されており、このドリフト層DFTjには、複数のトレンチTRが形成されている。そして、複数のトレンチTRのそれぞれの側面および底面には、ゲート電極GE（ゲート領域ともいう）が形成されており、隣り合うトレンチTRの側面および底面に形成されたゲート電極GEに挟まれるようにチャネル形成領域が形成されている。このチャネル形成領域の上部にはソース領域SRが形成されている。このように構成されている接合FETでは、ゲート電極GEに印加する電圧を制御することにより、ゲート電極GEからの空乏層の延びを制御する。これにより、互いに隣り合うゲート電極GEから延びる空乏層が繋がるとチャネル形成領域が消失してオフ状態が実現される一方、互いに隣り合うゲート電極GEから延びる空乏層が繋がらない場合には、チャネル形成領域が形成されてオン状態が実現される。20

### 【0131】

ここで、本実施の形態2における接合FETの特徴点は、チャネル形成領域のチャネル長CLが $1\text{ }\mu\text{m}$ 以上となる点である。言い換えれば、ソース領域SRの底部と、ゲート電極GEの底部との間の距離が $1\text{ }\mu\text{m}$ 以上になる点に本実施の形態2における特徴点がある。これにより、チャネル形成領域のチャネル長を長くすることができるため、接合FETのオフ時におけるチャネル形成領域内の静電ポテンシャルを高くすることができます。このことから、本実施の形態2によれば、チャネル長が $0.5\text{ }\mu\text{m}$ 程度のデバイス構造を使用する場合よりも、接合FETのドレインとソースの間を流れるリーク電流を小さく抑えることができる。このように、チャネル長CLを $1\text{ }\mu\text{m}$ 以上とする利点は、オフ時におけるチャネル形成領域内の静電ポテンシャルを高くできる点によってリーク電流を低減することができる点にあるが、さらに、チャネル長CL自体が長くなることも、リーク電流を低減することに寄与していると考えられる。30

### 【0132】

さらに、図33に示す接合FETのデバイス構造の場合、ドレインとなる半導体基板SUBjとソース領域SRとの間の距離よりも、半導体基板SUBjとゲート電極GEとの間の距離の方が小さい。そして、接合FETがオフしている状態では、ゲート電極GEとドリフト層DFTjの間に逆方向電圧（逆バイアス）が印加されることになる。この結果、オフ時に接合FETを流れるリーク電流は、距離の離れた半導体基板SUBjとソース領域SRとの間を流れるよりも、距離の短い半導体基板SUBjとゲート電極GEとの間の逆方向電流（リーク電流）として主に流れるものと考えられる。したがって、本実施の形態2によれば、接合FETがカットオフされた後、接合FETのドレインとソース間を流れるリーク電流を大幅に低減することができる。このことから、本実施の形態2によれば、オフ時における接合FETのドレインとソース間を流れるリーク電流に起因して、MOSFETのドレイン電圧が、耐圧以上の電圧に上昇することを抑制でき、これによって4050

、MOSFETがアバランシェ動作して、最終的に、MOSFETが破壊されることを効果的に防止することができる。なお、図33に示したトレンチ構造の接合FETによれば、接合FETを高密度に形成することができるため、電流密度の大きなスイッチング素子を実現できることは言うまでもない。

#### 【0133】

続いて、図34は、本実施の形態2における接合FETの他のデバイス構造を示す断面図である。図34に示すように、本実施の形態2における他の接合FETは、半導体基板SUBjを有し、この半導体基板SUBjの裏面にドレイン電極DEjが形成されている。一方、半導体基板SUBjの裏面とは反対側の主面側には、ドリフト層DFTjが形成されており、このドリフト層DFTjには、複数のゲート電極GEが離間して埋め込まれるように形成されている。そして、隣り合うゲート電極GE間のドリフト層DFTjの表面にソース領域SRが形成されている。このように構成されている図34に示す接合FETは、いわゆるトレンチ構造を有さない縦型の接合FETである。10

#### 【0134】

このような構造を有する接合FETにおいても、チャネル形成領域のチャネル長CLが $1\mu m$ 以上となる点に特徴点がある。言い換えれば、ソース領域SRの底部と、ゲート電極GEの底部との間の距離(チャネル長CL)が $1\mu m$ 以上になる点に特徴点がある。これにより、チャネル形成領域のチャネル長を長くすることができるため、図34に示す接合FETでも、オフ時におけるチャネル形成領域内の静電ポテンシャルを高くすることができる。このことから、図34に示す接合FETにおいても、チャネル長が $0.5\mu m$ 程度のデバイス構造を使用する場合よりも、接合FETのドレインとソースの間を流れるリーク電流を小さく抑えることができる。このように、チャネル長CLを $1\mu m$ 以上とする利点は、オフ時におけるチャネル形成領域内の静電ポテンシャルを高くできる点によってリーク電流を低減することができる点にあるが、さらに、チャネル長CL自体が長くなることも、リーク電流を低減することに寄与していると考えられる。20

#### 【0135】

図34に示す接合FETの利点は、デバイス構造が簡素であり、製造コストを低くできる点にある。さらには、図33に示す接合FETでは、トレンチTRの側面に導電型不純物(p型不純物)を高度な斜めイオン注入技術などの手段で形成する必要があるのに対し、図34に示す接合FETでは、ゲート電極GEを形成するために、高度な斜めイオン注入技術を使用する必要がなく、ゲート電極GEに導入される不純物プロファイルの精度が高いという利点がある。つまり、図34に示す接合FETによれば、特性の揃った接合FETを容易に形成できる利点が得られる。30

#### 【0136】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0137】

例えば、前記実施の形態では、MOSFETのゲート電極をゲート駆動回路(ゲートドライバ)で駆動する例について説明したが、接合FETのゲート電極もゲート駆動回路で駆動するように構成してもよい。この場合、接合FETのゲート電極をゲート駆動回路で制御することにより、接合FETのソース電圧を所望のレベルに制御できるので、中間ノードのサージ電圧を抑制できる効果を得ることができる。この構成の場合、端子数が増加してしまうが、より低損失なスイッチング素子を提供できる利点が得られる。40

#### 【0138】

また、前記実施の形態1で説明したパッケージ形態に関し、リード配置もこれらに限定されない。つまり、ゲートリード、ドレインリード、および、ソースリードの配置位置は、様々な変更が可能である。例えば、パッケージを実装基板に実装する際、既存のリード配置を流用できるように、パッケージのリード配置を決定することができる。この場合、実装基板の変更が不要となり、設計変更に伴うコストの増加も抑制することができる。50

## 【0139】

さらに、積層半導体チップのレイアウト構成も、特に、明細書で説明したレイアウト構成だけに限定されるものではなく、各半導体チップの形状、パッドの形状、ターミネーション領域の形状なども、特に限定されない。また、接合FETやMOSFETの構造も限定されるものではなく、様々な既存の構造を適用することができる。さらには、デバイスの不純物プロファイルも自由に変更することができる。例えば、MOSFETでは、パンチスルーしないように表面の不純物濃度を薄くし、かつ、深さ方向に徐々に不純物濃度を濃くするように不純物を注入するようにしてもよい。

## 【0140】

なお、上述のMOSFETは、ゲート絶縁膜を酸化膜から形成する場合に限定するものではなく、ゲート絶縁膜を広く絶縁膜から形成するMISFET (Metal Insulator Semiconductor Field Effect Transistor)をも含むものと想定している。つまり、本明細書では、便宜上MOSFETという用語を使用しているが、このMOSFETは、MISFETをも含む意図の用語として本明細書では使用している。10

## 【0141】

また、上述した各ワイヤの金属材料としては、金(Au)、金合金、銅(Cu)、銅合金、アルミニウム(Al)、アルミニウム合金等を用いるといい。

## 【0142】

本発明のスイッチング素子は、例えば、電源回路に適用することができるが、これに限定されるものではなく、例えば、エアコン用のインバータ、太陽光発電システムのパワー・コンディショナー、ハイブリッド車や電気自動車のインバータ、パソコンの電源モジュール、白色LEDのインバータなどの様々な機器への適用が可能である。20

## 【産業上の利用可能性】

## 【0143】

本発明は、半導体装置を製造する製造業に幅広く利用することができる。

## 【符号の説明】

## 【0144】

A C T j アクティブ領域

A C T m アクティブ領域

C H P 1 半導体チップ

C H P 2 半導体チップ

C L チャネル長

C L P クリップ

D ドレイン

D 1 ドレイン

D 2 ドレイン

D E j ドレイン電極

D E m ドレイン電極

D F T j ドリフト層

D F T m ドリフト層

D j 1 ドレイン

D j 2 ドレイン

D L ドレインリード

D m ドレイン

D m 1 ドレイン

D m 2 ドレイン

G ゲート電極

G E ゲート電極

G j ゲート電極

G j 1 ゲート電極

30

40

50

|           |             |    |

|-----------|-------------|----|

| G j 2     | ゲート電極       |    |

| G L       | ゲートリード      |    |

| G m       | ゲート電極       |    |

| G m 1     | ゲート電極       |    |

| G m 2     | ゲート電極       |    |

| G O X     | ゲート絶縁膜      |    |

| G P j     | ゲートパッド      |    |

| G P m     | ゲートパッド      |    |

| G P S T   | ゲートリードポスト部  |    |

| I d       | 定格電流        | 10 |

| I d 1     | リーク電流       |    |

| I L 1     | 絶縁膜         |    |

| I L 2     | 絶縁膜         |    |

| L g i 1   | 寄生インダクタンス   |    |

| L g i 2   | 寄生インダクタンス   |    |

| L L       | 負荷インダクタンス   |    |

| L s       | 寄生インダクタンス   |    |

| L s e 1   | 寄生インダクタンス   |    |

| L s e 2   | 寄生インダクタンス   |    |

| M R       | 封止体         | 20 |

| P K G 1   | パッケージ       |    |

| P K G 2   | パッケージ       |    |

| P K G 3   | パッケージ       |    |

| P K G 4   | パッケージ       |    |

| P K G 5   | パッケージ       |    |

| P K G 6   | パッケージ       |    |

| P K G 7   | パッケージ       |    |

| P K G 8   | パッケージ       |    |

| P K G 9   | パッケージ       |    |

| P K G 1 0 | パッケージ       | 30 |

| P K G 1 1 | パッケージ       |    |

| P K G 1 2 | パッケージ       |    |

| P K G 1 3 | パッケージ       |    |

| P L T     | チップ搭載部      |    |

| P L T 1   | チップ搭載部      |    |

| P L T 2   | チップ搭載部      |    |

| P R       | ボディ領域       |    |

| Q 1       | 接合F E T     |    |

| Q 1 a     | 接合F E T     |    |

| Q 1 b     | 接合F E T     | 40 |

| Q 2       | M O S F E T |    |

| Q 2 a     | M O S F E T |    |

| Q 2 b     | M O S F E T |    |

| S         | ソース         |    |

| S 1       | ソース         |    |

| S 2       | ソース         |    |

| S E       | ソース電極       |    |

| S e       | 中間ノード       |    |

| S j       | ソース         |    |

| S j 1     | ソース         | 50 |

|           |            |

|-----------|------------|

| S j 2     | ソース        |

| S L       | ソースリード     |

| S m       | ソース        |

| S m 1     | ソース        |

| S m 2     | ソース        |

| S P j     | ソースパッド     |

| S P m     | ソースパッド     |

| S P S T   | ソースリードポスト部 |

| S R       | ソース領域      |

| S U B j   | 半導体基板      |

| S U B m   | 半導体基板      |

| T M j     | ターミネーション領域 |

| T M m     | ターミネーション領域 |

| T R       | トレンチ       |

| V a k     | 電圧         |

| V d s u   | 電圧         |

| V d s m u | 電圧         |

| V d s m d | 電圧         |

| W d s     | ワイヤ        |

| W g j     | ワイヤ        |

| W g m     | ワイヤ        |

| W s m     | ワイヤ        |

10

20

【図1】

図1

【図2】

図2

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

【図18】

【図19】

【図21】

【図20】

【図22】

【図23】

【図25】

【図24】

【図26】

【図27】

【図28】

【図29】

【図 3 0】

【図 3 1】

【図 3 2】

【図 3 3】

【図 3 4】

---

フロントページの続き

(72)発明者 秋山 悟

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

審査官 多賀 和宏

(56)参考文献 特開2006-114674(JP,A)

特開2011-166673(JP,A)

特開2012-199548(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L21/336

21/76

21/8234

23/48

25/00-25/07

25/10-25/11

25/16-25/18

27/04

27/088

29/06

29/12

29/739

29/78