(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-237778

(P2011-237778A)

(43) 公開日 平成23年11月24日(2011.11.24)

(51) Int.Cl.

G02F 1/1343 (2006.01)

G02F 1/139 (2006.01)

G02F 1/1334 (2006.01)

F 1

G02F 1/1343

G02F 1/139

G02F 1/1334

テーマコード(参考)

2H088

2H092

2H189

審査請求 未請求 請求項の数 10 O L (全 44 頁)

(21) 出願番号 特願2011-85056 (P2011-85056)

(22) 出願日 平成23年4月7日 (2011.4.7)

(31) 優先権主張番号 特願2010-91712 (P2010-91712)

(32) 優先日 平成22年4月12日 (2010.4.12)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 久保田 大介

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山下 晃央

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 石谷 哲二

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 田村 智宏

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【要約】

【課題】より高コントラスト化を可能とするブルー相を示す液晶材料を用いた液晶表示装置を提供することを目的の一とする。また、ブルー相を示す液晶を用いた液晶表示装置において、より低消費電力化を達成することを目的の一とする。

【解決手段】第1の基板と第2の基板とでブルー相を示す液晶層を挟持する液晶表示装置において、層間膜を介して画素電極層はトランジスタのドレイン電極層と、共通電極層はドレイン電極層と同工程で形成される導電層と電気的に接続する。画素電極層と共通電極層との間の層間膜は選択的に除去されて開口が形成されている。該開口には液晶が充填され液晶層が形成される。よって、液晶層において、画素電極層と共通電極層との間と、ドレイン電極層と導電層との間の開口の領域にも広く電界を形成することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

ブルー相を示す液晶材料を含む液晶層を挟持する第1の基板及び第2の基板と、

前記第1の基板上に、半導体層及び前記半導体層と電気的に接続する第1の導電層を含むトランジスタと、

前記第1の導電層が設けられた同一面に接して並置される第2の導電層と、

前記トランジスタ、前記第1の導電層、及び前記第2の導電層上に層間膜と、

前記層間膜の同一表面に接して並置される第1の電極層及び第2の電極層とを有し、

前記第1の電極層は、前記第1の導電層と電気的に接続し、かつ前記第1の導電層と前記層間膜を介して積層され、

前記第2の電極層は、前記第2の導電層と電気的に接続し、かつ前記第2の導電層と前記層間膜を介して積層され、

前記層間膜は、前記第1の電極層及び前記第2の電極層の間に開口を有し、

前記開口には前記液晶層が設けられていることを特徴とする液晶表示装置。

**【請求項 2】**

請求項1において、前記第1の電極層、及び前記第2の電極層は前記液晶層に接していることを特徴とする液晶表示装置。

**【請求項 3】**

請求項1又は請求項2において、前記第1の電極層、及び前記第2の電極層は櫛歯状であることを特徴とする液晶表示装置。

**【請求項 4】**

ブルー相を示す液晶材料を含む液晶層を挟持する第1の基板及び第2の基板と、

前記第1の基板上に、半導体層及び前記半導体層と電気的に接続する第1の導電層を含むトランジスタと、

前記第1の導電層が設けられた同一面に接して並置される第2の導電層と、

前記トランジスタ、前記第1の導電層、及び前記第2の導電層上に層間膜と、

前記層間膜の同一表面に接して並置される第1の電極層及び第2の電極層と、

前記第2の電極層と重畠し前記第2の基板と前記液晶層との間に設けられた第3の電極層とを有し、

前記第1の電極層は、前記第1の導電層と電気的に接続し、かつ前記第1の導電層と前記層間膜を介して積層され、

前記第2の電極層は、前記第2の導電層と電気的に接続し、かつ前記第2の導電層と前記層間膜を介して積層され、

前記層間膜は、前記第1の電極層及び前記第2の電極層の間に開口を有し、

前記開口には前記液晶層が設けられていることを特徴とする液晶表示装置。

**【請求項 5】**

請求項4において、前記第1の電極層、前記第2の電極層、前記第3の電極層は前記液晶層に接していることを特徴とする液晶表示装置。

**【請求項 6】**

請求項1又は請求項2において、前記第1の電極層、前記第2の電極層、前記第3の電極層は櫛歯状であることを特徴とする液晶表示装置。

**【請求項 7】**

請求項1乃至6のいずれか一項において、前記第1の導電層及び前記第2の導電層は前記開口において露出されており、前記第1の導電層及び前記第2の導電層は前記液晶層と接することを特徴とする液晶表示装置。

**【請求項 8】**

請求項1乃至7のいずれか一項において、前記第1の基板と前記第1の導電層及び前記第2の導電層との間に、絶縁層を有し、

前記絶縁層は、前記第1の電極層及び前記第2の電極層の間に開口を有し、

前記開口には前記液晶層が設けられていることを特徴とする液晶表示装置。

10

20

30

40

50

**【請求項 9】**

請求項 1 乃至 8 のいずれか一項において、前記液晶層は、カイラル剤を含むことを特徴とする液晶表示装置。

**【請求項 10】**

請求項 1 乃至 9 のいずれか一項において、前記液晶層は、光硬化樹脂及び光重合開始剤を有することを特徴とする液晶表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

液晶表示装置及び液晶表示装置の作製方法に関する。

10

**【背景技術】****【0002】**

薄型、軽量化を図った表示装置（所謂フラットパネルディスプレイ）には液晶素子を有する液晶表示装置、自発光素子を有する発光装置、フィールドエミッションディスプレイ（FED）などが競合し、開発されている。

**【0003】**

液晶表示装置においては、液晶分子の応答速度の高速化が求められている。液晶の表示モードは種々あるが、中でも高速応答可能な液晶モードとしてFLC (Ferroelectric Liquid Crystal) モード、OCB (Optical Compensated Birefringence) モード、ブルー相を示す液晶を用いるモードがあげられる。

20

**【0004】**

特にブルー相を示す液晶を使用するモードは配向膜が不要であり、かつ広視野角化が得られるので、実用化に向けてより研究が行われている（例えば特許文献1参照。）。特許文献1は、ブルー相の出現する温度範囲を広げるために、液晶に高分子安定化処理を行う報告である。

**【先行技術文献】****【特許文献】****【0005】****【特許文献1】国際公開第2005-090520号**

30

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

液晶表示装置における問題として高いコントラストを実現するためには、白透過率（白表示時の光の透過率）が大きいことが必要である。

**【0007】**

従って、より高コントラスト化に向けて、ブルー相を示す液晶を用いた液晶表示モードに適した液晶表示装置を提供することを目的の一とする。

**【0008】**

また、ブルー相を示す液晶を用いた液晶表示装置において、より低消費電力化を達成することを目的の一とする。

40

**【課題を解決するための手段】****【0009】**

第1の基板と第2の基板とでブルー相を示す液晶層を挟持し、複数の画素がマトリクス状に配置されているアクティブマトリクス型の液晶表示装置では、各画素ごとにトランジスタと、画素電極層、液晶層及び共通電極層で構成される液晶素子とが配置されている。画素電極層と共通電極層とは、トランジスタ上を覆うように設けられた層間膜上に設けられ、層間膜の同一表面に、互いが接しないように配置される。

**【0010】**

画素電極層及び共通電極層は、平板状でなく、様々な開口パターン（スリット）を有し、

50

屈曲部や枝分かれした櫛歯状を含む形状である。例えば、画素電極層及び共通電極層が有する形状としては、閉空間を形成せず開かれた櫛歯状のようなパターンを用いることができる。この場合、画素電極層と共通電極層とは互いの櫛歯状のパターンがかみ合うように同一の絶縁表面（例えば同一基板や同一絶縁膜）に設けることができる。

【0011】

共通電極層は、第1の基板側の第1の共通電極層と、一対の共通電極層が対向するように、対向基板（第2の基板）側にも設けてもよく、この場合液晶層を間に挟んで第1の基板側の第1の共通電極層と、第2の基板側の第2の共通電極層（第3の電極層）とが互いに重畠するように配置される。

【0012】

第2の共通電極層を形成する場合、第1の共通電極層及び第2の共通電極層は少なくとも画素領域において、平面図でみるとほぼ同形状であり液晶層を介して重畠するように配置される。なお、第1の共通電極層及び第2の共通電極層は少なくとも一部重なって（重畠して）いればよい。

【0013】

液晶素子の画素電極層には、トランジスタの半導体層と電気的に接続するソース電極層又はドレイン電極層を介して、画像信号の電位が与えられる。一方、液晶素子の共通電極層（第1の共通電極層及び第2の共通電極層）には、画素電極層に供給される画像信号の電位に対して基準となる固定電位（一例としてはグラウンド電位（接地電位））が与えられる。共通電位はデータとして送られる画像信号の中間電位近傍でフリッカーの生じないレベルに設定すると好ましい。また、共通電極層はフローティング状態（電気的に孤立した状態）として動作させることも可能である。

【0014】

層間膜を介して画素電極層はトランジスタのドレイン電極層と、共通電極層はドレイン電極層と同材料及び同工程で形成される導電層と電気的に接続する（または同電位を与える）。画素電極層と共通電極層との間の層間膜は選択的に除去されて開口が形成されている。該開口には液晶が充填され液晶層が形成される。なお、本明細書においては、該開口以外の領域に設けられた液晶層を第1の液晶層、該開口に充填されている液晶層を第2の液晶層とし、液晶層は第1の液晶層及び第2の液晶層から構成されているともいう。

【0015】

従って、画素電極層及び共通電極層間に電圧を印加すると、ドレイン電極層及び導電層にもそれぞれ同じ電圧を印加することができる。よって、液晶層において、画素電極層と共通電極層との間と、ドレイン電極層と導電層との間の開口の領域にも広く電界を形成することができる。

【0016】

電界は、画素電極層と共通電極層の間にも形成され、かつ画素電極層と同電位の導電層（ドレイン電極層）と共通電極層と同電位の導電層との間にも形成されるため、第2の基板側の液晶層（第1の液晶層）だけでなく、第1の基板側に設けられた層間膜の開口領域の液晶層（第2の液晶層）にも電界を形成することができる。このように同電位を有する導電層と電極層とを積層体とすることにより、広く液晶層に電界を形成することができる。よって、その電界を用いて液晶分子を制御できる。

【0017】

また、第2の基板側に第2の共通電極層を設けると、画素電極層と第2の共通電極層との間に液晶に対して斜め方向（基板に対して斜めの方向）の電界も加えるため、より効率よく液晶分子を制御できる。

【0018】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率（黒表示時の光の透過率）との比であるコントラスト比も高くすることができる。また、粘度の高いブルー相を示す液晶材料（液晶混合物）であっても、効果的に電界を印加することができるため、低消費電力化も達成できる。

10

20

30

40

50

## 【0019】

本明細書では、半導体素子（例えばトランジスタ）、画素電極層、第1の共通電極層及び層間膜が形成されている基板を素子基板（第1の基板）といい、該素子基板と液晶層を介して対向する基板を対向基板（第2の基板）という。対向基板（第2の基板）と液晶層との間に第1の共通電極層と重畠する第2の共通電極層が形成されてもよい。

## 【0020】

液晶層には、ブルー相を示す液晶材料を用いる。なお、液晶材料とは、液晶層に用いる液晶を含む混合物をさす。ブルー相を示す液晶材料は、応答速度が1 msec以下と短く高速応答が可能であるため、液晶表示装置の高性能化が可能になる。

## 【0021】

ブルー相を示す液晶材料として液晶及びカイラル剤を含む。カイラル剤は、液晶を螺旋構造に配向させ、ブルー相を発現させるために用いる。例えば、5重量%以上のカイラル剤を混合させた液晶材料を液晶層に用いればよい。

10

## 【0022】

液晶は、サーモトロピック液晶、低分子液晶、高分子液晶、強誘電液晶、反強誘電液晶等を用いる。

## 【0023】

カイラル剤は、液晶に対する相溶性が良く、かつ捩れ力の強い材料を用いる。また、R体、S体のどちらか片方の材料が良く、R体とS体の割合が50:50のラセミ体は使用しない。

20

## 【0024】

上記液晶材料は、条件により、コレステリック相、コレステリックブルー相、スマクチック相、スマクチックブルー相、キュービック相、カイラルネマチック相、等方相等を示す。

## 【0025】

ブルー相であるコレステリックブルー相及びスマクチックブルー相は、螺旋ピッチが500nm以下とピッチの比較的短いコレステリック相またはスマクチック相を有する液晶材料にみられる。液晶材料の配向は二重ねじれ構造を有する。可視光の波長以下の秩序を有しているため、透明であり、電圧印加によって配向秩序が変化して光学的変調作用が生じる。ブルー相は光学的に等方であるため視野角依存性がなく、配向膜を形成しなくとも良いため、表示画像の質の向上及びコスト削減が可能である。

30

## 【0026】

また、ブルー相は狭い温度範囲でしか発現が難しく、温度範囲を広く改善するために液晶材料に、光硬化樹脂及び光重合開始剤を添加し、高分子安定化処理を行うことが好ましい。高分子安定化処理は、液晶、カイラル剤、光硬化樹脂、及び光重合開始剤を含む液晶材料に、光硬化樹脂、及び光重合開始剤が反応する波長の光を照射して行う。この高分子安定化処理は、温度制御を行い、等方相を示した状態で光照射して行っても良いし、ブルー相を示した状態で光照射して行ってもよい。

## 【0027】

例えば、液晶層の温度を制御し、ブルー相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行う。但し、これに限定されず、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内の等方相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行ってもよい。ブルー相と等方相間の相転移温度とは、昇温時にブルー相から等方相に転移する温度又は降温時に等方相からブルー相に相転移する温度をいう。高分子安定化処理の一例としては、液晶層を等方相まで加熱した後、徐々に降温させてブルー相にまで相転移させ、ブルー相が発現する温度を保持した状態で光を照射することができる。他にも、液晶層を徐々に加熱して等方相に相転移させた後、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内の状態（等方相を発現した状態）で光を照射することができる。また、液晶材料に含まれる光硬化樹脂として、紫外線硬化樹脂（UV硬化樹脂）を用いる場合、液晶層に紫外線を照射すればよい

40

50

。なお、ブルー相を発現させなくとも、ブルー相と等方相間の相転移温度から +10 以内、好ましくは +5 以内の状態（等方相を発現した状態）で光を照射して高分子安定化処理を行えば、応答速度が 1 m s e c 以下と短く高速応答が可能である。

#### 【0028】

本明細書で開示する発明の構成の一形態は、ブルー相を示す液晶材料を含む液晶層を挟持する第1の基板及び第2の基板と、第1の基板上に、半導体層及び半導体層と電気的に接続する第1の導電層を含むトランジスタと、第1の導電層が設けられた同一面に接して並置される第2の導電層と、トランジスタ、第1の導電層、及び第2の導電層上に層間膜と、層間膜の同一表面に接して並置される第1の電極層及び第2の電極層とを有し、第1の電極層は、第1の導電層と電気的に接続し、かつ第1の導電層と層間膜を介して積層され、第2の電極層は、第2の導電層と電気的に接続し、かつ第2の導電層と層間膜を介して積層され、層間膜は、第1の電極層及び第2の電極層の間に開口を有し、開口には液晶層が設けられている液晶表示装置である。

10

#### 【0029】

本明細書で開示する発明の構成の他の一形態は、ブルー相を示す液晶材料を含む液晶層を挟持する第1の基板及び第2の基板と、第1の基板上に、半導体層及び半導体層と電気的に接続する第1の導電層を含むトランジスタと、第1の導電層が設けられた同一面に接して並置される第2の導電層と、トランジスタ、第1の導電層、及び第2の導電層上に層間膜と、層間膜の同一表面に接して並置される第1の電極層及び第2の電極層と、第2の電極層と重疊し第2の基板と液晶層との間に設けられた第3の電極層とを有し、第1の電極層は、第1の導電層と電気的に接続し、かつ第1の導電層と層間膜を介して積層され、第2の電極層は、第2の導電層と電気的に接続し、かつ第2の導電層と層間膜を介して積層され、層間膜は、第1の電極層及び第2の電極層の間に開口を有し、開口には液晶層が設けられている液晶表示装置である。

20

#### 【0030】

ブルー相を示す液晶層を用いることにより、配向膜を形成する必要がないため、画素電極層（第1の電極層）と液晶層、及び第2の電極層（第1の共通電極層）と液晶層とは接する構成となる。なお、第3の電極層（第2の共通電極層）を設ける場合、第3の電極層（第2の共通電極層）も液晶層と接する構成となる。

30

#### 【0031】

なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

#### 【0032】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

40

#### 【発明の効果】

#### 【0033】

膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上し、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

#### 【0034】

また、粘度の高いブルー相を示す液晶層であっても、効果的に電界を形成することができるため、液晶表示装置の低消費電力化も達成できる。

#### 【図面の簡単な説明】

#### 【0035】

【図1】液晶表示装置を説明する図。

【図2】液晶表示装置の作製方法を説明する図。

【図3】液晶表示装置を説明する図。

【図4】液晶表示装置を説明する図。

50

【図5】液晶表示モジュールを説明する図。

【図6】液晶表示モジュールを説明する図。

【図7】液晶表示装置に適用できるトランジスタを説明する図。

【図8】液晶表示装置に適用できるトランジスタ及びトランジスタの作製方法を説明する図。

【図9】電子機器を説明する図。

【図10】電子機器を説明する図。

【図11】液晶表示装置の電界モードの計算結果を説明する図。

【図12】液晶表示装置の電界モードの計算結果を説明する図。

【発明を実施するための形態】

10

【0036】

実施の形態について、図面を用いて詳細に説明する。但し、以下の説明に限定されず、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

【0037】

(実施の形態1)

本明細書に開示する発明を適用したアクティブマトリクス型の液晶表示装置の例を、図1、図2、図4、及び図11を用いて説明する。

20

【0038】

ブルー相を示す液晶層を含む液晶表示装置において、基板に概略平行（すなわち水平な方向）な電界を生じさせて、基板と平行な面内で液晶分子を動かして、階調を制御する方式を用いることができる。このような方式として、IPS (In-Plane-Switching) モードで用いる電極構成が適用できる。

【0039】

IPSモードなどに示される横電界モードは、液晶層の下方に開口パターンを有する第1の電極層（例えば各画素別に電圧が制御される画素電極層）及び第2の電極層（例えば全画素に共通の電圧が供給される共通電極層）を配置する。第1の電極層及び第2の電極層は、平面形状でなく、様々な開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む。第1の電極層及び第2の電極層はその電極間に電界を発生させるため、同形状で重ならない配置とする。

30

【0040】

画素電極層と共通電極層との間に電界を加えることで、液晶を制御する。液晶には水平方向の電界が加わるため、その電界を用いて液晶分子を制御できる。つまり、基板と平行に配向している液晶分子を、基板と平行な方向で制御できるため、視野角が広くなる。

【0041】

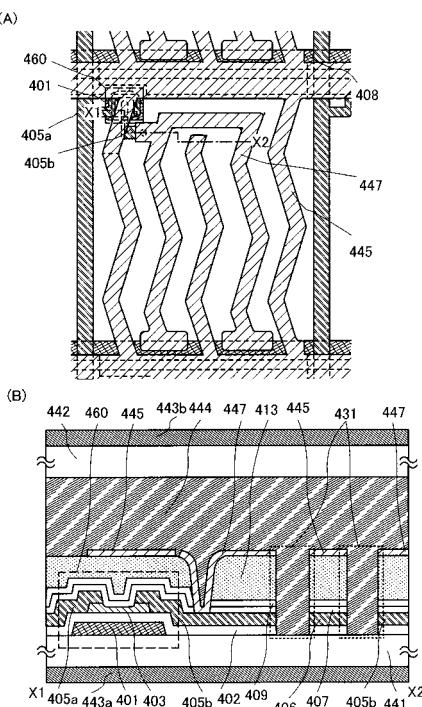

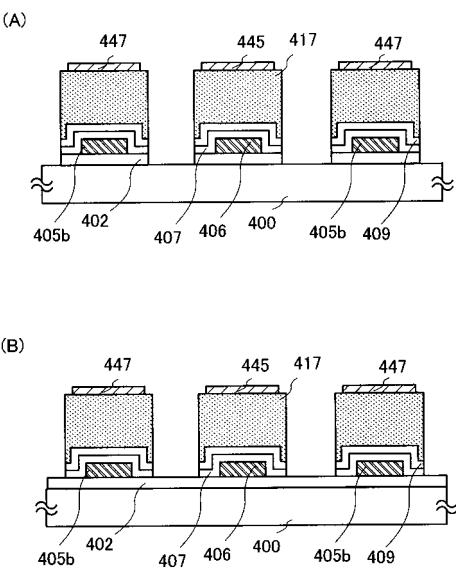

図1(A)は液晶表示装置の平面図であり1画素を示している。図1(B)は図1(A)の線X1-X2における断面図である。

40

【0042】

図1(A)において、複数のソース配線層（ソース電極層405aを含む）が互いに平行（図中上下方向に延伸）かつ互いに離間した状態で配置されている。複数のゲート配線層（ゲート電極層401を含む）は、ソース配線層に略直交する方向（図中左右方向）に延伸し、かつ互いに離間するように配置されている。容量配線層408は、複数のゲート配線層それぞれに隣接する位置に配置されており、ゲート配線層に概略平行な方向、つまり、ソース配線層に概略直交する方向（図中左右方向）に延伸している。ソース配線層と、容量配線層408及びゲート配線層とによって、略長方形の空間が囲まれているが、この空間に液晶表示装置の画素電極層、共通電極層が配置されている。画素電極層を駆動するトランジスタ460は、図中左上の角に配置されている。画素電極層及びトランジスタは、マトリクス状に複数配置されている。

50

## 【0043】

図1の液晶表示装置において、画素電極層として機能する第1の電極層447には、トランジスタ460の半導体層403と電気的に接続するソース電極層405a又はドレイン電極層405bを介して、画像信号の電位が与えられる。一方、液晶素子の共通電極層として機能する第2の電極層445には、画素電極層に供給される画像信号の電位に対して基準となる固定電位（一例としてはグラウンド電位（接地電位））が与えられる。共通電位はデータとして送られる画像信号の中間電位近傍でフリッカーの生じないレベルに設定すると好ましい。また、共通電極層として機能する第2の電極層445はフローティング状態（電気的に孤立した状態）として動作させることも可能である。

## 【0044】

トランジスタ460は逆スタガ型の薄膜トランジスタであり、絶縁表面を有する基板である第1の基板441上に形成され、ゲート電極層401、ゲート絶縁層402、半導体層403、ソース電極層405a又はドレイン電極層405bを含む。

## 【0045】

トランジスタ460を覆い、半導体層403に接する絶縁膜407、絶縁膜409が設けられ、絶縁膜409上に絶縁層413が積層されている。絶縁膜407、絶縁膜409、及び絶縁層413はトランジスタ460と第1の電極層447及び第2の電極層445との間に設けられた層間膜として機能する。

## 【0046】

図1(A)及び(B)において示すように、第1の電極層447と、第2の電極層445とは重疊せず互い違いに設けられている。

## 【0047】

第1の電極層447、及び第2の電極層445は平板状ではなく、様々な開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。

## 【0048】

第1の電極層447と電気的に接続するドレイン電極層405bは第1の電極層447の下に絶縁層413、絶縁膜409、及び絶縁膜407を介して、ゲート絶縁層402上に延在して設けられる。第2の電極層445の下にも絶縁層413、絶縁膜409、及び絶縁膜407を介して、ゲート絶縁層402上に、ドレイン電極層405bと同工程で形成される導電層406が延在して設けられる。

## 【0049】

ドレイン電極層405b及び導電層406はそれぞれ、該上方に形成される第1の電極層447、又は第2の電極層445の形状を反映し、開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。

## 【0050】

第1の電極層447と、第2の電極層445との間に設けられるゲート絶縁層402、絶縁膜407、絶縁膜409、絶縁層413は選択的に除去されており、開口431が形成されている。本実施の形態では該開口431は第1の基板441に達する例を示す。該開口431を充填するように液晶層444が形成されている。

## 【0051】

第1の電極層447及び第2の電極層445上には液晶層444が設けられ、対向基板である第2の基板442で封止されている。

## 【0052】

第1の基板441及び第2の基板442は透光性基板であり、それぞれ外側（液晶層444と反対側）に偏光板443a、443bが設けられている。

## 【0053】

第1の電極層447とドレイン電極層405bとは電気的に接続しており、同電位を与えることができる。また、第2の電極層445と導電層406とも電気的に接続しており、同電位を与えることができる。なお、同電位を与えることができるのであれば、第1の電極層447とドレイン電極層405b、第2の電極層445と導電層406とは直接接し

10

20

30

40

50

て設けられなくてもよく、他の配線層を介して（他の配線層に与えられた電位によって）、それぞれ同電位となつていればよい。

【0054】

従つて、第1の電極層447及び第2の電極層445間に電圧を印加すると、ドレイン電極層405b及び導電層406にもそれぞれ同じ電圧を印加することができる。よつて、液晶層444において、第1の電極層447と第2の電極層445との間と、ドレイン電極層405bと導電層406との間の開口431の領域にも広く電界を形成することができる。

【0055】

液晶層444の厚さ（膜厚）の最大値は1μm以上20μm以下とすることが好ましい。

なお、本明細書においては、液晶層の厚さ（膜厚）の最大値をセルギャップともいう。

【0056】

また、液晶層444を介して隣接する第1の電極層447と第2の電極層445との最短距離は0.5μm以上30μm以下、好ましくは1μm以上10μm以下とする。

【0057】

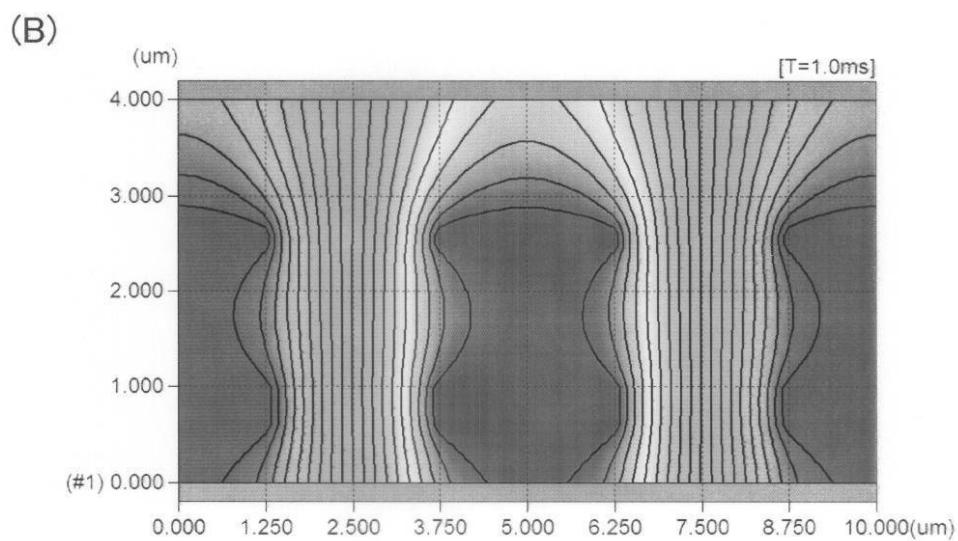

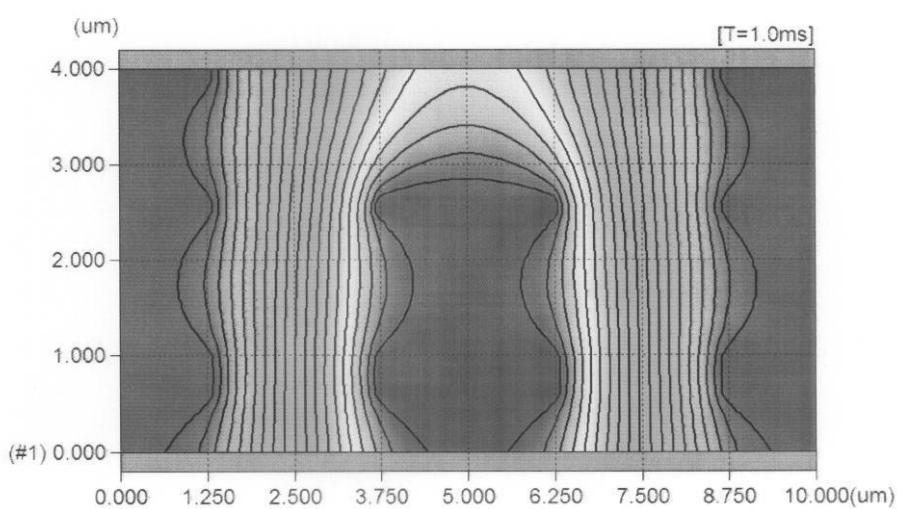

液晶表示装置における電界の印加状態を計算した結果を、図11（B）に示す。計算は、シンテック社製、LCD Master、2s Benchを用いて行った。

【0058】

図11（A）は計算した液晶表示装置の構成を示す図である。図11（A）は、第1の基板200と第2の基板201とが、ブルー相を示す液晶材料を用いた液晶層208を間に挟持して対向するように配置された液晶表示装置である。図11（A）（B）及び図11（A）にて、第1の基板441が第1の基板200に、第2の基板442が第2の基板201に、第1の電極層447が画素電極層230に、液晶層444が液晶層208に、ドレイン電極層405bが導電層233に、第2の電極層445が共通電極層232a、232bに、導電層406が導電層234a、234bに、ゲート絶縁層402が層間膜235、236a、236bに、絶縁膜407、絶縁膜409、及び絶縁層413が層間膜237、238a、238bに、それぞれ対応している。

【0059】

層間膜235、236a、236b、237、238a、238bとしては誘電率4の絶縁体を用い、断面の幅は2.5μmとした。層間膜235、236a、236bの膜厚（高さ）は0.6μm、層間膜237、238a、238bの膜厚（高さ）は1.5μmである。

【0060】

画素電極層230は、層間膜235、導電層233、層間膜237の積層上に形成され、同様に共通電極層232a、232bもそれぞれ層間膜236a、236b、導電層234a、234b、層間膜238a、238bの積層上に形成されている。なお、画素電極層230及び導電層233、共通電極層232a、232b及び導電層234a、234bは、それぞれ電気的に接続されている。また、画素電極層230と共通電極層232a、232bとの間には第1の基板200に達する開口が形成され、該開口にも液晶層208が形成されている。

【0061】

画素電極層230、共通電極層232a、232bの膜厚は0.1μm、導電層233、234a、234bの膜厚は0.4μm、画素電極層230と共に導電層232a、232bとの間の距離は2.5μmである。セルギャップ（液晶層の最大膜厚）に相当する第1の基板200から第2の基板201まで距離は4μmである。

【0062】

図11（A）の構造に対して、共通電極層232a、232b及び同電位となる導電層234a、234bを0V、画素電極層230及び同電位となる導電層233は10Vの設定として計算した計算結果を図11（B）に示す。

【0063】

10

20

30

40

50

図11(B)において、実線は等電位線を示しており、円状に広がる等電位線の中心に画素電極層、共通電極層、又は導電層が配置されている。

【0064】

電界は等電位線と垂直に発現するので、図11(B)に示すように、層間膜237を介して積層された導電層233及び画素電極層230と、層間膜238a、238bを介して積層された導電層234a、234b及び共通電極層232a、232bとの間にそれぞれ横方向の電界が加わっていることが確認できる。

【0065】

電界は、画素電極層230と共に電極層232a、232bとの間に形成され、かつ導電層233と導電層234a、234bとの間に形成されるため、第2の基板201側の液晶層208だけでなく、第1の基板200側に設けられた層間膜の開口領域の液晶層208にも電界を形成することができる。このように同電位を有する導電層と電極層とを積層体とすることにより、広く液晶層に電界を形成することができる。よって、その電界を用いて液晶分子を制御できる。

10

【0066】

従って、液晶表示装置において広く液晶層208に電界を形成することができ、かつ膜厚方向も含め液晶層208全体における液晶分子を応答させることができる。よって白透過率が向上し、白透過率と黒透過率(黒表示時の光の透過率)との比であるコントラスト比も高くすることができる。また、粘度の高いブルー相を示す液晶材料(液晶混合物)であっても、効果的に電界を印加することができるため、低消費電力化も達成できる。

20

【0067】

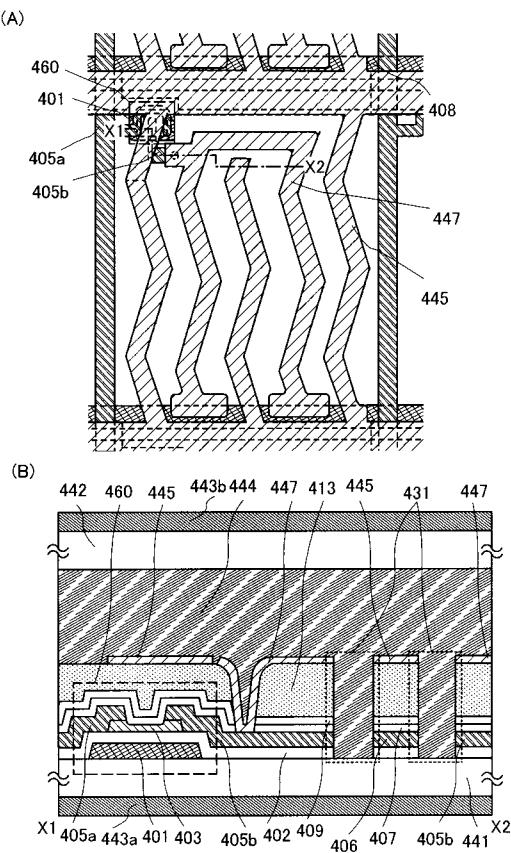

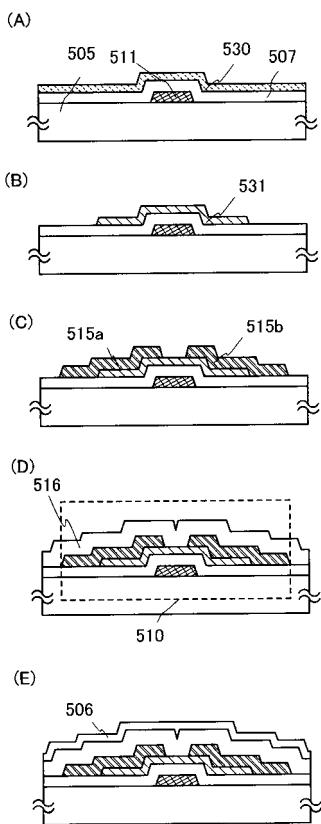

図2(A)乃至(E)を用いて図1に示す液晶表示装置の作製工程を説明する。図2(A)乃至(E)は液晶表示装置の作製工程の断面図である。

【0068】

図2(A)において、素子基板である第1の基板441上にゲート電極層401、ゲート絶縁層402、及び半導体層403が形成され、ゲート電極層401、ゲート絶縁層402、及び半導体層403上に導電膜433が形成されている。

30

【0069】

下地膜となる絶縁膜を第1の基板441とゲート電極層401の間に設けてもよい。下地膜は、第1の基板441からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜から選ばれた一又は複数の膜による単層、又は積層構造により形成することができる。

【0070】

ゲート電極層401の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。ゲート電極層401に遮光性を有する導電膜を用いることで、バックライトからの光(第1の基板441から入射する光)が、半導体層403へ入射することを防止することができる。

40

【0071】

例えば、ゲート電極層401の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、または銅層上にモリブデン層を積層した2層構造、または銅層上に窒化チタン層若しくは窒化タンタルを積層した2層構造、窒化チタン層とモリブデン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タングステン層または窒化タングステン層と、アルミニウムとシリコンの合金またはアルミニウムとチタンの合金と、窒化チタン層またはチタン層とを積層した積層構造とすることが好ましい。

【0072】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層又は窒化酸化シリコン層を単層で又は積層して形成することができる。また、ゲート絶縁層402として、有機シランガスを用いたC

50

V D 法により酸化シリコン層を形成することも可能である。有機シランガスとしては、珪酸エチル (T E O S : 化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$  )、テトラメチルシラン (T M S : 化学式  $\text{Si}(\text{CH}_3)_4$  )、テトラメチルシクロテトラシロキサン (T M C T S )、オクタメチルシクロテトラシロキサン (O M C T S )、ヘキサメチルジシラザン (H M D S )、トリエトキシシラン (S i H  $(\text{OC}_2\text{H}_5)_3$  )、トリスジメチルアミノシラン (S i H  $(\text{N}(\text{CH}_3)_2)_3$  ) 等のシリコン含有化合物を用いることができる。

#### 【0073】

導電膜 433 の材料としては、A l、C r、T a、T i、M o、W から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、熱処理を行う場合には、この熱処理に耐える耐熱性を導電膜に持たせることができが好ましい。例えば、A l 単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。A l と組み合わせる耐熱性導電性材料としては、チタン (T i)、タンタル (T a)、タングステン (W)、モリブデン (M o)、クロム (C r)、N d (ネオジム)、S c (スカンジウム) から選ばれた元素、または上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、または上述した元素を成分とする窒化物で形成する。

10

#### 【0074】

また、導電膜 433 としては導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム ( $\text{In}_2\text{O}_3$ )、酸化スズ ( $\text{SnO}_2$ )、酸化亜鉛 ( $\text{ZnO}$ )、酸化インジウム酸化スズ合金 ( $\text{In}_2\text{O}_3 - \text{SnO}_2$ 、ITO と略記する)、酸化インジウム酸化亜鉛合金 ( $\text{In}_2\text{O}_3 - \text{ZnO}$ ) またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

20

#### 【0075】

ゲート絶縁層 402、半導体層 403、導電膜 433 を大気に触れさせることなく連続的に形成してもよい。大気に触れさせることなく連続成膜することで、大気成分や大気中に浮遊する汚染不純物元素に汚染されることなく各積層界面を形成することができるので、トランジスタ特性のばらつきを低減することができる。

20

#### 【0076】

導電膜 433 をフォトリソグラフィ工程により加工し、ソース電極層 405a、ドレイン電極層 405b、導電層 406 を形成する (図 2 (B) 参照。)。なお、本実施の形態では、導電膜 433 のエッティング工程において半導体層 403 はソース電極層 405a、ドレイン電極層 405b が形成されない領域が一部エッティングされ、溝部 (凹部) を有する半導体層となる例を示す。

30

#### 【0077】

トランジスタ 460、導電層 406 上に絶縁膜 407、絶縁膜 409、及び絶縁層 413 を積層する (図 2 (C) 参照。)。

#### 【0078】

トランジスタ 460 を覆う絶縁膜 407、絶縁膜 409、絶縁層 413 は、乾式法や湿式法で形成される無機絶縁膜、有機絶縁膜を用いることができる。例えば、窒化シリコン、酸化シリコン、窒化酸化シリコン、酸化窒化シリコン、窒化アルミニウム、酸化アルミニウム、窒化酸化アルミニウム、酸化窒化アルミニウムなどを用いて、C V D 法やスパッタリング法などの乾式法により形成してもよいし、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の有機材料を用いて、スピンドルコート、ディップ、スプレー塗布、液滴吐出法 (インクジェット法、スクリーン印刷、オフセット印刷等)、ロールコート、カーテンコート、ナイフコートなどの湿式法により形成してもよい。また上記有機材料の他に、低誘電率材料 (low-k 材料)、シロキサン系樹脂、P S G (リンガラス)、B P S G (リンボロンガラス) 等を用いることができる。

40

#### 【0079】

なおシロキサン系樹脂とは、シロキサン系材料を出発材料として形成された  $\text{Si} - \text{O} - \text{Si}$  結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基 (例えばアルキ

50

ル基やアリール基)やフルオロ基を用いても良い。また、有機基はフルオロ基を有しても良い。シロキサン系樹脂は塗布法により成膜し、焼成することによって絶縁層413として用いることができる。

#### 【0080】

なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁膜407、絶縁膜409を形成してもよい。例えば、無機絶縁膜上に有機樹脂膜を積層する構造としてもよい。

#### 【0081】

絶縁膜407、絶縁膜409、及び絶縁層413にドレイン電極層405bに達する開口(コンタクトホール)を形成し、開口及び絶縁層413上に導電膜を形成する。導電膜をフォトリソグラフィ工程により加工し、ドレイン電極層405bと電気的に接続する第1の電極層447と、導電層406と電気的に接続する第2の電極層445を形成する(図2(D)参照。)。第2の電極層445と導電層406との電気的な接続は図示しないが、第1の電極層447とドレイン電極層405bとの接続のように、導電層406に達する開口を形成し、該開口に第2の電極層445を形成して行ってもよいし、第2の電極層445と同じ電位を与えられている配線層と接続することで導電層406にも第2の電極層445と同電位を与えてよい。

#### 【0082】

画素の表示領域において、第1の電極層447とドレイン電極層405b、第2の電極層445と導電層406とは、ほぼ同形状で重なることが好ましい。

#### 【0083】

第1の電極層447、第2の電極層445においては透光性が好ましいが、開口パターンを有するために形状によっては金属膜などの非透光性材料を用いてよい。

#### 【0084】

第1の電極層447、及び第2の電極層445は、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

#### 【0085】

また、第1の電極層447、及び第2の電極層445はタンゲステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

#### 【0086】

また、第1の電極層447、及び第2の電極層445として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した第1の電極層447、及び第2の電極層445は、シート抵抗が10000/以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1·cm以下であることが好ましい。

#### 【0087】

導電性高分子としては、いわゆる電子共役系導電性高分子が用いることができる。例えば、ポリアニリンまたはその誘導体、ポリピロールまたはその誘導体、ポリチオフェンまたはその誘導体、若しくはアニリン、ピロールおよびチオフェンの2種以上からなる共重合体またはその誘導体などがあげられる。

#### 【0088】

次に、第1の電極層447と第2の電極層445の間に設けられた絶縁膜407、絶縁膜

10

20

30

40

50

409、絶縁層413を選択的に除去し、第1の基板441に達する開口431を形成する(図2(E)参照。)。

【0089】

図1及び図2ではゲート絶縁層402まで除去し、第1の基板441に達する開口431を形成する例であるが、開口431においてゲート絶縁層402を残存させてもよい。また、図1及び図2では開口431において、ドレイン電極層405b、導電層406の端部が露出し、第1の電極層447、第2の電極層445の端部と一致している例であるが、ドレイン電極層405b、導電層406は端部を上に形成される絶縁膜407で覆われてもよい。

【0090】

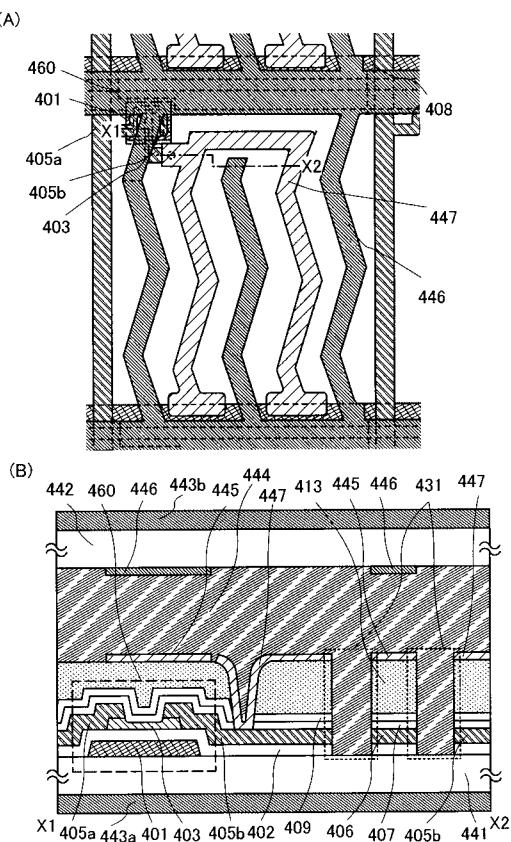

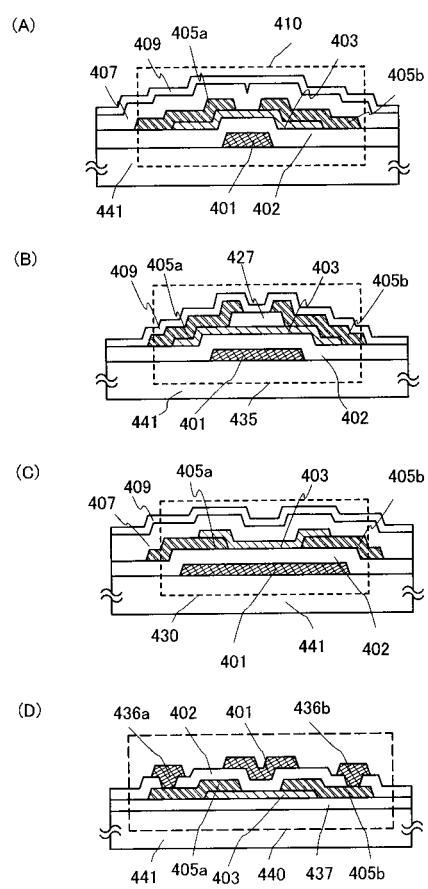

画素電極層である第1の電極層447と共通電極層である第2の電極層445との間に設けられる開口の形成例を図4(A)(B)に示す。

【0091】

図4(A)は、ドレイン電極層405b、導電層406が開口に露出していない例であり、ドレイン電極層405b、導電層406の端部は絶縁膜407で覆われている。第1の電極層447、第2の電極層445の端部も開口と一致していない例である。また、図4(B)は、開口において、ゲート絶縁層402を除去せず残存させる例である。

【0092】

このように、画素電極層と共通電極層との間の層間膜を除去し形成する開口は、少なくともドレイン電極層405bと導電層406との間まで形成すればよい。ドレイン電極層405bと導電層406との間に形成された開口に充填された液晶分子は、ドレイン電極層405bと導電層406とで形成される電界によって制御することができる。

【0093】

半導体層、電極層、導電層などの作製工程、開口の形成工程において、薄膜を所望の形状に加工するためにフォトリソグラフィ工程により形成したレジストマスクを用いてエッチング工程を行う。加工する材料や形状に応じてマスクやエッチング工程は複数用いてよい。

【0094】

レジストマスク数の削減として、第1のエッチング工程で用いたレジストマスクをアッシングによって加工し、次の第2のエッチング工程で用いることもできる。

【0095】

また、多階調マスクにより形成した複数(代表的には二種類)の厚さの領域を有するレジストマスクを用いると、レジストマスクの数を減らすことができるため、工程簡略化、低コスト化が図れる。

【0096】

エッチング工程は、ドライエッチングやウェットエッチングを用いることができる。

【0097】

ドライエッチングに用いるエッチング装置としては、反応性イオンエッチング法(RIE法)を用いたエッチング装置や、ECR(Electron Cyclotron Resonance)やICP(Inductively Coupled Plasma)などの高密度プラズマ源を用いたドライエッチング装置を用いることができる。また、ICPエッチング装置と比べて広い面積に渡って一様な放電が得られやすいドライエッチング装置としては、上部電極を接地させ、下部電極に13.56MHzの高周波電源を接続し、さらに下部電極に3.2MHzの低周波電源を接続したECCP(Enhanced Capacitively Coupled Plasma)モードのエッチング装置がある。このECCPモードのエッチング装置であれば、例えば基板として、第10世代の3mを超えるサイズの基板を用いる場合にも対応することができる。

【0098】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件を適宜調節する。例えばドライエッチングにおいては、エッチング条件として、コイル型の電極に印加

10

20

30

40

50

される電力量、基板側の電極に印加される電力量、基板側の電極温度などを適宜調節する。また、ウェットエッティングにおいては、エッティング条件としてエッティング液、エッティング時間、温度などを適宜調節する。ウェットエッティングでは、エッティングが膜厚方向にも膜幅方向にも等方性に進行するので、エッティング工程によって除去されてしまう膜幅方向の領域（長さ）も計算してレジストマスクの大きさ及び形状を考慮する。

#### 【0099】

例えば、ゲート絶縁層402、絶縁膜407、絶縁膜409、及び絶縁層413を選択的に除去して形成される開口431は、図1（B）では開口431の壁面は直線上で一致している例であるが、用いる材料やエッティング方法により開口431の壁面は異なる膜幅を有する凹凸の面となる例もある。

10

#### 【0100】

例えば、ゲート絶縁層として酸化窒化シリコン膜（膜厚600nm）、絶縁層としてアクリル樹脂膜（膜厚2μm）を用いて、該積層を選択的に除去して開口を形成する一例を説明する。なお、ゲート絶縁層と絶縁層の間には、チタン膜（膜厚50nm）、アルミニウム膜（膜厚200nm）、チタン膜（膜厚50nm）の積層からなる導電層が形成されている。

#### 【0101】

ゲート絶縁層である酸化窒化シリコン膜をICPドライエッティング法によりエッティングし開口を形成する。エッティング条件はCHF<sub>3</sub>をとHeを用いて、コイル型の電極に印加される電力量475W、基板側の電極に印加される電力量300W、圧力5.5Pa、下部電極温度70、時間160秒で行う。

20

#### 【0102】

次にゲート絶縁層及び導電層上に絶縁層としてアクリル樹脂を塗布法により形成し、絶縁層上に画素電極層及び共通電極層となるインジウム錫酸化物膜をスパッタリング法により積層する。

#### 【0103】

インジウム錫酸化物膜をウェットエッティング法によりエッティングし画素電極層及び共通電極層を形成する。エッティング液としては、ITO07N（関東化学社製）を用いることができる。

30

#### 【0104】

そして絶縁層であるアクリル樹脂膜をRIE法によりエッティングし、開口を形成する。エッティング条件はCF<sub>4</sub>、He及びO<sub>2</sub>を用いて、電力量500W、圧力500mTorr、時間150秒で行う。以上の工程でゲート絶縁層である酸化窒化シリコン膜と、絶縁層であるアクリル樹脂膜に開口を形成することができる。

#### 【0105】

ゲート絶縁層である酸化窒化シリコン膜と、絶縁層であるアクリル樹脂膜とを一回のエッティング工程によってエッティングし、開口を形成してもよい。また、画素電極層及び共通電極層となるインジウム錡酸化物膜がエッティングされにくいエッティング条件を選択することで、インジウム錡酸化物膜をマスクとしてゲート絶縁層である酸化窒化シリコン膜と、絶縁層であるアクリル樹脂膜をエッティングすることもできる。勿論、別途インジウム錫酸化物膜上にマスクを形成してもよい。

40

#### 【0106】

また、開口431にドレン電極層405bと導電層406が露出する場合、ゲート絶縁層402、絶縁膜407、絶縁膜409、及び絶縁層413をエッティングする際に、ドレン電極層405bと導電層406がエッティングされにくい条件を適宜選択する必要がある。

#### 【0107】

第1の基板441と対向基板である第2の基板442とを、液晶層を間に挟持させてシール材で固着する。液晶層を形成する方法として、ディスペンサ法（滴下法）や、第1の基板441と第2の基板442とを貼り合わせてから毛細管現象等を用いて液晶を注入する

50

注入法を用いることができる。

【0108】

液晶層444には、ブルー相を示す液晶材料を用いる。

【0109】

ブルー相を示す液晶材料として液晶及びカイラル剤を含む。カイラル剤は、液晶を螺旋構造に配向させ、ブルー相を発現させるために用いる。例えば、数重量%以上のカイラル剤を混合させた液晶材料を液晶層に用いればよい。

【0110】

液晶は、サーモトロピック液晶、低分子液晶、高分子液晶、強誘電液晶、反強誘電液晶等を用いる。

10

【0111】

カイラル剤は、液晶に対する相溶性が良く、かつ捩れ力の強い材料を用いる。また、R体、S体のどちらか片方の材料が良く、R体とS体の割合が50:50のラセミ体は使用しない。

【0112】

上記液晶材料は、条件により、コレステリック相、コレステリックブルー相、スマクチック相、スマクチックブルー相、キュービック相、カイラルネマチック相、等方相等を示す。

20

【0113】

ブルー相であるコレステリックブルー相及びスマクチックブルー相は、螺旋ピッチが500nm以下とピッチの比較的短いコレステリック相またはスマクチック相を有する液晶材料にみられる。液晶材料の配向は二重ねじれ構造を有する。可視光の波長以下の秩序を有しているため、透明であり、電圧印加によって配向秩序が変化して光学的変調作用が生じる。ブルー相は光学的に等方であるため視野角依存性がなく、配向膜を形成しなくとも良いため、表示画像の質の向上及びコスト削減が可能である。

【0114】

また、ブルー相は狭い温度範囲でしか発現が難しく、温度範囲を広く改善するために液晶材料に、光硬化樹脂及び光重合開始剤を添加し、高分子安定化処理を行うことが好ましい。高分子安定化処理は、液晶、カイラル剤、光硬化樹脂、及び光重合開始剤を含む液晶材料に、光硬化樹脂、及び光重合開始剤が反応する波長の光を照射して行う。この高分子安定化処理は、温度制御を行い、等方相を示した状態で光照射して行っても良いし、ブルー相を示した状態で光照射して行ってもよい。

30

【0115】

例えば、液晶層の温度を制御し、ブルー相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行う。但し、これに限定されず、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内の等方相を発現した状態で液晶層に光を照射することにより高分子安定化処理を行ってもよい。ブルー相と等方相間の相転移温度とは、昇温時にブルー相から等方相に転移する温度又は降温時に等方相からブルー相に相転移する温度をいう。高分子安定化処理の一例としては、液晶層を等方相まで加熱した後、徐々に降温させてブルー相にまで相転移させ、ブルー相が発現する温度を保持した状態で光を照射することができる。他にも、液晶層を徐々に加熱して等方相に相転移させた後、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内の状態（等方相を発現した状態）で光を照射することができる。また、液晶材料に含まれる光硬化樹脂として、紫外線硬化樹脂（UV硬化樹脂）を用いる場合、液晶層に紫外線を照射すればよい。なお、ブルー相を発現させなくとも、ブルー相と等方相間の相転移温度から+10以内、好ましくは+5以内の状態（等方相を発現した状態）で光を照射して高分子安定化処理を行えば、応答速度が1ms以下と短く高速応答が可能である。

40

【0116】

光硬化樹脂は、アクリレート、メタクリレートなどの単官能モノマーでもよく、ジアクリレート、トリアクリレート、ジメタクリレート、トリメタクリレートなどの多官能モノマ

50

ーでもよく、これらを混合させたものでもよい。また、液晶性のものでも非液晶性のものでもよく、両者を混合させてもよい。光硬化樹脂は、用いる光重合開始剤の反応する波長の光で硬化する樹脂を選択すれば良く、代表的には紫外線硬化樹脂を用いることができる。

【0117】

光重合開始剤は、光照射によってラジカルを発生させるラジカル重合開始剤でもよく、酸を発生させる酸発生剤でもよく、塩基を発生させる塩基発生剤でもよい。

【0118】

具体的には、液晶材料として、J C - 1 0 4 1 X X (チッソ株式会社製)と4 - シアノ - 4' - ペンチルビフェニルの混合物を用いることができ、カイラル剤としては、Z L I - 4 5 7 2 (メルク株式会社製)を用いることができ、光硬化樹脂は、2 - エチルヘキシリーアクリレート、R M 2 5 7 (メルク株式会社製)、トリメチロールプロパントリアクリレートを用いることができ、光重合開始剤としては2 , 2 - ジメトキシ - 2 - フェニルアセトフェノンを用いることができる。

10

【0119】

本明細書において、液晶表示装置は光源の光を透過することによって表示を行う透過型の液晶表示装置である(又は半透過型の液晶表示装置)場合、少なくとも画素領域において光を透過させる必要がある。よって光が透過する画素領域に存在する第1の基板、第2の基板、他絶縁膜、導電膜などの薄膜はすべて可視光の波長領域の光に対して透光性とする。

20

【0120】

シール材としては、代表的には可視光硬化性、紫外線硬化性または熱硬化性の樹脂を用いるのが好ましい。代表的には、アクリル樹脂、エポキシ樹脂、アミン樹脂などを用いることができる。また、光(代表的には紫外線)重合開始剤、熱硬化剤、フィラー、カップリング剤を含んでもよい。

【0121】

液晶層に、光を照射して高分子安定化処理を行い、液晶層444を形成する。光は、液晶層に含まれる光硬化樹脂、及び光重合開始剤が反応する波長の光とする。この光照射による高分子安定化処理により、液晶層444がブルー相を示す温度範囲を広く改善することができる。

30

【0122】

シール材に紫外線などの光硬化樹脂を用い、滴下法で液晶層を形成する場合など、高分子安定化処理の光照射工程によってシール材の硬化も行ってよい。

【0123】

遮光層をトランジスタの少なくとも半導体層上方を覆うように設けると、トランジスタの半導体層への光の入射を遮断することができるため、半導体の光感度によるトランジスタの電気特性の変動を防止し、より安定化させることができる。また、遮光層をコンタクトホール上や画素間を覆うように設けるとコンタクトホール上に発生しやすい液晶の配向欠陥による光漏れ等の表示ムラを隠すことができるため、コントラストの低下を抑制することができる。よって、液晶表示装置の高精細化、高信頼性化を達成することができる。

40

【0124】

遮光層は、光を反射、又は吸収し、遮光性を有する材料を用いる。例えば、黒色の有機樹脂を用いることができ、感光性又は非感光性のポリイミドなどの樹脂材料に、顔料系の黒色樹脂やカーボンブラック、チタンブラック等を混合させて形成すればよい。また、遮光性の金属膜を用いることもでき、例えばクロム、モリブデン、ニッケル、チタン、コバルト、銅、タンクステン、又はアルミニウムなどを用いればよい。

【0125】

遮光層の形成方法は特に限定されず、材料に応じて、蒸着法、スパッタ法、CVD法などの乾式法、又はスピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)などの湿式法を用い、必要に応じてエッティング法

50

(ドライエッティング又はウェットエッティング)により所望のパターンに加工すればよい。

【0126】

遮光層を素子基板である第1の基板441側に作り込む構成であると、高分子安定化のための光照射処理工程において、該遮光層によって対向基板(第2の基板442)側から照射される光が吸収、遮断されることはないとするために、液晶層全体に均一に照射し、液晶層を光重合することができる。よって、不均一な光重合による液晶の配向乱れやそれに伴う表示ムラなどを防止することができる。

【0127】

本実施の形態では、第1の基板441の外側(液晶層444と反対側)に偏光板443aを、第2の基板442の外側(液晶層444と反対側)に偏光板443bを設ける。また、偏光板の他、位相差板、反射防止膜などの光学フィルムなどを設けてもよい。例えば、偏光板及び位相差板による円偏光を用いてもよい。以上の工程で、液晶表示装置を完成させることができる。

【0128】

また、大型の基板を用いて複数の液晶表示装置を作製する場合(所謂多面取り)、その分断工程は、高分子安定化処理の前か、偏光板を設ける前に行うことができる。分断工程による液晶層への影響(分断工程時にかかる力などによる配向乱れなど)を考慮すると、第1の基板と第2の基板とを貼り合わせた後、高分子安定化処理の前が好ましい。

【0129】

図示しないが、光源としてバックライト、サイドライトなどを用いればよい。光源は素子基板である第1の基板441側から、視認側である第2の基板442へと透過するように照射される。

【0130】

ブルー相を示す液晶材料は、応答速度が1 msec以下と短く高速応答が可能であるため、液晶表示装置の高性能化が可能になる。

【0131】

例えば、高速応答が可能であるため、バックライト装置にRGBの発光ダイオード(LED)等を配置し、時分割によりカラー表示する継時加法混色法(フィールドシーケンシャル法)や、時分割により左右の映像を交互に見るシャッター眼鏡方式による3次元表示方式に好適に採用できる。

【0132】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

【0133】

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

【0134】

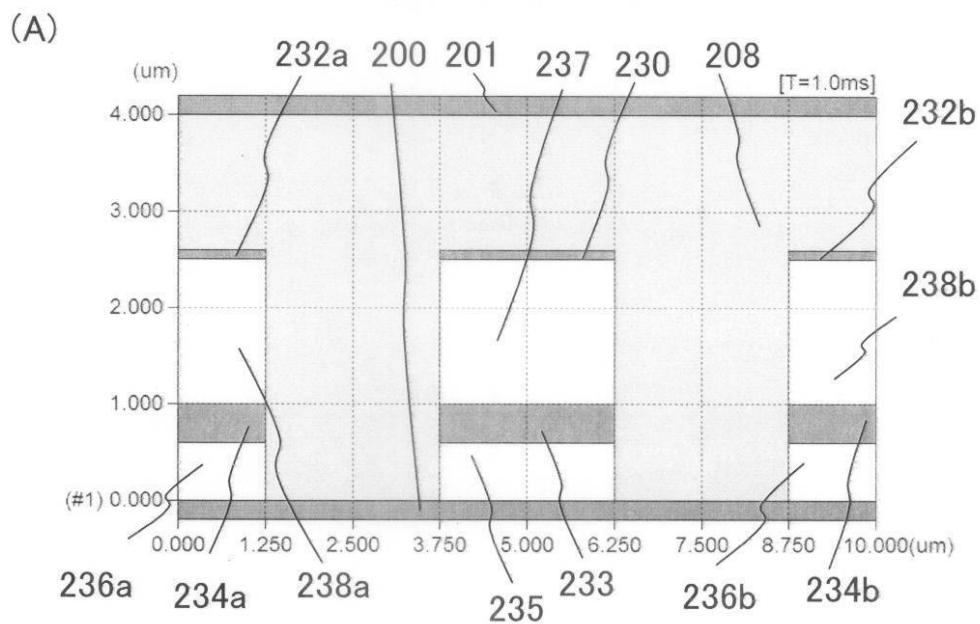

(実施の形態2)

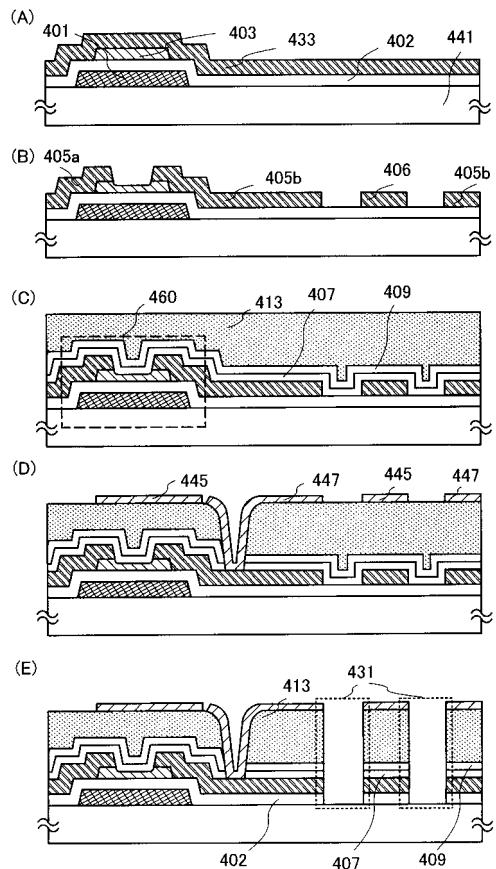

本明細書で開示する発明の構成の他の一形態である液晶表示装置を、図3及び図12を用いて説明する。図3は液晶表示装置の断面図であり、実施の形態1で示す液晶表示装置において、対向基板(第2の基板)側にも共通電極層を設ける構成である。なお、実施の形態1と同様なものに関しては同様の材料及び作製方法を適用することができ、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

【0135】

図3(A)は液晶表示装置の平面図であり、図3(B)は図3(A)の線X1-X2の断面図である。なお、図3(A)の平面図では第1の基板441側及び第2の基板側の第3の電極層446のみ図示しており、他の構成要素の記載は省略している。

【0136】

共通電極層は、対向基板(第2の基板)側にも一対の共通電極層が対向するように設けてもよく、図3のように液晶層444を間に挟んで第1の基板441側の共通電極層(第1

10

20

30

40

50

の共通電極層ともいう)である第2の電極層445と、第2の基板442側の共通電極層(第2の共通電極層ともいう)である第3の電極層446とが互いに重畠するように配置される。本実施の形態のように、共通電極層として第1の共通電極層及び第2の共通電極層と2種類設ける場合は、第1の共通電極層(第2の電極層445)及び第2の共通電極層(第3の電極層446)は等電位が好ましい。

#### 【0137】

第1の電極層447、第2の電極層445、及び第3の電極層446は平板状でなく、様々な開口パターンを有し、屈曲部や枝分かれした櫛歯状を含む形状である。また、第3の電極層446を形成する場合、第2の電極層445及び第3の電極層446は少なくとも画素領域において、平面図でみるとほぼ同形状であり液晶層を介して重畠するように配置される。なお、図3(B)の断面図では、第2の電極層445の端部と第3の電極層446の端部とは一致する例を示しているが、少なくとも一部重なって(重畠して)いれば端部が揃っていないてもよい(例えば、第2の電極層445の端部が第3の電極層446の端部より、外側に位置している、又は逆に内側に位置しているなど)。

10

#### 【0138】

トランジスタ460が有するドレイン電極層405bは第1の電極層447と電気的に接続し、第1の電極層447の下に絶縁層413、絶縁膜409、及び絶縁膜407を介して、ゲート絶縁層402上に延在して設けられる。第2の電極層445の下にも絶縁層413、絶縁膜409、及び絶縁膜407を介して、ゲート絶縁層402上に、ドレイン電極層405bと同工程で形成される導電層406が延在して設けられる。

20

#### 【0139】

第1の電極層447と、第2の電極層445との間に設けられるゲート絶縁層402、絶縁膜407、絶縁膜409、及び絶縁層413は選択的に除去されており、開口431が形成されている。本実施の形態では該開口431は第1の基板441に達する例を示す。該開口431を充填するように液晶層444が形成されている。

#### 【0140】

第1の電極層447及び第2の電極層445上には液晶層444が設けられ、対向基板である第2の基板442で封止されている。

#### 【0141】

第1の基板441及び第2の基板442は透光性基板であり、それぞれ外側(液晶層444と反対側)に偏光板443a、443bが設けられている。

30

#### 【0142】

第1の電極層447とドレイン電極層405bとは電気的に接続しており、同電位を与えることができる。また、第2の電極層445と導電層406とも電気的に接続しており、同電位を与えることができる。なお、同電位を与えることができるのであれば、第1の電極層447とドレイン電極層405b、第2の電極層445と導電層406とは直接接して設けられなくてもよく、他の配線層を介して(他の配線層に与えられた電位によって)、それぞれ同電位となつていればよい。

#### 【0143】

従って、第1の電極層447及び第2の電極層445に電圧を印加すると、ドレイン電極層405b及び導電層406にもそれぞれ同じ電圧を印加することができる。よって、液晶層444において、第1の電極層447と第2の電極層445との間と、ドレイン電極層405bと導電層406との間の開口431の領域にも広く電界を形成することができる。

40

#### 【0144】

さらに、本実施の形態のように、第2の基板442側に第2の共通電極層として第3の電極層446を設けると、第1の電極層447と第3の電極層446との間に液晶に対して斜め方向(基板に対して斜めの方向)の電界も加えることができるため、より効率よく液晶分子を制御できる。

#### 【0145】

50

液晶表示装置における電界の印加状態を計算した結果を、図12(B)に示す。計算は、シンテック社製、LCD Master、2s Benchを用いて行った。

【0146】

図12(A)は計算した液晶表示装置の構成を示す図である。図12(A)は、第1の基板200と第2の基板201とが、ブルー相を示す液晶材料を用いた液晶層208を間に挟持して対向するように配置された液晶表示装置である。図3及び図12(A)は、第1の基板441が第1の基板200に、第2の基板442が第2の基板201に、第1の電極層447が画素電極層230に、液晶層444が液晶層208に、ドレン電極層405bが導電層233に、第2の電極層445が共通電極層232a、232bに、導電層406が導電層234a、234bに、ゲート絶縁層402が層間膜235、236a、236bに、絶縁膜407、絶縁膜409、及び絶縁層413が層間膜237、238a、238bに、第3の電極層446が共通電極層231a、231bに、それぞれ対応している。

10

【0147】

層間膜235、236a、236b、237、238a、238bとしては誘電率4の絶縁体を用い、断面の幅は2.5μmとした。層間膜235、236a、236bの膜厚(高さ)は0.6μm、層間膜237、238a、238bの膜厚(高さ)は1.5μmである。また、図12(A)(B)において第2の基板201と液晶層208との間に共通電極層232a、232bと重なるように共通電極層231a、231bが設けられている。

20

【0148】

画素電極層230は、層間膜235、導電層233、層間膜237の積層上に形成され、同様に共通電極層232a、232bもそれぞれ層間膜236a、236b、導電層234a、234b、層間膜238a、238bの積層上に形成されている。なお、画素電極層230及び導電層233、共通電極層232a、232b及び導電層234a、234bは、それぞれ電気的に接続されている。また、画素電極層230と共通電極層232a、232bとの間には第1の基板200に達する開口が形成され、該開口にも液晶層208が形成されている。

30

【0149】

画素電極層230、共通電極層232a、232bの膜厚は0.1μm、導電層233、234a、234bの膜厚は0.4μm、画素電極層230と共通電極層232a、232bとの間の距離は2.5μmである。セルギャップ(液晶層の最大膜厚)に相当する第1の基板200から第2の基板201まで距離は4μmである。なお、共通電極層231aと共通電極層231bとの距離は7.5μmである。

【0150】

図12(A)の構造に対して、共通電極層231a、231b、共通電極層232a、232b及び同電位となる導電層234a、234bを0V、画素電極層230及び同電位となる導電層233は10Vの設定として計算した計算結果を図12(B)に示す。

40

【0151】

図12(B)において、実線は等電位線を示しており、円状に広がる等電位線の中心に画素電極層、共通電極層、又は導電層が配置されている。

【0152】

電界は等電位線と垂直に発現するので、図12(B)に示すように、層間膜237を介して積層された導電層233及び画素電極層230と、層間膜238a、238bを介して積層された導電層234a、234b及び共通電極層232a、232bとの間にそれぞれ横方向の電界が加わっていることが確認できる。

【0153】

さらに、画素電極層230と、共通電極層231a、231bとの間に斜め方向にも電界を形成することができる。よって、液晶層208全体にさらに広く電界を形成することが可能となる。

50

## 【 0 1 5 4 】

電界は、画素電極層 230 と共に電極層 232a、232b にも形成され、かつ導電層 233 と導電層 234a、234b との間に形成されるため、第 2 の基板 201 側の液晶層 208 だけでなく、第 1 の基板 200 側に設けられた層間膜の開口領域の液晶層 208 にも電界を形成することができる。さらに第 2 の基板側において画素電極層と重ならない位置に第 2 の共通電極層を設けることによって、画素電極層と第 2 の共通電極層との間に斜め電界が形成できる。このように同電位を有する導電層と電極層とを積層体とすることにより、広く液晶層に電界を形成することができる。よって、その電界を用いて液晶分子を制御できる。

## 【 0 1 5 5 】

従って、液晶表示装置において広く液晶層 208 に電界を形成することができ、かつ膜厚方向も含め液晶層 208 全体における液晶分子を応答させることができる。よって白透過率が向上し、白透過率と黒透過率（黒表示時の光の透過率）との比であるコントラスト比も高くすることができる。また、粘度の高いブルー相を示す液晶材料（液晶混合物）であっても、効果的に電界を印加することができるため、低消費電力化も達成できる。

## 【 0 1 5 6 】

第 2 の共通電極層である第 3 の電極層 446 は実施の形態 1 で示した共通電極層である第 2 の電極層 445 と同様な材料及び方法で形成することができる。

## 【 0 1 5 7 】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

## 【 0 1 5 8 】

また、より低電圧で高い白透過率を得るために、液晶表示装置の低消費電力化も達成できる。

## 【 0 1 5 9 】

（実施の形態 3 ）

本実施の形態では、本明細書に開示する液晶表示装置に適用できるトランジスタの例を示す。本明細書に開示する液晶表示装置に適用できるトランジスタの構造は特に限定されず、例えばトップゲート構造、又はボトムゲート構造のスタガ型及びブレーナ型などを用いることができる。また、トランジスタはチャネル形成領域が一つ形成されるシングルゲート構造でも、2つ形成されるダブルゲート構造もしくは3つ形成されるトリブルゲート構造であっても良い。また、チャネル形成領域の上下にゲート絶縁層を介して配置された2つのゲート電極層を有する、デュアルゲート型でもよい。なお、図 7 (A) 乃至 (D) にトランジスタの断面構造の一例を以下に示す。

## 【 0 1 6 0 】

図 7 (A) に示すトランジスタ 410 は、ボトムゲート構造の薄膜トランジスタの一つであり、逆スタガ型薄膜トランジスタともいう。

## 【 0 1 6 1 】

トランジスタ 410 は、絶縁表面を有する第 1 の基板 441 上に、ゲート電極層 401、ゲート絶縁層 402、半導体層 403、ソース電極層 405a、及びドレイン電極層 405b を含む。また、トランジスタ 410 を覆い、半導体層 403 に積層する絶縁膜 407 が設けられている。絶縁膜 407 上にはさらに絶縁膜 409 が形成されている。

## 【 0 1 6 2 】

図 7 (B) に示すトランジスタ 420 は、チャネル保護型（チャネルトップ型ともいう）と呼ばれるボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

## 【 0 1 6 3 】

トランジスタ 420 は、絶縁表面を有する第 1 の基板 441 上に、ゲート電極層 401、ゲート絶縁層 402、半導体層 403、半導体層 403 のチャネル形成領域を覆うチャネル保護層として機能する絶縁膜 427、ソース電極層 405a、及びドレイン電極層 405b を含む。また、トランジスタ 420 を覆い、絶縁膜 409 が形成されている。

10

20

30

40

50

## 【0164】

図7(C)に示すトランジスタ430はボトムゲート型の薄膜トランジスタであり、絶縁表面を有する基板である第1の基板441上に、ゲート電極層401、ゲート絶縁層402、ソース電極層405a、ドレイン電極層405b、及び半導体層403を含む。また、トランジスタ430を覆い、半導体層403に接する絶縁膜407が設けられている。絶縁膜407上にはさらに絶縁膜409が形成されている。

## 【0165】

トランジスタ430においては、ゲート絶縁層402は第1の基板441及びゲート電極層401上に接して設けられ、ゲート絶縁層402上にソース電極層405a、ドレイン電極層405bが接して設けられている。そして、ゲート絶縁層402、及びソース電極層405a、ドレイン電極層405b上に半導体層403が設けられている。

10

## 【0166】

図7(D)に示すトランジスタ440は、トップゲート構造の薄膜トランジスタの一つである。トランジスタ440は、絶縁表面を有する第1の基板441上に、絶縁膜437、半導体層403、ソース電極層405a、及びドレイン電極層405b、ゲート絶縁層402、ゲート電極層401を含み、ソース電極層405a、ドレイン電極層405bにそれぞれ配線層436a、配線層436bが接して設けられ電気的に接続している。

## 【0167】

実施の形態1又は実施の形態2と同様に、トランジスタ410、420、430、440において、画素電極層と電気的に接続するドレイン電極層405bは画素電極層と層間膜を介して、重なるように延在して設けられている。共通電極層の下にも層間膜を介して、ドレイン電極層405bと同工程で形成される導電層が延在して設けられている。

20

## 【0168】

また、半導体層とソース電極層の間にソース領域(一導電型を有する半導体層、バッファ層ともいう)を設けてもよい。例えば、ソース領域及びドレイン領域として、n型の導電型を示す半導体層を用いる。

## 【0169】

ソース領域またはドレイン領域として、半導体層を用いる場合は、チャネル形成領域として用いる半導体層の膜厚よりも薄く、且つ、より高い導電率(電気伝導度)を有するのが好ましい。

30

## 【0170】

ソース電極層405a、ドレイン電極層405bに接続する配線層436a、配線層436bのような導電膜も、ソース電極層405a、ドレイン電極層405bと同様な材料を用いることができる。

## 【0171】

絶縁膜427、437は、絶縁膜407と同様な材料を用いることができ、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などの無機絶縁膜を用いることができる。

## 【0172】

また、実施の形態1のように、絶縁膜409上にトランジスタ起因の表面凹凸を低減するために平坦化絶縁膜として絶縁層413を形成してもよい。

40

## 【0173】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

## 【0174】

## (実施の形態4)

上記実施の形態1乃至3において、トランジスタの半導体層に用いることのできる例として酸化物半導体を説明する。

## 【0175】

実施の形態3で示した図7(A)乃至(D)のトランジスタ410、420、430、4

50

40において、半導体層403として酸化物半導体層を用いることができる。

【0176】

半導体層403に用いる酸化物半導体としては、四元系金属酸化物であるIn-Sn-Ga-Zn-O系や、三元系金属酸化物であるIn-Ga-Zn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系や、二元系金属酸化物であるIn-Zn-O系、Sn-Zn-O系、Al-Zn-O系、Zn-Mg-O系、Sn-Mg-O系、In-Mg-O系や、In-O系、Sn-O系、Zn-O系などを用いることができる。また、上記酸化物半導体にSiO<sub>2</sub>を含んでもよい。ここで、例えば、In-Ga-Zn-O系酸化物半導体とは、少なくともInとGaとZnを含む酸化物であり、その組成比に特に制限はない。また、InとGaとZn以外の元素を含んでもよい。

10

【0177】

また、酸化物半導体層は、化学式InM<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記される薄膜を用いることができる。ここで、Mは、Ga、Al、MnおよびCoから選ばれた一または複数の金属元素を示す。例えばMとして、Ga、Ga及びAl、Ga及びMn、またはGa及びCoなどがある。

【0178】

酸化物半導体層を用いたトランジスタ410、420、430、440は、オフ状態における電流値(オフ電流値)を低くすることができる。よって、酸化物半導体層を用いたトランジスタを用いると、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力をより抑制する効果を奏する。

20

【0179】

また、半導体層403として酸化物半導体層を用いたトランジスタ410、420、430、440は、比較的高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に該トランジスタを用いることで、高画質な画像を提供することができる。また、該トランジスタを用いて、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

【0180】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

30

【0181】

(実施の形態5)

本実施の形態は、酸化物半導体層を含むトランジスタ、及び作製方法の他の一例を図8を用いて詳細に説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

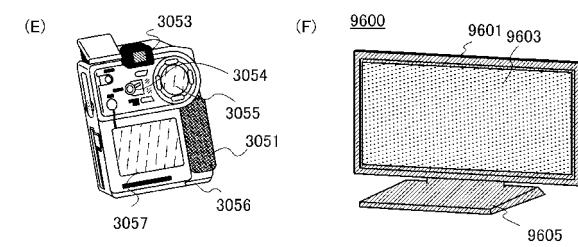

【0182】

図8(A)乃至(E)にトランジスタの断面構造の一例を示す。図8(A)乃至(E)に示すトランジスタ510は、図7(A)に示すトランジスタ410と同様なボトムゲート構造の逆スタガ型薄膜トランジスタである。

40

【0183】

本実施の形態の半導体層に用いる酸化物半導体は、n型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することによりI型(真性)の酸化物半導体、又はI型(真性)に限りなく近い酸化物半導体としたものである。すなわち、不純物を添加してI型化するのではなく、水素や水等の不純物を極力除去したことにより、高純度化されたI型(真性半導体)又はそれに近づけることを特徴としている。そうすることにより、フェルミ準位(E<sub>f</sub>)を真性フェルミ準位(E<sub>i</sub>)と同じレベルにまですることができる。従って、トランジスタ510が有する酸化物半導体層は、高純度化及び電気的にI型(真性)化された酸化物半導体層である。

50

## 【0184】

また、高純度化された酸化物半導体中にはキャリアが極めて少なく（ゼロに近い）、キャリア濃度は  $1 \times 10^{14} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{12} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満である。

## 【0185】

酸化物半導体中にキャリアが極めて少ないため、トランジスタのオフ電流を少なくすることができる。オフ電流は少なければ少ないほど好ましい。

## 【0186】

具体的には、上述の酸化物半導体層を具備するトランジスタ 510 は、オフ状態における電流値（オフ電流値）を、チャネル幅  $1 \mu\text{m}$  当たり  $10 \text{ zA} / \mu\text{m}$  未満、85 にて  $10 \text{ zA} / \mu\text{m}$  未満レベルにまで低くすることができる。10

## 【0187】

オフ状態における電流値（オフ電流値）が極めて小さいトランジスタを画素部におけるトランジスタとして用いることにより、静止画領域におけるリフレッシュ動作を少ない画像データの書き込み回数で行うことができる。

## 【0188】

また、上述の酸化物半導体層を具備するトランジスタ 510 はオン電流の温度依存性がほとんど見られず、オフ電流も非常に小さいままである。また、光劣化によるトランジスタ特性の変動も少ない。20

## 【0189】

以下、図 8 (A) 乃至 (E) を用い、基板 505 上にトランジスタ 510 を作製する工程を説明する。

## 【0190】

まず、絶縁表面を有する基板 505 上に導電膜を形成した後、第 1 のフォトリソグラフィ工程によりゲート電極層 511 を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0191】

絶縁表面を有する基板 505 は、実施の形態 1 に示した第 1 の基板 441 と同様な基板を用いることができる。本実施の形態では基板 505 としてガラス基板を用いる。30

## 【0192】

下地膜となる絶縁膜を基板 505 とゲート電極層 511 との間に設けてもよい。下地膜は、基板 505 からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

## 【0193】

また、ゲート電極層 511 の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

## 【0194】

次いで、ゲート電極層 511 上にゲート絶縁層 507 を形成する。ゲート絶縁層 507 は、プラズマ CVD 法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、酸化アルミニウム層、窒化アルミニウム層、酸化窒化アルミニウム層、窒化酸化アルミニウム層、又は酸化ハフニウム層を単層で又は積層して形成することができる。40

## 【0195】

本実施の形態の酸化物半導体は、不純物を除去され、I 型化又は実質的に I 型化された酸化物半導体を用いる。このような高純度化された酸化物半導体は界面準位、界面電荷に対して極めて敏感であるため、酸化物半導体層とゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体に接するゲート絶縁層は、高品質化が要求される。50

## 【0196】

例えば、 $\mu$ 波（例えば周波数2.45GHz）を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるので好ましい。高純度化された酸化物半導体と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好なものとすることができるからである。

## 【0197】

もちろん、ゲート絶縁層として良質な絶縁層を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁層の膜質、酸化物半導体との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであれば良い。

10

## 【0198】

また、ゲート絶縁層507、酸化物半導体膜530に水素、水酸基及び水分がなるべく含まれないようにするために、酸化物半導体膜530の成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層511が形成された基板505、又はゲート絶縁層507までが形成された基板505を予備加熱し、基板505に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、絶縁膜516の成膜前に、ソース電極層515a及びドレイン電極層515bまで形成した基板505にも同様に行ってもよい。

20

## 【0199】

次いで、ゲート絶縁層507上に、膜厚2nm以上200nm以下、好ましくは5nm以上30nm以下の酸化物半導体膜530を形成する（図8（A）参照。）。

## 【0200】

なお、酸化物半導体膜530をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層507の表面に付着している粉状物質（パーティクル、ごみともいう）を除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

30

## 【0201】

酸化物半導体膜530に用いる酸化物半導体は、実施の形態4に示した四元系金属酸化物や、三元系金属酸化物や、二元系金属酸化物や、In-O系、Sn-O系、Zn-O系などの酸化物半導体を用いることができる。また、上記酸化物半導体にSiO<sub>2</sub>を含んでもよい。本実施の形態では、酸化物半導体膜530としてIn-Ga-Zn-O系酸化物ターゲットを用いてスパッタリング法により成膜する。この段階での断面図が図8（A）に相当する。また、酸化物半導体膜530は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下においてスパッタリング法により形成することができる。

30

## 【0202】

酸化物半導体膜530をスパッタリング法で作製するためのターゲットとしては、例えば、組成比として、In<sub>2</sub>O<sub>3</sub>：Ga<sub>2</sub>O<sub>3</sub>：ZnO = 1 : 1 : 1 [mol比]（すなわち、In : Ga : Zn = 1 : 1 : 0.5 [atom比]）を用いることができる。また、他にも、In : Ga : Zn = 1 : 1 : 1 [atom比]、又はIn : Ga : Zn = 1 : 1 : 2 [atom比]の組成比を有するターゲットを用いてもよい。酸化物ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

40

## 【0203】

酸化物半導体膜530を、成膜する際に用いるスパッタガスは水素、水、水酸基又は水素

50

化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0204】

減圧状態に保持された成膜室内に基板を保持し、基板温度を100以上600以下好ましくは200以上400以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板505上に酸化物半導体膜530を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

10

【0205】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ごみともいう)が軽減でき、膜厚分布も均一となるために好ましい。

20

【0206】

次いで、酸化物半導体膜530を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

30

【0207】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体膜530の加工時に同時にを行うことができる。

【0208】

なお、ここで酸化物半導体膜530のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。例えば、酸化物半導体膜530のウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N(関東化学社製)を用いてもよい。

30

【0209】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化または脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、または400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層531を得る(図8(B)参照。)。

40

【0210】

なお、加熱処理装置は電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

【0211】

50

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。

【0212】

なお、第1の加熱処理においては、窒素、またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

【0213】

また、第1の加熱処理で酸化物半導体層を加熱した後、同じ炉に高純度の酸素ガス、高純度のN<sub>2</sub>Oガス、又は超乾燥エア(露点が-40以下、好ましくは-60以下)を導入してもよい。酸素ガスまたはN<sub>2</sub>Oガスに、水、水素などが含まれないことが好ましい。または、加熱処理装置に導入する酸素ガスまたはN<sub>2</sub>Oガスの純度を、6N以上好ましくは7N以上(即ち、酸素ガスまたはN<sub>2</sub>Oガス中の不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。酸素ガス又はN<sub>2</sub>Oガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給することによって、酸化物半導体層を高純度化及び電気的にI型(真性)化する。

【0214】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜530に行うことでもできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0215】

なお、第1の加熱処理は、上記以外にも、酸化物半導体層成膜後であれば、酸化物半導体層上にソース電極層及びドレイン電極層を積層させた後、あるいは、ソース電極層及びドレイン電極層上に絶縁層を形成した後、のいずれで行っても良い。

【0216】

また、ゲート絶縁層507にコンタクトホールを形成する場合、その工程は酸化物半導体膜530に第1の加熱処理を行う前でも行った後に行ってもよい。

【0217】

また、酸化物半導体層を2回に分けて成膜し、2回に分けて加熱処理を行うことで、下地部材の材料が、酸化物、窒化物、金属など材料を問わず、膜厚の厚い結晶領域(単結晶領域)、即ち、膜表面に垂直にc軸配向した結晶領域を有する酸化物半導体層を形成してもよい。例えば、3nm以上15nm以下の第1の酸化物半導体膜を成膜し、窒素、酸素、希ガス、または乾燥空気の雰囲気下で450以上850以下、好ましくは550以上750以下の第1の加熱処理を行い、表面を含む領域に結晶領域(板状結晶を含む)を有する第1の酸化物半導体膜を形成する。そして、第1の酸化物半導体膜よりも厚い第2の酸化物半導体膜を形成し、450以上850以下、好ましくは600以上700以下の第2の加熱処理を行い、第1の酸化物半導体膜を結晶成長の種として、上方に結晶成長させ、第2の酸化物半導体膜の全体を結晶化させ、結果として膜厚の厚い結晶領域を有する酸化物半導体層を形成してもよい。

【0218】

次いで、ゲート絶縁層507、及び酸化物半導体層531上に、ソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)となる導電膜を形成する。ソース電極層、及びドレイン電極層に用いる導電膜としては、実施の形態1に示したソース電極層405a、ドレイン電極層405bに用いる材料を用いることができる。

【0219】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層515a、ドレイン電極層515bを形成した後、レジスト

10

20

30

40

50

マスクを除去する（図8（C）参照。）。

【0220】

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いるとよい。酸化物半導体層531上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成されるトランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）を用いて第3のフォトリソグラフィ工程でのレジストマスク形成時の露光を行うとよい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化できる。

10

【0221】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

20

【0222】

なお、導電膜のエッチングの際に、酸化物半導体層531がエッチングされ、分断することのないようエッチング条件を最適化することが望まれる。しかしながら、導電膜のみをエッチングし、酸化物半導体層531を全くエッチングしないという条件を得ることは難しく、導電膜のエッチングの際に酸化物半導体層531は一部のみがエッチングされ、溝部（凹部）を有する酸化物半導体層となることもある。

【0223】

本実施の形態では、導電膜としてTi膜を用い、酸化物半導体層531にはIn-Ga-Zn-O系酸化物半導体を用いたので、エッチャントとしてアンモニア過水（アンモニア、水、過酸化水素水の混合液）を用いる。

30

【0224】

次いで、N<sub>2</sub>O、N<sub>2</sub>、またはArなどのガスを用いたプラズマ処理を行い、露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる絶縁膜516を形成する。

【0225】

絶縁膜516は、少なくとも1nm以上の膜厚とし、スパッタリング法など、絶縁膜516に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。絶縁膜516に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが低抵抗化（N型化）してしまい、寄生チャネルが形成されるおそれがある。よって、絶縁膜516はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

40

【0226】

本実施の形態では、絶縁膜516として膜厚200nmの酸化シリコン膜をスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化シリコン膜のスパッタリング法による成膜は、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、または希ガスと酸素の混合雰囲気下において行うことができる。また、ターゲットとして酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素を含む雰囲気下でスパッタリング法により酸化シリコンを形成することができる。酸化物半導体

50

層に接して形成する絶縁膜 516 は、水分や、水素イオンや、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、または酸化窒化アルミニウム膜などを用いる。

【0227】

酸化物半導体膜 530 の成膜時と同様に、絶縁膜 516 の成膜室内の残留水分を除去するためには、吸着型の真空ポンプ（クライオポンプなど）を用いることが好ましい。クライオポンプを用いて排気した成膜室で成膜した絶縁膜 516 に含まれる不純物の濃度を低減できる。また、絶縁膜 516 の成膜室内の残留水分を除去するための排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。

10

【0228】

絶縁膜 516 を、成膜する際に用いるスパッタガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0229】

次いで、不活性ガス雰囲気下、または酸素ガス雰囲気下で第2の加熱処理（好ましくは200以上400以下、例えば250以上350以下）を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部（チャネル形成領域）が絶縁膜 516 と接した状態で加熱される。

【0230】

以上の工程を経ることによって、酸化物半導体膜に対して第1の加熱処理を行って水素、水分、水酸基又は水素化物（水素化合物ともいう）などの不純物を酸化物半導体層より意図的に排除し、かつ不純物の排除工程によって同時に減少してしまう酸化物半導体を構成する主成分材料の一つである酸素を供給することができる。よって、酸化物半導体層は高純度化及び電気的にI型（真性）化する。

20

【0231】

以上の工程でトランジスタ 510 が形成される（図8（D）参照。）。

【0232】

また、絶縁膜 516 に欠陥を多く含む酸化シリコン層を用いると、酸化シリコン層形成後の加熱処理によって酸化物半導体層中に含まれる水素、水分、水酸基又は水素化物などの不純物を絶縁膜に拡散させ、酸化物半導体層中に含まれる該不純物をより低減させる効果を奏する。

30

【0233】

絶縁膜 516 上にさらに絶縁膜 506 を形成してもよい。例えば、RFスパッタリング法を用いて窒化シリコン膜を形成する。RFスパッタリング法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜などを用いる。本実施の形態では、絶縁膜 506 を、窒化シリコン膜を用いて形成する（図8（E）参照。）。

【0234】

本実施の形態では、保護絶縁層である絶縁膜 506 として、絶縁膜 516 まで形成された基板 505 を 100 ~ 400 の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜する。この場合においても、絶縁膜 516 と同様に、処理室内の残留水分を除去しつつ絶縁膜 506 を成膜することが好ましい。

40

【0235】

保護絶縁層の形成後、さらに大気中、100 以上 200 以下、1時間以上 30 時間以下での加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。

【0236】

50

図示しないが、絶縁膜409上に絶縁層413を形成する。以上の工程で実施の形態1における図2(C)の工程に対応する素子基板が完成する。よって、後工程は、実施の形態1と同様に行えばよい。

#### 【0237】

このように、本実施の形態を用いて作製した、高純度化された酸化物半導体層を含むトランジスタを用いることにより、オフ状態における電流値(オフ電流値)をより低くすることができる。よって、駆動方法において、画像信号等の電気信号の保持時間を長くすることができ、書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度をより少なくすることができるため、消費電力を抑制する効果を高くできる。

#### 【0238】

液晶表示装置に設けられる保持容量の大きさは、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定される。保持容量の大きさは、トランジスタのオフ電流等を考慮して設定すればよい。本実施の形態で示した高純度の酸化物半導体層を有するトランジスタを用いるのであれば、各画素における液晶容量に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。

#### 【0239】

また、高純度化された酸化物半導体層を含むトランジスタは、高い電界効果移動度が得られるため、高速駆動が可能である。よって、液晶表示装置の画素部に該トランジスタを用いることで、高画質な画像を提供することができる。また、該トランジスタによって、同一基板上に駆動回路部または画素部を作り分けて作製することができるため、液晶表示装置の部品点数を削減することができる。

#### 【0240】

また、ブルー相の液晶材料を用いると、配向膜へのラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中に引き起こされる静電気の影響によるトランジスタの電気的な特性の変動などの液晶表示装置の不良や破損を軽減することができる。よって液晶表示装置の生産性を向上させることができる。

#### 【0241】

ブルー相の液晶材料の応答速度が従来液晶材料よりも一桁以上速いため、酸化物半導体層を用いるトランジスタの様な倍速(高速)駆動が可能なデバイスと組み合わせることによって、液晶表示装置の高機能化及び高速応答化が実現できる。

#### 【0242】

以上のことから、本実施の形態のように酸化物半導体層を用いるトランジスタを有する液晶表示装置にブルー相の液晶材料を用いることはより効果的である。

#### 【0243】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

#### 【0244】

##### (実施の形態6)

上記実施の形態1乃至3において、トランジスタの半導体層に用いることのできる他の材料の例を説明する。

#### 【0245】

半導体素子が有する半導体層を形成する材料は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製される非晶質(アモルファス、以下「AS」ともいう。)半導体、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた多結晶半導体、或いは微結晶半導体などを用いることができる。半導体層はスパッタリング法、LPCVD法、またはプラズマCVD法等により成膜することができる。

#### 【0246】

10

20

30

40

50

微結晶半導体膜は、周波数が数十MHz～数百MHzの高周波プラズマCVD法、または周波数が1GHz以上のマイクロ波プラズマCVD装置により形成することができる。代表的には、SiH<sub>4</sub>、Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub>などの水素化珪素を水素で希釈して形成することができる。また、水素化珪素及び水素に加え、ヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素で希釈して微結晶半導体膜を形成することができる。これらのときの水素化珪素に対して水素の流量比を5倍以上200倍以下、好ましくは50倍以上150倍以下、更に好ましくは100倍とする。

#### 【0247】

アモルファス半導体としては、代表的には水素化アモルファスシリコン、結晶性半導体としては代表的にはポリシリコンなどがあげられる。ポリシリコン（多結晶シリコン）には、800以上 のプロセス温度を経て形成されるポリシリコンを主材料として用いた所謂高温ポリシリコンや、600以下 のプロセス温度で形成されるポリシリコンを主材料として用いた所謂低温ポリシリコン、また結晶化を促進する元素などを用いて、非晶質シリコンを結晶化させたポリシリコンなどを含んでいる。もちろん、前述したように、微結晶半導体又は半導体層の一部に結晶相を含む半導体を用いることもできる。

10

#### 【0248】

半導体層に、結晶性半導体膜を用いる場合、その結晶性半導体膜の作製方法は、種々の方法（レーザ結晶化法、熱結晶化法、またはニッケルなどの結晶化を助長する元素を用いた熱結晶化法等）を用いれば良い。また、SASである微結晶半導体をレーザ照射して結晶化し、結晶性を高めることもできる。結晶化を助長する元素を導入しない場合は、非晶質珪素膜にレーザ光を照射する前に、窒素雰囲気下500で1時間加熱することによって非晶質珪素膜の含有水素濃度を $1 \times 10^{20}$ atoms/cm<sup>3</sup>以下にまで放出させる。これは水素を多く含んだ非晶質珪素膜にレーザ光を照射すると非晶質珪素膜が破壊されてしまうからである。

20

#### 【0249】

非晶質半導体膜への金属元素の導入の仕方としては、当該金属元素を非晶質半導体膜の表面又はその内部に存在させ得る手法であれば特に限定はなく、例えばスパッタリング法、CVD法、プラズマ処理法（プラズマCVD法も含む）、吸着法、金属塩の溶液を塗布する方法を使用することができる。このうち溶液を用いる方法は簡便であり、金属元素の濃度調整が容易であるという点で有用である。また、このとき非晶質半導体膜の表面の濡れ性を改善し、非晶質半導体膜の表面全体に水溶液を行き渡らせるため、酸素雰囲気中のUV光の照射、熱酸化法、ヒドロキシラジカルを含むオゾン水又は過酸化水素による処理等により、酸化膜を成膜することが望ましい。

30

#### 【0250】

また、非晶質半導体膜を結晶化し、結晶性半導体膜を形成する結晶化工程で、非晶質半導体膜に結晶化を促進する元素（触媒元素、金属元素とも示す）を添加し、熱処理（550～750で3分～24時間）により結晶化を行ってもよい。結晶化を助長（促進）する元素としては、鉄（Fe）、ニッケル（Ni）、コバルト（Co）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、白金（Pt）、銅（Cu）及び金（Au）から選ばれた一種又は複数種類を用いることができる。

40

#### 【0251】

結晶化を助長する元素を結晶性半導体膜から除去、又は軽減するため、結晶性半導体膜に接して、不純物元素を含む半導体膜を形成し、ゲッタリングシンクとして機能させる。不純物元素としては、n型を付与する不純物元素、p型を付与する不純物元素や希ガス元素などを用いることができ、例えばリン（P）、窒素（N）、ヒ素（As）、アンチモン（Sb）、ビスマス（Bi）、ボロン（B）、ヘリウム（He）、ネオン（Ne）、アルゴン（Ar）、Kr（クリプトン）、Xe（キセノン）から選ばれた一種または複数種を用いることができる。結晶化を促進する元素を含む結晶性半導体膜に、希ガス元素を含む半

50

導体膜を形成し、熱処理（550～750で3分～24時間）を行う。結晶性半導体膜中に含まれる結晶化を促進する元素は、希ガス元素を含む半導体膜中に移動し、結晶性半導体膜中の結晶化を促進する元素は除去、又は軽減される。その後、ゲッタリングシンクとなつた希ガス元素を含む半導体膜を除去する。

【0252】

非晶質半導体膜の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、熱処理やレーザ光照射を単独で、複数回行っても良い。

【0253】

また、結晶性半導体膜を、直接基板にプラズマ法により形成しても良い。また、プラズマ法を用いて、結晶性半導体膜を選択的に基板に形成してもよい。

10

【0254】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0255】

（実施の形態7）

トランジスタを作製し、該トランジスタを画素部、さらには駆動回路に用いて表示機能を有する液晶表示装置を作製することができる。また、トランジスタを用いて駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

20

【0256】

また、液晶表示装置は、液晶素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。さらに、該液晶表示装置を作製する過程における、液晶素子が完成する前の一形態に相当する素子基板に関し、該素子基板は、電流を液晶素子に供給するための手段を複数の各画素に備える。素子基板は、具体的には、液晶素子の画素電極のみが形成された状態であっても良いし、画素電極となる導電膜を成膜した後であって、エッチングして画素電極を形成する前の状態であっても良いし、あらゆる形態があてはまる。

【0257】

なお、本明細書中における液晶表示装置とは、画像表示デバイス、表示デバイスを指す。また、コネクター、例えばFPC（Flexible printed circuit）もしくはTAB（Tape Automated Bonding）テープもしくはTCP（Tape Carrier Package）が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG（Chip On Glass）方式によりIC（集積回路）が直接実装されたモジュールも全て液晶表示装置に含むものとする。

30

【0258】

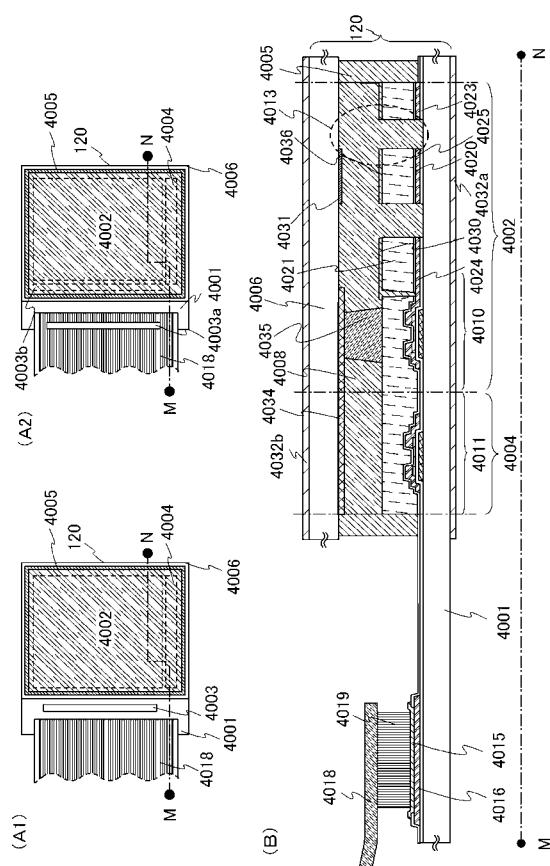

液晶表示装置の一形態に相当する液晶表示パネル120の外観及び断面について、図5を用いて説明する。図5（A1）（A2）は、第1の基板4001上に形成されたトランジスタ4010、4011、及び液晶素子4013を、第2の基板4006との間にシール材4005によって封止した、パネルの平面図であり、図5（B）は、図5（A1）（A2）のM-Nにおける断面図に相当する。

40

【0259】

第1の基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また画素部4002と、走査線駆動回路4004の上に第2の基板4006が設けられている。よって画素部4002と、走査線駆動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とによって、液晶層4008と共に封止されている。

【0260】

また、図5（A1）は第1の基板4001上のシール材4005によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成

50

された信号線駆動回路 4003 が実装されている。なお、図 5 (A2) は信号線駆動回路の一部を第 1 の基板 4001 上に設けられたトランジスタで形成する例であり、第 1 の基板 4001 上に信号線駆動回路 4003b が形成され、かつ別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路 4003a が実装されている。

#### 【0261】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG 方法、ワイヤボンディング方法、或いは TAB 方法などを用いることができる。図 5 (A1) は、COG 方法により信号線駆動回路 4003 を実装する例であり、図 5 (A2) は、TAB 方法により信号線駆動回路 4003 を実装する例である。

10

#### 【0262】

また第 1 の基板 4001 上に設けられた画素部 4002 と、走査線駆動回路 4004 は、トランジスタを複数有しており、図 5 (B) では、画素部 4002 に含まれるトランジスタ 4010 と、走査線駆動回路 4004 に含まれるトランジスタ 4011 とを例示している。トランジスタ 4010、4011 上には絶縁膜 4020、絶縁層 4021 が設けられている。

#### 【0263】

トランジスタ 4010、4011 は、実施の形態 1 乃至 6 のいずれかに示すトランジスタを適用することができる。トランジスタ 4010、4011 は n チャネル型薄膜トランジスタである。

20

#### 【0264】

また、絶縁層 4021、又は絶縁膜 4020 上において、駆動回路用のトランジスタ 4011 の半導体層のチャネル形成領域と重なる位置に導電層を設けてもよい。導電層は、電位がトランジスタ 4011 のゲート電極層と同じでもよいし、異なっていても良く、第 2 のゲート電極層として機能させることもできる。また、導電層の電位が GND、0V、或いはフローティング状態であってもよい。

#### 【0265】

液晶素子 4013 は、画素電極層 4030、第 2 の共通電極層 4031、第 1 の共通電極層 4036 及び液晶層 4008 を含む。なお、第 1 の基板 4001、第 2 の基板 4006 の外側にはそれぞれ偏光板 4032a、4032b が設けられている。また、本実施の形態では、第 2 の共通電極層 4031 が第 2 の基板 4006 側にも設けられる例であり、画素電極層 4030 及び第 1 の共通電極層 4036 と第 2 の共通電極層 4031 とは液晶層 4008 を介して積層する構成となっている。第 2 の共通電極層 4031 は実施の形態 1 のように設けない構成であってもよい。

30

#### 【0266】

層間膜 (ゲート絶縁層 4023、絶縁膜 4020、絶縁層 4021) を介して画素電極層 4030 はトランジスタ 4010 のドレイン電極層 4024 と、第 1 の共通電極層 4036 はドレイン電極層 4024 と同工程で形成される導電層 4025 と電気的に接続する (または同電位を与えられる)。画素電極層 4030 と第 1 の共通電極層 4036 との間の層間膜 (ゲート絶縁層 4023、絶縁膜 4020、絶縁層 4021) は選択的に除去されて開口が形成されている。該開口には液晶が充填され液晶層 4008 が形成される。

40

#### 【0267】

従って、画素電極層 4030 及び第 1 の共通電極層 4036 に電圧を印加すると、ドレイン電極層 4024 及び導電層 4025 にもそれぞれ同じ電圧を印加することができる。よって、液晶層 4008 において、画素電極層 4030 と第 1 の共通電極層 4036 との間と、ドレイン電極層 4024 と導電層 4025 との間の開口の領域にも広く電界を形成することができる。よって、その電界を用いて液晶分子を制御できる。

#### 【0268】

また、第 2 の基板 4006 側に第 2 の共通電極層 4031 を設けると、画素電極層 4030 と第 2 の共通電極層 4031 との間にも液晶に対して斜め方向 (基板に対して斜めの方

50

向)の電界も加えることができるため、より効率よく液晶分子を制御できる。

【0269】

従って、膜厚方向も含め液晶層全体における液晶分子を応答させることができ、白透過率が向上する。よって白透過率と黒透過率との比であるコントラスト比も高くすることができる。

【0270】

なお、第1の基板4001、第2の基板4006としては、透光性を有するガラス、プラスチックなどを用いることができる。プラスチックとしては、FRP (Fiberglass - Reinforced Plastics) 板、PVF (ポリビニルフルオライド) フィルム、ポリエスチルフィルムまたはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフィルムやポリエスチルフィルムで挟んだ構造のシートを用いることもできる。

10

【0271】

また4035は絶縁膜を選択的にエッティングすることで得られる柱状のスペーサであり、液晶層4008の膜厚(セルギャップ)を制御するために設けられている。なお球状のスペーサを用いていても良い。液晶層4008を用いる液晶表示装置において液晶層の厚さであるセルギャップは1μm以上20μm以下とすることが好ましい。

【0272】

なお図5は透過型液晶表示装置の例であるが、半透過型液晶表示装置でも適用できる。

20

【0273】

また、図5の液晶表示装置では、基板の外側(視認側)に偏光板を設ける例を示すが、偏光板は基板の内側に設けてもよい。偏光板の材料や作製工程条件によって適宜設定すればよい。また、ブラックマトリクスとして機能する遮光層を設けてもよい。

【0274】

図5においては、トランジスタ4010、4011上方を覆うように遮光層4034が第2の基板4006側に設けられている。遮光層4034を設けることにより、さらにコントラスト向上やトランジスタの安定化の効果を高めることができる。

【0275】

トランジスタの保護膜として機能する絶縁膜4020で覆う構成としてもよいが、特に限定されない。

30

【0276】

なお、保護膜は、大気中に浮遊する有機物や金属物、水蒸気などの汚染不純物の侵入を防ぐためのものであり、緻密な膜が好ましい。保護膜は、スパッタ法を用いて、酸化珪素膜、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜の単層、又は積層で形成すればよい。

【0277】

また、平坦化絶縁膜として透光性の絶縁層をさらに形成する場合、ポリイミド、アクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(LOW-k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、絶縁層を形成してもよい。

40

【0278】

積層する絶縁層の形成法は、特に限定されず、その材料に応じて、スパッタ法、SOG法、スピニコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法、スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。絶縁層を材料液を用いて形成する場合、ベークする工程で同時に、半導体層の加熱処理(200 ~ 400)を行ってもよい。絶縁層の焼成工程と半導体層の加熱処理を兼ねることで効率よく液晶表示装置を作製することが可能

50

となる。

【0279】

画素電極層4030、第2の共通電極層4031及び第1の共通電極層4036は、酸化タンクスチレンを含むインジウム酸化物、酸化タンクスチレンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。

【0280】

また、画素電極層4030、第2の共通電極層4031及び第1の共通電極層4036はタンクスチレン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、チタン(Ti)、白金(Pt)、アルミニウム(Al)、銅(Cu)、銀(Ag)等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

【0281】

また、画素電極層4030、第2の共通電極層4031及び第1の共通電極層4036として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。

【0282】

また別途形成された信号線駆動回路4003と、走査線駆動回路4004または画素部4002に与えられる各種信号及び電位は、FPC4018から供給されている。

【0283】

また、トランジスタは静電気などにより破壊されやすいため、ゲート線またはソース線に対して、駆動回路保護用の保護回路を同一基板上に設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

【0284】

図5では、接続端子電極4015が、画素電極層4030と同じ導電膜から形成され、端子電極4016は、トランジスタ4010、4011のソース電極層及びドレイン電極層と同じ導電膜で形成されている。

【0285】

接続端子電極4015は、FPC4018が有する端子と、異方性導電膜4019を介して電気的に接続されている。

【0286】

また図5においては、信号線駆動回路4003を別途形成し、第1の基板4001に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装しても良いし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成して実装しても良い。

【0287】

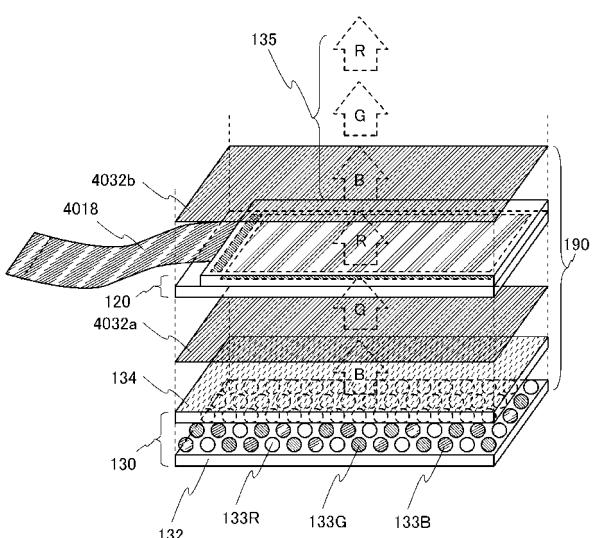

本明細書に開示する液晶表示装置として液晶表示モジュールを構成する一例を示す。本実施の形態ではカラー表示を行う液晶表示モジュールの一例として図6に液晶表示モジュール190の構成を示す。

【0288】

液晶表示モジュール190はバックライト部130と、液晶素子がマトリクス状に設けられた液晶表示パネル120と、液晶表示パネル120を挟む偏光板4032a、及び偏光板4032bを有する。バックライト部130には発光素子、例えば三原色のLED(133R、133G、及び133B)をマトリクス状に配置し、また液晶表示パネル120と発光素子の間に拡散板134を配置したものをバックライト部130として用いることができる。また、外部入力端子となるFPC4018は液晶表示パネル120に設けた端子部と電気的に接続されている。

【0289】

10

20

30

40

50

本実施の形態では、発光ダイオード（ＬＥＤ）を用いて、時分割によりカラー表示する継時加法混色法（フィールドシーケンシャル法）を採用する。

【0290】

バックライト部130はバックライト制御回路、及びバックライト132を有する。バックライト132には発光素子133が配置されている。

【0291】

本実施の形態では、バックライト132は、複数の異なる発光色の発光素子133を有する。異なる発光色の組み合わせとしては、例えば、赤（R）、緑（G）、及び青（B）の3種類の発光素子を用いることができる。R、G、及びBの三原色を用いることで、フルカラー画像を表示できる。

10

【0292】

また、R、G、及びBの発光素子から選んだ複数を同時に光らせて表現する色（例えば、RとGで表す黄（Y）、GとBで表すシアン（C）、BとRで表すマゼンタ（M）など）を発する別の発光素子を、R、G、及びBの発光素子に加えて配置してもよい。

【0293】

また、液晶表示装置の色再現特性をより豊かにするため、三原色以外の光を発する発光素子を加えてもよい。R、G、及びBの発光素子を用いて表現できる色は、色度図上のそれぞれの発光色に対応する3点が描く三角形の内側に示される色に限られる。従って、色度図上の該三角形の外側に配置される発光素子を別途加えることで、表示装置の色再現特性を豊かにすることができる。

20

【0294】

例えば、色度図の中心から、色度図上の青色の発光素子Bに対応する点に向かって概ね外側に位置する点で表される深い青色（Deep Blue：DB）や、色度図の中心から、赤色の発光素子Rに対応する色度図上の点に向かって概ね外側に位置する点で表されるより深い赤色（Deep Red：DR）を発する発光素子を、バックライト132のR、G、及びBに加えて使用することができる。

【0295】

図6には、3色の光135が矢印（R、G、及びB）で模式的に示してある。バックライト部130から逐次発せられるパルス状の異なる色の光が、バックライト部130と同期して動作する液晶表示パネル120の液晶素子により変調され、液晶表示モジュール190から観察者に達する。観察者は逐次的に発せられる光を映像として捉える。

30

【0296】

また、本実施の形態で例示される液晶表示装置は、カラーフィルタを用いることなく、フルカラー画像の表示が可能である。カラーフィルタがバックライトの光を吸収しないため光の利用効率が高く、フルカラー画像の表示においても消費電力が抑制されている。

【0297】

以上のように、ブルー相を示す液晶層を用いた液晶表示装置において、コントラスト比を高めることができる。

【0298】

また、より低電圧で高い白透過率を得ることができるために、液晶表示装置の低消費電力化も達成できる。

40

【0299】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

【0300】

（実施の形態8）

本明細書に開示する液晶表示装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともい

50

う)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態で説明した液晶表示装置を具備する電子機器の例について説明する。

### 【0301】

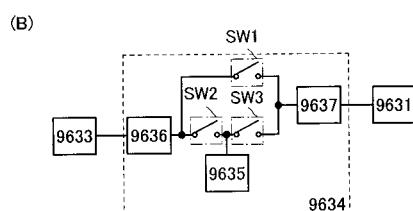

図9(A)は電子書籍(E-bookともいう)であり、筐体9630、表示部9631、操作キー9632、太陽電池9633、充放電制御回路9634を有することができる。図9(A)に示した電子書籍は、様々な情報(静止画、動画、テキスト画像など)を表示する機能、カレンダー、日付又は時刻などを表示部に表示する機能、表示部に表示した情報を操作又は編集する機能、様々なソフトウェア(プログラム)によって処理を制御する機能、等を有することができる。なお、図9(A)では充放電制御回路9634の一例としてバッテリー9635、DCDCコンバータ(以下、コンバータと略記)9636を有する構成について示している。実施の形態1乃至7のいずれかで示した液晶表示装置を表示部9631に適用することにより、高コントラストで視認性がよく、かつ低消費電力な電子書籍とすることができる。

10

### 【0302】

図9(A)に示す構成とすることにより、表示部9631として半透過型、又は反射型の液晶表示装置を用いる場合、比較的明るい状況下での使用も予想され、太陽電池9633による発電、及びバッテリー9635での充電を効率よく行うことができ、好適である。なお太陽電池9633は、筐体9630の空きスペース(表面や裏面)に適宜設けることができるため、効率的なバッテリー9635の充電を行う構成とすることができますため好適である。なおバッテリー9635としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

20

### 【0303】

また図9(A)に示す充放電制御回路9634の構成、及び動作について図9(B)にブロック図を示し説明する。図9(B)には、太陽電池9633、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3、表示部9631について示しており、バッテリー9635、コンバータ9636、コンバータ9637、スイッチSW1乃至SW3が充放電制御回路9634に対応する箇所となる。

30

### 【0304】

まず外光により太陽電池9633により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー9635を充電するための電圧となるようコンバータ9636で昇圧または降圧がなされる。そして、表示部9631の動作に太陽電池9633からの電力が用いられる際にはスイッチSW1をオンにし、コンバータ9637で表示部9631に必要な電圧に昇圧または降圧することとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2をオンにしてバッテリー9635の充電を行う構成とすればよい。

40

### 【0305】

次いで外光により太陽電池9633により発電がされない場合の動作の例について説明する。バッテリー9635に蓄電された電力は、スイッチSW3をオンにすることでコンバータ9637により昇圧または降圧がなされる。そして、表示部9631の動作にバッテリー9635からの電力が用いられることとなる。

### 【0306】

なお太陽電池9633については、充電手段の一例として示したが、他の手段によるバッテリー9635の充電を行う構成であってもよい。また他の充電手段を組み合わせて行う構成としてもよい。

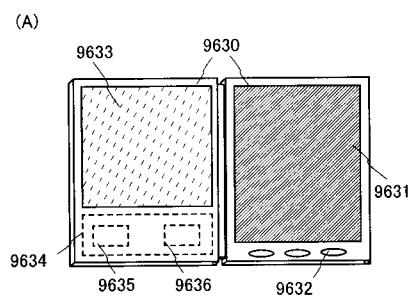

### 【0307】

図10(A)は、ノート型のパーソナルコンピュータであり、本体3001、筐体3002、表示部3003、キーボード3004などによって構成されている。実施の形態1乃至7のいずれかで示した液晶表示装置を表示部3003に適用することにより、高コントラストで視認性がよく、かつ低消費電力なノート型のパーソナルコンピュータとすること

50

ができる。

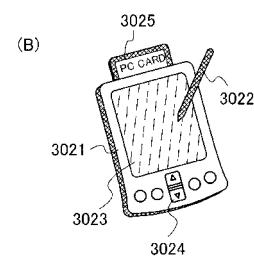

【0308】

図10(B)は、携帯情報端末(PDA)であり、本体3021には表示部3023と、外部インターフェイス3025と、操作ボタン3024等が設けられている。また操作用の付属品としてスタイルス3022がある。実施の形態1乃至7のいずれかで示した液晶表示装置を表示部3023に適用することにより、高コントラストで視認性がよく、低消費電力な携帯情報端末(PDA)とすることができる。

【0309】

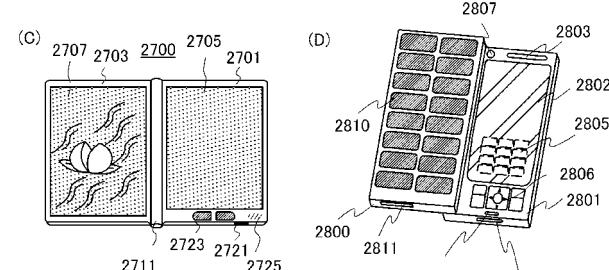

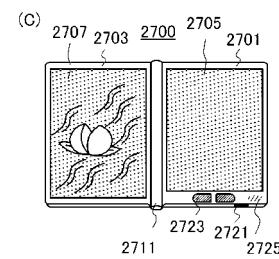

図10(C)は、電子書籍の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により一体とされており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

10

【0310】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、継ぎ画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成として、例えば右側の表示部(図10(C)では表示部2705)に文章を表示し、左側の表示部(図10(C)では表示部2707)に画像を表示することができる。実施の形態1乃至7のいずれかで示した液晶表示装置を表示部2705、表示部2707に適用することにより、高コントラストで視認性がよく、かつ低消費電力な電子書籍とすることができる。

20

【0311】

また、図10(C)では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングデバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

30

【0312】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0313】

図10(D)は、携帯電話であり、筐体2800及び筐体2801の二つの筐体で構成されている。筐体2801には、表示パネル2802、スピーカー2803、マイクロフォン2804、ポインティングデバイス2806、カメラ用レンズ2807、外部接続端子2808などを備えている。また、筐体2800には、携帯電話の充電を行う太陽電池セル2810、外部メモリスロット2811などを備えている。また、アンテナは筐体2801内部に内蔵されている。実施の形態1乃至7のいずれかで示した液晶表示装置を表示パネル2802に適用することにより、高コントラストで視認性がよく、かつ低消費電力な携帯電話とすることができる。

40

【0314】

また、表示パネル2802はタッチパネルを備えており、図10(D)には映像表示されている複数の操作キー2805を点線で示している。なお、太陽電池セル2810で出力される電圧を各回路に必要な電圧に昇圧するための昇圧回路も実装している。

【0315】

表示パネル2802は、使用形態に応じて表示の方向が適宜変化する。また、表示パネル2802と同一面上にカメラ用レンズ2807を備えているため、テレビ電話が可能である。スピーカー2803及びマイクロフォン2804は音声通話に限らず、テレビ電話、

50

録音、再生などが可能である。さらに、筐体 2800 と筐体 2801 は、スライドし、図 10 (D) のように展開している状態から重なり合った状態とすることができ、携帯に適した小型化が可能である。

#### 【0316】

外部接続端子 2808 は A C アダプタ及び U S B ケーブルなどの各種ケーブルと接続可能であり、充電及びパーソナルコンピュータなどとのデータ通信が可能である。また、外部メモリスロット 2811 に記録媒体を挿入し、より大量のデータ保存及び移動に対応できる。

#### 【0317】

また、上記機能に加えて、赤外線通信機能、テレビ受信機能などを備えたものであってもよい。

#### 【0318】

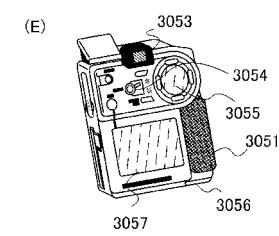

図 10 (E) は、デジタルビデオカメラであり、本体 3051、表示部 (A) 3057、接眼部 3053、操作スイッチ 3054、表示部 (B) 3055、バッテリー 3056 などによって構成されている。実施の形態 1 乃至 7 のいずれかで示した液晶表示装置を表示部 (A) 3057、表示部 (B) 3055 に適用することにより、高コントラストで視認性がよく、かつ低消費電力なデジタルビデオカメラとすることができる。

#### 【0319】

図 10 (F) は、テレビジョン装置の一例を示している。テレビジョン装置 9600 は、筐体 9601 に表示部 9603 が組み込まれている。表示部 9603 により、映像を表示することが可能である。また、ここでは、スタンド 9605 により筐体 9601 を支持した構成を示している。実施の形態 1 乃至 7 のいずれかで示した液晶表示装置を表示部 9603 に適用することにより、高コントラストで視認性がよく、かつ低消費電力なテレビジョン装置とすることができる。

#### 【0320】

テレビジョン装置 9600 の操作は、筐体 9601 が備える操作スイッチや、別体のリモコン操作機により行うことができる。また、リモコン操作機に、当該リモコン操作機から出力する情報を表示する表示部を設ける構成としてもよい。

#### 【0321】

なお、テレビジョン装置 9600 は、受信機やモデムなどを備えた構成とする。受信機により一般的のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向（送信者から受信者）または双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

#### 【0322】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 1 2】

(A)

(B)

---

フロントページの続き

(72)発明者 三上 真弓

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

F ターク(参考) 2H088 GA02 GA03 GA04 GA06 GA10 GA17 HA02 HA04 HA08 JA03

MA02 MA10

2H092 GA14 GA17 GA29 JA24 JA46 JB05 JB16 JB57 KA08 MA05

MA08 MA13 MA17 NA01 NA05 NA26 QA05 QA15

2H189 AA04 BA04 CA08 HA16 JA03 JA14 JA30 LA03 LA10