(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2007-0095041

(43) 공개일자 2007년09월28일

(51) Int. Cl.

*H01L 33/00* (2006.01)

(21) 출원번호 10-2006-0025212

(22) 출원일자 2006년03월20일

심사청구일자 2007년05월09일

(71) 출원인

삼성전기주식회사

경기도 수원시 영통구 매탄동 314

(72) 발명자

정재우

서울 서초구 잠원동 반포한양아파트 1-103

김형근

경기 수원시 영통구 영통동 청명마을3단지아파트

336-1301

(뒷면에 계속)

(74) 대리인

특허법인 씨엔에스·로고스

전체 청구항 수 : 총 6 항

## (54) 교류 전압용 발광 소자 유닛

## (57) 요 약

교류 전압용 발광 소자 유닛이 개시된다.

개시된 발광 소자 유닛은, 전기 배선이 형성되어 있는 서브 마운트; 복수 개의 제1 발광 소자가 상기 서브 마운트 상에 직렬 연결된 제1 발광 소자 어레이; 복수 개의 제2 발광 소자가 상기 서브 마운트 상에 브릿지 회로로 연결된 것으로, 상기 제1 발광 소자 어레이에 연결된 제2 발광 소자 어레이;를 포함하는 것을 특징으로 한다.

본 발명은 발광 소자들을 브릿지 회로 및 직렬로 연결하여 별도의 정류 소자 없이 브릿지 회로를 통해 정류 동작을 하도록 함으로써 구조를 단순화 및 소형화할 수 있다.

## 대표도 - 도2

(72) 발명자

**조제희**

경기 용인시 기흥읍 영덕리 태영아파트 206-1603

김유식

경기 수원시 영통구 망포동 595번지 동수원엘지빌

리지 101-1105

---

## 특허청구의 범위

### 청구항 1

교류 전압용 발광 소자 유닛에 있어서,

전기 배선이 형성되어 있는 서브 마운트;

복수 개의 제1 발광 소자가 상기 서브 마운트 상에 직렬 연결된 제1 발광 소자 어레이;

복수 개의 제2 발광 소자가 상기 서브 마운트 상에 브릿지 회로로 연결된 것으로, 상기 제1 발광 소자 어레이에

연결된 제2 발광 소자 어레이;를 포함하는 것을 특징으로 하는 발광 소자 유닛.

### 청구항 2

제 1항에 있어서,

상기 제1 및 제2 발광 소자는 발광 칩으로 이루어진 것을 특징으로 하는 발광 소자 유닛.

### 청구항 3

제 1항 또는 제 2항에 있어서,

상기 제2 발광 소자의 브레이크 다운 전압(Vb)은 다음의 조건식을 만족하는 것을 특징으로 하는 발광 소자

유닛.

<조건식>

$$V_b > \frac{(V_p - nV_f)}{n}$$

여기서, Vf는 제2 발광 소자의 순방향 전압을, Vp는 공급 전압의 최대값을, n은 브릿지 회로의 한 번에 배열되는 제2 발광 소자의 개수를 나타낸다.

### 청구항 4

제 1항 또는 제 2항에 있어서,

상기 제1 및 제2 발광 소자는 상기 서브 마운트에 플립칩으로 실장되는 것을 특징으로 하는 발광 소자 유닛.

### 청구항 5

제 1항 또는 제 2항에 있어서,

상기 브릿지 회로의 한 번에는 상기 제2 발광 소자가 한 개로 구성되거나 복수 개의 제2 발광 소자가 직렬로

연결되는 것을 특징으로 하는 발광 소자 유닛.

### 청구항 6

제 1항 또는 제 2항에 있어서,

상기 제1 및 제2 발광 소자는 교류 전압의 절반의 주기 동안, Vf가 제1 및 제2 발광 소자의 순방향 전압을, Vp

가 공급 전압의 최대값을 나타낼 때 ( $V_p/V_f$ ) 보다 큰 개수 만큼 발광되는 것을 특징으로 하는 발광 소자 유닛.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <10> 본 발명은 교류 전압용 발광 소자 유닛에 관한 것으로, 더욱 상세하게는 브릿지 회로를 이용하여 소형화되고, 발광 효율을 향상시킨 발광 소자 유닛에 관한 것이다.

- <11> 발광 다이오드와 같은 발광 소자는 LCD 백라이트 유닛, 카레라폰 플래시, 전광판, 조명 등 그 적용 영역이 점점 확대되고 있다. 발광 다이오드는 반도체의 p-n 접합 구조를 이용하여 전자와 정공을 만들어내고, 이들의 재결합에 의해 빛을 발산한다. 발광 다이오드는 기존의 전구 또는 형광등에 비해 소모 전력이 작고 수명이 길어 일반 조명으로의 적용을 위한 연구가 활발히 진행되고 있다.

- <12> 일반적으로, 발광 다이오드를 조명용으로 사용하기 위해서는 패키징 공정을 통해 단일의 발광 소자 칩을 형성하고, 패키징된 각각의 발광 다이오드를 직렬 또는 병렬 연결하고, 외부에서 보호 회로 및 교류/직류 변환기 등을 설치하여 램프의 형태로 제작한다. 하지만, 이와 같이 복수 개의 패키징된 발광 소자를 이용하여 조명을 제작하면 발광 소자 자체의 크기도 클 뿐만 아니라 발광 소자와 발광 소자 사이의 공간도 크기 때문에 조명 광원 전체가 매우 커지는 문제점이 있다.

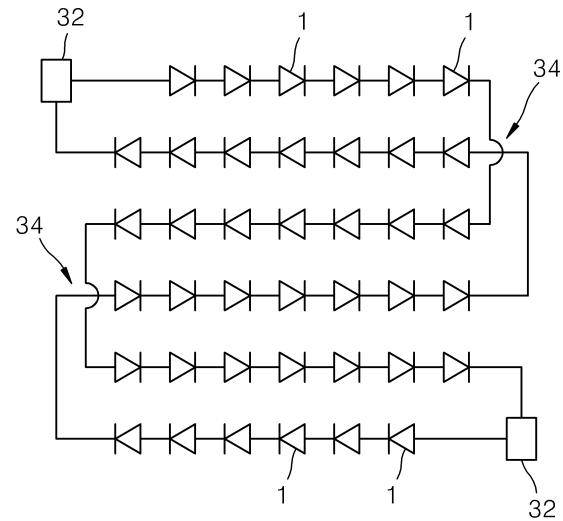

- <13> 한편, 발광 다이오드를 조명용으로 사용하는 경우 전원으로 교류를 사용하게 되며, 발광 효율을 높일 수 있도록 고안된 발광 장치가 개발된다. 도 1은 국제공개 WO 2004/023568호에 개시된 발광 장치를 나타낸 것이다. 이 발광 장치는 전원으로 사용되는 교류 전압을 교대로 조명에 사용하기 위해 서로 반대의 극성으로 병렬 접속된 제1 및 제2 발광 다이오드 어레이(1)(2)를 포함한다. 도면 부호 32는 전극을 나타내며, 34는 제1 및 제2 발광 다이오드 어레이(1)(2)를 지그재그 형상으로 배열할 때 생기는 교차 부분을 나타낸다.

- <14> 교류 전압이 인가되면, 반주기 동안에는 예를 들어 제1 발광 다이오드 어레이(1)가 발광되고, 나머지 반주기 동안에는 제2 발광 다이오드 어레이(2)가 발광된다. 따라서, 교류 전압이 인가되는 동안 항상 전체 발광 다이오드 개수의 절반만이 발광되고, 전체 발광 다이오드의 개수가 많아지는 단점이 있다.

- <15> 이러한 문제를 해결하기 위해 정류 소자를 구비하여 발광 효율을 높이면서 발광 다이오드의 개수도 늘릴 필요가 없도록 하는 방식이 제안되었다. 하지만, 정류 소자는 부피가 크고, 별도로 제작되어야 하므로 공정이 복잡해지고, 제조 비용이 상승되는 다른 문제가 발생된다. 따라서, 소형의 조명용 광원에 적용하기 위한 발광 다이오드 장치에 별도의 정류 소자를 채용하는 것은 적합하지 않다.

### 발명이 이루고자 하는 기술적 과제

- <16> 본 발명은 상기한 문제점을 해결하기 위해 창안된 것으로, 발광 소자들을 브릿지 회로 및 직렬로 연결하여 발광 효율을 높이고 공정을 단순화하여 제조 비용을 저감시킨 교류 전압용 발광 소자 유닛을 제공하는 것을 목적으로 한다.

### 발명의 구성 및 작용

- <17> 상기한 목적을 달성하기 위해, 본 발명에 따른 교류 전압용 발광 소자 유닛은, 전기 배선이 형성되어 있는 서브 마운트; 복수 개의 제1 발광 소자가 상기 서브 마운트 상에 직렬 연결된 제1 발광 소자 어레이; 복수 개의 제2 발광 소자가 상기 서브 마운트 상에 브릿지 회로로 연결된 것으로, 상기 제1 발광 소자 어레이에 연결된 제2 발광 소자 어레이;를 포함하는 것을 특징으로 한다.

- <18> 상기 제1 및 제2 발광 소자는 발광 칩으로 이루어진다.

- <19> 상기 제2 발광 소자의 브레이크 다운 전압(V<sub>b</sub>)은 다음의 조건식을 만족한다.

- <20> <조건식>

$$V_b > \frac{(V_p - nV_f)}{n}$$

- <21> 여기서, V<sub>f</sub>는 제2 발광 소자의 순방향 전압을, V<sub>p</sub>는 공급 전압의 최대값을, n은 브릿지 회로의 한 변에 배열되는 제2 발광 소자의 개수를 나타낸다.

- <23> 상기 제1 및 제2 발광 소자는 상기 서브 마운트에 플립칩으로 실장될 수 있다.

- <24> 상기 제1 및 제2 발광 소자는 교류 전압의 절반의 주기 동안, V<sub>f</sub>가 제1 및 제2 발광 소자의 순방향 전압을, V<sub>p</sub>가 공급 전압의 최대값을 나타낼 때 (V<sub>p</sub>/V<sub>f</sub>) 보다 큰 개수 만큼 발광될 수 있다.

- <25> 이하, 본 발명에 따른 교류 전압용 발광 소자 유닛에 대해 첨부된 도면을 참조하여 상세히 설명한다.

- <26> 본 발명에 따른 발광 소자 유닛은 교류 전압용에 적용하기 위한 것으로, 발광 소자를 브릿지 회로 형태로 연결하여 정류 작용을 하도록 함으로써 발광 효율을 높인다.

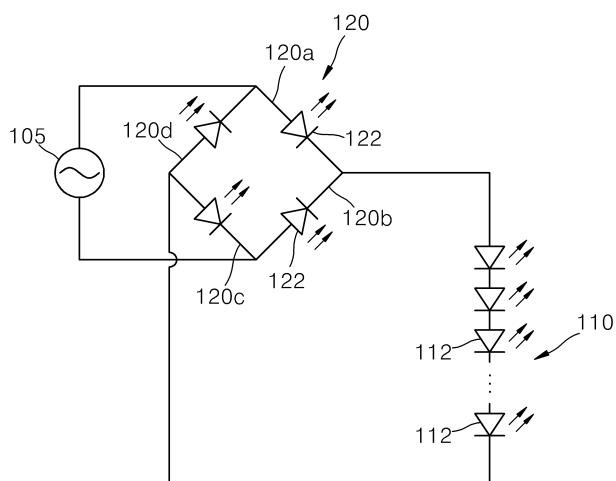

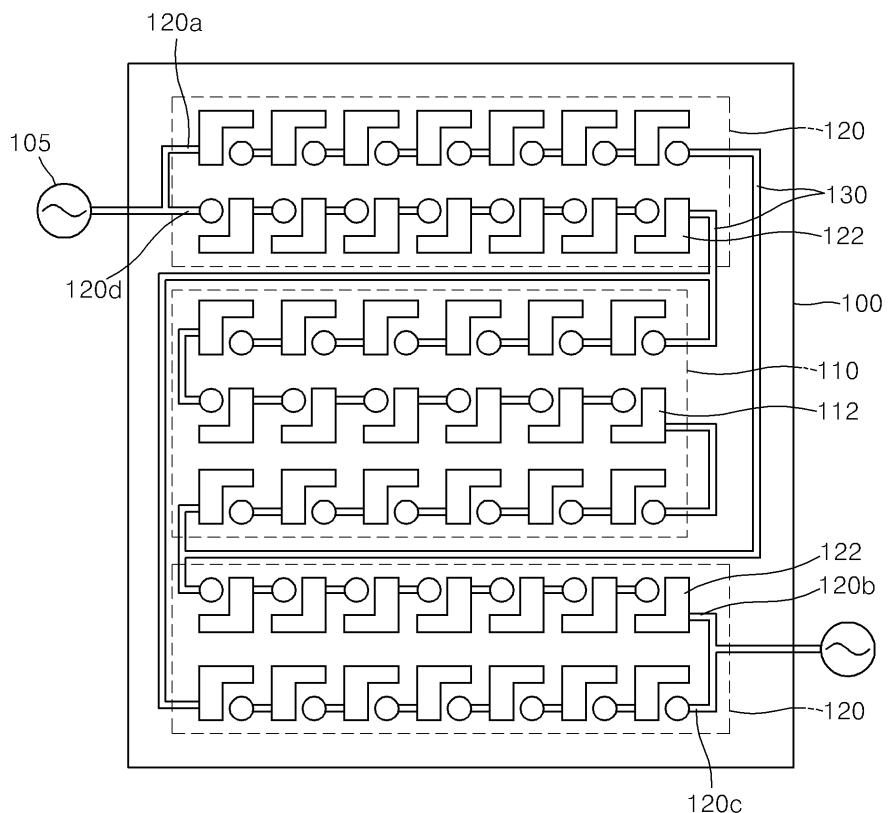

- <27> 도 2를 참조하면, 본 발명에 따른 발광 소자 유닛은 복수 개의 제1 발광 소자(112)가 직렬로 연결된 제1 발광 소자 어레이(110)와, 복수 개의 제2 발광 소자(122)가 브릿지 회로 형태로 연결된 제2 발광 소자 어레이(120)를 포함한다. 상기 제1 발광 소자 어레이(110)와 제2 발광 소자 어레이(120)가 직렬로 연결되고, 전원(105)으로부터 교류 전압이 공급된다.

- <28> 상기 제2 발광 소자들(122)은 브릿지 회로 형태로 결합되며, 제1 내지 제4 변(120a)(120b)(120c)(120d)으로 구성된 브릿지 회로의 한 변에 하나의 제2 발광 소자가 배치되거나, 복수 개의 제2 발광 소자가 직렬로 연결될 수 있다. 상기 제2 발광 소자 어레이(120)는 발광 소자들을 브릿지 회로 형태로 배열되어 정류 작용을 하도록 되어 있다.

- <29> 상기 제1 및 제2 발광 소자는 발광 칩으로 구성되거나 패키징된 발광 소자로 구성될 수 있다. 즉, 본 발명에 따른 발광 소자 유닛은 패키징된 발광 소자를 이용하여 PCB(Printed Circuit Board) 레벨로 제작되거나 발광 칩을 이용하여 칩 레벨로 제작될 수 있다. 칩 레벨로 제작되는 경우에는 발광 소자를 패키징하는 공정이 필요 없기 때문에 제작 비용이 절감되고 PCB 레벨에 비해 소형으로 제작할 수 있는 이점이 있다.

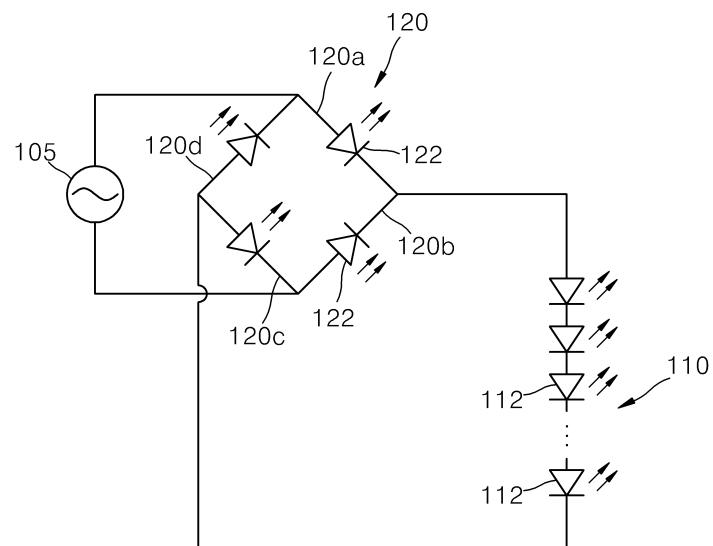

- <30> 도 3은 본 발명에 따른 발광 소자 유닛의 일 예를 도시한 것으로,  $7 \times 7$  배열 구조를 갖는다. 서브 마운트(100)에 전기 배선(130)이 형성되어 있고, 상기 전기 배선(130)에 따라 제1 및 제2 발광 소자들(112)(122)이 실장된다. 도면에서는 편의상 발광 소자들의 전극 구조만을 도시하였다.

- <31> 제1 발광 소자들(112)이 직렬로 연결되고, 제2 발광 소자들(122)이 브릿지 형태로 배열되어 있다. 상기 제2 발광 소자들(122)은 브릿지 회로의 한 변에 7개씩 직렬로 연결되어 있다. 제2 발광 소자를 7개로 구성하는 것은 일 예에 불과하며, 제2 발광 소자들 중의 한 소자에 걸리는 역방향 전압이 브레이크 다운 전압(V<sub>b</sub>) 보다 작은 한도 내에서 제2 발광 소자의 개수를 다양하게 구성할 수 있다.

- <32> 상기 제2 발광 소자(122)는 브레이크 다운 전압(V<sub>b</sub>)이 다음의 수학식을 만족하도록 구성되는 것이 좋다.

- $$<33> V_b > \frac{(V_p - nV_f)}{n}$$

- <34> 여기서, V<sub>f</sub>는 제2 발광 소자의 순방향 전압을, V<sub>p</sub>는 공급 전압의 최대값을, n은 브릿지 회로의 한 변에 배열되는 제2 발광 소자의 개수를 나타낸다. 다시 말하면, 제2 발광 소자(122)의 브레이크 다운 전압(V<sub>b</sub>)은 역방향 전압보다 커야 한다. 예를 들어, V<sub>p</sub>=110(V)이고, n=7이고, V<sub>f</sub>=3.5(V) 일 때, V<sub>b</sub>는 12(V)보다 큰 값을 가지는 것이 좋다. 제2 발광 소자의 역방향 전압이 상기 수학식 1을 만족시키는 범위 내에서 제2 발광 소자의 개수(n)를 정할 수 있다.

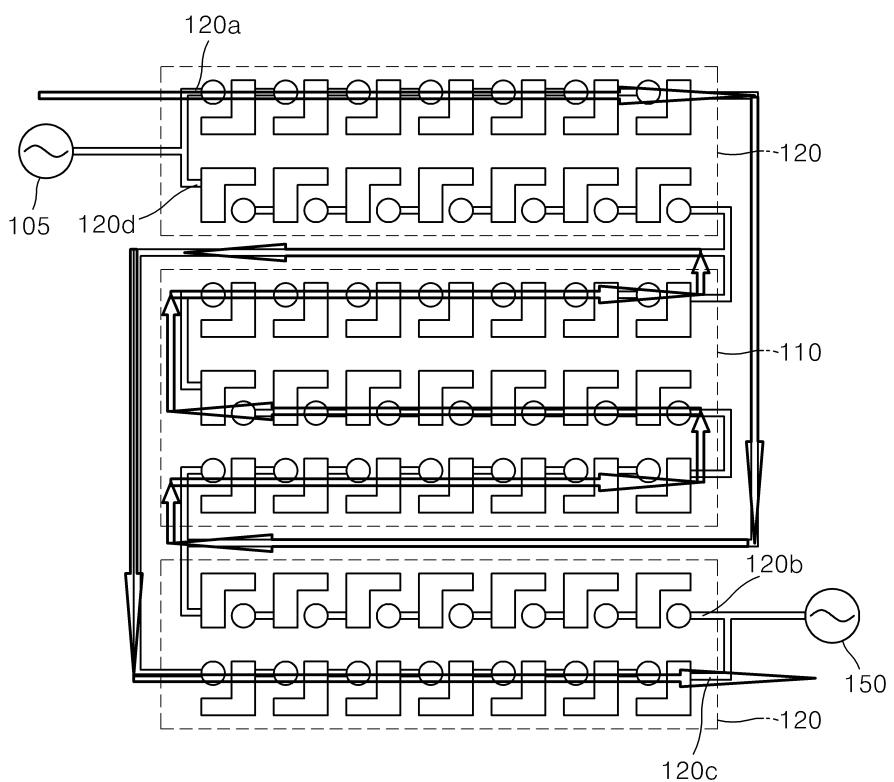

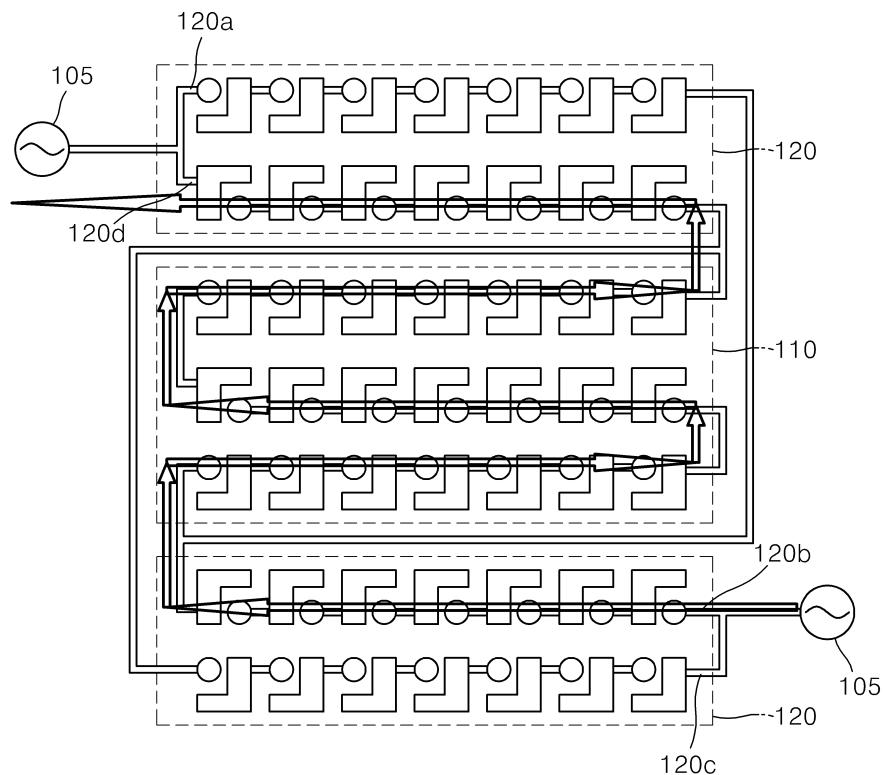

- <35> 다음, 도 4a 및 도 4b를 참조하여 발광 소자 유닛의 발광 동작에 대해 설명하기로 한다.

- <36> 도 4a는 전원(105)으로부터의 교류 전압의 순방향의 제1 반주기 동안의 전류의 흐름을, 도 4b는 역방향의 제2 반주기 동안의 전류의 흐름을 나타낸 것이다. 제1 반주기 동안에는 제1변(120a)의 제2 발광소자들, 제1 발광소자들(112), 제3변(120c)의 제2 발광소자들을 통해 전류가 흐른다. 한편, 제2 반주기 동안에는 제2변(120c)의 제2 발광소자들, 제1 발광소자들(112), 제4변(120d)의 제2 발광소자들을 통해 전류가 흐른다. 결과적으로, 제2 발광소자들은 전체 개수의 절반씩 교대로 발광되는 한편, 제1 발광소자들은 연속적으로 발광된다. 제2 발광 소자들은 정류 작용과 발광 작용을 같이 하게 된다. 따라서, 기존에 병렬 구조의 발광 소자에 비해 발광 효율이 향상된다. 본 발명의 발광 소자 유닛에서 교류 전압의 절반의 주기 동안 발광이 되는 제1 및 제2 발광 소자의 개수는 (V<sub>p</sub>/V<sub>f</sub>) 보다 크다.

- <37> 한편, 상기 제1 및 제2 발광 소자(112)(122)는 상기 서브 마운트에 플립칩으로 실장될 수 있다. 발광 소자를 와이어 없이 플립칩으로 실장함으로써 제조 공정을 단순화함과 아울러 발광 소자와 발광 소자 사이의 간격을 줄일 수 있어 소형화에 도움이 된다.

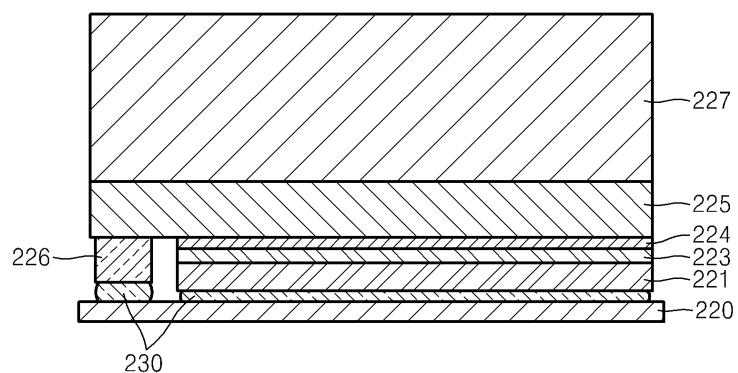

- <38> 도 5는 발광 소자의 일예를 도시한 것으로, 사파이어 기판(227) 상에 전자가 도핑된 n형 클래드층(225), 활성층(224), 정공이 도핑된 p형 클래드층(223) 및 p형 전극(221)이 차례대로 적층되어 있다. 그리고, 상기 n형 클래드층(225)의 일측 하부면에 n형 전극(226)이 구비된다. 상기 n형 클래드층(225)이 단차지게 형성되고, 그 단차

진 부분에 n형 전극(226)이 구비된다.

<39> 상기 제p형 전극 및 n형 전극(221)(226)에 각각 플러스와 마이너스 전압을 순방향으로 가하면 상기 p형 및 n형 클래드층(223)(225)에서 상기 활성층(224)으로 전자와 정공이 이동되고, 이 전자와 정공의 결합을 통하여 에너지 밴드 캡에 해당하는 에너지를 갖는 광자가 발생되어 발광된다. 상기와 같이 구성된 발광 소자를 서브 마운트(220)의 배선에 따라 배치하여 플립칩으로 실장함으로써 간단하게 발광 소자 유닛을 제작할 수 있다. 도면 부호 230은 본딩 메탈을 나타낸다. 이 밖에 p형 전극 및 n형 전극이 서로 반대 방향의 면에 배치되는 구조의 발광 소자를 이용하여 발광 소자 유닛을 제작하는 것도 가능하다.

<40> 본 발명에서는 발광 소자를 브릿지 형태로 배열함으로써 정류 작용과 함께 발광 작용을 하도록 함으로써 발광 소자 유닛의 발광 효율을 높임과 아울러 소형화에 기여할 수 있다.

### 발명의 효과

<41> 상술한 바와 같이 본 발명에 따른 발광 소자 유닛은, 발광 소자들을 브릿지 회로 및 직렬로 연결하여 별도의 정류 소자 없이 브릿지 회로를 통해 정류 동작을 하도록 함으로써 구조를 단순화 및 소형화할 수 있다. 또한, 브릿지 회로를 통한 정류 동작에 의해 일반적인 직렬 및 병렬 배열에 비해 발광 효율을 향상시킬 수 있다. 또한, 정류 소자를 별도로 제작할 필요 없이 발광 소자들의 배열만으로 정류 작용을 구현함으로써 비용이 절감되는 효과가 있다. 이와 같이 발광 소자 유닛의 소형화 및 고휘도화를 통해 교류 전압의 조명 광원에 유용하게 적용될 수 있다.

<42> 상기한 실시예 들은 예시적인 것에 불과한 것으로, 당해 기술분야의 통상을 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시예가 가능하다. 따라서, 본 발명의 진정한 기술적 보호범위는 하기의 특허청구범위에 기재된 발명의 기술적 사상에 의해 정해져야만 할 것이다.

### 도면의 간단한 설명

<1> 도 1은 국제공개 WO 2004/023568호에 개시된 발광 장치를 나타낸 것이다.

<2> 도 2는 본 발명의 바람직한 실시예에 따른 교류 전압용 발광 소자 유닛의 등가 회로도를 도시한 것이다.

<3> 도 3은 본 발명의 바람직한 실시예에 따른 교류 전압용 발광 소자 유닛의 일 예를 도시한 것이다.

<4> 도 4a 및 도 4b는 도 3에 도시된 발광 소자 유닛의 발광 동작을 설명하기 위한 도면이다.

<5> 도 5는 본 발명에 따른 교류 전압용 발광 소자 유닛에 채용되는 발광 칩의 일 예를 도시한 것이다.

<6> <도면 중 주요 부분에 대한 설명>

<7> 100...서브 마운트, 105...전원

<8> 110...제1 발광 소자 어레이, 112, 122...발광 소자,

<9> 120...제2 발광 소자 어레이

도면

도면1

도면2

도면3

도면4a

도면4b

도면5