(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5764370号

(P5764370)

(45) 発行日 平成27年8月19日(2015.8.19)

(24) 登録日 平成27年6月19日(2015.6.19)

|                |           |

|----------------|-----------|

| (51) Int.Cl.   | F 1       |

| G 11 C 11/405  | (2006.01) |

| HO 1 L 29/786  | (2006.01) |

| HO 1 L 21/8242 | (2006.01) |

| HO 1 L 27/108  | (2006.01) |

| HO 1 L 27/10   | (2006.01) |

| G 11 C 11/34   | 3 5 2 B   |

| HO 1 L 29/78   | 6 1 8 B   |

| HO 1 L 29/78   | 6 1 3 B   |

| HO 1 L 27/10   | 3 2 1     |

| HO 1 L 27/10   | 4 8 1     |

請求項の数 4 (全 43 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2011-88799 (P2011-88799)    |

| (22) 出願日     | 平成23年4月13日(2011.4.13)         |

| (65) 公開番号    | 特開2011-238334 (P2011-238334A) |

| (43) 公開日     | 平成23年11月24日(2011.11.24)       |

| 審査請求日        | 平成26年4月4日(2014.4.4)           |

| (31) 優先権主張番号 | 特願2010-95196 (P2010-95196)    |

| (32) 優先日     | 平成22年4月16日(2010.4.16)         |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 長塚 修平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 加藤 清<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 松崎 隆徳<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 井上 広樹<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、遅延回路と、を有し、

前記第1のトランジスタのゲートは、前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第1のトランジスタのゲートは、前記容量素子の一方の電極と電気的に接続され、前記第1のトランジスタのソースまたはドレインの一方は、前記第2のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第1の配線と電気的に接続され、

前記容量素子の他方の電極は、前記第1の配線と電気的に接続され、

前記遅延回路は、前記第2の配線を介して前記第3のトランジスタのソースまたはドレインの他方と電気的に接続され、

前記第3のトランジスタは、i型化または実質的にi型化された酸化物半導体を含む第3のチャネル形成領域を有し、

85 の温度環境下であって、ソース-ドレイン電圧が3.1Vの条件において、前記第3のトランジスタのチャネル幅あたりのオフ電流は、100zA/μm以下であることを特徴とする半導体装置。

## 【請求項 2】

10

20

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、遅延回路と、を有し、

前記第1のトランジスタのゲートは、前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第1のトランジスタのゲートは、前記容量素子の一方の電極と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの一方は、前記第2のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第1の配線と電気的に接続され、

前記容量素子の他方の電極は、前記第1の配線と電気的に接続され、

前記遅延回路は、前記第2の配線を介して前記第3のトランジスタのソースまたはドレインの他方と電気的に接続され、

前記第3のトランジスタは、真性化または実質的に真性化された酸化物半導体を含む第3のチャネル形成領域を有し、

85 の温度環境下であって、ソース - ドレイン電圧が 3.1 V の条件において、前記第3のトランジスタのチャネル幅あたりのオフ電流は、100 zA / μm 以下であることを特徴とする半導体装置。

【請求項3】

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、容量素子と、第1の配線と、第2の配線と、遅延回路と、を有し、

前記第1のトランジスタのゲートは、前記第3のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第1のトランジスタのゲートは、前記容量素子の一方の電極と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの一方は、前記第2のトランジスタのソースまたはドレインの一方と電気的に接続され、

前記第1のトランジスタのソースまたはドレインの他方は、前記第1の配線と電気的に接続され、

前記容量素子の他方の電極は、前記第1の配線と電気的に接続され、

前記遅延回路は、前記第2の配線を介して前記第3のトランジスタのソースまたはドレインの他方と電気的に接続され、

前記第3のトランジスタは、高純度化された酸化物半導体を含む第3のチャネル形成領域を有し、

85 の温度環境下であって、ソース - ドレイン電圧が 3.1 V の条件において、前記第3のトランジスタのチャネル幅あたりのオフ電流は、100 zA / μm 以下であることを特徴とする半導体装置。

【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第1のトランジスタは、シリコンを含む第1のチャネル形成領域を有し、

前記第2のトランジスタは、シリコンを含む第2のチャネル形成領域を有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

開示する発明は、半導体素子を利用した半導体装置およびその駆動方法に関するものである。

【背景技術】

【0002】

半導体素子を利用した記憶装置は、電力の供給がなくなると記憶内容が失われる揮発性のものと、電力の供給がなくなっても記憶内容は保持される不揮発性のものとに大別される

10

20

30

40

50

。

### 【0003】

揮発性記憶装置の代表的な例としては、DRAM (Dynamic Random Access Memory) がある。DRAMは、記憶素子を構成するトランジスタを選択してキャパシタに電荷を蓄積することで、情報を記憶する。

### 【0004】

上述の原理から、DRAMでは、情報を読み出すとキャパシタの電荷は失われるため、情報の読み出しの度に、再度の書き込み動作が必要となる。また、記憶素子を構成するトランジスタにおいてはオフ状態でのソースとドレイン間のリーク電流（オフ電流）等によって、トランジスタが選択されていない状況でも電荷が流出、または流入するため、データの保持期間が短い。このため、所定の周期で再度の書き込み動作（リフレッシュ動作）が必要であり、消費電力を十分に低減することは困難である。また、電力の供給がなくなると記憶内容が失われるため、長期間の記憶の保持には、磁性材料や光学材料を利用した別の記憶装置が必要となる。

10

### 【0005】

揮発性記憶装置の別の例としてはSRAM (Static Random Access Memory) がある。SRAMは、フリップフロップなどの回路を用いて記憶内容を保持するため、リフレッシュ動作が不要であり、この点においてはDRAMより有利である。しかし、フリップフロップなどの回路を用いているため、記憶容量あたりの単価が高くなるという問題がある。また、電力の供給がなくなると記憶内容が失われるという点については、DRAMと変わることろはない。

20

### 【0006】

不揮発性記憶装置の代表例としては、フラッシュメモリがある。フラッシュメモリは、トランジスタのゲート電極とチャネル形成領域との間にフローティングゲートを有し、当該フローティングゲートに電荷を保持させることで記憶を行うため、データの保持期間は極めて長く（半永久的）、揮発性記憶装置で必要なリフレッシュ動作が不要であるという利点を有している（例えば、特許文献1参照）。

### 【0007】

しかし、書き込みの際に生じるトンネル電流によって記憶素子を構成するゲート絶縁層が劣化するため、所定回数の書き込みによって記憶素子が機能しなくなるという問題が生じる。この問題の影響を緩和するために、例えば、各記憶素子の書き込み回数を均一化する手法が採られるが、これを実現するためには、複雑な周辺回路が必要になってしまう。そして、このような手法を採用しても、根本的な寿命の問題が解消するわけではない。つまり、フラッシュメモリは、情報の書き換え頻度が高い用途には不向きである。

30

### 【0008】

また、フローティングゲートに電荷を注入させるため、または、その電荷を除去するためには、高い電圧が必要であり、また、そのための回路も必要である。さらに、電荷の注入、または除去のためには比較的長い時間を要し、書き込み、消去の高速化が容易ではないという問題もある。

### 【先行技術文献】

40

### 【特許文献】

### 【0009】

### 【特許文献1】特開昭57-105889号公報

### 【発明の概要】

### 【発明が解決しようとする課題】

### 【0010】

上述の問題に鑑み、開示する発明の一態様では、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的のとする。

### 【課題を解決するための手段】

50

**【0011】**

開示する発明では、トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。

**【0012】**

また、開示する発明では、例えば、ワイドギャップ半導体を用いて構成されたメモリセルを含む半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。

**【0013】**

より具体的には、例えば次のような構成を採用することができる。

10

**【0014】**

本発明の一態様は、書き込みワード線と、読み出しワード線と、ビット線と、ソース線と、信号線と、複数のメモリセルでなるメモリセルアレイと、信号線と電気的に接続された遅延回路を有する第1の駆動回路と、第2の駆動回路と、を有し、メモリセルの一は、第1のゲート電極、第1のソース電極、第1のドレイン電極、及び第1のチャネル形成領域を含む第1のトランジスタと、第2のゲート電極、第2のソース電極、第2のドレイン電極、及び第2のチャネル形成領域を含む第2のトランジスタと、第3のゲート電極、第3のソース電極、第3のドレイン電極、及び第3のチャネル形成領域を含む第3のトランジスタと、を有し、第1のチャネル形成領域は、第2のチャネル形成領域とは異なる半導体材料を含んで構成され、第1のゲート電極と、第2のドレイン電極とは電気的に接続されて電荷が保持されるノードを構成し、第1のドレイン電極と、第3のソース電極とは電気的に接続され、ソース線は、第1のソース電極と電気的に接続され、第1の駆動回路は、ビット線を介して、第3のドレイン電極と電気的に接続され、また、遅延回路および信号線を介して、第2のソース電極と電気的に接続され、第2の駆動回路は、読み出しワード線を介して、第2のゲート電極と電気的に接続される半導体装置である。

20

**【0015】**

また、本発明の別の一態様は、電源電位より高い電位が少なくとも与えられる書き込みワード線と、読み出しワード線と、ビット線と、ソース線と、信号線と、複数のメモリセルでなるメモリセルアレイと、信号線と電気的に接続された遅延回路を有する第1の駆動回路と、第2の駆動回路と、電位変換回路と、を有し、メモリセルの一は、第1のゲート電極、第1のソース電極、第1のドレイン電極、及び第1のチャネル形成領域を含む第1のトランジスタと、第2のゲート電極、第2のソース電極、第2のドレイン電極、及び第2のチャネル形成領域を含む第2のトランジスタと、第3のゲート電極、第3のソース電極、第3のドレイン電極、及び第3のチャネル形成領域を含む第3のトランジスタと、を有し、第1のチャネル形成領域は、第2のチャネル形成領域とは異なる半導体材料を含んで構成され、第1のゲート電極と、第2のドレイン電極とは電気的に接続されて電荷が保持されるノードを構成し、第1のドレイン電極と、第3のソース電極とは電気的に接続され、ソース線は、第1のソース電極と電気的に接続され、第1の駆動回路は、ビット線を介して、第3のドレイン電極と電気的に接続され、また、遅延回路および信号線を介して、第2のソース電極と電気的に接続され、第2の駆動回路は、読み出しワード線を介して第3のゲート電極と電気的に接続され、また、書き込みワード線を介して、第2のゲート電極と電気的に接続され、電位変換回路は、第2の駆動回路に電源電位より高い電位を出力する半導体装置である。

30

**【0016】**

または、上記の半導体装置において、一方の電極は電荷が保持されるノードと電気的に接続され、他方の電極はソース線と電気的に接続される、容量素子を有する構成としてもよい。

40

**【0017】**

50

または、上記の半導体装置において、第2の駆動回路は、電位変換回路および書き込みワード線と電気的に接続された昇圧用レベルシフタを有する構成としてもよい。

【0018】

また、上記の半導体装置において、ビット線とソース線との間に、メモリセルの一を含む複数のメモリセルが並列に接続される構成としてもよい。

【0019】

または、上記の半導体装置において、第2のトランジスタの第2のチャネル形成領域は、酸化物半導体を含む構成としてもよい。また、第3のチャネル形成領域は、第1のチャネル形成領域と同じ半導体材料を含んで構成されてもよい。

【0020】

なお、上記において、酸化物半導体を用いてトランジスタを構成することがあるが、開示する発明はこれに限定されない。酸化物半導体と同等のオフ電流特性が実現できる材料、例えば、炭化シリコンをはじめとするワイドギャップ材料（より具体的には、例えば、エネルギーギャップ  $E_g$  が 3 eV より大きい半導体材料）などを適用しても良い。

【0021】

なお、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。

【0022】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

【0023】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0024】

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

【0025】

例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

【発明の効果】

【0026】

酸化物半導体を用いたトランジスタはオフ電流が極めて小さいため、これを用いることにより極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合（ただし、電位は固定されていることが望ましい）であっても、長期にわたって記憶内容を保持することが可能である。

【0027】

また、開示する発明に係る半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁層の劣化といった問題が生じない。すなわち、開示する発明に係る半導体装置

10

20

30

40

50

では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。また、情報を消去するための動作が不要であるというメリットもある。

【0028】

また、酸化物半導体以外の材料を用いたトランジスタは、十分な高速動作が可能であるため、これを、酸化物半導体を用いたトランジスタと組み合わせて用いることにより、半導体装置の動作（例えば、情報の読み出し動作）の高速性を十分に確保することができる。また、酸化物半導体以外の材料を用いたトランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することが可能である。

10

【0029】

このように、酸化物半導体以外の材料を用いたトランジスタ（換言すると、十分な高速動作が可能なトランジスタ）と、酸化物半導体を用いたトランジスタ（より広義には、十分にオフ電流が小さいトランジスタ）とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。

【図面の簡単な説明】

【0030】

【図1】半導体装置の回路図。

【図2】半導体装置の回路図。

【図3】半導体装置の回路図。

20

【図4】半導体装置のタイミングチャート。

【図5】半導体装置の回路図。

【図6】半導体装置の回路図。

【図7】半導体装置の回路図。

【図8】半導体装置の回路図。

【図9】半導体装置の回路図。

【図10】半導体装置の回路図。

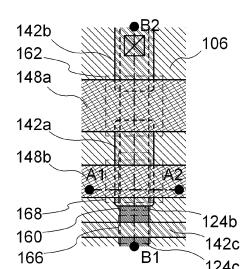

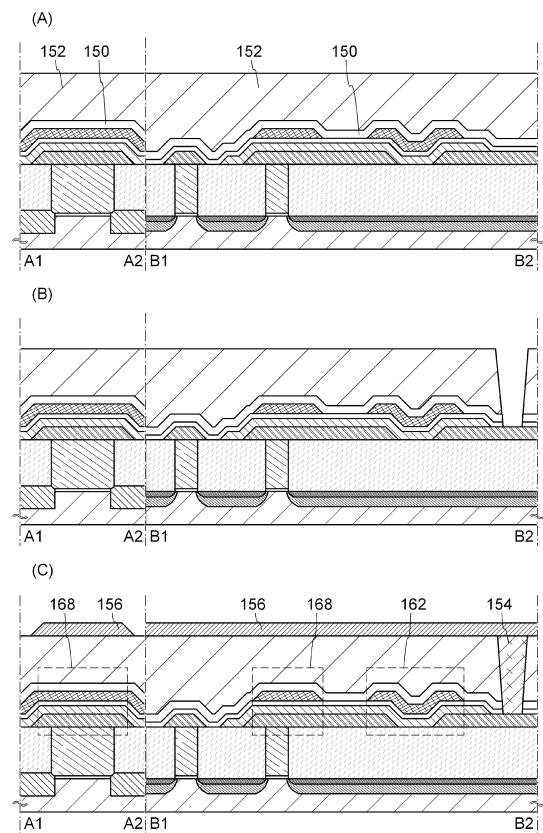

【図11】半導体装置の断面図および平面図。

【図12】半導体装置の作製工程に係る断面図。

【図13】半導体装置の作製工程に係る断面図。

30

【図14】半導体装置の作製工程に係る断面図。

【図15】半導体装置の作製工程に係る断面図。

【図16】半導体装置の平面図。

【図17】半導体装置を用いた電子機器を説明するための図。

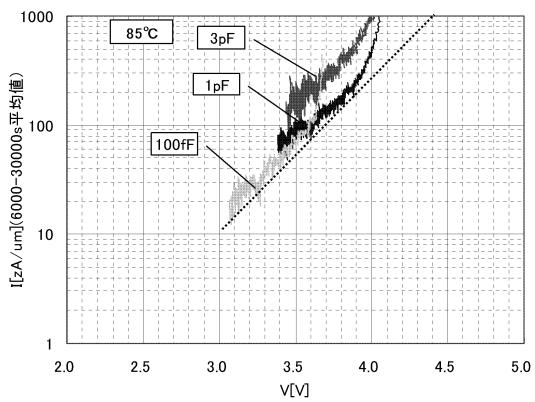

【図18】酸化物半導体を用いたトランジスタの特性を示す図。

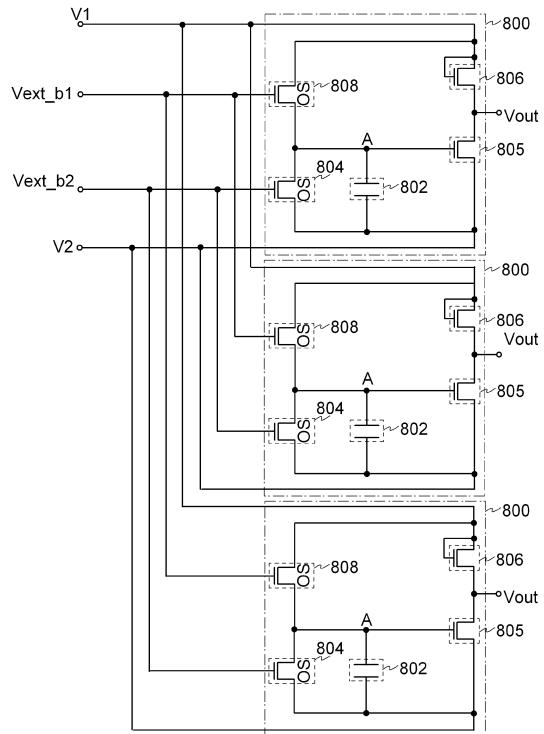

【図19】酸化物半導体を用いたトランジスタの特性評価用回路図。

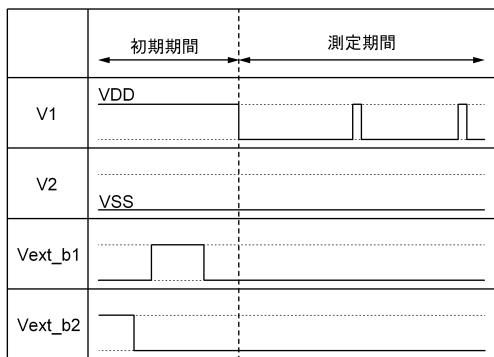

【図20】酸化物半導体を用いたトランジスタの特性評価用タイミングチャート。

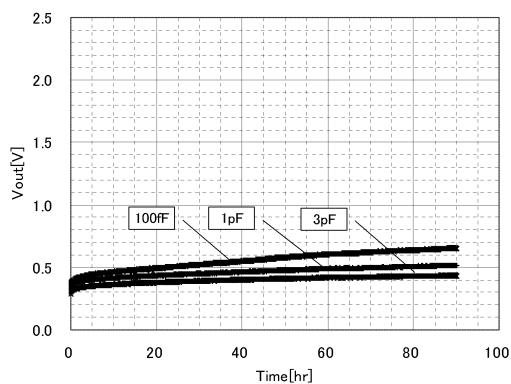

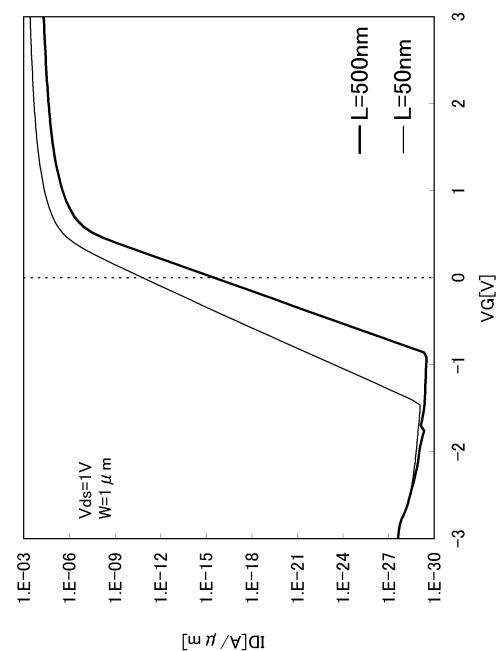

【図21】酸化物半導体を用いたトランジスタの特性を示す図。

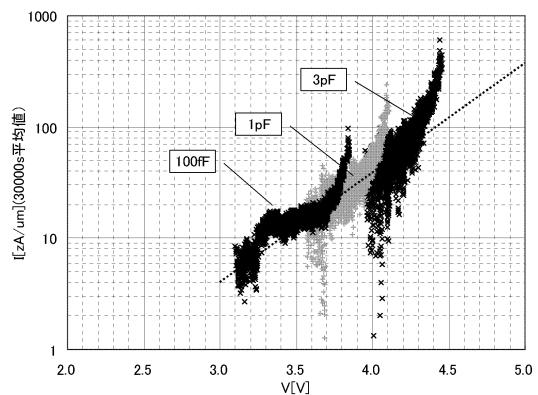

【図22】酸化物半導体を用いたトランジスタの特性を示す図。

【図23】酸化物半導体を用いたトランジスタの特性を示す図。

40

【図24】計算に用いたトランジスタの構造を示す断面図。

【図25】計算により求められたトランジスタの特性を示す図。

【発明を実施するための形態】

【0031】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0032】

なお、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実

50

際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

【0033】

なお、本明細書等における「第1」、「第2」、「第3」などの序数は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0034】

(実施の形態1)

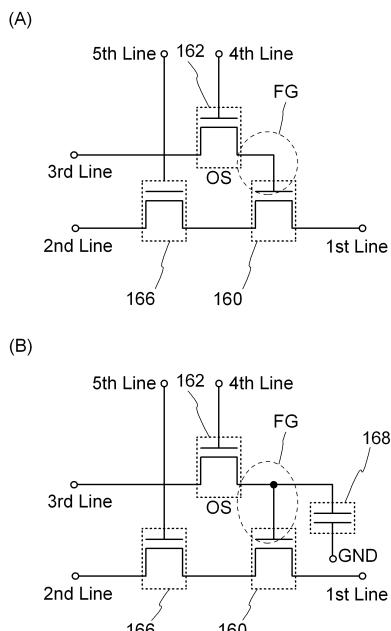

本実施の形態では、開示する発明の一態様に係る半導体装置の回路構成および動作について、図1乃至図9を参照して説明する。なお、回路図においては、酸化物半導体を用いたトランジスタであることを示すために、OSの符号を併せて付す場合がある。

10

【0035】

基本回路

はじめに、基本的な回路構成およびその動作について、図1を参照して説明する。図1(A)に示す半導体装置において、第1の配線(1st Line)とトランジスタ160のソース電極(またはドレイン電極)とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ166のドレイン電極(またはソース電極)とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ162のソース電極(またはドレイン電極)とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ162のゲート電極とは、電気的に接続されている。そして、トランジスタ160のゲート電極と、トランジスタ162のドレイン電極(またはソース電極)とは、電気的に接続され、トランジスタ160のドレイン電極(またはソース電極)と、トランジスタ166のソース電極(またはドレイン電極)とは、電気的に接続されている。また、第5の配線(5th Line)と、トランジスタ166のゲート電極とは電気的に接続されている。

20

【0036】

ここで、トランジスタ162には、例えば、酸化物半導体を用いたトランジスタが適用される。酸化物半導体を用いたトランジスタは、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ162をオフ状態とすることで、トランジスタ160のゲート電極の電位を極めて長時間にわたって保持することができる。

30

【0037】

なお、トランジスタ160、トランジスタ166については特に限定されない。情報の読み出し速度を向上させるという観点からは、例えば、単結晶シリコンを用いたトランジスタなど、スイッチング速度の高いトランジスタを適用するのが好適である。

【0038】

また、図1(B)に示すように、トランジスタ160のゲート電極およびトランジスタ162のドレイン電極(またはソース電極)と、電極の一方が電気的に接続されるように、容量素子168を設けてもよい。容量素子168の電極の他方は、所定の電位が与えられている。所定の電位とは、例えばGNDなどである。また、容量素子168の電極の他方は、第1の配線と電気的に接続されていてもよい。そして、容量素子168を設けることにより、トランジスタ160のゲート電極に多くの電荷を保持することができ、情報の保持特性を向上させることができる。

40

【0039】

図1(A)に示す半導体装置では、トランジスタ160のゲート電極の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

【0040】

はじめに、情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位が、トランジスタ160のゲート電極に与えられる。すなわち、トランジスタ160のゲート電極には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位を与える電荷(以下、低電位を与える電荷を電荷Q<sub>L</sub>、高電位

50

を与える電荷を電荷  $Q_H$  という) のいずれかが与えられるものとする。なお、異なる三つまたはそれ以上の電位を与える電荷を適用して、記憶容量を向上させても良い。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極に与えられた電荷が保持される(保持)。

【0041】

トランジスタ162のオフ電流は極めて小さいから、トランジスタ160のゲート電極の電荷は長時間にわたって保持される。

【0042】

次に、情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与え、トランジスタ166をオン状態とすると、トランジスタ160のゲート電極に保持された電荷量に応じて、第2の配線は異なる電位をとる。これは、書き込みにおいて  $Q_H$  が与えられた場合には、トランジスタ160は「オン状態」となり、 $Q_L$  が与えられた場合には、トランジスタ160は「オフ状態」となるからである。よって、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

10

【0043】

なお、メモリセルをアレイ状に配置して用いる場合には、所望のメモリセルの情報のみを読み出せることが必要になる。そこで、上述のように、情報に応じた電荷がゲート電極に保持されたトランジスタ160と第2の配線との間に、第5の配線がゲート電極に接続されたトランジスタ166を設けることが好ましい。このようにして、読み出し対象のメモリセルの第5の配線に適切な電位を与えてトランジスタ166をオン状態にし、読み出し対象ではないメモリセルの第5の配線に対してトランジスタ166がオフ状態となるような電位、例えば接地電位などを与えて、トランジスタ166をオフ状態にすればよい。これにより、各メモリセルのトランジスタ160のゲート電極に保持された電荷によることなく、読み出し対象ではないメモリセルのトランジスタ160と第2の配線の間に電気的に接続される当該メモリセルのトランジスタ166を選択的にオフ状態とすることができます。よって、読み出し対象のメモリセルに接続された第2の配線の電位のみを見ることが出来るので、メモリセルをアレイ状に配置しても、所望のメモリセルの情報のみを容易に読み出すことができる。

20

【0044】

次に、情報の書き換えについて説明する。情報の書き換えは、上記情報の書き込みおよび保持と同様に行われる。つまり、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位(新たな情報に係る電位)が、トランジスタ160のゲート電極に与えられる。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極は、新たな情報に係る電荷が与えられた状態となる。

30

【0045】

このように、開示する発明に係る半導体装置は、再度の情報の書き込みによって直接的に情報を書き換えることが可能である。このためフラッシュメモリなどにおいて必要とされる高電圧を用いてのフローティングゲートからの電荷の引き抜きが不要であり、消去動作に起因する動作速度の低下を抑制することができる。つまり、半導体装置の高速動作が実現される。

40

【0046】

なお、トランジスタ162のドレイン電極(またはソース電極)は、トランジスタ160のゲート電極と電気的に接続されることにより、不揮発性メモリ素子として用いられるフローティングゲート型トランジスタのフローティングゲートと同等の作用を奏する。以下において、トランジスタ162のドレイン電極(またはソース電極)とトランジスタ160のゲート電極が電気的に接続される部位をノードFGと呼ぶ場合がある。トランジスタ

50

162がオフの場合、当該ノードF Gは絶縁体中に埋設されたと見ることができ、ノードF Gには電荷が保持される。酸化物半導体を用いたトランジスタ162のオフ電流は、シリコン半導体などで形成されるトランジスタの10万分の1以下であるため、トランジスタ162のリークによる、ノードF Gに蓄積された電荷の消失を無視することが可能である。つまり、酸化物半導体を用いたトランジスタ162により、電力の供給が無くても情報の保持が可能な不揮発性の記憶装置を実現することが可能である。

【0047】

例えば、トランジスタ162の室温(25)でのオフ電流が10zA(1zA(ゼットアンペア))は $1 \times 10^{-21} A$ 以下である場合には、10<sup>4</sup>秒以上のデータ保持を行うことも可能である。なお、当該保持時間が、トランジスタ特性や容量値によって変動することはいうまでもない。

10

【0048】

また、開示する発明の半導体装置においては、従来のフローティングゲート型トランジスタにおいて指摘されているゲート絶縁膜(トンネル絶縁膜)の劣化という問題が存在しない。つまり、従来問題とされていた、フローティングゲートへの電子の注入またはフローティングゲートからの電子の引き抜きによるゲート絶縁膜の劣化という問題を解消することができる。これは、原理的な書き込み回数の制限が存在しないことを意味するものである。また、従来のフローティングゲート型トランジスタにおいて書き込みや消去の際に必要であった高電圧も不要である。

【0049】

20

なお、半導体装置の記憶容量を大きくするためには、多値化の手法を探ることもできる。例えば、メモリセルの一に3段階以上の情報を書き込む構成とすることで、2段階(1ビット)の情報を書き込む場合と比較して記憶容量を増大させることができる。例えば、上述のような、低電位を与える電荷Q<sub>L</sub>、高電位を与える電荷Q<sub>H</sub>に加え、他の電位を与える電荷Qをトランジスタ160のゲート電極に与えることで、多値化を実現することができる。この場合、比較的規模の大きい回路構成を採用しても十分な記憶容量を確保することができる。

【0050】

応用例1

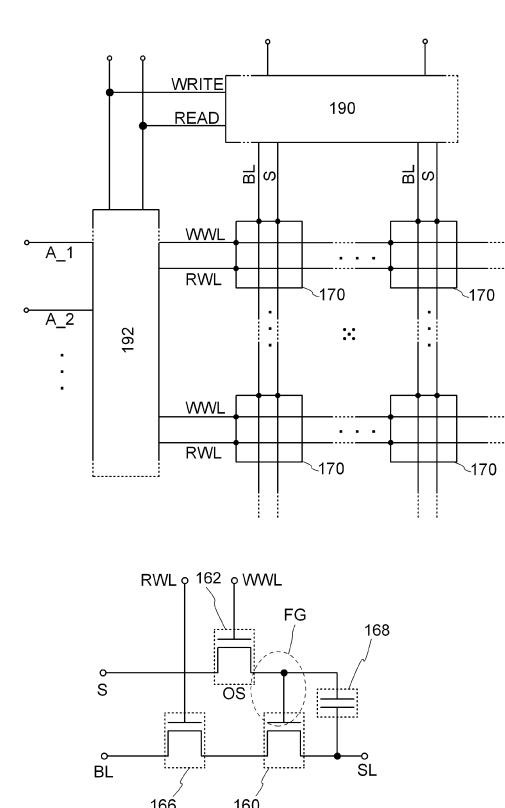

次に、図1に示す回路を応用したより具体的な回路構成および動作について、図2乃至図5を参照して説明する。

30

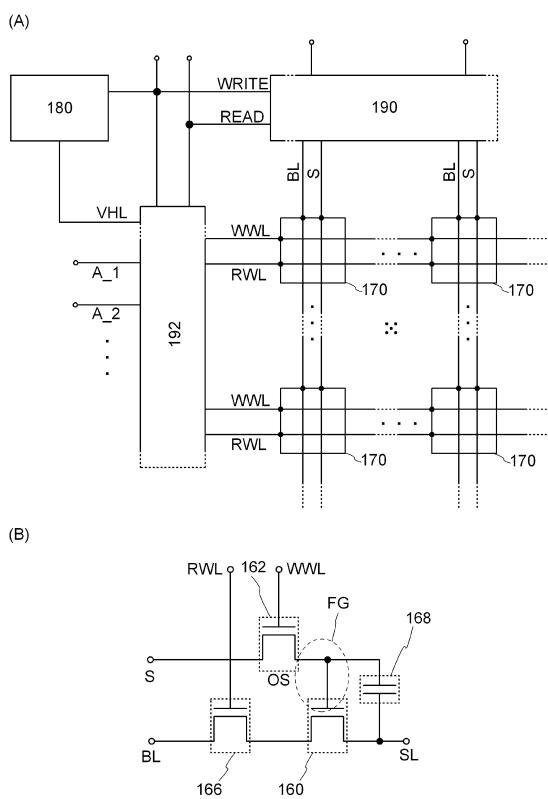

【0051】

図2(A)及び図2(B)は、(m×n)個のメモリセル170を有する半導体装置の回路図の一例である。図2中のメモリセル170の構成は、図1(B)と同様である。すなわち、図1(B)における第1の配線が図2(B)におけるソース線S Lに相当し、図1(B)における第2の配線が図2におけるビット線B Lに相当し、図1(B)における第3の配線が図2における信号線Sに相当し、図1(B)における第4の配線が図2における書き込みワード線W W Lに相当し、図1(B)における第5の配線が図2における読み出しワード線R W Lに相当する(図2(B)参照)。ただし、図2(A)では、図1(B)における第1の配線であるソース線S Lは省略している。

40

【0052】

図2に示す半導体装置は、m本(mは2以上の整数)の書き込みワード線W W Lと、m本の読み出しワード線R W Lと、n本(nは2以上の整数)のビット線B Lと、n本の信号線Sと、メモリセル170が縦m個(行)×横n個(列)のマトリクス状に配置されたメモリセルアレイと、n本のビット線B Lおよびn本の信号線Sに接続する第1の駆動回路190と、m本の書き込みワード線W W Lおよびm本の読み出しワード線R W Lに接続する第2の駆動回路192と、を有する。ここで、各メモリセル170は、各ソース線S Lとビット線B Lとの間に並列に接続されている。また、第1の駆動回路190、および第2の駆動回路192を、配線W R I T Eおよび配線R E A Dによって接続する構成とするのが好ましい。

50

## 【0053】

その他、第2の駆動回路192には、アドレス選択信号線A\_1乃至アドレス選択信号線A\_mが接続されている。アドレス選択信号線A\_1乃至アドレス選択信号線A\_mは、メモリセルの行方向のアドレスを選択する信号を伝達する配線である。

## 【0054】

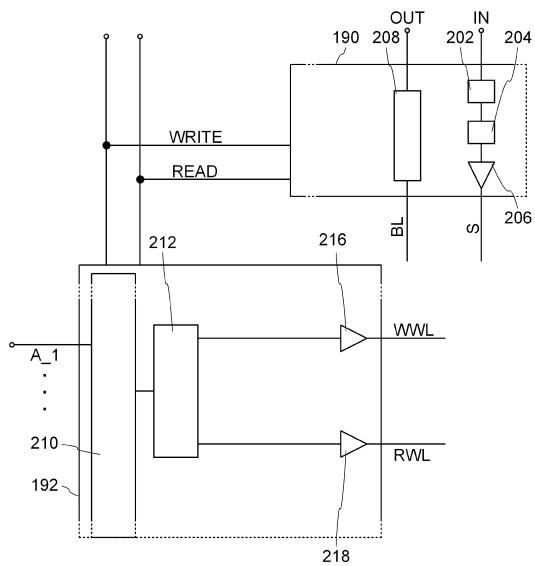

図3に、図2に示す半導体装置における第1の駆動回路190及び第2の駆動回路192の具体的構成の一例を示す。ただし、第1の駆動回路190及び第2の駆動回路192の構成は、これに限られるものではない。

## 【0055】

図3において、第1の駆動回路190は、入力端子と接続した制御回路202と、制御回路202と接続した遅延回路204と、遅延回路204及び信号線Sと接続したバッファ回路206と、ビット線と接続した読み出し回路208と、読み出し回路208からの信号を出力する出力端子と、を有している。10

## 【0056】

また、図3において、第2の駆動回路192は、アドレス選択信号線A\_1乃至アドレス選択信号線A\_mと接続したデコーダ210と、デコーダ210と接続した制御回路212と、制御回路212および書き込みワード線WWLと接続したバッファ回路216と、制御回路212および読み出しワード線RWLと接続したバッファ回路218と、を有している。ここでは、第2の駆動回路192から書き込みワード線WWLおよび読み出しワード線RWLに接地電位GNDまたは電源電位VDDが出力される。20

## 【0057】

図2に示す半導体装置において、データの書き込み、保持、および読み出しは、基本的に図1の場合と同様である。つまり、具体的な書き込みの動作は以下のようになる。なお、ここでは一例として、ノードFGに電位V1（電源電位VDDよりトランジスタ162のしきい値分低い電位）または接地電位GNDのいずれかを与える場合について説明するが、ノードFGに与える電位の関係はこれに限られない。また、ノードFGに電位V1を与えた場合に保持されるデータをデータ”1”、ノードFGに接地電位GND（0V）を与えた場合に保持されるデータをデータ”0”とする。

## 【0058】

まず、書き込み対象のメモリセル170に接続される読み出しワード線RWLの電位をGNDとし、書き込みワード線WWLの電位をVDDとしてメモリセル170を選択する。30

## 【0059】

メモリセル170にデータ”0”を書き込む場合には、信号線SにはGNDを与え、メモリセル170にデータ”1”を書き込む場合には、信号線Sにはトランジスタ162において生じるしきい値分の電位の低下を考慮した電位を与える。

## 【0060】

データの保持は、書き込みワード線WWLの電位を、接地電位GNDとすることにより行われる。

## 【0061】

書き込みワード線WWLには接地電位GNDが与えられているため、データ”1”とデータ”0”のいずれが書き込まれた場合でも、トランジスタ162はオフ状態となる。トランジスタ162のオフ電流は極めて小さいから、トランジスタ160のゲート電極の電荷は長時間にわたって保持される。40

## 【0062】

データの読み出しは、読み出しワード線RWLの電位をVDDとし、書き込みワード線WWLの電位をGNDとして読み出し対象のメモリセル170を選択して行われる。ここでの各メモリセル170には、データに応じた電荷がゲート電極に保持されたトランジスタ160とビット線BLとの間に、読み出しワード線RWLがゲート電極に接続されたトランジスタ166が設けられている。よって、読み出し対象ではないメモリセルに接続された読み出しワード線RWLの電位をGNDとすることで、読み出し対象のメモリセル1750

0を容易に選択することができる。このように、データの読み出しの際の読み出しワード線RWLの電位は、電位VDDまたは接地電位GNDとすればよいので、図2に示す半導体装置において電位変換回路を設けたり、外部に別途電源を設ける必要がない。

【0063】

読み出しワード線RWLの電位をGNDからVDDに上昇させると、トランジスタ166のゲート電極の電位が上昇してしきい値以上となり、トランジスタ166はオン状態となる。

【0064】

上述の読み出し動作により、メモリセル170にデータ"1"(電位V1)が書き込まれている場合には、トランジスタ160がオン状態となり、ビット線BLの電位が低下する。また、データ"0"(接地電位GND)が書き込まれている場合には、トランジスタ160がオフ状態となり、読み出し開始時のビット線BLの電位が維持されるか、または上昇する。

【0065】

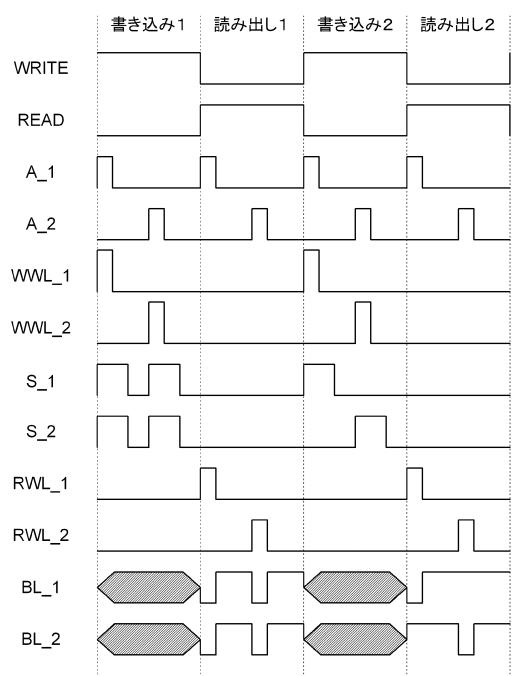

図4には、図2に係る半導体装置のより詳細な動作に係るタイミングチャートの例を示す。タイミングチャート中のREAD、A等の名称は、タイミングチャートに示す電位が与えられる配線を示しており、同様の機能を有する配線が複数ある場合には、配線の名称の末尾に\_\_1、\_\_2等を付することで区別している。なお、ここでは説明を簡単にするため、メモリセル170が2(行)×2(列)に配列された半導体装置を例に説明するが、開示する発明はこれに限られない。

10

20

【0066】

図4に示されるタイミングチャートは、全てのメモリセルにデータ"1"を書き込み(書き込み1)、その後、書き込まれた全データを読み出し(読み出し1)、次に、第1行第1列のメモリセルおよび第2行第2列のメモリセルにデータ"1"を書き込むと共に、第1行第2列のメモリセルおよび第2行第1列のメモリセルにデータ"0"を書き込み(書き込み2)、その後、書き込まれた全データを読み出す(読み出し2)場合の各配線の電位の関係を示すものである。

【0067】

書き込み1において、WRITEを高電位とし、READを低電位として、第1の駆動回路190および第2の駆動回路192をメモリセルへの書き込みが行える状態にする。第2の駆動回路192は、A\_\_1、A\_\_2の電位に応じた行選択信号をWWLに出力する。ここでは、A\_\_1、A\_\_2が高電位の場合には対象の行が選択されることとする。また、選択された行のWWLは、高電位となり、RWLは、選択、非選択に関わらず低電位となる。

30

【0068】

書き込み1においては、全てのメモリセルにデータ"1"を書き込むため、行選択のタイミングに合わせて、S\_\_1およびS\_\_2を高電位とする。なお、S\_\_1およびS\_\_2の信号入力期間は、WWLの信号入力期間と同期間、またはWWLの信号入力期間より長くなるようにする。または、S\_\_1およびS\_\_2の信号入力を、WWLの信号入力より遅らせる。S\_\_1およびS\_\_2の信号入力期間がWWLの信号入力期間より短いと、メモリセルへの書き込みが不十分となる可能性があるためである。S\_\_1およびS\_\_2の信号入力期間をWWLの信号入力期間より長くするためには、S\_\_1やS\_\_2に遅延回路を接続して、S\_\_1やS\_\_2の信号入力を、WWLの信号入力より遅らせることが好ましい。または、S\_\_1やS\_\_2に接続されるバッファ回路を構成するトランジスタのチャネル長を、WWLに接続されるバッファ回路を構成するトランジスタのチャネル長より大きくして、S\_\_1およびS\_\_2の信号入力を、WWLの信号入力より遅らせねばよい。または、S\_\_1やS\_\_2に接続されるバッファ回路を構成するトランジスタのチャネル幅を、WWLに接続されるバッファ回路を構成するトランジスタのチャネル幅より小さくして、S\_\_1およびS\_\_2の信号入力を、WWLの信号入力より遅らせねばよい。なお、BL\_\_1およびBL\_\_2の電位は、書き込み時には問題とならない(高電位であっても良いし低電位であつ

40

50

ても良い)。

【0069】

読み出し1においては、READを高電位とし、WRITEを低電位として、第1の駆動回路190および第2の駆動回路192をメモリセルからの読み出しが行える状態にする。第2の駆動回路192は、A\_1、A\_2に応じた行選択信号をRWLに出力する。ここでは、A\_1、A\_2が高電位の場合には対象の行が選択されることとする。また、選択された行のRWLは高電位となり、WWLは、選択、非選択に関わらず低電位となる。

【0070】

上述の動作により、BL\_1およびBL\_2には、選択された行のメモリセルに保持されているデータに応じた電位が与えられる。なお、S\_1およびS\_2の電位は、読み出し時には問題とならない。

10

【0071】

書き込み2における各配線の電位の関係は、書き込み1の場合と同様である。ただし、第1行第1列のメモリセルおよび第2行第2列のメモリセルにデータ”1”を書き込むと共に、第1行第2列のメモリセルおよび第2行第1列のメモリセルにデータ”0”を書き込むために、行選択のタイミングに合わせて、S\_1およびS\_2を低電位または高電位とする。

【0072】

読み出し2における各配線の電位の関係は、読み出し1の場合と同様である。BL\_1およびBL\_2には、選択された行のメモリセルに保持されているデータに応じた電位が与えられることがわかる。

20

【0073】

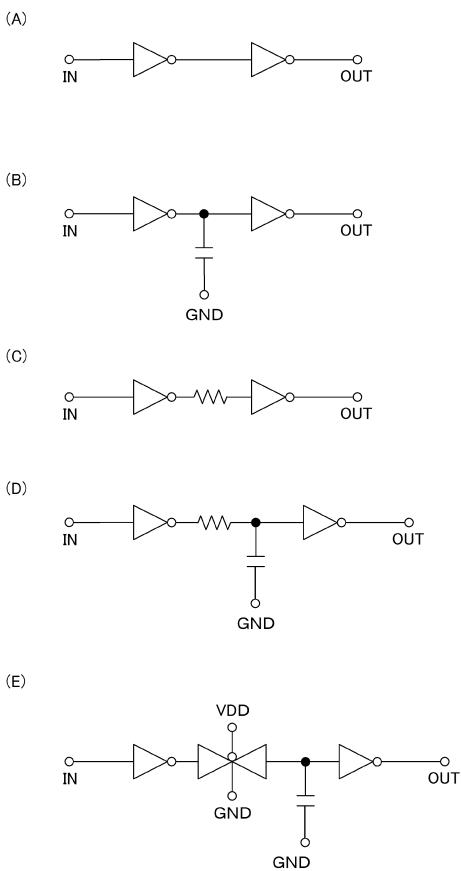

なお、上述の書き込み動作において、書き込みワード線WWLに入力される信号よりも信号線Sに入力される信号を遅らせるためには、図5に示す遅延回路を、図3に示す第1の駆動回路190内の遅延回路204として用い、信号線Sと接続することが好ましい。遅延回路204と信号線Sとを接続することで、書き込みワード線WWLの電位の変化より信号線Sの電位の変化を遅らせることができ、メモリセル170への情報の書き込みを十分に行うことができる。

【0074】

遅延回路として、例えば、図5(A)に示すような偶数個のインバータ回路を直列に接続した回路を用いることができる。または、図5(B)に示すように、直列に接続した偶数個のインバータ回路の間に容量素子を附加した構成や、図5(C)に示すように、直列に接続した偶数個のインバータ回路の間に抵抗を附加した構成としてもよい。または、図5(D)に示すように、直列に接続した偶数個のインバータ回路の間に、抵抗および容量素子を附加した構成としてもよい。さらに、図5(E)に示すように、直列に接続した偶数個のインバータ回路の間に、アナログスイッチおよび容量素子を附加した構成としてもよい。ここで、アナログスイッチは常にオン状態としており、抵抗として機能する。また、アナログスイッチは、寄生容量を有するので、さらに遅延効果を向上させることができる。

30

【0075】

または、上述の書き込み動作において、書き込みワード線WWLに入力される信号よりも信号線Sに入力される信号を遅らせるために、第1の駆動回路190および第2の駆動回路192に設けられるバッファ回路において、第2の駆動回路192が有するバッファ回路のトランジスタのチャネル長よりも、第1の駆動回路190が有するバッファ回路のトランジスタのチャネル長を大きくしても良い。または、第1の駆動回路190および第2の駆動回路192に設けられるバッファ回路において、第2の駆動回路192が有するバッファ回路のトランジスタのチャネル幅よりも、第1の駆動回路190が有するバッファ回路のトランジスタのチャネル幅を小さくしても良い。この場合にも、書き込みワード線WWLの電位の変化より、信号線Sの電位の変化を遅らせることができ、メモリセル170への書き込みミスを抑制することができる。

40

50

## 【0076】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【0077】

## 応用例 2

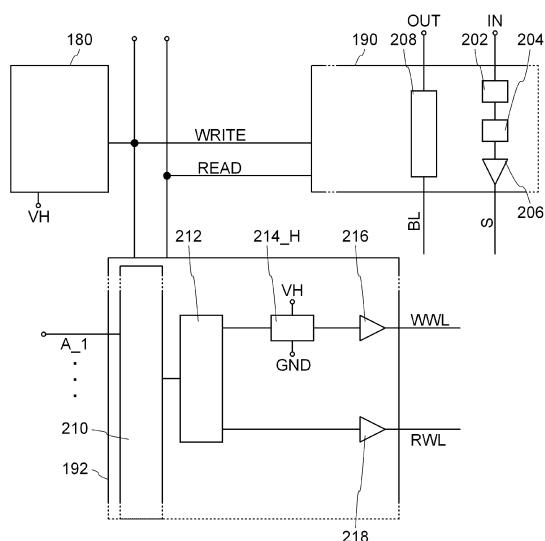

図2に示す回路構成とは異なる回路構成について、図6乃至図9を参照して説明する。

## 【0078】

図6(A)及び図6(B)は、(m × n)個のメモリセル170を有する半導体装置の回路図の一例である。図6中のメモリセル170の構成は、図2と同様であるため、詳細な説明は省略する。

10

## 【0079】

図6に示す半導体装置は、m本(mは2以上の整数)の書き込みワード線WWLと、m本の読み出しワード線RWLと、n本(nは2以上の整数)のビット線BLと、n本の信号線Sと、メモリセル170が縦m個(行)×横n個(列)のマトリクス状に配置されたメモリセルアレイと、電位変換回路180と、n本のビット線BLおよびn本の信号線Sに接続する第1の駆動回路190と、m本の書き込みワード線WWLおよびm本の読み出しワード線RWLに接続する第2の駆動回路192と、を有する。ここで、電位変換回路180は、配線VHLによって第2の駆動回路192と接続され、第2の駆動回路192に電源電位よりも高い電位(高電位:VH)を出力する。なお、本実施の形態では、配線WRITEを電位変換回路180に接続することで、第1の駆動回路190の出力に合わせて電位を変換する構成としている。また、第1の駆動回路190、および第2の駆動回路192を、配線WRITEおよび配線READによって接続する構成とするのが好ましい。

20

## 【0080】

その他、第2の駆動回路192には、アドレス選択信号線Aが接続されている。アドレス選択信号線Aは、メモリセルの行方向のアドレスを選択する信号を伝達する配線である。

## 【0081】

図7に、図6に示す半導体装置における第1の駆動回路190及び第2の駆動回路192の具体的構成の一例を示す。ただし、第1の駆動回路190及び第2の駆動回路192の構成は、これに限られるものではない。

30

## 【0082】

図7において、第1の駆動回路190は、入力端子と接続した制御回路202と、制御回路202と接続した遅延回路204と、遅延回路204及び信号線Sと接続したバッファ回路206と、ビット線と接続した読み出し回路208と、読み出し回路208からの信号を出力する出力端子と、を有している。なお、遅延回路204については、図5に示す回路と同様の回路を用いることができる。

## 【0083】

また、図7において、第2の駆動回路192は、アドレス選択信号線Aと接続したデコーダ210と、デコーダ210と接続した制御回路212と、制御回路212と接続した昇圧用レベルシフタ214\_Hと、昇圧用レベルシフタ214\_Hおよび書き込みワード線WWLと接続したバッファ回路216と、制御回路212および読み出しワード線RWLと接続したバッファ回路218と、を有している。第2の駆動回路192に含まれる昇圧用レベルシフタ214\_Hは、電位変換回路180で変換された電位VHを用いて信号の振幅変換を行う。ここでは、書き込みワード線WWLにはGNDまたはVHが出力され、読み出しワード線RWLには、GNDまたはVDDが出力される。

40

## 【0084】

図6に示す半導体装置において、データの書き込み、保持、および読み出しが、図2の場合と同様である。ただし、図6に示す構成においては、書き込みの際に、書き込みワード線WWLの電位を電源電位より高い電位(VH)とすることができます。これにより、信号線Sを介してノードFGに与えられる電位が、トランジスタ162でしきい値分低下させ

50

られることを防ぐことができる。このため、ノード F G に十分に高い電位（例えば、V D D）を与えることができ、より長期間のデータ保持が可能になる。また、データの識別力が向上する。

【0085】

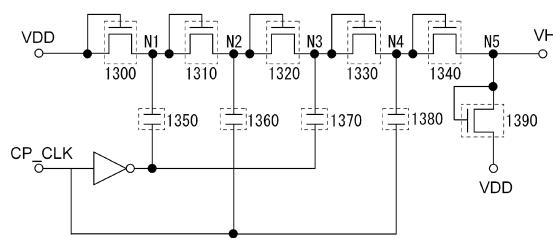

電位変換回路 180 には、昇圧回路などを用いることができる。図 8 に 4 段の昇圧を行う昇圧回路の一例を示す。図 8 において、第 1 のトランジスタ 1300 の入力端子（ここでは、ソース端子またはドレイン端子であって、ゲート端子と接続されている端子をいう）には電源電位 V D D が供給される。第 1 のトランジスタ 1300 の出力端子（ここでは、ソース端子またはドレイン端子であって、ゲート端子と接続されていない端子をいう）には第 2 のトランジスタ 1310 の入力端子及び第 1 の容量素子 1350 の一方の端子が接続されている。同様に、第 2 のトランジスタ 1310 の出力端子には第 3 のトランジスタ 1320 の入力端子及び第 2 の容量素子 1360 の一方の端子が接続されている。以下、同様であるため詳細な説明は省略するが、第 n のトランジスタの出力端子には第 n の容量素子の一方の端子が接続されているということもできる（n：自然数）。図 8 においては、最終段のトランジスタの出力端子には、電源 V D D と接続したトランジスタ 1390 が接続されているが、この構成に限られない。例えば、接地電位 G N D と接続した容量をさらに付加した構成としても良い。なお、図 8 においては、第 5 のトランジスタ 1340 の出力が、昇圧回路の出力 V H となる。

【0086】

さらに、第 2 の容量素子 1360 の他方の端子及び第 4 の容量素子 1380 の他方の端子には、クロック信号 C P \_ C L K が入力される。また、第 1 の容量素子 1350 の他方の端子及び第 3 の容量素子 1370 の他方の端子には、クロック信号 C P \_ C L K を反転させたクロック信号が入力される。すなわち、第 2 k の容量素子の他方の端子にはクロック信号 C P \_ C L K が入力され、第 2 k - 1 の容量素子の他方の端子にはその反転クロック信号が入力されるといえる（k：自然数）。もちろん、クロック信号 C P \_ C L K と反転クロック信号とは、入れ替えて用いることができる。

【0087】

クロック信号 C P \_ C L K が L o w である場合、つまり反転クロック信号が H i g h である場合には、第 2 の容量素子 1360 および第 4 の容量素子 1380 が充電される。反転クロック信号と容量結合するノード N 1 およびノード N 3 の電位は、所定の電圧（クロック信号 C P \_ C L K の H i g h と L o w の電位差に相当する電圧）分だけ引き上げられる。一方で、クロック信号 C P \_ C L K と容量結合するノード N 2 およびノード N 4 の電位は、所定の電圧分だけ引き下げられる。

【0088】

これにより、第 2 のトランジスタ 1310、第 4 のトランジスタ 1330 を通じて電荷が移動し、ノード N 2 およびノード N 4 の電位が所定の値まで引き上げられる。

【0089】

次にクロック信号 C P \_ C L K が H i g h になり、反転クロック信号が L o w になると、ノード N 2 及びノード N 4 の電位がさらに引き上げられる。一方で、ノード N 1、ノード N 3 の電位は、所定の電圧分だけ引き下げられる。

【0090】

これにより、第 1 のトランジスタ 1300、第 3 のトランジスタ 1320、第 5 のトランジスタ 1340 を通じて電荷が移動し、その結果、ノード N 1、ノード N 3 及びノード N 5 の電位が所定の電位まで引き上げられることになる。このように、それぞれのノードにおける電位が  $V_{N5} = V_{N4} (C P _ C L K = H i g h) > V_{N3} (C P _ C L K = L o w) > V_{N2} (C P _ C L K = H i g h) > V_{N1} (C P _ C L K = L o w) > V D D$  となることにより、昇圧が行われる。なお、昇圧回路の構成は、4 段の昇圧を行うものに限定されない。昇圧回路の段数は適宜変更することができる。なお、第 1 のトランジスタ 1300、第 2 のトランジスタ 1310、第 3 のトランジスタ 1320、第 4 のトランジスタ 1330、第 5 のトランジスタ 1340 として n チャネル型トランジスタ、トランジス

10

20

30

40

50

タ 1 3 9 0 として p チャネル型トランジスタを用いることができる。

【 0 0 9 1 】

なお、昇圧回路に用いるトランジスタとして、オフ電流特性の良好な酸化物半導体を含むトランジスタを用いることにより、各ノードの電圧の保持時間を長くすることができる。

【 0 0 9 2 】

電位変換回路 1 8 0 で高電位へ変換された電位を用いて、第 2 の駆動回路 1 9 2 に含まれる昇圧用レベルシフタによって振幅変換した信号を、書き込みワード線 W W L から各メモリセル 1 7 0 へと出力する。さらに、電位変換回路 1 8 0 で高電位へ変換された電位を用いて、第 1 の駆動回路 1 9 0 に含まれる昇圧用レベルシフタによって振幅変換した信号を、信号線 S から各メモリセル 1 7 0 へと出力する構成としてもよい。

10

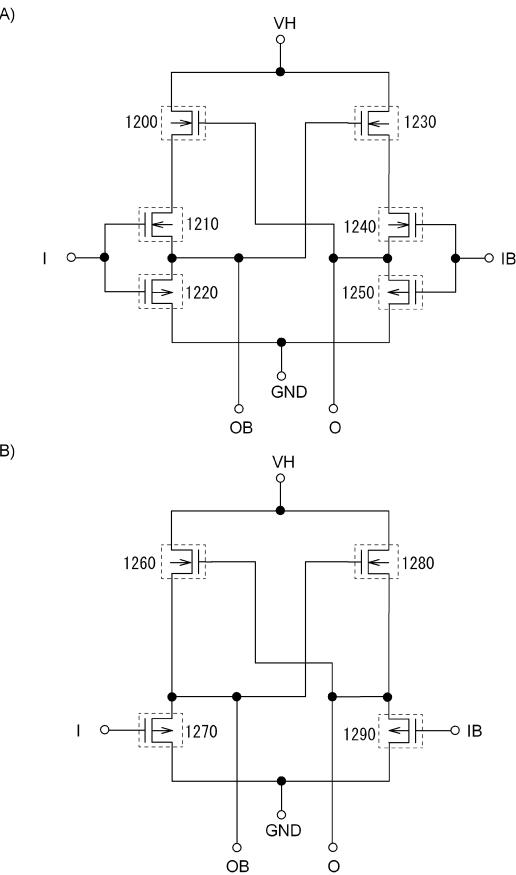

【 0 0 9 3 】

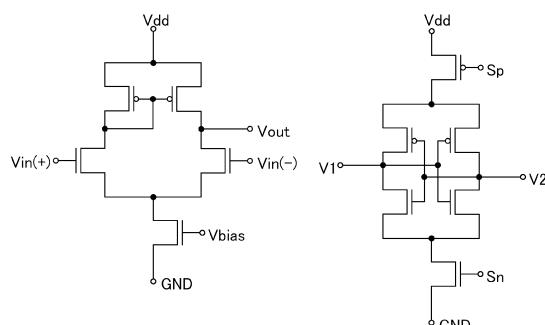

図 9 ( A ) 及び図 9 ( B ) に、昇圧用レベルシフタの回路図の例を示す。図 9 ( A ) に示すレベルシフタの構成は、以下の通りである。第 1 の p 型トランジスタ 1 2 0 0 のソース端子と第 3 の p 型トランジスタ 1 2 3 0 のソース端子は、共に電位 V H を供給する電源に電気的に接続している。第 1 の p 型トランジスタ 1 2 0 0 のドレイン端子は、第 2 の p 型トランジスタ 1 2 1 0 のソース端子と電気的に接続され、第 3 の p 型トランジスタ 1 2 3 0 のドレイン端子は、第 4 の p 型トランジスタ 1 2 4 0 のソース端子と電気的に接続されている。第 2 の p 型トランジスタ 1 2 1 0 のドレイン端子は、第 1 の n 型トランジスタ 1 2 2 0 のドレイン端子及び第 3 の p 型トランジスタ 1 2 3 0 のゲート端子に電気的に接続され、第 4 の p 型トランジスタ 1 2 4 0 のドレイン端子は、第 2 の n 型トランジスタ 1 2 5 0 のドレイン端子及び第 1 の p 型トランジスタ 1 2 0 0 のゲート端子と電気的に接続されている。また、第 1 の n 型トランジスタ 1 2 2 0 のソース端子と第 2 の n 型トランジスタ 1 2 5 0 のソース端子には、共に G N D ( = 0 [ V ] ) が与えられている。

20

【 0 0 9 4 】

図 9 ( A ) において、入力信号 ( I ) は、第 2 の p 型トランジスタ 1 2 1 0 のゲート端子と、第 1 の n 型トランジスタ 1 2 2 0 のゲート端子とに入力され、入力信号の反転信号 ( I B ) は、第 4 の p 型トランジスタ 1 2 4 0 のゲート端子と、第 2 の n 型トランジスタ 1 2 5 0 のゲート端子とに入力される。出力信号 ( O ) は、第 4 の p 型トランジスタ 1 2 4 0 のドレイン端子から取り出される。また、第 2 の p 型トランジスタ 1 2 1 0 のドレイン端子から出力信号の反転信号 ( O B ) を取り出すこともできる。

30

【 0 0 9 5 】

図 9 ( A ) に示すレベルシフタの基本的な動作を説明する。入力信号 ( I ) に H i g h が入力されると、第 1 の n 型トランジスタ 1 2 2 0 が導通状態となるため、第 3 の p 型トランジスタ 1 2 3 0 のゲート端子に電位 G N D が入力され、第 3 の p 型トランジスタ 1 2 3 0 が導通状態となるとともに、出力信号の反転信号 ( O B ) には L o w が出力され、このときの電位は G N D となる。一方、反転入力信号 ( I B ) は、このとき L o w であるから、第 4 の p 型トランジスタ 1 2 4 0 は導通状態となり、第 2 の n 型トランジスタ 1 2 5 0 は非導通状態となる。ここで、第 3 の p 型トランジスタ 1 2 3 0 と第 4 の p 型トランジスタ 1 2 4 0 が共に導通状態となるため、出力信号 ( O ) には H i g h が出力され、このときの電位は V H となる。

40

【 0 0 9 6 】

入力信号 ( I ) の電位が L o w のときは、図 9 ( A ) に示すレベルシフタが対称構造をとることから、上記と同様に理解でき、出力信号 ( O ) からは L o w が出力され、このときの電位は G N D となる。

【 0 0 9 7 】

このようにして、入力した信号に対して振幅を変換した出力信号 ( O ) を得ることができる。

【 0 0 9 8 】

図 9 ( B ) は、図 9 ( A ) とは異なる昇圧用レベルシフタの回路図の例を示す。図 9 ( B ) に示すレベルシフタの構成は、以下の通りである。第 1 の p 型トランジスタ 1 2 6 0 の

50

ソース端子と第2のp型トランジスタ1280のソース端子は、共に電位VHを供給する電源に電気的に接続している。第1のn型トランジスタ1270のドレイン端子は、第1のp型トランジスタ1260のドレイン端子及び第2のp型トランジスタ1280のゲート端子に電気的に接続され、第2のn型トランジスタ1290のドレイン端子は、第2のp型トランジスタ1280のドレイン端子及び第1のp型トランジスタ1260のゲート端子と電気的に接続されている。また、第1のn型トランジスタ1270のソース端子と第2のn型トランジスタ1290のソース端子には、共にGND(=0[V])が与えられている。

【0099】

図9(B)において、入力信号(I)は、第1のn型トランジスタ1270のゲート端子に入力され、入力信号の反転信号(IB)は、第2のn型トランジスタ1290のゲート端子に入力される。出力信号(O)は、第2のn型トランジスタ1290のドレイン端子から取り出される。また、第1のn型トランジスタ1270のドレイン端子から出力信号の反転信号(OB)を取り出すこともできる。

10

【0100】

図9(B)に示すレベルシフタの基本的な動作を説明する。入力信号(I)にHighが入力されると、第1のn型トランジスタ1270は導通状態となるため、第2のp型トランジスタ1280のゲート端子に電位GNDが入力され、第2のp型トランジスタ1280が導通状態となるとともに、出力信号の反転信号(OB)にはLowが出力され、このときの電位はGNDとなる。一方、反転入力信号(IB)は、このときLowであるから、第2のn型トランジスタ1290は非導通状態となる。ここで、第2のp型トランジスタ1280が導通状態となるため、出力信号(O)にはHighが出力され、このときの電位はVHとなる。

20

【0101】

入力信号(I)の電位がLowのときは、図9(B)に示すレベルシフタが対称構造をとることから、上記と同様に理解でき、出力信号(O)からはLowが出力され、このときの電位はGNDとなる。

【0102】

このようにして、入力した信号に対して振幅を変換した出力信号(O)を得ることができる。

30

【0103】

読み出し回路

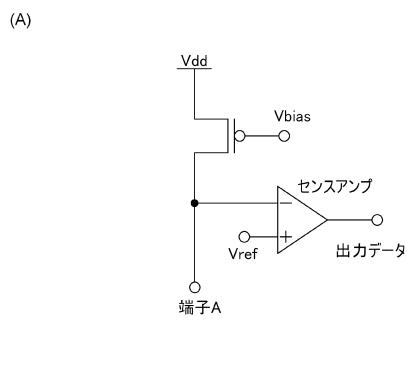

次に、図3及び図7に示す半導体装置などに用いることができる読み出し回路208の一例について図10を用いて説明する。

【0104】

図10(A)には、読み出し回路の概略を示す。当該読み出し回路は、トランジスタとセンスアンプ回路を有する。

【0105】

読み出し時には、端子Aは読み出しを行うメモリセルが接続されたビット線BLに接続される。また、トランジスタのゲート電極にはバイアス電位Vbiasが印加され、端子Aの電位が制御される。

40

【0106】

メモリセル170は、格納されるデータに応じて、異なる抵抗値を示す。具体的には、選択したメモリセル170のトランジスタ160がオン状態の場合には低抵抗状態となり、選択したメモリセル170のトランジスタ160がオフ状態の場合には高抵抗状態となる。

【0107】

メモリセルが高抵抗状態の場合、端子Aの電位が参照電位Vrefより高くなり、センスアンプ回路は端子Aの電位に対応する電位(データ"0")を出力する。一方、メモリセルが低抵抗状態の場合、端子Aの電位が参照電位Vrefより低くなり、センスアンプ回

50

路は端子Aの電位に対応する電位（データ”1”）を出力する。

【0108】

このように、読み出し回路を用いることで、メモリセルからデータを読み出すことができる。なお、本実施の形態の読み出し回路は一例である。他の公知の回路を用いても良い。また、読み出し回路は、プリチャージ回路を有しても良い。参照電位Vrefの代わりに参照用メモリセルに接続されたビット線が接続される構成としても良い。

【0109】

図10(B)に、センスアンプ回路の一例である差動型センスアンプを示す。差動型センスアンプは、入力端子Vin(+)とVin(-)と出力端子Voutを有し、Vin(+)とVin(-)の差を増幅する。Vin(+) > Vin(-)であればVoutは、概ねHigh出力、Vin(+) < Vin(-)であればVoutは、概ねLow出力となる。

10

【0110】

図10(C)に、センスアンプ回路の一例であるラッチ型センスアンプを示す。ラッチ型センスアンプは、入出力端子V1およびV2と、制御用信号Sp、Snの入力端子を有する。まず、信号SpをHigh、信号SnをLowとして、電源電位(Vdd)を遮断する。そして、比較を行う電位をV1とV2に与える。その後、信号SpをLow、信号SnをHighとして、電源電位(Vdd)を供給すると、比較を行う電位V1inとV2inがV1in > V2inの関係にあれば、V1の出力はHigh、V2の出力はLowとなり、V1in < V2inの関係にあれば、V1の出力はLow、V2の出力はHighとなる。このような関係を利用して、V1inとV2inの差を増幅することができる。

20

【0111】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

【0112】

(実施の形態2)

本実施の形態では、開示する発明の一態様に係る半導体装置の構成およびその作製方法について、図11乃至図16を参照して説明する。

30

【0113】

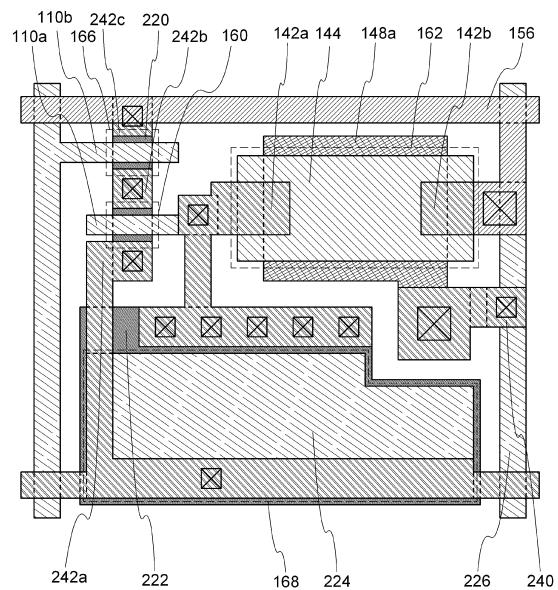

図16は、図2(B)に示す回路に対応する半導体装置の平面レイアウトである。基板上にトランジスタ160、トランジスタ166および容量素子168が設けられる。トランジスタ160は、半導体層220と、第1のゲート絶縁層と、ゲート電極110aと、ソース線SLとしても機能するソース電極またはドレイン電極242aと、ソース電極またはドレイン電極242bと、を含む。トランジスタ166は、半導体層220と、第1のゲート絶縁層と、読み出しワード線RWLとしても機能するゲート電極110bと、ソース電極またはドレイン電極242bと、ビット線BLとしても機能するソース電極またはドレイン電極242cと、を含む。容量素子168は、第1の電極(導電性を有する半導体層222)と、コンタクトホールを介してソース電極またはドレイン電極242aと接続される第2の電極(導電層224)と、誘電体として機能する第1のゲート絶縁層と、を含む。

40

【0114】

トランジスタ160、トランジスタ166および容量素子168上には、絶縁層が設けられ、該絶縁層上にトランジスタ162が設けられる。トランジスタ162は、書き込みワード線WWLとして機能する配線226と導電層240を介して電気的に接続されたゲート電極148aと、酸化物半導体層144と、第2のゲート絶縁層と、コンタクトホールを介してゲート電極110aおよび半導体層222と電気的に接続されたソース電極142aと、信号線Sとして機能する配線156とコンタクトホールを介して電気的に接続されたドレイン電極142bと、を含む。トランジスタ162上に絶縁層を設けるのが好ましい。

50

## 【0115】

半導体層220、導電性を有する半導体層222は、後述する基板100に用いる半導体材料と同様の材料を用いることができる。また、ゲート電極110a、ゲート電極110bは、後述するものと同様の材料を用いることができる、導電層224および配線226も同様の材料を用いることができる。また、ゲート電極148aは、後述するものと同様の材料を用いることができる。また、酸化物半導体層144は、後述するものと同様の材料を用いることができる。また、ソース電極142aおよびドレイン電極142bは、後述するものと同様の材料を用いることができ、ソース電極またはドレイン電極242a乃至ソース電極またはドレイン電極242c、導電層240も同様の材料を用いることができる。

10

## 【0116】

以下に図16に示す半導体装置を高集積化させた平面レイアウトを有する半導体装置について説明する。

## 【0117】

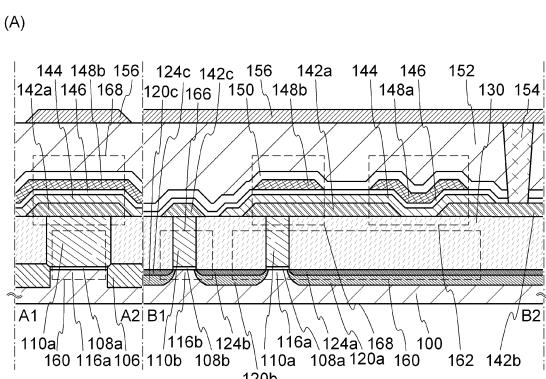

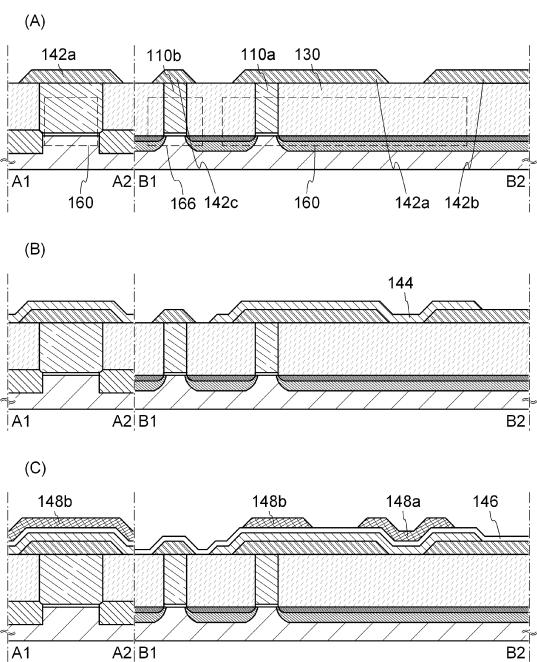

## 半導体装置の断面構成および平面構成

図11は、図2(B)に示す回路に対応する半導体装置を高集積化させた構成の一例である。図11(A)には、半導体装置の断面を、図11(B)には、半導体装置の平面を、それぞれ示す。ここで、図11(A)は、図11(B)のA1-A2およびB1-B2における断面に相当する。図11(A)および図11(B)に示される半導体装置は、下部に第1の半導体材料を用いたトランジスタ160およびトランジスタ166を有し、上部に第2の半導体材料を用いたトランジスタ162を有するものである。ここで、第1の半導体材料と第2の半導体材料とは異なる材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができます。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

20

## 【0118】

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるのはいうまでもない。また、開示する発明の技術的な本質は、情報を保持するために酸化物半導体のようなオフ電流を十分に低減することが可能な半導体材料をトランジスタ162に用いる点にあるから、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。また、図11に示す半導体装置は、トランジスタ160、トランジスタ162およびトランジスタ166をトップゲート構造で形成しているが、半導体装置に用いるトランジスタの構造はこれに限られるものではない。例えば、トランジスタ162をボトムゲート構造で形成するようにしても良い。

30

## 【0119】

図11におけるトランジスタ160は、半導体材料(例えば、シリコンなど)を含む基板100に設けられたチャネル形成領域116aと、チャネル形成領域116aを挟むように設けられた不純物領域120aおよび不純物領域120bと、不純物領域120aおよび不純物領域120bに接する金属化合物領域124aおよび金属化合物領域124bと、チャネル形成領域116a上に設けられたゲート絶縁層108aと、ゲート絶縁層108a上に設けられたゲート電極110aと、を有する。なお、図において、明示的にはソース電極やドレイン電極を有しない場合があるが、便宜上、このような状態を含めてトランジスタと呼ぶ場合がある。また、この場合、トランジスタの接続関係を説明するために、ソース領域やドレイン領域を含めてソース電極やドレイン電極と表現することがある。つまり、本明細書において、ソース電極との記載には、ソース領域が、ドレイン電極との記載には、ドレイン領域が、含まれうる。

40

## 【0120】

また、図11におけるトランジスタ166もトランジスタ160と同様に、半導体材料(

50

例えば、シリコンなどを含む基板 100 に設けられたチャネル形成領域 116b と、チャネル形成領域 116b を挟むように設けられた不純物領域 120b および不純物領域 120c と、不純物領域 120b および不純物領域 120c に接する金属化合物領域 124b および金属化合物領域 124c と、チャネル形成領域 116b 上に設けられたゲート絶縁層 108b と、ゲート絶縁層 108b 上に設けられたゲート電極 110b と、を有する。また、ゲート電極 110b 上に導電層 142c を設けることにより、トランジスタ 162 のソース電極およびドレイン電極をエッチングなどにより形成する際に、ゲート電極 110b が同時にエッチングされることを防ぐことができる。

#### 【0121】

また、基板 100 上にはトランジスタ 160 およびトランジスタ 166 を囲むように素子分離絶縁層 106 が設けられており、トランジスタ 160 およびトランジスタ 166 を覆うように絶縁層 130 が設けられている。なお、高集積化を実現するためには、図 11 に示すようにトランジスタ 160 およびトランジスタ 166 がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ 160 およびトランジスタ 166 の特性を重視する場合には、ゲート電極 110a およびゲート電極 110b の側面にサイドウォール絶縁層を設け、不純物濃度が異なる領域を含む不純物領域 120a 乃至不純物領域 120c を設けても良い。

#### 【0122】

図 11 におけるトランジスタ 162 は、絶縁層 130 上に設けられたソース電極 142a およびドレイン電極 142b と、ソース電極 142a およびドレイン電極 142b と電気的に接続されている酸化物半導体層 144 と、ソース電極 142a、ドレイン電極 142b、酸化物半導体層 144 を覆うゲート絶縁層 146 と、ゲート絶縁層 146 上に酸化物半導体層 144 と重畠するように設けられたゲート電極 148a と、を有する。

#### 【0123】

ここで、酸化物半導体層 144 は水素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。具体的には、例えば、酸化物半導体層 144 の水素濃度は  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、望ましくは  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より望ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。なお、上述の酸化物半導体層 144 中の水素濃度は、二次イオン質量分析法 (SIMS: Secondary Ion Mass Spectroscopy) で測定されるものである。このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠乏に起因するエネルギー・ギャップ中の欠陥準位が低減された酸化物半導体層 144 では、キャリア濃度が  $1 \times 10^{12}$  / cm<sup>3</sup> 未満、望ましくは、 $1 \times 10^{11}$  / cm<sup>3</sup> 未満、より望ましくは  $1.45 \times 10^{10}$  / cm<sup>3</sup> 未満となる。例えば、トランジスタ 162 の室温 (25) でのオフ電流 (ここでは、単位チャネル幅 (1 μm)あたりの値) は 100 zA (1 zA (ゼプトアンペア) は  $1 \times 10^{-12}$  A) 以下、好ましくは 10 zA 以下、より好ましくは 1 zA 以下、さらに好ましくは 100 yA 以下とができる。また、トランジスタ 162 のオフ電流は、低ければ低いほどよいが、トランジスタ 162 のオフ電流の下限値は  $10^{-30}$  A であると見積もられる。このように、i型化 (真性化) または実質的に i型化された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタ 162 を得ることができる。

#### 【0124】

なお、図 11 のトランジスタ 162 では、微細化に起因して素子間に生じるリークを抑制するために、島状に加工された酸化物半導体層 144 を用いているが、島状に加工されていない構成を採用しても良い。酸化物半導体層を島状に加工しない場合には、加工の際のエッチングによる酸化物半導体層 144 の汚染を防止できる。

#### 【0125】

図 11 における容量素子 168 は、ソース電極 142a、酸化物半導体層 144、ゲート絶縁層 146、および電極 148b、で構成される。すなわち、ソース電極 142a は、容量素子 168 の一方の電極として機能し、電極 148b は、容量素子 168 の他方の電

10

20

30

40

50

極として機能することになる。

【0126】

なお、図11の容量素子168では、酸化物半導体層144とゲート絶縁層146を積層させることにより、ソース電極142aと、電極148bとの間の絶縁性を十分に確保することができる。ここで、電極148bには接地電位などが与えられるのが好ましい。もちろん、十分な容量を確保するために、酸化物半導体層144を有しない構成の容量素子168を採用しても良い。さらに、容量が不要の場合は、容量素子168を設けない構成とすることも可能である。

【0127】

なお、トランジスタ162および容量素子168において、ソース電極142a、およびドレイン電極142bの端部は、テーパー形状であることが好ましい。ソース電極142a、ドレイン電極142bの端部をテーパー形状とすることにより、酸化物半導体層144の被覆性を向上し、段切れを防止することができるためである。ここで、テーパー角は、例えば、30°以上60°以下とする。なお、テーパー角とは、テーパー形状を有する層（例えば、ソース電極142a）を、その断面（基板の表面と直交する面）に垂直な方向から観察した際に、当該層の側面と底面がなす傾斜角を示す。

【0128】

図11に示す半導体装置では、トランジスタ162および容量素子168が、トランジスタ160と重畠するように設けられている。このような、平面レイアウトを採用することにより、高集積化が可能である。例えば、最小加工寸法をFとして、メモリセルの占める面積を $15F^2 \sim 25F^2$ とすることが可能である。

【0129】

トランジスタ162および容量素子168の上には、絶縁層150が設けられており、絶縁層150上には絶縁層152が設けられている。そして、ゲート絶縁層146、絶縁層150、絶縁層152などに形成された開口には、電極154が設けられ、絶縁層152上には電極154と接続する配線156が形成される。なお、図11では電極154を用いて、ドレイン電極142bと、配線156とを接続しているが、開示する発明はこれに限定されない。例えば、配線156を直接、ドレイン電極142bに接触させても良い。

【0130】

半導体装置の作製方法

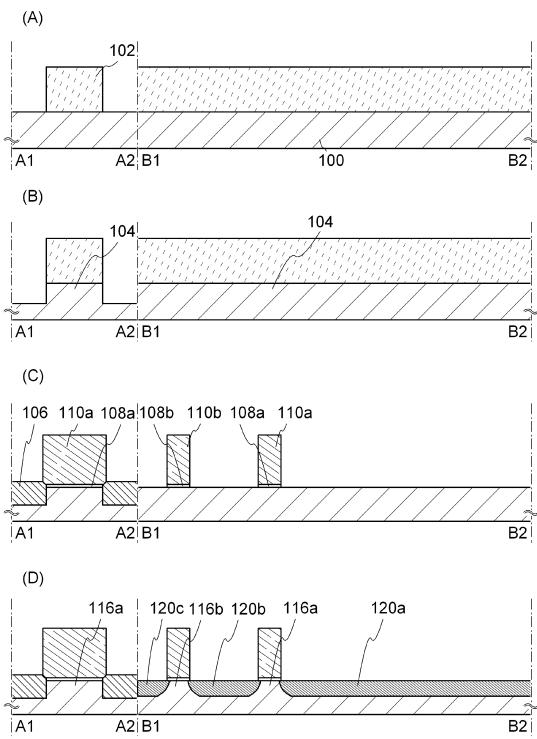

次に、上記半導体装置の作製方法の一例について説明する。以下では、はじめに下部のトランジスタ160およびトランジスタ166の作製方法について図12および図13を参照して説明し、その後、上部のトランジスタ162および容量素子168の作製方法について図14および図15を参照して説明する。

【0131】

下部のトランジスタの作製方法

まず、半導体材料を含む基板100を用意する（図12（A）参照）。半導体材料を含む基板100としては、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することができる。ここでは、半導体材料を含む基板100として、単結晶シリコン基板を用いる場合の一例について示すものとする。なお、一般に「SOI基板」は、絶縁表面上にシリコン半導体層が設けられた構成の基板をいうが、本明細書等においては、絶縁表面上にシリコン以外の材料からなる半導体層が設けられた構成の基板も含む概念として用いる。つまり、「SOI基板」が有する半導体層は、シリコン半導体層に限定されない。また、SOI基板には、ガラス基板などの絶縁基板上に絶縁層を介して半導体層が設けられた構成のものが含まれるものとする。

【0132】

半導体材料を含む基板100として、特に、シリコンなどの単結晶半導体基板を用いる場合には、半導体装置の読み出し動作を高速化することができるため好適である。

【0133】

10

20

30

40

50

基板 100 上には、素子分離絶縁層を形成するためのマスクとなる保護層 102 を形成する（図 12 (A) 参照）。保護層 102 としては、例えば、酸化シリコンや窒化シリコン、酸窒化シリコンなどを材料とする絶縁層を用いることができる。なお、この工程の前後において、トランジスタのしきい値電圧を制御するために、n 型の導電性を付与する不純物元素や p 型の導電性を付与する不純物元素を基板 100 に添加してもよい。半導体がシリコンの場合、n 型の導電性を付与する不純物としては、例えば、リンや砒素などを用いることができる。また、p 型の導電性を付与する不純物としては、例えば、硼素、アルミニウム、ガリウムなどを用いることができる。

【 0134 】

次に、上記の保護層 102 をマスクとしてエッティングを行い、保護層 102 に覆われていない領域（露出している領域）の、基板 100 の一部を除去する。これにより他の半導体領域と分離された半導体領域 104 が形成される（図 12 (B) 参照）。当該エッティングには、ドライエッティングを用いるのが好適であるが、ウェットエッティングを用いても良い。エッティングガスやエッティング液については被エッティング材料に応じて適宜選択することができる。

【 0135 】

次に、半導体領域 104 を覆うように絶縁層を形成し、半導体領域 104 に重畠する領域の絶縁層を選択的に除去することで、素子分離絶縁層 106 を形成する（図 12 (C) 参照）。当該絶縁層は、酸化シリコンや窒化シリコン、酸窒化シリコンなどを用いて形成される。絶縁層の除去方法としては、C M P（化学的機械的研磨）などの研磨処理やエッティング処理などがあるが、そのいずれを用いても良い。なお、半導体領域 104 の形成後、または、素子分離絶縁層 106 の形成後には、上記保護層 102 を除去する。

【 0136 】

次に、半導体領域 104 の表面に絶縁層を形成し、当該絶縁層上に導電材料を含む層を形成する。

【 0137 】

絶縁層は後のゲート絶縁層となるものであり、例えば、半導体領域 104 表面の熱処理（熱酸化処理や熱窒化処理など）によって形成することができる。熱処理に代えて、高密度プラズマ処理を適用しても良い。高密度プラズマ処理は、例えば、He、Ar、Kr、Xe などの希ガス、酸素、酸化窒素、アンモニア、窒素、水素などの混合ガスを用いて行うことができる。もちろん、C V D 法やスパッタリング法等を用いて絶縁層を形成しても良い。当該絶縁層は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0$ 、 $y > 0$ ))、窒素が添加されたハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0$ 、 $y > 0$ )) 等を含む単層構造または積層構造とすることが望ましい。また、絶縁層の厚さは、例えば、1 nm 以上 100 nm 以下、好ましくは 10 nm 以上 50 nm 以下とすることができる。

【 0138 】

導電材料を含む層は、アルミニウムや銅、チタン、タンタル、タングステン等の金属材料を用いて形成することができる。また、多結晶シリコンなどの半導体材料を用いて、導電材料を含む層を形成しても良い。形成方法も特に限定されず、蒸着法、C V D 法、スパッタリング法、スピノコート法などの各種成膜方法を用いることができる。なお、本実施の形態では、導電材料を含む層を、金属材料を用いて形成する場合の一例について示すものとする。

【 0139 】

その後、絶縁層および導電材料を含む層を選択的にエッティングして、ゲート絶縁層 108 a、ゲート絶縁層 108 b、ゲート電極 110 a およびゲート電極 110 b を形成する（図 12 (C) 参照）。

【 0140 】

10

20

30

40

50

次に、半導体領域 104 にリン (P) やヒ素 (As) などを添加して、チャネル形成領域 116a、チャネル形成領域 116b および不純物領域 120a 乃至不純物領域 120c を形成する (図 12 (D) 参照)。なお、ここでは n 型トランジスタを形成するためにリンやヒ素を添加しているが、p 型トランジスタを形成する場合には、硼素 (B) やアルミニウム (Al) などの不純物元素を添加すればよい。ここで、添加する不純物の濃度は適宜設定することができるが、半導体素子が高度に微細化される場合には、その濃度を高くすることが望ましい。

#### 【0141】

なお、ゲート電極 110a およびゲート電極 110b の周囲にサイドウォール絶縁層を形成して、不純物元素が異なる濃度で添加された不純物領域を形成しても良い。

10

#### 【0142】

次に、ゲート電極 110a およびゲート電極 110b、不純物領域 120a 乃至不純物領域 120c 等を覆うように金属層 122 を形成する (図 13 (A) 参照)。当該金属層 122 は、真空蒸着法やスパッタリング法、スピンドル法などの各種成膜方法を用いて形成することができる。金属層 122 は、半導体領域 104 を構成する半導体材料と反応することによって低抵抗な金属化合物となる金属材料を用いて形成することが望ましい。このような金属材料としては、例えば、チタン、タンタル、タンクスチール、ニッケル、コバルト、白金等がある。

#### 【0143】

次に、熱処理を施して、上記金属層 122 と半導体材料とを反応させる。これにより、不純物領域 120a 乃至不純物領域 120c に接する金属化合物領域 124a 乃至金属化合物領域 124c が形成される (図 13 (A) 参照)。なお、ゲート電極 110a およびゲート電極 110b として多結晶シリコンなどを用いる場合には、ゲート電極 110a およびゲート電極 110b の金属層 122 と接触する部分にも、金属化合物領域が形成されることになる。

20

#### 【0144】

上記熱処理としては、例えば、フラッシュランプの照射による熱処理を用いることができる。もちろん、その他の熱処理方法を用いても良いが、金属化合物の形成に係る化学反応の制御性を向上させるためには、ごく短時間の熱処理を実現できる方法を用いることが望ましい。なお、上記の金属化合物領域は、金属材料と半導体材料との反応により形成されるものであり、十分に導電性が高められた領域である。当該金属化合物領域を形成することで、電気抵抗を十分に低減し、素子特性を向上させることができる。なお、金属化合物領域 124a 乃至金属化合物領域 124c を形成した後には、金属層 122 は除去する。

30

#### 【0145】

次に、上述の工程により形成された各構成を覆うように、絶縁層 130 を形成する (図 13 (B) 参照)。絶縁層 130 は、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。特に、絶縁層 130 に誘電率の低い (low-k) 材料を用いることで、各種電極や配線の重なりに起因する容量を十分に低減することが可能になるため好ましい。なお、絶縁層 130 には、これらの材料を用いた多孔性の絶縁層を適用しても良い。多孔性の絶縁層では、密度の高い絶縁層と比較して誘電率が低下するため、電極や配線に起因する容量をさらに低減することが可能である。また、絶縁層 130 は、ポリイミド、アクリル等の有機絶縁材料を用いて形成することも可能である。なお、絶縁層 130 は単層の構造としても良いし、2 層以上の積層構造としても良い。

40

#### 【0146】

以上により、半導体材料を含む基板 100 を用いたトランジスタ 160 およびトランジスタ 166 が形成される (図 13 (B) 参照)。このようなトランジスタ 160 およびトランジスタ 166 は、高速動作が可能であるという特徴を有する。このため、当該トランジスタを読み出し用のトランジスタおよび読み出し時のメモリセル選択用のトランジスタとして用いることで、情報の読み出しを高速に行うことができる。

50

## 【0147】

その後、トランジスタ162および容量素子168の形成前の処理として、絶縁層130にCMP処理を施して、ゲート電極110aおよびゲート電極110bの上面を露出させる(図13(C)参照)。ゲート電極110aおよびゲート電極110bの上面を露出させる処理としては、CMP処理の他にエッティング処理などを適用することも可能であるが、トランジスタ162の特性を向上させるために、絶縁層130の表面は可能な限り平坦にしておくことが望ましい。

## 【0148】

なお、上記の各工程の前後には、さらに電極や配線、半導体層、絶縁層などを形成する工程を含んでいても良い。例えば、配線の構造として、絶縁層および導電層の積層構造である多層配線構造を採用して、高度に集積化した半導体装置を実現することも可能である。

10

## 【0149】

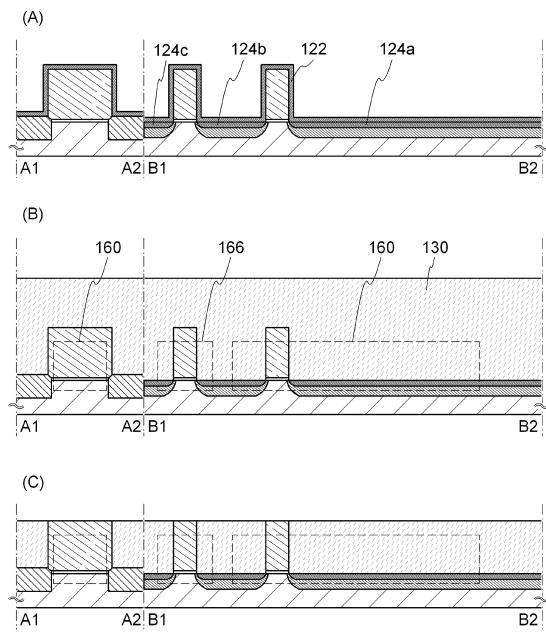

## 上部のトランジスタの作製方法

次に、ゲート電極110aおよびゲート電極110b、絶縁層130などの上に導電層を形成し、該導電層を選択的にエッティングして、ソース電極142a、ドレイン電極142bおよび導電層142cを形成する(図14(A)参照)。

## 【0150】

導電層は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形成することができる。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。

20

## 【0151】

導電層は、単層構造であっても良いし、2層以上の積層構造としてもよい。例えば、チタン膜や窒化チタン膜の単層構造、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜が積層された2層構造、窒化チタン膜上にチタン膜が積層された2層構造、チタン膜とアルミニウム膜とチタン膜とが積層された3層構造などが挙げられる。なお、導電層を、チタン膜や窒化チタン膜の単層構造とする場合には、テーパー形状を有するソース電極142aおよびドレイン電極142bへの加工が容易であるというメリットがある。

30

## 【0152】

また、導電層は、導電性の金属酸化物を用いて形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ合金( $In_2O_3 - SnO_2$ 、ITOと略記する場合がある)、酸化インジウム酸化亜鉛合金( $In_2O_3 - ZnO$ )、または、これらの金属酸化物材料にシリコン若しくは酸化シリコンを含有させたものを用いることができる。

## 【0153】

導電層のエッティングは、形成されるソース電極142aおよびドレイン電極142bの端部が、テーパー形状となるように行なうことが好ましい。ここで、テーパー角は、例えば、 $30^\circ$ 以上 $60^\circ$ 以下であることが好ましい。ソース電極142aおよびドレイン電極142bの端部をテーパー形状となるようにエッティングすることにより、後に形成されるゲート絶縁層146の被覆性を向上し、段切れを防止することができる。

40

## 【0154】

上部のトランジスタのチャネル長( $L$ )は、ソース電極142aおよびドレイン電極142bの下端部の間隔によって決定される。なお、チャネル長( $L$ )が $25\text{nm}$ 未満のトランジスタを形成する場合に用いるマスク形成の露光を行う際には、数 $\text{nm}$ ～数 $10\text{nm}$ と波長の短い超紫外線( $extreme\ ultraviolet$ )を用いるのが望ましい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長( $L$ )を、 $10\text{nm}$ 以上 $1000\text{nm}$ ( $1\mu\text{m}$ )以下とすることも

50

可能であり、回路の動作速度を高めることができるものである。また、微細化によって、半導体装置の消費電力を低減することも可能である。

【0155】

なお、ゲート電極110b上に導電層142cを設けるようにすることにより、導電層のエッティングの際に、ゲート電極110bが同時にエッティングされることを防ぐことができる。

【0156】

なお、絶縁層130の上には、下地として機能する絶縁層を設けても良い。当該絶縁層は、PVD法やCVD法などを用いて形成することができる。

【0157】

次に、ソース電極142a、およびドレイン電極142bを覆うように酸化物半導体層を形成した後、当該酸化物半導体層を選択的にエッティングして酸化物半導体層144を形成する(図14(B)参照)。

【0158】

酸化物半導体層は、四元系金属酸化物であるIn-Sn-Ga-Zn-O系や、三元系金属酸化物であるIn-Ga-Zn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系や、二元系金属酸化物であるIn-Zn-O系、Sn-Zn-O系、Al-Zn-O系、Zn-Mg-O系、Sn-Mg-O系、In-Mg-O系、In-Ga-O系や、単元系金属酸化物であるIn-O系、Sn-O系、Zn-O系などを用いて形成することができる。また、上記酸化物半導体にInとGaとSnとZn以外の元素、例えばSiO<sub>2</sub>を含ませてもよい。

【0159】

中でも、In-Ga-Zn-O系の酸化物半導体材料は、無電界時の抵抗が十分に高くオフ電流を十分に小さくすることが可能であり、また、電界効果移動度も高いため、半導体装置に用いる半導体材料としては好適である。

【0160】

In-Ga-Zn-O系の酸化物半導体材料の代表例としては、InGaO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)で表記されるものがある。また、Gaに代えてMを用い、InMO<sub>3</sub>(ZnO)<sub>m</sub>(m>0)のように表記される酸化物半導体材料がある。ここで、Mは、ガリウム(Ga)、アルミニウム(Al)、鉄(Fe)、ニッケル(Ni)、マンガン(Mn)、コバルト(Co)などから選ばれた一の金属元素または複数の金属元素を示す。例えば、Mとしては、Ga、GaおよびAl、GaおよびFe、GaおよびNi、GaおよびMn、GaおよびCoなどを適用することができる。なお、上述の組成は結晶構造から導き出されるものであり、あくまでも一例に過ぎないことを付記する。

【0161】

酸化物半導体層をスパッタ法で作製するためのターゲットとしては、In:Ga:Zn=1:x:y(xは0以上、yは0.5以上5以下)の組成比で表されるものを用いるのが好適である。例えば、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:2[mol数比](x=1、y=1)の組成比を有するターゲットなどを用いることができる。また、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1[mol数比](x=1、y=0.5)の組成比を有するターゲットや、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:4[mol数比](x=1、y=2)の組成比を有するターゲットや、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:0:2[mol数比](x=0、y=1)の組成比を有するターゲットを用いることもできる。

【0162】

また、酸化物半導体としてIn-Zn-O系の材料を用いる場合、用いるターゲットの組成比は、原子数比で、In:Zn=50:1~1:2(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO=25:1~1:4)、好ましくはIn:Zn=20:1~1:1(モル数比に換算するとIn<sub>2</sub>O<sub>3</sub>:ZnO=10:1~1:2)、さらに好ましくはIn:Zn=1

10

20

30

40

50

5 : 1 ~ 1 . 5 : 1 (モル数比に換算すると  $In_2O_3 : ZnO = 15 : 2 \sim 3 : 4$  ) とする。例えば、  $In - Zn - O$  系酸化物半導体の形成に用いるターゲットは、原子数比が  $In : Zn : O = X : Y : Z$  のとき、  $Z > 1 . 5 X + Y$  とする。

#### 【0163】

本実施の形態では、酸化物半導体層を、  $In - Ga - Zn - O$  系の金属酸化物ターゲットを用いるスパッタ法により形成することとする。

#### 【0164】

金属酸化物ターゲット中の金属酸化物の相対密度は 80 % 以上、好ましくは 95 % 以上、さらに好ましくは 99 . 9 % 以上である。相対密度の高い金属酸化物ターゲットを用いることにより、緻密な構造の酸化物半導体層を形成することが可能である。

10

#### 【0165】

酸化物半導体層の形成雰囲気は、希ガス (代表的にはアルゴン) 雰囲気、酸素雰囲気、または、希ガス (代表的にはアルゴン) と酸素との混合雰囲気とするのが好適である。具体的には、例えば、水素、水、水酸基、水素化物などの不純物が、濃度 1 ppm 以下 (望ましくは濃度 10 ppb 以下) にまで除去された高純度ガス雰囲気を用いるのが好適である。

#### 【0166】

酸化物半導体層の形成の際には、例えば、減圧状態に保持された処理室内に被処理物を保持し、被処理物の温度が 100 以上 550 未満、好ましくは 200 以上 400 以下となるように被処理物を熱する。または、酸化物半導体層の形成の際の被処理物の温度は、室温 (25 ± 10) としてもよい。そして、処理室内の水分を除去しつつ、水素や水などが除去されたスパッタガスを導入し、上記ターゲットを用いて酸化物半導体層を形成する。被処理物を熱しながら酸化物半導体層を形成することにより、酸化物半導体層に含まれる不純物を低減することができる。また、スパッタによる損傷を軽減することができる。処理室内の水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプなどを用いることができる。また、ターボポンプにコールドトラップを加えたものを用いてもよい。クライオポンプなどを用いて排気することで、処理室から水素や水などを除去することができるため、酸化物半導体層中の不純物濃度を低減できる。

20

#### 【0167】

酸化物半導体層の形成条件としては、例えば、被処理物とターゲットの間との距離が 170 mm、圧力が 0 . 4 Pa、直流 (DC) 電力が 0 . 5 kW、雰囲気が酸素 (酸素 100 %) 雰囲気、またはアルゴン (アルゴン 100 %) 雰囲気、または酸素とアルゴンの混合雰囲気、といった条件を適用することができる。なお、パルス直流 (DC) 電源を用いると、ごみ (成膜時に形成される粉状の物質など) を低減でき、膜厚分布も均一となるため好ましい。酸化物半導体層の厚さは、1 nm 以上 50 nm 以下、好ましくは 1 nm 以上 30 nm 以下、より好ましくは 1 nm 以上 10 nm 以下とする。このような厚さの酸化物半導体層を用いることで、微細化に伴う短チャネル効果を抑制することができる。ただし、適用する酸化物半導体材料や、半導体装置の用途などにより適切な厚さは異なるから、その厚さは、用いる材料や用途などに応じて選択することもできる。

40

#### 【0168】

なお、酸化物半導体層をスパッタ法により形成する前には、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、形成表面 (例えば絶縁層 130 の表面) の付着物を除去するのが好適である。ここで、逆スパッタとは、通常のスパッタにおいては、スパッタターゲットにイオンを衝突させるところを、逆に、処理表面にイオンを衝突させることによってその表面を改質する方法のことをいう。処理表面にイオンを衝突させる方法としては、アルゴン雰囲気下で処理表面側に高周波電圧を印加して、被処理物付近にプラズマを生成する方法などがある。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などによる雰囲気を適用してもよい。

#### 【0169】

50

その後、酸化物半導体層に対して、熱処理（第1の熱処理）を行うことが望ましい。この第1の熱処理によって酸化物半導体層中の、過剰な水素（水や水酸基を含む）を除去し、酸化物半導体層の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。第1の熱処理の温度は、例えば、300以上550未満、または400以上500以下とする。

【0170】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450、1時間の条件で行うことができる。この間、酸化物半導体層は大気に触れさせず、水や水素の混入が生じないようにする。

【0171】

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、G R T A ( G a s R a p i d T h e r m a l A n n e a l ) 装置、L R T A ( L a m p R a p i d T h e r m a l A n n e a l ) 装置等のR T A ( R a p i d T h e r m a l A n n e a l ) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。

【0172】

例えば、第1の熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出すG R T A 処理を行ってもよい。G R T A 処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えるても良い。酸素を含む雰囲気において第1の熱処理を行うことで、酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減することができるためである。

【0173】

なお、不活性ガス雰囲気としては、窒素、または希ガス（ヘリウム、ネオン、アルゴン等）を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N（99.9999%）以上、好ましくは7N（99.9999%）以上（すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下）とする。

【0174】

いずれにしても、第1の熱処理によって不純物を低減し、i型（真性半導体）またはi型に限りなく近い酸化物半導体層を形成することで、極めて優れた特性のトランジスタを実現することができる。

【0175】

ところで、上述の熱処理（第1の熱処理）には水素や水などを除去する効果があるから、当該熱処理を、脱水化処理や、脱水素化処理などと呼ぶこともできる。当該脱水化処理や、脱水素化処理は、酸化物半導体層の形成後やゲート絶縁層の形成後、ゲート電極の形成後、などのタイミングにおいて行うことも可能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても良い。

【0176】

酸化物半導体層のエッティングは、上記熱処理の前、または上記熱処理の後のいずれにおいて行っても良い。また、素子の微細化という観点からはドライエッティングを用いるのが好適であるが、ウェットエッティングを用いても良い。エッティングガスやエッティング液については被エッティング材料に応じて適宜選択することができる。なお、素子におけるリークなどが問題とならない場合には、酸化物半導体層を島状に加工しないで用いても良い。

10

20

30

40

50

## 【0177】

次に、酸化物半導体層144に接するゲート絶縁層146を形成し、その後、ゲート絶縁層146上において酸化物半導体層144と重畠する領域にゲート電極148aを形成し、ソース電極142aと重畠する領域に電極148bを形成する(図14(C)参照)。

## 【0178】

ゲート絶縁層146は、CVD法やスパッタ法等を用いて形成することができる。また、ゲート絶縁層146は、酸化シリコン、窒化シリコン、酸窒化シリコン、酸化アルミニウム、酸化タンタル、酸化ハフニウム、酸化イットリウム、酸化ガリウム、ハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムアルミネート( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、などを含むように形成するのが好適である。ゲート絶縁層146は、単層構造としても良いし、積層構造としても良い。また、その厚さは特に限定されないが、半導体装置を微細化する場合には、トランジスタの動作を確保するために薄くするのが望ましい。例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

10

## 【0179】

しかし、ゲート絶縁層を薄くすると、トンネル効果などに起因するゲートリークが問題となる。ゲートリークの問題を解消するには、ゲート絶縁層146に、酸化ハフニウム、酸化タンタル、酸化イットリウム、ハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート( $HfSi_xO_y$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムアルミネート( $HfAl_xO_y$  ( $x > 0$ ,  $y > 0$ ))、などの高誘電率(high-k)材料を用いると良い。high-k材料をゲート絶縁層146に用いることで、電気的特性を確保しつつ、ゲートリークを抑制するために膜厚を大きくすることが可能になる。なお、high-k材料を含む膜と、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウムなどのいずれかを含む膜との積層構造としてもよい。

20

## 【0180】

ゲート絶縁層146の形成後には、不活性ガス雰囲気下、または酸素雰囲気下で第2の熱処理を行うのが望ましい。熱処理の温度は、200以上450以下、好ましくは250以上350以下である。例えば、窒素雰囲気下で250、1時間の熱処理を行えばよい。第2の熱処理を行うことによって、トランジスタの電気的特性のばらつきを軽減することができる。また、ゲート絶縁層146が酸素を含む場合、酸化物半導体層144に酸素を供給し、該酸化物半導体層144の酸素欠損を補填して、i型(真性半導体)またはi型に限りなく近い酸化物半導体層を形成することもできる。

30

## 【0181】

なお、本実施の形態では、ゲート絶縁層146の形成後に第2の熱処理を行っているが、第2の熱処理のタイミングはこれに限定されない。例えば、ゲート電極の形成後に第2の熱処理を行っても良い。また、第1の熱処理に続けて第2の熱処理を行っても良いし、第1の熱処理に第2の熱処理を兼ねさせてても良いし、第2の熱処理に第1の熱処理を兼ねさせてても良い。

40

## 【0182】

上述のように、第1の熱処理と第2の熱処理の少なくとも一方を適用することで、酸化物半導体層144を、その主成分以外の不純物が極力含まれないように高純度化することができる。

## 【0183】

ゲート電極148aおよび電極148bは、ゲート絶縁層146上に導電層を形成した後に、当該導電層を選択的にエッチングすることによって形成することができる。ゲート電極148aおよび電極148bとなる導電層は、スパッタ法をはじめとするPVD法や、プラズマCVD法などのCVD法を用いて形成することができる。詳細は、ソース電極142aなどの場合と同様であり、これらの記載を参照できる。

50

**【 0 1 8 4 】**

次に、ゲート絶縁層 146、ゲート電極 148a、および電極 148b 上に、絶縁層 150 および絶縁層 152 を形成する（図 15（A）参照）。絶縁層 150 および絶縁層 152 は、PVD 法や CVD 法などを用いて形成することができる。また、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム等の無機絶縁材料を含む材料を用いて形成することができる。

**【 0 1 8 5 】**

なお、絶縁層 150 や絶縁層 152 には、誘電率の低い材料や、誘電率の低い構造（多孔性の構造など）を用いることが望ましい。絶縁層 150 や絶縁層 152 の誘電率を低くすることにより、配線や電極などの間に生じる容量を低減し、動作の高速化を図ることができるためである。

10

**【 0 1 8 6 】**

なお、本実施の形態では、絶縁層 150 と絶縁層 152 の積層構造としているが、開示する発明の一態様はこれに限定されない。1 層としても良いし、3 層以上の積層構造としても良い。また、絶縁層を設けない構成とすることも可能である。

**【 0 1 8 7 】**

なお、上記絶縁層 152 は、その表面が平坦になるように形成することが望ましい。表面が平坦になるように絶縁層 152 を形成することで、半導体装置を微細化した場合などにおいても、絶縁層 152 上に、電極や配線などを好適に形成することができるためである。なお、絶縁層 152 の平坦化は、CMP（化学的機械的研磨）などの方法を用いて行うことができる。

20

**【 0 1 8 8 】**

次に、ゲート絶縁層 146、絶縁層 150、絶縁層 152 に、ドレイン電極 142b にまで達する開口を形成する（図 15（B）参照）。当該開口の形成は、マスクなどを用いた選択的なエッチングにより行われる。

**【 0 1 8 9 】**

その後、上記開口に電極 154 を形成し、絶縁層 152 上に電極 154 に接する配線 156 を形成する（図 15（C）参照）。

**【 0 1 9 0 】**

電極 154 は、例えば、開口を含む領域に PVD 法や CVD 法などを用いて導電層を形成した後、エッチング処理や CMP といった方法を用いて、上記導電層の一部を除去することにより形成することができる。

30

**【 0 1 9 1 】**

より具体的には、例えば、開口を含む領域に PVD 法によりチタン膜を薄く形成し、CVD 法により窒化チタン膜を薄く形成した後に、開口に埋め込むようにタンゲステン膜を形成する方法を適用することができる。ここで、PVD 法により形成されるチタン膜は、被形成面の酸化膜（自然酸化膜など）を還元し、下部電極など（ここではドレイン電極 142b）との接触抵抗を低減させる機能を有する。また、その後に形成される窒化チタン膜は、導電性材料の拡散を抑制するバリア機能を備える。また、チタンや窒化チタンなどによるバリア膜を形成した後に、メッキ法により銅膜を形成してもよい。

40

**【 0 1 9 2 】**

なお、上記導電層の一部を除去して電極 154 を形成する際には、その表面が平坦になるように加工することが望ましい。例えば、開口を含む領域にチタン膜や窒化チタン膜を薄く形成した後に、開口に埋め込むようにタンゲステン膜を形成する場合には、その後の CMP 処理によって、不要なタンゲステン、チタン、窒化チタンなどを除去すると共に、その表面の平坦性を向上させることができる。このように、電極 154 を含む表面を平坦化することにより、後の工程において、良好な電極、配線、絶縁層、半導体層などを形成することが可能となる。

**【 0 1 9 3 】**

配線 156 は、スパッタ法をはじめとする PVD 法や、プラズマ CVD 法などの CVD 法

50

を用いて導電層を形成した後、当該導電層をパターニングすることによって形成される。また、導電層の材料としては、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンゲステンから選ばれた元素や、上述した元素を成分とする合金等を用いることができる。マンガン、マグネシウム、ジルコニウム、ベリリウム、ネオジム、スカンジウムのいずれか、またはこれらを複数組み合わせた材料を用いてもよい。詳細は、ソース電極 142a などと同様である。

#### 【0194】

以上により、高純度化された酸化物半導体層 144 を用いたトランジスタ 162 、および容量素子 168 が完成する（図 15 (C) 参照）。

#### 【0195】

本実施の形態において示すトランジスタ 162 では、酸化物半導体層 144 が高純度化されているため、その水素濃度は、 $5 \times 10^{-9}$  atoms / cm<sup>3</sup> 以下、望ましくは $5 \times 10^{-8}$  atoms / cm<sup>3</sup> 以下、より望ましくは $5 \times 10^{-7}$  atoms / cm<sup>3</sup> 以下である。また、酸化物半導体層 144 のキャリア密度は、一般的なシリコンウェハにおけるキャリア密度（ $1 \times 10^{14}$  / cm<sup>3</sup> 程度）と比較して、十分に小さい値（例えば、 $1 \times 10^{12}$  / cm<sup>3</sup> 未満、より好ましくは、 $1.45 \times 10^{10}$  / cm<sup>3</sup> 未満）をとる。そして、トランジスタ 162 のオフ電流も十分に小さくなる。例えば、トランジスタ 162 の室温（25℃）でのオフ電流（ここでは、単位チャネル幅（1 μm）あたりの値）は 100 zA (1 zA (ゼプトアンペア) は  $1 \times 10^{-21}$  A) 以下、好ましくは 10 zA 以下、より好ましくは 1 zA 以下、さらに好ましくは 100 yA 以下とすることができる。また、トランジスタ 162 のオフ電流は、低ければ低いほどよいが、トランジスタ 162 のオフ電流の下限値は  $10^{-30}$  A であると見積もられる。

#### 【0196】

このように高純度化され、真性化された酸化物半導体層 144 を用いることで、トランジスタのオフ電流を十分に低減することが容易になる。そして、このようなトランジスタを用いることで、極めて長期にわたり記憶内容を保持することが可能な半導体装置が得られる。

#### 【0197】

以上、本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0198】

##### （実施の形態 3）

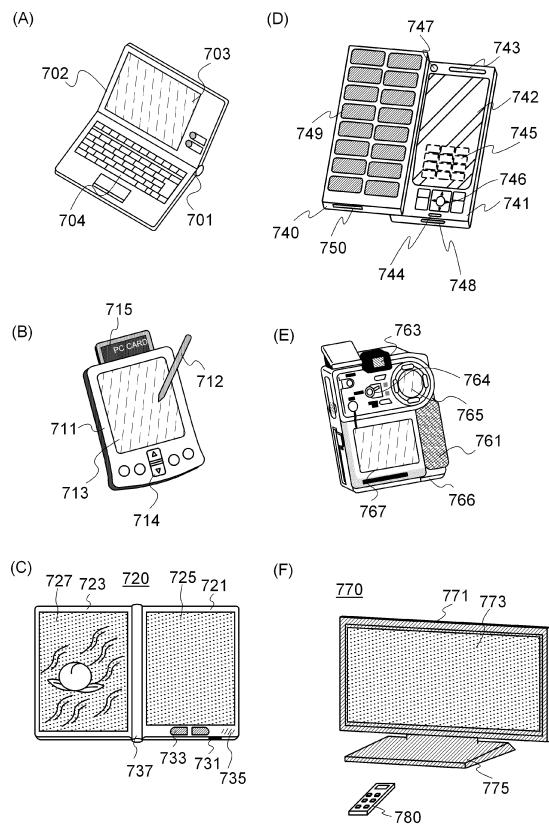

本実施の形態では、上述の実施の形態で説明した半導体装置を電子機器に適用する場合について、図 17 を用いて説明する。本実施の形態では、コンピュータ、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯情報端末（携帯型ゲーム機、音響再生装置なども含む）、デジタルカメラ、デジタルビデオカメラ、電子ペーパー、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）などの電子機器に、上述の半導体装置を適用する場合について説明する。

#### 【0199】

図 17 (A) は、ノート型のパーソナルコンピュータであり、筐体 701 、筐体 702 、表示部 703 、キーボード 704 などによって構成されている。筐体 701 と筐体 702 の少なくとも一には、先の実施の形態に示す半導体装置が設けられている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減されたノート型のパーソナルコンピュータが実現される。

#### 【0200】

図 17 (B) は、携帯情報端末 (PDA) であり、本体 711 には、表示部 713 と、外部インターフェイス 715 と、操作ボタン 714 等が設けられている。また、携帯情報端末を操作するスティラス 712 などを備えている。本体 711 内には、先の実施の形態に示す半導体装置が設けられている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された携帯情報端末が実現される

10

20

30

40

50

。

## 【0201】

図17(C)は、電子ペーパーを実装した電子書籍であり、電子書籍720は、筐体721と筐体723の2つの筐体で構成されている。筐体721および筐体723には、それぞれ表示部725および表示部727が設けられている。筐体721と筐体723は、軸部737により接続されており、該軸部737を軸として開閉動作を行うことができる。また、筐体721は、電源731、操作キー733、スピーカー735などを備えている。筐体721、筐体723の少なくとも一には、先の実施の形態に示す半導体装置が設けられている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された電子書籍が実現される。

10

## 【0202】

図17(D)は、携帯電話機であり、筐体740と筐体741の2つの筐体で構成されている。さらに、筐体740と筐体741は、スライドし、図17(D)のように展開している状態から重なり合った状態とすることができる、携帯に適した小型化が可能である。また、筐体741は、表示パネル742、スピーカー743、マイクロフォン744、ポイントティングデバイス746、カメラ用レンズ747、外部接続端子748などを備えている。また、筐体740は、携帯電話機の充電を行う太陽電池セル749、外部メモリスロット750などを備えている。ここで、表示パネル742はタッチパネル機能を備えており、図17(D)には映像表示されている複数の操作キー745を点線で示している。また、アンテナは、筐体741に内蔵されている。筐体740と筐体741の少なくとも一には、先の実施の形態に示す半導体装置が設けられている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された携帯電話機が実現される。

20

## 【0203】

図17(E)は、デジタルカメラであり、本体761、表示部767、接眼部763、操作スイッチ764、表示部765、バッテリー766などによって構成されている。本体761内には、先の実施の形態に示す半導体装置が設けられている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減されたデジタルカメラが実現される。

30

## 【0204】

図17(F)は、テレビジョン装置であり、テレビジョン装置770は、筐体771、表示部773、スタンド775などで構成されている。テレビジョン装置770の操作は、筐体771が備えるスイッチや、リモコン操作機780により行うことができる。筐体771およびリモコン操作機780には、先の実施の形態に示す半導体装置が搭載されている。そのため、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減されたテレビジョン装置が実現される。

## 【0205】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭載されている。このため、消費電力を低減した電子機器が実現される。

## 【実施例1】

40

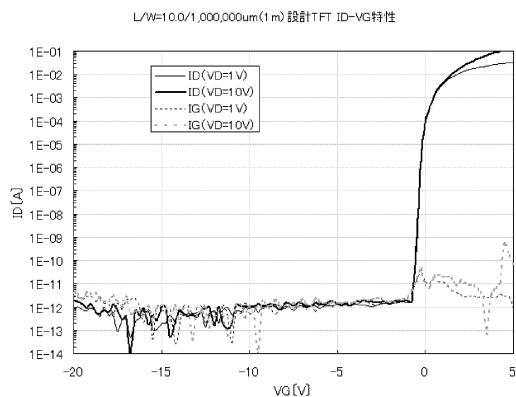

## 【0206】

本実施例では、高純度化された酸化物半導体を用いたトランジスタのオフ電流を求めた結果について説明する。

## 【0207】

まず、高純度化された酸化物半導体を用いたトランジスタのオフ電流が十分に小さいことを考慮して、チャネル幅Wが1mと十分に大きいトランジスタを用意してオフ電流の測定を行った。チャネル幅Wが1mのトランジスタのオフ電流を測定した結果を図18に示す。図18において、横軸はゲート電圧VG、縦軸はドレイン電流IDである。ドレイン電圧VDが+1Vまたは+10Vの場合、ゲート電圧VGが-5Vから-20Vの範囲では、トランジスタのオフ電流は、検出限界である $1 \times 10^{-12} A$ 以下であることがわかつ

50

た。また、トランジスタのオフ電流（ここでは、単位チャネル幅（ $1 \mu m$ ）あたりの値）は $1 aA / \mu m$  ( $1 \times 10^{-18} A / \mu m$ ) 以下となることがわかった。

#### 【0208】

次に、高純度化された酸化物半導体を用いたトランジスタのオフ電流をさらに正確に求めた結果について説明する。上述したように、高純度化された酸化物半導体を用いたトランジスタのオフ電流は、測定器の検出限界である $1 \times 10^{-12} A$  以下であることがわかった。そこで、特性評価用素子を作製し、より正確なオフ電流の値（上記測定における測定器の検出限界以下の値）を求めた結果について説明する。

#### 【0209】

はじめに、電流測定方法に用いた特性評価用素子について、図19を参照して説明する。

10

#### 【0210】

図19に示す特性評価用素子は、測定系800が3つ並列に接続されている。測定系800は、容量素子802、トランジスタ804、トランジスタ805、トランジスタ806、トランジスタ808を有する。トランジスタ804、トランジスタ805、トランジスタ806、トランジスタ808には、高純度化された酸化物半導体を用いたトランジスタを適用した。

#### 【0211】

測定系800において、トランジスタ804のソース端子およびドレイン端子の一方と、容量素子802の端子の一方と、トランジスタ805のソース端子およびドレイン端子の一方は、電源（V2を与える電源）に電気的に接続されている。また、トランジスタ804のソース端子およびドレイン端子の他方と、トランジスタ808のソース端子およびドレイン端子の一方と、容量素子802の端子の他方と、トランジスタ805のゲート端子とは、電気的に接続されている。また、トランジスタ808のソース端子およびドレイン端子の他方と、トランジスタ806のソース端子およびドレイン端子の一方と、トランジスタ806のゲート端子は、電源（V1を与える電源）に電気的に接続されている。また、トランジスタ805のソース端子およびドレイン端子の他方と、トランジスタ806のソース端子およびドレイン端子の他方とは、電気的に接続され、出力端子となっている。

20

#### 【0212】

なお、トランジスタ804のゲート端子には、トランジスタ804のオン状態と、オフ状態を制御する電位Vext\_b2が供給され、トランジスタ808のゲート端子には、トランジスタ808のオン状態と、オフ状態を制御する電位Vext\_b1が供給される。また、出力端子からは電位Voutが出力される。

30

#### 【0213】

次に、上記の特性評価用素子を用いた電流測定方法について説明する。

#### 【0214】

まず、オフ電流を測定するために電位差を付与する初期期間の概略について説明する。初期期間においては、トランジスタ808のゲート端子に、トランジスタ808をオン状態とする電位Vext\_b1を入力して、トランジスタ804のソース端子またはドレイン端子の他方と電気的に接続されるノード（つまり、トランジスタ808のソース端子およびドレイン端子の一方、容量素子802の端子の他方、およびトランジスタ805のゲート端子に電気的に接続されるノード）であるノードAに電位V1を与える。ここで、電位V1は、例えば高電位とする。また、トランジスタ804はオフ状態としておく。

40

#### 【0215】

その後、トランジスタ808のゲート端子に、トランジスタ808をオフ状態とする電位Vext\_b1を入力して、トランジスタ808をオフ状態とする。トランジスタ808をオフ状態とした後に、電位V1を低電位とする。ここでも、トランジスタ804はオフ状態としておく。また、電位V2は電位V1と同じ電位とする。以上により、初期期間が終了する。初期期間が終了した状態では、ノードAとトランジスタ804のソース端子及びドレイン端子の一方との間に電位差が生じ、また、ノードAとトランジスタ808のソース端子及びドレイン端子の他方との間に電位差が生じることになるため、トランジスタ

50

804 およびトランジスタ 808 には僅かに電荷が流れる。つまり、オフ電流が発生する。

【0216】

次に、オフ電流の測定期間の概略について説明する。測定期間においては、トランジスタ 804 のソース端子またはドレイン端子の一方の端子の電位（つまり  $V_2$ ）、および、トランジスタ 808 のソース端子またはドレイン端子の他方の端子の電位（つまり  $V_1$ ）は低電位に固定しておく。一方で、測定期間中は、上記ノード A の電位は固定しない（フローティング状態とする）。これにより、トランジスタ 804 に電荷が流れ、時間の経過と共にノード A に保持される電荷量が変動する。そして、ノード A に保持される電荷量の変動に伴って、ノード A の電位が変動する。つまり、出力端子の出力電位  $V_{out}$  も変動する。

10

【0217】

上記電位差を付与する初期期間、および、その後の測定期間における各電位の関係の詳細（タイミングチャート）を図 20 に示す。

【0218】

初期期間において、まず、電位  $V_{ext\_b2}$  を、トランジスタ 804 がオン状態となるような電位（高電位）とする。これによって、ノード A の電位は  $V_2$  すなわち低電位（ $V_{SS}$ ）となる。なお、ノード A に低電位（ $V_{SS}$ ）を与えるのは必須ではない。その後、電位  $V_{ext\_b2}$  を、トランジスタ 804 がオフ状態となるような電位（低電位）として、トランジスタ 804 をオフ状態とする。そして、次に、電位  $V_{ext\_b1}$  を、トランジスタ 808 がオン状態となるような電位（高電位）とする。これによって、ノード A の電位は  $V_1$ 、すなわち高電位（ $V_{DD}$ ）となる。その後、 $V_{ext\_b1}$  を、トランジスタ 808 がオフ状態となるような電位とする。これによって、ノード A がフローティング状態となり、初期期間が終了する。

20

【0219】

その後の測定期間においては、電位  $V_1$  および電位  $V_2$  を、ノード A に電荷が流れ込み、またはノード A から電荷が流れ出すような電位とする。ここでは、電位  $V_1$  および電位  $V_2$  を低電位（ $V_{SS}$ ）とする。ただし、出力電位  $V_{out}$  を測定するタイミングにおいては、出力回路を動作させる必要が生じるため、一時的に  $V_1$  を高電位（ $V_{DD}$ ）とすることがある。なお、 $V_1$  を高電位（ $V_{DD}$ ）とする期間は、測定に影響を与えない程度の短期間とする。

30

【0220】

上述のようにして電位差を与え、測定期間が開始されると、時間の経過と共にノード A に保持される電荷量が変動し、これに従ってノード A の電位が変動する。これは、トランジスタ 805 のゲート端子の電位が変動することを意味するから、時間の経過と共に、出力端子の出力電位  $V_{out}$  の電位も変化することとなる。

【0221】

得られた出力電位  $V_{out}$  から、オフ電流を算出する方法について、以下に説明する。

【0222】

オフ電流の算出に先だって、ノード A の電位  $V_A$  と、出力電位  $V_{out}$  との関係を求めておく。これにより、出力電位  $V_{out}$  からノード A の電位  $V_A$  を求めることができる。上述の関係から、ノード A の電位  $V_A$  は、出力電位  $V_{out}$  の関数として次式のように表すことができる。

40

【0223】

【数1】

$$V_A = F(V_{out})$$

【0224】

50

また、ノード A の電荷  $Q_A$  は、ノード A の電位  $V_A$ 、ノード A に接続される容量  $C_A$ 、定数 (const) を用いて、次式のように表される。ここで、ノード A に接続される容量  $C_A$  は、容量素子 802 の容量と他の容量の和である。

【0225】

【数2】

$$Q_A = C_A V_A + \text{const}$$

【0226】

10

ノード A の電流  $I_A$  は、ノード A に流れ込む電荷（またはノード A から流れ出る電荷）の時間微分であるから、ノード A の電流  $I_A$  は次式のように表される。

【0227】

【数3】

$$I_A = \frac{\Delta Q_A}{\Delta t} = \frac{C_A \cdot \Delta F(V_{out})}{\Delta t}$$

【0228】

20

このように、ノード A に接続される容量  $C_A$  と、出力端子の出力電位  $V_{out}$  から、ノード A の電流  $I_A$  を求めることができる。

【0229】

以上に示す方法により、オフ状態においてトランジスタのソースとドレイン間を流れるリーク電流（オフ電流）を測定することができる。

【0230】

本実施例では、チャネル長  $L = 10 \mu m$ 、チャネル幅  $W = 50 \mu m$  の、高純度化した酸化物半導体を用いてトランジスタ 804、トランジスタ 805、トランジスタ 806、トランジスタ 808 を作製した。また、並列された各測定系 800 において、容量素子 802 の各容量値を、100 fF、1 pF、3 pF とした。

30

【0231】

なお、本実施例に係る測定では、 $V_{DD} = 5 V$ 、 $V_{SS} = 0 V$  とした。また、測定期間ににおいては、電位  $V_1$  を原則として  $V_{SS}$  とし、10 sec から 300 sec の範囲ごとに、100 msec の期間だけ  $V_{DD}$  として  $V_{out}$  を測定した。また、素子に流れる電流  $I$  の算出に用いられる  $t$  は、約 30000 sec とした。

【0232】

図 21 に、上記電流測定に係る経過時間  $Time$  と、出力電位  $V_{out}$  との関係を示す。

図 21 より、時間の経過にしたがって、電位が変化している様子が確認できる。

【0233】

図 22 には、上記電流測定によって算出された室温（25）におけるオフ電流を示す。なお、図 22 は、ソース - ドレイン電圧  $V$  と、オフ電流  $I$  との関係を表すものである。図 22 から、ソース - ドレイン電圧が 4 V の条件において、オフ電流は約  $40 zA / \mu m$  であることが分かった。また、ソース - ドレイン電圧が 3.1 V の条件において、オフ電流は  $10 zA / \mu m$  以下であることが分かった。なお、 $1 zA$  は  $10^{-21} A$  を表す。

40

【0234】

さらに、上記電流測定によって算出された 85 の温度環境下におけるオフ電流について図 23 に示す。図 23 は、85 の温度環境下におけるソース - ドレイン電圧  $V$  と、オフ電流  $I$  との関係を表すものである。図 23 から、ソース - ドレイン電圧が 3.1 V の条件において、オフ電流は  $100 zA / \mu m$  以下であることが分かった。

【0235】

50

以上、本実施例により、高純度化された酸化物半導体を用いたトランジスタでは、オフ電流が十分に小さくなることが確認された。

【実施例 2】

【0236】

本実施例では、真性化された酸化物半導体を用いたトランジスタのオフ電流  $I_{off}$  を詳細に求めた結果について説明する。なお、計算には、sentaurus device (synopsys 社製 TCA D ソフト) を用いた。また、キャリア再結合モデルとして、SRH モデルおよび Auger 再結合モデルを用いた。

【0237】

計算に用いたトランジスタの構造は、図 24 のとおりである。図 24 に示すトランジスタ 562 は、絶縁層 543 (材質: 酸化珪素) と、ソース電極 542a およびドレイン電極 542b (材質: 窒化チタン) と、上記絶縁層 543 の上面、ソース電極 542a の上面、およびドレイン電極 542b の上面、の一部と接する酸化物半導体層 544 (材質: In-Ga-Zn-O 系の酸化物半導体、厚さ: 10 nm) と、酸化物半導体層 544 を覆うゲート絶縁層 546 (材質: 酸化ハフニウム、厚さ: 10 nm) と、ゲート絶縁層 546 上のゲート電極 548 (材質: タングステン) と、を有する。なお、酸化物半導体は i 型と仮定し、ドナー密度  $N_d$  と真性キャリア密度  $n_i$  が等しいという条件の元で計算を行った。

【0238】

チャネル長  $L$  としては、50 nm、500 nm の 2 条件を採用した。また、ソース電極 542a とドレイン電極 542b の間の電圧  $V_{ds}$  は、1 V とした。

【0239】

計算に用いたパラメータは以下の通りである。

1. In-Ga-Zn-O 系の酸化物半導体 (酸化物半導体層の材料)

バンドギャップ  $E_g$  : 3.15 eV、電子親和力 : 4.3 eV、比誘電率 : 15、電子移動度 : 10 cm<sup>2</sup> / Vs

2. 窒化チタン (ソース電極およびドレイン電極の材料)

仕事関数  $\phi_M$  : 3.9 eV

3. 酸化ハフニウム (ゲート絶縁層の材料)

比誘電率 : 15

4. タングステン (ゲート電極の材料)

仕事関数  $\phi_M$  : 4.9 eV

【0240】

計算結果を図 25 に示す。図 25 において、横軸はゲート電圧  $V_G$  (V) を、縦軸はドレイン電流  $I_D$  (A /  $\mu$ m) を、それぞれ示している。また、図中、太い線がチャネル長  $L = 500$  nm の計算結果、細い線がチャネル長  $L = 50$  nm の計算結果を、それぞれ示している。

【0241】

図 25 の計算結果により、チャネル長  $L = 50$  nm、500 nm の場合のいずれにおいても、オフ電流の下限値は  $10^{-2.9} \sim 10^{-3.0}$  (A /  $\mu$ m) と見積もられることがわかる。

【0242】

なお、本実施例においては、図 24 に示すトップゲート構造のトランジスタを用いて、真性化された酸化物半導体を用いたトランジスタのオフ電流を計算したが、ボトムゲート構造などの異なる構造のトランジスタにおいてもほぼ同様のオフ電流が得られる。

【符号の説明】

【0243】

100 基板

102 保護層

104 半導体領域

10

20

30

40

50

|         |                |    |

|---------|----------------|----|

| 1 0 6   | 素子分離絶縁層        |    |

| 1 0 8 a | ゲート絶縁層         |    |

| 1 0 8 b | ゲート絶縁層         |    |

| 1 1 0 a | ゲート電極          |    |

| 1 1 0 b | ゲート電極          |    |

| 1 1 6 a | チャネル形成領域       |    |

| 1 1 6 b | チャネル形成領域       |    |

| 1 2 0 a | 不純物領域          | 10 |

| 1 2 0 b | 不純物領域          |    |

| 1 2 0 c | 不純物領域          |    |

| 1 2 2   | 金属層            |    |

| 1 2 4 a | 金属化合物領域        |    |

| 1 2 4 b | 金属化合物領域        |    |

| 1 2 4 c | 金属化合物領域        |    |

| 1 3 0   | 絶縁層            |    |

| 1 4 2 a | ソース電極          |    |

| 1 4 2 b | ドレイン電極         |    |

| 1 4 2 c | 導電層            |    |

| 1 4 4   | 酸化物半導体層        |    |

| 1 4 6   | ゲート絶縁層         | 20 |

| 1 4 8 a | ゲート電極          |    |

| 1 4 8 b | 電極             |    |

| 1 5 0   | 絶縁層            |    |

| 1 5 2   | 絶縁層            |    |

| 1 5 4   | 電極             |    |

| 1 5 6   | 配線             |    |

| 1 6 0   | トランジスタ         |    |

| 1 6 2   | トランジスタ         |    |

| 1 6 6   | トランジスタ         |    |

| 1 6 8   | 容量素子           | 30 |

| 1 7 0   | メモリセル          |    |

| 1 8 0   | 電位変換回路         |    |

| 1 9 0   | 第1の駆動回路        |    |

| 1 9 2   | 第2の駆動回路        |    |

| 2 0 2   | 制御回路           |    |

| 2 0 4   | 遅延回路           |    |

| 2 0 6   | バッファ回路         |    |

| 2 0 8   | 読み出し回路         |    |

| 2 1 0   | デコーダ           |    |

| 2 1 2   | 制御回路           | 40 |

| 2 1 4   | 昇圧用レベルシフタ      |    |

| 2 1 6   | バッファ回路         |    |

| 2 1 8   | バッファ回路         |    |

| 2 2 0   | 半導体層           |    |

| 2 2 2   | 半導体層           |    |

| 2 2 4   | 導電層            |    |

| 2 2 6   | 配線             |    |

| 2 4 0   | 導電層            |    |

| 2 4 2 a | ソース電極またはドレイン電極 |    |

| 2 4 2 b | ソース電極またはドレイン電極 | 50 |

|         |                |    |

|---------|----------------|----|

| 2 4 2 c | ソース電極またはドレイン電極 |    |

| 5 4 2 a | ソース電極          |    |

| 5 4 2 b | ドレイン電極         |    |

| 5 4 3   | 絶縁層            |    |

| 5 4 4   | 酸化物半導体層        |    |

| 5 4 6   | ゲート絶縁層         |    |

| 5 4 8   | ゲート電極          |    |

| 5 6 2   | トランジスタ         |    |

| 7 0 1   | 筐体             |    |

| 7 0 2   | 筐体             | 10 |

| 7 0 3   | 表示部            |    |

| 7 0 4   | キー ボード         |    |

| 7 1 1   | 本体             |    |

| 7 1 2   | スタイルス          |    |

| 7 1 3   | 表示部            |    |

| 7 1 4   | 操作ボタン          |    |

| 7 1 5   | 外部インターフェイス     |    |

| 7 2 0   | 電子書籍           |    |

| 7 2 1   | 筐体             |    |

| 7 2 3   | 筐体             | 20 |

| 7 2 5   | 表示部            |    |

| 7 2 7   | 表示部            |    |

| 7 3 1   | 電源             |    |

| 7 3 3   | 操作キー           |    |

| 7 3 5   | スピーカー          |    |

| 7 3 7   | 軸部             |    |

| 7 4 0   | 筐体             |    |

| 7 4 1   | 筐体             |    |

| 7 4 2   | 表示パネル          |    |

| 7 4 3   | スピーカー          | 30 |

| 7 4 4   | マイクロフォン        |    |

| 7 4 5   | 操作キー           |    |

| 7 4 6   | ポインティングデバイス    |    |

| 7 4 7   | カメラ用レンズ        |    |

| 7 4 8   | 外部接続端子         |    |

| 7 4 9   | 太陽電池セル         |    |

| 7 5 0   | 外部メモリスロット      |    |

| 7 6 1   | 本体             |    |

| 7 6 3   | 接眼部            |    |

| 7 6 4   | 操作スイッチ         | 40 |

| 7 6 5   | 表示部            |    |

| 7 6 6   | バッテリー          |    |

| 7 6 7   | 表示部            |    |

| 7 7 0   | テレビジョン装置       |    |

| 7 7 1   | 筐体             |    |

| 7 7 3   | 表示部            |    |

| 7 7 5   | スタンド           |    |

| 7 8 0   | リモコン操作機        |    |

| 8 0 0   | 測定系            |    |

| 8 0 2   | 容量素子           | 50 |

|         |             |

|---------|-------------|

| 8 0 4   | トランジスタ      |

| 8 0 5   | トランジスタ      |

| 8 0 6   | トランジスタ      |

| 8 0 8   | トランジスタ      |

| 1 2 0 0 | 第1のp型トランジスタ |

| 1 2 1 0 | 第2のp型トランジスタ |

| 1 2 2 0 | 第1のn型トランジスタ |

| 1 2 3 0 | 第3のp型トランジスタ |

| 1 2 4 0 | 第4のp型トランジスタ |

| 1 2 5 0 | 第2のn型トランジスタ |

| 1 2 6 0 | 第1のp型トランジスタ |

| 1 2 7 0 | 第1のn型トランジスタ |

| 1 2 8 0 | 第2のp型トランジスタ |

| 1 2 9 0 | 第2のn型トランジスタ |

| 1 3 0 0 | 第1のトランジスタ   |

| 1 3 1 0 | 第2のトランジスタ   |

| 1 3 2 0 | 第3のトランジスタ   |

| 1 3 3 0 | 第4のトランジスタ   |

| 1 3 4 0 | 第5のトランジスタ   |

| 1 3 5 0 | 第1の容量素子     |

| 1 3 6 0 | 第2の容量素子     |

| 1 3 7 0 | 第3の容量素子     |

| 1 3 8 0 | 第4の容量素子     |

| 1 3 9 0 | トランジスタ      |

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

(B)

【図11】

(B)

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

---

フロントページの続き

審査官 堀田 和義

(56)参考文献 特許第5604560 (JP, B2)

米国特許出願公開第2006/0164876 (US, A1)

特表2006-502597 (JP, A)

国際公開第2005/088726 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

G 11 C 11/405

H 01 L 27/10

H 01 L 29/786