(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5853351号

(P5853351)

(45) 発行日 平成28年2月9日(2016.2.9)

(24) 登録日 平成27年12月18日(2015.12.18)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 25/065  | (2006.01) | HO1L | 25/08 | Z    |

| HO1L 25/07   | (2006.01) | HO1L | 27/14 | A    |

| HO1L 25/18   | (2006.01) | HO1L | 27/08 | 102E |

| HO1L 27/146  | (2006.01) | HO1L | 27/08 | 321G |

| HO1L 21/8234 | (2006.01) | HO1L | 21/88 | J    |

請求項の数 59 (全 38 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2010-70925 (P2010-70925)    |

| (22) 出願日  | 平成22年3月25日 (2010.3.25)        |

| (65) 公開番号 | 特開2011-204915 (P2011-204915A) |

| (43) 公開日  | 平成23年10月13日 (2011.10.13)      |

| 審査請求日     | 平成25年2月8日 (2013.2.8)          |

前置審査

|           |                                        |

|-----------|----------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (74) 代理人  | 110000925<br>特許業務法人信友国際特許事務所           |

| (72) 発明者  | 高橋 洋<br>東京都港区港南1丁目7番1号 ソニー株式会社内        |

| (72) 発明者  | 助川 俊一<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

| (72) 発明者  | 井上 啓司<br>東京都港区港南1丁目7番1号 ソニー株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置、半導体装置の製造方法、及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

表面側に多層配線層を有する半導体領域を複数積層して貼り合わせ、前記複数の半導体領域からなる積層体を形成する工程と、

前記積層体のうち、上層の半導体領域を薄肉化する工程と、

前記上層の半導体領域の表面側に形成された配線に達する接続孔、及び、前記上層の半導体領域を貫通し、下層の半導体領域の表面側に形成された配線に達する貫通接続孔であつて、直径が前記接続孔の直径の1.5~10倍程度大きい貫通接続孔を、前記上層の半導体領域側から開口することにより形成する工程と、

前記上層の半導体領域を貫通して、下層の半導体領域の表面側に形成された電極パッド部となる配線に達する貫通開口部を形成し、前記電極パッド部を露出させる工程とを有し

10

前記上層の半導体領域には受光量に応じた信号電荷を生成する光電変換部と複数の画素トランジスタとからなる画素を形成し、裏面照射型の固体撮像装置として構成された半導体装置の製造方法。

## 【請求項 2】

前記貫通接続孔は、前記上層の半導体領域を貫通して、下層の半導体領域上部に形成された多層配線層のうち、最上層の配線が露出するように形成し、

前記接続孔は、前記上層の半導体領域上部に形成された多層配線層のうち、最下層の配線が露出するように形成する

20

請求項 1 に記載の半導体装置の製造方法。

**【請求項 3】**

さらに、前記接続孔及び貫通接続孔に導電材料を埋め込むことにより、積層された半導体領域を電気的に接続する基板間配線を形成する工程を有する

請求項 1 に記載の半導体装置の製造方法。

**【請求項 4】**

前記接続孔及び前記貫通接続孔を含む領域の前記接続孔及び前記貫通接続孔上部に、溝部を形成し、前記導電材料によって前記溝部を埋め込むことにより、前記接続孔内に形成された基板間配線と前記貫通接続孔内に形成された基板間配線とを電気的に接続する

請求項 3 に記載の半導体装置の製造方法。

10

**【請求項 5】**

前記溝部が形成される層と同層の所望の遮光領域に遮光膜用溝部を形成し、前記遮光膜用溝部を導電材料で埋め込むことにより、遮光膜を形成する

請求項 4 に記載の半導体装置の製造方法。

**【請求項 6】**

前記基板間配線は、積層される前記半導体領域の回路間の共通の電位を有する配線を接続する

請求項 3 に記載の半導体装置の製造方法。

**【請求項 7】**

前記上層の半導体領域の裏面側に形成され、前記基板間配線に電気的に接続された裏面配線によって積層される前記半導体領域の回路間で共通に用いられる回路の一部を形成する

20

請求項 3 に記載の半導体装置の製造方法。

**【請求項 8】**

前記基板間配線が形成された後に、前記画素が形成された半導体領域上部にオンチップカラーフィルタ及びオンチップレンズを形成する工程を有する、

請求項 1 記載の半導体装置の製造方法。

**【請求項 9】**

第 1 の多層配線層を備えた第 1 の半導体領域と、

第 2 の多層配線層を備えた第 2 の半導体領域であって、前記第 1 の多層配線層と前記第 2 の多層配線層との間に貼り合わせ面を有して前記第 1 の半導体領域に積層された第 2 の半導体領域と、

30

前記第 1 の半導体領域から、前記第 1 の多層配線層の配線に達する接続孔と、

前記第 1 の半導体領域から前記貼り合わせ面を貫通して前記第 2 の多層配線層の配線に達し、直径が前記接続孔の直径の 1.5 ~ 10 倍程度大きい貫通接続孔と、

前記上層の半導体領域を貫通して、下層の半導体領域の表面側に形成された電極パッド部が露出するように形成された貫通開口部とを備え、

前記第 1 の半導体領域には受光量に応じた信号電荷を生成する光電変換部と複数の画素トランジスタとからなる画素が形成され、裏面照射型の固体撮像装置として構成された半導体装置。

40

**【請求項 10】**

前記接続孔は、前記第 1 の多層配線層の配線のうち、最下層の配線に達し、

前記貫通接続孔は、前記第 2 の多層配線層の配線のうち、最上層の配線に達する

請求項 9 に記載の半導体装置。

**【請求項 11】**

前記接続孔及び前記貫通接続孔に導電材料が埋め込まれて形成された基板間配線を有する

請求項 9 に記載の半導体装置。

**【請求項 12】**

前記接続孔、及び前記貫通接続孔の側壁には、絶縁材料からなる絶縁層が形成されてお

50

り、前記基板間配線と、前記第1の半導体領域は電気的に分離されている

請求項11に記載の半導体装置。

**【請求項13】**

前記接続孔及び前記貫通接続孔を含む領域の前記接続孔及び前記貫通接続孔上部には、溝部が形成されており、導電材料によって前記溝部が埋め込まれることにより、前記接続孔内に形成された基板間配線と前記貫通接続孔内に形成された基板間配線とが電気的に接続されている

請求項11に記載の半導体装置。

**【請求項14】**

前記溝部が形成される層と同層の所望の遮光領域に遮光膜用溝部が形成され、前記遮光膜用溝部が導電材料で埋め込まれることにより形成された遮光膜を有する

請求項13に記載の半導体装置。

**【請求項15】**

前記基板間配線により、前記第1の多層配線層と前記第2の多層配線層とに共通の電位を有する配線が接続される

請求項11に記載の半導体装置。

**【請求項16】**

前記第1の半導体領域の、前記第1の多層配線層が形成される側とは反対側の裏面側に形成され、前記基板間配線に電気的に接続された裏面配線によって前記第1の半導体領域に設けられた第1の半導体集積回路と前記第2の半導体領域に設けられた第2の半導体集積回路とに共通に用いられる回路の一部が形成されている

請求項15に記載の半導体装置。

**【請求項17】**

前記接続孔と前記貫通接続孔は、画素領域内に配置されている

請求項9に記載の半導体装置。

**【請求項18】**

前記接続孔と前記貫通接続孔は、画素領域外に配置されている

請求項9に記載の半導体装置。

**【請求項19】**

前記第2の多層配線層の配線の最上層は、アルミニウムを含む

請求項9に記載の半導体装置。

**【請求項20】**

前記第2の多層配線層の配線の最上層は、信号入出力端子である

請求項9に記載の半導体装置。

**【請求項21】**

前記画素領域内に複数の接続孔及び貫通接続孔を含む

請求項17に記載の半導体装置。

**【請求項22】**

前記第1の半導体領域は、フォトダイオードを含む

請求項9に記載の半導体装置。

**【請求項23】**

前記第2の半導体領域は、信号処理回路または制御回路を含む

請求項9に記載の半導体装置。

**【請求項24】**

電源端子と接地端子が、該四角形のチップにおいて対向する角に形成される

請求項9に記載の半導体装置。

**【請求項25】**

前記信号入出力端子は、第2の半導体領域の少なくとも3辺に沿って形成される

請求項20に記載の半導体装置。

**【請求項26】**

10

20

30

40

50

固体撮像装置と、

前記固体撮像装置のフォトダイオードに入射光を導く光学レンズと、

前記固体撮像装置の出力信号を処理する信号処理回路とを備え、

前記固体撮像装置は、表面側に第1の多層配線層を備えた第1の半導体領域と、表面側に第2の多層配線層を備えた第2の半導体領域であって、前記第1の多層配線層と前記第2の多層配線層との間に貼り合わせ面を有して前記第1の半導体領域に積層された第2の半導体領域と、前記第1の半導体領域の裏面側から、前記第1の多層配線層の配線に達する接続孔と、前記第1の半導体領域の裏面側から前記貼り合わせ面を貫通して前記第2の多層配線層の配線に達し、直径が前記接続孔の直径の1.5~10倍程度大きい貫通接続孔と、

10

前記上層の半導体領域を貫通して、下層の半導体領域の表面側に形成された電極パッド部が露出するように形成された貫通開口部とを備え、

前記第1の半導体領域には受光量に応じた信号電荷を生成する光電変換部と複数の画素トランジスタとからなる画素が形成され、裏面照射型の固体撮像装置として構成された電子機器。

#### 【請求項27】

前記接続孔は、前記第1の多層配線層の配線のうち、最下層の配線に達し、

前記貫通接続孔は、前記第2の多層配線層の配線のうち、最上層の配線に達する

請求項26に記載の電子機器。

#### 【請求項28】

前記接続孔及び前記貫通接続孔に導電材料が埋め込まれて形成された基板間配線を有する

請求項26に記載の電子機器。

#### 【請求項29】

前記接続孔、及び前記貫通接続孔の側壁には、絶縁材料からなる絶縁層が形成されており、前記基板間配線と、前記第1の半導体領域は電気的に分離されている

請求項28に記載の電子機器。

#### 【請求項30】

前記接続孔及び前記貫通接続孔を含む領域の前記接続孔及び前記貫通接続孔上部には、溝部が形成されており、導電材料によって前記溝部が埋め込まれることにより、前記接続孔内に形成された基板間配線と前記貫通接続孔内に形成された基板間配線とが電気的に接続されている

20

請求項29に記載の電子機器。

#### 【請求項31】

前記溝部が形成される層と同層の所望の遮光領域に遮光膜用溝部が形成され、前記遮光膜用溝部が導電材料で埋め込まれることにより形成された遮光膜を有する

請求項30に記載の電子機器。

#### 【請求項32】

前記基板間配線により、前記第1の多層配線層と前記第2の多層配線層とに共通の電位を有する配線が接続される

30

請求項28に記載の電子機器。

#### 【請求項33】

前記第1の半導体領域の、前記第1の多層配線層が形成される側とは反対側の裏面側に形成され、前記基板間配線に電気的に接続された裏面配線によって前記第1の半導体領域に設けられた第1の半導体集積回路と前記第2の半導体領域に設けられた第2の半導体集積回路とに共通に用いられる回路の一部が形成されている

請求項32に記載の電子機器。

#### 【請求項34】

前記接続孔と前記貫通接続孔は、画素領域内に配置されている

請求項26に記載の電子機器。

40

50

**【請求項 3 5】**

前記接続孔と前記貫通接続孔は、画素領域外に配置されている

請求項 2 6 に記載の電子機器。

**【請求項 3 6】**

前記第 2 の多層配線層の配線の最上層は、アルミニウムを含む

請求項 2 6 に記載の電子機器。

**【請求項 3 7】**

前記第 2 の多層配線層の配線の最上層は、信号入出力端子である

請求項 2 6 に記載の電子機器。

**【請求項 3 8】**

前記画素領域内に複数の接続孔及び貫通接続孔を含む

請求項 3 4 に記載の電子機器。

10

**【請求項 3 9】**

前記第 1 の半導体領域は、フォトダイオードを含む

請求項 2 6 に記載の電子機器。

**【請求項 4 0】**

前記第 2 の半導体領域は、信号処理回路または制御回路を含む

請求項 2 6 に記載の電子機器。

**【請求項 4 1】**

電源端子と接地端子が、該四角形のチップにおいて対向する角に形成される

請求項 2 6 に記載の電子機器。

20

**【請求項 4 2】**

前記信号入出力端子は、第 2 の半導体領域の少なくとも 3 辺に沿って形成される

請求項 3 7 に記載の電子機器。

**【請求項 4 3】**

第 1 の多層配線層を備えた第 1 の半導体領域と、

第 2 の多層配線層を備えた第 2 の半導体領域であって、前記第 1 の多層配線層と前記第 2 の多層配線層との間に貼り合わせ面を有して前記第 1 の半導体領域に積層された第 2 の半導体領域と、

前記第 1 の半導体領域から、前記第 1 の多層配線層の配線に達する接続孔と、

30

前記第 1 の半導体領域から前記貼り合わせ面を貫通して前記第 2 の多層配線層の配線に達する貫通接続孔と、

前記上層の半導体領域を貫通して、下層の半導体領域の表面側に形成された電極パッド部が露出するように形成された貫通開口部とを備え、

前記第 1 の半導体領域には受光量に応じた信号電荷を生成する光電変換部と複数の画素トランジスタとからなる画素が形成され、裏面照射型の固体撮像装置として構成され、

前記接続孔の前記第 1 の多層配線層の配線に接続する部分の直径と、前記貫通接続孔の前記第 2 の多層配線層の配線に接続する部分の直径が異なり、前記貫通接続孔の直径は前記接続孔の直径の 1.5 ~ 10 倍程度大きい

半導体装置。

40

**【請求項 4 4】**

前記接続孔は、前記第 1 の多層配線層の配線のうち、最下層の配線に達し、

前記貫通接続孔は、前記第 2 の多層配線層の配線のうち、最上層の配線に達する

請求項 4 3 に記載の半導体装置。

**【請求項 4 5】**

前記接続孔及び前記貫通接続孔に導電材料が埋め込まれて形成された基板間配線を有する

請求項 4 3 に記載の半導体装置。

**【請求項 4 6】**

前記接続孔、及び前記貫通接続孔の側壁には、絶縁材料からなる絶縁層が形成されてお

50

り、前記基板間配線と、前記第1の半導体領域は電気的に分離されている

請求項45に記載の半導体装置。

**【請求項47】**

前記接続孔及び前記貫通接続孔を含む領域の前記接続孔及び前記貫通接続孔上部には、溝部が形成されており、導電材料によって前記溝部が埋め込まれることにより、前記接続孔内に形成された基板間配線と前記貫通接続孔内に形成された基板間配線とが電気的に接続されている

請求項45記載の半導体装置。

**【請求項48】**

前記溝部が形成される層と同層の所望の遮光領域に遮光膜用溝部が形成され、前記遮光膜用溝部が導電材料で埋め込まれることにより形成された遮光膜を有する

請求項47に記載の半導体装置。

**【請求項49】**

前記基板間配線により、前記第1の多層配線層と前記第2の多層配線層とに共通の電位を有する配線が接続される

請求項45に記載の半導体装置。

**【請求項50】**

前記第1の半導体領域の、前記第1の多層配線層が形成される側とは反対側の裏面側に形成され、前記基板間配線に電気的に接続された裏面配線によって前記第1の半導体領域に設けられた第1の半導体集積回路と前記第2の半導体領域に設けられた第2の半導体集積回路とに共通に用いられる回路の一部が形成されている

請求項49に記載の半導体装置。

**【請求項51】**

前記接続孔と前記貫通接続孔は、画素領域内に配置されている

請求項43に記載の半導体装置。

**【請求項52】**

前記接続孔と前記貫通接続孔は、画素領域外に配置されている

請求項43に記載の半導体装置。

**【請求項53】**

前記第2の多層配線層の配線の最上層は、アルミニウムを含む

請求項43に記載の半導体装置。

**【請求項54】**

前記第2の多層配線層の配線の最上層は、信号入出力端子である

請求項43に記載の半導体装置。

**【請求項55】**

前記画素領域内に複数の接続孔及び貫通接続孔を含む

請求項51に記載の半導体装置。

**【請求項56】**

前記第1の半導体領域は、フォトダイオードを含む

請求項43に記載の半導体装置。

**【請求項57】**

前記第2の半導体領域は、信号処理回路または制御回路を含む

請求項43に記載の半導体装置。

**【請求項58】**

電源端子と接地端子が、該四角形のチップにおいて対向する角に形成される

請求項43に記載の半導体装置。

**【請求項59】**

前記信号入出力端子は、第2の半導体領域の少なくとも3辺に沿って形成される

請求項54に記載の半導体装置。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、固体撮像装置等の半導体装置とその製造方法、設計方法、及びこの固体撮像装置を備えたカメラ等の電子機器に関する。

**【背景技術】****【0002】**

固体撮像装置として、CMOS (Complementary Metal Oxide Semiconductor) 等のMOS型イメージセンサに代表される増幅型固体撮像装置が知られている。また、CCD (Charge Coupled Device) イメージセンサに代表される電荷転送型固体撮像装置が知られている。これら固体撮像装置は、デジタルスチルカメラ、デジタルビデオカメラなどに広く用いられている。近年、カメラ付き携帯電話やPDA (Personal Digital Assistant) などのモバイル機器に搭載される固体撮像装置としては、電源電圧が低く、消費電力の観点などからMOS型イメージセンサが多く用いられている。10

**【0003】**

MOS型の固体撮像装置は、単位画素が光電変換部となるフォトダイオードと複数の画素トランジスタで形成され、この複数の単位画素が2次元アレイ状に配列された画素アレイ(画素領域)と、周辺回路領域を有して構成される。複数の画素トランジスタは、MOSトランジスタで形成され、転送トランジスタ、リセットトランジスタ、増幅トランジスタの3トランジスタ、あるいは選択トランジスタを加えた4トランジスタで構成される。20

**【0004】**

従来、このようなMOS型固体撮像装置において、複数の画素が配列された画素領域が形成された半導体チップと、信号処理を行うロジック回路が形成された半導体チップを電気的に接続して1つのデバイスとして構成した固体撮像装置が種々提案されている。例えば、特許文献1では、各画素セル毎にマイクロパッドを有する裏面照射型のイメージセンサチップと、信号処理回路が形成されマイクロパッドを有する信号処理チップとを、マイクロバンプによって接続した半導体モジュールが開示されている。

**【0005】**

特許文献2では、インターポーラ(中間基板)上に、撮像画素部が設けられた裏面照射型のMOS固体撮像素子であるセンサチップと、信号処理を行う周辺回路が設けられた信号処理チップを実装したデバイスが開示されている。特許文献3では、イメージセンサチップと、薄型回路基板と、信号処理を行うロジック回路チップとを備えた構成である。そして、この薄膜回路基板とロジック回路チップが電気的に接続され、薄膜回路基板がイメージセンサチップの裏面からスルホールビアを介して電気的に接続された構成が開示されている。30

**【0006】**

また、特許文献4では、透明基板に支持された固体撮像素子に貫通電極を設け、この貫通電極を介して固体撮像素子をフレキシブル回路基板に電気的に接続した固体撮像装置が開示されている。さらに、特許文献5では、裏面照射型の固体撮像装置において、支持基板を貫通する電極を設けた構成が開示されている。40

**【0007】**

特許文献1～3に示すように、イメージセンサチップとロジック回路などの異種回路チップを混載する技術は、種々提案されている。従来技では、いずれも機能チップがほぼ完成した状態のものを用い、貫通接続孔を形成して、上下に積層されるチップ間の相互接続を可能な状態で1つのチップ上に形成されることが特徴となっている。

**【先行技術文献】****【特許文献】****【0008】**

【特許文献1】特開2006-49361号公報

【特許文献2】特開2007-13089号公報

10

20

30

40

50

【特許文献3】特開2008-130603号公報

【特許文献4】特許第4000507号公報

【特許文献5】特開2003-31785号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

上述した従来の固体撮像装置にも見られるように、基板を貫通する接続導体によって積層された異種チップ間を接続して半導体デバイスを構成することは、アイデアとして知られていた。しかし、深い基板に絶縁を確保しながら接続孔を開けねばならず、接続孔の加工と、接続導体の埋め込みに必要な製造プロセスのコスト経済性から実用化は困難とされていた。10

【0010】

一方、例えば $1\text{ }\mu\text{m}$ 程度の小さなコンタク穴を形成するためには、上部チップを極限まで薄肉化する必要がある。この場合、薄肉化する前に上部チップを支持基板に貼り付ける等の複雑な工程とコスト増を招いてしまう。しかも、高アスペクト比の接続孔に接続導体で埋めるためには、接続導体としてタンゲステン(W)等の被覆性の良いCVD膜を使うことが必然的に求められ、接続導体材料が制約される。

【0011】

量産で簡便に適用できる経済性を有する為には、この接続孔のアスペクト比を劇的に下げる、形成し易くすると共に、特別な接続孔加工を用いずに従来のウェハ製造プロセス内で加工できる技術を選択できることが望ましい。この際、上部チップに接続するコンタクト穴と、上部チップを貫通して下部チップに達するコンタクト穴は深さが異なるが、可能な限り同一のエッティング工程や金属埋め込み工程での形成ができることが求められている。20

【0012】

また、固体撮像装置などでは、画像領域と、信号処理を行うロジック回路とを、それぞれの性能を十分発揮できるように形成し、高性能化が図られることが望まれている。

固体撮像装置に限らず、他の半導体集積回路を有する半導体装置においても、それぞれの半導体集積回路の性能を十分に発揮できるように形成し、高性能化が図れることが望まれる。30

【0013】

しかしながら、上下のチップそれぞれに必要な機能を盛り込んだ設計を行うと、共通の機能を持った部分の回路面積が重複してしまうため、チップサイズが大きくなり、コスト低減が困難になる。このため、少なくとも、コスト削減のためには、上下のチップで同じ機能を持つ部分の面積を極力共通に使えるような構成で設計されることが臨まれる。

【0014】

本発明は、上述の点に鑑み、積層される半導体ウェハのそれぞれの性能を十分に発揮して高性能化を図り、且つ量産性、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供するものである。また、本発明は、上記固体撮像装置を備えたカメラ等の電子機器を提供するものである。40

【課題を解決するための手段】

【0015】

本発明に係る半導体装置の製造方法は、表面側に多層配線層を有する半導体領域を複数積層して貼り合わせ、複数の半導体領域からなる積層体を形成する工程と、積層体のうち、上層の半導体領域を薄肉化する工程とを有する。また、上層の半導体領域の表面側に形成された配線に達する接続孔、及び、上層の半導体領域を貫通し、下層の半導体領域の表面側に形成された配線に達する貫通接続孔であって、直径が接続孔の直径の1.5~10倍程度大きい貫通接続孔を、上層の半導体領域側から開口することにより形成する工程とを有する。また、上層の半導体領域を貫通して、下層の半導体領域の表面側に形成された電極パッド部となる配線に達する貫通開口部を形成し、電極パッド部を露出させる工程を50

有する。さらに、上層の半導体領域には受光量に応じた信号電荷を生成する光電変換部と複数の画素トランジスタとからなる画素を形成し、裏面照射型の固体撮像装置として構成されている。

#### 【0016】

本発明の半導体装置の製造方法では、貫通接続孔は、接続孔の直径よりも大きい直径を有するように形成されるので、導電材料を埋め込む際に、ボイドの発生などを防ぐことができる。

#### 【0017】

本発明に係る半導体装置は、表面側に第1の多層配線層を備えた第1の半導体領域と、表面側に第2の多層配線層を備えた第2の半導体領域であって、第1の多層配線層と第2の多層配線層との間に貼り合わせ面を有して第1の半導体領域に積層された第2の半導体領域とを有する。また、第1の半導体領域の裏面側から、第1の多層配線層の配線に達する接続孔と、第1の半導体領域の裏面側から貼り合わせ面を貫通して第2の多層配線層の配線に達し、直径が接続孔の直径の1.5～10倍程度大きい貫通接続孔と、上層の半導体領域を貫通して、下層の半導体領域の表面側に形成された電極パッド部が露出するよう<sup>10</sup>に形成された貫通開口部とを有する。さらに、第1の半導体領域には受光量に応じた信号電荷を生成する光電変換部と複数の画素トランジスタとからなる画素が形成され、裏面照射型の固体撮像装置として構成されている。

#### 【0018】

本発明の半導体装置では、貫通接続孔は、接続孔の直径よりも大きい直径を有するよう<sup>20</sup>に形成されているので、貫通接続孔内には、ボイドが発生することなく導電材料が埋め込まれている。

#### 【0019】

本発明に係る電子機器は、固体撮像装置と、光学レンズと、信号処理回路とを備える。

固体撮像装置は、表面側に第1の多層配線層を備えた第1の半導体領域と、表面側に第2の多層配線層を備えた第2の半導体領域であって、第1の多層配線層と第2の多層配線層との間に貼り合わせ面を有して第1の半導体領域に積層された第2の半導体領域とを有する。また、第1の半導体領域の裏面側から、第1の多層配線層の配線に達する接続孔と、第1の半導体領域の裏面側から貼り合わせ面を貫通して第2の多層配線層の配線に達し、直径が接続孔の直径の1.5～10倍程度大きい貫通接続孔と、上層の半導体領域を貫通して、下層の半導体領域の表面側に形成された電極パッド部が露出するよう<sup>30</sup>に形成された貫通開口部とを備え、さらに、第1の半導体領域には受光量に応じた信号電荷を生成する光電変換部と複数の画素トランジスタとからなる画素が形成され、裏面照射型の固体撮像装置として構成されている。

光学レンズは、固体撮像装置のフォトダイオードに入射光を導く。

信号処理回路は、固体撮像装置の出力信号を処理する。

#### 【発明の効果】

#### 【0020】

本発明によれば、最適なプロセス技術で、それぞれの性能を十分に発揮することができる回路が形成された半導体ウェハが複数積層された構成とされるので、量産性に優れ、低コストで高性能の半導体装置を得ることができる。また、半導体装置を裏面照射型の固体撮像装置とし、その固体撮像装置を電子機器に用いることにより、高性能な電子機器を得<sup>40</sup>ることができる。

#### 【図面の簡単な説明】

#### 【0021】

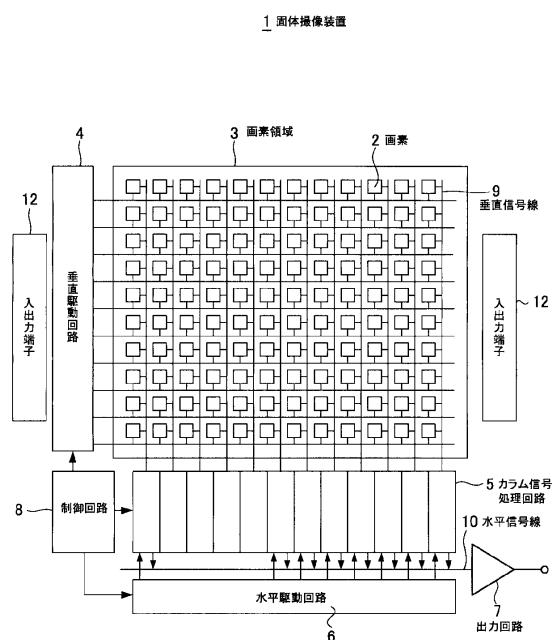

【図1】本発明に適用されるMOS固体撮像装置の一例を示す概略構成図である。

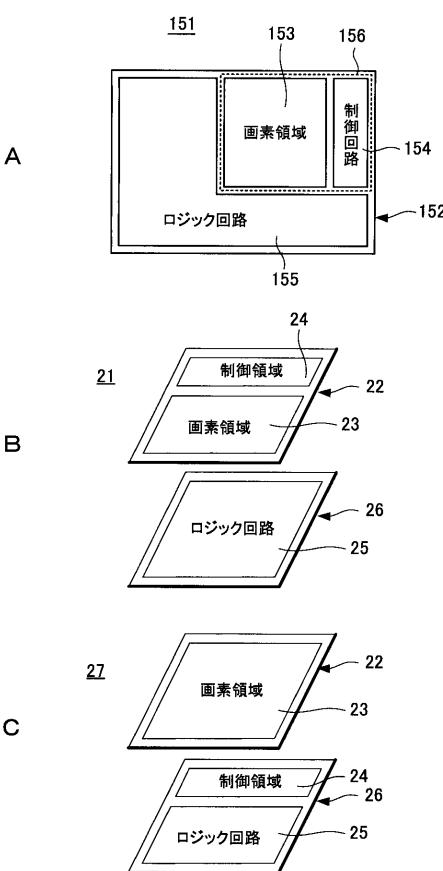

【図2】A 従来の固体撮像装置の模式図である。B, C 本発明の実施の形態に係る固体撮像装置の模式図である。

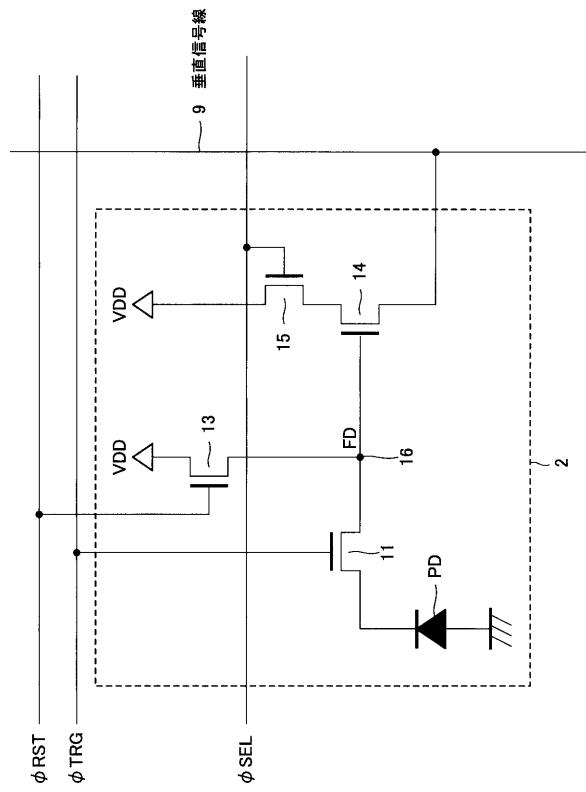

【図3】本発明に適用されるMOS固体撮像装置の画素構成の回路の一例を示す図である

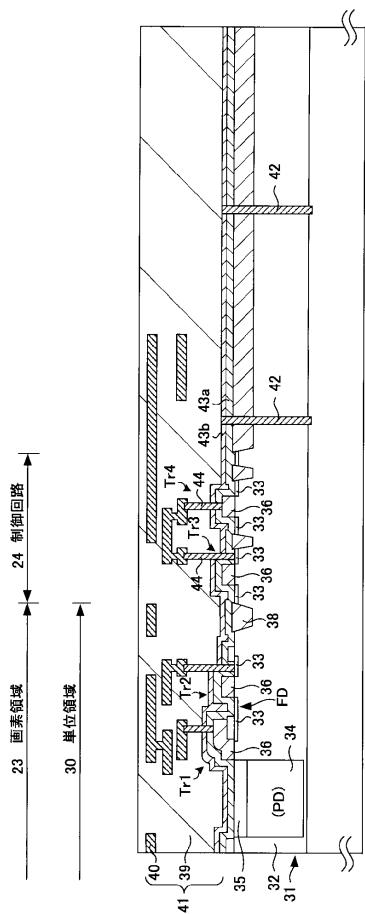

【図4】第1の実施形態に係る固体撮像装置を示す要部の概略構成図である。

【図5】第1の実施形態に係る固体撮像装置の製造方法例を示す製造工程図（その1）である。

【図6】第1の実施形態に係る固体撮像装置の製造方法例を示す製造工程図（その2）である。

【図7】第1の実施形態に係る固体撮像装置の製造方法例を示す製造工程図（その3）である。

【図8】第1の実施形態に係る固体撮像装置の製造方法例を示す製造工程図（その4）である。

【図9】第1の実施形態に係る固体撮像装置の製造方法例を示す製造工程図（その5）である。 10

【図10】第1の実施形態に係る固体撮像装置の製造方法例を示す製造工程図（その6）である。

【図11】第1の実施形態に係る固体撮像装置の製造方法例を示す製造工程図（その7）である。

【図12】第1の実施形態に係る固体撮像装置及びその製造方法を示す製造工程図（その8）である。

【図13】第1の実施形態に係る固体撮像装置の製造方法を示す製造工程図（その9）である。

【図14】第1の実施形態に係る固体撮像装置の製造方法を示す製造工程図（その10）である。 20

【図15】第1の実施形態に係る固体撮像装置の製造方法を示す製造工程図（その11）である。

【図16】第1の実施形態に係る固体撮像装置の製造方法を示す製造工程図（その12）である。

【図17】第1の実施形態に係る固体撮像装置の製造方法を示す製造工程図（その13）である。

【図18】第1の実施形態に係る固体撮像装置の製造方法を示す製造工程図（その14）である。

【図19】第1の実施形態に係る固体撮像装置の製造方法を示す製造工程図（その15）である。 30

【図20】本発明の第2の実施形態に係る固体撮像装置の概略断面構成図である。

【図21】第2の実施形態に係る半導体装置の製造方法を示す製造工程図（その1）である。

【図22】第2の実施形態に係る半導体装置の製造方法を示す製造工程図（その2）である。

【図23】第2の実施形態に係る半導体装置の製造方法を示す製造工程図（その3）である。

【図24】第2の実施形態に係る半導体装置の製造方法を示す製造工程図（その4）である。 40

【図25】第2の実施形態に係る半導体装置の製造方法を示す製造工程図（その5）である。

【図26】第2の実施形態に係る半導体装置の製造方法を示す製造工程図（その6）である。

【図27】本発明の第3の実施形態に係る固体撮像装置の要部の概略断面構成図である。

【図28】A，B 第1の半導体基板の裏面側に裏面配線を用いた例と、用いない例である。

【図29】A，B 積層されるチップ間で共通の電位の配線を接続した場合の平面レイアウトの構成例と、共通の電位の配線を接続しない場合の平面レイアウトの構成例である。

【図30】本発明の固体撮像装置の設計方法を示すフローである。 50

【図31】A,B 本発明の設計方法に沿った上チップ及び下チップの製造工程図である。

【図32】A,B 本発明の設計方法に沿った上チップ及び下チップの製造工程図である。

【図33】A,B 本発明の設計方法に沿った上チップ及び下チップの製造工程図である。

【図34】A,B 本発明の設計方法に沿った上チップ及び下チップの製造工程図である。

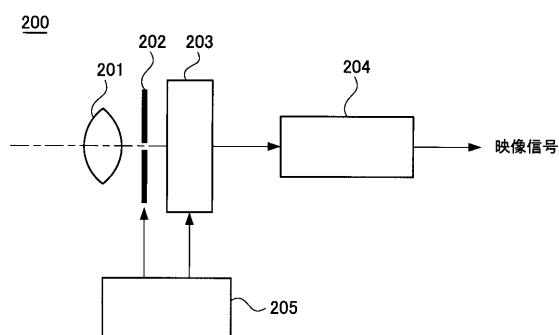

【図35】本発明の第4の実施形態に係る電子機器を示す概略構成図である。

【発明を実施するための形態】

10

【0022】

以下、発明を実施するための形態（以下実施の形態とする）について説明する。なお、説明は以下の順序で行う。

1. MOS型固体撮像装置の概略構成例

2. 第1の実施形態（裏面照射型の固体撮像装置の構成例とその製造方法例）

3. 第2の実施形態（半導体装置の構成例とその製造方法例）

4. 第3の実施形態（固体撮像装置の構成例と、その設計方法）

5. 第4の実施形態（電子機器の構成例）

【0023】

1. MOS型固体撮像装置の概略構成例

20

図1に、本発明の半導体装置に適用されるMOS型固体撮像装置の概略構成を示す。このMOS型固体撮像装置は、各実施の形態の固体撮像装置に適用される。本例の固体撮像装置1は、図示しない半導体基板例えばシリコン基板に複数の光電変換部を含む画素2が規則的に2次元アレイ状に配列された画素領域（いわゆる画素アレイ）3と、周辺回路部とを有して構成される。画素2は、光電変換部となる例えばフォトダイオードと、複数の画素トランジスタ（いわゆるMOSトランジスタ）を有して成る。複数の画素トランジスタは、例えば転送トランジスタ、リセットトランジスタ及び増幅トランジスタの3つのトランジスタで構成することができる。その他、選択トランジスタ追加して4つのトランジスタで構成することもできる。単位画素の等価回路については後述する。画素2は、1つの単位画素として構成することができ、また、複数の画素でトランジスタを共有する共有画素構造とすることもできる。この共有画素構造は、複数のフォトダイオードが、転送トランジスタを構成するフローティングディフェュージョン、及び転送トランジスタ以外の他のトランジスタを共有する構造である。

30

【0024】

周辺回路部は、垂直駆動回路4と、カラム信号処理回路5と、水平駆動回路6と、出力回路7と、制御回路8などを有して構成される。

【0025】

制御回路8は、入力クロックと、動作モードなどを指令するデータを受け取り、また固体撮像装置の内部情報などのデータを出力する。すなわち、制御回路8では、垂直同期信号、水平同期信号及びマスタクロックに基いて、垂直駆動回路4、カラム信号処理回路5及び水平駆動回路6などの動作の基準となるクロック信号や制御信号を生成する。そして、これらの信号を垂直駆動回路4、カラム信号処理回路5及び水平駆動回路6等に入力する。

40

【0026】

垂直駆動回路4は、例えばシフトレジスタによって構成され、画素駆動配線を選択し、選択された画素駆動配線に画素を駆動するためのパルスを供給し、行単位で画素を駆動する。すなわち、垂直駆動回路4は、画素領域3の各画素2を行単位で順次垂直方向に選択走査し、垂直信号線9を通して各画素2の光電変換部となる例えばフォトダイオードにおいて受光量に応じて生成した信号電荷に基づく画素信号をカラム信号処理回路5に供給する。

50

**【 0 0 2 7 】**

カラム信号処理回路 5 は、画素 2 の例えれば列ごとに配置されており、1 行分の画素 2 から出力される信号を画素列ごとにノイズ除去などの信号処理を行う。すなわちカラム信号処理回路 5 は、画素 2 固有の固定パターンノイズを除去するための C D S (Correlated Double Sampling: 相関二重サンプリング) や、信号増幅、A D 変換等の信号処理を行う。カラム信号処理回路 5 の出力段には水平選択スイッチ (図示せず) が水平信号線 1 0 との間に接続されて設けられる。

**【 0 0 2 8 】**

水平駆動回路 6 は、例えればシフトレジスタによって構成され、水平走査パルスを順次出力することによって、カラム信号処理回路 5 の各々を順番に選択し、カラム信号処理回路 5 の各々から画素信号を水平信号線 1 0 に出力させる。

10

**【 0 0 2 9 】**

出力回路 7 は、カラム信号処理回路 5 の各々から水平信号線 1 0 を通して順次に供給される信号に対し、信号処理を行って出力する。例えれば、バファリングだけする場合もあるし、黒レベル調整、列ばらつき補正、各種デジタル信号処理などが行われる場合もある。入出力端子 1 2 は、外部と信号のやりとりをする。

**【 0 0 3 0 】**

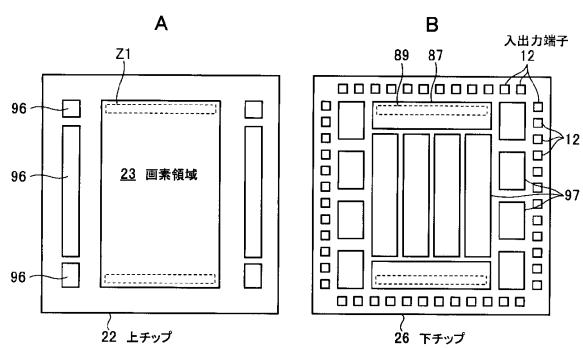

次に、本実施形態に係る M O S 型固体撮像装置の構造について説明する。図 2 A は、従来の M O S 型固体撮像装置の構造を示す概略構成図であり、図 2 B 及び図 2 C は、本実施形態に係る M O S 型固体撮像装置の構造を示す概略構成図である。

20

**【 0 0 3 1 】**

従来の M O S 型固体撮像装置 1 5 1 は、図 2 A に示すように、1 つの半導体チップ 1 5 2 内に、画素領域 1 5 3 と、制御回路 1 5 4 と、信号処理するためのロジック回路 1 5 5 とを搭載して構成される。通常、画素領域 1 5 3 と制御回路 1 5 4 でイメージセンサ 1 5 6 が構成される。

**【 0 0 3 2 】**

これに対して、本実施形態例の M O S 型固体撮像装置 2 1 は、図 2 B に示すように、第 1 の半導体チップ部 2 2 に画素領域 2 3 と制御領域 2 4 を搭載し、第 2 の半導体チップ部 2 6 に信号処理するための信号処理回路を含むロジック回路 2 5 を搭載する。この第 1 の半導体チップ部 2 2 と第 2 の半導体チップ部 2 6 を相互に電気的に接続して 1 つの半導体チップとして M O S 型固体撮像装置 2 1 が構成される。

30

**【 0 0 3 3 】**

本発明の他の実施形態例における M O S 型固体撮像装置 2 7 は、図 2 C に示すように、第 1 の半導体チップ部 2 2 に画素領域 2 3 を搭載し、第 2 の半導体チップ部 2 6 にと制御領域 2 4 、信号処理回路を含むロジック回路 2 5 を搭載する。この第 1 の半導体チップ部 2 2 と第 2 の半導体チップ部 2 6 を相互に電気的に接続して 1 つの半導体チップとして M O S 型固体撮像装置 2 7 が構成される。

**【 0 0 3 4 】**

図 3 は、単位画素 2 の回路構成の一例を示す回路図である。本回路例に係る単位画素 2 は、光電変換部、例えはフォトダイオード P D と、4 つの画素トランジスタとを有して構成される。4 つの画素トランジスタは、例えは転送トランジスタ 1 1 、リセットトランジスタ 1 3 、増幅トランジスタ 1 4 及び選択トランジスタ 1 5 である。これら画素トランジスタは、例えは n チャネルの M O S トランジスタを用いている。

40

**【 0 0 3 5 】**

転送トランジスタ 1 1 は、フォトダイオード P D のカソードとフロー・ティング・ディ・フュージョン部 1 6 との間に接続される。フォトダイオード P D で光電変換され、ここに蓄積された信号電荷 (ここでは、電子) を、ゲートに転送パルス T R G が与えられることによってフロー・ティング・ディ・フュージョン部 1 6 に転送する。

**【 0 0 3 6 】**

リセットトランジスタ 1 3 は、電源 V D D にドレインが、フロー・ティング・ディ・フュージ

50

ヨン部 16 にソースがそれぞれ接続される。そして、フォトダイオード P D からフローティングディフュージョン部 16 への信号電荷の転送に先立って、ゲートにリセットパルス R S T が与えられることによってフローティングディフュージョン部 16 の電位をリセットする。

#### 【 0 0 3 7 】

選択トランジスタ 15 は、例えば、電源 V D D にそのドレインが接続され、増幅トランジスタ 14 のドレインにそのソースがそれぞれ接続される。そして選択トランジスタ 15 のゲートに選択パルス S E L が与えられることによってオン状態となり、増幅トランジスタ 14 に対して電源 V D D を供給することによって画素 2 の選択ができる。なお、この選択トランジスタ 15 については、増幅トランジスタ 14 のソースと垂直信号線 9 との間に接続した構成を探ることも可能である。10

#### 【 0 0 3 8 】

増幅トランジスタ 14 は、フローティングディフュージョン部 16 にゲートが、選択トランジスタ 15 のソースにドレインが、垂直信号線 9 にソースがそれぞれ接続されたソースフォロア構成となっている。増幅トランジスタ 14 は、リセットトランジスタ 13 によってリセットした後のフローティングディフュージョン部 16 の電位をリセットレベルとして垂直信号線 9 に出力する。さらに増幅トランジスタ 14 は、転送トランジスタ 11 によって信号電荷を転送した後のフローティングディフュージョン部 16 の電位を信号レベルとして垂直信号線 9 に出力する。

#### 【 0 0 3 9 】

本実施形態例の固体撮像装置 1 では、例えば、フォトダイオード及び複数の M O S トランジスタ等の素子が図 2 B 又は図 2 C の第 1 の半導体チップ部 2 2 に形成される。また、転送パルス、リセットパルス、選択パルス、電源電圧は、図 2 B 又は図 2 C の制御領域 2 4 から供給される。また、選択トランジスタのドレインに接続される垂直信号線 9 から後段の素子は、図 2 B 又は図 2 C のロジック回路 2 5 に構成されており、第 2 の半導体チップ部 2 6 に形成される。20

#### 【 0 0 4 0 】

上述の実施形態例に係る M O S 型固体撮像装置は、異種の半導体チップが積層した構造を有しており、後述するように、その製造方法と、その製造方法に基づいて得られた構成に特徴を有している。30

以下に説明する実施形態例では、本発明の固体撮像装置と、その製造方法について説明する。

#### 【 0 0 4 1 】

##### 2 . 第 1 の実施形態

###### [ 固体撮像装置の構成例とその製造方法例 ]

図 4 ~ 図 1 9 を用いて、本発明の第 1 の実施形態例に係る半導体装置として、裏面照射型の M O S 型固体撮像装置をその製造方法と共に説明する。

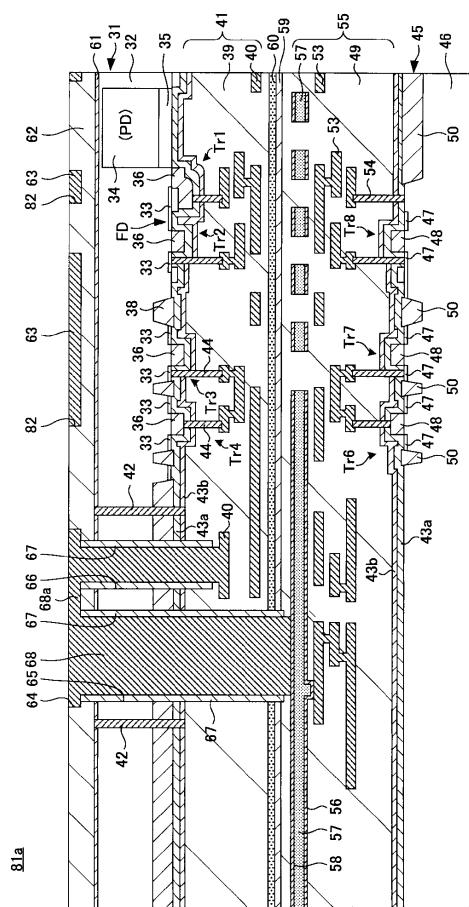

#### 【 0 0 4 2 】

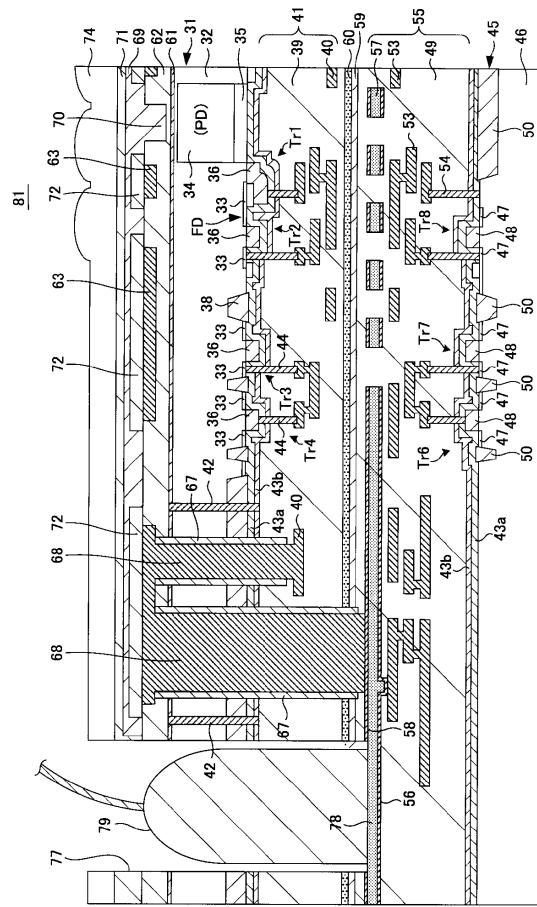

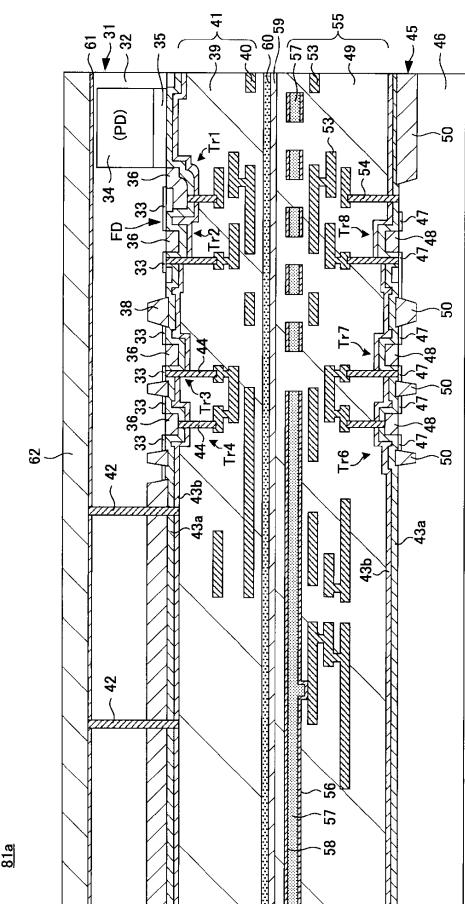

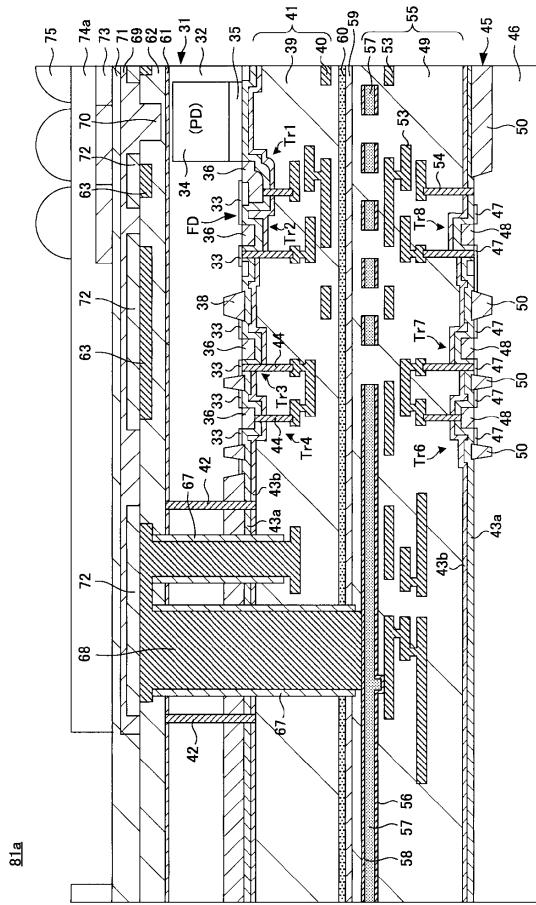

図 4 は、本実施形態例の固体撮像装置 8 1 の電極パッド部 7 8 を含む概略断面構成図(完成図)である。本実施形態例の固体撮像装置 8 1 は、画素アレイ(以下、画素領域という) 2 3 と制御領域 2 4 とを含む第 1 の半導体チップ部 2 2 と、ロジック回路 2 5 が搭載された第 2 の半導体チップ部 2 6 が電気的に接続された状態で上下に積層されている。40

図 5 ~ 図 1 9 を用いて、本実施形態例の固体撮像装置 8 1 の製造方法について説明する。

#### 【 0 0 4 3 】

第 1 の実施形態例においては、先ず、図 5 に示すように、第 1 の半導体ウェハ(以下、第 1 の半導体基板といふ) 3 1 の各チップ部となる領域に、半製品状態のイメージセンサ、すなわち画素領域 2 3 と制御領域 2 4 を形成する。すなわち、シリコン基板からなる第 1 の半導体基板 3 1 の各チップ部となる領域に、各画素の光電変換部となるフォトダイオード( P D )を形成し、その半導体ウェル領域 3 2 に各画素トランジスタのソース / ドレ

50

イン領域33を形成する。半導体ウェル領域32は、第1導電型、例えばp型の不純物を導入して形成し、ソース／ドレイン領域33は、第2導電型、例えばn型の不純物を導入して形成する。フォトダイオード(PD)及び各画素トランジスタのソース／ドレイン領域33は、基板表面からのイオン注入で形成する。

#### 【0044】

フォトダイオード(PD)は、n型半導体領域34と基板表面側のp型半導体領域35を有して形成される。画素を構成する基板表面上にはゲート絶縁膜を介してゲート電極36を形成し、ゲート電極36と対のソース／ドレイン領域33により画素トランジスタTr1、Tr2を形成する。図5では、複数の画素トランジスタを、2つの画素トランジスタTr1、Tr2で代表して示す。フォトダイオード(PD)に隣接する画素トランジスタTr1が転送トランジスタに相当し、そのソース／ドレイン領域がフローティングディフージョン(FD)に相当する。各単位画素30が素子分離領域38で分離される。

10

#### 【0045】

一方、制御領域24側では、第1の半導体基板31に制御回路を構成するMOSトランジスタを形成する。図4では、MOSトランジスタTr3、Tr4で代表して、制御領域24を構成するMOSトランジスタを示す。各MOSトランジスタTr3、Tr4は、n型のソース／ドレイン領域33と、ゲート絶縁膜を介して形成したゲート電極36とのより形成される。

#### 【0046】

次いで、第1の半導体基板31の表面上に、1層目の層間絶縁膜39を形成し、その後、層間絶縁膜39にコンタクトホールを形成し、所要のトランジスタに接続する接続導体44を形成する。高さの異なる接続導体44の形成に際しては、トランジスタ上面を含む全面に第1絶縁薄膜43aを例えばシリコン酸化膜にて形成し、エッチングストップとなる第2絶縁薄膜43bを例えばシリコン窒化膜にて形成して積層する。この第2絶縁薄膜43b上に1層目の層間絶縁膜39を形成する。1層目の層間絶縁膜39は、例えば、P-SiO膜(プラズマ酸化膜)を10～150nmで成膜後、NSG(ノンドープケイ酸ガラス)膜又はPSG膜(リンケイ酸ガラス)を50nm～1000nmで形成する。その後、dTEOS膜を100～1000nmで成膜後、P-SiH<sub>4</sub>膜(プラズマ酸化膜)を50～200nmで成膜することで形成することができる。

20

#### 【0047】

その後、1層目の層間絶縁膜39に深さの異なるコンタクトホールをエッチングストップとなる第2絶縁薄膜43bまで選択的に形成する。次いで、各コンタクトホールに連続するように、各部で同じ膜厚の第1絶縁薄膜43a及び第2絶縁薄膜43bを選択エッチングしてコンタクトホールを形成する。そして、各コンタクトホールに接続導体44を埋め込む。

30

#### 【0048】

また、第2絶縁薄膜43b形成後、第1の半導体基板31の半導体ウェル領域32内の所望の領域を分離する絶縁スペーサ層42を形成する。絶縁スペーサ層42は、第2絶縁薄膜43b形成後、第1の半導体基板31の所望の位置を表面側から開口し、絶縁材料を埋め込むことで形成される。この絶縁スペーサ層42は、図4の基板間配線68を囲む領域に形成されるものである。

40

#### 【0049】

次いで、各接続導体44に接続するように、層間絶縁膜39を介して複数層、本例では3層の銅配線40を形成して第1の多層配線層41を形成する。通常、各銅配線40は、Cu拡散を防止するため図示しないバリアメタル層で覆われる。バリアメタル層は、例えばSiN膜、SiC膜を10～150nmで成膜することで形成することができる。また、2層目からの層間絶縁膜39は、dTEOS膜(プラズマCVD(Chemical Vapor Deposition)法により形成されたシリコン酸化膜)を100～1000nmで成膜することで形成することができる。層間絶縁膜39とバリアメタル層を介して形成される銅配線40とを交互に形成することにより、第1の多層配線層41が形成される。本実施形態例で

50

は、第1の多層配線層41を銅配線40で形成する例としたが、その他の金属材料によるメタル配線とすることも可能である。

#### 【0050】

これまでの工程で、上部に第1の多層配線層41を有し、半製品状態の画素領域23及び制御領域24が構成された第1の半導体基板31が形成される。

#### 【0051】

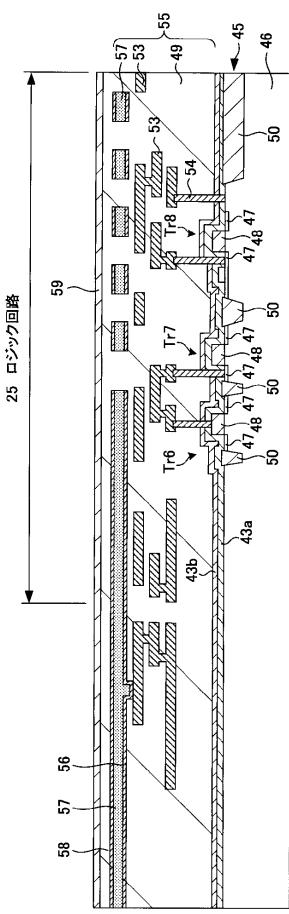

一方、図6に示すように、例えばシリコンからなる第2の半導体基板(半導体ウェハ)45の各チップ部となる領域に、半製品状態の信号処理するための信号処理回路を含むロジック回路25を形成する。すなわち、第2の半導体基板45の表面側のp型の半導体ウェル領域46に、素子分離領域50で分離されるようにロジック回路25を構成する複数のMOSトランジスタを形成する。ここでは、複数のMOSトランジスタを、MOSトランジスタTr6, Tr7、Tr8で代表する。各MOSトランジスタTr6、Tr7、Tr8は、それぞれ1対のn型のソース/ドレイン領域47と、ゲート絶縁膜を介して形成したゲート電極48を有して形成される。ロジック回路25は、CMOSトランジスタで構成することができる。

10

#### 【0052】

次いで、第2の半導体基板45の表面上に、1層目の層間絶縁膜49を形成し、その後、層間絶縁膜49にコンタクトホールを形成し、所要のトランジスタに接続する接続導体54を形成する。高さの異なる接続導体54の形成に際しては、前述と同様に、トランジスタ上面を含む全面に第1絶縁薄膜43a、例えばシリコン酸化膜と、エッチングストップとなる第2絶縁薄膜43b、例えばシリコン窒化膜を積層する。この第2絶縁薄膜43b上に1層目の層間絶縁膜49を形成する。そして、1層目の層間絶縁膜39に深さの異なるコンタクトホールをエッチングストップとなる第2絶縁薄膜43bまで選択的に形成する。次いで、各コンタクトホールに連続するように、各部で同じ膜厚の第1絶縁薄膜43a及び第2絶縁薄膜43bを選択エッチングしてコンタクトホールを形成する。そして、各コンタクトホールに接続導体54を埋め込む。

20

#### 【0053】

その後、層間絶縁膜49の形成と複数層のメタル配線の形成を繰り返すことにより、第2の多層配線層55を形成する。本実施形態例では、第1の半導体基板31上に形成した第1の多層配線層41の形成工程と同様の工程と同様にして3層の銅配線53を形成したあと、最上層にアルミ配線57を形成する例とする。アルミ配線57の形成は、まず、最上層の銅配線53上部に層間絶縁膜49形成した後、最上層の銅配線53上部の所望の位置が露出されるように層間絶縁膜49をエッチング除去し、コンタクトホールを形成する。そして、コンタクトホール内を含む領域にバリアメタル層56となるTiN(下層)/Ti(上層)からなる積層膜を5~10nm、又はTaN(下層)/Ta(上層)からなる積層膜を10~100nmで成膜する。その後、コンタクトホールを被覆してアルミニウムを500~2000nmで成膜した後、所望の形状にパターニングすることによりアルミ配線57を形成する。さらに、アルミ配線57上部に、後の工程で必要となるバリアメタル層58を成膜する。このバリアメタル層58も、アルミ配線57の下層に成膜したバリアメタル層56と同様の構成とすることができます。

30

#### 【0054】

続いて、上部にバリアメタル層58が形成されたアルミ配線57を被覆して層間絶縁膜49を成膜する。アルミ配線57上部の層間絶縁膜49は、例えばHDP膜(高密度プラズマ酸化膜)又はP-SiO膜(プラズマ酸化膜)を500~2000nmで成膜した後、その上部にさらにP-SiO膜を100~2000nmの厚みで成膜することで形成することができる。以上により、層間絶縁膜49を介して形成された3層の銅配線53と最上層に形成されたアルミ配線57からなる第2の多層配線層55が形成される。

40

#### 【0055】

そして、第2の多層配線層55上部には、第1の半導体基板31と第2の半導体基板45の貼り合わせの際に反りを軽減するための反り矯正膜59を形成する。反り矯正膜59

50

は、例えば P - SiN 膜又は P - SiON 膜（プラズマ窒酸化膜）を 100 ~ 2000 nm で成膜することで形成することができる。

#### 【0056】

これまでの工程で、上部に第 2 の多層配線層 55 を有し、半製品状態のロジック回路が構成された第 2 の半導体基板 45 が形成される。

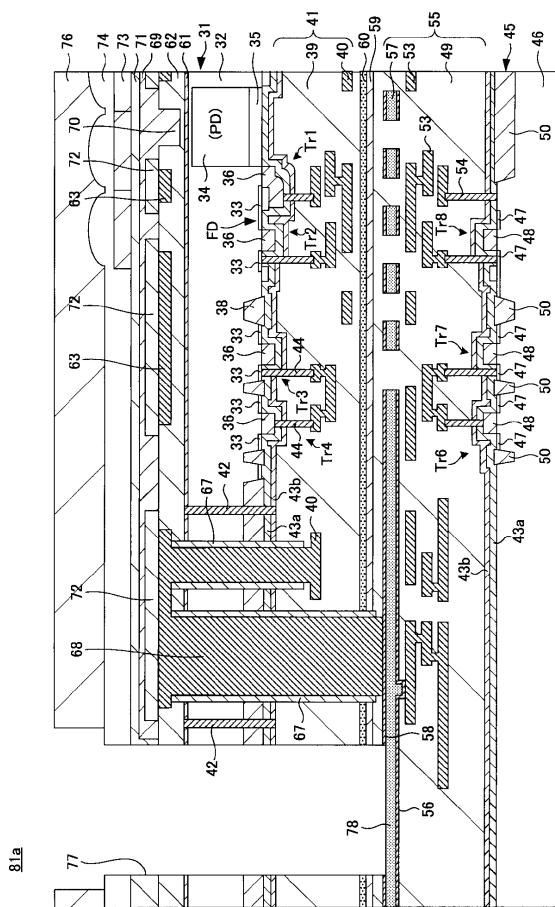

#### 【0057】

次に、図 7 に示すように、第 1 の半導体基板 31 と第 2 の半導体基板 45 とを、第 1 の多層配線層 41、及び第 2 の多層配線層 55 が向き合うように貼り合わせる。貼り合わせは、例えば接着剤にて行う。接着剤にて接合する場合には、第 1 の半導体基板 31 又は第 2 の半導体基板 45 の接合面の一方の側に接着剤層 60 を形成し、この接着剤層 60 を介して重ね合わせて両者を接合する。本実施形態例では、画素領域が構成された第 1 の半導体基板 31 を上層に配置し、第 2 の半導体基板 45 を下層に配置して貼り合わせた。10

#### 【0058】

また、本実施形態例では、接着剤層 60 を介して第 1 の半導体基板 31 上部の第 1 の多層配線層 41 と第 2 の半導体基板 45 上部の第 2 の多層配線層 55 とを貼り合わせる例としたが、この他、プラズマ接合で貼り合わせる例としてもよい。プラズマ接合の場合には、第 1 の多層配線層 41 と第 2 の多層配線層 55 の接合面に、それぞれプラズマTEOS 膜、プラズマSiN 膜、SiON 膜（プロック膜）、あるいは、SiC 膜などを形成する。この膜が形成された接合面をプラズマ処理して重ね合わせ、その後、アニール処理して両者を接合する。貼り合わせ処理は、配線などに影響を与えない 400 以下の低温プロセスで行なうことが好ましい。20

#### 【0059】

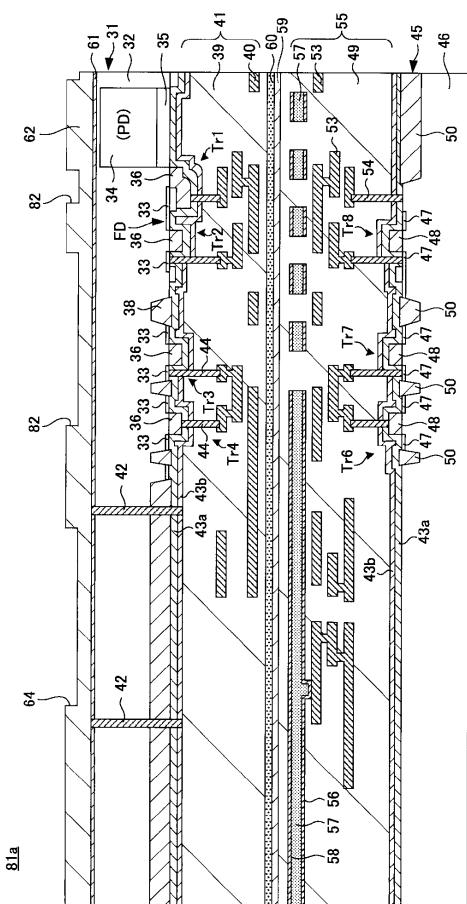

そして、上部に多層配線層を有する第 1 の半導体基板 31 と第 2 の半導体基板 45 とが積層して貼り合わされることにより、2 つの異種基板からなる積層体 81a が形成される。

#### 【0060】

次に、図 8 に示すように、第 1 の半導体基板 31 の裏面側から研削、研磨して第 1 の半導体基板 31 を薄肉化する。この薄肉化は、フォトダイオード（PD）が臨むように行われる。第 1 の半導体基板 31 として、例えば p 型の高濃度不純物層をエッティングストップ層（図示せず）として形成された半導体基板を用いることにより、エッティングストップ層まで基板をエッティング除去することで平坦に薄肉化することができる。薄肉化した後、フォトダイオード（PD）の裏面に暗電流抑制のための p 型半導体層（図示せず）を形成する。第 1 の半導体基板 31 の厚さは例えば 600 μm 程度あるが、例えば 3 ~ 5 μm 程度まで薄肉化する。30

#### 【0061】

従来、このような薄肉化は、別途用意した支持基板を第 1 の半導体基板 31 上に形成された第 1 の多層配線層 41 側に貼り合わせて行われていた。しかし、本実施の形態では、ロジック回路 25 が形成された第 2 の半導体基板 45 を支持基板に兼用して第 1 の半導体基板 31 の薄肉化が行われる。この第 1 の半導体基板 31 の裏面が裏面照射型の固体撮像装置として構成されたときの、光入射面となる。40

#### 【0062】

次に、図 9 に示すように、第 1 の半導体基板 31 の裏面上に、反射防止膜 61 を形成する。反射防止膜 61 は、例えば TaO<sub>2</sub> 又は HfO<sub>2</sub> を 5 ~ 100 nm で成膜し、必要な熱処理を行うことで暗電流が抑制する効果を付加することができる。その後、反射防止膜 61 上に、プラズマSiO 膜を 100 ~ 1500 nm の厚みに成膜することにより、絶縁膜 62 を形成する。

#### 【0063】

次に、図 10 に示すように、絶縁スペーサ層 42 の内側の所望の領域に溝部 64 を形成し、遮光が必要な遮光領域に、遮光膜用溝部 82 を形成する。この溝部 64 及び遮光膜用溝部 82 は、第 1 の半導体基板 31 の裏面側に形成された絶縁膜 62 上面からエッティング

10

20

30

40

50

により開口を形成することで形成し、例えば第1の半導体基板31に達しない深さに形成する。

#### 【0064】

次に、図11に示すように、絶縁スペーサ層42の内側に形成された溝部64の所望の底部領域から第1の多層配線層41の最下層(図11では、一番上側)の銅配線40に達する直前の深さまで開口し、接続孔66を形成する。

#### 【0065】

また、同じく、絶縁スペーサ層42の内側に形成された溝部64の所望の底部領域から第1の多層配線層41と第2の多層配線層55との貼り合わせ面を貫通する貫通接続孔65を形成する。この貫通接続孔65は、第2の半導体基板45上部に形成された第2の多層配線層55の最上層のアルミ配線57に達する直前の深さまで開口することにより形成する。このとき、貫通接続孔65の直径は接続孔66の直径の1.5~10倍程度大きく、より好ましくは、3~4倍程度大きく形成する。10

#### 【0066】

貫通接続孔65の直径が接続孔66の1.5倍よりも小さい場合には、貫通接続孔65のアスペクト比が大きくなり、後の工程で導電材料を孔内に埋め込む際に、ボイドが発生するおそれがある。また、貫通接続孔65の直径が接続孔66の10倍よりも大きい場合には、貫通接続孔65の占める領域が大きくなり、装置の小型化が実施できないという問題がある。したがって、貫通接続孔65の直径を接続孔66の直径の1.5~10倍程度大きくすることで、導電材料の埋め込みに最適なアスペクト比で、かつ、レイアウトスペースも大きくならない孔とすることができます。20

#### 【0067】

接続孔66、及び貫通接続孔65は、第1の半導体基板31を薄肉化(図8の工程)した後に形成するので、アスペクト比が小さくなり、微細孔として形成することができる。また、接続孔66は、第1の半導体基板31上部の第1の多層配線層41のうち、最下層、すなわち、第1の半導体基板31に最も近い側の銅配線40に達する直前まで開口して形成されるため、開口深さがより浅くなり、微細孔に形成に有利になる。

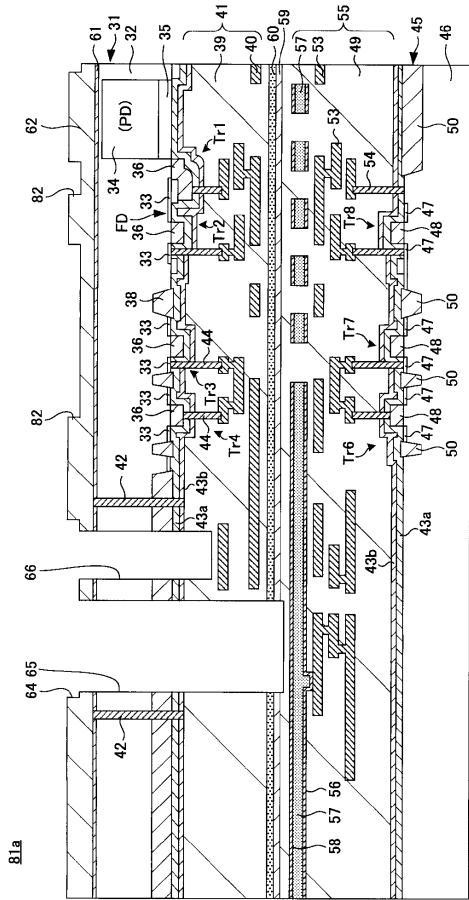

#### 【0068】

次に、接続孔66、及び貫通接続孔65の側壁及び底部を含む領域に、例えばSiO<sub>2</sub>膜から成る絶縁層67を成膜し、その後エッチバックする。これにより、図12に示すように接続孔66及び貫通接続孔65の側壁のみに絶縁層67を残す。その後、接続孔66及び貫通接続孔65の底部をさらにエッティング除去する。これにより、接続孔66においては、第1の多層配線層41の最下層の銅配線40を、貫通接続孔65においては第2の多層配線層55の最上層のアルミ配線57(厳密にはアルミ配線上部のバリアメタル層58)を露出させる。30

#### 【0069】

この結果、接続孔66は、は第1の多層配線層41の銅配線40に達する。また、貫通接続孔65は、第1の多層配線層41及び第2の多層配線層55の貼り合わせ面を貫通し、第2の多層配線層55に形成されたアルミ配線57に達する。

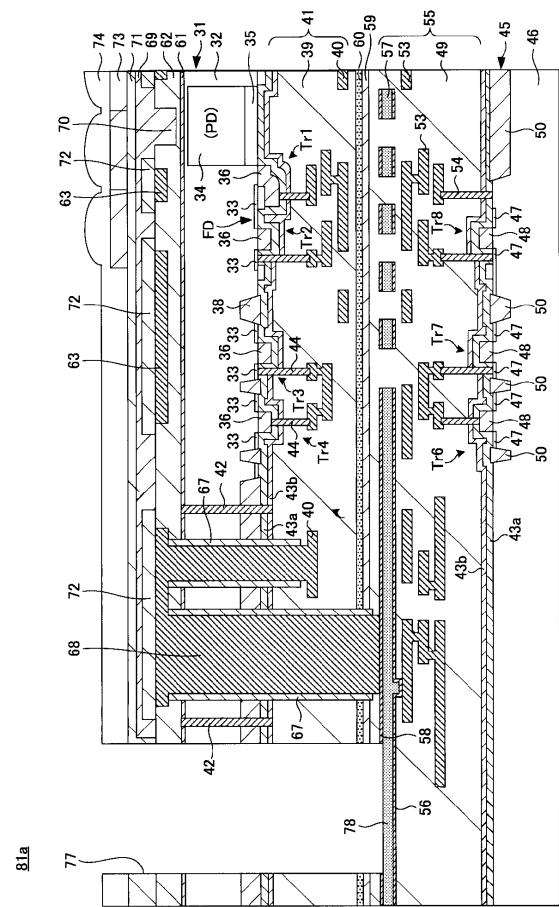

#### 【0070】

この時点では未だ画素アレイの製造プロセスとしてオンチップカラーフィルタ、オンチップレンズの加工工程を経ておらず、未完成である。それと共に、銅配線40上に形成された接続孔66とアルミ配線57上に形成された貫通接続孔65は、従来のウェハプロセスの延長で加工、形成することが可能である。一方、ロジック回路25においても、回路技術として最適な最上層のメタル配線までの工程であって未完成である。このように、半製品である異種基板を貼り合わせるので、完成品とされた異種基板を貼り合わせる場合よりも製造コストの抑制を可能となる。40

#### 【0071】

その後、図13に示すように、溝部64、遮光膜用溝部82、接続孔66、及び貫通接続孔65を含む領域に、例えば、銅などの導電材料を形成し、CMP(Chemical Mechanic

al Polising) 法で表面を研磨する。これにより、溝部 64、遮光膜用溝部 82、接続孔 66、及び貫通接続孔 65 の導電材料のみを残存させる。これにより、絶縁スペーサ層 42 内の領域では、基板間配線 68 が形成されると共に、遮光領域では遮光膜 63 が形成される。本実施形態例では、接続孔 66 内に形成された基板間配線 68、及び貫通接続孔 65 内に形成された基板間配線 68 は、溝部 64 に形成されたダマシン配線からなる接続配線 68a により電気的に接続される。また、遮光膜 63 もダマシン法によって形成される。そして、溝部 64、遮光膜用溝部 82、接続孔 66、及び貫通接続孔 65 が導電材料で埋め込まれることにより、第 1 の多層配線層 41 に形成された銅配線 40 と第 2 の多層配線層 55 に形成されたアルミ配線 57 とが電気的に接続される。

## 【0072】

10

そして、このとき、第 2 の半導体基板 45 上の第 2 の多層配線層 55 に形成されたアルミ配線 57 上部にはバリアメタル層 58 が形成されるため、基板間配線 68 を銅で形成した場合でも、銅の拡散が防止される。また、接続孔 66 及び貫通接続孔 65 の孔内における第 1 の半導体基板 31 を貫通する側壁には、絶縁層 67 が形成されている。このため、基板間配線 68 と第 1 の半導体基板 31 とが電気的に分離されており、接続されることがない。また、本実施形態例では、基板間配線 68 は、第 1 の半導体基板 31 に形成された絶縁スペーサ層 42 の領域内に形成されるので、これによつても、基板間配線 68 と第 1 の半導体基板 31 が電気的に接続されることが防止される。

## 【0073】

20

本実施形態例の基板間配線 68 の形成工程では、溝部 64 と遮光膜用溝部 82、接続孔 66、貫通接続孔 65 を 3 段階に分けて形成し、銅を埋め込むダマシン法を用いたが、これに限られるものでは無い。第 1 の半導体基板 31 上部の第 1 の多層配線層 41 の銅配線 40 と、第 2 の半導体基板 45 上部の第 2 の多層配線層 55 のアルミ配線 57 とが電気的に接続される基板間配線 68 が形成される例であれば種々の変更が可能である。

## 【0074】

たとえば、基板間配線 68 は、CVD 法やスパッタ法などにより形成し、通常のリソグラフィーとドライエッティングにより形成することも可能であるが、配線層を積み上げることにより感度劣化が許容し難くなる。このため、絶縁膜の積み増しが少ないダマシン配線構造を適用することが望ましい。

## 【0075】

30

また、本実施形態例では、遮光膜 63 を形成するための遮光膜用溝部 82 を、基板間配線 68 を形成するための溝部 64 と同時に加工する構成としたが、溝部 64、接続孔 66、貫通接続孔 65 及び絶縁スペーサ層 42 の形成後に形成してもよい。この場合にも、遮光膜用溝部 82 は、溝部 64 と同層に形成し、遮光膜用溝部 82 内への導電材料の埋め込みは、溝部 64、接続孔 66、及び貫通接続孔 65 への導電材料の埋め込みと同時に行う。遮光膜用溝部 82 を溝部 64、接続孔 66、及び貫通接続孔 65 と一緒に加工する方が工程としては簡略化される。しかしながら、この場合には、絶縁スペーサ層 42 を形成する際に遮光膜用溝部 82 内にも絶縁スペーサ層 42 が形成されてしまい、所望の遮光膜 63 の線幅が得られない可能性がある。画素の微細化が進んだ場合は、遮光膜用溝部 82 を溝部 64、接続孔 66、及び貫通接続孔 65 と別工程で形成する方がより望ましい。

40

## 【0076】

従来は、遮光膜 63 は、基板間配線 68 を形成する前の工程において、タンゲステンやアルミニウムなどによって別に形成されていたが、基板間配線 68 の形成と同時のダマシン法によって形成することにより、工程を簡略できる。それと共に、第 1 の半導体基板 31 の受光部側(裏面側)の絶縁膜厚を薄膜化することができ、感度向上に寄与できる。

## 【0077】

また、貫通接続孔 65 は接続孔 66 の深さに対して、1.5 ~ 10 倍の範囲内で深くなるため、同じ開口サイズでは、接続孔 66 が導電材料で埋め込まれても、貫通接続孔 65 内の導電材料にボイドを生じることがあり得る。

## 【0078】

50

本実施形態例では、深さに応じて、開口サイズの異なる貫通接続孔 6 5 及び接続孔 6 6 を開口することにより、導電材料の埋め込みに最適なアスペクト比で、かつ、レイアウトスペースも大きくならない孔を形成することを可能としている。これにより、深さの深い貫通接続孔 6 5 においても、導電材料の埋め込み時におけるボイドの発生を防止することができる。

#### 【0079】

また、本実施形態例では、接続孔 6 6 は第 1 の半導体基板 3 1 上部の第 1 の多層配線層 4 1 の最下層の銅配線 4 0 に接続する構成としているため、接続孔 6 6 の周辺やその直下のスペースを、配線を通すことのできる有効スペースとして活用できる。このため、チップの縮小化に有利に働く。

10

#### 【0080】

なお、本実施形態例では、基板間配線 6 8 と第 1 の半導体基板 3 1 との絶縁は、絶縁層 6 7 及び、絶縁スペーサ層 4 2 で行う例としたが、どちらか一方で構成する例としてもよい。絶縁スペーサ層 4 2 を形成しない場合には、絶縁スペーサ層 4 2 分の領域が必要無くなるので、画素面積の縮小や、フォトダイオード ( P D ) の面積の拡大が可能となる。

#### 【0081】

次に、図 14 に示すように、基板間配線 6 8 、及び遮光膜 6 3 の上部を覆うように、キャップ膜 7 2 を形成する。このキャップ膜 7 2 は、例えば SiN 膜、又は SiCN 膜を 10 ~ 150 nm で成膜することにより形成することができる。その後、フォトダイオード ( P D ) 上部の絶縁膜 6 2 に開口部を形成し、その開口部を含む所望の領域に導波路材料膜 6 9 を成膜する。導波路材料膜 6 9 としては、例えば、SiN を用いることができ、開口部に形成された導波路材料膜 6 9 により、導波路 7 0 が構成される。導波路 7 0 を形成することにより、第 1 の半導体基板 3 1 の裏面側から入射してくる光は、効率よくフォトダイオード ( P D ) に集光される。その後、導波路材料膜 6 9 を含む全面に平坦化膜 7 1 を形成する。

20

#### 【0082】

本実施形態例では、キャップ膜 7 2 と、その上部の導波路材料膜 6 9 を別の工程で別々に形成したが、導波路材料膜 6 9 をキャップ膜 7 2 に兼用する例としてもよい。また、本実施形態例では、フォトダイオード ( P D ) の光入射面側に導波路 7 0 を形成する例としたが、導波路 7 0 を形成しない例としてもよい。

30

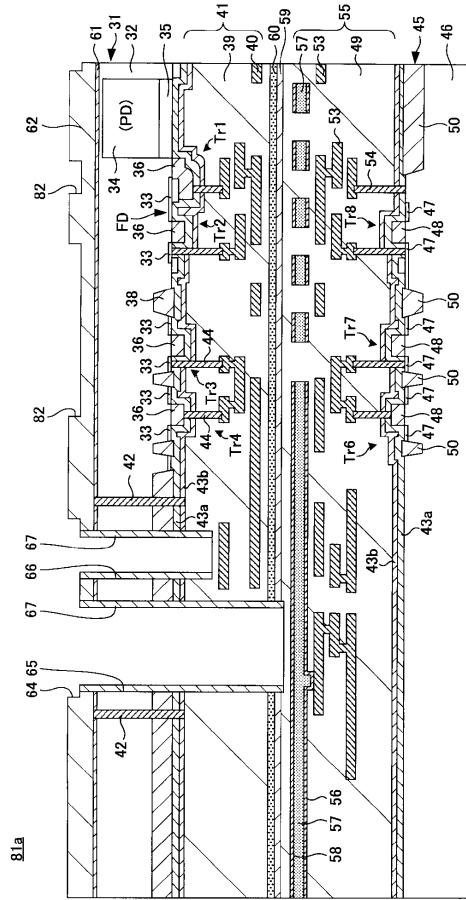

#### 【0083】

次に、図 15 に示すように、平坦化膜 7 1 上に各画素に対応して例えば赤 ( R ) 、緑 ( G ) 、青 ( B ) のオンチップカラーフィルタ 7 3 を形成する。オンチップカラーフィルタ 7 3 は、所望の色の顔料又は染料が含有された有機膜を成膜し、パターニングすることにより、所望の画素アレイを構成するフォトダイオード ( P D ) 上部に形成することができる。その後、オンチップカラーフィルタ 7 3 上部を含む画素アレイ領域にオンチップレンズ材料 7 4 a を成膜する。オンチップレンズ材料 7 4 a としては、例えば有機膜、又は SiO 、 SiN 、 SiON 等の無機膜を用いることができ、3000 nm ~ 4500 nm に成膜する。

40

#### 【0084】

次に、図 16 に示すように、オンチップレンズ材料 7 4 a 上部の各画素に対応する領域に、オンチップレンズ用のレジスト膜 7 5 を、例えば 300 nm ~ 1000 nm の厚みに形成し、エッティング処理を行う。これにより、オンチップレンズ用のレジスト膜 7 5 の形状が、オンチップレンズ材料 7 4 a に転写され、図 17 に示すように、各画素上部に、オンチップレンズ 7 4 が形成される。その後、CF<sub>4</sub> 系のガス ( 流量 10 ~ 200 sccm ) により、第 1 の半導体基板 3 1 上部に形成された絶縁膜 6 2 等の酸化膜をエッティングし、第 1 の半導体基板 3 1 を露出させる。

#### 【0085】

次に、図 18 に示すように、オンチップレンズ 7 4 上部に、図 3 の電極パッド部 7 8 が開口されたレジスト膜 7 6 を形成する。このレジスト膜 7 6 は、図 18 に示すように、開

50

□端部がオンチップレンズ74の端部よりも画素側にくるように形成する。

#### 【0086】

次に、レジスト膜76をマスクとして所望のエッティング条件でエッティング処理する。これにより、図19に示すように、最上層の基板である第1の半導体基板31側からエッティングされ、第1の多層配線層41と第2の多層配線層55の接合面を貫通する貫通開口部77が形成される。そして、最下層の基板である第2の半導体基板45上部に形成された第2の多層配線層55に形成されたアルミ配線57が露出するまで貫通開口部77を形成する。このエッティング工程では、例えば、SF<sub>6</sub>/O<sub>2</sub>系のガス（流量は、SF<sub>6</sub>:50~500sccm、O<sub>2</sub>:10~300sccm）を用い、1~60分間エッティング処理することにより、第1の半導体基板31をエッティング除去することができる。その後、CF<sub>4</sub>系のガス（流量10~150sccm）を用いて1~100分間エッティング処理することにより、アルミ配線57に至るまでの酸化膜等をエッティング除去することができる。10

#### 【0087】

そして、このようにして露出されたアルミ配線57は、外部配線との接続を行う際に用いられる電極パッド部78とされる。以下、露出されたアルミ配線57を電極パッド部78という。この電極パッド部78は、各チップに形成される画素領域の外側の3辺若しくは4辺に複数ずつ形成されるのが好ましい。

#### 【0088】

そして、図19に示したような2つ半導体基板を積層して形成された積層体81aは、その後、ダイシング加工することにより各チップ部に分割される。これにより、図4に示すように、第1の半導体チップ部22と第2の半導体チップ部26とからなる固体撮像装置81が完成される。20

#### 【0089】

このようにして形成された固体撮像装置81は、図4に示すように、電極パッド部78に対してボンディングワイヤ79を接続し、ボンディングワイヤ79によって実装基板の外部配線と接続することができる。そして、電極パッド部78に外部配線が電気的に接続されることにより、基板間配線68で接続された第1の多層配線層41、及び第2の多層配線層55の各配線間も電気的に接続される。

#### 【0090】

第1の実施形態の固体撮像装置81では、電極パッド部78に対してボンディングワイヤ79を接続する例としたが、半田バンプを用い、電極パッド部78と外部配線とを接続することができる。ユーザの希望により、ボンディングワイヤか半田バンプを選択することができる。30

#### 【0091】

なお、第1の実施形態において、半導体ウェハでの固体撮像装置81に対する検査は、電極パッド部78を用いて行われる。また、検査は、ウェハ状態での検査と、チップに切断して最終モジュール状態での検査の2回である。

#### 【0092】

第1の実施形態に係る固体撮像装置81及びその製造方法によれば、第1の半導体基板31側のチップ部に画素領域23及び制御領域24を形成し、第2の半導体基板45側のチップ部に信号処理するロジック回路25を形成している。このように画素アレイの機能とロジック機能を異なるチップ部に形成した構成であるので、画素アレイ、ロジック回路のそれぞれに最適なプロセス形成技術を用いることができる。従って、画素アレイ、ロジック回路それぞれの性能を十分に発揮させることができ、高性能の固体撮像装置を提供することができる。40

#### 【0093】

図2Cの構成を採用すれば、第1の半導体チップ部22側には光を受ける画素領域23を形成するだけで良く、その制御領域24及びロジック回路25は分離して第2の半導体チップ部26に形成することができる。これによって、それぞれの機能チップに最適なプロセス技術を独立して選択できると共に、製品モジュールの面積も削減することができる50

。

#### 【 0 0 9 4 】

従来のウェハプロセス技術で画素アレイとロジック回路との混載を可能にするので、製造も容易である。

#### 【 0 0 9 5 】

また、本実施形態例では、画素領域 2 3 及び制御領域 2 4 を有する第 1 の半導体基板 3 1 と、ロジック回路 2 5 を有する第 2 の半導体基板 4 5 を共に半製品状態で貼り合わせ、第 1 の半導体基板 3 1 を薄肉化している。つまり、第 2 の半導体基板 4 5 を、第 1 の半導体基板 3 1 の薄肉化の際の支持基板として用いている。これによって、部材の節約、製造工程の節減を図ることができる。さらに、薄肉化後に貫通接続孔 6 5 、接続孔 6 6 の形成を行うので、孔のアスペクト比が小さくなり、高精度の接続孔の形成が可能になる。10

#### 【 0 0 9 6 】

また、基板間配線 6 8 は、低アスペクト比の貫通接続孔 6 5 及び接続孔 6 6 に導電材料を埋め込むことで形成できるため、被覆性の良いタンゲステン (W) などの金属材料は勿論のこと、被覆性の悪い例えば銅 (Cu) などの金属材料を用いることができる。つまり、基板間配線 6 8 を構成する導体材料の制約を受けることがない。これにより、画素領域及び制御回路と、ロジック回路の電気的接続を高精度で行うことができる。従って、量産性を図り、製造コストを抑え、且つ高性能の固体撮像装置を製造することができる。

#### 【 0 0 9 7 】

さらに、本実施形態例では、電極パッド部 7 8 を開口するために形成された貫通開口部 7 7 は、第 1 の多層配線層 4 1 と第 2 の多層配線層 5 5 の接合面を貫通して形成され、電極パッド部 7 8 は、接合面より下層の第 2 の多層配線層 5 5 の配線で構成される。これにより、電極パッド部 7 8 は、第 1 の多層配線層 4 1 と第 2 の多層配線層 5 5 との間の脆弱な面とされる接合面よりも下層に形成される。このため、例えば、ボンディングワイヤ 7 9 を電極パッド部 7 8 に押し付ける際に、脆弱な面となる接合面にかかるボンディング応力を低減することができる。これにより、ワイヤボンディング時において、脆弱な接合面からクラックが発生するのを防ぐことができる。20

#### 【 0 0 9 8 】

本実施形態例では、2 層の半導体ウェハを積層する例としたが、2 層以上の複数層積層する構成に本発明を応用することができる。その場合には、一番下層の半導体ウェハの配線層を構成する配線が露出するように貫通開口部を形成し、その露出された配線を配線パッド部とする。これにより、外部配線と電極パッド部との接続を行う際に、基板間の脆弱な接合面に応力が発生することを低減することができる。30

#### 【 0 0 9 9 】

また、本実施形態例のように、裏面照射型の固体撮像装置では、受光部となるフォトダイオードを回路に近づけることが必要であるため、上述したような半導体層の薄肉化が必須とされている。また、接合面よりも下側の配線を露出させるための開口はより浅い方が好みらしい。したがって、本実施形態例のように上層の半導体基板（本実施形態例では、第 1 の半導体基板）が画素アレイを備えた固体撮像素子である場合には、半導体層が薄肉化された第 1 の半導体基板側から電極パッド部を開口することが好みらしい。40

#### 【 0 1 0 0 】

なお、上述の実施の形態に係る固体撮像装置では、信号電荷を電子とし、第 1 導電型を p 型、第 2 導電型を n 型として構成したが、信号電荷を正孔とする固体撮像装置にも適用できる。この場合、各半導体基板、半導体ウェル領域あるいは半導体領域の導電型を逆にし、n 型が第 1 導電型、p 型が第 2 導電型となる。

#### 【 0 1 0 1 】

上述の第 1 の実施形態例では、MOS 型固体撮像装置を例としたが、本発明は、半導体装置にも適用することができる。次に、本発明の第 2 の実施形態として、異種チップが積層された構造を有する半導体装置について説明する。

#### 【 0 1 0 2 】

10

20

30

40

50

### 3. 第2の実施形態

#### [半導体装置の構成例とその製造方法例]

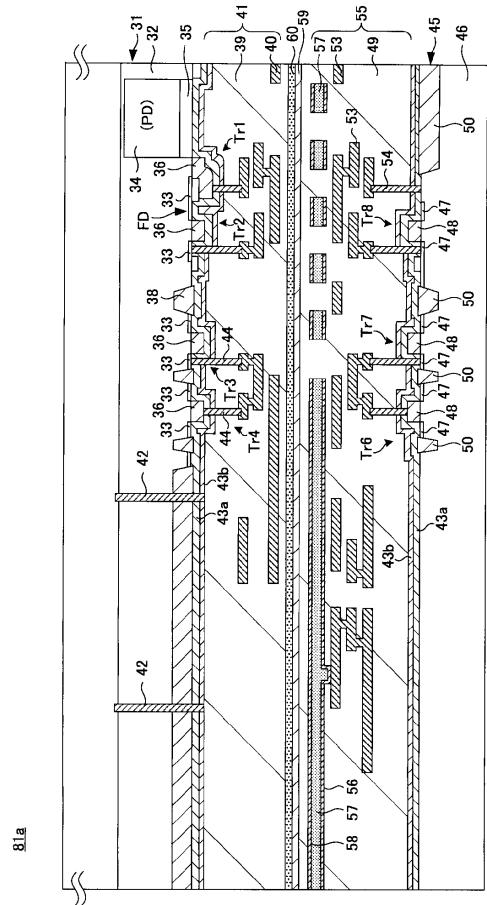

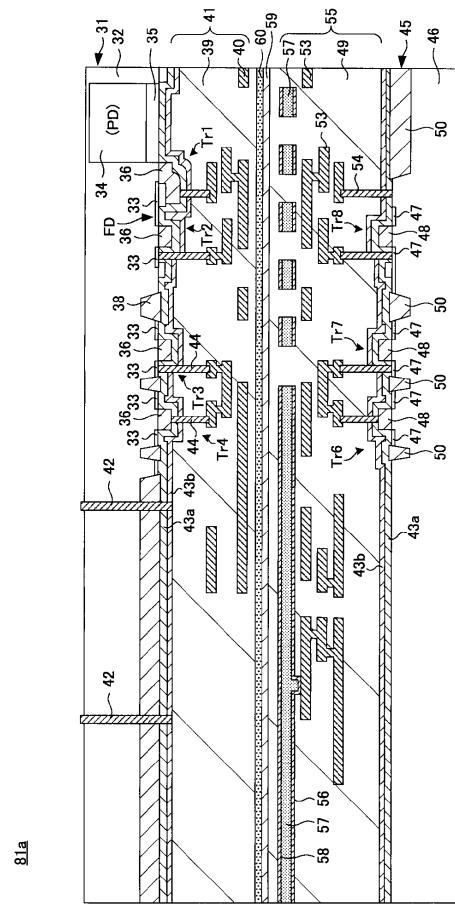

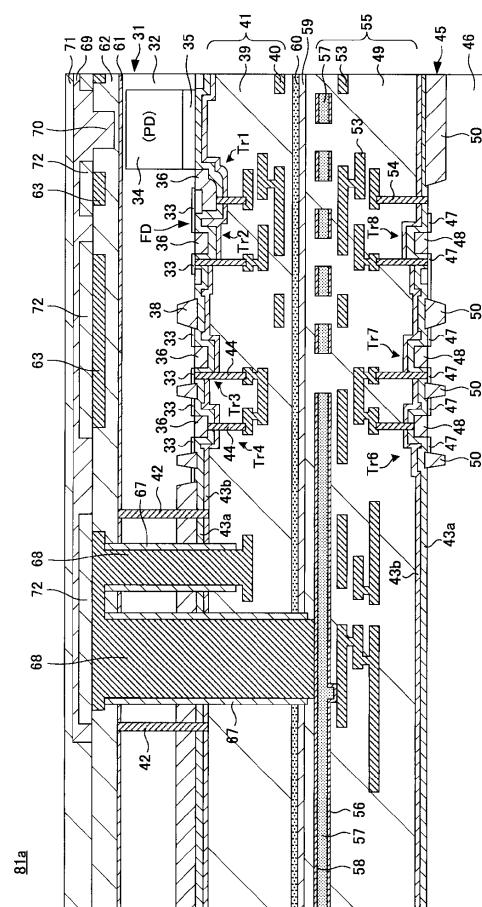

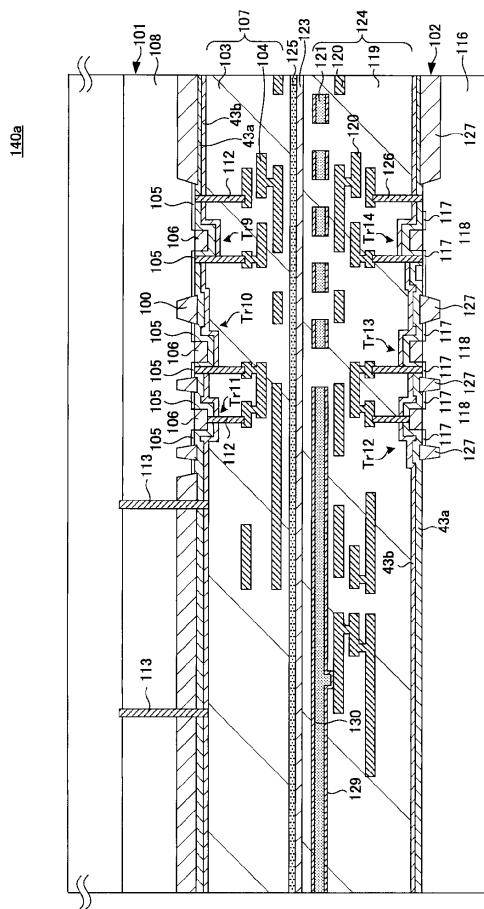

図20～図26を用いて、本発明の第2の実施形態に係る半導体装置をその製造方法と共に説明する。本実施形態例の半導体装置140は、第1の半導体集積回路が形成された第1の半導体基板101と第2の半導体集積回路が形成された第2の半導体基板102が積層して構成された半導体装置である。図20において、図4に対応する部分には同一符号を付し重複説明を省略する。

#### 【0103】

第2の実施形態においては、先ず、図21に示すように、第1の半導体基板(半導体ウェハ)101の各チップ部となる領域に、半製品状態の第1の半導体集積回路、本例ではロジック回路を形成する。すなわち、シリコン基板からなる第1の半導体基板101に形成した半導体ウェル領域108の各チップ部となる領域に、複数のMOSトランジスタTr9、Tr10、Tr11を形成する。各MOSトランジスタTr9～Tr11は、それぞれ1対のソース／ドレイン領域105と、ゲート絶縁膜を介して形成されたゲート電極106とを有して構成される。各MOSトランジスタTr9～Tr11は、素子分離領域100により分離される。

#### 【0104】

MOSトランジスタは、複数形成されるものであるが、図21では、MOSトランジスタTr9～Tr11をその代表として示した。ロジック回路は、CMOSトランジスタで構成することができる。このため、これら複数のMOSトランジスタTr9～Tr11としては、nチャネルMOSトランジスタ、あるいはpチャネルMOSトランジスタとして構成することができる。従って、nチャネルMOSトランジスタを形成するときは、p型の半導体ウェル領域108にn型のソース／ドレイン領域が形成される。pチャネルMOSトランジスタを形成するときは、n型の半導体ウェル領域にp型のソース／ドレイン領域が形成される。

#### 【0105】

なお、第1の半導体集積回路としては、ロジック回路に代えて、例えば半導体メモリ回路とすることもできる。この場合、後述する第2の半導体集積回路となるロジック回路は半導体メモリ回路の信号処理に供される。

#### 【0106】

また、第2絶縁薄膜43b形成後、第1の実施形態と同様に、第1の半導体基板101の半導体ウェル領域108内の所望の領域を分離する絶縁スペーサ層113を形成する。絶縁スペーサ層113は、第2絶縁薄膜43b形成後、第1の半導体基板101の所望の位置を裏面側から開口し、絶縁材料を埋め込むことで形成される。この絶縁スペーサ層113は、図20の基板間配線115を囲む領域に形成されるものである。

#### 【0107】

次いで、第1の半導体基板101上に層間絶縁膜103を介して複数層、本例では3層の銅配線104を積層した第1の多層配線層107を形成する。本実施形態例では、第1の多層配線層107を構成する配線を銅で構成する例としたが、その他の金属材料でメタル配線を構成することもできる。これらの第1の多層配線層107は、第1の実施形態例と同様にして形成することができる。なお、各MOSトランジスタTr9～Tr11は所要の1層目の銅配線104と接続導体112を介して接続する。また、3層の銅配線104は接続導体112を介して相互に接続する。

#### 【0108】

一方、図22に示すように、第2の半導体基板(半導体ウェハ)102の各チップ部となる領域に、半製品状態の第2の半導体集積回路、本例ではロジック回路を形成する。すなわち、図20と同様に、シリコンからなる第2の半導体基板102に形成した半導体ウェル領域116の各チップ部となる領域に、複数のMOSトランジスタTr12、Tr13、Tr14を形成する。各MOSトランジスタTr12～Tr14は、それぞれ1対のソース／ドレイン領域117と、ゲート絶縁膜を介して形成されたゲート電極118とを有

10

20

30

40

50

して構成される。また、各MOSトランジスタTr12～Tr14は、素子分離領域127により分離される。

#### 【0109】

MOSトランジスタは、複数形成されるものであるが、図24では、MOSトランジスタTr12～Tr14を代表として示した。ロジック回路は、CMOSトランジスタで構成することができる。このため、これら複数のMOSトランジスタとしては、nチャネルMOSトランジスタ、あるいはpチャネルMOSトランジスタとして構成することができる。従って、nチャネルMOSトランジスタを形成するときは、p型半導体ウェル領域にn型ソース／ドレイン領域が形成される。pチャネルMOSトランジスタを形成するときは、n型半導体ウェル領域にp型ソース／ドレイン領域が形成される。

10

#### 【0110】

次いで、第2の半導体基板102上に層間絶縁膜119を介して複数層、本例では4層のメタル配線を積層した第2の多層配線層124を形成する。本実施形態例では、3層の銅配線120と最上層に形成された1層のアルミ配線121とを形成する例とした。なお、各MOSトランジスタTr12～Tr14は所要の1層目の銅配線120と接続導体126を介して接続する。また、3層の銅配線120とアルミ配線121とは接続導体126により相互に接続される。さらに、本実施形態例においてもアルミ配線121の上下には、バリアメタル層129、130が成膜されており、アルミ配線121は、下層のバリアメタル層129を介して下層の銅配線120に接続されている。この第2の多層配線層124は、第1の実施形態の多層配線層と同様にして形成することができる。

20

#### 【0111】

そして、第2の多層配線層124上部には、第1の半導体基板101と第2の半導体基板102の貼り合わせの際に反りを軽減するための反り矯正膜123を形成する。反り矯正膜123も、第1の実施形態と同様にして形成することができる。

#### 【0112】

次に、図23に示すように、第1の半導体基板101と第2の半導体基板102とを、互いの第1の多層配線層107及び第2の多層配線層124が向かい合うように、貼り合わせる。貼り合わせは、例えば接着剤にて行う。接着剤にて接合する場合には、第1の半導体基板101又は第2の半導体基板102の接合面の一方の側に接着剤層125を形成し、この接着剤層125を介して重ね合わせて両者を接合する。本実施形態例では、接着剤層125を介して第1の半導体基板101と第2の半導体基板102とを貼り合わせる例としたが、この他、プラズマ接合で貼り合わせる例としてもよい。プラズマ接合の場合には、第1の半導体基板101と第2の半導体基板102の接合面に、それぞれプラズマTEOS膜、プラズマSiN膜、SiON膜（ブロック膜）、あるいは、SiC膜などを形成する。この膜が形成された接合面をプラズマ処理して重ね合わせ、その後、アニール処理して両者を接合する。貼り合わせ処理は、配線などに影響を与えない400以下以下の低温プロセスで行なうことが好ましい。そして、第1の半導体基板101と第2の半導体基板102とが積層して張り合わされることにより、2つの異種基板からなる積層体140aが形成される。

30

#### 【0113】

次に、図24に示すように、一方の第1の半導体基板101を、裏面側から研削、研磨して薄肉化する。第1の半導体基板101の厚さは例えば600μm程度としたとき、膜厚が例えば5～10μm程度となるように、薄肉化する。

40

#### 【0114】

次に、図25に示すように、薄肉化したのち、第1の実施形態における図10～図13と同様の工程にて、絶縁スペーサ層113内に溝部164、貫通接続孔165及び接続孔166を形成する。その後、溝部164、貫通接続孔165及び接続孔166内に絶縁層114を介して基板間配線115を形成する。また、図示を省略するが、必要に応じて、第1の実施形態と同様に遮光領域には、遮光膜を形成する。本実施形態例においても、貫通接続孔165及び接続孔166は、第1の半導体基板101を薄肉化した後に形成する

50

ので、アスペクト比が小さくなり、微細孔として形成することができる。また、本実施形態例においても、深さに応じて、開口サイズの異なる貫通接続孔 165 及び接続孔 166 を別々に開口することにより、導電材料の埋め込みに最適なアスペクト比で、かつ、レイアウトスペースも大きくならない孔を形成することを可能としている。これにより、深さの深い貫通接続孔 165 においても、導電材料の埋め込み時におけるボイドの発生を防止することができる。

#### 【0115】

そして、基板間配線 115 により、第 1 の半導体基板 101 に形成された回路と第 2 の半導体基板 102 に形成された回路が電気的に接続される。その後、第 1 の実施形態と同様にして、基板間配線 115 上部を含む全面にキャップ膜 72 を成膜する。

10

#### 【0116】

次に、所望の領域が開口されたマスク（図示せず）用いて、図 26 に示すようにエッチングすることにより、第 1 の半導体基板 101 を貫通する貫通開口部 132 を形成し、アルミ配線 121 を露出させる。これにより、露出されたアルミ配線 121 からなる電極パッド部 142 が形成される。

その後、ダイシング加工することにより、各チップ部に分割することで、図 20 に示す本実施形態例の半導体装置 140 が完成される。

#### 【0117】

分割された各チップは、図 20 に示すように、電極パッド部 142 に対してポンディングワイヤ 131 を接続し、ポンディングワイヤ 131 によって実装基板の外部配線と接続することができる。そして、電極パッド部 142 に外部配線が電気的に接続されることにより、基板間配線 115 で接続された第 1 の半導体基板 101 及び第 2 の半導体基板 102 に形成されたそれぞれの配線間（回路間）も電気的に接続される。

20

#### 【0118】

第 2 の実施形態に係る半導体装置 140 及びその製造方法によれば、前述と同様に、異なるチップ部にそれぞれ第 1 の半導体集積回路、第 2 の半導体集積回路を最適なプロセス技術で形成することができ、高性能の半導体集積回路を提供することができる。また、半製品状態で第 1 及び第 2 の半導体ウェハを貼り合わせ、薄肉化し、また第 1 及び第 2 の半導体集積回路の電気接続の後、完成品状態としてチップ化することにより、製造コストの低減を図ることができる。

30

#### 【0119】

その他、第 1 の実施形態と同様の効果を得ることができる。

#### 【0120】

上述の第 1 の実施形態、及び第 2 の実施形態では、基板間配線は、第 1 の半導体基板に形成された第 1 の半導体集積回路と第 2 の半導体基板に形成された第 2 の半導体集積回路とを電気的に接続する配線としてのみ用いる例を示した。しかしながら、これに限定されるものではなく、例えば、基板間配線を用いることで、第 1 の半導体基板と第 2 の半導体基板とで別個に形成されていた同電位の配線（例えば、電源配線や接地配線）の一部を、各基板で共通に用いることができる。

以下に、基板間配線を、第 1 の半導体基板及び第 2 の半導体基板に共通に用いられる電源配線、及び接地配線として形成する例を説明する。

40

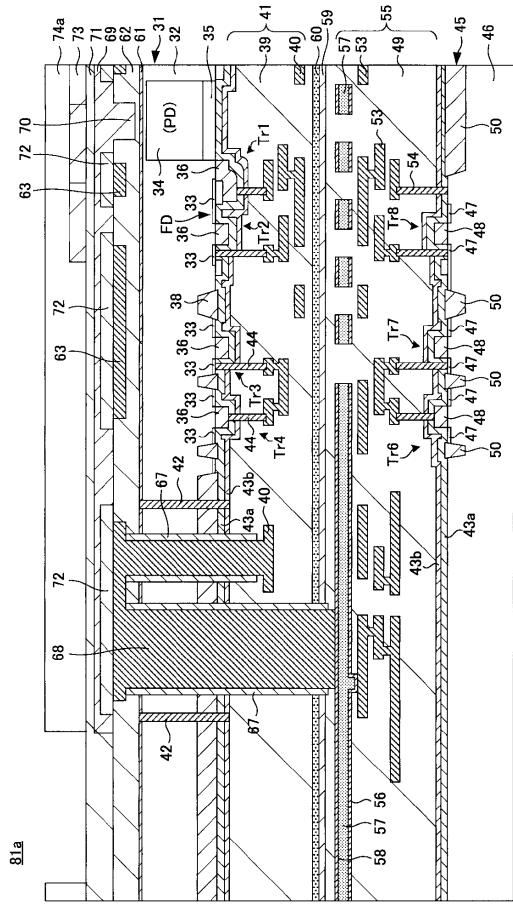

#### 【0121】

##### 4. 第 3 の実施形態

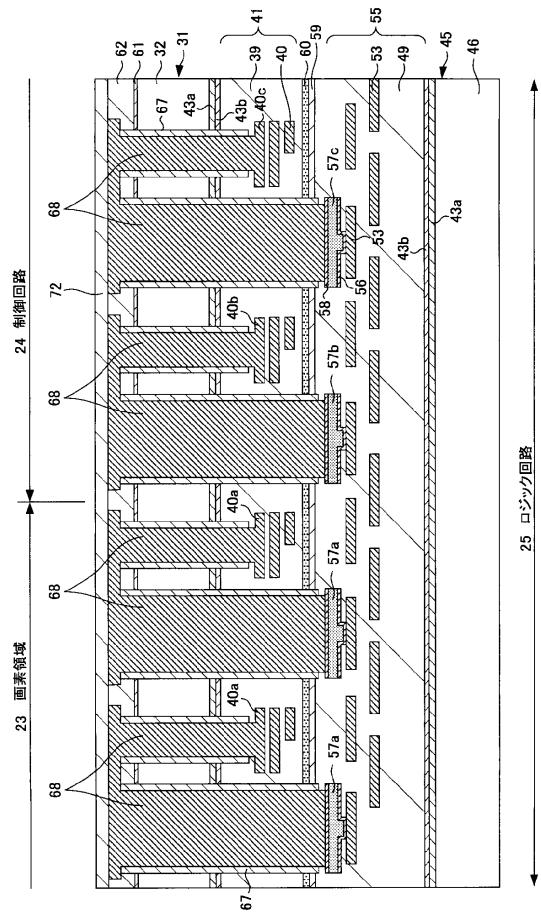

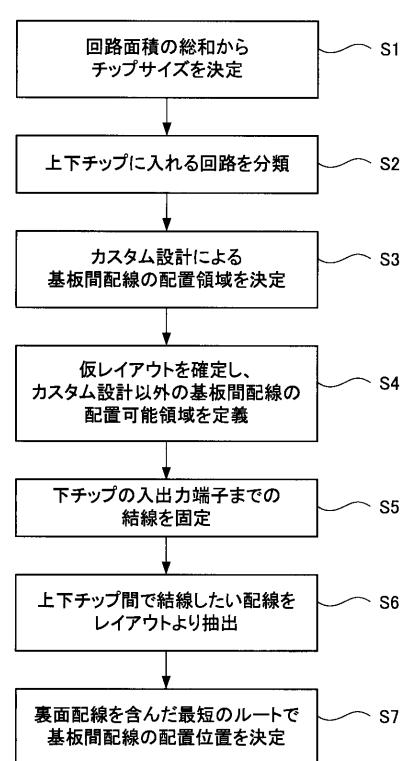

図 27 に、本発明の第 3 の実施形態に係る固体撮像装置の概略構成図を示す。図 27 において、図 4 に対応する部分には同一符号を付し、重複説明を省略する。

#### 【0122】

図 27 は、固体撮像装置の画素領域 23 と、制御領域 24 とを含む領域を示したものであり、簡略化のため、トランジスタやフォトダイオードの図示を省略する。

#### 【0123】

図 27 に示すように、画素領域 23 では、第 1 の半導体基板 31 に形成された画素信号

50

を出力する銅配線 40a が、基板間配線 68 を介して第 2 の多層配線層 55 の最上層の配線で形成された信号配線 57a に接続されている。この場合には、図 3 に示す回路構成において、第 1 の半導体基板 31 に形成された選択トランジスタのドレインに接続される配線と、信号配線との間に基板間配線が形成されている。そして、信号配線 57a より後段の処理は、第 2 の半導体基板 45 で構成されたロジック回路 25 内で行われる。

#### 【0124】

本実施形態例では、第 2 の多層配線層 55 の最上層の配線で形成された電源配線 57b 及び接地配線 57c と、第 1 の多層配線層 41 の最上層の配線で形成された銅配線 40b、40c とが基板間配線 68 を介して接続されている。これにより、第 1 の半導体基板 31 と第 2 の半導体基板 45 との間で、電源配線 57b、及び接地配線 57c が共有されている。10

#### 【0125】

2 枚の半導体基板を貼り合わせて基板間配線で接続する 3 次元デバイスにおいては、基板の貼り合わせ面における段差低減のために、配線層（図 27 では、第 1 の多層配線層 41 及び第 2 の多層配線層 55 に相当）を厚く形成することができないという問題がある。このため、従来の 3 次元デバイスでは、配線間の距離が近くなり、配線間抵抗を下げることができず、2 つの半導体基板上に、別々に電源配線や接地配線を形成すると大きな不可抵抗が乗り、素子の肥大化、ないし電源降下によるノイズの原因となる。

#### 【0126】

本実施形態例の固体撮像装置では、基板間配線 68 を経由して、電源配線 57b や接地配線 57c を上下に形成された第 1 の半導体基板 31 及び第 2 の半導体基板 45 の間で共有化することにより、実効的に低抵抗な配線を形成することができる。また、薄肉化した第 1 の半導体基板 31 の裏面側に基板間配線 68 に接続される裏面配線を形成することにより、素子や異電位配線を跨ぐことも可能である。20

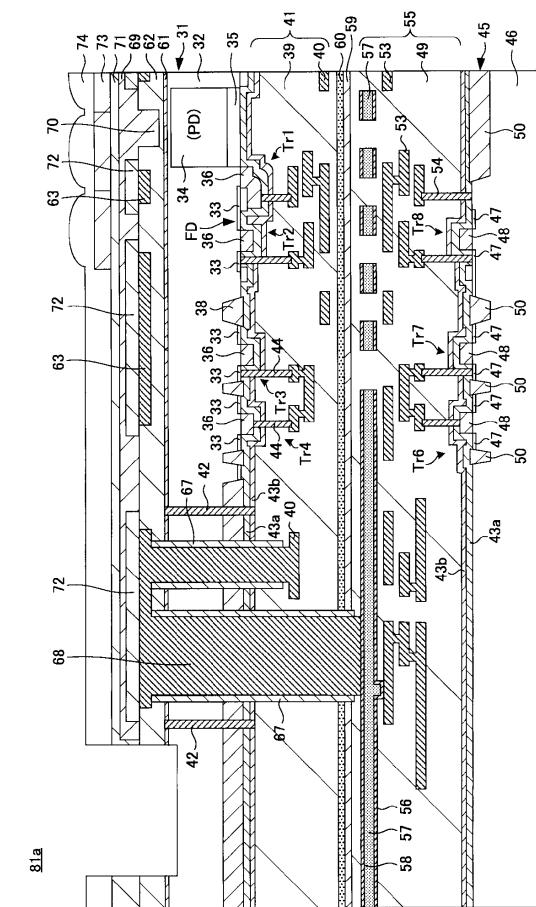

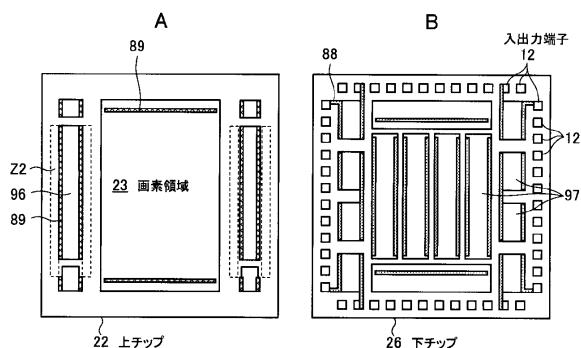

#### 【0127】

以下に、第 1 の半導体チップ（以下、上チップ）と第 2 の半導体チップ（以下、下チップ）が積層された積層チップにおける配線レイアウト、及びその設計方法について説明する。

#### 【0128】

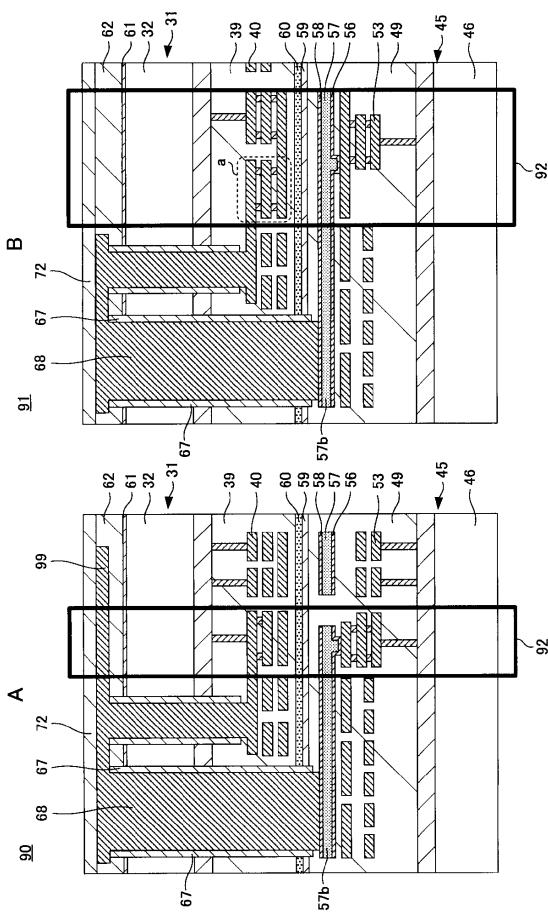

図 28A に、本実施形態例の固体撮像装置において、電源配線 57b が形成される電源供給回路 92 の一部を裏面配線 99 で形成した場合の積層チップ 90 の概略構成図を示す。また、図 28B に、比較例として、電源配線 57b が形成される電源供給回路 92 を全て第 2 の多層配線層 55 内に形成した場合の積層チップ 91 の概略構成図を示す。30

#### 【0129】

図 28A に示すように、第 1 の半導体基板 31 と第 2 の半導体基板 45 との間で、基板間配線 68 を介してチップ間の電源配線を共有する。そして、電源供給回路 92 の電源配線に接続される端子の実装基板への接続は、第 2 の多層配線層 55 の最上層の電源配線 57b を介して行う。また、第 1 の多層配線層 41 で形成された電源供給回路 92 の一部は、レイアウトの重複を最小にできる位置で中断され、基板間配線 68 を介して裏面配線 99 で構成されている。すなわち、比較例として示した図 28B の構成における電源供給回路 92 の一部（破線で囲む領域 a）を、本実施形態例では、第 1 の半導体基板 31 の裏面側に形成された裏面配線 99 で構成する。この場合、裏面配線 99 は、基板間配線 68 上部に形成される接続配線 68a と同様にダマシン法で形成することができる。40

#### 【0130】

このように、図 28A の例では電源供給回路 92 の一部を第 1 の半導体基板 31 の裏面側に移動し、裏面配線 99 によって構成することにより、配線を縦に積層することができる。このため、図 28B の構成に比較して、電源供給回路 92 の面積を縮小することができる。

#### 【0131】

図 29A に、本実施形態例における積層チップ 90 の、電源配線から電源端子への接続50

、及び接地配線から接地端子への接続を示したブロック図を示す。また、図29Bに、比較例における積層チップ91における回路部の、電源配線から電源端子への接続、及び接地配線から接地端子への接続を示したブロック図を示す。

#### 【0132】

図29A、Bでは、上チップと下チップとが積層された積層チップ90、91を上面から見たときの要部の概略構成図であり、上チップに形成された回路部96と下チップに形成された回路部97を模式的に示したものである。

#### 【0133】

比較例では、図29Bに示すように、上チップの回路部96の電源配線40b及び接地配線40cと、下チップの回路部97の電源配線57b及び接地配線57cが、別々に各電源端子95及び接地端子94に接続されている。この場合、上チップ及び下チップの両方において、電源配線40b、57b及び接地配線40c、57cの引き回しが必要となる。

10

#### 【0134】

このように、積層チップの設計において、上下のチップをそれぞれ独立して動作させるためには、電源配線又は接地配線等の入出力端子までの結線、及び入出力部の保護回路(図示せず)はそれぞれのチップ内で完結させなければならない。しかしながら、図29Bに示すような積層チップ91では電源配線や接地配線などの共有電位の配線や、図示しない保護回路を両方のチップに重複して配置する構成はレイアウト効率が悪く、チップコストを上げる要因となる

20

#### 【0135】

これに対し、本実施形態例の構成では、図29Aに示すように、上チップ、及び下チップ内の電源配線40b、57b及び接地配線40c、57cは、それぞれ接続孔66及び貫通接続孔65に形成された基板間配線や裏面配線99を介して接続されている。そして、接地端子94及び電源端子95への接続は、下チップの電源配線57b及び接地配線57cで行われる。このため、上チップでは、電源配線40b及び接地配線40cが基板間配線68に接続された後は、配線の引き回しが不要ない。これにより、図29Bの例に比較して、図29Aに示す破線で囲まれた領域zに余剰スペースができるので、この余剰スペースに新たな回路を形成することもできる。この結果、チップ面積を最大限に利用する最適な配置が実現できる。

30

#### 【0136】

本実施形態例では、回路の一部を、第1の半導体基板31の裏面側に形成した裏面配線99で構成する例としたが、配線の敷地面積に、余剰のスペースがより多くある基板側に2つのチップ間で共通の回路を形成すればよい。これにより、互いの多層配線層の配線层数やレイアウト面積を抑えることが可能となる。

#### 【0137】

ところで、本来同じ基板上で電源配線や接地配線等の同電位の配線が形成される場合には、隣接する回路間で共有し、レイアウト面積を抑えることは容易に実現できる。しかしながら、2層のチップを別々の基板に形成する構成では、相互の回路の結線経路が基板間配線によって限定されるため、共通電位の配線を共有することは容易ではない。

40

以下に、本実施形態例の固体撮像装置の設計を実現するための設計方法について説明する。

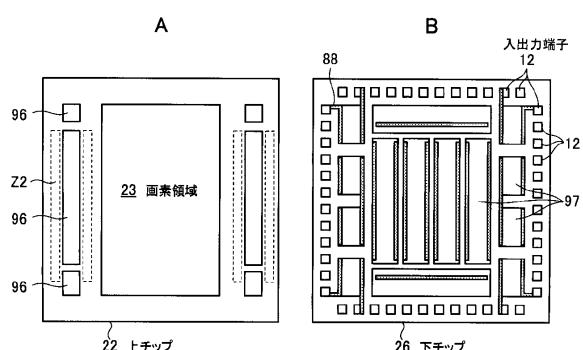

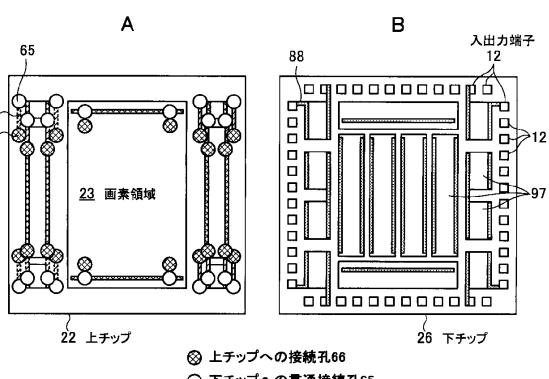

#### 【0138】

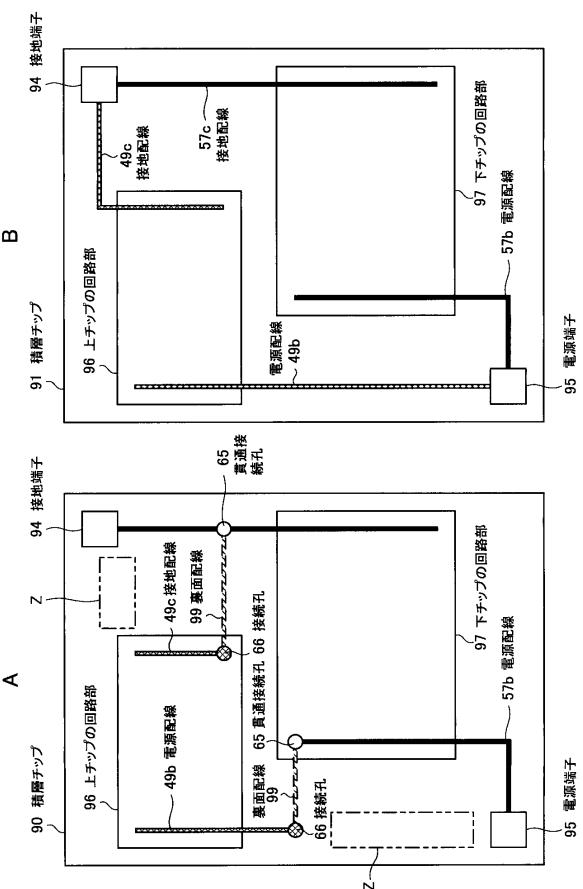

図30に、本実施形態例の固体撮像装置の設計方法を示し、図31～図34に、その設計プロセスに沿った上チップ(図31～図34のA)と下チップ(図31～図34のB)製造工程図を示す。

#### 【0139】

本実施形態例の固体撮像装置では、積層する上チップ22及び下チップ26間を基板間配線で接続するためには、回路や配線とバッティングしない位置に基板間配線68を配置することが重要である。

50

**【0140】**

まず、回路面積の総和からチップサイズを決定する(ステップS1)。次に、上チップ22及び下チップ26に入る回路を分類する(ステップS2)。本実施形態例では、図31A,Bに示すように、上チップ22に、画素領域23と、制御回路96を形成し、下チップ26に、ロジック回路97と入出力端子12を形成する例とする。

**【0141】**

次に、基板間配線のレイアウトを決定する。基板間配線のレイアウトは、上チップ22及び下チップ26との間で多くの信号線が直接接続するような個所(固体撮像装置においては、画素と信号配線との間の接続個所)などのように、カスタム設計(客先の注文による設計)された領域から決定する(ステップS2)。これにより、図32A,Bの領域z1で示される領域にカスタム設計による基板間配線の配置領域が決定される。図32A,Bに示すように、直接接続する回路面(すなわち、カスタム設計における基板間配線の位置)は上チップ22及び下チップ26で同じ位置に来なければならず、これを決定すると回路の大まかな配置が限定される。10

**【0142】**

次に、上チップ22及び下チップ26に搭載する回路部品の仮の外形サイズを定義し仮レイアウトを確定し、回路が配置されない隙間の領域を確定する。これにより、カスタム設計以外の基板間配線の配置可能領域(図32Aの領域z2)を確定する(ステップS4)。下チップ26に関しては、基板間配線を受ける配線を置くことができれば、その直下にも回路を置くことができる。しかしながら、上チップ22は、基板間配線を配置した場合、その直下と周辺には回路を置けなくなるため、基板間配線を配置する領域は、主に上チップ22の回路配置によって限定される。20

**【0143】**

次に、下チップ26における入出力端子12と各回路の接続結線の配線経路(図32Bの配線88)を通常の回路設計と同様の自動配線により求める(ステップS5)。これにより、図32Bに示すように、下チップ26における入出力端子12と、ロジック回路97が配線88により結線される。

**【0144】**

次に、上チップ22及び下チップ26間で結線したい同電位の配線を抽出する(ステップS6)。これにより、図33Aに示すように、上チップ22において、下チップ26の配線88と結線したい配線89がレイアウトされる。次に、図34A,Bに示すように、ステップS4で確定した基板間配線の配置可能領域内において、自動配置により上チップ22の配線89と下チップ26の配線88の間の距離が裏面配線を含んで最短になる位置に貫通接続孔65及び接続孔66の配置位置を決定する。これにより、基板間配線の配置位置を決定する(ステップS7)。すなわち、ここにおいて、裏面配線99の配線経路も決定される。これにより、下チップ26と上チップ22の所望の電極間が基板間配線で接続され、下チップ26に接続される基板間配線と、上チップ22に接続される基板間配線とが裏面配線99によって接続される。30

**【0145】**

このようにして設計、製造された固体撮像装置は、一般的なフローと同様に、接続検証、物理検証、タイミング検証などを行い、完成される。40

**【0146】**

以上のように、本実施形態例の固体撮像装置では、積層されたチップ間を貫通する基板間配線を形成するため、回路や配線とバッティングしない位置に基板間配線を形成する必要があり、従来の設計プロセスには無いプロセスを追加する必要がある。

**【0147】**

そして、本実施形態例の固体撮像装置の設計方法によれば、上チップ22及び下チップ26との間で、共通電位の配線を基板間配線で接続して形成することができ、かつ、裏面配線を用いることで、チップ内に形成される回路を簡略化することができる。これにより、チップ面積を有效地に利用することが可能となり、また、チップサイズの縮小化が図られ50

る。

#### 【0148】

なお、本実施形態例では、固体撮像装置を例に説明したが、第2の実施形態の半導体装置の製造においても、本実施形態例の設計方法を適用できる。

#### 【0149】

従来の積層チップの半導体装置の設計は、回路が機能ブロックごとに切り分けられ、それぞれが上下のチップに振り分けられていた。一方、本発明の半導体装置では、接続孔及び貫通接続孔のピッチを十分小さく（例えば1μm以下まで）することも可能であるため、基板間配線の配置面積を増大させずに、機能ブロックの一部を別の基板に移動することが可能になる。これにより、配線の配置面積が不足している基板から、余剰面積の多い基板へ回路の一部を移動させたり、回路の一部を共通で用いることができ、全体的に余剰面積が少ない最適なレイアウトが可能となる。10

#### 【0150】

##### 5. 第4の実施形態

###### [電子機器の構成例]

上述した本発明の固体撮像装置は、例えばデジタルカメラやビデオカメラ等のカメラシステムや、撮像機能を有する携帯電話、あるいは撮像機能を備えた他の機器、などの電子機器に適用することができる。

#### 【0151】

図35に、本発明の第4の実施形態に係る電子機器の概略構成図を示す。図35は、本発明の電子機器として、カメラ200を例としたものである。本実施形態例に係るカメラ200は、静止画像又は動画撮影可能なビデオカメラを例とする。本実施形態例のカメラ200は、固体撮像装置203と、固体撮像装置203のフォトダイオードで構成される光電変換部に入射光を導く光学系201と、シャッタ装置202を有する。さらに、カメラ200は、固体撮像装置203を駆動する駆動回路205と、固体撮像装置203の出力信号を処理する信号処理回路204とを有する。20

#### 【0152】

固体撮像装置203は、上述した第1の実施形態における固体撮像装置が適用される。光学系（光学レンズ）201は、被写体からの像光（入射光）を固体撮像装置203の撮像面上に結像させる。これにより、固体撮像装置203内に、一定期間信号電荷が蓄積される。光学系201は、複数の光学レンズから構成された光学レンズ系としてもよい。シャッタ装置202は、固体撮像装置203への光照射期間及び遮光期間を制御する。駆動回路205は、固体撮像装置203の転送動作及びシャッタ装置202のシャッタ動作を制御する駆動信号を供給する。駆動回路205から供給される駆動信号（タイミング信号）により、固体撮像装置203の信号転送を行う。信号処理回路204は、各種の信号処理を行う。信号処理が行われた映像信号は、メモリなどの記憶媒体に記憶され、或いは、モニタに出力される。30

#### 【0153】

第4の実施形態に係るカメラ200などの電子機器によれば、固体撮像装置203において高性能化が図られ、かつ製造コストの低減が図られる。このため、本実施形態では、安価で信頼性の高い電子機器を提供することができる。40

#### 【符号の説明】

#### 【0154】

1・・・固体撮像装置、2・・・画素、3・・・画素領域、4・・・垂直駆動回路、5・・・カラム信号処理回路、6・・・水平駆動回路、7・・・出力回路、8・・・制御回路、9・・・垂直信号線、10・・・水平信号線、11・・・転送トランジスタ、12・・・入出力端子、13・・・リセットトランジスタ、14・・・増幅トランジスタ、15・・・選択トランジスタ、16・・・フローティングディフェュージョン部、21・・・MOS型固体撮像装置、22・・・第1の半導体チップ部、23・・・画素領域、24・・・制御領域、25・・・ロジック回路、2650

… 第 2 の半導体チップ部、 27 … M O S 型固体撮像置、 30 … 単位画素

、 31 … 第 1 の半導体基板、 31 b … 裏面、 32 … 半導体ウェル領域、

33 … ソース / ドレイン領域、 34 … n 型半導体領域、 35 … p

型半導体領域、 36 … ゲート電極、 38 … 素子分離領域、 39 … 層間

絶縁膜、 40 … 銅配線、 41 … 第 1 の多層配線層、 42 … 絶縁スペー

サ層、 43 a … 第 1 絶縁薄膜、 43 b … 第 2 絶縁薄膜、 44 … 接続導

体、 45 … 第 2 の半導体基板、 46 … 半導体ウェル領域、 47 … ソー

ス / ドレイン領域、 48 … ゲート電極、 49 … 層間絶縁膜、 50 … 素

子分離領域、 53 … 銅配線、 54 … 接続導体、 55 … 第 2 の多層配線

層、 56 … バリアメタル層、 57 … アルミ配線、 57 a … 信号配線、

57 b … 電源配線、 57 c … 接地配線、 58 … バリアメタル層、 59

… 反り矯正膜、 60 … 接着剤層、 61 … 反射防止膜、 62 … 絶縁

膜、 63 … 遮光膜、 64 … 溝部、 65 … 貫通接続孔、 66 … 接

続孔、 67 … 絶縁層、 68 … 基板間配線、 68 a … 接続配線、 69

… 導波路材料膜、 70 … 導波路、 71 … 平坦化膜、 72 … キャツ

プ膜、 73 … オンチップカラーフィルタ、 74 … オンチップレンズ、 74

a … オンチップレンズ材料、 75 … レジスト膜、 76 … レジスト膜、

77 … 貫通開口部、 78 … 電極パッド部、 79 … ボンディングワイヤ、

81 … 固体撮像装置、 81 a … 積層体、 140 … 半導体装置、 14

0 a … 積層体

10

20

【図 1】

【図 2】

【 図 3 】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図17】

【図16】

【図18】

【図19】

【図23】

【図27】

【図28】

【図29】

【図30】

【図31】

【図33】

【図32】

【図34】

【図35】

---

フロントページの続き

(51)Int.Cl. F I

H 01L 27/088 (2006.01)

H 01L 21/8238 (2006.01)

H 01L 27/092 (2006.01)

H 01L 21/3205 (2006.01)

H 01L 21/768 (2006.01)

H 01L 23/522 (2006.01)

審査官 松田 直也

(56)参考文献 特開2005-285988 (JP, A)

特開平09-232429 (JP, A)

特開2009-277719 (JP, A)

特開2007-129233 (JP, A)

特開2007-329257 (JP, A)

特開2002-319620 (JP, A)

特開2009-021604 (JP, A)

特開2011-091400 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 25 / 065

H 01L 21 / 3205

H 01L 21 / 768

H 01L 21 / 8234

H 01L 21 / 8238

H 01L 23 / 522

H 01L 25 / 07

H 01L 25 / 18

H 01L 27 / 088

H 01L 27 / 092

H 01L 27 / 146