(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7565409号

(P7565409)

(45)発行日 令和6年10月10日(2024.10.10)

(24)登録日 令和6年10月2日(2024.10.2)

(51)国際特許分類

|        |                  |     |        |       |         |

|--------|------------------|-----|--------|-------|---------|

| H 01 L | 21/336 (2006.01) | F I | H 01 L | 29/78 | 6 1 9 A |

| H 01 L | 29/786 (2006.01) |     | H 01 L | 29/78 | 6 1 7 K |

| H 10 B | 12/00 (2023.01)  |     | H 01 L | 29/78 | 6 1 8 B |

| H 10 B | 41/70 (2023.01)  |     | H 10 B | 12/00 | 6 7 1 C |

| H 10 B | 99/00 (2023.01)  |     | H 10 B | 12/00 | 6 7 1 Z |

請求項の数 1 (全78頁) 最終頁に続く

|                   |                               |

|-------------------|-------------------------------|

| (21)出願番号          | 特願2023-100498(P2023-100498)   |

| (22)出願日           | 令和5年6月20日(2023.6.20)          |

| (62)分割の表示         | 特願2021-79810(P2021-79810)の分割  |

| 原出願日              | 平成27年9月17日(2015.9.17)         |

| (65)公開番号          | 特開2023-112034(P2023-112034 A) |

| (43)公開日           | 令和5年8月10日(2023.8.10)          |

| 審査請求日             | 令和5年7月18日(2023.7.18)          |

| (31)優先権主張番号       | 特願2014-191690(P2014-191690)   |

| (32)優先日           | 平成26年9月19日(2014.9.19)         |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                       |

|          |                                                |

|----------|------------------------------------------------|

| (73)特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72)発明者  | 笹川 慎也<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| (72)発明者  | 下村 明久<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| (72)発明者  | 柄林 克明<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

| (72)発明者  | 遠藤 佑太<br>神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内       |

最終頁に続く

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

絶縁層上の酸化物半導体層と、前記酸化物半導体層上に接して設けられたソース電極と、前記酸化物半導体層上に接して設けられたドレイン電極と、前記ソース電極上に接して設けられた第1の絶縁体と、前記ドレイン電極上に接して設けられた第2の絶縁体と、前記第1の絶縁体及び前記第2の絶縁体上に設けられたゲート絶縁層と、前記ゲート絶縁層を介して前記酸化物半導体層上に位置するゲート電極と、を有し、前記ソース電極と前記ドレイン電極との間、及び前記第1の絶縁体と前記第2の絶縁体との間に、前記ゲート絶縁層と前記ゲート電極とが位置し、前記第1の絶縁体は、第1の領域と、第2の領域と、第3の領域と、第4の領域と、を有し、前記第1の領域は、平坦な領域であり、前記第3の領域は、傾斜を有する領域であり、前記第2の領域は、前記第3の領域における傾斜よりも緩やかな傾斜を有する領域であり、前記第2の絶縁体は、第5の領域と、第6の領域と、第7の領域と、第8の領域と、を有し、前記第5の領域は、平坦な領域であり、前記第7の領域は、傾斜を有する領域であり、

10

20

前記第6の領域は、前記第7の領域における傾斜よりも緩やかな傾斜を有する領域であり、前記ゲート絶縁層及び前記ゲート電極を介した前記第2の領域の上端部と前記第6の領域の上端部との距離は、前記ゲート絶縁層及び前記ゲート電極を介した前記第2の領域の下端部と前記第6の領域の下端部との距離よりも大きく、

前記第4の領域において前記第1の絶縁体の下端部は、前記ソース電極の上端部と一致し、前記第8の領域において前記第2の絶縁体の下端部は、前記ドレイン電極の上端部と一致し、

前記絶縁層は前記酸化物半導体層と上面で接する第9の領域と、前記ソース電極またはドレイン電極と上面で接する第10の領域とを、を有し、

前記絶縁層の前記第9の領域における膜厚は、前記絶縁層の前記第10の領域における膜厚より大きく、

平面視において、前記第9の領域は、前記第3の領域と前記第7の領域の間の領域である半導体装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、例えば、半導体、導電体、絶縁体、トランジスタおよび半導体装置に関する。または、本発明は、例えば、半導体、導電体、絶縁体、トランジスタおよび半導体装置の製造方法に関する。または、本発明は、例えば、半導体、導電体、絶縁体、表示装置、発光装置、照明装置、蓄電装置、記憶装置、プロセッサ、電子機器に関する。または、半導体、導電体、絶縁体、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の製造方法に関する。または、半導体装置、表示装置、液晶表示装置、発光装置、記憶装置、電子機器の駆動方法に関する。

##### 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関するものである。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関するものである。

##### 【0003】

なお、本明細書等において半導体装置とは、半導体特性を利用して機能しうる装置全般を指す。表示装置、発光装置、照明装置、電気光学装置、半導体回路および電子機器は、半導体装置を有する場合がある。

##### 【背景技術】

##### 【0004】

絶縁表面を有する基板上の半導体を用いて、トランジスタを構成する技術が注目されている。当該トランジスタは集積回路や表示装置のような半導体装置に広く応用されている。トランジスタに適用可能な半導体としてシリコンが知られている。

##### 【0005】

トランジスタの半導体に用いられるシリコンは、用途によって非晶質シリコンと多結晶シリコンとが使い分けられている。例えば、大型の表示装置を構成するトランジスタに適用する場合、大面積基板への成膜技術が確立されている非晶質シリコンを用いると好適である。一方、駆動回路と画素回路とを同一基板上に形成するような高機能の表示装置を構成するトランジスタに適用する場合、高い電界効果移動度を有するトランジスタを作製可能な多結晶シリコンを用いると好適である。多結晶シリコンは、非晶質シリコンに対し高温での熱処理、またはレーザ光処理を行うことで形成する方法が知られる。

##### 【0006】

近年では、酸化物半導体（代表的にはIn-Ga-Zn酸化物）を用いたトランジスタの開発が活発化している。

##### 【0007】

酸化物半導体の歴史は古く、1988年には、結晶In-Ga-Zn酸化物を半導体素子

10

20

30

40

50

へ利用することが開示されている（特許文献1参照。）。また、1995年には、酸化物半導体を用いたトランジスタが発明されており、その電気特性が開示されている（特許文献2参照。）。

#### 【0008】

酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタ、および多結晶シリコンを用いたトランジスタとは異なる特徴を有する。例えば、酸化物半導体を用いたトランジスタを適用した表示装置は、消費電力が低いことが知られている。酸化物半導体は、スパッタリング法などを用いて成膜できるため、大型の表示装置を構成するトランジスタに用いることができる。また、酸化物半導体を用いたトランジスタは、高い電界効果移動度を有するため、駆動回路と画素回路とを同一基板上に形成するような高機能の表示装置を実現できる。また、非晶質シリコンを用いたトランジスタの生産設備の一部を改良して利用することが可能であるため、設備投資を抑えられるメリットもある。

10

#### 【先行技術文献】

#### 【特許文献】

#### 【0009】

【文献】特開昭63-239117

【文献】特表平11-505377

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

20

微細な形状を提供することを課題の一とする。チャネル長の小さいトランジスタを提供することを課題の一とする。または、サブスレッショルドスイング値の小さいトランジスタを提供することを課題の一とする。または、短チャネル効果の小さいトランジスタを提供することを課題の一とする。または、ノーマリーオフの電気特性を有するトランジスタを提供することを課題の一とする。または、非導通時のリーク電流の小さいトランジスタを提供することを課題の一とする。または、電気特性の優れたトランジスタを提供することを課題の一とする。または、信頼性の高いトランジスタを提供することを課題の一とする。または、高い周波数特性を有するトランジスタを提供することを課題の一とする。

#### 【0011】

または、該トランジスタを有する半導体装置を提供することを課題の一とする。または、該半導体装置を有するモジュールを提供することを課題の一とする。または、該半導体装置、または該モジュールを有する電子機器を提供することを課題の一とする。または、新規な半導体装置を提供することを課題の一とする。または、新規なモジュールを提供することを課題の一とする。または、新規な電子機器を提供することを課題の一とする。

30

#### 【0012】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

#### 【課題を解決するための手段】

40

#### 【0013】

本発明の一態様は、基板上に半導体を形成し、半導体上に、第1の導電体を成膜し、第1の導電体上に第1の絶縁体を成膜し、第1の絶縁体上にレジストを成膜し、レジストを露光および現像することで、レジストの第2の領域および第3の領域を残存させて第1の絶縁体の一部を露出し、基板の上面に垂直な方向のバイアスを印加し、かつ炭素およびハロゲンを有するガスによってプラズマを生成し、プラズマによって、有機物を堆積させるとともに、有機物をエッチングした後、有機物、第2の領域および第3の領域をマスクとして第1の絶縁体をエッチングすることで、第2の絶縁体および第3の絶縁体を形成し、かつ第1の導電体を露出させ、第2の絶縁体および第3の絶縁体をマスクとして第1の導電体をエッチングすることで、第2の導電体および第3の導電体を形成し、かつ半導体を露

50

出させ、有機物、第2の領域および第3の領域を除去し、半導体の露出部上に第4の絶縁体を成膜し、第4の絶縁体上に第4の導電体を形成し、有機物は、第1の絶縁体の露出部においてはエッティング速度が堆積速度を上回り、第2の領域の側面においては堆積速度がエッティング速度を上回る半導体装置の作製方法である。

#### 【0014】

本発明の一態様は、上記構成において、第2の導電体と第3の導電体との間の距離が、第2の領域と第3の領域との間の距離の80%以下である。

#### 【発明の効果】

#### 【0015】

微細な形状を提供することができる。チャネル長の小さいトランジスタを提供することができる。または、サブスレッショルドスイング値の小さいトランジスタを提供することができる。または、短チャネル効果の小さいトランジスタを提供することができる。または、ノーマリーオフの電気特性を有するトランジスタを提供することができる。または、非導通時のリーク電流の小さいトランジスタを提供することができる。または、電気特性の優れたトランジスタを提供することができる。または、信頼性の高いトランジスタを提供することができる。または、高い周波数特性を有するトランジスタを提供することができる。

10

#### 【0016】

または、該トランジスタを有する半導体装置を提供することができる。または、該半導体装置を有するモジュールを提供することができる。または、該半導体装置、または該モジュールを有する電子機器を提供することができる。または、新規な半導体装置を提供することができる。または、新規なモジュールを提供することができる。または、新規な電子機器を提供することができる。

20

#### 【0017】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

#### 【図面の簡単な説明】

#### 【0018】

30

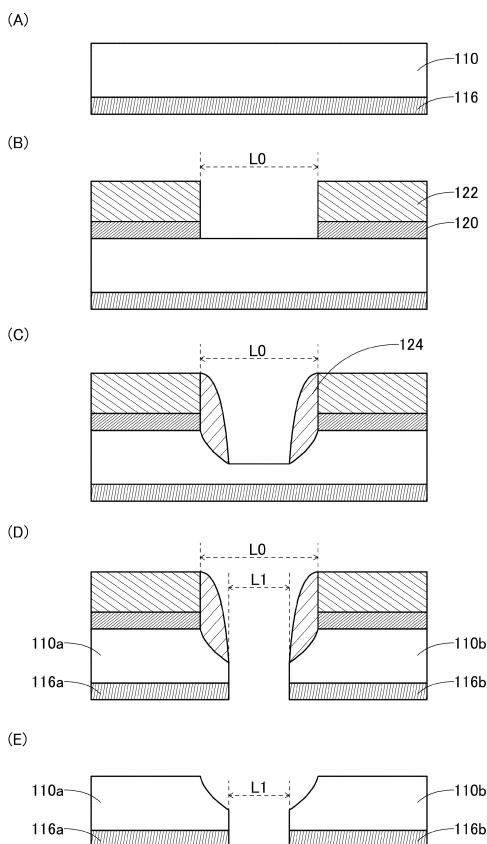

【図1】本発明の一態様に係る半導体装置の作製方法を説明する断面図。

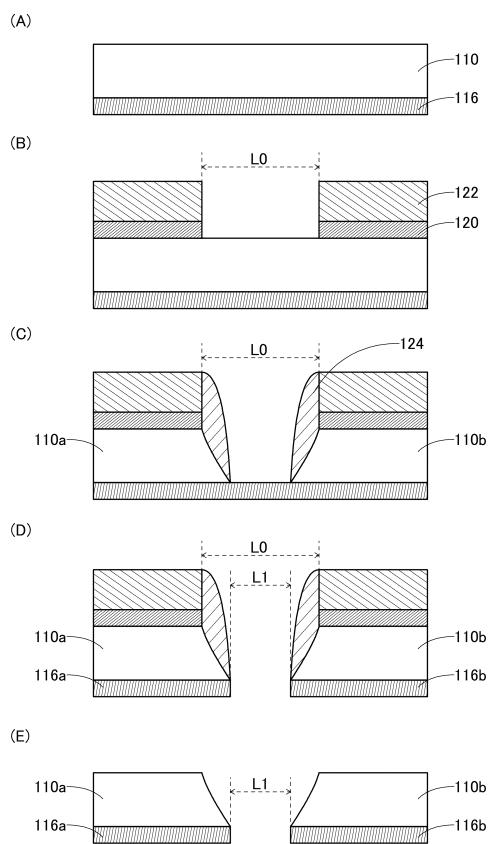

【図2】本発明の一態様に係る半導体装置の作製方法を説明する断面図。

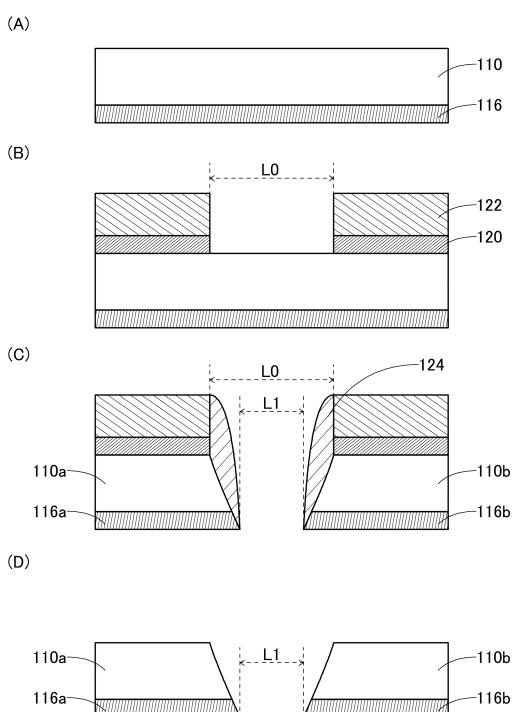

【図3】本発明の一態様に係る半導体装置の作製方法を説明する断面図。

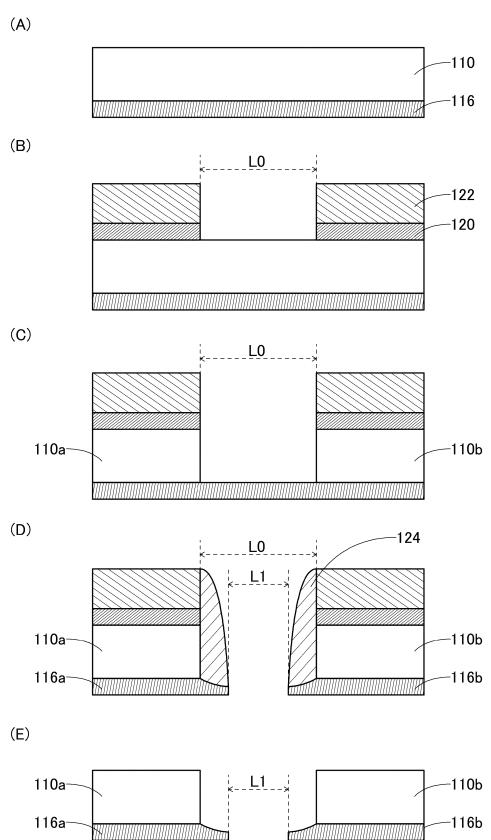

【図4】本発明の一態様に係る半導体装置の作製方法を説明する断面図。

【図5】本発明の一態様に係る半導体装置の作製方法を説明する断面図。

【図6】本発明の一態様に係る半導体装置の作製方法を説明する断面図。

【図7】本発明の一態様に係る半導体装置の作製方法を説明する断面図。

【図8】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図9】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図10】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

40

【図11】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図12】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

【図13】本発明の一態様に係るトランジスタを示す断面図およびバンド図。

【図14】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図15】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図16】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図17】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図18】本発明の一態様に係るトランジスタの作製方法を説明する上面図および断面図。

【図19】本発明の一態様に係るトランジスタの作製方法を説明する断面図。

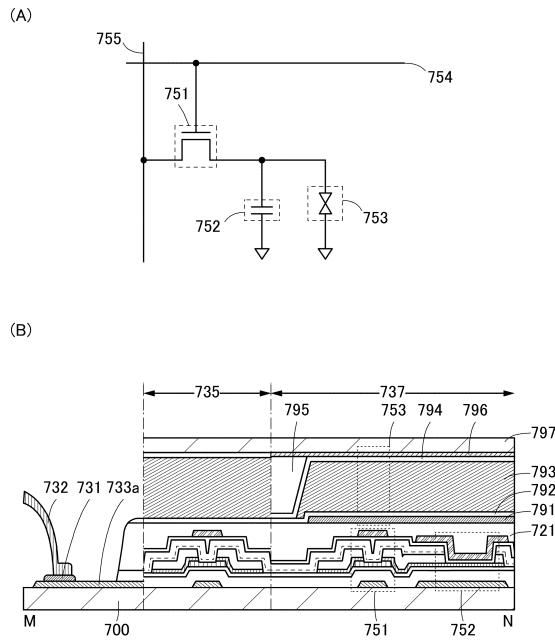

【図20】本発明の一態様に係る半導体装置を示す回路図。

50

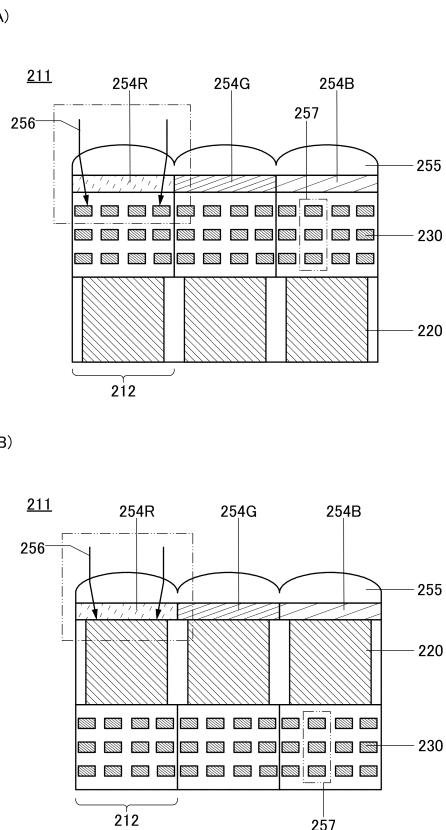

【図 2 1】本発明の一態様に係る半導体装置を示す断面図。

【図 2 2】本発明の一態様に係る半導体装置を示す断面図。

【図 2 3】本発明の一態様に係る半導体装置を示す断面図。

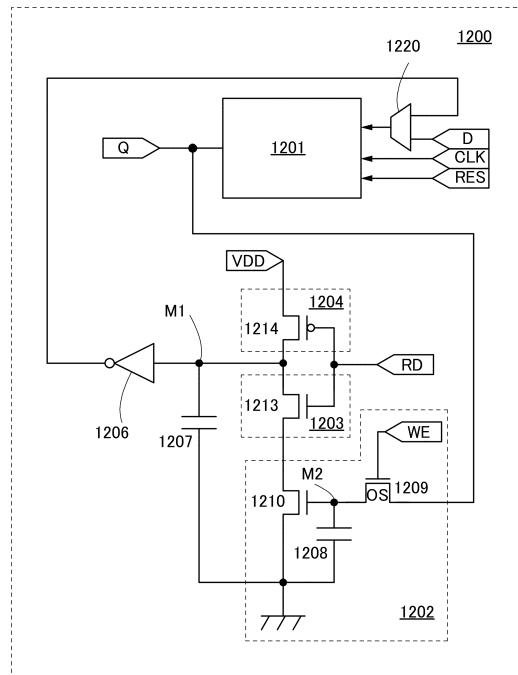

【図 2 4】本発明の一態様に係る記憶装置を示す回路図。

【図 2 5】本発明の一態様に係る半導体装置を示す断面図。

【図 2 6】本発明の一態様に係る半導体装置を示す断面図。

【図 2 7】本発明の一態様に係る半導体装置を示す断面図。

【図 2 8】本発明の一態様に係る半導体装置を示す上面図。

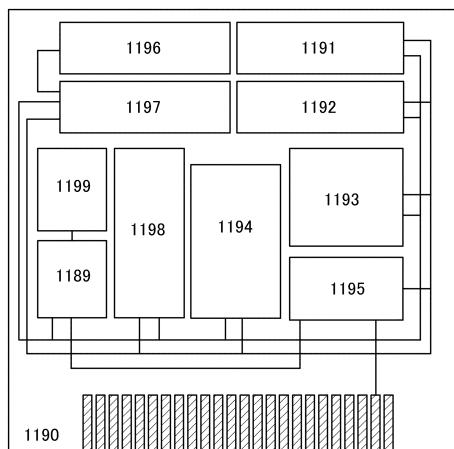

【図 2 9】本発明の一態様に係る半導体装置を示すブロック図。

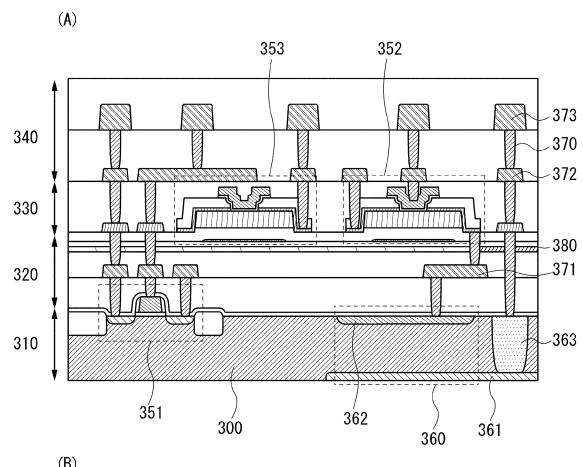

【図 3 0】本発明の一態様に係る半導体装置を示す断面図。

【図 3 1】本発明の一態様に係る半導体装置を示す断面図。

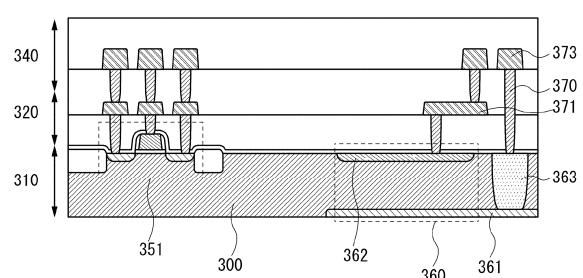

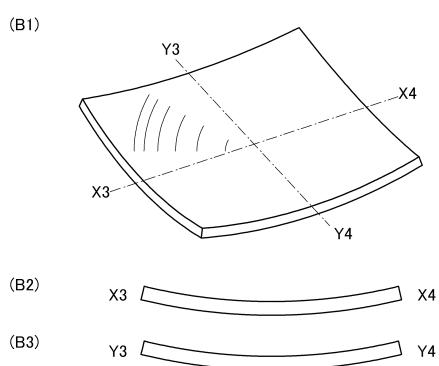

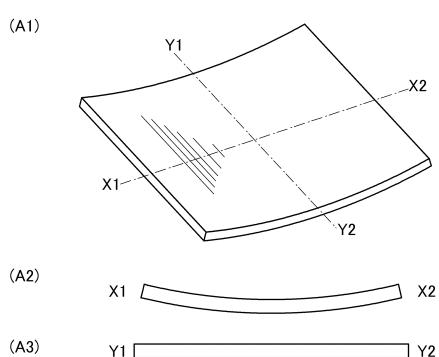

【図 3 2】本発明の一態様に係る半導体装置を示す斜視図および断面図。

【図 3 3】本発明の一態様に係る半導体装置を示すブロック図。

【図 3 4】本発明の一態様に係る半導体装置を示す回路図。

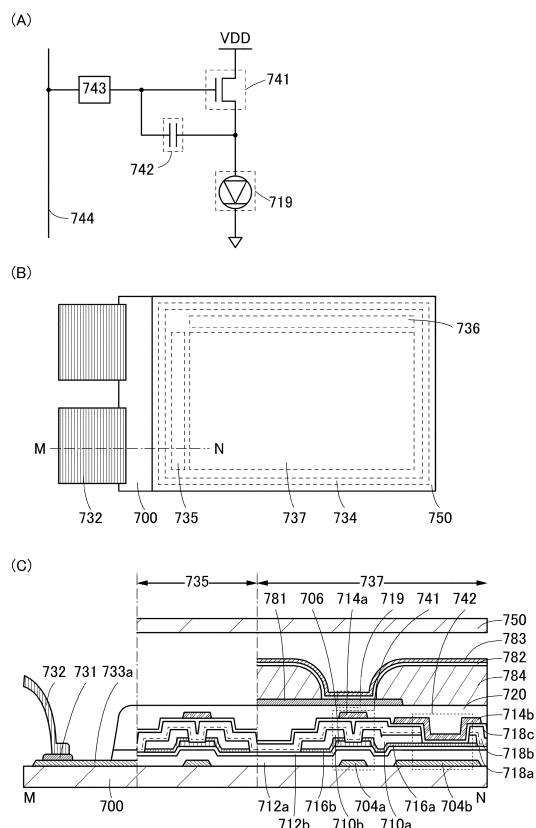

【図 3 5】本発明の一態様に係る半導体装置を示す回路図、上面図および断面図。

【図 3 6】本発明の一態様に係る半導体装置を示す回路図および断面図。

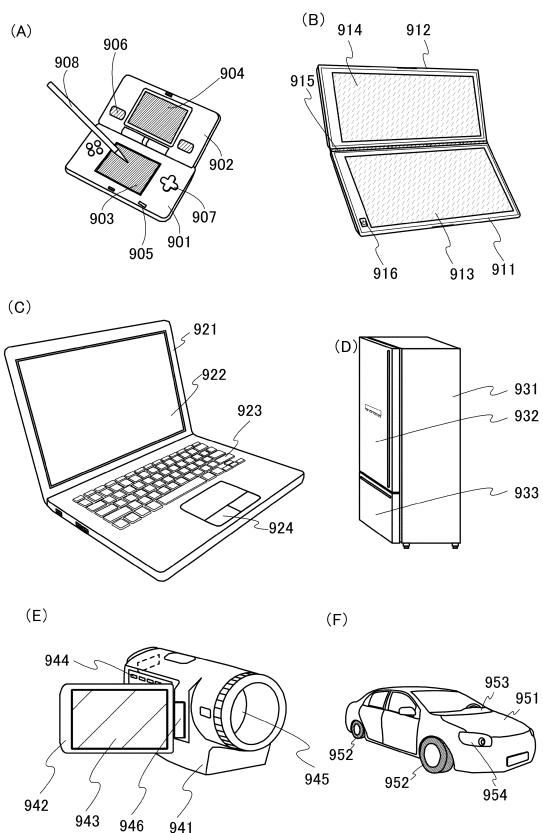

【図 3 7】本発明の一態様に係る電子機器を示す斜視図。

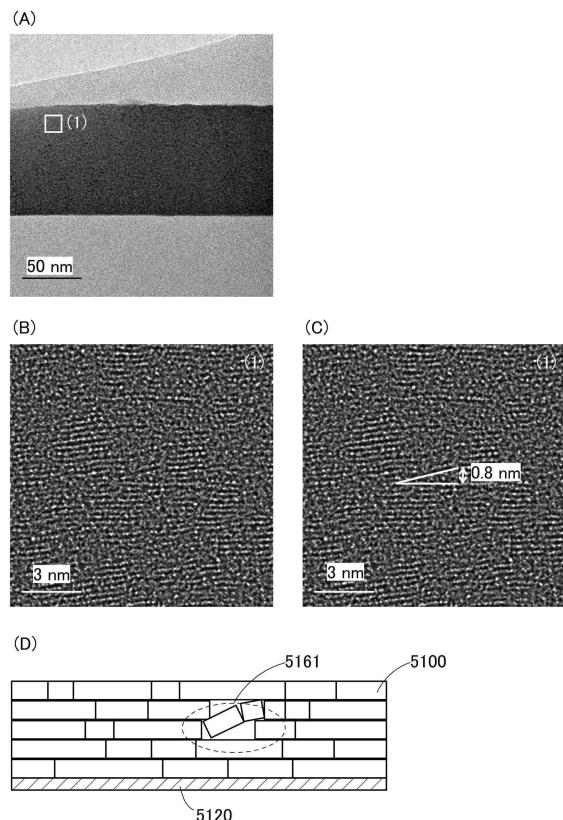

【図 3 8】C A A C - O S の断面における C s 補正高分解能 T E M 像、および C A A C - O S の断面模式図。

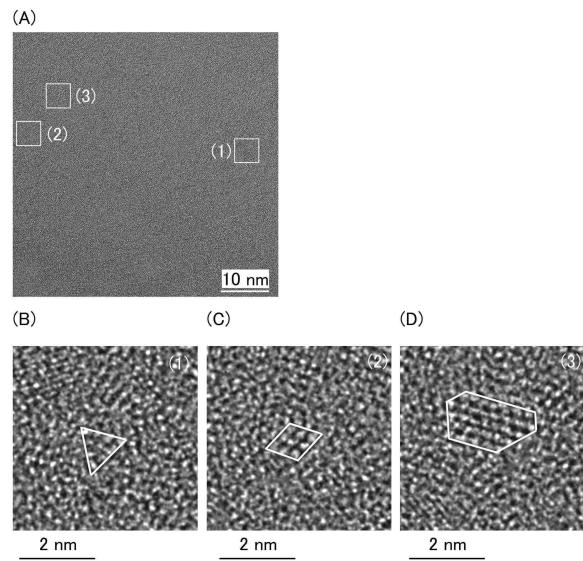

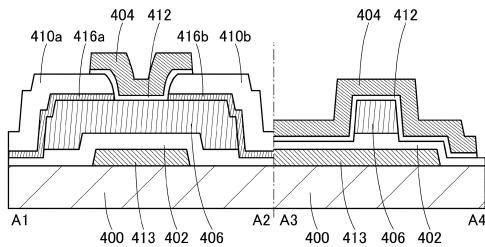

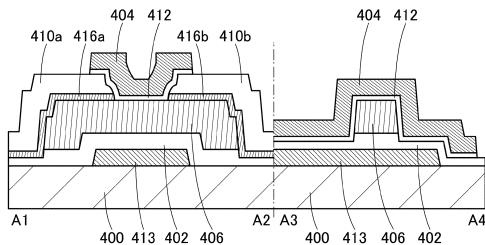

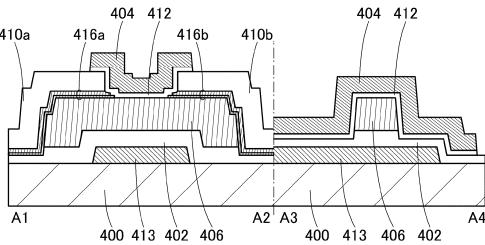

【図 3 9】C A A C - O S の平面における C s 補正高分解能 T E M 像。

【図 4 0】C A A C - O S および単結晶酸化物半導体の X R D による構造解析を説明する図。

【図 4 1】C A A C - O S の電子回折パターンを示す図。

【図 4 2】I n - G a - Z n 酸化物の電子照射による結晶部の変化を示す図。

【図 4 3】C A A C - O S および n c - O S の成膜モデルを説明する模式図。

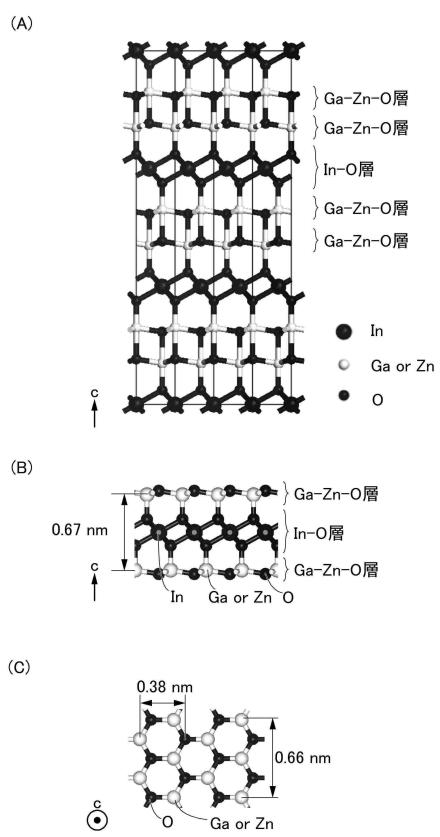

【図 4 4】I n G a Z n O 4 の結晶、およびペレットを説明する図。

【図 4 5】C A A C - O S の成膜モデルを説明する模式図。

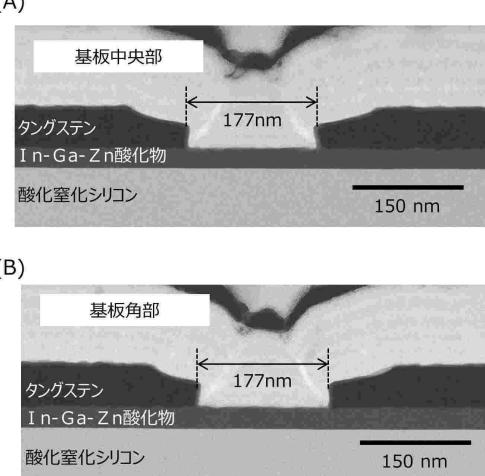

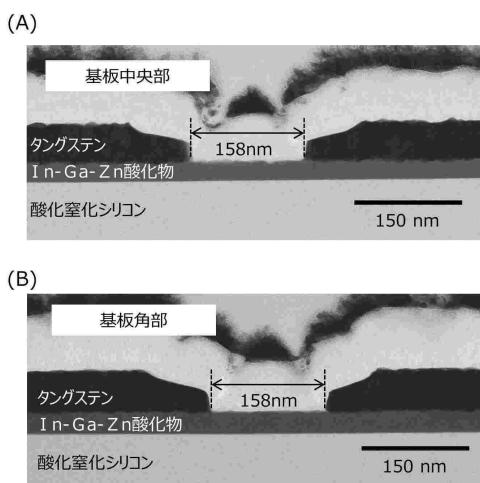

【図 4 6】断面 S T E M 像。

【図 4 7】断面 S T E M 像。

【図 4 8】トランジスタの上面図および断面図。

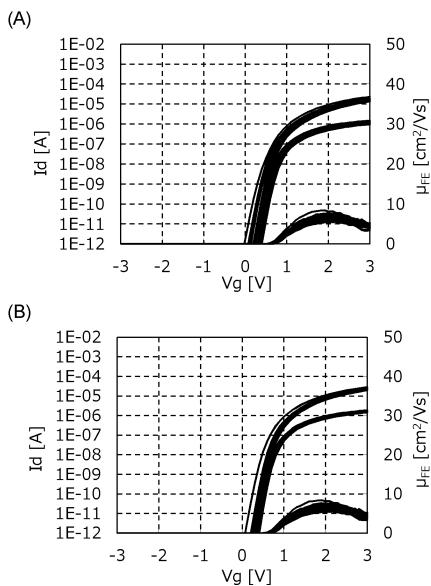

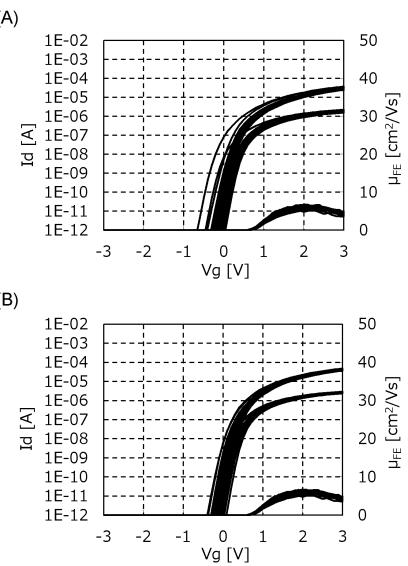

【図 4 9】トランジスタの I d - V g 特性。

【図 5 0】トランジスタの I d - V g 特性。

【図 5 1】本発明の一態様に係るトランジスタを示す断面図。

【図 5 2】本発明の一態様に係るトランジスタを示す断面図。

【図 5 3】本発明の一態様に係るトランジスタを示す断面図。

【発明を実施するための形態】

【0 0 1 9】

本発明の実施の形態について、図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。なお、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0 0 2 0】

なお、図において、大きさ、膜（層）の厚さ、または領域は、明瞭化のために誇張されている場合がある。

【0 0 2 1】

なお、本明細書において、「膜」という表記と、「層」という表記と、を互いに入れ替えることが可能である。

【0 0 2 2】

10

20

30

40

50

また、電圧は、ある電位と、基準の電位（例えば接地電位（GND）またはソース電位）との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。一般的に、電位（電圧）は、相対的なものであり、基準の電位からの相対的な大きさによって決定される。したがって、「接地電位」などと記載されている場合であっても、電位が0Vであるとは限らない。例えば、回路で最も低い電位が、「接地電位」となる場合もある。または、回路で中間くらいの電位が、「接地電位」となる場合もある。その場合には、その電位を基準として、正の電位と負の電位が規定される。

#### 【0023】

なお、第1、第2として付される序数詞は便宜的に用いるものであり、工程順または積層順を示すものではない。そのため、例えば、「第1の」を「第2の」または「第3の」などと適宜置き換えて説明することができる。また、本明細書などに記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

10

#### 【0024】

なお、「半導体」と表記した場合でも、例えば、導電性が十分低い場合は「絶縁体」としての特性を有する場合がある。また、「半導体」と「絶縁体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「絶縁体」と言い換えることができる場合がある。同様に、本明細書に記載の「絶縁体」は、「半導体」と言い換えることができる場合がある。

#### 【0025】

また、「半導体」と表記した場合でも、例えば、導電性が十分高い場合は「導電体」としての特性を有する場合がある。また、「半導体」と「導電体」は境界が曖昧であり、厳密に区別できない場合がある。したがって、本明細書に記載の「半導体」は、「導電体」と言い換えることができる場合がある。同様に、本明細書に記載の「導電体」は、「半導体」と言い換えることができる場合がある。

20

#### 【0026】

なお、半導体の不純物とは、例えば、半導体を構成する主成分以外をいう。例えば、濃度が0.1原子%未満の元素は不純物である。不純物が含まれることにより、例えば、半導体にDOS(Density of State)が形成されることや、キャリア移動度が低下することや、結晶性が低下することなどが起こる場合がある。半導体が酸化物半導体である場合、半導体の特性を変化させる不純物としては、例えば、第1族元素、第2族元素、第14族元素、第15族元素、主成分以外の遷移金属などがあり、特に、例えば、水素（水にも含まれる）、リチウム、ナトリウム、シリコン、ホウ素、リン、炭素、窒素などがある。酸化物半導体の場合、例えば水素などの不純物の混入によって酸素欠損を形成する場合がある。また、半導体がシリコンである場合、半導体の特性を変化させる不純物としては、例えば、酸素、水素を除く第1族元素、第2族元素、第13族元素、第15族元素などがある。

30

#### 【0027】

なお、本明細書において、Aが濃度Bの領域を有する、と記載する場合、例えば、Aのある領域における深さ方向全体の濃度がBである場合、Aのある領域における深さ方向の濃度の平均値がBである場合、Aのある領域における深さ方向の濃度の中央値がBである場合、Aのある領域における深さ方向の濃度の最大値がBである場合、Aのある領域における深さ方向の濃度の最小値がBである場合、Aのある領域における深さ方向の濃度の収束値がBである場合、測定上Aそのものの確からしい値の得られる領域における濃度がBである場合などを含む。

40

#### 【0028】

また、本明細書において、Aが大きさB、長さB、厚さB、幅Bまたは距離Bの領域を有する、と記載する場合、例えば、Aのある領域における全体の大きさ、長さ、厚さ、幅、または距離がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の平均値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の中央値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の最

50

大値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の最小値がBである場合、Aのある領域における大きさ、長さ、厚さ、幅、または距離の収束値がBである場合、測定上Aそのものの確からしい値の得られる領域での大きさ、長さ、厚さ、幅、または距離がBである場合などを含む。

#### 【0029】

なお、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソース（ソース領域またはソース電極）とドレイン（ドレイン領域またはドレイン電極）との間の距離をいう。なお、一つのトランジスタにおいて、チャネル長が全ての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル長は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル長は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

10

#### 【0030】

チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが互いに重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。なお、一つのトランジスタにおいて、チャネル幅がすべての領域で同じ値をとるとは限らない。即ち、一つのトランジスタのチャネル幅は、一つの値に定まらない場合がある。そのため、本明細書では、チャネル幅は、チャネルの形成される領域における、いずれか一の値、最大値、最小値または平均値とする。

20

#### 【0031】

なお、トランジスタの構造によっては、実際にチャネルの形成される領域におけるチャネル幅（以下、実効的なチャネル幅と呼ぶ。）と、トランジスタの上面図において示されるチャネル幅（以下、見かけ上のチャネル幅と呼ぶ。）と、が異なる場合がある。例えば、立体的な構造を有するトランジスタでは、実効的なチャネル幅が、トランジスタの上面図において示される見かけ上のチャネル幅よりも大きくなり、その影響が無視できなくなる場合がある。例えば、微細かつ立体的な構造を有するトランジスタでは、半導体の側面に形成されるチャネル領域の割合が大きくなる場合がある。その場合は、上面図において示される見かけ上のチャネル幅よりも、実際にチャネルの形成される実効的なチャネル幅の方が大きくなる。

30

#### 【0032】

ところで、立体的な構造を有するトランジスタにおいては、実効的なチャネル幅の、実測による見積もりが困難となる場合がある。例えば、設計値から実効的なチャネル幅を見積もるために、半導体の形状が既知という仮定が必要である。したがって、半導体の形状が正確にわからない場合には、実効的なチャネル幅を正確に測定することは困難である。

#### 【0033】

そこで、本明細書では、トランジスタの上面図において、半導体とゲート電極とが互いに重なる領域における、ソースとドレインとが向かい合っている部分の長さである見かけ上のチャネル幅を、「囲い込みチャネル幅（S C W : S u r r o u n d e d C h a n n e l W i d t h ）」と呼ぶ場合がある。また、本明細書では、単にチャネル幅と記載した場合には、囲い込みチャネル幅または見かけ上のチャネル幅を指す場合がある。または、本明細書では、単にチャネル幅と記載した場合には、実効的なチャネル幅を指す場合がある。なお、チャネル長、チャネル幅、実効的なチャネル幅、見かけ上のチャネル幅、囲い込みチャネル幅などは、断面TEM像などを取得して、その画像を解析することなどによって、値を決定することができる。

40

#### 【0034】

なお、トランジスタの電界効果移動度や、チャネル幅当たりの電流値などを計算して求める場合、囲い込みチャネル幅を用いて計算する場合がある。その場合には、実効的なチャネル幅を用いて計算する場合とは異なる値をとる場合がある。

50

**【 0 0 3 5 】**

なお、本明細書において、AがBより迫り出した形状を有すると記載する場合、上面図または断面図において、Aの少なくとも一端が、Bの少なくとも一端よりも外側にある形状を有することを示す場合がある。したがって、AがBより迫り出した形状を有すると記載されている場合、例えば上面図において、Aの一端が、Bの一端よりも外側にある形状を有すると読み替えることができる。

**【 0 0 3 6 】**

本明細書において、「平行」とは、二つの直線が - 10°以上 10°以下の角度で配置されている状態をいう。したがって、- 5°以上 5°以下の場合も含まれる。また、「略平行」とは、二つの直線が - 30°以上 30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が 80°以上 100°以下の角度で配置されている状態をいう。したがって、85°以上 95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が 60°以上 120°以下の角度で配置されている状態をいう。

10

**【 0 0 3 7 】**

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

**【 0 0 3 8 】**

## &lt; 加工方法 1 &gt;

以下では、本発明の一態様に係る導電体、絶縁体または半導体の加工方法について説明する。

20

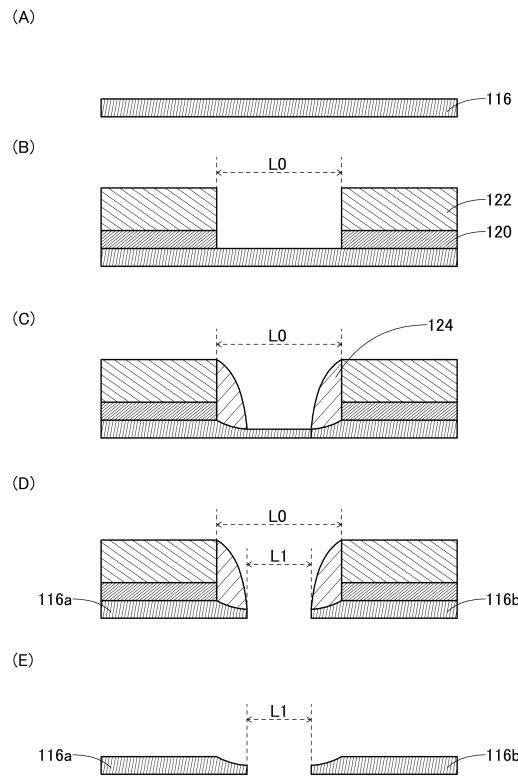

**【 0 0 3 9 】**

まず、層 116 と、層 116 上の層 110 と、を準備する（図 1（A）参照。）。層 116 としては、導電体、絶縁体または半導体を用いればよい。また、層 110 としては、導電体、絶縁体または半導体を用いればよい。

**【 0 0 4 0 】**

導電体としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニアム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

30

**【 0 0 4 1 】**

絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニアム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニアム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。特に、シリコンを有する酸化物を用いることが好ましい。

40

**【 0 0 4 2 】**

半導体としては、シリコン、ゲルマニウムなどの第 14 族半導体、炭化シリコン、ケイ化ゲルマニウム、ヒ化ガリウム、リン化インジウム、セレン化亜鉛、硫化カドミウム、酸化物半導体などの化合物半導体、および有機半導体を用いればよい。酸化物半導体については後述する。

**【 0 0 4 3 】**

次に、反射防止層（B A R C : Bottom Anti Reflective Coating）を成膜する。次に、レジストを成膜する。次に、レジストを加工する。レジストの加工は、まずフォトマスクなどを用いてレジストを露光する。このとき、反射防止層

50

の作用によって、ハレーションを抑制することができる。次に、露光された領域を、現像液を用いて除去または残存させてレジスト 122 を形成する。レジストの露光には、例えば、KrF エキシマレーザ光、ArF エキシマレーザ光、EUV (Extreme Ultraviolet) 光などを用いればよい。また、基板と投影レンズとの間に液体（例えば水）を満たして露光する、液浸技術を用いてもよい。また、前述した光に代えて、電子ビームやイオンビームを用いてもよい。なお、電子ビームやイオンビームを用いる場合には、フォトマスクは不要となる。

#### 【0044】

次に、レジスト 122 をマスクとして用いて反射防止層をエッチングし、反射防止層 120 を形成する（図 1 (B) 参照。）。ただし、反射防止層 120 に替えて、反射防止層の機能を有さない有機物または無機物を用いてもよい場合がある。または、反射防止層 120 を有さなくてもよい場合がある。

10

#### 【0045】

レジスト 122 の間の距離を L0 とする。最小となる L0 の寸法（最小加工寸法ともいう。）は、露光機やレジストなどによって決定する。

#### 【0046】

次に、プラズマ処理を行う。プラズマ処理は、平行平板型反応性イオンエッチング (RIE : Reactive Ion Etching) 法や、誘導結合型プラズマ (ICP : Inductively Coupled Plasma) エッチング法などによって行うことができる。

20

#### 【0047】

プラズマは、炭素およびハロゲンを有するガスを用いて生成する。該プラズマは、レジスト 122 などに含まれる炭素および水素などと反応し、被処理面（例えば、レジスト 122 の上面および側面、反射防止層 120 の側面、ならびに層 110 の露出部など）に有機物を堆積させる。有機物の堆積は、等方的に起こる。ここで、層 116 および層 110 の上面に垂直な方向のバイアスを印加すると、有機物の堆積と、有機物のエッチングと、が同時に起こる。有機物のエッチングは、バイアスの印加される方向のエッチング速度が高くなるため、異方的に起こる。

#### 【0048】

炭素およびハロゲンを有するガスとしては、例えば、三フッ化メタンガス、四フッ化メタンガス、六フッ化エタンガス、六フッ化プロパンガス、ハフッ化プロパンガスおよびハフッ化シクロブタンガスなどの炭素およびフッ素を有するガス、ならびに四塩化炭素などの炭素および塩素を有するガスなどを用いればよい。また、ヘリウムまたはアルゴンなどの希ガス、水素などを混合して用いてもよい。

30

#### 【0049】

有機物の堆積速度およびエッチング速度は、様々な条件が複合的に作用して決定される。例えば、プラズマの生成に用いるガス中の炭素の割合が高いと堆積速度が高くなり、ハロゲンの割合が高いとエッチング速度が高くなる。また、例えば、バイアスを弱くするとエッチング速度が低くなり、バイアスを強くするとエッチング速度が高くなる。ここでは、バイアスの印加される方向において、エッチング速度が堆積速度よりも高くなる条件を用いる。したがって、レジスト 122 の上面および層 110 の露出部では、有機物は堆積するのとほとんど同時にエッチングされる。また、層 110 の露出部もエッチングされる。ただし、プラズマ処理の条件によって、層 110 の露出部をエッチングさせないこともできる。また、プラズマ処理の条件を 2 段階、3 段階などの多段階で変化させることもできる。

40

#### 【0050】

一方、レジスト 122 の側面および反射防止層 120 の側面では、有機物のエッチング速度が堆積速度よりも遅くなる。したがって、該領域では有機物 124 が堆積する（図 1 (C) 参照。）。

#### 【0051】

50

次に、有機物 124、レジスト 122 および反射防止層 120 をマスクとして用いて、層 110 および層 116 をエッティングし、層 110a および層 110b、ならびに層 116a および層 116b を形成する（図 1（D）参照。）。層 110 および層 116 のエッティングは、ドライエッティング法または／およびウェットエッティング法によって行うことができる。このときに、有機物 124 を除去してもよい。なお、層 110a と層 110b とが奥行き方向で繋がっていても構わない。また、層 116a と層 116b とが奥行き方向で繋がっていても構わない。

#### 【0052】

層 116a と層 116b との間の距離を L1 とする。L1 は、有機物 124 の分だけ L0 よりも小さくなる。即ち、露光機やレジストなどによって決定する最小の寸法よりも小さい形状を得ることができる。10

#### 【0053】

次に、有機物 124、レジスト 122 および反射防止層 120 を除去することで最小加工寸法よりも小さい穴を形成することができる（図 1（E）参照。）。有機物 124、レジスト 122 および反射防止層 120 の除去には、プラズマアッシングなどのドライエッティング法または／およびウェットエッティング法を用いることができる。

#### 【0054】

このとき、層 110a は、第 1 の領域と、第 2 の領域と、第 3 の領域と、を有する。第 2 の領域は、第 1 の領域と第 3 の領域との間に位置する。第 1 の領域は、平坦な領域である。第 2 の領域および第 3 の領域は傾斜を有する領域である。第 2 の領域は、第 3 の領域よりも傾斜が緩やかである。第 2 の領域における傾斜は、第 1 の領域近傍から第 3 の領域近傍にかけて傾斜の度合いが変化する場合がある。例えば、第 1 の領域の近傍では傾斜がきつく、第 3 の領域の近傍では傾斜が緩くなるような形状を有する場合がある。層 110a が、このような形状を有することにより、層 110a よりも上方に形成する層などの段差被覆性を高くすることができる。そのため、形状不良などが起こりにくくなる。層 110b についても同様である。なお、傾斜とは、厚さの変化のことをいい、その角度が直角である場合も傾斜を有すると表記する。20

#### 【0055】

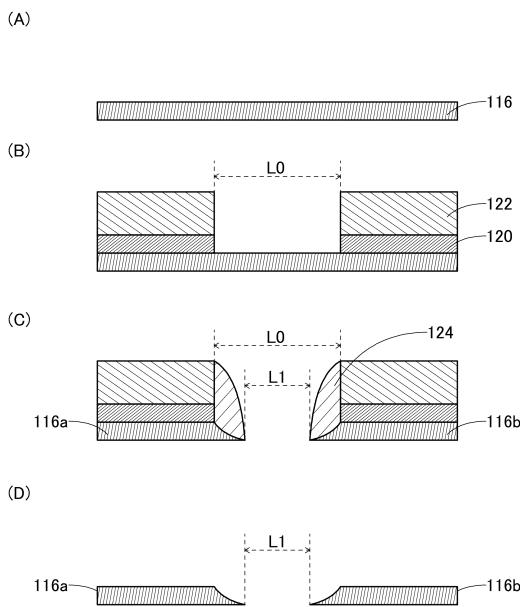

##### <加工方法 2>

また、図 2 に示すように、プラズマ処理の条件を変更することにより、図 1（E）とは異なる形状を得ることもできる。30

#### 【0056】

図 2（A）および図 2（B）は、それぞれ図 1（A）および図 1（B）と同じであるため、説明を省略する。

#### 【0057】

次に、プラズマ処理を行う。プラズマ処理によって、有機物の堆積とエッティングが起こる。また、層 110 の露出部もエッティングされる。ここでは、レジスト 122 の側面および反射防止層 120 の側面に有機物 124 を堆積させながら、層 116 が露出するまで層 110 をエッティングすることで、層 110a および層 110b を形成する（図 2（C）参照。）。なお、層 110a と層 110b とが奥行き方向で繋がっていても構わない。40

#### 【0058】

次に、有機物 124、レジスト 122 および反射防止層 120 をマスクとして用いて、層 116 をエッティングし、層 116a および層 116b を形成する（図 2（D）参照。）。層 116 のエッティングは、ドライエッティング法または／およびウェットエッティング法によって行うことができる。このときに、有機物 124 を除去してもよい。なお、層 116a と層 116b とが奥行き方向で繋がっていても構わない。

#### 【0059】

層 116a と層 116b との間の距離を L1 とする。L1 は、有機物 124 の分だけ L0 よりも小さくなる。即ち、露光機やレジストなどによって決定する最小の寸法よりも小さい形状を得ることができる。50

**【 0 0 6 0 】**

次に、有機物 124、レジスト 122 および反射防止層 120 を除去することで最小加工寸法よりも小さい穴を形成することができる（図 2（E）参照。）。有機物 124、レジスト 122 および反射防止層 120 の除去には、プラズマアッシングなどのドライエッチング法または／およびウェットエッチング法を用いることができる。

**【 0 0 6 1 】**

このとき、層 110a は、第 1 の領域と、第 2 の領域と、を有する。第 1 の領域は、平坦な領域である。第 2 の領域は傾斜を有する領域である。第 2 の領域は、傾斜の度合いが変化する場合がある。例えば、第 1 の領域の近傍では傾斜がきつく、第 1 の領域から遠ざかるほど傾斜が緩くなるような形状を有する場合がある。層 110a が、このような形状を有することにより、層 110a よりも上方に形成する層などの段差被覆性を高くすることができます。そのため、形状不良などが起こりにくくなる。層 110b についても同様である。

10

**【 0 0 6 2 】**

## &lt; 加工方法 3 &gt;

また、図 3 に示すように、プラズマ処理の条件を変更することにより、図 1（E）および図 2（E）とは異なる形状を得ることもできる。

**【 0 0 6 3 】**

図 3（A）および図 3（B）は、それぞれ図 1（A）および図 1（B）と同じであるため、説明を省略する。

20

**【 0 0 6 4 】**

次に、プラズマ処理を行う。プラズマ処理によって、有機物の堆積とエッチングが起こる。また、層 110 の露出部もエッチングされる。ここでは、レジスト 122 の側面および反射防止層 120 の側面に有機物 124 を堆積させながら、層 110 および層 116 をエッチングすることで、層 110a および層 110b、ならびに層 116a および層 116b を形成する（図 3（C）参照。）。なお、層 110a と層 110b とが奥行き方向で繋がっていても構わない。また、層 116a と層 116b とが奥行き方向で繋がっていても構わない。

**【 0 0 6 5 】**

層 116a と層 116b との間の距離を L1 とする。L1 は、有機物 124 の分だけ L0 よりも小さくなる。即ち、露光機やレジストなどによって決定する最小の寸法よりも小さい形状を得ることができる。

30

**【 0 0 6 6 】**

次に、有機物 124、レジスト 122 および反射防止層 120 を除去することで最小加工寸法よりも小さい穴を形成することができる（図 3（D）参照。）。有機物 124、レジスト 122 および反射防止層 120 の除去には、プラズマアッシングなどのドライエッチング法または／およびウェットエッチング法を用いることができる。

**【 0 0 6 7 】**

このとき、層 110a は、第 1 の領域と、第 2 の領域と、を有する。第 1 の領域は、平坦な領域である。第 2 の領域は傾斜を有する領域である。第 2 の領域は、傾斜の度合いが変化する場合がある。例えば、第 1 の領域の近傍では傾斜がきつく、第 1 の領域から遠ざかるほど傾斜が緩くなるような形状を有する場合がある。また、層 116a は、第 3 の領域と、第 4 の領域と、を有する。第 3 の領域は、平坦な領域である。第 4 の領域は傾斜を有する領域である。第 4 の領域は、傾斜の度合いが変化する場合がある。例えば、第 3 の領域の近傍では傾斜がきつく、第 3 の領域から遠ざかるほど傾斜が緩くなるような形状を有する場合がある。層 110a および層 116a が、このような形状を有することにより、層 110a および層 116a よりも上方に形成する層などの段差被覆性を高くすることができます。そのため、形状不良などが起こりにくくなる。層 110b および層 116b についても同様である。

40

**【 0 0 6 8 】**

50

## &lt; 加工方法 4 &gt;

また、図 4 に示すように、エッティングの工程を追加することにより、図 1 ( E )、図 2 ( E ) および図 3 ( D ) とは異なる形状を得ることもできる。

## 【 0 0 6 9 】

図 4 ( A ) および図 4 ( B ) は、それぞれ図 1 ( A ) および図 1 ( B ) と同じであるため、説明を省略する。

## 【 0 0 7 0 】

次に、レジスト 122 および反射防止層 120 をマスクとして用いて、層 116 が露出するように層 110 をエッティングすることで、層 110a および層 110b を形成する（図 4 ( C ) 参照。）。層 110 のエッティングは、ドライエッティング法または / およびウェットエッティング法によって行うことができる。なお、層 110a と層 110b とが奥行き方向で繋がっていても構わない。

10

## 【 0 0 7 1 】

次に、プラズマ処理を行う。プラズマ処理によって、有機物の堆積とエッティングが起こる。また、層 116 の露出部もエッティングされる。ただし、プラズマ処理の条件によって、層 116 の露出部をエッティングさせないこともできる。

## 【 0 0 7 2 】

一方、レジスト 122 の側面、反射防止層 120 の側面、層 110a の側面および層 110b の側面では、有機物のエッティング速度が堆積速度よりも遅くなる。したがって、該領域では有機物 124 が堆積する。

20

## 【 0 0 7 3 】

次に、有機物 124、レジスト 122 および反射防止層 120 をマスクとして用いて、層 116 をエッティングし、層 116a および層 116b を形成する（図 4 ( D ) 参照。）。層 116 のエッティングは、ドライエッティング法または / およびウェットエッティング法によって行うことができる。このときに、有機物 124 を除去してもよい。なお、層 116a と層 116b とが奥行き方向で繋がっていても構わない。

## 【 0 0 7 4 】

層 116a と層 116bとの間の距離を L1 とする。L1 は、有機物 124 の分だけ L0 よりも小さくなる。即ち、露光機やレジストなどによって決定する最小の寸法よりも小さい形状を得ることができる。

30

## 【 0 0 7 5 】

次に、有機物 124、レジスト 122 および反射防止層 120 を除去することで最小加工寸法よりも小さい穴を形成することができる（図 4 ( E ) 参照。）。有機物 124、レジスト 122 および反射防止層 120 の除去には、プラズマアッシングなどのドライエッティング法または / およびウェットエッティング法を用いることができる。

## 【 0 0 7 6 】

このとき、層 116a は、第 1 の領域と、第 2 の領域と、第 3 の領域と、を有する。第 2 の領域は、第 1 の領域と第 3 の領域との間に位置する。第 1 の領域は、平坦な領域である。第 2 の領域および第 3 の領域は傾斜を有する領域である。第 2 の領域は、第 3 の領域よりも傾斜が緩やかである。第 2 の領域における傾斜は、第 1 の領域近傍から第 3 の領域近傍にかけて傾斜の度合いが変化する場合がある。例えば、第 1 の領域の近傍では傾斜がきつく、第 3 の領域の近傍では傾斜が緩くなるような形状を有する場合がある。層 116a が、このような形状を有することにより、層 116a よりも上方に形成する層などの段差被覆性を高くすることができる。そのため、形状不良などが起りにくくなる。層 116b についても同様である。

40

## 【 0 0 7 7 】

## &lt; 加工方法 5 &gt;

また、図 5 に示すように、エッティングの工程を追加し、プラズマ処理の条件を変更することにより、図 1 ( E )、図 2 ( E )、図 3 ( D ) および図 4 ( E ) とは異なる形状を得ることもできる。

50

**【0078】**

図5(A)および図5(B)は、それぞれ図1(A)および図1(B)と同じであるため、説明を省略する。また、図5(C)は、図4(C)と同じであるため、説明を省略する。

**【0079】**

次に、プラズマ処理を行う。プラズマ処理によって、有機物の堆積とエッチングが起こる。また、層116の露出部をエッチングすることで、層116aおよび層116bを形成する。なお、層116aと層116bとが奥行き方向で繋がっていても構わない。

**【0080】**

一方、レジスト122の側面、反射防止層120の側面、層110aの側面および層110bの側面では、有機物のエッチング速度が堆積速度よりも遅くなる。したがって、該領域では有機物124が堆積する(図5(D)参照。)。

10

**【0081】**

層116aと層116bとの間の距離をL1とする。L1は、有機物124の分だけL0よりも小さくなる。即ち、露光機やレジストなどによって決定する最小の寸法よりも小さい形状を得ることができる。

**【0082】**

次に、有機物124、レジスト122および反射防止層120を除去することで最小加工寸法よりも小さい穴を形成することができる(図5(E)参照。)。有機物124、レジスト122および反射防止層120の除去には、プラズマアッシングなどのドライエッチング法または/およびウェットエッチング法を用いることができる。

20

**【0083】**

このとき、層116aは、第1の領域と、第2の領域と、を有する。第1の領域は、平坦な領域である。第2の領域は傾斜を有する領域である。第2の領域は、傾斜の度合いが変化する場合がある。例えば、第1の領域の近傍では傾斜がきつく、第1の領域から遠ざかるほど傾斜が緩くなるような形状を有する場合がある。層116aが、このような形状を有することにより、層116aよりも上方に形成する層などの段差被覆性を高くすることができます。そのため、形状不良などが起こりにくくなる。層116bについても同様である。

**【0084】**

30

**<加工方法6>**

また、図6に示すように、層110を有さないことにより、図1(E)、図2(E)、図3(D)、図4(E)および図5(E)とは異なる形状を得ることもできる。

**【0085】**

まず、層116を準備する(図6(A)参照。)。

**【0086】**

次に、反射防止層を成膜する。次に、レジストを成膜する。次に、レジストを加工し、レジスト122を形成する。

**【0087】**

次に、レジスト122をマスクとして用いて反射防止層をエッチングし、反射防止層120を形成する(図6(B)参照。)。ただし、反射防止層120を有さなくてもよい場合がある。

40

**【0088】**

レジスト122の間の距離をL0とする。

**【0089】**

次に、プラズマ処理を行う。プラズマ処理によって、有機物の堆積とエッチングが起こる。また、層110の露出部もエッチングされる。ただし、プラズマ処理の条件によって、層110の露出部をエッチングさせないこともできる。

**【0090】**

一方、レジスト122の側面および反射防止層120の側面では、有機物のエッチング速

50

度が堆積速度よりも遅くなる。したがって、該領域では有機物 124 が堆積する（図 6（C）参照。）。

#### 【0091】

次に、有機物 124、レジスト 122 および反射防止層 120 をマスクとして用いて、層 116 をエッチングし、層 116a および層 116b を形成する（図 6（D）参照。）。層 116 のエッチングは、ドライエッチング法または／およびウェットエッチング法によって行うことができる。このときに、有機物 124 を除去してもよい。なお、層 116a と層 116b とが奥行き方向で繋がっていても構わない。

#### 【0092】

層 116a と層 116b との間の距離を L1 とする。L1 は、有機物 124 の分だけ L0 よりも小さくなる。即ち、露光機やレジストなどによって決定する最小の寸法よりも小さい形状を得ることができる。

10

#### 【0093】

次に、有機物 124、レジスト 122 および反射防止層 120 を除去することで最小加工寸法よりも小さい穴を形成することができる（図 6（E）参照。）。有機物 124、レジスト 122 および反射防止層 120 の除去には、プラズマアッシングなどのドライエッチング法または／およびウェットエッチング法を用いることができる。なお、図 4（E）の形状を得た後に、層 110a および層 110b を除去することでも、図 6（E）と同様の形状を得ることができる。

20

#### 【0094】

このとき、層 116a は、第 1 の領域と、第 2 の領域と、第 3 の領域と、を有する。第 2 の領域は、第 1 の領域と第 3 の領域との間に位置する。第 1 の領域は、平坦な領域である。第 2 の領域および第 3 の領域は傾斜を有する領域である。第 2 の領域は、第 3 の領域よりも傾斜が緩やかである。第 2 の領域における傾斜は、第 1 の領域近傍から第 3 の領域近傍にかけて傾斜の度合いが変化する場合がある。例えば、第 1 の領域の近傍では傾斜がきつく、第 3 の領域の近傍では傾斜が緩くなるような形状を有する場合がある。層 116a が、このような形状を有することにより、層 116a よりも上方に形成する層などの段差被覆性を高くすることができる。そのため、形状不良などが起こりにくくなる。層 116b についても同様である。

#### 【0095】

30

#### < 加工方法 7 >

また、図 7 に示すように、プラズマ処理の条件などを変更することにより、図 1（E）、図 2（E）、図 3（D）、図 4（E）、図 5（E）および図 6（E）とは異なる形状を得ることもできる。

#### 【0096】

図 7（A）および図 7（B）は、それぞれ図 6（A）および図 6（B）と同じであるため、説明を省略する。

#### 【0097】

次に、プラズマ処理を行う。プラズマ処理によって、有機物の堆積とエッチングが起こる。また、層 116 の露出部もエッチングすることで、層 116a および層 116b を形成する。なお、層 116a と層 116b とが奥行き方向で繋がっていても構わない。

40

#### 【0098】

一方、レジスト 122 の側面および反射防止層 120 の側面では、有機物のエッチング速度が堆積速度よりも遅くなる。したがって、該領域では有機物 124 が堆積する（図 7（C）参照。）。

#### 【0099】

層 116a と層 116b との間の距離を L1 とする。L1 は、有機物 124 の分だけ L0 よりも小さくなる。即ち、露光機やレジストなどによって決定する最小の寸法よりも小さい形状を得ることができる。

#### 【0100】

50

次に、有機物 124、レジスト 122 および反射防止層 120 を除去することで最小加工寸法よりも小さい穴を形成することができる（図 7（D）参照。）。有機物 124、レジスト 122 および反射防止層 120 の除去には、プラズマアッティングなどのドライエッティング法または／およびウェットエッティング法を用いることができる。なお、図 5（E）の形状を得た後に、層 110a および層 110b を除去することでも、図 7（D）と同様の形状を得ることができる。

#### 【0101】

このとき、層 116a は、第 1 の領域と、第 2 の領域と、を有する。第 1 の領域は、平坦な領域である。第 2 の領域は傾斜を有する領域である。第 2 の領域は、傾斜の度合いが変化する場合がある。例えば、第 1 の領域の近傍では傾斜がきつく、第 1 の領域から遠ざかるほど傾斜が緩くなるような形状を有する場合がある。層 116a が、このような形状を有することにより、層 116a よりも上方に形成する層などの段差被覆性を高くすることができます。そのため、形状不良などが起こりにくくなる。層 116b についても同様である。

10

#### 【0102】

以上に示したように、本発明の一態様に係る加工方法によって、層の形状を最小加工寸法よりも小さい寸法で加工することが可能となる。また、形状不良が起こりにくい形状の層を形成することができる。

#### 【0103】

##### <トランジスタ 1>

20

以下では、本発明の一態様に係るトランジスタについて説明する。

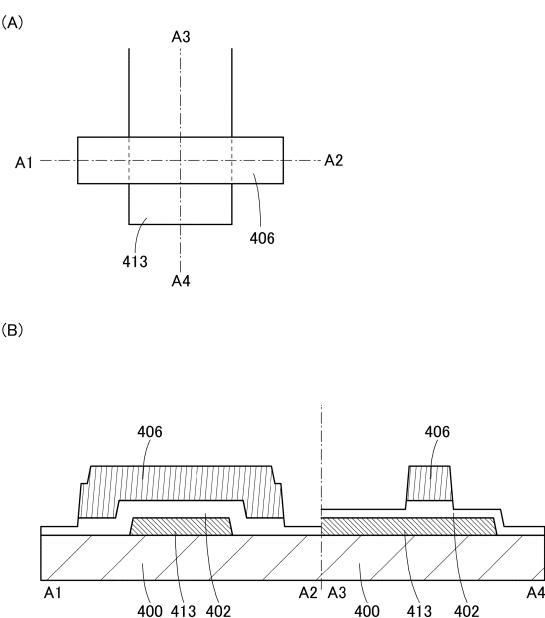

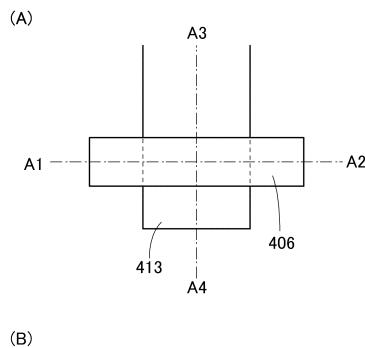

#### 【0104】

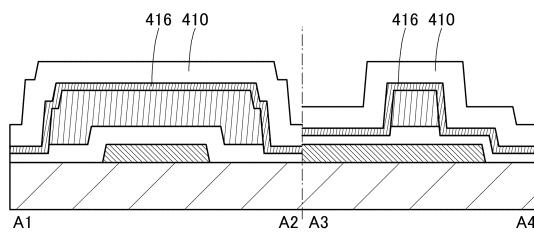

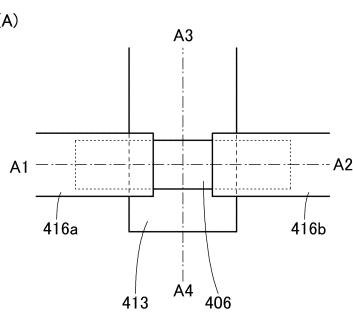

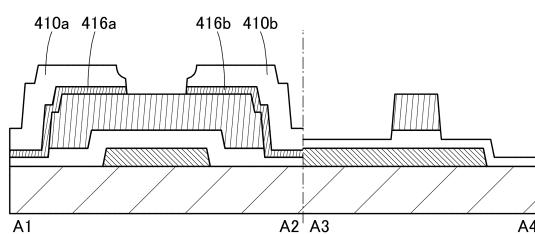

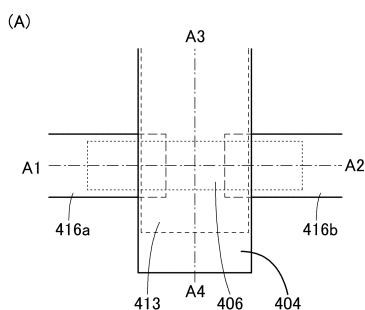

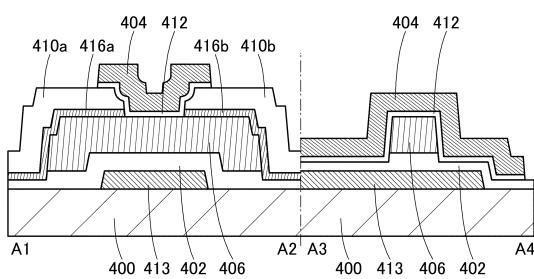

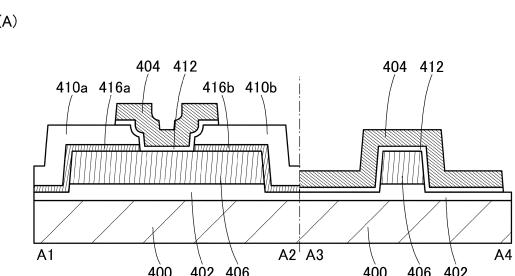

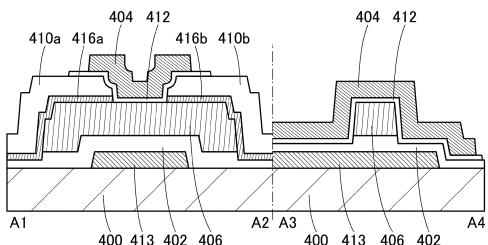

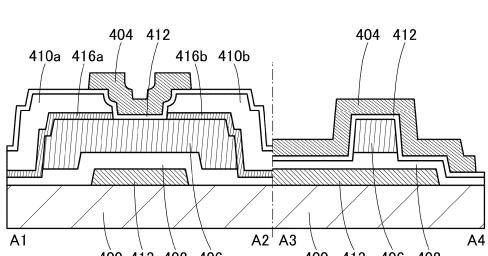

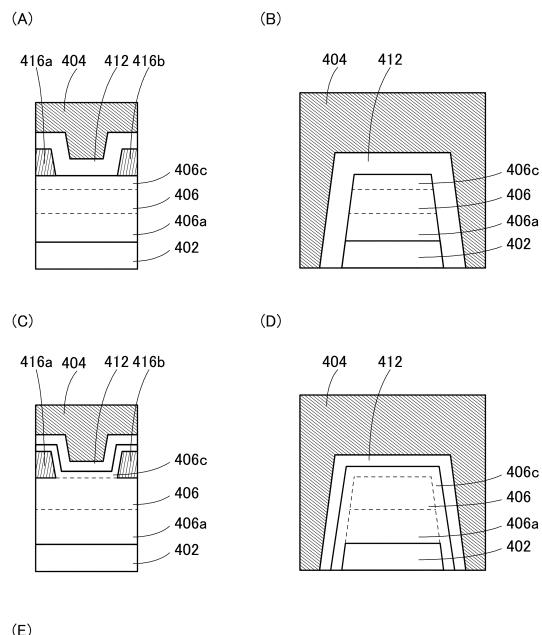

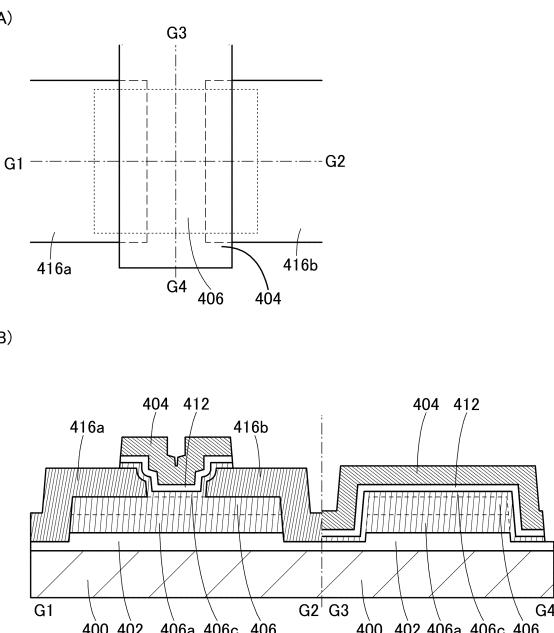

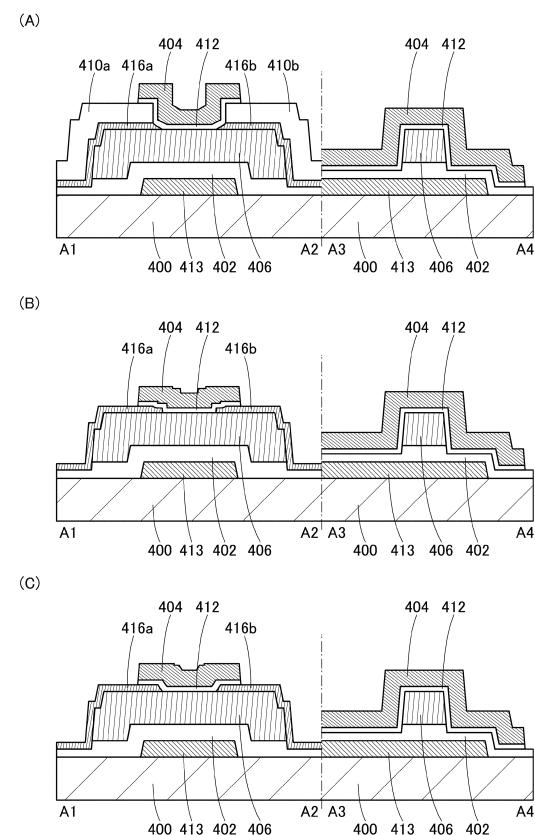

図 8（A）、図 9（A）、図 10（A）および図 11（A）は、トランジスタの作製方法を説明する上面図である。各上面図には、一点鎖線 A1 - A2 および一点鎖線 A3 - A4 が記され、それに対応した断面図を図 8（B）、図 9（B）、図 10（B）および図 11（B）に示す。

#### 【0105】

まずは、基板 400 を準備する。

#### 【0106】

基板 400 としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板（イットリア安定化ジルコニア基板など）、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムなどの化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えば SOI（Silicon On Insulator）基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

30

#### 【0107】

また、基板 400 として、可とう性基板を用いてよい。なお、可とう性基板上にトランジスタを設ける方法としては、非可とう性の基板上にトランジスタを作製した後、トランジスタを剥離し、可とう性基板である基板 400 に転置する方法もある。その場合には、非可とう性基板とトランジスタとの間に剥離層を設けるとよい。なお、基板 400 として、繊維を編みこんだシート、フィルムまたは箔などを用いてよい。また、基板 400 が伸縮性を有してもよい。また、基板 400 は、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有してもよい。または、元の形状に戻らない性質を有してもよい。基板 4

40

50

00の厚さは、例えば、5 μm以上700 μm以下、好ましくは10 μm以上500 μm以下、さらに好ましくは15 μm以上300 μm以下とする。基板400を薄くすると、半導体装置を軽量化することができる。また、基板400を薄くすることで、ガラスなどを用いた場合にも伸縮性を有する場合や、折り曲げや引っ張りをやめた際に、元の形状に戻る性質を有する場合がある。そのため、落下などによって基板400上の半導体装置に加わる衝撃などを緩和することができる。即ち、丈夫な半導体装置を提供することができる。

#### 【0108】

可とう性基板である基板400としては、例えば、金属、合金、樹脂もしくはガラス、またはそれらの繊維などを用いることができる。可とう性基板である基板400は、線膨張率が低いほど環境による変形が抑制されて好ましい。可とう性基板である基板400としては、例えば、線膨張率が $1 \times 10^{-3} / K$ 以下、 $5 \times 10^{-5} / K$ 以下、または $1 \times 10^{-5} / K$ 以下である材質を用いればよい。樹脂としては、例えば、ポリエステル、ポリオレフィン、ポリアミド（ナイロン、アラミドなど）、ポリイミド、ポリカーボネート、アクリルなどがある。特に、アラミドは、線膨張率が低いため、可とう性基板である基板400として好適である。

#### 【0109】

次に、導電体を成膜する。導電体の成膜は、スパッタリング法、化学気相成長（CVD：Chemical Vapor Deposition）法、分子線エピタキシー（MBE：Molecular Beam Epitaxy）法またはパルスレーザ堆積（PLD：Pulsed Laser Deposition）法、原子層堆積（ALD：Atomic Layer Deposition）法などを用いて行うことができる。

#### 【0110】

なお、CVD法は、プラズマを利用するプラズマCVD（PECVD：Plasma Enhanced CVD）法、熱を利用する熱CVD（TCVD：Thermal CVD）法、光を利用する光CVD（Photo CVD）法などに分類できる。さらに用いる原料ガスによって金属CVD（MCVD：Metal CVD）法、有機金属CVD（MOCSV：Metal Organic CVD）法に分けることができる。

#### 【0111】

PECVD法は、比較的低温で高品質の膜が得られる。また、TCVD法は、プラズマを用いないため、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。例えば、半導体装置に含まれる配線、電極、素子（トランジスタ、容量素子など）などは、プラズマから電荷を受け取ることでチャージアップする場合がある。このとき、蓄積した電荷によって、半導体装置に含まれる配線、電極、素子などが破壊される場合がある。一方、プラズマを用いないTCVD法の場合、こういったプラズマダメージが生じないため、半導体装置の歩留まりを高くすることができる。また、TCVD法では、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

#### 【0112】

また、ALD法も、被処理物へのプラズマダメージを小さくすることが可能な成膜方法である。また、ALD法も、成膜中のプラズマダメージが生じないため、欠陥の少ない膜が得られる。

#### 【0113】

CVD法およびALD法は、ターゲットなどから放出される粒子が堆積する成膜方法とは異なり、被処理物の表面における反応により膜が形成される成膜方法である。したがって、被処理物の形状の影響を受けにくく、良好な段差被覆性を有する成膜方法である。特に、ALD法は、優れた段差被覆性と、優れた厚さの均一性を有するため、アスペクト比の高い開口部の表面を被覆する場合などに好適である。ただし、ALD法は、比較的成膜速度が遅いため、成膜速度の速いCVD法などの他の成膜方法と組み合わせて用いることが好ましい場合もある。

#### 【0114】

10

20

30

40

50

CVD法およびALD法は、原料ガスの流量比によって、得られる膜の組成を制御することができる。例えば、CVD法およびALD法では、原料ガスの流量比によって、所望の組成の膜を成膜することができる。また、例えば、CVD法およびALD法では、成膜しながら原料ガスの流量比を変化させることによって、組成が連続的に変化した膜を成膜することができる。原料ガスの流量比を変化させながら成膜する場合、複数の成膜室を用いて成膜する場合と比べて、搬送や圧力調整に掛かる時間の分、成膜に掛かる時間を短くすることができる。したがって、半導体装置の生産性を高めることができる場合がある。

#### 【0115】

次に、導電体上にレジストなどを形成し、該レジストを用いて加工し、導電体413を形成する。なお、単にレジストを形成するという場合、レジストの下に反射防止層を形成する場合も含まれる。

10

#### 【0116】

レジストは、対象物をエッチングなどによって加工した後で除去する。レジストの除去には、プラズマ処理または／およびウェットエッチングを用いる。なお、プラズマ処理としては、プラズマアッシングが好適である。レジストなどの除去が不十分な場合、0.001 volume %以上1 volume %以下の濃度のフッ化水素酸または／およびオゾン水などによって取り残したレジストなどを除去しても構わない。

#### 【0117】

導電体を加工して導電体413を形成する際、図1乃至図7のいずれかに記載の加工方法を用いててもよい。

20

#### 【0118】

導電体413となる導電体としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンクスティンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0119】

次に、絶縁体402を成膜する。絶縁体402の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

30

#### 【0120】

絶縁体402としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体402としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

#### 【0121】

絶縁体402は、基板400からの不純物の拡散を防止する機能を有してもよい。

40

#### 【0122】

次に、半導体を成膜する。半導体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

#### 【0123】

次に、加熱処理を行うことが好ましい。加熱処理を行うことで、半導体中の水素濃度を低減させることができる場合がある。また、半導体中の酸素欠損を低減させることができる場合がある。

#### 【0124】

次に、半導体上にレジストなどを形成し、該レジストを用いて加工し、半導体406を形

50

成する（図8（A）および図8（B）参照。）。このとき、半導体406と重ならない絶縁体402の一部をエッチングしても構わない。こうすることで、絶縁体402に凸部が形成される。絶縁体402に凸部が形成されることで、後述するs-channel構造を実現しやすくなる。

#### 【0125】

半導体を加工して半導体406を形成する際、図1乃至図7のいずれかに記載の加工方法を用いてもよい。

#### 【0126】

次に、導電体416を成膜する。導電体416の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

10

#### 【0127】

導電体416としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニアム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンゲステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0128】

次に、絶縁体410を成膜する（図9（A）および図9（B）参照。）。絶縁体410の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

20

#### 【0129】

絶縁体410としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニアム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体410としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニアム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

30

#### 【0130】

次に、絶縁体410上にレジストなどを形成し、該レジストを用いて加工し、絶縁体410aおよび絶縁体410b、ならびに導電体416aおよび導電体416bを形成する（図10（A）および図10（B）参照。）。

#### 【0131】

この際、図1乃至図7のいずれかに記載の加工方法を用いてもよい。例えば、図1乃至図7において、層116を導電体416に、層110を絶縁体410に置き替えればよい。ここでは、図1に示した加工方法と同様の方法により、絶縁体410および導電体416を加工した場合を図示している。

40

#### 【0132】

例えば、導電体413をゲート電極、絶縁体402をゲート絶縁体、導電体416aをソース電極、導電体416bをドレイン電極とすれば、図10までで工程を完了し、ボトムゲート構造を有するトランジスタとしてもよい。

#### 【0133】

次に、絶縁体を成膜する。絶縁体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

#### 【0134】

次に、導電体を成膜する。導電体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

#### 【0135】

50

次に、導電体上にレジストなどを形成し、該レジストを用いて加工し、導電体404を形成する。また、該レジストまたは導電体404を用いて絶縁体を加工し、絶縁体412を形成する(図11(A)および図11(B)参照。)。なお、ここでは絶縁体412と導電体404とが上面から見たときに同様の形状となるよう加工しているが、この形状に限定されるものではない。例えば、絶縁体412と導電体404とを別のレジストを用いて加工してもよい。例えば、絶縁体412を形成してから、導電体404となる導電体を成膜してもよいし、導電体404を形成した後で絶縁体412となる絶縁体上に別途レジストなどを形成してもよい。

#### 【0136】

この際、図1乃至図7のいずれかに記載の加工方法を用いてもよい。例えば、図1乃至図7において、層116を絶縁体412となる絶縁体に、層110を導電体404となる導電体に置き替えればよい。

10

#### 【0137】

絶縁体412となる絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体412となる絶縁体としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

20

#### 【0138】

導電体404となる導電体としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンクステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

30

#### 【0139】

次に、絶縁体を成膜してもよい。絶縁体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

#### 【0140】

絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。絶縁体は、好ましくは酸化アルミニウム、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを含む絶縁体を、単層で、または積層で用いればよい。

40

#### 【0141】

絶縁体は、バリア層としての機能を有することが好ましい。絶縁体は、例えば、酸素または/および水素をブロックする機能を有する。または、絶縁体は、例えば、絶縁体402または絶縁体412よりも、酸素または/および水素をブロックする能力が高いことが好ましい。

#### 【0142】

以上の工程により、本発明の一態様に係るトランジスタを作製することができる。

#### 【0143】

図11(B)に示したトランジスタは、導電体416aと導電体404との間に絶縁体410aを有し、導電体416bと導電体404との間に絶縁体410bを有する。即ち、

50

導電体 416a および導電体 416b などに起因する寄生容量が小さい。そのため、図 1 (B) に示したトランジスタを用いた半導体装置は、高い周波数特性を有する。

#### 【0144】

図 11 (B) に示すように、半導体 406 の側面は、導電体 416a および導電体 416b と接する。また、導電体 404 の電界によって、半導体 406 を電気的に取り囲むことができる（導電体から生じる電界によって、半導体を電気的に取り囲むトランジスタの構造を、surrounded channel (s-channel) 構造とよぶ。）。そのため、半導体 406 の全体（上面、下面および側面）にチャネルが形成される。s-channel 構造では、トランジスタのソース - ドレイン間に大電流を流すことができ、導通時の電流（オン電流）を高くすることができます。

10

#### 【0145】

なお、トランジスタが s-channel 構造を有する場合、半導体 406 の側面にもチャネルが形成される。したがって、半導体 406 が厚いほどチャネル領域は大きくなる。即ち、半導体 406 が厚いほど、トランジスタのオン電流を高くすることができます。また、半導体 406 が厚いほど、キャリアの制御性の高い領域の割合が増えるため、サブスレッショルドスイッチング値を小さくすることができる。例えば、10 nm 以上、好ましくは 20 nm 以上、さらに好ましくは 40 nm 以上、より好ましくは 60 nm 以上、より好ましくは 100 nm 以上の厚さの領域を有する半導体 406 とすればよい。ただし、半導体装置の生産性が低下する場合があるため、例えば、300 nm 以下、好ましくは 200 nm 以下、さらに好ましくは 150 nm 以下の厚さの領域を有する半導体 406 とすればよい。なお、チャネル形成領域が縮小していくと、半導体 406 が薄いほうがトランジスタの電気特性が向上する場合もある。よって、半導体 406 の厚さが 10 nm 未満であってもよい。

20

#### 【0146】

高いオン電流が得られるため、s-channel 構造は、微細化されたトランジスタに適した構造といえる。トランジスタを微細化できるため、該トランジスタを有する半導体装置は、集積度の高い、高密度化された半導体装置とすることが可能となる。例えば、トランジスタは、チャネル長が好ましくは 40 nm 以下、さらに好ましくは 30 nm 以下、より好ましくは 20 nm 以下の領域を有し、かつ、トランジスタは、チャネル幅が好ましくは 40 nm 以下、さらに好ましくは 30 nm 以下、より好ましくは 20 nm 以下の領域を有する。

30

#### 【0147】

なお、導電体 413 を形成しなくてもよい（図 12 (A) 参照。）。また、絶縁体 412 が導電体 404 から迫り出した形状としてもよい（図 12 (B) 参照。）。また、絶縁体 412 となる絶縁体を加工しなくてもよい（図 12 (C) 参照。）。

#### 【0148】

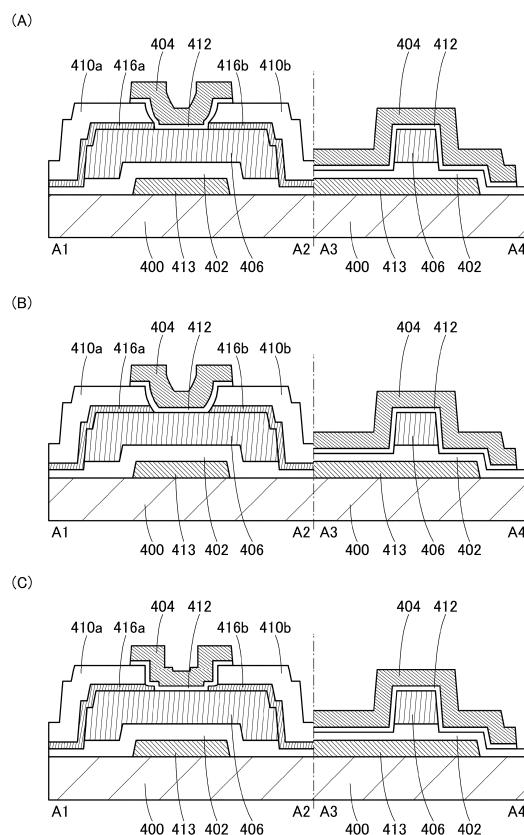

図 11 (B) などには、代表例として図 1 と同様の形状の導電体 416a および導電体 416b、ならびに絶縁体 410a および絶縁体 410b を示したが、本発明の一態様はこれに限定されるものではない。例えば、図 51 (A) に示すように、図 2 (E) と同様の形状としてもよい。また、図 51 (B) に示すように、図 3 (D) と同様の形状としてもよい。また、図 51 (C) に示すように、図 4 (D) と同様の形状としてもよい。また、図 52 (A) に示すように、図 5 (E) と同様の形状としてもよい。また、図 52 (B) に示すように、図 6 (E) と同様の形状としてもよい。また、図 52 (C) に示すように、図 7 (D) と同様の形状としてもよい。また、図 53 (A) に示すように、絶縁体 410a および絶縁体 410b が端部に向かって徐々に傾斜がきつくなる形状としてもよい。また、図 53 (B) に示すように、絶縁体 410a の端部および絶縁体 410b の端部において、段階的に傾斜角が変化する領域を有してもよい。また、図 53 (C) に示すように、導電体 416a および導電体 416b が積層構造を有してもよい。そのとき、例えば、下層が上層よりも迫り出していてもよい。また、これらの形状を部分的に組み合わせることもできる。こういった形状の作りわけは、プラズマ処理の条件の変更やエッチング工

40

50

程の追加などによって実現することができる。

**【0149】**

<半導体>

半導体406の上下に半導体を配置することで、トランジスタの電気特性を向上させることができる場合がある。以下では、半導体406、およびその上下に配置する半導体について、図13を用いて詳細に説明する。

**【0150】**

図13(A)は、図11(B)に示したトランジスタの、チャネル長方向における半導体406近傍を拡大した断面図である。また、図13(B)は、図11(B)に示したトランジスタの、チャネル幅方向における半導体406近傍を拡大した断面図である。

10

**【0151】**

図13(A)および図13(B)に示すトランジスタの構造では、絶縁体402と半導体406との間に、半導体406aが配置される。また、導電体416a、導電体416bおよび絶縁体412と、半導体406と、の間に半導体406cが配置される。

**【0152】**

または、トランジスタが図13(C)および図13(D)に示す構造を有しても構わない。

**【0153】**

図13(C)は、図11(B)に示したトランジスタの、チャネル長方向における半導体406近傍を拡大した断面図である。また、図13(D)は、図11(B)に示したトランジスタの、チャネル幅方向における半導体406近傍を拡大した断面図である。

20

**【0154】**

図13(C)および図13(D)に示すトランジスタの構造では、絶縁体402と半導体406との間に、半導体406aが配置される。また、絶縁体402、導電体416a、導電体416b、半導体406aおよび半導体406と、絶縁体412と、の間に半導体406cが配置される。

**【0155】**

半導体406は、例えば、インジウムを含む酸化物半導体である。半導体406は、例えば、インジウムを含むと、キャリア移動度(電子移動度)が高くなる。また、半導体406は、元素Mを含むと好ましい。元素Mは、好ましくは、アルミニウム、ガリウム、イットリウムまたはスズなどとする。そのほかの元素Mに適用可能な元素としては、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステンなどがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。元素Mは、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素Mは、例えば、酸化物半導体のエネルギーギャップを大きくする機能を有する元素である。また、半導体406は、亜鉛を含むと好ましい。酸化物半導体は、亜鉛を含むと結晶化しやすくなる場合がある。

30

**【0156】**

ただし、半導体406は、インジウムを含む酸化物半導体に限定されない。半導体406は、例えば、亜鉛スズ酸化物、ガリウムスズ酸化物などの、インジウムを含まず、亜鉛を含む酸化物半導体、ガリウムを含む酸化物半導体、スズを含む酸化物半導体などであっても構わない。

40

**【0157】**

半導体406は、例えば、エネルギーギャップが大きい酸化物を用いる。半導体406のエネルギーギャップは、例えば、2.5eV以上4.2eV以下、好ましくは2.8eV以上3.8eV以下、さらに好ましくは3eV以上3.5eV以下とする。

**【0158】**

例えば、半導体406aおよび半導体406cは、半導体406を構成する酸素以外の元素一種以上、または二種以上から構成される酸化物半導体である。半導体406を構成す

50

る酸素以外の元素一種以上、または二種以上から半導体406aおよび半導体406cが構成されるため、半導体406aと半導体406との界面、および半導体406と半導体406cとの界面において、欠陥準位が形成されにくい。

#### 【0159】

半導体406a、半導体406および半導体406cは、少なくともインジウムを含むと好ましい。なお、半導体406aがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高いとする。また、半導体406がIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが25atomic%より高く、Mが75atomic%未満、さらに好ましくはInが34atomic%より高く、Mが66atomic%未満とする。また、半導体406cがIn-M-Zn酸化物のとき、InおよびMの和を100atomic%としたとき、好ましくはInが50atomic%未満、Mが50atomic%より高く、さらに好ましくはInが25atomic%未満、Mが75atomic%より高くする。なお、半導体406cは、半導体406aと同種の酸化物を用いても構わない。ただし、半導体406aまたは/および半導体406cがインジウムを含まなくても構わぬ場合がある。例えば、半導体406aまたは/および半導体406cが酸化ガリウムであっても構わぬ。なお、半導体406a、半導体406および半導体406cに含まれる各元素の原子数が、簡単な整数比にならなくても構わぬ。

10

#### 【0160】

半導体406は、半導体406aおよび半導体406cよりも電子親和力の大きい酸化物を用いる。例えば、半導体406として、半導体406aおよび半導体406cよりも電子親和力の0.07eV以上1.3eV以下、好ましくは0.1eV以上0.7eV以下、さらに好ましくは0.15eV以上0.4eV以下大きい酸化物を用いる。なお、電子親和力は、真空準位と伝導帯下端のエネルギーとの差である。

20

#### 【0161】

なお、インジウムガリウム酸化物は、小さい電子親和力と、高い酸素プロック性を有する。そのため、半導体406cがインジウムガリウム酸化物を含むと好ましい。ガリウム原子割合[Ga/(In+Ga)]は、例えば、70%以上、好ましくは80%以上、さらに好ましくは90%以上とする。

30

#### 【0162】

このとき、ゲート電圧を印加すると、半導体406a、半導体406、半導体406cのうち、電子親和力の大きい半導体406にチャネルが形成される。

#### 【0163】

ここで、半導体406aと半導体406との間には、半導体406aと半導体406との混合領域を有する場合がある。また、半導体406と半導体406cとの間には、半導体406と半導体406cとの混合領域を有する場合がある。混合領域は、欠陥準位密度が低くなる。そのため、半導体406a、半導体406および半導体406cの積層体は、それぞれの界面近傍において、エネルギーが連続的に変化する（連続接合ともいう。）バンド構造となる（図13（E）参照。）。なお、半導体406a、半導体406および半導体406cは、それぞれの界面を明確に判別できない場合がある。

40

#### 【0164】

このとき、電子は、半導体406a中および半導体406c中ではなく、半導体406中を主として移動する。上述したように、半導体406aと半導体406との界面における欠陥準位密度、および半導体406と半導体406cとの界面における欠陥準位密度を低くすることによって、半導体406中で電子の移動が阻害されることが少なく、トランジスタのオン電流を高くすることができます。

#### 【0165】

トランジスタのオン電流は、電子の移動を阻害する要因を低減するほど、高くすることができます。

50

できる。例えば、電子の移動を阻害する要因のない場合、効率よく電子が移動すると推定される。電子の移動は、例えば、チャネル形成領域の物理的な凹凸が大きい場合にも阻害される。

#### 【0166】

トランジスタのオン電流を高くするためには、例えば、半導体406の上面または下面(被形成面、ここでは半導体406a)の、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における二乗平均平方根(RMS: Root Mean Square)粗さが $1\text{ nm}$ 未満、好ましくは $0.6\text{ nm}$ 未満、さらに好ましくは $0.5\text{ nm}$ 未満、より好ましくは $0.4\text{ nm}$ 未満とすればよい。また、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における平均面粗さ(Raともいう。)が $1\text{ nm}$ 未満、好ましくは $0.6\text{ nm}$ 未満、さらに好ましくは $0.5\text{ nm}$ 未満、より好ましくは $0.4\text{ nm}$ 未満とすればよい。また、 $1\text{ }\mu\text{m} \times 1\text{ }\mu\text{m}$ の範囲における最大高低差(P-Vともいう。)が $10\text{ nm}$ 未満、好ましくは $9\text{ nm}$ 未満、さらに好ましくは $8\text{ nm}$ 未満、より好ましくは $7\text{ nm}$ 未満とすればよい。RMS粗さ、RaおよびP-Vは、エスアイアイ・ナノテクノロジー株式会社製走査型プローブ顕微鏡システムSPA-500などを用いて測定することができる。10

#### 【0167】

また、トランジスタのオン電流を高くするためには、半導体406cの厚さは小さいほど好ましい。例えば、 $10\text{ nm}$ 未満、好ましくは $5\text{ nm}$ 以下、さらに好ましくは $3\text{ nm}$ 以下の領域を有する半導体406cとすればよい。一方、半導体406cは、チャネルの形成される半導体406へ、隣接する絶縁体を構成する酸素以外の元素(水素、シリコンなど)が入り込まないようブロックする機能を有する。そのため、半導体406cは、ある程度の厚さを有することが好ましい。例えば、 $0.3\text{ nm}$ 以上、好ましくは $1\text{ nm}$ 以上、さらに好ましくは $2\text{ nm}$ 以上の厚さの領域を有する半導体406cとすればよい。また、半導体406cは、絶縁体402などから放出される酸素の外方拡散を抑制するために、酸素をブロックする性質を有すると好ましい。20

#### 【0168】

また、信頼性を高くするためには、半導体406aは厚く、半導体406cは薄いことが好ましい。例えば、 $10\text{ nm}$ 以上、好ましくは $20\text{ nm}$ 以上、さらに好ましくは $40\text{ nm}$ 以上、より好ましくは $60\text{ nm}$ 以上の厚さの領域を有する半導体406aとすればよい。半導体406aの厚さを、厚くすることで、隣接する絶縁体と半導体406aとの界面からチャネルの形成される半導体406までの距離を離すことができる。ただし、半導体装置の生産性が低下する場合があるため、例えば、 $200\text{ nm}$ 以下、好ましくは $120\text{ nm}$ 以下、さらに好ましくは $80\text{ nm}$ 以下の厚さの領域を有する半導体406aとすればよい。30

#### 【0169】

例えば、半導体406と半導体406aとの間に、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)において、 $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $1 \times 10^{19}\text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $5 \times 10^{18}\text{ atoms/cm}^3$ 以下、さらに好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $2 \times 10^{18}\text{ atoms/cm}^3$ 以下のシリコン濃度となる領域を有する。また、半導体406と半導体406cとの間に、SIMSにおいて、 $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $1 \times 10^{19}\text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $5 \times 10^{18}\text{ atoms/cm}^3$ 以下、さらに好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $2 \times 10^{18}\text{ atoms/cm}^3$ 以下のシリコン濃度となる領域を有する。40

#### 【0170】

また、半導体406は、SIMSにおいて、 $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $2 \times 10^{20}\text{ atoms/cm}^3$ 以下、好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $5 \times 10^{19}\text{ atoms/cm}^3$ 以下、より好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 以上 $1 \times 10^{19}\text{ atoms/cm}^3$ 以下、さらに好ましくは $1 \times 10^{16}\text{ atoms/cm}^3$ 50

以上  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下の水素濃度となる領域を有する。また、半導体 406 の水素濃度を低減するために、半導体 406a および半導体 406c の水素濃度を低減すると好ましい。半導体 406a および半導体 406c は、SIMSにおいて、 $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以上  $2 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以上  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下の水素濃度となる領域を有する。また、半導体 406 は、SIMSにおいて、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下の窒素濃度となる領域を有する。また、半導体 406 の窒素濃度を低減するために、半導体 406a および半導体 406c の窒素濃度を低減すると好ましい。半導体 406a および半導体 406c は、SIMSにおいて、 $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{15}$  atoms / cm<sup>3</sup> 以上  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下の窒素濃度となる領域を有する。

#### 【0171】

上述の 3 層構造は一例である。例えば、半導体 406a または半導体 406c のない 2 層構造としても構わない。または、半導体 406a の上もしくは下、または半導体 406c 上もしくは下に、半導体 406a、半導体 406 および半導体 406c として例示した半導体のいずれか一を有する 4 層構造としても構わない。または、半導体 406a の上、半導体 406a の下、半導体 406c の上、半導体 406c の下のいずれか二箇所以上に、半導体 406a、半導体 406 および半導体 406c として例示した半導体のいずれか一以上を有する n 層構造 (n は 5 以上の整数) としても構わない。

#### 【0172】

##### <酸化物半導体の構造>

以下では、酸化物半導体の構造について説明する。

#### 【0173】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体などがある。

#### 【0174】

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC-O-S、多結晶酸化物半導体、微結晶酸化物半導体などがある。

#### 【0175】

##### <CAAC-OS>

まずは、CAAC-OSについて説明する。なお、CAAC-OSを、CANC (C-Axis Aligned nanocrystals) を有する酸化物半導体と呼ぶこともできる。

#### 【0176】

CAAC-OSは、c 軸配向した複数の結晶部（ペレットともいう。）を有する酸化物半導体の一つである。

#### 【0177】

透過型電子顕微鏡 (TEM: Transmission Electron Microscope) によって、CAAC-OSの明視野像と回折パターンとの複合解析像（高分

解能TEM像ともいう。)を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像ではペレット同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を明確に確認することができない。そのため、CAAC-OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0178】

以下では、TEMによって観察したCAAC-OSについて説明する。図38(A)に、試料面と略平行な方向から観察したCAAC-OSの断面の高分解能TEM像を示す。高分解能TEM像の観察には、球面収差補正(Spherical Aberration Corrector)機能を用いた。球面収差補正機能を用いた高分解能TEM像を、特にCs補正高分解能TEM像と呼ぶ。Cs補正高分解能TEM像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM-ARM200Fなどによって行うことができる。10

#### 【0179】

図38(A)の領域(1)を拡大したCs補正高分解能TEM像を図38(B)に示す。図38(B)より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、CAAC-OSの膜を形成する面(被形成面ともいう。)または上面の凹凸を反映しており、CAAC-OSの被形成面または上面と平行となる。

#### 【0180】

図38(B)に示すように、CAAC-OSは特徴的な原子配列を有する。図38(C)は、特徴的な原子配列を、補助線で示したものである。図38(B)および図38(C)より、ペレット一つの大きさは1nm以上3nm以下程度であり、ペレットとペレットとの傾きにより生じる隙間の大きさは0.8nm程度であることがわかる。したがって、ペレットを、ナノ結晶(nc:nanocrystal)と呼ぶこともできる。20

#### 【0181】

ここで、Cs補正高分解能TEM像をもとに、基板5120上のCAAC-OSのペレット5100の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる(図38(D)参照。)。図38(C)で観察されたペレットとペレットとの間で傾きが生じている箇所は、図38(D)に示す領域5161に相当する。

#### 【0182】

また、図39(A)に、試料面と略垂直な方向から観察したCAAC-OSの平面のCs補正高分解能TEM像を示す。図39(A)の領域(1)、領域(2)および領域(3)を拡大したCs補正高分解能TEM像を、それぞれ図39(B)、図39(C)および図39(D)に示す。図39(B)、図39(C)および図39(D)より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。30

#### 【0183】

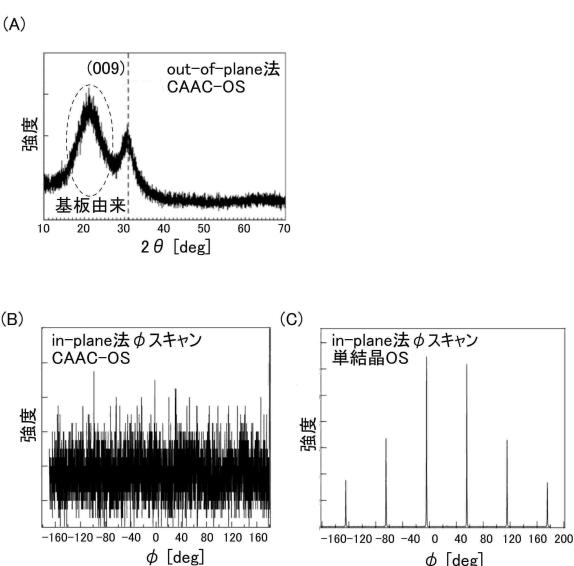

次に、X線回折(XRD:X-Ray Diffraction)によって解析したCAAC-OSについて説明する。例えば、InGaZnO<sub>4</sub>の結晶を有するCAAC-OSに対し、out-of-plane法による構造解析を行うと、図40(A)に示すように回折角(2θ)が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の(009)面に帰属されることから、CAAC-OSの結晶がc軸配向性を有し、c軸が被形成面または上面に略垂直な方向を向いていることが確認できる。40

#### 【0184】

なお、CAAC-OSのout-of-plane法による構造解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAAC-OS中の一部に、c軸配向性を有さない結晶が含まれることを示している。より好ましいCAAC-OSは、out-of-plane法による構造解析では、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さない。

#### 【0185】

一方、CAAC-OSに対し、c軸に略垂直な方向からX線を入射させるin-plane50

e 法による構造解析を行うと、 $2\theta$  が  $56^\circ$  近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub> の結晶の(110)面に帰属される。CAAC-OS の場合は、 $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸( $c$  軸)として試料を回転させながら分析(スキャン)を行っても、図40(B)に示すように明瞭なピークは現れない。これに対し、InGaZnO<sub>4</sub> の単結晶酸化物半導体であれば、 $2\theta$  を  $56^\circ$  近傍に固定してスキャンした場合、図40(C)に示すように(110)面と等価な結晶面に帰属されるピークが6本観察される。したがって、XRD を用いた構造解析から、CAAC-OS は、 $a$  軸および $b$  軸の配向が不規則であることが確認できる。

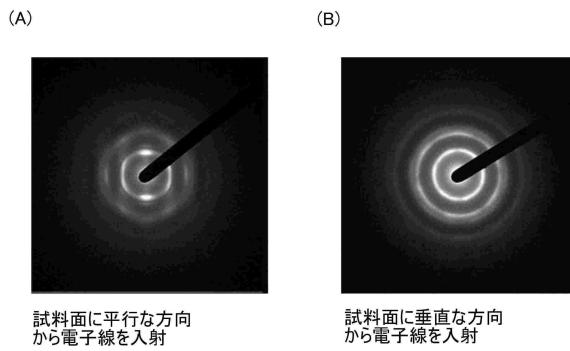

#### 【0186】

次に、電子回折によって解析した CAAC-OS について説明する。例えば、InGaZnO<sub>4</sub> の結晶を有する CAAC-OS に対し、試料面に平行にプローブ径が 300 nm の電子線を入射させると、図41(A)に示すような回折パターン(制限視野透過電子回折パターンともいう。)が現れる場合がある。この回折パターンには、InGaZnO<sub>4</sub> の結晶の(009)面に起因するスポットが含まれる。したがって、電子回折によっても、CAAC-OS に含まれるペレットが $c$  軸配向性を有し、 $c$  軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が 300 nm の電子線を入射させたときの回折パターンを図41(B)に示す。図41(B)より、リング状の回折パターンが確認される。したがって、電子回折によっても、CAAC-OS に含まれるペレットの $a$  軸および $b$  軸は配向性を有さないことがわかる。なお、図41(B)における第1リングは、InGaZnO<sub>4</sub> の結晶の(010)面および(100)面などに起因すると考えられる。また、図41(B)における第2リングは(110)面などに起因すると考えられる。

#### 【0187】

また、CAAC-OS は、欠陥準位密度の低い酸化物半導体である。酸化物半導体の欠陥としては、例えば、不純物に起因する欠陥や、酸素欠損などがある。したがって、CAAC-OS は、不純物濃度の低い酸化物半導体ということもできる。また、CAAC-OS は、酸素欠損の少ない酸化物半導体ということもできる。

#### 【0188】

酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

#### 【0189】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

#### 【0190】

また、欠陥準位密度の低い(酸素欠損が少ない)酸化物半導体は、キャリア密度を低くすることができる。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。CAAC-OS は、不純物濃度が低く、欠陥準位密度が低い。即ち、高純度真性または実質的に高純度真性な酸化物半導体となりやすい。したがって、CAAC-OS を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリオング)になることが少ない。また、高純度真性または実質的に高純度真性な酸化物半導体は、キャリアトラップが少ない。酸化物半導体のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体を用いたトランジスタは、電気特性が不安定となる場合がある。一方、CAAC-OS を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。

10

20

30

40

50

**【0191】**

また、 C A A C - O S は欠陥準位密度が低いため、光の照射などによって生成されたキャリアが、欠陥準位に捕獲されることが少ない。したがって、 C A A C - O S を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

**【0192】**

< 微結晶酸化物半導体 >

次に、微結晶酸化物半導体について説明する。

**【0193】**

微結晶酸化物半導体は、高分解能 T E M 像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。微結晶酸化物半導体に含まれる結晶部は、1 nm 以上 1 0 0 nm 以下、または 1 nm 以上 1 0 nm 以下の大きさであることが多い。特に、1 nm 以上 1 0 nm 以下、または 1 nm 以上 3 nm 以下の微結晶であるナノ結晶を有する酸化物半導体を、n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) と呼ぶ。n c - O S は、例えば、高分解能 T E M 像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、C A A C - O S におけるペレットと起源を同じくする可能性がある。そのため、以下では n c - O S の結晶部をペレットと呼ぶ場合がある。

10

**【0194】**

n c - O S は、微小な領域（例えば、1 nm 以上 1 0 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - O S に対し、ペレットよりも大きい径の X 線を用いる X R D 装置を用いて構造解析を行うと、o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、n c - O S に対し、ペレットよりも大きいプローブ径（例えば 5 0 nm 以上）の電子線を用いる電子回折（制限視野電子回折ともいう。）を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S に対し、ペレットの大きさと近いかペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O S に対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

20

**【0195】**

このように、ペレット（ナノ結晶）間では結晶方位が規則性を有さないことから、n c - O S を、R ANC ( R a n d o m A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体、またはN ANC ( N o n - A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体と呼ぶこともできる。

30

**【0196】**

n c - O S は、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - O S は、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、n c - O S は、C A A C - O S と比べて欠陥準位密度が高くなる。

40

**【0197】**

< 非晶質酸化物半導体 >

次に、非晶質酸化物半導体について説明する。

**【0198】**

非晶質酸化物半導体は、膜中における原子配列が不規則であり、結晶部を有さない酸化物半導体である。石英のような無定形状態を有する酸化物半導体が一例である。

**【0199】**

非晶質酸化物半導体は、高分解能 T E M 像において結晶部を確認することができない。

**【0200】**

50

非晶質酸化物半導体に対し、XRD装置を用いた構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、非晶質酸化物半導体に対し、電子回折を行うと、ハローパターンが観測される。また、非晶質酸化物半導体に対し、ナノビーム電子回折を行うと、スポットが観測されず、ハローパターンのみが観測される。

#### 【0201】

非晶質構造については、様々な見解が示されている。例えば、原子配列に全く秩序性を有さない構造を完全な非晶質構造 (completely amorphous structure) と呼ぶ場合がある。また、最近接原子間距離または第2近接原子間距離まで秩序性を有し、かつ長距離秩序性を有さない構造を非晶質構造と呼ぶ場合もある。したがって、最も厳格な定義によれば、僅かでも原子配列に秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。また、少なくとも、長距離秩序性を有する酸化物半導体を非晶質酸化物半導体と呼ぶことはできない。よって、結晶部を有することから、例えば、CAAC-OSおよびnc-OSを、非晶質酸化物半導体または完全な非晶質酸化物半導体と呼ぶことはできない。

10

#### 【0202】

##### <非晶質ライク酸化物半導体>

なお、酸化物半導体は、nc-OSと非晶質酸化物半導体との間の構造を有する場合がある。そのような構造を有する酸化物半導体を、特に非晶質ライク酸化物半導体 (a-like OS : amorphous-like Oxide Semiconductor) と呼ぶ。

20

#### 【0203】

a-like OSは、高分解能TEM像において鬆（ボイドともいう。）が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

#### 【0204】

鬆を有するため、a-like OSは、不安定な構造である。以下では、a-like OSが、CAAC-OSおよびnc-OSと比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。

30

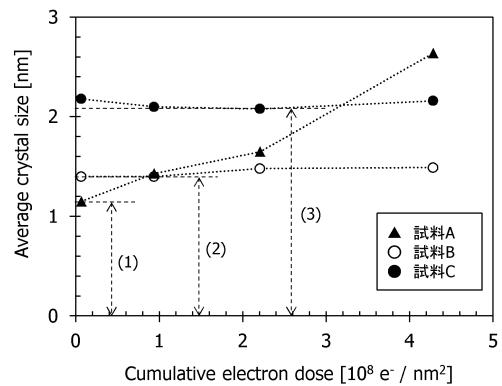

#### 【0205】

電子照射を行う試料として、a-like OS（試料Aと表記する。）、nc-OS（試料Bと表記する。）およびCAAC-OS（試料Cと表記する。）を準備する。いずれの試料もIn-Ga-Zn酸化物である。

#### 【0206】

まず、各試料の高分解能断面TEM像を取得する。高分解能断面TEM像により、各試料は、いずれも結晶部を有することがわかる。

#### 【0207】

なお、どの部分を一つの結晶部と見なすかの判定は、以下のように行えばよい。例えば、 $In_2Ga_3ZnO_4$ の結晶の単位格子は、In-O層を3層有し、またGa-Zn-O層を6層有する、計9層がc軸方向に層状に重なった構造を有することが知られている。これらの近接する層同士の間隔は、(009)面の格子面間隔（d値ともいう。）と同程度であり、結晶構造解析からその値は0.29nmと求められている。したがって、格子縞の間隔が0.28nm以上0.30nm以下の箇所を、 $In_2Ga_3ZnO_4$ の結晶部と見なすことができる。なお、格子縞は、 $In_2Ga_3ZnO_4$ の結晶のa-b面に対応する。

40

#### 【0208】

図42は、各試料の結晶部（22箇所から45箇所）の平均の大きさを調査した例である。ただし、上述した格子縞の長さを結晶部の大きさとしている。図42より、a-like OSは、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図42中に（1）で示すように、TEMによる観察初期においては1.2nm程度の大きさだった結晶部（初期核ともいう。）が、累積照射量が $4.2 \times 10^8 e^-/nm$

50

<sup>2</sup>においては2.6 nm程度の大きさまで成長していることがわかる。一方、n c - O SおよびC A A C - O Sは、電子照射開始時から電子の累積照射量が $4.2 \times 10^8 e^- / nm^2$ までの範囲で、結晶部の大きさに変化が見られないことがわかる。具体的には、図42中の(2)および(3)で示すように、電子の累積照射量によらず、n c - O SおよびC A A C - O Sの結晶部の大きさは、それぞれ1.4 nm程度および2.1 nm程度であることがわかる。

#### 【0209】

このように、a - l i k e O Sは、電子照射によって結晶部の成長が見られる場合がある。一方、n c - O SおよびC A A C - O Sは、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a - l i k e O Sは、n c - O SおよびC A A C - O Sと比べて、不安定な構造であることがわかる。

10

#### 【0210】

また、鬆を有するため、a - l i k e O Sは、n c - O SおよびC A A C - O Sと比べて密度の低い構造である。具体的には、a - l i k e O Sの密度は、同じ組成の単結晶の密度の78.6%以上92.3%未満となる。また、n c - O Sの密度およびC A A C - O Sの密度は、同じ組成の単結晶の密度の92.3%以上100%未満となる。単結晶の密度の78%未満となる酸化物半導体は、成膜すること自体が困難である。

#### 【0211】

例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において、菱面体晶構造を有する単結晶InGaZnO<sub>4</sub>の密度は6.357 g / cm<sup>3</sup>となる。よって、例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において、a - l i k e O Sの密度は5.0 g / cm<sup>3</sup>以上5.9 g / cm<sup>3</sup>未満となる。また、例えば、In : Ga : Zn = 1 : 1 : 1 [原子数比]を満たす酸化物半導体において、n c - O Sの密度およびC A A C - O Sの密度は5.9 g / cm<sup>3</sup>以上6.3 g / cm<sup>3</sup>未満となる。

20

#### 【0212】

なお、同じ組成の単結晶が存在しない場合がある。その場合、所望の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

30

#### 【0213】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えば、非晶質酸化物半導体、a - l i k e O S、微結晶酸化物半導体、C A A C - O Sのうち、二種以上を有する積層膜であってもよい。

#### 【0214】

##### <成膜モデル>

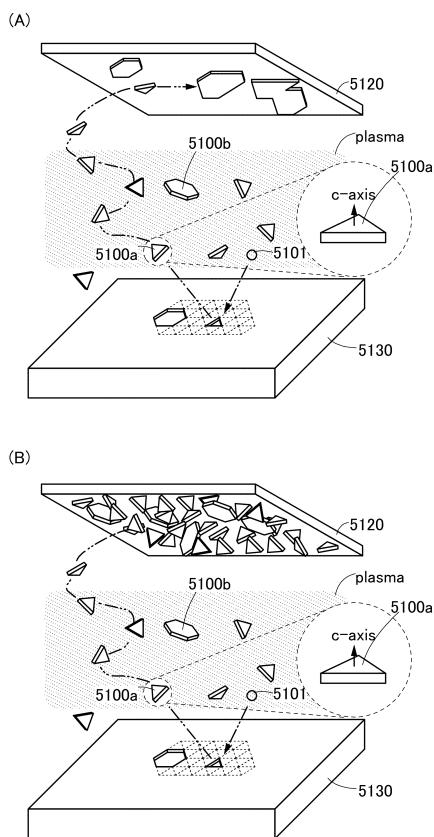

以下では、C A A C - O Sおよびn c - O Sの成膜モデルの一例について説明する。

#### 【0215】

図43(A)は、スパッタリング法によりC A A C - O Sが成膜される様子を示した成膜室内の模式図である。

40

#### 【0216】

ターゲット5130は、バッキングプレートに接着されている。バッキングプレートを介してターゲット5130と向かい合う位置には、複数のマグネットが配置される。該複数のマグネットによって磁場が生じている。マグネットの磁場を利用して成膜速度を高めるスパッタリング法は、マグнетロンスパッタリング法と呼ばれる。

#### 【0217】

基板5120は、ターゲット5130と向かい合うように配置しており、その距離d(ターゲット - 基板間距離(T-S間距離)ともいう。)は0.01 m以上1 m以下、好みくは0.02 m以上0.5 m以下とする。成膜室内は、ほとんどが成膜ガス(例えば、酸

50

素、アルゴン、または酸素を5体積%以上の割合で含む混合ガス)で満たされ、0.01 Pa以上100Pa以下、好ましくは0.1Pa以上10Pa以下に制御される。ここで、ターゲット5130に一定以上の電圧を印加することで、放電が始まり、プラズマが確認される。なお、ターゲット5130の近傍には磁場によって、高密度プラズマ領域が形成される。高密度プラズマ領域では、成膜ガスがイオン化することで、イオン5101が生じる。イオン5101は、例えば、酸素の陽イオン(O<sup>+</sup>)やアルゴンの陽イオン(Ar<sup>+</sup>)などである。

#### 【0218】

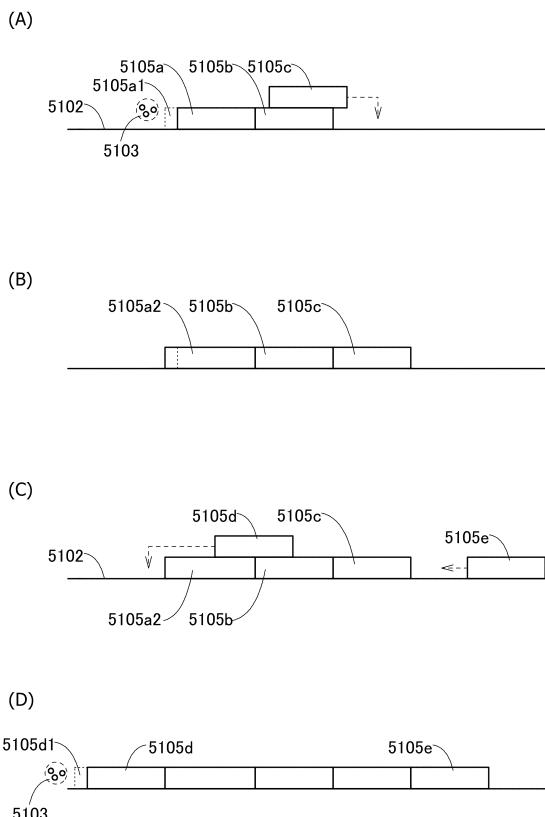

ここで、ターゲット5130は、複数の結晶粒を有する多結晶構造を有し、いずれかの結晶粒には劈開面が含まれる。図44(A)に、一例として、ターゲット5130に含まれるInGaZnO<sub>4</sub>の結晶の構造を示す。なお、図44(A)は、b軸に平行な方向からInGaZnO<sub>4</sub>の結晶を観察した場合の構造である。図44(A)より、近接する二つのGa-Zn-O層において、それぞれの層における酸素原子同士が近距離に配置されていることがわかる。そして、酸素原子が負の電荷を有することにより、近接する二つのGa-Zn-O層の間には斥力が生じる。その結果、InGaZnO<sub>4</sub>の結晶は、近接する二つのGa-Zn-O層の間に劈開面を有する。

10

#### 【0219】

高密度プラズマ領域で生じたイオン5101は、電界によってターゲット5130側に加速され、やがてターゲット5130と衝突する。このとき、劈開面から平板状またはペレット状のスパッタ粒子であるペレット5100aおよびペレット5100bが剥離し、叩き出される。なお、ペレット5100aおよびペレット5100bは、イオン5101の衝突の衝撃によって、構造に歪みが生じる場合がある。

20

#### 【0220】

ペレット5100aは、三角形、例えば正三角形の平面を有する平板状またはペレット状のスパッタ粒子である。また、ペレット5100bは、六角形、例えば正六角形の平面を有する平板状またはペレット状のスパッタ粒子である。なお、ペレット5100aおよびペレット5100bなどの平板状またはペレット状のスパッタ粒子を総称してペレット5100と呼ぶ。ペレット5100の平面の形状は、三角形、六角形に限定されない。例えば、三角形が複数個合わさった形状となる場合がある。例えば、三角形(例えば、正三角形)が2個合わさった四角形(例えば、ひし形)となる場合もある。

30

#### 【0221】

ペレット5100は、成膜ガスの種類などに応じて厚さが決定する。理由は後述するが、ペレット5100の厚さは、均一にすることが好ましい。また、スパッタ粒子は厚みのないペレット状である方が、厚みのあるサイコロ状であるよりも好ましい。例えば、ペレット5100は、厚さを0.4nm以上1nm以下、好ましくは0.6nm以上0.8nm以下とする。また、例えば、ペレット5100は、幅を1nm以上3nm以下、好ましくは1.2nm以上2.5nm以下とする。ペレット5100は、上述の図42中の(1)で説明した初期核に相当する。例えば、In-Ga-Zn酸化物を有するターゲット5130にイオン5101を衝突させると、図44(B)に示すように、Ga-Zn-O層、In-O層およびGa-Zn-O層の3層を有するペレット5100が剥離する。図44(C)に、剥離したペレット5100をc軸に平行な方向から観察した構造を示す。ペレット5100は、二つのGa-Zn-O層(パン)と、In-O層(具)と、を有するナノサイズのサンドイッチ構造と呼ぶこともできる。

40

#### 【0222】

ペレット5100は、プラズマを通過する際に、側面が負または正に帯電する場合がある。ペレット5100は、例えば、側面に位置する酸素原子が負に帯電する可能性がある。側面が同じ極性の電荷を有することにより、電荷同士の反発が起こり、平板状またはペレット状の形状を維持することが可能となる。なお、CAC-OSが、In-Ga-Zn酸化物である場合、インジウム原子と結合した酸素原子が負に帯電する可能性がある。または、インジウム原子、ガリウム原子または亜鉛原子と結合した酸素原子が負に帯電する

50

可能性がある。また、ペレット 5100 は、プラズマを通過する際に、プラズマ中のインジウム原子、ガリウム原子、亜鉛原子および酸素原子などと結合することで成長する場合がある。上述の図 42 中の(2)と(1)の大きさの違いが、プラズマ中での成長分に相当する。ここで、基板 5120 が室温程度である場合、基板 5120 上におけるペレット 5100 の成長が起こりにくいため nc - OS となる（図 43 (B) 参照。）。室温程度で成膜できることから、基板 5120 が大面積である場合でも nc - OS の成膜が可能である。なお、ペレット 5100 をプラズマ中で成長させるためには、スパッタリング法における成膜電力を高くすることが有効である。成膜電力を高くすることで、ペレット 5100 の構造を安定にすることができる。

## 【0223】

10

図 43 (A) および図 43 (B) に示すように、例えば、ペレット 5100 は、プラズマ中を飛翔し、ひらひらと基板 5120 上まで舞い上がっていく。ペレット 5100 は電荷を帯びているため、ほかのペレット 5100 が既に堆積している領域が近づくと、斥力が生じる。ここで、基板 5120 の上面では、基板 5120 の上面に平行な向きの磁場（水平磁場ともいう。）が生じている。また、基板 5120 およびターゲット 5130 間には、電位差が与えられるため、基板 5120 からターゲット 5130 に向かう方向に電流が流れる。したがって、ペレット 5100 は、基板 5120 の上面において、磁場および電流の作用によって、力（ローレンツ力）を受ける。このことは、フレミングの左手の法則によって理解できる。

## 【0224】

20

ペレット 5100 は、原子一つと比べると質量が大きい。そのため、基板 5120 の上面を移動するためには何らかの力を外部から印加することが重要となる。その力の一つが磁場および電流の作用で生じる力である可能性がある。なお、ペレット 5100 に、基板 5120 の上面を移動するために十分な力を与えるには、基板 5120 の上面において、基板 5120 の上面に平行な向きの磁場が 10 G 以上、好ましくは 20 G 以上、さらに好ましくは 30 G 以上、より好ましくは 50 G 以上となる領域を設けるとよい。または、基板 5120 の上面において、基板 5120 の上面に平行な向きの磁場が、基板 5120 の上面に垂直な向きの磁場の 1.5 倍以上、好ましくは 2 倍以上、さらに好ましくは 3 倍以上、より好ましくは 5 倍以上となる領域を設けるとよい。

## 【0225】

30

このとき、マグネットと基板 5120 とが相対的に移動すること、または回転することによって、基板 5120 の上面における水平磁場の向きは変化し続ける。したがって、基板 5120 の上面において、ペレット 5100 は、様々な方向から力を受け、様々な方向へ移動することができる。

## 【0226】

また、図 43 (A) に示すように基板 5120 が加熱されている場合、ペレット 5100 と基板 5120 との間で摩擦などによる抵抗が小さい状態となっている。その結果、ペレット 5100 は、基板 5120 の上面を滑空するように移動する。ペレット 5100 の移動は、平板面を基板 5120 に向けた状態で起こる。その後、既に堆積しているほかのペレット 5100 の側面まで到達すると、側面同士が結合する。このとき、ペレット 5100 の側面にある酸素原子が脱離する。脱離した酸素原子によって、CACOS 中の酸素欠損が埋まる場合があるため、欠陥準位密度の低い CACOS となる。なお、基板 5120 の上面の温度は、例えば、100 以上 500 未満、150 以上 450 未満、または 170 以上 400 未満とすればよい。したがって、基板 5120 が大面積である場合でも CACOS の成膜は可能である。

40

## 【0227】

また、ペレット 5100 は、基板 5120 上で加熱されることにより、原子が再配列し、イオン 5101 の衝突で生じた構造の歪みが緩和される。歪みの緩和されたペレット 5100 は、ほとんど単結晶となる。ペレット 5100 がほとんど単結晶となることにより、ペレット 5100 同士が結合した後に加熱されたとしても、ペレット 5100 自体の伸縮

50

はほとんど起こり得ない。したがって、ペレット 5100 間の隙間が広がることで結晶粒界などの欠陥を形成し、クレバス化することがない。

#### 【0228】

また、CAC-OS は、単結晶酸化物半導体が一枚板のようになっているのではなく、ペレット 5100（ナノ結晶）の集合体がレンガまたはブロックが積み重なったような配列をしている。また、ペレット 5100 同士の間には結晶粒界を有さない。そのため、成膜時の加熱、成膜後の加熱または曲げなどで、CAC-OS に縮みなどの変形が生じた場合でも、局部応力を緩和する、または歪みを逃がすことが可能である。したがって、可とう性を有する半導体装置に用いることに適した構造である。なお、nC-OS は、ペレット 5100（ナノ結晶）が無秩序に積み重なったような配列となる。

10

#### 【0229】

ターゲット 5130 をイオン 5101 でスパッタした際に、ペレット 5100 だけではなく、酸化亜鉛などが剥離する場合がある。酸化亜鉛はペレット 5100 よりも軽量であるため、先に基板 5120 の上面に到達する。そして、0.1 nm 以上 10 nm 以下、0.2 nm 以上 5 nm 以下、または 0.5 nm 以上 2 nm 以下の酸化亜鉛層 5102 を形成する。図 45 に断面模式図を示す。

#### 【0230】

図 45 (A) に示すように、酸化亜鉛層 5102 上にはペレット 5105a と、ペレット 5105b と、が堆積する。ここで、ペレット 5105a とペレット 5105b とは、互いに側面が接するように配置している。また、ペレット 5105c は、ペレット 5105b 上に堆積した後、ペレット 5105b 上を滑るように移動する。また、ペレット 5105a の別の側面において、酸化亜鉛とともにターゲットから剥離した複数の粒子 5103 が、基板 5120 からの加熱により結晶化し、領域 5105a1 を形成する。なお、複数の粒子 5103 は、酸素、亜鉛、インジウムおよびガリウムなどを含む可能性がある。

20

#### 【0231】

そして、図 45 (B) に示すように、領域 5105a1 は、ペレット 5105a と一体化し、ペレット 5105a2 となる。また、ペレット 5105c は、その側面がペレット 5105b の別の側面と接するように配置する。

#### 【0232】

次に、図 45 (C) に示すように、さらにペレット 5105d がペレット 5105a2 上およびペレット 5105b 上に堆積した後、ペレット 5105a2 上およびペレット 5105b 上を滑るように移動する。また、ペレット 5105c の別の側面に向けて、さらにペレット 5105e が酸化亜鉛層 5102 上を滑るように移動する。

30

#### 【0233】

そして、図 45 (D) に示すように、ペレット 5105d は、その側面がペレット 5105a2 の側面と接するように配置する。また、ペレット 5105e は、その側面がペレット 5105c の別の側面と接するように配置する。また、ペレット 5105d の別の側面において、酸化亜鉛とともにターゲット 5130 から剥離した複数の粒子 5103 が基板 5120 からの加熱により結晶化し、領域 5105d1 を形成する。

#### 【0234】

以上のように、堆積したペレット同士が接するように配置し、ペレットの側面において成長が起こることで、基板 5120 上に CAC-OS が形成される。したがって、CAC-OS は、nC-OS よりも一つ一つのペレットが大きくなる。上述の図 42 中の (3) と (2) の大きさの違いが、堆積後の成長分に相当する。

40

#### 【0235】

また、ペレット同士の隙間が極めて小さくなることで、一つの大きなペレットが形成される場合がある。一つの大きなペレットは、単結晶構造を有する。例えば、ペレットの大きさが、上面から見て 10 nm 以上 200 nm 以下、15 nm 以上 100 nm 以下、または 20 nm 以上 50 nm 以下となる場合がある。このとき、微細なトランジスタに用いる酸化物半導体において、チャネル形成領域が一つの大きなペレットに収まる場合がある。即

50

ち、単結晶構造を有する領域をチャネル形成領域として用いることができる。また、ペレットが大きくなることで、単結晶構造を有する領域をトランジスタのチャネル形成領域、ソース領域およびドレイン領域として用いることができる場合がある。

#### 【0236】

このように、トランジスタのチャネル形成領域などが、単結晶構造を有する領域に形成されることによって、トランジスタの周波数特性を高くすることができる場合がある。

#### 【0237】

以上のようなモデルにより、ペレット5100が基板5120上に堆積していくと考えられる。被形成面が結晶構造を有さない場合においても、C AAC - OSの成膜が可能であることから、エピタキシャル成長とは異なる成長機構であることがわかる。また、C AAC - OSは、レーザ結晶化が不要であり、大面積のガラス基板などであっても均一な成膜が可能である。例えば、基板5120の上面（被形成面）の構造が非晶質構造（例えば非晶質酸化シリコン）であっても、C AAC - OSを成膜することは可能である。

10

#### 【0238】

また、C AAC - OSは、被形成面である基板5120の上面に凹凸がある場合でも、その形状に沿ってペレット5100が配列することがわかる。例えば、基板5120の上面が原子レベルで平坦な場合、ペレット5100はa - b面と平行な平面である平板面を下に向けて並置する。ペレット5100の厚さが均一である場合、厚さが均一で平坦、かつ高い結晶性を有する層が形成される。そして、当該層がn段（nは自然数。）積み重なることで、C AAC - OSを得ることができる。

20

#### 【0239】

一方、基板5120の上面が凹凸を有する場合でも、C AAC - OSは、ペレット5100が凹凸に沿って並置した層がn段（nは自然数。）積み重なった構造となる。基板5120が凹凸を有するため、C AAC - OSは、ペレット5100間に隙間が生じやすい場合がある。ただし、この場合でも、ペレット5100間で分子間力が働き、凹凸があってもペレット間の隙間はなるべく小さくなるように配列する。したがって、凹凸があっても高い結晶性を有するC AAC - OSとすることができます。

30

#### 【0240】

このようなモデルによってC AAC - OSが成膜されるため、スパッタ粒子が厚みのないペレット状である方が好ましい。なお、スパッタ粒子が厚みのあるサイコロ状である場合、基板5120上に向ける面が一定とならず、厚さや結晶の配向を均一にできない場合がある。

#### 【0241】

以上に示した成膜モデルにより、非晶質構造を有する被形成面上であっても、高い結晶性を有するC AAC - OSを得ることができます。

40

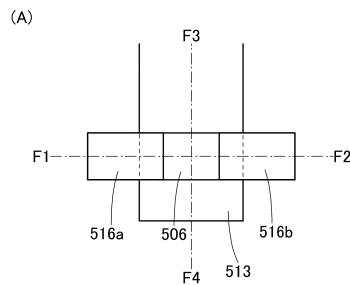

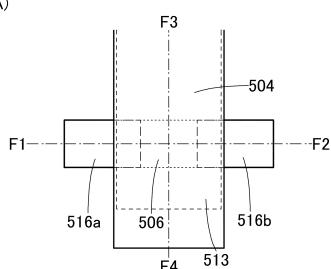

#### 【0242】

##### <トランジスタ2>

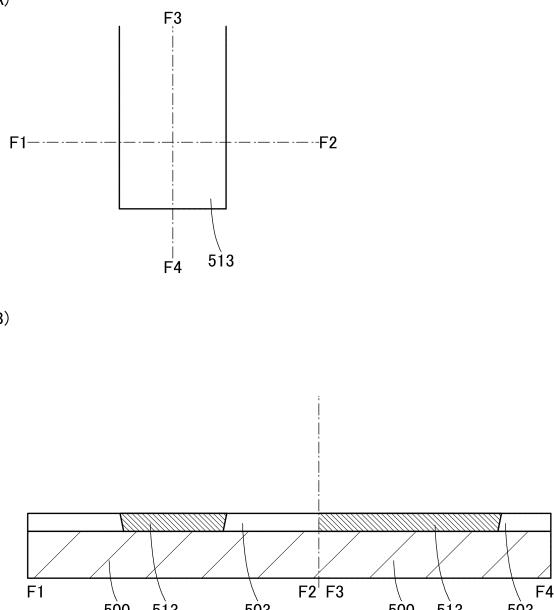

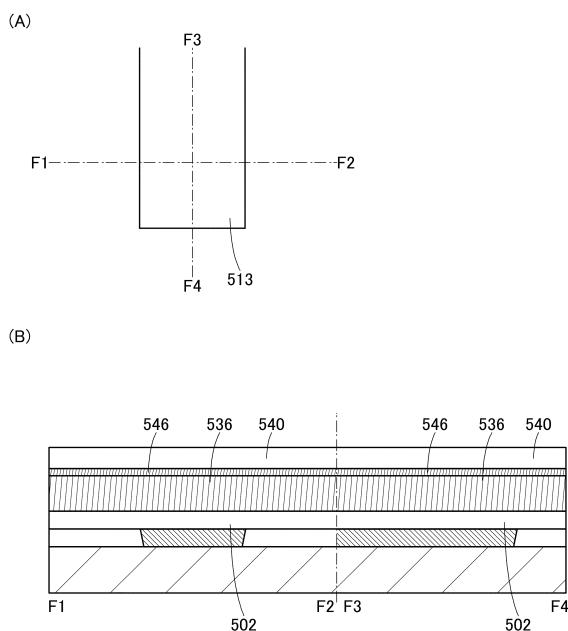

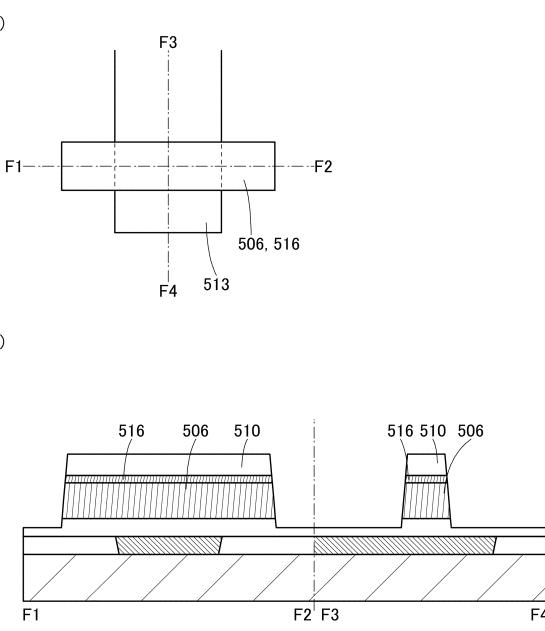

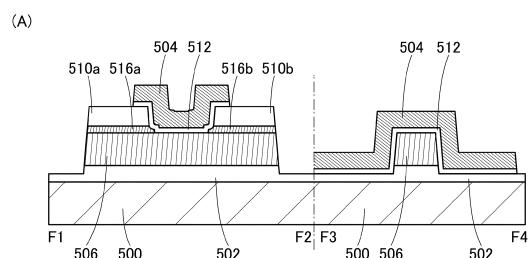

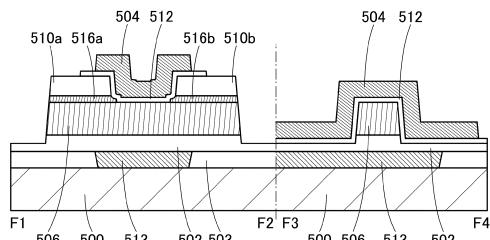

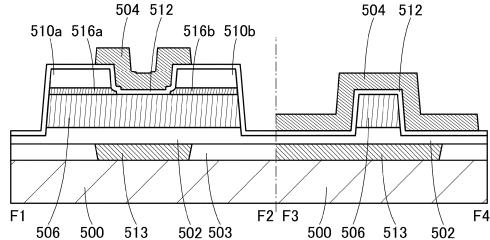

次に、一部形状の異なるトランジスタの作製方法について説明する。図14(A)、図15(A)、図16(A)、図17(A)および図18(A)は、トランジスタの作製方法を説明する上面図である。各上面図には、一点鎖線F1 - F2および一点鎖線F3 - F4が記され、それに対応した断面図を図14(B)、図15(B)、図16(B)、図17(B)および図18(B)に示す。

40

#### 【0243】

まずは、基板500を準備する。基板500は、基板400についての記載を参照する。

#### 【0244】

次に、絶縁体を成膜する。絶縁体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

#### 【0245】

次に、絶縁体上にレジストなどを形成し、該レジストを用いて加工し、絶縁体503を形成する。

50

**【0246】**

絶縁体を加工して絶縁体503を形成する際、図1乃至図7のいずれかに記載の加工方法を用いてもよい。

**【0247】**

次に、導電体を成膜する。導電体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

**【0248】**

次に、導電体の上面から下面に向けて、基板500の下面と平行な形状となるようにエッチングを行うことで、絶縁体503の溝部に導電体513を形成する（埋め込む）ことができる（図14（A）および図14（B）参照。）。このような方法で導電体513を形成することで、導電体513の上面の高さと、絶縁体503の上面の高さと、を同程度にすることができる。したがって、後の工程における形状不良を抑制することができる。

10

**【0249】**

絶縁体503は、絶縁体402についての記載を参照する。導電体513は、導電体413について記載を参照する。

**【0250】**

次に、絶縁体502を成膜する。絶縁体502の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。絶縁体502は、絶縁体402についての記載を参照する。

20

**【0251】**

次に、半導体536を成膜する。半導体536の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。半導体536は、半導体406についての記載を参照する。

**【0252】**

次に、加熱処理を行うことが好ましい。

**【0253】**

次に、導電体546を成膜する。導電体546の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。導電体546は、導電体416についての記載を参照する。

30

**【0254】**

次に、絶縁体540を成膜する（図15（A）および図15（B）参照。）。絶縁体540の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。絶縁体540は、絶縁体510についての記載を参照する。

40

**【0255】**

次に、絶縁体540上にレジストなどを形成し、該レジストを用いて加工し、絶縁体510、導電体516および半導体506を形成する（図16（A）および図16（B）参照。）。このとき、導電体516またはノおよび半導体506は、レジストを除去してから絶縁体510を用いて加工してもよい。このとき、半導体506と重ならない絶縁体502の一部をエッチングしても構わない。こうすることで、絶縁体502に凸部が形成される。

**【0256】**

この際、図1乃至図7のいずれかに記載の加工方法を用いてもよい。例えば、図1乃至図7において、層116を導電体516に、層110を絶縁体510に置き替える。

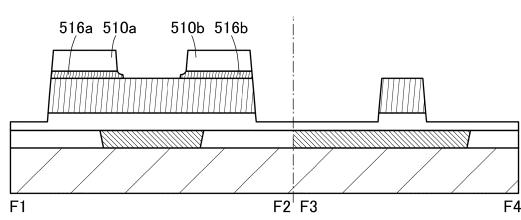

**【0257】**

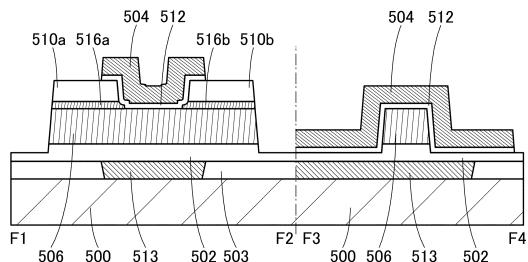

次に、絶縁体510上にレジストなどを形成し、該レジストを用いて加工し、絶縁体510aおよび絶縁体510b、ならびに導電体516aおよび導電体516bを形成する（図17（A）および図17（B）参照。）。ここでは、図4に示した加工方法と同様の方法により、絶縁体510および導電体516を加工した場合を図示している。ただし図1、図51、図52および図53などに示した形状に、導電体516aおよび導電体516b、ならびに絶縁体510aおよび絶縁体510bを加工しても構わない。

50

**【 0 2 5 8 】**

次に、絶縁体を成膜する。絶縁体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

**【 0 2 5 9 】**

次に、導電体を成膜する。導電体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

**【 0 2 6 0 】**

次に、導電体上にレジストなどを形成し、該レジストを用いて加工し、導電体504を形成する。また、該レジストまたは導電体504を用いて絶縁体を加工し、絶縁体512を形成する（図18（A）および図18（B）参照。）。なお、ここでは絶縁体512と導電体504とが上面から見たときに同様の形状となるよう加工しているが、この形状に限定されるものではない。例えば、絶縁体512と導電体504とを別のレジストを用いて加工してもよい。例えば、絶縁体512を形成してから、導電体504となる導電体を成膜してもよいし、導電体504を形成した後で絶縁体512となる絶縁体上に別途レジストなどを形成してもよい。

10

**【 0 2 6 1 】**

この際、図1乃至図7のいずれかに記載の加工方法を用いてもよい。例えば、図1乃至図7において、層116を絶縁体512となる絶縁体に、層110を導電体504となる導電体に置き替えればよい。

20

**【 0 2 6 2 】**

絶縁体512は、絶縁体412についての記載を参照する。導電体504は、導電体404について記載を参照する。

**【 0 2 6 3 】**

次に、絶縁体を成膜してもよい。絶縁体の成膜は、スパッタリング法、CVD法、MBE法またはPLD法、ALD法などを用いて行うことができる。

30

**【 0 2 6 4 】**

絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。絶縁体は、好ましくは酸化アルミニウム、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを含む絶縁体を、単層で、または積層で用いればよい。

**【 0 2 6 5 】**

絶縁体は、バリア層としての機能を有することが好ましい。絶縁体は、例えば、酸素または/および水素をブロックする機能を有する。または、絶縁体は、例えば、絶縁体502または絶縁体512よりも、酸素または/および水素をブロックする能力が高いことが好ましい。

**【 0 2 6 6 】**

以上の工程により、本発明の一態様に係るトランジスタを作製することができる。

40

**【 0 2 6 7 】**

図18（B）に示したトランジスタは、導電体516aと導電体504との間に絶縁体510aを有し、導電体516bと導電体504との間に絶縁体510bを有する。即ち、導電体516aおよび導電体516bなどに起因する寄生容量が小さい。そのため、図18（B）に示したトランジスタを用いた半導体装置は、高い周波数特性を有する。また、導電体516aの絶縁体510aから迫り出す長さを、絶縁体512の厚さの70%以上130%以下、好ましくは80%以上120%以下、さらに好ましくは90%以上110%以下とすることで、寄生容量を小さく、かつオン抵抗を小さくすることができる。導電体516bについても同様である。

**【 0 2 6 8 】**

50

図18(B)に示すように、トランジスタはs-channel構造を有する。また、導電体504からの電界が、半導体506の側面において導電体516aおよび導電体516bなどによって阻害されにくい構造である。

#### 【0269】

なお、導電体513を形成しなくてもよい(図19(A)参照。)。また、絶縁体512が導電体504から迫り出した形状としてもよい(図19(B)参照。)。また、絶縁体512となる絶縁体を加工しなくてもよい(図19(C)参照。)。

#### 【0270】

##### <回路>

以下では、本発明の一態様に係るトランジスタなどを利用した半導体装置の回路の一例について説明する。

10

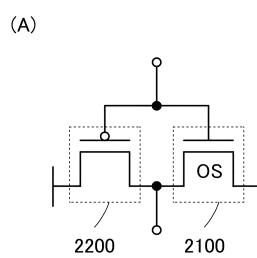

#### 【0271】

##### <CMOSインバータ>

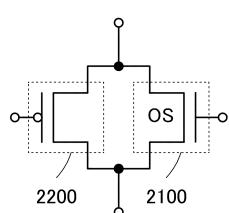

図20(A)に示す回路図は、pチャネル型のトランジスタ2200とnチャネル型のトランジスタ2100を直列に接続し、かつそれぞれのゲートを接続した、いわゆるCMOSインバータの構成を示している。

#### 【0272】

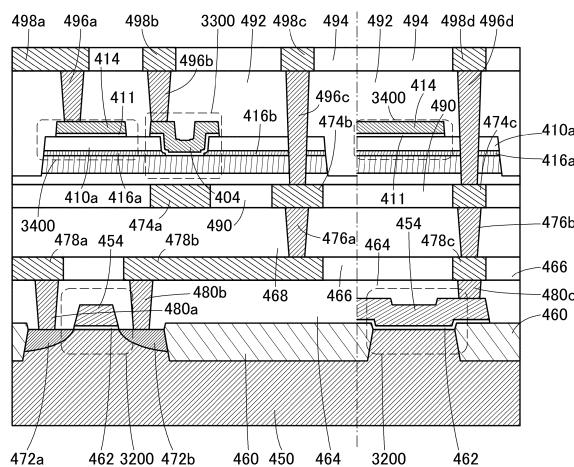

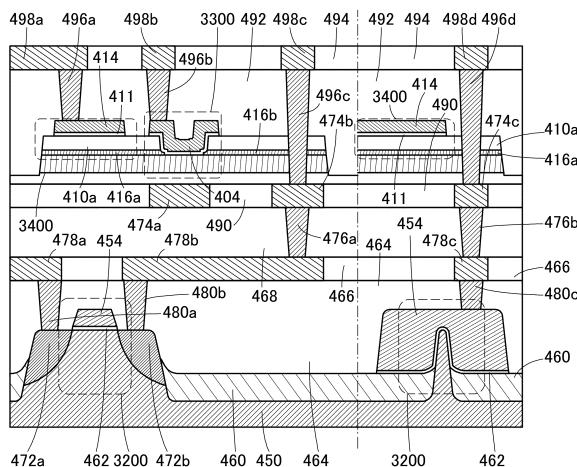

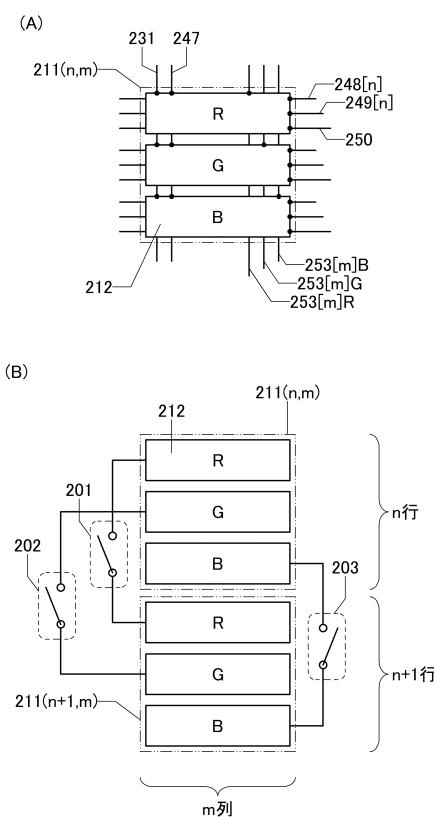

##### <半導体装置の構造1>

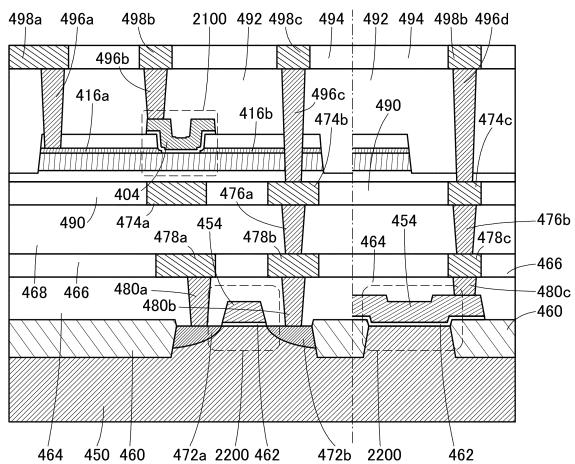

図21は、図20(A)に対応する半導体装置の断面図である。図21に示す半導体装置は、トランジスタ2200と、トランジスタ2100と、を有する。また、トランジスタ2100は、トランジスタ2200の上方に配置する。なお、トランジスタ2100として、図18に示したトランジスタを用いた例を示しているが、本発明の一態様に係る半導体装置は、これに限定されるものではない。例えば、図11、図12、図19、図51、図52または図53に示したトランジスタなどを、トランジスタ2100として用いても構わない。よって、トランジスタ2100については、適宜上述したトランジスタについての記載を参照する。

20

#### 【0273】

図21に示すトランジスタ2200は、半導体基板450を用いたトランジスタである。トランジスタ2200は、半導体基板450中の領域472aと、半導体基板450中の領域472bと、絶縁体462と、導電体454と、を有する。

30

#### 【0274】

トランジスタ2200において、領域472aおよび領域472bは、ソース領域およびドレイン領域としての機能を有する。また、絶縁体462は、ゲート絶縁体としての機能を有する。また、導電体454は、ゲート電極としての機能を有する。したがって、導電体454に印加する電位によって、チャネル形成領域の抵抗を制御することができる。即ち、導電体454に印加する電位によって、領域472aと領域472bとの間の導通・非導通を制御することができる。

#### 【0275】

半導体基板450としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコングルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムなどの化合物半導体基板などを用いればよい。好ましくは、半導体基板450として単結晶シリコン基板を用いる。

40

#### 【0276】

半導体基板450は、n型の導電型を付与する不純物を有する半導体基板を用いる。ただし、半導体基板450として、p型の導電型を付与する不純物を有する半導体基板を用いても構わない。その場合、トランジスタ2200となる領域には、n型の導電型を付与する不純物を有するウェルを配置すればよい。または、半導体基板450がi型であっても構わない。

#### 【0277】

半導体基板450の上面は、(110)面を有することが好ましい。こうすることで、ト

50

ランジスタ 2200 のオン特性を向上させることができる。

【0278】

領域 472a および領域 472b は、p 型の導電型を付与する不純物を有する領域である。このようにして、トランジスタ 2200 は p チャネル型トランジスタを構成する。

【0279】

なお、トランジスタ 2200 は、領域 460 などによって隣接するトランジスタと分離される。領域 460 は、絶縁性を有する領域である。

【0280】

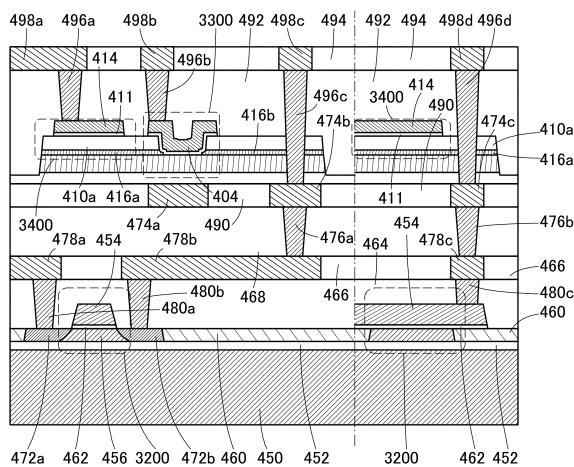

図 21 に示す半導体装置は、絶縁体 464 と、絶縁体 466 と、絶縁体 468 と、導電体 480a と、導電体 480b と、導電体 480c と、導電体 478a と、導電体 478b と、導電体 478c と、導電体 476a と、導電体 476b と、導電体 474a と、導電体 474b と、導電体 474c と、導電体 496a と、導電体 496b と、導電体 496c と、導電体 496d と、導電体 498a と、導電体 498b と、導電体 498c と、絶縁体 490 と、絶縁体 492 と、絶縁体 494 と、を有する。10

【0281】

絶縁体 464 は、トランジスタ 2200 上に配置する。また、絶縁体 466 は、絶縁体 464 上に配置する。また、絶縁体 468 は、絶縁体 466 上に配置する。また、絶縁体 490 は、絶縁体 468 上に配置する。また、トランジスタ 2100 は、絶縁体 490 上に配置する。また、絶縁体 492 は、トランジスタ 2100 上に配置する。また、絶縁体 494 は、絶縁体 492 上に配置する。20

【0282】

絶縁体 464 は、領域 472a に達する開口部と、領域 472b に達する開口部と、導電体 454 に達する開口部と、を有する。また、開口部には、それぞれ導電体 480a、導電体 480b または導電体 480c が埋め込まれている。

【0283】

また、絶縁体 466 は、導電体 480a に達する開口部と、導電体 480b に達する開口部と、導電体 480c に達する開口部と、を有する。また、開口部には、それぞれ導電体 478a、導電体 478b または導電体 478c が埋め込まれている。

【0284】

また、絶縁体 468 は、導電体 478b に達する開口部と、導電体 478c に達する開口部と、を有する。また、開口部には、それぞれ導電体 476a または導電体 476b が埋め込まれている。30

【0285】

また、絶縁体 490 は、トランジスタ 2100 のチャネル形成領域と重なる開口部と、導電体 476a に達する開口部と、導電体 476b に達する開口部と、を有する。また、開口部には、それぞれ導電体 474a、導電体 474b または導電体 474c が埋め込まれている。

【0286】

導電体 474a は、トランジスタ 2100 のゲート電極としての機能を有しても構わない。または、例えば、導電体 474a に一定の電位を印加することで、トランジスタ 2100 のしきい値電圧などの電気特性を制御しても構わない。または、例えば、導電体 474a とトランジスタ 2100 のゲート電極としての機能を有する導電体 404 とを電気的に接続しても構わない。こうすることで、トランジスタ 2100 のオン電流を大きくすることができます。また、パンチスルーエフェクトを抑制することができるため、トランジスタ 2100 の飽和領域における電気特性を安定にすることができる。40

【0287】

また、絶縁体 492 は、トランジスタ 2100 のソース電極またはドレイン電極の一方である導電体 416b を通って、導電体 474b に達する開口部と、トランジスタ 2100 のソース電極またはドレイン電極の他方である導電体 416a に達する開口部と、トランジスタ 2100 のゲート電極である導電体 404 に達する開口部と、導電体 474c に達

10

20

30

40

50

する開口部と、を有する。また、開口部には、それぞれ導電体 496a、導電体 496b、導電体 496c または導電体 496d が埋め込まれている。ただし、それぞれの開口部は、さらにトランジスタ 2100 などの構成要素のいずれかを介する場合がある。

#### 【0288】

また、絶縁体 494 は、導電体 496a に達する開口部と、導電体 496b および導電体 496d に達する開口部と、導電体 496c に達する開口部と、を有する。また、開口部には、それぞれ導電体 498a、導電体 498b または導電体 498c が埋め込まれている。

#### 【0289】

絶縁体 464、絶縁体 466、絶縁体 468、絶縁体 490、絶縁体 492 および絶縁体 494 としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。例えば、絶縁体 401 としては、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウムまたは酸化タンタルを用いればよい。

10

#### 【0290】

絶縁体 464、絶縁体 466、絶縁体 468、絶縁体 490、絶縁体 492 または絶縁体 494 の一以上は、水素などの不純物および酸素をブロックする機能を有する絶縁体を有することが好ましい。トランジスタ 2100 の近傍に、水素などの不純物および酸素をブロックする機能を有する絶縁体を配置することによって、トランジスタ 2100 の電気特性を安定にすることができる。

20

#### 【0291】

水素などの不純物および酸素をブロックする機能を有する絶縁体としては、例えば、ホウ素、炭素、窒素、酸素、フッ素、マグネシウム、アルミニウム、シリコン、リン、塩素、アルゴン、ガリウム、ゲルマニウム、イットリウム、ジルコニウム、ランタン、ネオジム、ハフニウムまたはタンタルを含む絶縁体を、単層で、または積層で用いればよい。

#### 【0292】

導電体 480a、導電体 480b、導電体 480c、導電体 478a、導電体 478b、導電体 478c、導電体 476a、導電体 476b、導電体 474a、導電体 474b、導電体 474c、導電体 496a、導電体 496b、導電体 496c、導電体 496d、導電体 498a、導電体 498b および導電体 498c としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニウム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタングステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

30

#### 【0293】

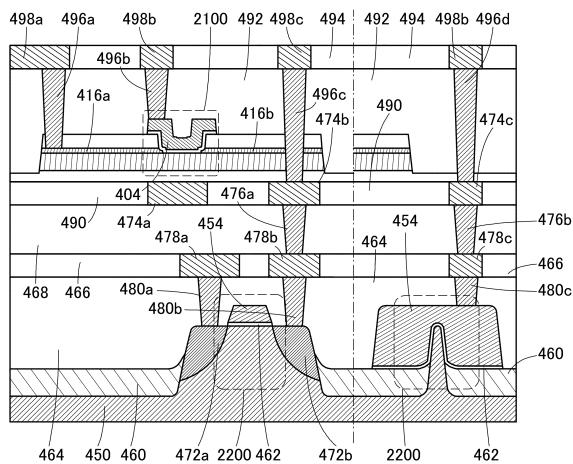

なお、図 22 に示す半導体装置は、図 21 に示した半導体装置のトランジスタ 2200 の構造が異なるのみである。よって、図 22 に示す半導体装置については、図 21 に示した半導体装置の記載を参照する。具体的には、図 22 に示す半導体装置は、トランジスタ 2200 が Fin 型である場合を示している。トランジスタ 2200 を Fin 型とすることにより、実効上のチャネル幅が増大することによりトランジスタ 2200 のオン特性を向上させることができる。また、ゲート電極の電界の寄与を高くすることができるため、トランジスタ 2200 のオフ特性を向上させることができる。

40

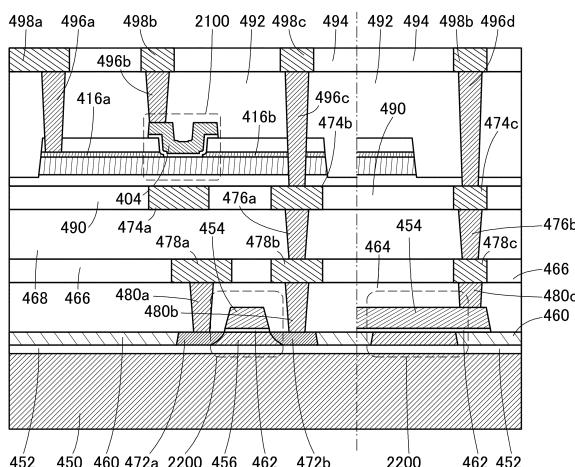

#### 【0294】

また、図 23 に示す半導体装置は、図 21 に示した半導体装置のトランジスタ 2200 の構造が異なるのみである。よって、図 23 に示す半導体装置については、図 21 に示した

50

半導体装置の記載を参照する。具体的には、図23に示す半導体装置は、トランジスタ2200がSOI基板に設けられた場合を示している。図23には、絶縁体452によって領域456が半導体基板450と分離されている構造を示す。SOI基板を用いることによって、パンチスルーハウジングなどを抑制することができるためトランジスタ2200のオフ特性を向上させることができる。なお、絶縁体452は、半導体基板450の一部を絶縁体化させることによって形成することができる。例えば、絶縁体452としては、酸化シリコンを用いることができる。

#### 【0295】

図21乃至図23に示した半導体装置は、半導体基板を用いてpチャネル型トランジスタを作製し、その上方にnチャネル型トランジスタを作製するため、素子の占有面積を縮小することができる。即ち、半導体装置の集積度を高くすることができます。また、nチャネル型トランジスタと、pチャネル型トランジスタとを同一の半導体基板を用いて作製した場合と比べて、工程を簡略化することができるため、半導体装置の生産性を高くすることができます。また、半導体装置の歩留まりを高くすることができます。また、pチャネル型トランジスタは、LDD(Lightly Doped Drain)領域、シャロートレンチ構造、歪み設計などの複雑な工程を省略できる場合がある。そのため、nチャネル型トランジスタを、半導体基板を用いて作製する場合と比べて、生産性および歩留まりを高くすることができる場合がある。

10

#### 【0296】

##### <CMOSアナログスイッチ>

20

また図20(B)に示す回路図は、トランジスタ2100とトランジスタ2200のそれぞれのソースとドレインを接続した構成を示している。このような構成とすることで、いわゆるCMOSアナログスイッチとして機能させることができます。

#### 【0297】

##### <記憶装置1>

本発明の一態様に係るトランジスタを用いた、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を図24に示す。

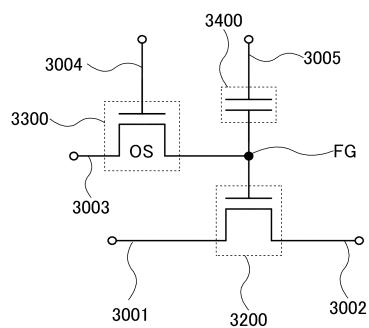

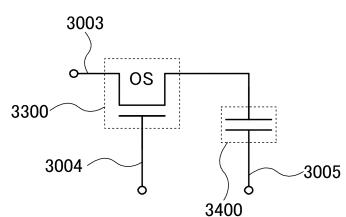

#### 【0298】

図24(A)に示す半導体装置は、第1の半導体を用いたトランジスタ3200と第2の半導体を用いたトランジスタ3300、および容量素子3400を有している。なお、トランジスタ3300としては、上述したトランジスタを用いることができる。

30

#### 【0299】

トランジスタ3300は、オフ電流の小さいトランジスタが好ましい。トランジスタ3300は、例えば、酸化物半導体を用いたトランジスタを用いることができる。トランジスタ3300のオフ電流が小さいことにより、半導体装置の特定のノードに長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、またはリフレッシュ動作の頻度が極めて少なくすることが可能となるため、消費電力の低い半導体装置となる。

#### 【0300】

図24(A)において、第1の配線3001はトランジスタ3200のソースと電気的に接続され、第2の配線3002はトランジスタ3200のドレインと電気的に接続される。また、第3の配線3003はトランジスタ3300のソース、ドレインの一方と電気的に接続され、第4の配線3004はトランジスタ3300のゲートと電気的に接続されている。そして、トランジスタ3200のゲート、およびトランジスタ3300のソース、ドレインの他方は、容量素子3400の電極の一方と電気的に接続され、第5の配線3005は容量素子3400の電極の他方と電気的に接続されている。

40

#### 【0301】

図24(A)に示す半導体装置は、トランジスタ3200のゲートの電位が保持可能という特性を有することで、以下に示すように、情報の書き込み、保持、読み出しが可能であ

50

る。

### 【0302】

情報の書き込みおよび保持について説明する。まず、第4の配線3004の電位を、トランジスタ3300が導通状態となる電位にして、トランジスタ3300を導通状態とする。これにより、第3の配線3003の電位が、トランジスタ3200のゲート、および容量素子3400の電極の一方と電気的に接続するノードFGに与えられる。即ち、トランジスタ3200のゲートには、所定の電荷が与えられる（書き込み）。ここでは、異なる二つの電位レベルを与える電荷（以下Lowレベル電荷、Highレベル電荷という。）のどちらかが与えられるものとする。その後、第4の配線3004の電位を、トランジスタ3300が非導通状態となる電位にして、トランジスタ3300を非導通状態することにより、ノードFGに電荷が保持される（保持）。

10

### 【0303】

トランジスタ3300のオフ電流が小さいため、ノードFGの電荷は長期間にわたって保持される。

### 【0304】

次に情報の読み出しについて説明する。第1の配線3001に所定の電位（定電位）を与えた状態で、第5の配線3005に適切な電位（読み出し電位）を与えると、第2の配線3002は、ノードFGに保持された電荷量に応じた電位をとる。これは、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲートにHighレベル電荷が与えられている場合の見かけ上のしきい値電圧 $V_{th\_H}$ は、トランジスタ3200のゲートにLowレベル電荷が与えられている場合の見かけ上のしきい値電圧 $V_{th\_L}$ より低くなるためである。ここで、見かけ上のしきい値電圧とは、トランジスタ3200を「導通状態」とするために必要な第5の配線3005の電位をいうものとする。したがって、第5の配線3005の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、ノードFGに与えられた電荷を判別できる。例えば、書き込みにおいて、ノードFGにHighレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0 (> V_{th\_H})$ となれば、トランジスタ3200は「導通状態」となる。一方、ノードFGにLowレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0 (< V_{th\_L})$ となっても、トランジスタ3200は「非導通状態」のままである。このため、第2の配線3002の電位を判別することで、ノードFGに保持されている情報を読み出すことができる。

20

### 【0305】

なお、メモリセルをアレイ状に配置する場合、読み出し時には、所望のメモリセルの情報を読み出さなくてはならない。ほかのメモリセルの情報を読み出さないために、ノードFGに与えられた電荷によらずトランジスタ3200が「非導通状態」となるような電位、つまり、 $V_{th\_H}$ より低い電位を第5の配線3005に与えればよい。または、ノードFGに与えられた電荷によらずトランジスタ3200が「導通状態」となるような電位、つまり、 $V_{th\_L}$ より高い電位を第5の配線3005に与えればよい。

30

### 【0306】

<半導体装置の構造2>

40

図25は、図24(A)に対応する半導体装置の断面図である。図25に示す半導体装置は、トランジスタ3200と、トランジスタ3300と、容量素子3400と、を有する。また、トランジスタ3300および容量素子3400は、トランジスタ3200の上方に配置する。なお、トランジスタ3300としては、上述したトランジスタ2100についての記載を参照する。また、トランジスタ3200としては、図21に示したトランジスタ2200についての記載を参照する。なお、図21では、トランジスタ2200がpチャネル型トランジスタである場合について説明したが、トランジスタ3200がnチャネル型トランジスタであっても構わない。

### 【0307】

図25に示すトランジスタ3200は、半導体基板450を用いたトランジスタである。

50

トランジスタ3200は、半導体基板450中の領域472aと、半導体基板450中の領域472bと、絶縁体462と、導電体454と、を有する。

#### 【0308】

図25に示す半導体装置は、絶縁体464と、絶縁体466と、絶縁体468と、導電体480aと、導電体480bと、導電体480cと、導電体478aと、導電体478bと、導電体478cと、導電体476aと、導電体476bと、導電体474aと、導電体474bと、導電体474cと、導電体496aと、導電体496bと、導電体496cと、導電体496dと、導電体498aと、導電体498bと、導電体498cと、導電体498dと、絶縁体490と、絶縁体492と、絶縁体494と、を有する。

#### 【0309】

絶縁体464は、トランジスタ3200上に配置する。また、絶縁体466は、絶縁体464上に配置する。また、絶縁体468は、絶縁体466上に配置する。また、絶縁体490は、絶縁体468上に配置する。また、トランジスタ3300は、絶縁体490上に配置する。また、絶縁体492は、トランジスタ3300上に配置する。また、絶縁体494は、絶縁体492上に配置する。

10

#### 【0310】

絶縁体464は、領域472aに達する開口部と、領域472bに達する開口部と、導電体454に達する開口部と、を有する。また、開口部には、それぞれ導電体480a、導電体480bまたは導電体480cが埋め込まれている。

#### 【0311】

また、絶縁体466は、導電体480aに達する開口部と、導電体480bに達する開口部と、導電体480cに達する開口部と、を有する。また、開口部には、それぞれ導電体478a、導電体478bまたは導電体478cが埋め込まれている。

20

#### 【0312】

また、絶縁体468は、導電体478bに達する開口部と、導電体478cに達する開口部と、を有する。また、開口部には、それぞれ導電体476aまたは導電体476bが埋め込まれている。

#### 【0313】

また、絶縁体490は、トランジスタ3300のチャネル形成領域と重なる開口部と、導電体476aに達する開口部と、導電体476bに達する開口部と、を有する。また、開口部には、それぞれ導電体474a、導電体474bまたは導電体474cが埋め込まれている。

30

#### 【0314】

導電体474aは、トランジスタ3300のボトムゲート電極としての機能を有しても構わない。または、例えば、導電体474aに一定の電位を印加することで、トランジスタ3300のしきい値電圧などの電気特性を制御しても構わない。または、例えば、導電体474aとトランジスタ3300のトップゲート電極である導電体404とを電気的に接続しても構わない。こうすることで、トランジスタ3300のオン電流を大きくすることができる。また、パンチスルー現象を抑制することができるため、トランジスタ3300の飽和領域における電気特性を安定にすることができる。

40

#### 【0315】

また、絶縁体492は、トランジスタ3300のソース電極またはドレイン電極の一方である導電体416bを通って、導電体474bに達する開口部と、トランジスタ3300のソース電極またはドレイン電極の他方である導電体414に達する開口部と、トランジスタ3300のゲート電極である導電体404に達する開口部と、トランジスタ3300のソース電極またはドレイン電極の他方である導電体416aを通って、導電体474cに達する開口部と、を有する。また、開口部には、それぞれ導電体496a、導電体496b、導電体496cまたは導電体496dが埋め込まれている。ただし、それぞれの開口部は、さらにトランジスタ3300などの構成要素のいずれかを介する場合がある。

#### 【0316】

50

また、絶縁体 494 は、導電体 496a に達する開口部と、導電体 496b に達する開口部と、導電体 496c に達する開口部と、導電体 496d に達する開口部と、を有する。また、開口部には、それぞれ導電体 498a、導電体 498b、導電体 498c または導電体 498d が埋め込まれている。

#### 【0317】

絶縁体 464、絶縁体 466、絶縁体 468、絶縁体 490、絶縁体 492 または絶縁体 494 の一以上は、水素などの不純物および酸素をブロックする機能を有する絶縁体を有することが好ましい。トランジスタ 3300 の近傍に、水素などの不純物および酸素をブロックする機能を有する絶縁体を配置することによって、トランジスタ 3300 の電気特性を安定にすることができる。

10

#### 【0318】

導電体 498d としては、例えば、ホウ素、窒素、酸素、フッ素、シリコン、リン、アルミニウム、チタン、クロム、マンガン、コバルト、ニッケル、銅、亜鉛、ガリウム、イットリウム、ジルコニアム、モリブデン、ルテニウム、銀、インジウム、スズ、タンタルおよびタンクステンを一種以上含む導電体を、単層で、または積層で用いればよい。例えば、合金や化合物であってもよく、アルミニウムを含む導電体、銅およびチタンを含む導電体、銅およびマンガンを含む導電体、インジウム、スズおよび酸素を含む導電体、チタンおよび窒素を含む導電体などを用いてもよい。

#### 【0319】

トランジスタ 3200 のソースまたはドレインは、導電体 480b と、導電体 478b と、導電体 476a と、導電体 474b と、導電体 496c と、を介してトランジスタ 3300 のソース電極またはドレイン電極の一方である導電体 416b と電気的に接続する。また、トランジスタ 3200 のゲート電極である導電体 454 は、導電体 480c と、導電体 478c と、導電体 476b と、導電体 474c と、導電体 496d と、を介してトランジスタ 3300 のソース電極またはドレイン電極の他方である導電体 416a と電気的に接続する。

20

#### 【0320】

容量素子 3400 は、トランジスタ 3300 のソース電極またはドレイン電極の他方と電気的に接続する電極と、導電体 414 と、絶縁体 411 と、を有する。なお、絶縁体 411 は、トランジスタ 3300 のゲート絶縁体と同一工程を経て形成できるため、生産性を高めることができる。また、導電体 414 として、トランジスタ 3300 のゲート電極と同一工程を経て形成した層を用いると、生産性を高めることができる。

30

#### 【0321】

そのほかの構造については、適宜図 21 などについての記載を参酌することができる。

#### 【0322】

なお、図 26 に示す半導体装置は、図 25 に示した半導体装置のトランジスタ 3200 の構造が異なるのみである。よって、図 26 に示す半導体装置については、図 25 に示した半導体装置の記載を参照する。具体的には、図 26 に示す半導体装置は、トランジスタ 3200 が F<sub>in</sub> 型である場合を示している。F<sub>in</sub> 型であるトランジスタ 3200 については、図 22 に示したトランジスタ 2200 の記載を参照する。なお、図 22 では、トランジスタ 2200 が p チャネル型トランジスタである場合について説明したが、トランジスタ 3200 が n チャネル型トランジスタであっても構わない。

40

#### 【0323】

また、図 27 に示す半導体装置は、図 25 に示した半導体装置のトランジスタ 3200 の構造が異なるのみである。よって、図 27 に示す半導体装置については、図 25 に示した半導体装置の記載を参照する。具体的には、図 27 に示す半導体装置は、トランジスタ 3200 が SOI 基板である半導体基板 450 に設けられた場合を示している。SOI 基板である半導体基板 450 に設けられたトランジスタ 3200 については、図 23 に示したトランジスタ 2200 の記載を参照する。なお、図 23 では、トランジスタ 2200 が p チャネル型トランジスタである場合について説明したが、トランジスタ 3200 が n チャ

50

ネル型トランジスタであっても構わない。

**【0324】**

<記憶装置2>

図24(B)に示す半導体装置は、トランジスタ3200を有さない点で図24(A)に示した半導体装置と異なる。この場合も図24(A)に示した半導体装置と同様の動作により情報の書き込みおよび保持動作が可能である。

**【0325】**

図24(B)に示す半導体装置における、情報の読み出しについて説明する。トランジスタ3300が導通状態になると、浮遊状態である第3の配線3003と容量素子3400とが導通し、第3の配線3003と容量素子3400の間で電荷が再分配される。その結果、第3の配線3003の電位が変化する。第3の配線3003の電位の変化量は、容量素子3400の電極の一方の電位（または容量素子3400に蓄積された電荷）によって、異なる値をとる。

10

**【0326】**

例えば、容量素子3400の電極の一方の電位をV、容量素子3400の容量をC、第3の配線3003が有する容量成分をCB、電荷が再分配される前の第3の配線3003の電位をVB0とすると、電荷が再分配された後の第3の配線3003の電位は、 $(CB \times VB_0 + C \times V) / (CB + C)$ となる。したがって、メモリセルの状態として、容量素子3400の電極の一方の電位がV1とV0 ( $V1 > V0$ ) の2つの状態をとるとすると、電位V1を保持している場合の第3の配線3003の電位( $= (CB \times VB_0 + C \times V_1) / (CB + C)$ )は、電位V0を保持している場合の第3の配線3003の電位( $= (CB \times VB_0 + C \times V_0) / (CB + C)$ )よりも高くなることがわかる。

20

**【0327】**

そして、第3の配線3003の電位を所定の電位と比較することで、情報を読み出すことができる。

**【0328】**

この場合、メモリセルを駆動させるための駆動回路に上記第1の半導体が適用されたトランジスタを用い、トランジスタ3300として第2の半導体が適用されたトランジスタを駆動回路上に積層して配置する構成とすればよい。

30

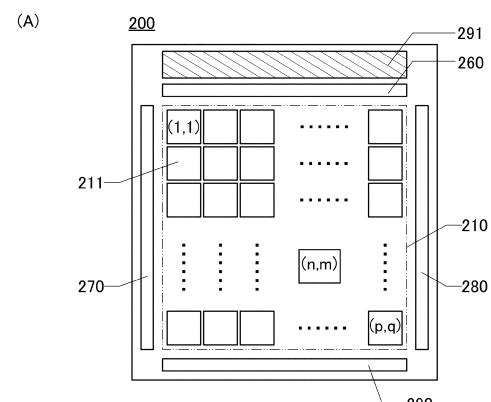

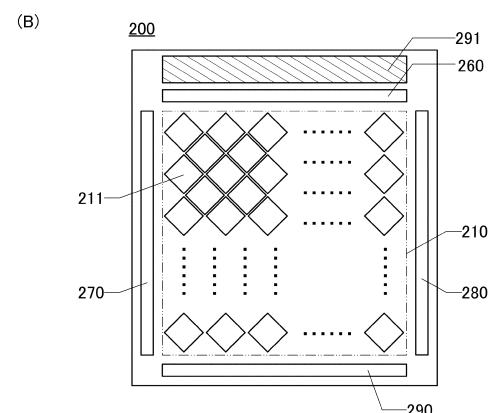

**【0329】**