(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6509495号

(P6509495)

(45) 発行日 令和1年5月8日(2019.5.8)

(24) 登録日 平成31年4月12日(2019.4.12)

|                          |                     |

|--------------------------|---------------------|

| (51) Int.Cl.             | F 1                 |

| HO 1 L 21/3065 (2006.01) | HO 1 L 21/302 101 G |

| HO 1 L 21/28 (2006.01)   | HO 1 L 21/302 101 C |

| HO 5 H 1/46 (2006.01)    | HO 1 L 21/302 105 A |

|                          | HO 1 L 21/28 E      |

|                          | HO 1 L 21/28 301 A  |

請求項の数 29 外国語出願 (全 50 頁) 最終頁に続く

|              |                               |           |                                                                                                                   |

|--------------|-------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2014-77139 (P2014-77139)    | (73) 特許権者 | 592010081<br>ラム リサーチ コーポレーション<br>LAM RESEARCH CORPORATION<br>アメリカ合衆国, カリフォルニア 945<br>38, フレモント, クッシング パークウェイ 4650 |

| (22) 出願日     | 平成26年4月3日(2014.4.3)           | (74) 代理人  | 110000028<br>特許業務法人明成国際特許事務所                                                                                      |

| (65) 公開番号    | 特開2014-209622 (P2014-209622A) | (74) 代理人  | 100113527<br>弁理士 堀 研一                                                                                             |

| (43) 公開日     | 平成26年11月6日(2014.11.6)         | (72) 発明者  | アレックス・パターソン<br>アメリカ合衆国 カリフォルニア州951<br>20 サン・ホセ, マートウッド・ウェイ<br>, 7268                                              |

| 審査請求日        | 平成29年3月31日(2017.3.31)         |           |                                                                                                                   |

| (31) 優先権主張番号 | 61/809, 246                   |           |                                                                                                                   |

| (32) 優先日     | 平成25年4月5日(2013.4.5)           |           |                                                                                                                   |

| (33) 優先権主張国  | 米国(US)                        |           |                                                                                                                   |

| (31) 優先権主張番号 | 14/082, 009                   |           |                                                                                                                   |

| (32) 優先日     | 平成25年11月15日(2013.11.15)       |           |                                                                                                                   |

| (33) 優先権主張国  | 米国(US)                        |           |                                                                                                                   |

| (31) 優先権主張番号 | 14/184, 491                   |           |                                                                                                                   |

| (32) 優先日     | 平成26年2月19日(2014.2.19)         |           |                                                                                                                   |

| (33) 優先権主張国  | 米国(US)                        |           |                                                                                                                   |

最終頁に続く

(54) 【発明の名称】半導体製造用の内部プラズマグリッドの適用

## (57) 【特許請求の範囲】

## 【請求項 1】

プラズマを処理する方法であって、

反応チャンバ内に基板を受け取るステップであって、前記反応チャンバが、前記反応チャンバの内部を、プラズマ発生器の近傍の上部サブチャンバと、基板ホルダの近傍の下部サブチャンバと、に分割するグリッド構造を備えるステップと、

プラズマ発生ガスを前記上部サブチャンバに流すステップと、

前記上部サブチャンバ内で、前記プラズマ発生ガスから、第1の電子密度を有する第1のプラズマを発生させ、前記下部サブチャンバ内で、第2のプラズマを発生させるステップであって、前記第2のプラズマが、前記第1の電子密度の10分の1未満の第2の電子密度を有するイオン-イオンプラズマであるステップと、

前記第2のプラズマを用いて前記基板を処理して、ソースドレインリセスエッチングでのステップを行うステップであって、

(a) 前記基板を垂直方向にエッチングするために第1のエッチングプロセスを行って、垂直エッチングフィーチャを形成するステップと、

(b) 前記垂直エッチングフィーチャの内部で前記基板を水平方向にエッチングするために、第2のエッチングプロセスを行うステップと、

(c) 前記水平方向にエッチングされた前記垂直エッチングフィーチャ内部に酸化層を形成するために、酸化プロセスを行うステップと、

(d) 前記垂直エッチングフィーチャ内にソースドレインリセスを形成するために(

10

20

a) ~ (c) を少なくとも 1 回繰り返すステップと、を含むステップとを含み、

前記第 1 のエッティングプロセス、第 2 のエッティングプロセス、および酸化プロセスがすべて、各プロセスでの前記第 2 のプラズマがイオン・イオンプラズマであるように、前記グリッド構造を有する前記反応チャンバ内で行われる、方法。

【請求項 2】

請求項 1 に記載の方法であって、

前記第 1 のプラズマが、2 eV 以上の第 1 の電子温度を有し、前記第 2 のプラズマが、1 eV 以下の第 2 の実効電子温度を有する、方法。

【請求項 3】

請求項 1 に記載の方法であって、

前記第 2 の電子密度が、5 × 10<sup>9</sup> cm<sup>-3</sup> 以下である、方法。

【請求項 4】

請求項 1 に記載の方法であって、前記第 2 のプラズマ中の負イオン：正イオンの比が、0.5 ~ 1 の間である、方法。

【請求項 5】

請求項 1 に記載の方法であって、

前記水平方向にエッティングされた前記垂直エッティングフィーチャが、(c) の後に、第 1 のエッティング部分の上に前記第 1 のエッティング部分より狭い第 2 エッティング部分を有する凹角形状を有する、方法。

【請求項 6】

プラズマを処理する方法であって、

反応チャンバ内に基板を受け取るステップであって、前記反応チャンバの内部を、プラズマ発生器の近傍の上部サブチャンバと、基板ホルダの近傍の下部サブチャンバと、に分割するグリッド構造を、前記反応チャンバが備える、ステップと、

プラズマ発生ガスを前記上部サブチャンバに流すステップと、

前記上部サブチャンバ内で、前記プラズマ発生ガスから、第 1 の電子密度を有する第 1 のプラズマを発生させ、前記下部サブチャンバ内で、第 2 のプラズマを発生させるステップであって、前記第 2 のプラズマが、前記第 1 の電子密度の少なくとも1/10 分の 1 未満の第 2 の電子密度を有するイオン・イオンプラズマであり、前記第 1 のプラズマが、誘導結合プラズマであるステップと、

前記第 2 のプラズマを用いて前記基板を処理して、シャロートレンチ・アイソレーション・エッティングを行うステップと、を含み、

前記基板が、前記エッティング中に300 ~ 1200 V の間にバイアスされ、

前記エッティングプロセスが、少なくとも第 1 のフィーチャ形状と第 2 のフィーチャ形状を同時にエッティングするステップを含み、前記第 1 のフィーチャ形状が、1/10 以上のアスペクト比を有し、前記第 2 のフィーチャ形状が、1 以下のアスペクト比を有し、

エッティング後、前記第 1 のフィーチャ形状のエッティング深さが、前記第 2 のフィーチャ形状の前記エッティング深さの少なくとも95% である、方法。

【請求項 7】

F i n F E T ゲート領域を画定するために、半製造された集積回路上のポリシリコンをエッティングする方法であって、

(a) 上にポリシリコン層を有する基板を反応チャンバ内に受け取るステップであって、前記反応チャンバが、前記反応チャンバの内部を、プラズマ発生器の近傍の上部サブチャンバと、基板ホルダの近傍の下部サブチャンバと、に分割するグリッド構造を備えるステップと、

(b) プラズマ発生ガスを前記上部サブチャンバに流すステップと、

(c) 前記上部サブチャンバ内で前記プラズマ発生ガスから第 1 のプラズマを発生させ、前記下部サブチャンバ内で第 2 のプラズマを発生させるステップであって、前記第 2 のプラズマが、イオン・イオンプラズマであるステップと、

(d) 前記基板に提供された前記ポリシリコン層を前記第 2 のプラズマでエッティングし

10

20

30

40

50

、それにより F i n F E T ゲート領域を画定するステップと、

( e ) ( a ) ~ ( d ) を繰り返すステップと、を含み、

( a ) ~ ( d ) の第 1 の繰り返し中において、前記プラズマ発生ガスが、第 1 の組成を有する第 1 のプラズマ発生ガスであり、( a ) ~ ( d ) の第 2 の繰り返し中において、前記プラズマ発生ガスが、第 2 の組成を有する第 2 のプラズマ発生ガスであり、前記第 1 の組成が、前記第 2 の組成と異なる、方法。

【請求項 8】

請求項 7 に記載の方法であって、

( d ) において前記ポリシリコン層をエッチングするステップが、完成された集積回路において F i n F E T ゲートの近傍となる位置にキャビティを形成する、方法。 10

【請求項 9】

請求項 8 に記載の方法であって、

前記エッチング中の前記反応チャンバ内の圧力が、0 . 6 6 7 ~ 2 . 6 7 P a の間である、方法。

【請求項 10】

請求項 8 に記載の方法であって、

オンフィン領域とオフフィン領域との間のエッチングプロファイル・ローディングが、実質的に存在しない、方法。

【請求項 11】

請求項 7 に記載の方法であって、

( d ) において前記ポリシリコン層をエッチングするステップが、完成された集積回路において F i n F E T ゲートが配される位置にキャビティを形成する、方法。 20

【請求項 12】

前記第 1 のプラズマ発生ガスが H B r を含み、前記第 2 のプラズマ発生ガスが C l <sub>2</sub> を含み、前記第 1 および第 2 のプラズマ発生ガスが、実質的に酸素含有反応物を含まない請求項 11 に記載の方法。

【請求項 13】

請求項 12 に記載の方法であって、

前記反応チャンバ内の圧力が、前記第 1 の繰り返し中に2 . 6 7 ~ 1 0 . 7 P a の間であり、前記第 2 の繰り返し中に0 . 5 3 3 ~ 1 0 . 7 P a の間である、方法。 30

【請求項 14】

請求項 7 に記載の方法であって、

前記第 2 のプラズマでの実効電子温度が、1 e V 以下であり、前記第 1 のプラズマでの実効電子温度未満である、方法。

【請求項 15】

請求項 14 に記載の方法であって、

前記第 2 のプラズマでの電子密度が、5 × 1 0 <sup>9</sup> c m <sup>-3</sup> 以下であり、前記第 1 のプラズマ内での電子密度よりも小さい、方法。

【請求項 16】

請求項 7 に記載の方法であって、

前記グリッド構造が、2 つ以上のグリッドを備え、前記グリッドの少なくとも 1 つが、他のグリッドに対して移動可能である、方法。 40

【請求項 17】

請求項 1 に記載の方法であって、

( a ) における前記第 1 のエッチングプロセスが、第 1 のプラズマ発生ガスを用いて行われ、( b ) における前記第 2 のエッチングプロセスが、第 2 のプラズマ発生ガスを用いて行われ、前記第 1 のプラズマ発生ガスの組成が、前記第 2 のプラズマ発生ガスの組成と異なり、( c ) における前記酸化プロセスが、酸素を含む第 3 のプラズマ発生ガスを用いて行われる、方法。

【請求項 18】

請求項 17 に記載の方法であって、

前記第1のプラズマ発生ガスが、 $C\ 1_2$ を含み、前記第2のプラズマ発生ガスが、 $N\ F_3$ および $C\ 1_2$ を含む、方法。

【請求項 19】

請求項 6 に記載の方法であって、

前記第1のプラズマが、 $2\ e\ V$ 以上の第1の電子温度を有し、前記第2のプラズマが、 $1\ e\ V$ 以下の第2の実効電子温度を有する、方法。

【請求項 20】

請求項 6 に記載の方法であって、

前記第2の電子密度が、 $5 \times 10^9\ c\ m^{-3}$ 以下である、方法。 10

【請求項 21】

請求項 6 に記載の方法であって、

前記第2のプラズマ中の負イオン：正イオンの比が、 $0.5 \sim 1$ の間である、方法。

【請求項 22】

請求項 6 に記載の方法であって、さらに、

前記基板に印加された前記バイアスをパルス化するステップを含む、方法。

【請求項 23】

請求項 6 に記載の方法であって、

前記基板に印加された前記バイアスが、DCバイアスである、方法。

【請求項 24】

請求項 6 に記載の方法であって、

エッティング後、前記第1のフィーチャ形状が、少なくとも $88^\circ$ のエッティングプロファイルを有し、前記第2のフィーチャ形状が、少なくとも $85^\circ$ のエッティングプロファイルを有する、方法。

【請求項 25】

請求項 8 に記載の方法であって、

前記ポリシリコン層の上に位置決めされたマスク層の厚さが、(d)における前記エッティング中に $10\%$ 未満だけ減少する、方法。

【請求項 26】

請求項 7 に記載の方法であって、

前記第1のプラズマが、連続波プラズマである、方法。 30

【請求項 27】

請求項 7 に記載の方法であって、

異なるフィーチャ密度で配された前記基板上に位置するエッティング後の複数のフィーチャの間のエッティングプロファイル・ローディングが、実質的に存在しない、方法。

【請求項 28】

請求項 7 に記載の方法であって、

前記反応チャンバ内の圧力が、(a)～(d)の前記第1の繰り返し中に $2.67 \sim 10.7\ Pa$ の間であり、(a)～(d)の前記第2の繰り返し中に $0.533 \sim 10.7\ Pa$ の間である、方法。 40

【請求項 29】

請求項 10 に記載の方法であって、

前記エッティングされた領域の側壁が、エッティング中に凹まない、方法。

【発明の詳細な説明】

【技術分野】

【0001】

[関連出願の相互参照]

本出願は、“INTERNAL PLASMA GRID APPLICATIONS FOR SEMICONDUCTOR FABRICATION (半導体製造用の内部プラズマグリッドの適用)”という名称で2014年2月19日に出願された米国特許出 50

願第14/184, 491号の優先権の利益を主張するものであり、この特許文献は、“INTERNAL PLASMA GRID FOR SEMICONDUCTOR FABRICATION (半導体製造用の内部プラズマグリッド)”という名称で2013年11月15日に出願された米国特許出願第14/082, 009号の一部継続出願であり、その優先権の利益を主張し、この特許文献は、“INTERNAL PLASMA GRID FOR SEMICONDUCTOR FABRICATION (半導体製造用の内部プラズマグリッド)”という名称で2013年4月5日に出願された米国仮特許出願第61/809, 246号の優先権の利益を主張するものである。これらの文献はそれぞれ、その全体がすべての目的のために参照により本明細書に組み込まれる。

【背景技術】

10

【0002】

半導体製造においてよく採用される工程の1つは、エッチング工程である。エッチング工程では、半製品の集積回路から1つ以上の材料が部分的または完全に除去される。特に、関わるジオメトリが小さいか、高いアスペクト比が採用されるか、または精密なパターン転写が要求される場合には、プラズマエッチングがよく用いられる。

【0003】

一般に、プラズマは、電子と、さらに正・負イオン、およびいくつかのラジカルを含んでいる。ラジカル、正イオン、および負イオンは、基板と相互作用することで、基板上のフィーチャ、表面、および材料をエッチングする。誘導結合プラズマ源を用いてエッチングを実施する場合には、チャンバコイルが、変圧器の一次コイルと同様の機能を果たし、プラズマが、変圧器の二次コイルと同様の機能を果たす。

20

【0004】

プレーナ型から3Dトランジスタ構造（例えば、論理デバイス用のFinFETゲート構造）に移行すると、プラズマエッチングプロセスは、良品を製造するためには、ますます精密かつ均一であることが要求される。精密なエッチングから利益を得る操作の例は、限定はしないが、FinFETの形成中に使用されるエッチング／除去プロセス（例えば、ソースドレインリセスエッチング、FinFETゲートエッチング、およびダミーポリシリコン除去）、シャロートレンチアイソレーションプロセス、およびフォトレジスト・リフロープロセスを含む。

【0005】

30

プラズマエッチングプロセスは、数ある因子の中でも特に、良好な選択性、プロファイル角、疎／密ローディング、全面均一性を示すものでなければならない。エッチングプロセスは、エッチングされる材料と残される材料との間の選択性が良好であると有用である。FinFETゲート構造の文脈では、これは、窒化ケイ素マスクなど他の露出部品に対して、エッチングされるゲートの選択性が良好でなければならないことを意味する。プロファイル角は、直近にエッチングされた（略垂直な）側壁と水平面との間の角度として測定される。多くの応用において、理想的なプロファイル角は90度であり、垂直エッチングにより段差または開口が作製される。場合によって、ウェハ上の局所フィーチャ密度がエッチングプロセスに影響することがある。例えば、フィーチャが密なウェハ領域は、フィーチャがより疎なウェハ領域に比べて、（例えば、より高速の、より低速の、より等方的な、より異方的なエッチングになり得るなど）エッチングに若干違いが生じ得る。フィーチャ密度の違いに起因して生じる差異は、疎（Iso）／密（Dense）ローディング（I/Dローディング）と呼ばれる。製造の際に、このような差異を最小限に抑えることは有用である。これらの要件および他の可能性のあるデバイス固有の要件を満たすことに加えて、多くの場合、エッチングプロセスが基板の全面にわたって一貫して実施されることが要求される（例えば、エッチング条件ならびに結果は、半導体ウェハの中心からエッジまで均一でなければならない）。

40

【発明の概要】

【発明が解決しようとする課題】

【0006】

50

F i n F E T ゲートのような先進構造をエッティングする際に、上記のような複数の目的を達成することは難しいことが分かっている。

【課題を解決するための手段】

【 0 0 0 7 】

本明細書に開示する実施形態は、半導体を製造するための方法および装置を提供する。開示される実施形態の一態様では、プラズマを処理する方法であって、反応チャンバ内に基板を受け取るステップであって、反応チャンバが、反応チャンバの内部を、プラズマ発生器の近傍の上部サブチャンバと、基板ホルダの近傍の下部サブチャンバと、に分割するグリッド構造を備えるステップと、プラズマ発生ガスを上部サブチャンバに流すステップと、上部サブチャンバ内で、プラズマ発生ガスから、第1の電子密度を有する第1のプラズマを発生させ、下部サブチャンバ内で、第2のプラズマを発生させるステップであって、第2のプラズマが、第1の電子密度の約10分の1未満の第2の電子密度を有するイオン-イオンプラズマであるステップと、第2のプラズマを用いて基板を処理して、ソースドレインリセスエッティング、F i n F E T ゲートエッティング、ダミーポリシリコン除去、シャロートレンチ・アイソレーション・エッティング、またはフォトレジスト・リフローでのステップを行うステップとを含む方法が提供される。10

【 0 0 0 8 】

特定の実施形態では、第1のプラズマが、約2eV以上の第1の電子温度を有することがあり、第2のプラズマが、約1eV以下の第2の実効電子温度を有することがある。第2の電子密度は、約 $5 \times 10^9 \text{ cm}^{-3}$ 以下でよい。一部の実施形態では、第2のプラズマ中の負イオン：正イオンの比が、約0.5~1の間であることがある。20

【 0 0 0 9 】

この方法は、ソースドレインリセスエッティングを行うために行われることがある。ソースドレインリセスエッティングは、垂直エッティングフィーチャを形成するために、基板を垂直方向にエッティングするために第1のエッティングプロセスを行うステップと、垂直エッティングフィーチャの内部で基板を水平方向にエッティングするために、第2のエッティングプロセスを行うステップと、垂直エッティングフィーチャ内部に酸化層を形成するために、酸化プロセスを行うステップと、垂直エッティングフィーチャ内にソースドレインリセスを形成するために上記の方法を繰り返すステップとを含むことがあり、第1のエッティングプロセス、第2のエッティングプロセス、および酸化プロセスがすべて、グリッド構造を有する反応チャンバ内で行われ、それにより、各プロセスでの第2のプラズマが、イオン-イオンプラズマとなる。第1のエッティングプロセスは、C<sub>1</sub><sub>2</sub>を含む第1のプラズマ発生ガスを用いて行われることがあり、第2のエッティングプロセスは、N<sub>F</sub><sub>3</sub>およびC<sub>1</sub><sub>2</sub>を含む第2のプラズマ発生ガスを用いて行われることがあり、酸化プロセスは、酸素を含む第3のプラズマ発生ガスを用いて行われることがある。この方法は、凹角形状を有する垂直エッティングフィーチャを形成するために繰り返されることがある。30

【 0 0 1 0 】

他の実施形態では、この方法は、シャロートレンチ・アイソレーション・エッティングを行うために行われることがある。この場合、プラズマ発生ガスは、HBrを含むことがあり、基板は、エッティング中に約300~1200Vの間にバイアスされることがある。プラズマ発生ガスは、約50~500sccmの間の流量で流れがある。プラズマ発生ガスは、さらに、C<sub>1</sub><sub>2</sub>を含むことがある。一部の実施形態では、エッティングプロセスが、少なくとも第1のフィーチャ形状と第2のフィーチャ形状を同時にエッティングするステップを含み、第1のフィーチャ形状が、約10以上のアスペクト比を有し、第2のフィーチャ形状が、約1以下のアスペクト比を有することがある。エッティング後、第1のフィーチャのエッティング深さが、第2のフィーチャのエッティング深さの少なくとも約95%であることがある。さらに、エッティング後、第1のフィーチャ形状が、少なくとも約88°のエッティングプロファイルを有することがあり、第2のフィーチャ形状が、少なくとも約85°のエッティングプロファイルを有することがある。40

【 0 0 1 1 】

50

いくつかの場合には、この方法は、フォトレジスト・リフロー・プロセスを行うために行われることがある。これらの実施形態では、反応チャンバ内に受け取られる基板は、パターン形成されたフォトレジストを上に有する。フォトレジスト・リフロー・プロセスは、基板上のパターン形成されたフォトレジストをリフローするために、第1のプラズマプロセスを行うステップと、基板上のフット領域内のフォトレジストの一部分を除去するために、第2のプラズマプロセスを行うステップとを含むことがあり、第1のプラズマプロセスと第2のプラズマプロセスがどちらも、グリッドを有する反応チャンバ内で行われ、第1のプラズマプロセスおよび第2のプラズマプロセス中の第2のプラズマが、イオン-イオンプラズマである。第1のプラズマプロセス中のプラズマ発生ガスは、H<sub>2</sub>を含むことがあり、第2のプラズマプロセス中のプラズマ発生ガスは、不活性ガスを含むことがある。不活性ガスは、Arでよい。いくつかの場合には、第1および第2のプラズマプロセス後のパターン形成されたフォトレジストの最終的な高さが、第1および第2のプラズマプロセス前のパターン形成されたフォトレジストの初期高さの少なくとも約50%である。第1および第2のプラズマプロセス後の最終的な線幅粗さは、第1および第2のプラズマプロセス前の初期線幅粗さの約75%以下であることがある。例えば、最終的な線幅粗さは、初期線幅粗さの約65%以下であることがある。

#### 【0012】

開示される実施形態の別の態様では、FinFETゲート領域を画定するために、半製造された集積回路上のポリシリコンをエッチングする方法であって、上にポリシリコンの層を有する基板を反応チャンバ内に受け取るステップであって、反応チャンバが、反応チャンバの内部を、プラズマ発生器の近傍の上部サブチャンバと、基板ホルダの近傍の下部サブチャンバと、に分割するグリッド構造を含むステップと、プラズマ発生ガスを上部サブチャンバに流すステップと、上部サブチャンバ内でプラズマ発生ガスから第1のプラズマを発生させ、下部サブチャンバ内で第2のプラズマを発生させるステップであって、第2のプラズマが、イオン-イオンプラズマであるステップと、基板に提供されたポリシリコン層をエッチングし、それによりFinFETゲート領域を画定するステップとを含む方法が提供される。

#### 【0013】

いくつかの場合には、ポリシリコン層をエッチングし、それによりFinFETゲート領域を画定するステップが、ポリシリコンをエッチングして、完成された集積回路においてFinFETゲートの近傍となる位置にキャビティを形成するステップを含む。マスク層が、ポリシリコン層の上に位置決めされることがあり、このマスク層の厚さは、エッチング中に約10%未満だけ減少することがある。エッチング中の反応チャンバ内の圧力は、約5~20mTorr(約0.667~2.67Pa)の間でよい。いくつかの場合には、エッチング中に、オンフィン領域とオフフィン領域との間のプロファイルローディングが、実質的に存在しない。様々な実施形態で、エッチングされた領域に近いフィンは、エッチング中に凹まされない。

#### 【0014】

ポリシリコン層をエッチングし、それによりFinFETゲート領域を画定するステップは、ポリシリコンをエッチングして、完成された集積回路においてFinFETゲートが配される位置にキャビティを形成するステップを含むことがある。この方法は、HBrを含む第1のプラズマ発生ガスを用いた第1の繰返しと、Cl<sub>2</sub>を含む第2のプラズマ発生ガスを用いた第2の繰返しとで行われることがある。いくつかの場合には、他の化学物質が使用されることもある。様々な実施形態において、第1のプラズマ発生ガスと第2のプラズマ発生ガスはどちらも、実質的に酸素含有反応物を含まない。反応チャンバ内の圧力は、第1の繰返し中には約20~80mTorr(約2.67~10.7Pa)の間でよく、第2の繰返し中には約4~80mTorr(約0.533~10.7Pa)の間でよい。異なるフィーチャ密度で配されたエッチングされたフィーチャの間のエッチングプロファイル・ローディングは、実質的に存在しないことがある。

#### 【0015】

10

20

30

40

50

様々な実施形態で、第2のプラズマでの実効電子温度は、約1eV以下であり、第1のプラズマでの実効電子温度未満であることがある。さらに、第2のプラズマでの電子密度は、約 $5 \times 10^9 \text{ cm}^{-3}$ 以下であり、第1のプラズマ内での電子密度よりも小さいことがある。特定の実施形態において、グリッド構造は、2つ以上のグリッドを含み、グリッドの少なくとも1つが、他のものに対して移動可能であることがある。

【0016】

これらおよび他の特徴について、関連する図面を参照して以下で説明する。

【図面の簡単な説明】

【0017】

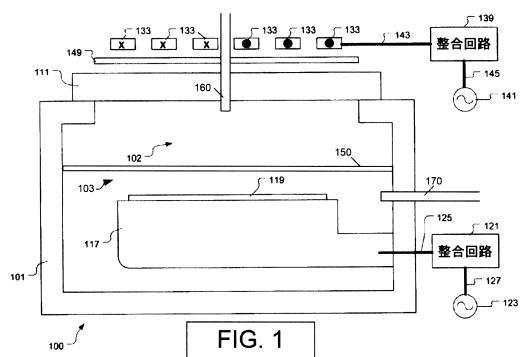

【図1】図1は、本明細書で開示するいくつかの実施形態により、エッチング工程で使用されるプラズマ処理システムを示す断面模式図である。 10

【0018】

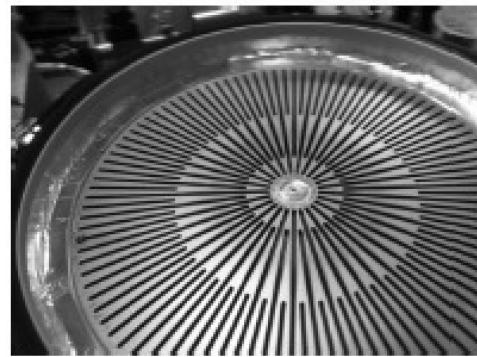

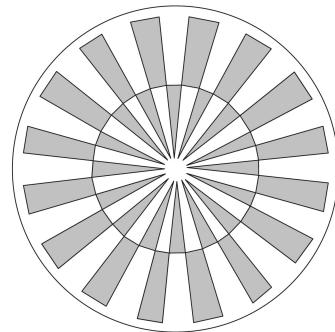

【図2A】図2Aは、本明細書で開示するいくつかの実施形態によるグリッド構造の簡略上視図である。

【0019】

【図2B】図2Bは、本明細書で記載するいくつかの実施形態によるグリッド構造の写真である。

【0020】

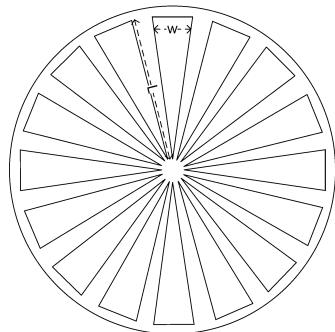

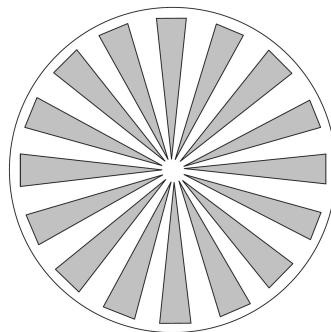

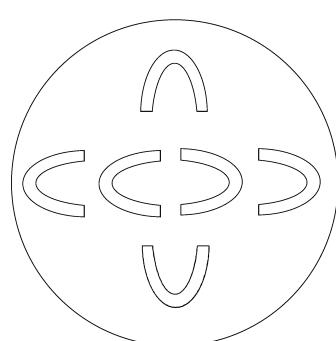

【図3A】図3Aおよび3Bは、下部サブチャンバにおけるプラズマ条件を径方向に調整するために用いることができる一対のプラズマグリッドを示している。 20

【図3B】図3Aおよび3Bは、下部サブチャンバにおけるプラズマ条件を径方向に調整するために用いることができる一対のプラズマグリッドを示している。

【0021】

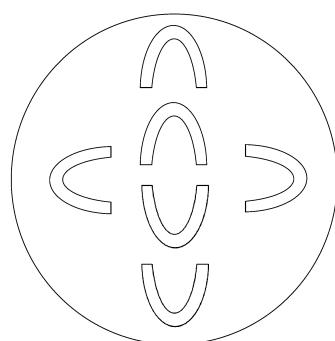

【図3C】図3Cおよび3Dは、本明細書で記載する一実施形態によるC形スロットを有する一対のプラズマグリッドを示している。

【図3D】図3Cおよび3Dは、本明細書で記載する一実施形態によるC形スロットを有する一対のプラズマグリッドを示している。

【0022】

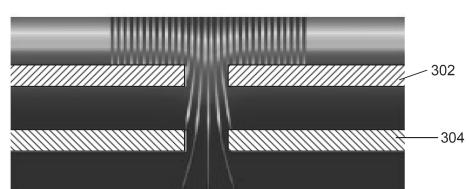

【図3E】図3Eおよび3Fは、回転可能なグリッドのアーチャを通るイオンの軌跡を示している。 30

【図3F】図3Eおよび3Fは、回転可能なグリッドのアーチャを通るイオンの軌跡を示している。

【0023】

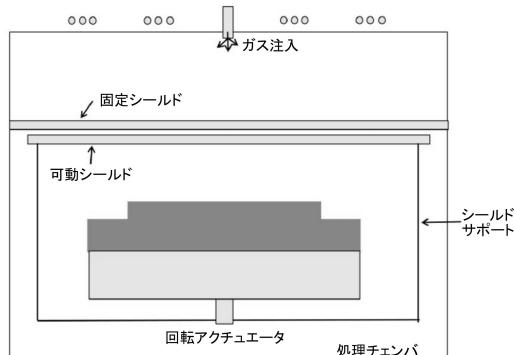

【図4】図4は、本明細書で記載する一実施形態により、可動プラズマグリッドの上方に配置される固定プラズマグリッドを有する処理チャンバの簡略図を示している。

【0024】

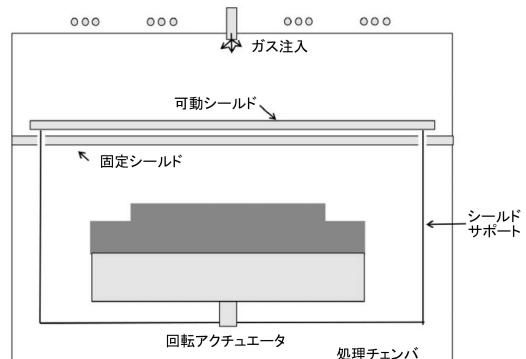

【図5】図5は、本明細書で記載する一実施形態により、固定プラズマグリッドの上方に可動プラズマグリッドを有する処理チャンバの簡略図を示している。

【0025】

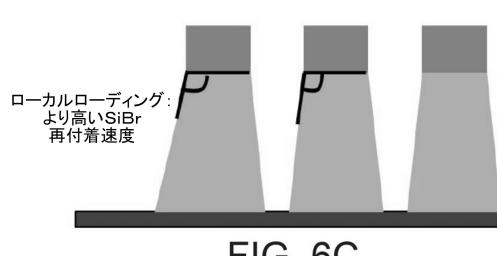

【図6A】図6A～6Cは、エッチング副生成物の解離によって生じるいくつかの問題を示している。 40

【図6B】図6A～6Cは、エッチング副生成物の解離によって生じるいくつかの問題を示している。

【図6C】図6A～6Cは、エッチング副生成物の解離によって生じるいくつかの問題を示している。

【0026】

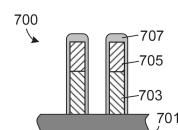

【図7A】図7A～7Cは、ソース・ドレインリソスエッチング中に基板にエッチングすることができる様々な形状をまとめて示している。

【図7B】図7A～7Cは、ソース・ドレインリソスエッチング中に基板にエッチングすることができる様々な形状をまとめて示している。 50

【図 7 C】図 7 A ~ 7 C は、ソース - ドレインリソスエッチング中に基板にエッチングすることができる様々な形状をまとめて示している。

【0027】

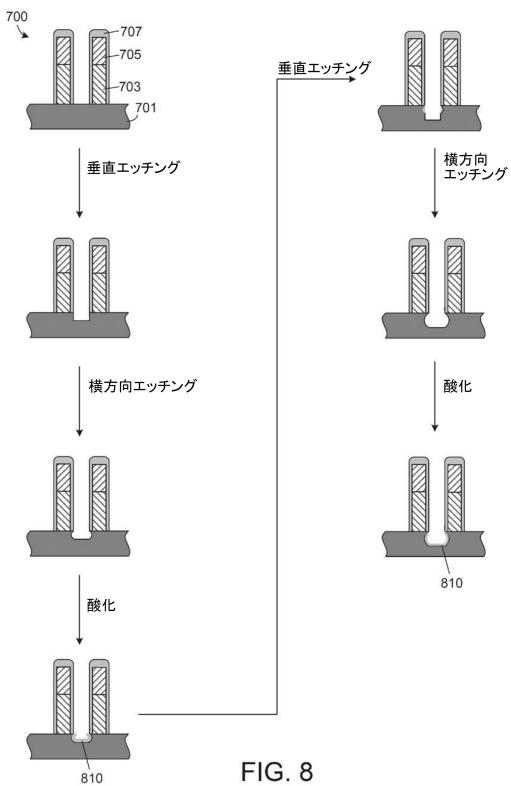

【図 8】図 8 は、ソース - ドレインリセスエッチング中の様々なエッチングおよび酸化段階を受けたときの基板を示している。

【0028】

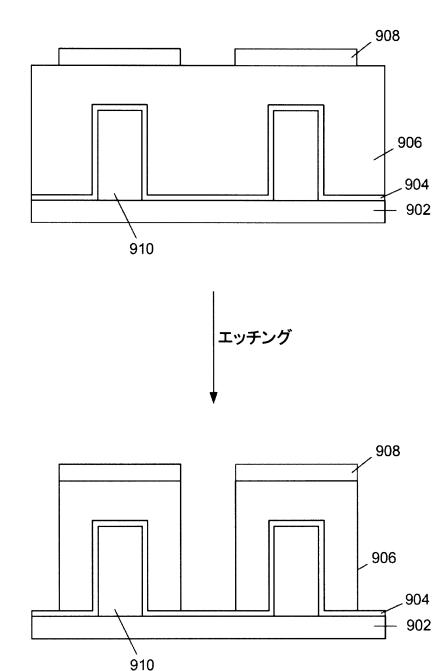

【図 9】図 9 は、FinFET ポリシリコンゲートエッチングを受けたときの、半製造された半導体デバイスを示している。

【0029】

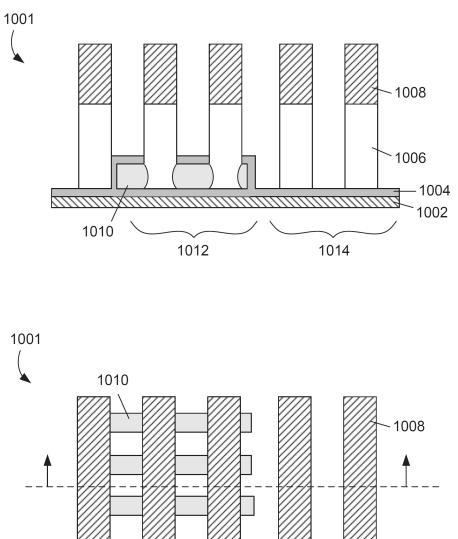

【図 10】図 10 は、FinFET ポリシリコンゲートエッチング後の、半製造された半導体デバイスの断面図および上面図を示している。

【0030】

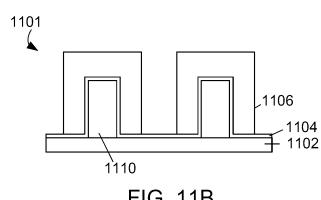

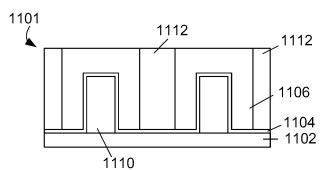

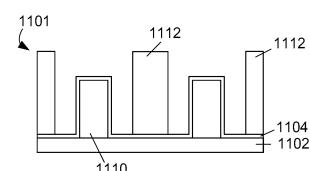

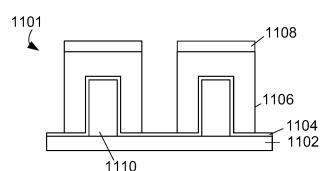

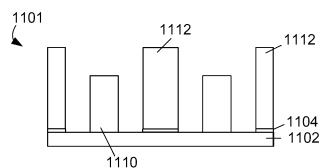

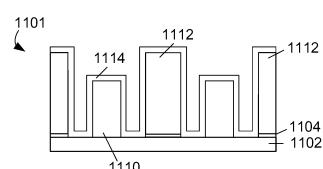

【図 11 A】図 11 A ~ 11 G は、ダミーポリシリコン除去プロセス中を含めた、様々な製造段階中の、半製造された半導体デバイスの断面図を示している。

【図 11 B】図 11 A ~ 11 G は、ダミーポリシリコン除去プロセス中を含めた、様々な製造段階中の、半製造された半導体デバイスの断面図を示している。

【図 11 C】図 11 A ~ 11 G は、ダミーポリシリコン除去プロセス中を含めた、様々な製造段階中の、半製造された半導体デバイスの断面図を示している。

【図 11 D】図 11 A ~ 11 G は、ダミーポリシリコン除去プロセス中を含めた、様々な製造段階中の、半製造された半導体デバイスの断面図を示している。

【図 11 E】図 11 A ~ 11 G は、ダミーポリシリコン除去プロセス中を含めた、様々な製造段階中の、半製造された半導体デバイスの断面図を示している。

【図 11 F】図 11 A ~ 11 G は、ダミーポリシリコン除去プロセス中を含めた、様々な製造段階中の、半製造された半導体デバイスの断面図を示している。

【図 11 G】図 11 A ~ 11 G は、ダミーポリシリコン除去プロセス中を含めた、様々な製造段階中の、半製造された半導体デバイスの断面図を示している。

【0031】

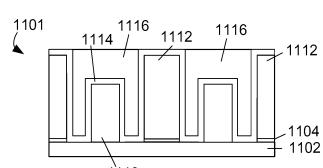

【図 12】図 12 は、イオン - イオンプラズマおよび従来のプラズマに関する電子エネルギー分布関数を示している。

【0032】

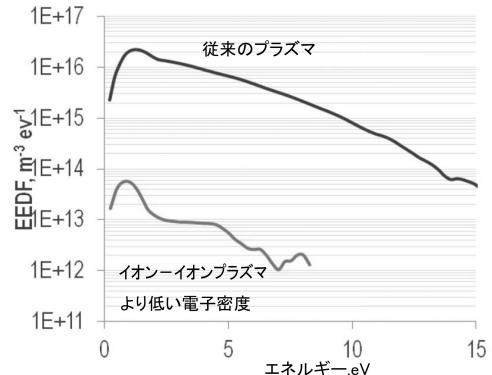

【図 13】図 13 は、フォトレジスト・リフロープロセス中の、上にフォトレジストを有する基板を示している。

【0033】

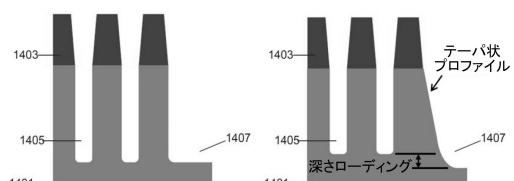

【図 14】図 14 は、シャロートレンチアイソレーションプロセス中にエッチングされた基板に関する様々なエッチングプロファイルを示している。

【0034】

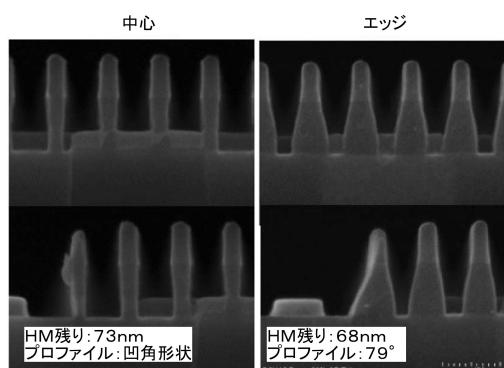

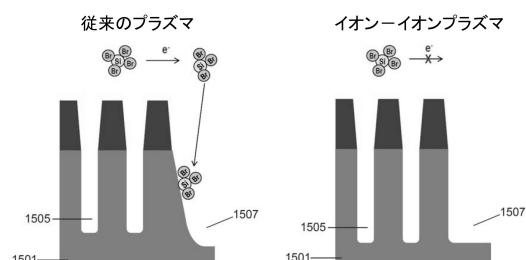

【図 15】図 15 は、従来のプラズマを使用して、およびイオン - イオンプラズマを使用して、シャロートレンチアイソレーションプロセス中に実現されるエッチングプロファイルを示している。

【0035】

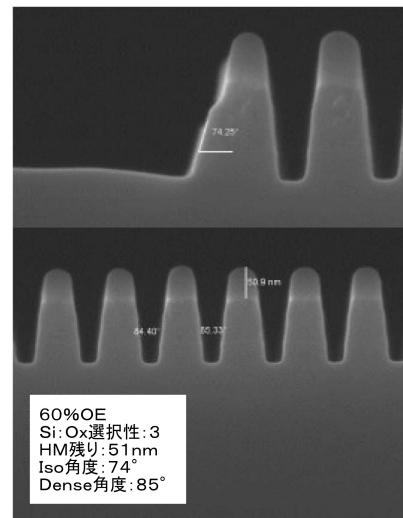

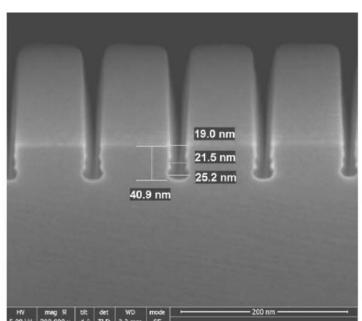

【図 16 A】図 16 A および 16 B は、高圧の従来の技法に従って (16 A)、およびプラズマグリッドを使用する一実施形態に従って (16 B) エッチングした FinFET 構造の SEM 像を示している。

【図 16 B】図 16 A および 16 B は、高圧の従来の技法に従って (16 A)、およびプラズマグリッドを使用する一実施形態に従って (16 B) エッチングした FinFET 構造の SEM 像を示している。

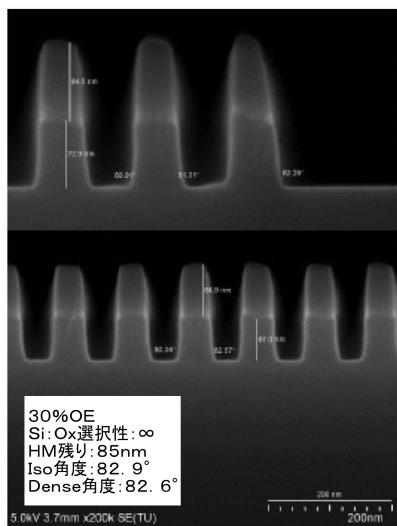

【0036】

【図 17 A】図 17 A および 17 B は、低圧の従来の技法に従って (17 A)、およびプラズマグリッドを使用する本明細書で開示される実施形態に従って (17 B) エッチングしたフィーチャの SEM 像を示している。

10

20

30

40

50

【図17B】図17Aおよび17Bは、低圧の従来の技法に従って(17A)、およびプラズマグリッドを使用する本明細書で開示される実施形態に従って(17B)エッティングしたフィーチャのSEM像を示している。

【0037】

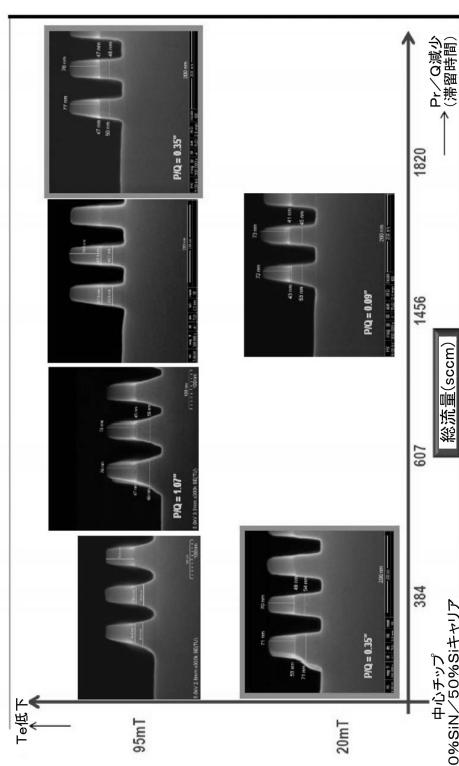

【図18】図18は、プラズマグリッドを使用せずに、様々なレジームに従ってエッティングしたフィーチャの様々なSEM像を示している。

【0038】

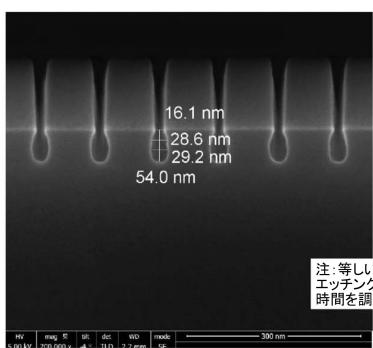

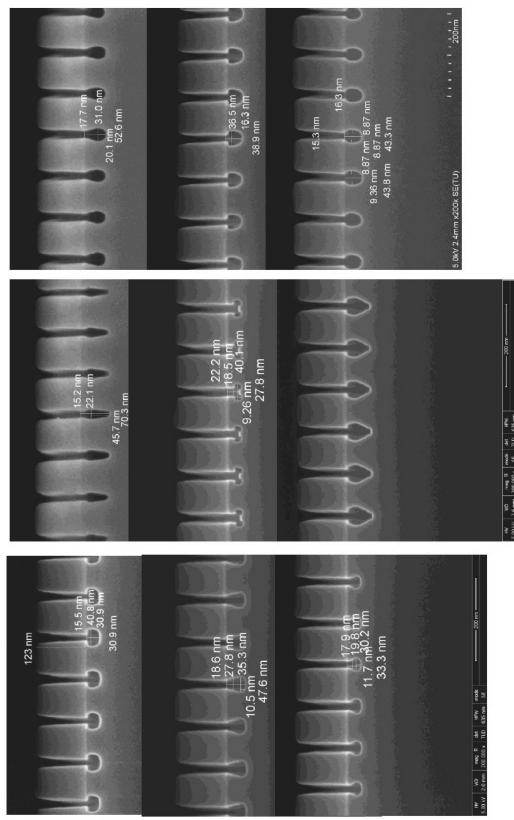

【図19】図19は、ソース-ドレインリセスエッティング中の、従来のプラズマおよびイオン-イオンプラズマを用いて実現される様々なエッティング形状を示している。

【0039】

【図20】図20は、ソース-ドレインリセスエッティングプロセス中に実現される様々なエッティング形状を示している。

【0040】

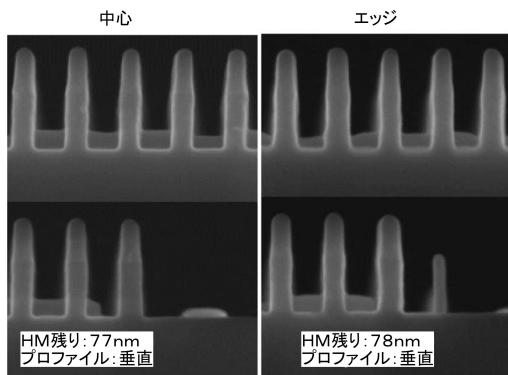

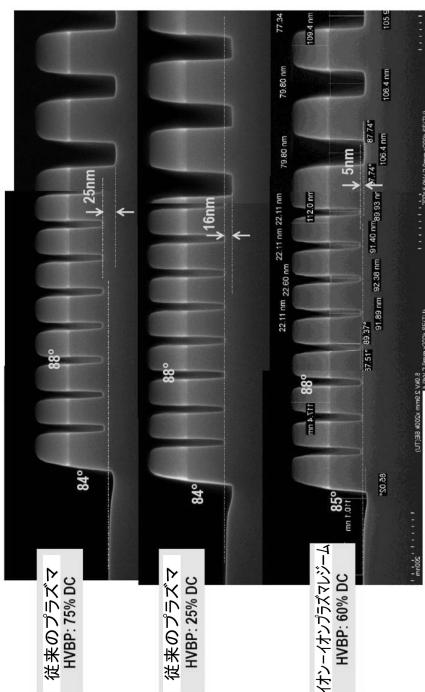

【図21】図21は、従来のプラズマレジームおよびイオン-イオンプラズマレジームで実行されるシャロートレンチアイソレーションプロセスに関するエッティングプロファイルおよびローディングの効果を示している。

【発明を実施するための形態】

【0041】

本出願において、「半導体ウェハ」、「ウェハ」、「基板」、「ウェハ基板」、および「半製品の集積回路」という用語は、区別なく用いられる。「半製品の集積回路」という用語が、集積回路がその上に作製される多くの段階のいずれかにおける半導体ウェハ上のデバイスを指し得ることは、当業者であれば理解できるであろう。以下の詳細な説明では、本発明がウェハ上で実施されることを想定している。ただし、本発明はこれに限定されない。ワーカピースは、様々な形状、サイズ、材質のものであり得る。

【0042】

以下の説明では、提示する実施形態についての完全な理解を与えるため、様々な具体的な詳細について記載する。開示する実施形態は、それら特定の詳細の一部または全部がなくても実施することができる。また、開示する実施形態を必要に不明瞭にすることがないよう、周知の工程処理については詳細に記載していない。開示する実施形態は、具体的な実施形態に関連させて説明されるが、当然のことながら、開示する実施形態を限定するものではない。

【0043】

開示するのは、半導体デバイスの製造において半導体基板およびその上に形成された層のエッティングに用いられる装置である。装置は、エッティングが実施されるチャンバによって画成される。一部の実施形態では、チャンバは、平面窓と、略平面状の励起コイルと、エッティング中に半導体基板を保持するためのペデスタルまたはチャックと、を備える。当然のことながら、本開示は、特定のタイプのプラズマ源に限定されない。平面状の励起コイルの他に、ドーム型および平板型のプラズマ源を採用することができる。プラズマ源には、誘導結合プラズマ( ICP )源、容量結合プラズマ( CCP )源、ならびにその他、当業者に周知のものが含まれる。本明細書で記載する実施形態では、チャンバ内に配置されて、チャンバを2つのサブチャンバに分割するグリッドを利用する。いくつかの実施形態において、「グリッドアセンブリ」と呼ばれることがある2つ以上のグリッドからなる積層群が用いられる。作動中には、サブチャンバはそれぞれ、異なる特性のプラズマを収容している。プラズマは、主として、または専ら、上部サブチャンバにおいて生成され、一部の種は、影響なくグリッドもしくはグリッドアセンブリを通り抜けて、下部サブチャンバに入ることができる。グリッドは、グリッドの厚さを貫通したスロットを有する。いくつかの実現形態では、これらのスロットは、略径方向外向きに延びている。本明細書で用いられる場合の「略径方向外向きに延びる」とは、その説明される特徴部が、少なくともある程度、径方向に向いた成分を有することを意味する。つまり、その特徴部の一部が、略中心からエッジへの方向に延びていればよく、特徴部全体が、すべて径方向に向いて

10

20

30

40

50

いる必要はない。また、「中心からエッジへの方向」は、中心からエッジへの真の方向の周囲のある角度範囲（例えば、中心からエッジへの真の方向の約20°の範囲内）を含むものと定義される。

#### 【0044】

グリッドもしくはグリッドアセンブリは、グリッドの厚さを貫通した複数の径方向スロットを含むことができる。グリッドおよびスロットは、上部サブチャンバ内のほんの一部の高エネルギー電子のみがグリッドを通過し得るように設計されている。一般に、より高エネルギーの電子は、集合的に、グリッドを通過して下部サブチャンバに入るときに、より低エネルギーの「より低温の」電子になる。高エネルギー電子は、グリッドを通過するのに十分なエネルギーを有し得るもの、それらの多くは、グリッドと衝突する角度でグリッドに接近して、エネルギーを損失する。実際にグリッドを通り抜ける高エネルギー電子は、励起源から既に切り離されているため、集合的に、グリッドの下でプラズマを維持するのに十分なエネルギーを持たない。高温電子が下部チャンバで低温となるメカニズムには、グリッドとの衝突と、グリッドの下での中性種との衝突と、グリッドの下の電子がグリッドの上方の励起源から遮蔽されることと、が含まれる。このようにして、グリッドにより、下部サブチャンバにおいて、低電子密度( $n_e$ )および低平均実効電子温度( $T_e$ )を有するプラズマを生成することができる。グリッドもしくはグリッドアセンブリの上方では、一般に、プラズマは、通常の電子イオンプラズマであり、その中の負に帯電した種のうち極めて多くの部分が電子である。グリッドもしくはグリッドアセンブリの下方では、プラズマは、はるかに高い割合で負イオンを含み、実際には、イオンイオンプラズマであり得る。イオンイオンプラズマのいくつかの特性については、後述する。大まかには、イオンイオンプラズマは、電子イオンプラズマと比較して、負に帯電した種として（電子よりも）イオンを、はるかに高い割合で含むものである。

10

#### 【0045】

##### [反応器内のグリッドの位置]

グリッドもしくはグリッドアセンブリは、プラズマチャンバ内に配置されて、これにより、チャンバを上部サブチャンバと下部サブチャンバとに分割している。本明細書で記載するようなグリッドを備えるように改良するのに適したチャンバの一例は、カリフォルニア州フリーモントのラムリサーチ社（Lam Research Corporation）による反応器Kiyoである。文脈として、以下の説明では図1を参照することを想定することができ、これについてはさらに後述する。いくつかの実現形態において、グリッドは、反応チャンバの内部底面の上方、約1～6インチの間に、またはペデスタルなどの基板支持部の上方、約1～6インチの間（例えば、約1.5～3インチの間）に配置される。これらまたは他の実現形態において、グリッドは、反応チャンバの内部天井の下方、約1～6インチの間（例えば、約1.5～3インチの間）に配置することができる。多くの場合、天井には、誘電体窓が装備されている。

20

#### 【0046】

一部の実施形態では、上部サブチャンバと下部サブチャンバの高さは、略同じ（例えば、約5%以内）であり、一方、他の実施形態では、それらの高さは、より顕著に異なり得る。サブチャンバ高さ比とも呼ばれる、下部チャンバの高さに対する上部チャンバの高さの比率( $h_u/h_l$ )は、約0.1～1.0の間、または約0.2～5の間とすることができる。いくつかの実施形態において、サブチャンバ高さ比は、約1/6よりも大きい。

30

#### 【0047】

グリッドは、ウェハに近すぎると、ウェハ面にグリッドの跡が生じる原因となり得るので、そのように配置されてはならない。すなわち、処理後のウェハ面に、望ましくないグリッドのスロットパターンが生じて、基板表面上で深刻なエッチング不均一性を引き起こすことがある。多くの応用において、基板の頂面からグリッドまでの離間距離が少なくとも約1インチであると十分である。

40

#### 【0048】

##### [グリッド設計]

50

グリッドを実現するために、様々な設計を採用することができる。いくつかの実施形態では、グリッドは、比較的単純な薄板材であって、一部の電子が上部サブチャンバから下部サブチャンバへ通過することを可能にするスロット、略円形の孔、または他の穿孔部を有する。他の実施形態では、グリッドは、より複雑な、複数の構成要素を有するグリッドアセンブリで構成することができる。例えば、グリッドアセンブリは、複数のグリッド、支持要素、および／または駆動要素を有することができる。

#### 【0049】

単純な実装形態では、グリッドは、スロットを有する比較的薄い板である。加えて、一部の実施形態では、グリッドは、孔を有することができる。この場合、グリッドは、孔とスロットとを併せて有する。グリッド構造の非限定的な例を、図2A、2Bおよび3A～3Dに示している。グリッドに含まれる材料は、絶縁体、導体、またはそれらの組み合わせとすることができます。いくつかの実現形態において、グリッドは1つ以上の材料を含み、それらの材料には、限定するものではないが、金属と、ステンレス鋼、アルミニウム、チタンなどの金属合金と、セラミック、シリコン、炭化ケイ素、窒化ケイ素、およびそれらの組み合わせが含まれる。材料は、例えば耐食性のための陽極酸化または他の不動態化が施されても、または施されていないものであってもよい。一実施形態において、グリッドは、セラミックコーティングを有する金属材料で構成される。他のコーティングを用いることもできる。コーティングされたグリッドを用いることは、特に被エッチング層が揮発性である場合に有効である。いくつかの実現形態において、グリッドは、純粋なコーティングで被覆することができ、それには、例えば、 $Y_2O_3$ 、 $YF_3$ 、 $YAG$ 、窒化チタン、または $CeO_2$ のコーティングが含まれるが、ただし、これらに限定されない。また、グリッドは、接地するか、フローティングとするか、またはバイアスすることができる。いくつかの実現形態において、接地されたグリッドは、陰極の拡張バイアス電流帰路として機能する。

10

#### 【0050】

グリッドは、一般に、チャンバの水平断面全体に及ぶものである。チャンバが（上から見て）円形である場合、グリッドも円形となる。これによって、グリッドは、反応チャンバを2つのサブチャンバに効果的に分割することができる。いくつかの設計において、グリッドの円形形状は、典型的には円形ウェハである基板のジオメトリによって規定される。周知のように、ウェハは、一般に、200mm、300mm、450mmなど、様々なサイズで提供される。正方形もしくは他の多角形の基板、またはより小さな基板の場合には、チャンバ内で実施されるエッチング工程に応じて、他の形状が可能である。この場合、グリッドの断面は、様々な形状およびサイズとすることができます。平坦な平面状のグリッド断面は、一部の実施形態には適している。しかしながら、他の実施形態では、皿状、ドーム状、周期的形状（例えば、正弦波形状、矩形波形状、山形状）、傾斜状などのグリッド断面が適切である。これらの断面形状のいずれかを貫通したスロットまたは孔は、（本明細書の別項に記載するようなアスペクト比を含む）特性を有することになる。

20

#### 【0051】

グリッドは、平均して、約1～50mmの間の厚さ、好ましくは約5～20mmの間の厚さとすることができます。グリッドは、厚すぎると、適正に機能しない場合がある（例えば、通過を阻まれる種が多すぎること、質量が大きすぎること、反応チャンバで占めるスペースが大きすぎること、などがある）。グリッドは、薄すぎると、プラズマ処理に耐えることができない場合があり、かなり頻繁な交換が必要となり得る。一般に、スロットの高さはグリッドの厚さによって決まるので、グリッドの厚さは、後述するように、グリッドにおけるスロットの所望のアスペクト比によっても制限される。

30

#### 【0052】

一部の実施形態において、グリッドは、上流プラズマと下流プラズマとの間の分離器として機能し、この場合、下流プラズマは、下部サブチャンバ内にあって、ラジカルリッチとなり得る。このように、グリッドを装備したプラズマチャンバによって、現在はカリфорニア州フリーモントのラムリサーチ社であるノベラスシステムズ社（Novel

40

50

s Systems) から入手可能な GAMMA (登録商標) プラットフォームツールなどの既存のリモートプラズマ・ツールで達成されるのと同様の結果を得ることができる。この目的で機能させる場合には、グリッドは、比較的厚く、例えば約 20 ~ 50 mm 厚とすることができる。

#### 【0053】

いくつかの実施形態において、グリッドは、長くて薄い形状のスロットを有する。スロットは、グリッドの中心から径方向外向きに延びている。スロットは、高さ、幅、および長さを有する（幅と長さを、図 2A においてラベルで明示している）。スロット高さは、グリッド面に垂直な軸に沿って測定され（すなわち、スロット高さは、ほとんどの作動構成において垂直な向きとなる）、この高さは、グリッドの厚さに略等しい。スロットの幅は、スロットの径方向範囲にわたって可変または一定とすることができます。いくつかの例において、スロットは、扇形と（すなわち、グリッドの中心に向かってより薄く、エッジに向かってより厚く）することができます。いくつかの実施形態において、スロットは、その長さ方向がグリッドの中心から外向きに（すなわち、径方向に）延びている。いくつかの実施形態において、スロット幅は、約 25 mm 以下である。スロットの長さは、グリッドの方位角方向範囲の周りで可変または一定することができます。径方向スロットの分離角は、グリッドの周りで可変または一定することができます。

#### 【0054】

もしグリッドにスロットがない場合には、プラズマ生成中に、グリッドに電流が誘導されることになる。この電流は、グリッドの周りに略環状に流れるか、または局所渦電流を形成し、そして、電力消費が増加することになる。ところが、スロットがあることによって、そのような寄生電流の発生が防止され、これにより電力が節約されて、その結果、より効率的なプロセスとなる。略円形の孔などのような形状の開口部は、このような電流の発生を防ぐ効果が比較的低い。そこで、上述のように、円形開口部は、スロット状開口部と併せて用いることができる。

#### 【0055】

スロットのアスペクト比は、スロットの幅に対するその高さの比 (h / w) と定義される。通常、このアスペクト比のジオメトリは、スロットの長さ方向（多くの場合、径方向）に垂直な断面として見ることができます。スロットの幅は可変とすることができますので、アスペクト比は、同様に可変とすることができます。いくつかの実施形態において、（グリッド全体にわたって可変または一定とすることができます）スロットのアスペクト比は、約 0.01 ~ 5 の間、または約 0.3 ~ 5 の間、または約 1 ~ 4 の間、または約 0.5 ~ 2 の間である。多くの実施形態では、このようなアスペクト比を有するグリッドによって、上部サブチャンバと比較して、下部サブチャンバにおける電子密度および実効電子温度を低下させる。上述のように、電子がスロットを通過する際に、多くの高温電子がグリッドに衝突することを少なくとも一因として、実効電子温度が低下すると考えられる。また、下部サブチャンバの電子はグリッドによって遮蔽されることで、プラズマコイル（または他のプラズマ源）からの誘導加熱を受けないため、下部サブチャンバにおける実効電子温度は、上部サブチャンバと比較して低下する。

#### 【0056】

孔をスロットと共に用いる場合には、孔は、スロットと同じ目的を果たすことができる。従って、それらは、通常、上記のようなアスペクト比を有する。いくつかの実施形態において、孔は、約 0.05 インチ ~ 約 0.2 インチの範囲の直径を有する。それらは、グリッドの厚さ全体を貫通している。

#### 【0057】

グリッドにより得られる更なる効果は、メイン注入器からの対流効果を緩和することができることである。これによって、ウェハ面へのガス流を、より均一とすることが可能である。ウェハと上部チャンバ内のガス注入器（複数の場合もある）との間にグリッドもしくはグリッドアセンブリがあることによって、グリッドがガス流を妨げることで、ウェハ上で、より拡散性の高いフローレジームが得られるので、ガス注入器から送出されるガス

10

20

30

40

50

の対流の影響を著しく軽減することが可能である。

【0058】

一部の実施形態では、グリッドは、ガス吐出孔を含んでいる。このような実施形態では、グリッドは、上部サブチャンバおよび／または下部サブチャンバのためのシャワーヘッドであるという付加的な目的を果たすことができる。このような実施形態では、1つ以上のグリッドに、1つ以上のチャネルを含むことができる。これらのチャネルに、注入口（または複数の注入口）からガスを供給して、そのガスをグリッド（複数の場合もある）の複数の出口孔に送ることができる。出口孔は、上部サブチャンバおよび下部サブチャンバのいずれかまたは両方に処理ガスを送出するガス分配シャワーヘッドを形成することができる。

10

【0059】

いくつかの実現形態において、グリッドは、グリッドを貫通してプロービング装置を配置することを可能にする特徴部を含む中心領域などの領域を有する。プロービング装置は、作動中のプラズマ処理システムに関連するプロセスパラメータをプローブするために設けることができる。プロービングプロセスには、発光終点検出、干渉法による終点検出、プラズマ密度測定、イオン密度測定、および他の計量プロービング操作を含むことができる。一部の実施形態では、グリッドの中心領域は、開口している。他の実施形態では、グリッドの中心領域は、光がグリッドを透過することを可能とするため、光学的に透明な材料（例えば、石英、サファイアなど）を含んでいる。

【0060】

いくつかの実施形態では、300mmウェハ用エッチャの場合に、グリッドの外縁付近で約15mm～40mm毎に、グリッドにスロットを有することが好ましい場合がある。これは、方位隣接スロットが、それぞれ約18°または約48°で隔てられていることに相当する。このように、いくつかの実施形態において、方位隣接スロットは、少なくとも約10°または少なくとも約15°で隔てられている。これらまたは他の実施形態において、方位隣接スロットは、約40°以下、または約50°以下、または約60°以下で隔てられている。

20

【0061】

一部の実施形態では、プラズマグリッドは、グリッドに埋め込まれた冷却チャネルを有することができ、これらの冷却チャネルは、流動性または非流動性の冷却材で満たすことができる。いくつかの実施形態において、冷却材は、ヘリウムもしくは他の不活性ガス、またはDI水、プロセス冷却水、フロリナートなどの液体といった流体、あるいはパーフルオロカーボン、ハイドロフルオロカーボン、アンモニア、CO<sub>2</sub>などの冷媒である。これらまたは他の実施形態において、プラズマグリッドは、埋め込まれた発熱体および／または温度測定装置を有することができる。冷却チャネルと埋め込みヒータとによって正確な温度制御を可能とし、これにより、粒子および壁の条件に対する精密制御が可能となる。このような制御は、一部の例において、下部ゾーン・プラズマにおける条件を調整するために用いることができる。例えば、プラズマグリッドがより低い温度に維持される場合には、ウェハからのエッチング副生成物をグリッドに選択的に沈着させて、これにより、下部サブチャンバにおけるエッチング副生成物の気相密度を抑える。あるいは、グリッドもしくはグリッドアセンブリを高温（例えば、80°超）に維持することができ、これにより、グリッドへの沈着を抑えて、チャンバを比較的清浄に保つことができるようにし、さらに／またはウェハレス自動クリーニング（WAC：Waferless Auto Clean）でチャンバをクリーニングするのに要する時間を削減できるようにする。

30

【0062】

いくつかの実施形態に含まれ得る他の特徴は、グリッドが、上部サブチャンバおよび下部サブチャンバのいずれかまたは両方に對して、処理ガスを送出するためのシャワーヘッドとして機能し得るということである。この場合、グリッドは、ガス供給源を上部サブチャンバおよび／または下部サブチャンバに接続する複数のチャネルを含むことができる。シャワーヘッド孔は、サブチャンバ内へのガス送出が均一となるように配置することができる。

40

50

きる。

【0063】

また、一部の実施形態では、複数のガス供給源が用いられる。例えば、(1つまたは複数のシャワー・ヘッド型グリッドによるか、または他のガス送出手段によるか、いずれかにより)上部サブチャンバと下部サブチャンバに、異なる処理ガスを送出することができる。具体的な実現形態では、不活性ガスが上部サブチャンバに送出され、プラズマエッティング化学物質が下部サブチャンバに送出される。他のいくつかの実施形態では、上部サブチャンバに送出されるガスは、H<sub>2</sub>、N<sub>2</sub>、O<sub>2</sub>、N F<sub>3</sub>、またはC<sub>4</sub>F<sub>8</sub>もしくは他のフルオロカーボンであるが、ただし、実施形態はこのように限定されない。これらまたは他の実現形態において、下部サブチャンバに送出されるガスは、N<sub>2</sub>、CO<sub>2</sub>、またはCF<sub>4</sub>もしくは他のフルオロカーボンとすることができますが、ただし、先と同じく実施形態はこのように限定されない。10

【0064】

場合によっては、ワーク基板に隣接するプラズマ条件を幅広く可能とするプラズマ処理反応器を用いることが、有用である。そのような条件には、プラズマ密度、プラズマの実効電子温度、およびプラズマ中のイオンに対する電子の比率が含まれる。in situ処理では、チャンバ内で複数の層が処理されている場合に、それぞれの層の処理条件に変更することが必要となり得る。位置固定されたグリッドによって、反応器の動作ウィンドウが制限される場合があり、例えば、下部サブチャンバでイオンイオンプラズマを発生させるようにグリッドが最適化されると、高プラズマ密度が実現可能とならないことがある。そこで、一部の実施形態では、回転および/または並進により照準開口領域のグリッド線を調整可能なグリッドおよびグリッドアセンブリを設ける。20

【0065】

一部の実施形態では、プラズマグリッドを、プラズマコイルまたは他のプラズマ源に対して上昇または下降させることができる。これは、例えば、可動ステージ上にグリッドを取り付けることによって実現することができる。いくつかの実現形態において、この上下移動により、オペレータまたはコントローラは、上部ゾーン・プラズマおよび下部ゾーン・プラズマにおける実効電子温度、電子密度またはプラズマ密度、イオンに対する電子の比率、ラジカル濃度などを変更することができます。また、ラジカル濃度は、プラズマグリッドの高さの影響を受けるので、可動プラズマグリッドを用いることにより、多段階プロセス全体にわたってラジカル濃度を調整できるプロセスが可能となる。ラジカル種は化学反応性が高く、負イオンは電子と異なるエッティング特性を有するので、このパラメータは、所望の反応を得るように調整/制御するのに、特に有用である。30

【0066】

また、いくつかの実現形態において、反応チャンバ内で、複数のプラズマグリッドを単一のグリッドアセンブリで用いることができる。複数のグリッドを用いる場合のグリッド数は、典型的には約2~5の間である。複数のプラズマグリッドを用いる場合には、プラズマグリッドのうち少なくとも1つを、他のプラズマグリッドの少なくとも1つに対して可動とすることが多い。一般に、そのような動きは、グリッドを回転させるか、または引き離すか、いずれかによって達成される(場合によっては、両タイプの動きが用いられる)。グリッドアセンブリにおいて回転可能グリッドを用いることで、異なるプロセス/ウェハ間と、単一のプロセス/ウェハでそのウェハを処理する過程内と、その両方で、グリッド開口面積を変更することが容易に可能となる。重要なことは、下部サブチャンバにおける実効電子温度および電子密度は、グリッド開口面積に依存するということである。40

【0067】

複数のグリッドを用いる場合には、いくつかの追加パラメータを規定すると有用である。アセンブリ・スロットまたは他の開口部は、上から見て、1つのグリッドの開口部が他のグリッド(複数の場合もある)の開口部と位置が揃うと、これによって、図3Eに示すように、プラズマグリッドアセンブリを通り抜ける明確な照準線が形成されるような、アセンブリの領域である。グリッドのスロット/孔の位置が揃っていない場合には、図3F50

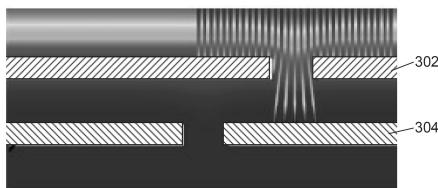

に示すように、グリッドアセンブリを通り抜ける明確な照準線がない。図3Eおよび3Fについて、上側グリッド302が、下側グリッド304の上方に配置されている。グリッド302および304のそれぞれの下の暗い領域は、そこを通って種が移動することができる開放領域である。具体的な実施形態では、下側グリッド304の下の暗い領域は、下部サブチャンバの上側部分である。典型的には、単一のプラズマグリッドアセンブリに、複数のアセンブリ開口部がある。個々のグリッドが相互に動くと、アセンブリ開口部のジオメトリは変化する。例えば、第1のグリッドが第2のグリッドに対して回転すると、アセンブリ・スロットの幅が変化し得る。同様に、グリッドが回転または他の動きを相互にすると、最上グリッドの上面と最下グリッドの底面との間の総距離を照準開口幅で除算したものとして定義されるアセンブリ・スロットのアスペクト比が、変化し得る。いくつかの実施形態において、アセンブリ・スロットのアスペクト比は、約0.1~5の範囲内とすることができる。10

#### 【0068】

グリッドアセンブリ開口面積は、（グリッド面に平行な平面から見て）スロットの位置が揃っている場合のグリッドアセンブリのスロットの総面積と定義される。図3Fに示すようにスロットの位置がずれている場合には、プラズマ中の一部の種（特に、イオンおよび電子などの荷電種）が、下部サブチャンバに移動することは実質的でない。このようにスロットの位置をずらした配置によって、アセンブリにおけるスロットのアスペクト比を効果的に増加させるか、またはスロットの重なりがない場合にはアセンブリ・スロットが完全になくなることで、上部サブチャンバから下部サブチャンバに移動する高温電子の割合を減少させる。一方、図3Eにあるようにスロットの位置が揃っている場合には、上述のようにプラズマ種がスロットを通り抜けることができる。一例では、2つの同一のプラズマグリッドが用いられ、それぞれが約50%の開口（スロット）面積を有する。本例では、グリッドアセンブリ開口面積は、0%（個々のプラズマグリッドを完全にずらした場合）と約50%（個々のプラズマグリッドの位置を正確に揃えた場合）との間で変化し得る。別の例では、それぞれのプラズマグリッドは、約75%の開口面積を有する。この場合、グリッドアセンブリ開口面積は、約50~75%の間で変化し得る。グリッドアセンブリ開口面積を変化させることにより、下部サブチャンバにおけるプラズマ条件を調整することができる。例えば、グリッドアセンブリ開口面積がより大きいと、グリッドアセンブリ開口面積がより小さい場合と比較して、下部ゾーン・プラズマの実効電子温度が高く、下部ゾーン・プラズマの電子密度が高く、下部ゾーン・プラズマ中のイオンに対する電子の比率が高く、下部ゾーン・プラズマ中のラジカル濃度が低い。20

#### 【0069】

複数のグリッドを用いることは、それによって、単一の処理ステーションでウェハ上のプラズマ密度および他のプラズマ条件の広いプロセスウインドウが得られることから、特に効果的である。このような効果は、多層および/または多種の露出材料を有する複雑な構造を処理する場合に、特に有用である。上述のように、処理される各層で処理条件を変更することが、しばしば必要となる。30

#### 【0070】

各プラズマグリッドのスロットパターンは、他のプラズマグリッドのスロットパターンと同じであっても、または異なっていてもよい。また、スロットパターンは、ウェハの特定の領域の上方で開口領域を提供するように設計されていてもよい。例えば、スロットは、ウェハのエッジと比べてウェハの中心付近に、より多くの開口領域があるように（またはその逆に）設計することができる。さらに、スロットは、グリッドアセンブリ開口領域が、プロセスにおける異なる時点でウェハの異なる部分に集中するように設計することができる。例えば、スロットは、グリッドアセンブリ開口領域が、プロセスの開始に向けてウェハの中心付近に集中し、プロセスの終わりに向けてウェハのエッジ付近に集中するように（またはその逆に）設計することができる。このような回転によって、いくつかのパラメータの例として、ガス流、プラズマ密度、プラズマの種類（例えば、イオン・イオン・プラズマ）、および実効電子温度などを、プロセスの過程でウェハの径方向にわたって調40

整することが可能となる。このような調整機能は、ウェハ全面にわたって均一なエッティング結果を得るのに有用となり得るものであり、また、そうでなければ処理の際に生じるような中心からエッジへの不均一性に対処する上で、特に有用となり得るものである。このような径方向の調整効果を得るために、プラズマグリッドアセンブリで用いることができる一対の電子グリッドの一例を、図3A 3Bに示している。これらの図では、スロット（開口領域）を灰色で示し、グリッドの実体部分を白色で示している。

#### 【0071】

引き離し可能なグリッドを用いることで、いくつかの距離を制御および調整することが可能となる。例えば、調整され得る距離には、ウェハと下側グリッドとの間の距離、上部サブチャンバの上端と上側グリッドとの間の距離、および／またはグリッド間の距離が含まれる。これらの可変距離によって、単一の固定グリッドと比較して、ウェハ上方で、より幅広い電子温度およびプラズマ密度の調整が可能となる。

10

#### 【0072】

一部の実現形態では、可動と固定の両方のプラズマグリッドを有するプラズマグリッドアセンブリを利用する。グリッドは、接地するか、または電気的にフロー・ティングとすることができる、また、回転アクチュエータまたはリフタなどの駆動要素に接続された支持脚または他の機能によって支持することができる。いくつかの実施形態において、駆動要素は、ウェハおよびウェハ支持台の下方に配置されるが、ただし、他の配置を採用することもできる。支持脚は、支持されるグリッドが接地されるか、または電気的にフロー・ティングとされるかに応じて、導電性または絶縁性とすることができる。

20

#### 【0073】

一般に、固定グリッドを接地することが有効である。図4に示すように、固定グリッドが可動グリッドの上方に配置される場合には、固定グリッドの接地接続は、上部チャンバの励起源からグリッドに流れるRF電流のための良好な接地経路を提供する。これは、上部チャンバが、ICP源で励起され、かつ約5cm未満の高さである場合か、またはVHF CCP源を用いて上部ゾーン・プラズマを発生させる場合に、特に有用となり得る。図5に示すように、固定グリッドが可動グリッドの下方に配置される場合には、接地接続は、下部ゾーン・プラズマのバイアス電流用の大きな接地帰路面を提供する。これは、エッティングプロセスでウェハ上に大きなバイアス電圧（例えば、約100V超）を必要とする場合に、特に望ましいことがある。

30

#### 【0074】

可動グリッドの最適な電気的接続は、固定グリッドと可動グリッドの相対位置に依存し得る。固定グリッドが可動グリッドの上方に配置される場合には、可動グリッドを電気的にフロー・ティングとすると有効であり得る。一方、固定グリッドが可動グリッドの下方に配置される場合には、可動グリッドを接地するか、またはフロー・ティングとするか、いずれかとすることができます。可動グリッドが接地される場合には、支持構造は、導電性（例えば、金属）でなければならない。可動グリッドが電気的にフロー・ティングである場合には、支持構造は、絶縁性でなければならない。

#### 【0075】

固定グリッドが可動グリッドの下方に配置される場合には、固定グリッドは、可動グリッドサポートが該サポートを駆動要素と接続するために固定グリッドを貫通して延びることを可能とするための、弧状スロット（または、そのスロットに沿って弧状の動きを可能とする他のスロット）を有することができる。上述のように、この実現形態を図5に示している。あるいは、可動グリッドは、反応チャンバの周囲から内側に延出する可動支持構造によって支持することができる、または反応チャンバの上端に接続する構造によって支持することができる。どのような実現形態を用いる場合でも、支持構造は、所望の上部ゾーン・プラズマおよび下部ゾーン・プラズマの形成を妨げないように設計されなければならない。また、グリッドを動かすためのアクチュエータは、アクチュエータからウェハへの粒子付着のリスクを最小限とするように、ウェハ平面から十分下方に保持されることが望ましい。

40

50

## 【0076】

グリッドアセンブリは、DC源またはRF源を用いてバイアスすることができる。グリッドアセンブリが複数の導電性グリッドを有する場合は、それらをまとめて同電位にバイアスすることが望ましい。あるいは、グリッドアセンブリを、1つのみの導電性グリッドと1つ以上のフローティング／絶縁性グリッドで構成することができ、その場合、導電性グリッドのみがバイアスされる。

## 【0077】

複数の構成要素からなるグリッドアセンブリは、“INTERNAL PLASMA GRID FOR SEMICONDUCTOR FABRICATION (半導体製造用の内部プラズマグリッド)”という名称で2013年6月12日に出願された米国特許出願第13/916,318号でさらに論じられて説明されており、その文献の全体は参考により本明細書に組み込まれる。

10

## 【0078】

## [プラズマ特性]

グリッドは、チャンバのプラズマを、2つのゾーン、すなわちプラズマ生成用のコイルに近接した上部ゾーンと、基板ホルダに近接した下部ゾーンとに、効果的に分割する。いくつかの実施形態において、上部ゾーンのプラズマは、比較的「高温」の高エネルギー電子を含んでいる。このプラズマは、しばしば電子イオンプラズマと特徴付けられる。いくつかの実施形態において、下部ゾーンのプラズマは、比較的「低温」の低エネルギー電子を含んでいる。この下部ゾーン・プラズマは、しばしばイオンイオンプラズマと特徴付けられる。

20

## 【0079】

プラズマは、主として、または専ら、上部サブチャンバにおいて生成することができる。一実施形態では、上部サブチャンバの上方に位置するコイルに電流を流すことによって、上部サブチャンバにおいて誘導結合プラズマが生成される。シングルコイルまたは多重コイルを採用することができる。他の実施形態では、例えば、VHF CCP源を用いて、容量結合プラズマが生成される。グリッドがあることによって、上部サブチャンバのプラズマは、下位サブチャンバのプラズマとは明確に異なる特性を有する。

## 【0080】

多くの実施形態において、上部ゾーン・プラズマは、通常の電子イオンプラズマである。この種のプラズマでは、正に帯電した種のほとんどは正イオンであり、負に帯電した種のほとんどは電子である。負イオンは存在するものの、それらは比較的低濃度にすぎない。これに対し、下部サブチャンバのプラズマは、イオンリッチ・プラズマであり、多くの場合、イオンイオンプラズマである。イオンイオンプラズマは、電子イオンプラズマと比較して、負イオンである負に帯電した種の割合がより大きく、電子である負に帯電した種の割合がより低い。いくつかの実現形態において、イオンイオンプラズマ中の電子濃度に対する正イオン濃度の比率（電子に対する正イオンの比  $n_i / n_e$ とも呼ばれる）は、約2以上であり、いくつかの例では、約5以上であるか、さらには約10以上である。一部の例では、電子に対する正イオンの比は、下部プラズマでは、上部プラズマよりも少なくとも約2倍大きい（例えば、少なくとも5倍大きい）。

30

## 【0081】

2つのプラズマ間の関連差異は、上部ゾーン・プラズマのほうが、著しく高い電子密度を有することである。例えば、下部ゾーン・プラズマの電子密度は、約  $5 \times 10^9 \text{ cm}^{-3}$  以下（例えば、約  $1 \times 10^9 \text{ cm}^{-3}$  以下）とすることができます。このような範囲は、特に電子負性処理ガスに適用可能である。上部ゾーン・プラズマは、下部ゾーン・プラズマのそれよりも少なくとも約10倍大きい（例えば、少なくとも約100倍大きい、または少なくとも約1000倍大きい）電子密度を有することができる。いくつかの例において、下部サブチャンバは、イオンイオンプラズマを有し、その場合の電子密度は、負イオン密度および正イオン密度よりも、少なくとも一桁小さい。具体的な一例では、 $N_e$  は  $\sim 10^8 \text{ cm}^{-3}$ 、 $N_{i+}$  は  $\sim 10^9 \text{ cm}^{-3}$ 、 $N_{i-}$  は  $\sim 10^9 \text{ cm}^{-3}$  である。

40

50

## 【0082】

上部ゾーン・プラズマと下部ゾーン・プラズマとの間の追加的な差異は、電子：イオン比に間接的に多少基づくものであるが、通常、下部ゾーン・プラズマのほうが、正イオンに対する負イオンの比率がより高いということである。上部ゾーンの電子 イオンプラズマは、通常、主として正イオンと電子を含み、負イオンは比較的少ないので、負イオン：正イオン比は低くなる。下部ゾーン・プラズマにおける負イオン：正イオン比は、約0.5～1の間（例えば、約0.8～0.95の間）とすることができます。

## 【0083】

下部ゾーン・プラズマ中の比較的低い電子濃度についての、限定的ではない1つの説明は、最初に下部ゾーンにある電子（例えば、上部ゾーンから下部ゾーンにグリッドを通り抜けた電子）は、一般に、RF電場により加熱されず、ガス分子との非弾性衝突によって急速にエネルギーを損失し、その結果、低実効電子温度となるということである。これらの低エネルギー電子は、中性種と相互作用して負イオンを生成する可能性が、（上部ゾーン・プラズマ中の高エネルギー電子と比較して）より高い。電子は、中性粒子に付着して負イオンを生成するためには、比較的低エネルギーでなければならない。このような負イオンの生成は、高エネルギー電子では発生せず、それらは、中性種と衝突したときに、結合して負イオンを生成するのではなく、他の電子を「蹴り出す」ことがある。

10

## 【0084】

指摘したように、実効電子温度は、下部ゾーン・プラズマに比べて、上部ゾーン・プラズマで高い。電子は、グリッドのスロットを通過する際に冷却され得る。典型的には、下部ゾーン・プラズマの実効電子温度は、約1eV以下である。いくつかの例において、下部ゾーン・プラズマの実効電子温度は、約0.1～1eVの間（例えば、約0.2～0.9eVの間）とすることができます。実効電子温度は、電子ボルトで測定した場合、下部ゾーン・プラズマにおけるよりも、上部ゾーン・プラズマにおいて、少なくとも約2倍高く（例えば、少なくとも約3倍高く）なり得る。具体的な実現形態では、上部ゾーン・プラズマは、約2.5eVの実効電子温度を有し、下部ゾーン・プラズマは、約0.8eVの実効電子温度を有する。いくつかの実施形態において、このような実効電子温度の違いは、全面的または部分的に、グリッドがあることに起因して生じる。

20

## 【0085】

グリッドの役割は、特定の理論またはメカニズムに制限されることなく、以下のように説明することができる。グリッドは、下部サブチャンバを部分的に遮蔽して、その中の荷電種がプラズマコイルからの電力を直接受けることがないようにすることができます。さらに、グリッドのスロットの特定のアスペクト比によって、高エネルギー電子の一部がスロットを通過するときにグリッドと衝突するようにする。これによって、2つのプラズマゾーンで、2つの質的に異なるプラズマを発生させる。

30

## 【0086】

上部ゾーン・プラズマと下部ゾーン・プラズマのもう1つの区別される特徴は、それらのプラズマ電位である。一般に、下部チャンバにおけるよりも、上部チャンバにおけるプラズマ電位は高い。例えば、上部プラズマにおけるプラズマ電位は、約8～35Vの間（例えば、約10～20Vの間）とすることができます、下部プラズマにおけるプラズマ電位は、約0.4～1.0Vの間（例えば、約0.5～3Vの間）とすることができます。これは、電子エネルギーが低下しているため、プラズマは電子を失うことを防ぐことに積極的である必要がないからである。

40

## 【0087】

また、2つのプラズマは、通常、異なるエネルギー分布関数（例えば、イオンエネルギー分布関数および電子エネルギー分布関数）を有する。電子エネルギー分布関数とイオンエネルギー分布関数は、どちらも、下部プラズマでは幅がより狭く、上部プラズマでは幅がより広い。グリッドを用いることにより、波形発生器による高度な制御を用いることなく、極めて狭いイオンエネルギー分布関数を得ることができる。例えば、下部プラズマのイオンエネルギー分布関数は、わずか約5Vの半値全幅を有し得る。その結果、負イオン

50

から負電流を引き出すことが可能であり、これが基板表面に達して（電子がこの目的を果たす代わりに）電気的中性を維持する。こうして、独特なエッティング機構が得られる。

#### 【0088】

下部ゾーン・プラズマ中のラジカル濃度は、約1%の全中性密度～約70%の全中性密度の範囲、または約10%～約70%の全中性密度の範囲、または約10%～約50%の全中性密度の範囲とすることができます。

#### 【0089】

エッティング工程中のチャンバ圧力は、約1～2000 mTorr (約0.133～267 Pa) の間（例えば、約2～200 mTorr (約0.267～26.7 Pa) の間）など、約2000 mTorr (約267 Pa) 未満とすることができます。具体的な一例では、チャンバ圧力は約20 mTorr (約2.67 Pa) 以下に維持される。このような圧力は、約0.5 eV以下の実効電子温度および/または約 $5 \times 10^8 \text{ cm}^{-3}$ 以下の電子密度を有する下部ゾーン・プラズマで用いる場合に、特に有用である。また、これらの圧力は、下部ゾーンのイオン イオンプラズマで用いる場合に特に有用である。

#### 【0090】

上述したように、特定の実施形態では、プラズマは、変圧器結合プラズマである。プラズマを発生させるために、1つまたは複数のTCPコイルが使用されることがある。一部の例では、プラズマは、内側TCPコイルおよび外側TCPコイルによって発生され、これらのコイルはそれぞれ、反応チャンバの誘電体窓を通るRFパワーを分散させる。内側TCPコイルと外側TCPコイルは、実質的に同一平面にあることがあり、外側コイルが内側コイルを取り囲む。内側コイルと外側コイルはそれぞれ、プラズマの一部を維持するための電流を伝導するために使用されることがある。内側コイルと外側コイルそれぞれを通る電流のアンペア数を調節するために、並列回路が使用されることがある。すなわち、内側コイルと外側コイルに送給される電力を調整することができる。並列回路は、電源とコイルの間に電気的に結合されることがある、互いに並列に電気的に接続されたインダクタと可変コンデンサを含むことがある。外側コイルに送給される電力に対する内側コイルに送給される電力の比は、変圧器結合容量性同調（TCCCT）と呼ばれる。例えば、0.75のTCCCTは、内側コイルに送給される電力が外側コイルに送給される電力の値の約75%のみであることを意味する。特定の実施形態では、TCCCTは、約0.25～1.5の間、例えば約0.25～0.75の間または約0.5～1.5の間でよく、しかし、これらの例は限定するものではない。変圧器結合容量性同調は、“ADJUSTING CURRENT RATIOS IN INDUCTIVELY COUPLED PLASMA PROCESSING SYSTEMS（誘導結合プラズマ処理システムにおける電力の比の調整）”という名称で2010年3月19日に出願された米国特許出願第12/728,112号でさらに論じられて説明されており、その文献の全体は参照により本明細書に組み込まれる。

#### 【0091】

イオン イオンプラズマは、半導体処理において、いくつかの効果が得られると考えられる。例えば、イオン イオンプラズマでエッティングされた半製品の半導体デバイスは、被エッティング基板の面にわたり、極めて良好な選択性、プロファイル角、I/Dローディング、および全面均一性を示す。従来の技術では、これらの効果をすべて得ることはできなかった（すなわち、プロセス設計者は、例えば、良好な全面エッティング均一性を達成することと、他の効果を得ることとの間で、選択しなければならなかった）。従って、本明細書に記載の実施形態は、エッティング方法における大きな進歩を示すものである。

#### 【0092】

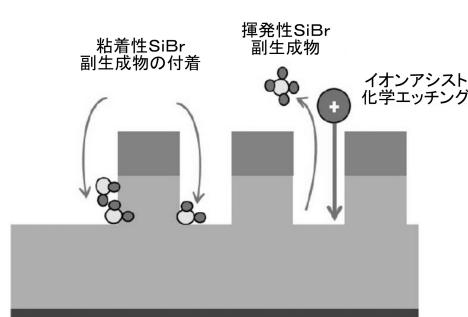

図6A～6Cは、エッティング副生成物の分解が、エッティングされているフィーチャに及ぼす影響を示している。最初に、図6Aは、3層がその上に堆積された基板を示している。最下層はゲート酸化物を表し、中間層はポリシリコンを表し、（3つの個々のブロックとして示す）最上層はハードマスクを表す。従来のエッティングプロセスでは、チャンバ内にあるプラズマが、図6Bに示すように、エッティング副生成物を一部解離するように作用

10

20

30

40

50

すると考えられる。これらの副生成物は、多くの場合、揮発性成分（例えば、 $\text{SiBr}_4$ ）であり、条件が整えば、基板から掃去される。ところが、電子 イオンプラズマに特徴的である高電子密度のプラズマが、ウェハに接触すると、プラズマ中の高エネルギー電子が、揮発性副生成物と反応することで、それらを物理化学的に「粘着性」の解離生成物（例えば、 $\text{SiBr}_2$ ）に解離させる可能性がある。これらの解離生成物は、図 6 B に示すように、基板に付着し、多くの場合、エッチングされているフィーチャの側壁に付着して、図 6 C に示すように、エッチングプロセスを、非垂直または他の望ましくない形で発生させる。このような解離生成物の付着 / 再付着は、結果的に非垂直エッチングとなるローカルローディング効果につながる。

## 【0093】

10

これらの望ましくない効果は、被エッチング基板に近接したプラズマの実効電子温度を抑えるためのグリッドを用いることによって、軽減される。イオン イオンプラズマの生成は、それに応じて電子密度および実効電子温度が低下することで、これらの望ましくない効果を著しく軽減させる。一般に、イオンは電子よりもかなり低いエネルギーを有するので、本発明の実施形態のイオン イオンプラズマ中のイオンは、このような副生成物の解離を引き起こすことはない。本発明の実施形態では、電子 イオンプラズマを生成し得るもの、この高電子密度 / 高実効電子温度プラズマを上部サブチャンバに留めることができる。このため、エッチング副生成物は、下部ゾーン・プラズマのみに接触する傾向にあり、高実効電子温度の上部ゾーン・プラズマとは接触しない。また、イオン イオンプラズマ中には多少の電子は存在するものの、それらの電子は一般に、低  $T_e$  を有し、従つて、通常、副生成物の解離を引き起こすのに十分なエネルギーを持たない。このように、エッチング副生成物は、「粘着性」の問題を引き起こす化合物に解離されることはない。

## 【0094】

20

## [ウェハバイアス]

いくつかの実現形態において、ウェハは処理中にバイアスされる。これは、ウェハを保持 / 支持するのに用いられる静電チャックにバイアスを印加することにより実現される。ウェハは、下部サブチャンバにおいて（イオン イオンプラズマなどの）低  $T_e$  の低電子密度プラズマに暴露されるので、そのイオン イオンプラズマに特有の効果が享受 / 促進されるように、チャックにバイアスを印加することができる。さらに、下部サブチャンバにおいて電子 イオンプラズマの形成が回避されるように、バイアスを印加することができる。例えば、バイアスは、イオン イオンプラズマから電子 イオンプラズマへの変換を防ぐのに適した周波数および電力とすることができます。

## 【0095】

30

いくつかの実施形態において、基板へのバイアス電力の印加により発生する電子加熱量を抑えるように、R F バイアスは、30 MHz 未満の周波数、好ましくは約 100 kHz ~ 約 13.56 MHz の間の周波数とすることができます。一部の実施形態では、（周波数にかかわらず）バイアスは、約 1 % ~ 99 % の間のデューティサイクルで、約 1 Hz ~ 約 10 kHz の範囲でパルス化される。

## 【0096】

40

上述のように、通常の電子 イオンプラズマでは、プラズマ電位は、かなり高い正電位である。このようなプラズマ電位によって、プラズマから逃げ出す電子の能力は効果的に制限される。一方、下部ゾーン・プラズマは、一般に、通常とは異なる低い電子密度および温度を有し、よって、その電子を効果的に留めるのに必要なプラズマ電位ははるかに低い。この低プラズマ電位によって、動作ウィンドウの制限が緩和され、任意選択的に、バイアス波形の正サイクル期間に、イオン イオンプラズマ中に負イオンを存在させることで、ウェハに向けた衝突を加速させることができるとなる。このようなエッチングレジームは、従来の連続波プラズマでは得ることができなかつたものである。

## 【0097】

静電チャックに印加されるバイアスの周波数は、イオン イオンプラズマ中のイオン（限定されないが、特に負イオン）の形成および引力を最適化するように設計することができ

50

きる。この観点から、静電チャックに印加されるバイアスの周波数は、約 0 . 1 ~ 1 5 M Hz の間（例えば、約 4 0 0 kHz ~ 1 3 . 5 6 MHz の間）である。具体的な一例では、バイアスは、約 8 MHz である。このような周波数は、イオン移動周波数に相当するので、特に有用となり得る。他の周波数を用いてもよいが、効果が低くなる場合がある。例えば、約 1 0 0 kHz ~ 1 MHz の間の周波数は、ある程度は機能し得るが、より高い上記周波数よりも効果は低くなる場合がある。

#### 【 0 0 9 8 】

注目すべきことは、グリッドを使用し、かつ静電チャック / ウェハに適切な周波数の AC バイアスを印加する場合には、プラズマから負イオンと正イオンを交互に引き出してウェハ面に向けて加速せしめるように、ウェハ上方のプラズマシースを機能させることができることである。すなわち、プラズマシースによって、正サイクルで負イオンを、そして負サイクルで正イオンを引き付けて、これらのサイクルを AC バイアスによって繰り返す。上述のように、このような（ウェハへの）負イオンの引き付けは、本発明の実施形態の実現より以前には、プラズマ電位が高すぎるために、これによって AC バイアス・サイクルの当該半分の引き付け効果を打ち消すことで、不可能であったものである。

10

#### 【 0 0 9 9 】

前述のように、バイアスは、パルスで印加することができる。しかしながら、パルス化の必要がない多くのケースある。本発明の実施形態では、エッチングの全過程において、ウェハ上方に安定したイオン / イオンプラズマが得られる。従って、本明細書に記載の効果を得るためにには、チャック / ウェハへのバイアスをパルス化する必要はない。ところが、いくつかの実施形態では、それでもバイアスがパルスで印加される場合があり、それはエッチング速度または基板のイオン衝撃量を抑えるためであって、これにより下層に対するエッチング選択性を向上させる。イオン / イオンプラズマにおけるバイアスのパルス化は、イオンとラジカルを交互に用いて選択性を向上させることにより、特に有用とすることができる。すなわち、パルス化によって、基板表面へのイオンとラジカルの流れを分けることができる（パルスオン：ラジカル + イオン パルスオフ：ラジカルのみ）。

20

#### 【 0 1 0 0 】

##### [ プロセス / 応用 ]

本明細書で開示する装置およびプラズマ条件は、シリコン（多結晶、アモルファス、単結晶、および / または微結晶シリコンを含む）、金属（TiN、W、TaNなどを含むが、これらに限定されない）、酸化物および窒化物（SiO、SiOC、SiN、SiONなどを含むが、これらに限定されない）、有機物（フォトレジスト、アモルファスカーボンなどを含むが、これらに限定されない）など、様々な材料のいずれかをエッチングするために用いることができ、さらに他の様々な材料として、限定するものではないが、W、Pt、Ir、PtMn、PdCo、Co、CoFeB、CoFe、NiFe、W、Ag、Cu、Mo、TaSn、Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>2</sub>、InSbTe、Ag、Ge、S、Cu、Te、S、IrMn、Ruが含まれる。本コンセプトは、NiO<sub>x</sub>、SrTiO<sub>x</sub>、ペロブスカイト（CaTiO<sub>3</sub>）、PrCaMnO<sub>3</sub>、PZT（PbZr<sub>1-x</sub>Ti<sub>x</sub>O<sub>3</sub>）、（SrBiTa）O<sub>3</sub>などの材料に拡張することができる。本装置は、現今の製造設備で使用可能な任意のガスの組み合わせ（HBr、CO、NH<sub>3</sub>、CH<sub>3</sub>OHなどを含む）で用いることが可能である。

30

#### 【 0 1 0 1 】

本明細書で開示する装置およびプラズマ条件は、任意のテクノロジノードのデバイスまたは他の構造においてフィーチャをエッチングするために採用することができる。一部の実施形態では、エッチングは、20 ~ 10 nm ノードまたはそれ以降のものの製造において用いられる。エッチングは、製造手順のフロントエンドと製造手順のバックエンドの両方で行うことができる。エッチングによって、優れた垂直プロファイル、材料選択性、I / D ローディング、および / または約 2 % よりも良好なウェハの中心からエッジへの均一性を提供することができる。好適なエッチング用途のいくつかの例には、シャロートレンチ・アイソレーション、ゲートエッチング、スペーサエッチング、ソース / ドレインリセ

40

50

スエッチング、酸化物リセス、およびハードマスク開口エッチングが含まれる。

【0102】

F i n F E T のためのソースドレインリセスエッチング

F i n F E T の形成における 1 つのステップは、ソースドレインリセスをエッチングすることである。様々な用途に関して、エッチングしながら、ソーストレインリセス内に凹角形状を作成することが望ましい。この凹角プロファイルは、ソースドレインリセスエッチングによって作成された凹んだ空間内での S i G e または S i C のエピタキシャル堆積後に、F i n F E T のチャネル領域内の望ましい応力レベルを促す助けとなることがある。エッチング形状は、より広いエッチング部分の上により狭いエッチング部分がある場合に、凹角とみなされる。ソースドレインリセス形成は、プラズマエッチングプロセスによって達成されることがある。従来のプラズマエッチング条件で処理することによって、垂直エッチングプロファイルおよびテーパ状エッチングプロファイルを作成することが可能となっている。また、従来の方法は、円形の等方性リセスを形成することもできる。しかし、ソースドレインリセスに関してより複雑な形状が望まれる場合には、従来のプラズマエッチング技法は良い結果が出ていない。

10

【0103】

イオン - イオンプラズマ条件下でエッチングすることにより、様々な新たな凹形状を実現することができる。図 7 A は、ソースドレインリセスエッチングプロセスが行われる前の、基板フィン構造 701 上の、スペーサ堆積後の半製造された半導体デバイスゲート構造 700 を示す。デバイス 700 は、フィンの形状を定める助けとなる特徴を含む。例えば、マスク層 705 が、ポリ層 703 の上方にあることがある。スペーサ層 707 が、マスク 705 およびポリまたは S i ゲート構造 703 を取り囲むことがある。スペーサ層 707 は、ソースドレインリセスがエッチングされるときに、下にある層 703、705、および構造 701 の一部分を保護することがある。図 7 B は、従来のプラズマ処理で実現可能なりセス形状の例を示し、図 7 C は、イオン - イオンプラズマ処理を使用して形成されることがあるさらなるリセス形状の例を示す。エッチングされた形状は、ソースドレインリセス領域を成し、この領域は、後で、例えばエピタキシャル S i G e で充填される。開示される技法を使用して形成されることがあるリセス形状のさらなる例が、図 19 および図 20 に提供されており、これらは、実施例の項で説明する。

20

【0104】

30

ソースドレインリセス領域を形成するための一方法は、(1) 垂直エッチング、(2) 横方向エッチング、および(3) 酸化ステップを含むマルチステッププロセスを行うものである。このプロセスは、図 8 に示されている。これらのプロセスの 1 つ、2 つ、またはすべてが、イオン - イオンプラズマ条件下で行われることがある。エッチングと酸化の繰り返しが 2 回だけ図示されているが、任意の回数の繰り返しが使用されることがある。このマルチステッププロセスは、凹形状が比較的ゆっくりと基板 701 にエッチングされることを可能にし、この基板 701 は、しばしば単結晶シリコンである。垂直エッチングステップおよび横方向エッチングステップは、それぞれ垂直方向および水平方向で材料を除去するために行われる。酸化ステップは、酸化物層 810 を形成するために行われ、酸化物層 810 は、エッチングされたリセスの側壁をさらなる横方向エッチングから保護する。従来のプラズマが使用される場合、このマルチステッププロセスは、凹形フィーチャの側壁に、認識できるスキヤロップ形状を形成し、これらの形状は、異なる酸化エッチングステップおよび横方向エッチングステップに対応する。図 8 は、イオン - イオンプラズマが使用される場合に実現される形状を示し、従来のプラズマ処理で生じるスキヤロップを示してはいない。

40

【0105】

スキヤロップの形成を促す 1 つの要因は、酸化ステップ中に使用される従来の比較的活発なプラズマが厚い / 硬い酸化物を形成することであり、この酸化物は、後続のエッチングで再成形するのが非常に難しい。酸化物形成の速度は、基板に対する酸素ラジカルの流束に比例する。従来のプラズマは、より高い電子密度および電子温度に相関するかなり高

50

いラジカル密度により、厚い／硬い酸化物を生じる。それに対し、イオン - イオンプラズマでは、電子温度、電子密度、およびラジカル密度はすべてかなり低い。したがって、酸化ステップ中のイオン - イオンプラズマレジームでの処理は、より薄く、より加工しやすい酸化物を形成する。このより薄い酸化物は、従来のプラズマを使用して形成される厚い酸化物に比べて、後続のエッティングステップでの再成形が容易である。有利には、イオン - イオンプラズマ条件下で形成される酸化物は、依然として、凹形フィーチャをオーバーエッティングから適切に保護するのに十分に厚く、高品質である。さらに、イオン - イオンプラズマレジームは、穏やかなプラズマ条件が、例えば表面への低いイオン流束により、比較的低い垂直エッティングレートおよび横方向エッティングレートをもたらすので、エッティングプロセス中に有益である。

10

#### 【0106】

イオン - イオンプラズマ条件下で垂直エッティングを行うために、上部サブチャンバ内で、 $\text{Cl}_2$ （または $\text{HBr}$ 、 $\text{CF}_4$ 、 $\text{SF}_6$ 、 $\text{CHF}_3$ 、それらの何らかの組み合わせ、またはシリコンをエッティングするガスの任意の他の組み合わせ）などのエッチャントから、プラズマが発生する。グリッドの下で、イオン - イオンプラズマが生じ、基板（例えば単結晶シリコン）を垂直方向にエッティングする。エッチャントの流量は、約1~1000 sccmの間でよい。サブチャンバ圧力は、約10~200 mTの間でよい。チャンバ温度は、約40~60 の間でよい。基板温度は、約0~120 の間でよい。プラズマを発生させるために使用される電力は、約100~1100 ワット/ステーションの間でよい。プラズマを発生させるために使用されるRF周波数は、13.56 MHzである。基板は、約0~850 Vの間でバイアスされることがある。1回の垂直エッティングプロセスは、約10~120 nm/minの間でよい。

20

#### 【0107】

イオン - イオンプラズマ条件下で横方向エッティングステップを行うために、上部サブチャンバ内で、 $\text{NF}_3$ と $\text{Cl}_2$ の混合物などのエッチャントからプラズマが発生する。一部の場合には、 $\text{SF}_6$ が使用されることもある。グリッドの下で、イオン - イオンプラズマが生じ、ここでは主に横方向に基板をエッティングする。エッチャントの総流量は、約50~500 sccmの間でよい。 $\text{NF}_3$ と $\text{Cl}_2$ の混合物が使用される場合、 $\text{NF}_3$ の流量は、約5~50 sccmの間でよく、 $\text{Cl}_2$ の流量は、約20~300 sccmの間でよい。チャンバ圧力は、約5~100 mTの間でよい。チャンバ温度は、約40~60 の間でよい。基板温度は、-5 ~ 120 の間でよい。プラズマを発生させるために使用される電力は、約200~1000 ワット/ステーション（TCP）の間でよい。プラズマを発生させるために使用されるRF周波数は、13.56 MHzである。一部の実施形態では、基板は、バイアスされないことがある。1回の横方向エッティングプロセスは、約5~120 秒の間の継続時間を持つことがある。

30

#### 【0108】

イオン - イオンプラズマレジームの下で酸化ステップを行うために、上部サブチャンバ内で、酸素ベースのプラズマ発生ガスからプラズマが発生する。一部の場合には、プラズマ発生ガスは、 $\text{O}_2$ である。他の場合には、ソースガスは、追加または代替として、 $\text{N}_2$ など他の成分を含むことがある。グリッドの下で、イオン - イオン酸素ベースプラズマが生じて、基板と相互作用して、凹形領域内に酸化層を形成する。この酸化層は、後続のエッティング操作でのオーバーエッティングを防止する助けとなる。プラズマ発生ガスの流量は、約10~800 sccmの間でよい。チャンバ圧力は、約10~100 mTの間でよい。チャンバ温度は、約40~60 の間でよい。基板温度は、約0~120 の間でよい。プラズマを発生させるために使用される電力は、約0~1500 ワット/ステーションの間、例えば約100~1500 W/ステーションの間でよい。プラズマを発生させるために使用されるRF周波数は、13.56 MHzである。基板は、約0~300 Vの間、例えば約50~300 Vの間でバイアスされることがある。1回の酸化プロセスは、約5~60 秒の間の継続時間を持つことがある。

40

50

## 【0109】

## FinFETゲートエッティング

イオン-イオンプラズマレジームの下での処理から利益を得ることができる用途の次の例は、FinFETのためのゲート構造をエッティングすることである。様々な用途において、このプロセスは、最終的なゲート構造の外形を形成するために、上に重なったマスク（例えば、SiNまたは酸化物材料）を有するポリシリコンをエッティングすることを含むことがある。したがって、FinFETゲートエッティング後に残るポリシリコンは、最終的なゲートが成形／位置決めされる場所に成形／位置決めされる。ポリシリコンは、ポリシリコンのダミー層でよく、これは、最終的なゲートが位置決めされる領域形状を画定する助けとなるように使用される一時的な材料であることを意味する。後の処理ステップで、ポリシリコンは除去され、所望の最終的なゲート材料で置き換えられる。FinFETゲートエッティングプロセスを表す別の方法は、ポリシリコン層がエッティングされ、それにより、完成された集積回路においてFinFETゲートの近傍となる位置にキャビティを形成することによって、FinFETゲート領域を画定するというものである。上記の位置は、（ポリシリコン層全体、またはエッティングされたキャビティ間の位置ではなく）エッティングされた実際のキャビティである。

10

## 【0110】

FinFETポリシリコンゲートエッティングは、典型的には、特に20～10nmテクノロジノードに関して、難しい性能目標を含む。そのような性能目標の例は、（1）約3よりも大きいアスペクト比のための垂直ポリシリコンエッティングプロファイル；（2）約0nm以下のフィンのシリコンリセス；（3）エッティング後に残る少なくとも50nmのマスク（例えば、SiNマスク）；（4）約0nmの疎／密ローディング；（5）基板にわたる約0nmの中心からエッジへの不均一性を含む。第2の性能目標に関して、下方向に垂直にエッティングしてゲートプロファイルを画定するとき、フィンと呼ばれるフィーチャが現れる。フィンは、ゲートに垂直に延びる。フィンの高さは、約30nmであり、ゲートエッティングの最後の30nmに現れる。フィンは、シリコンから形成されるが、約3～5nmの厚さを有する薄い酸化物層を上に有する。ゲートエッティングプロセスは、高い選択性を有さなければならず、そうでないと、フィンをエッティングし始める。これは、フィンリセスと呼ばれる。ゲートエッティングプロセスは、典型的には、ゲートを垂直にするために、ゲートの底部テーパ内にオーバーエッティングを引き込む必要がある。FinFETポリシリコンゲートエッティング中にフィンがエッティングされないことが重要である。

20

## 【0111】

従来のプラズマ処理では、これらの目標を同時に実現することは非常に難しかった。従来、FinFETポリシリコンゲートエッティングのために、3ステップエッティングプロセスが使用されている。これらのステップは、（1）低圧メインエッティング、（2）高圧ソフトランディングエッティング、および（3）高圧オーバーエッティングを含んでいた。これらのプロセスは、ゲートプロファイル、選択性、疎／密ローディング、および中心からエッジへの不均一性の間の妥協点をもたらす。

30

## 【0112】

しかし、イオン-イオンプラズマが使用される場合、FinFETポリシリコンゲートエッティングは、1回のエッティングで達成することができ、プロセス目標間の妥協は実質的に少ない。本明細書で述べるグリッドは、イオン-イオンプラズマが下部サブチャンバで生成されるようにプラズマ処理環境を効果的に変える。この処理環境は、従来のプラズマで処理するときに得られるのとは異なるプラズマ-ウェハ表面相互作用をもたらす。具体的には、ラジカルの多いイオン-イオンプラズマ環境は、利用可能なプロセス窓を、より低い圧力レジーム（例えば5～20mTorr（約0.667～2.67Pa））を開き、このような低い圧力レジームは、従来は、ポリシリコンと酸化物との間の不十分な選択性、および大きな疎／密ローディングによって制限されていた。従来、所望のマスク選択性およびエッティングプロファイルを実現するためには高圧エッティングレジーム（例えば、>80mTorr（10.67Pa））が必要であったが、これはまた、中心からエッジ

40

50

への比較的高い不均一性をもたらした。対照的に、イオン-イオンプラズマレジームでの処理によって、上に列挙した目標の全てを、1ステップエッチングによって実現することができる。具体的には、イオン-イオンプラズマレジームは、無限のポリシリコン：酸化物選択性を有し、（ポリシリコンをエッチングするが、酸化物は全くエッチングしない）、垂直エッチングゲートプロファイルを有し、中心からエッジへの不均一性がなく、または実質的ではなく、かつ疎／密ローディングがない、または実質的でないエッチングプロセスをもたらす。

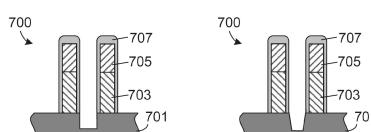

#### 【0113】

図9は、FinFETポリシリコンゲートエッチングを受けたときの、半製造された半導体デバイス901を示している。デバイス901は、シリコン基板902上にフィン910を含み、これらはどちらも、薄い保護酸化物層904によってカバーされる。保護酸化物904は、例えばSiO<sub>2</sub>でよい。保護酸化物904の上に、ポリシリコン906の層がある。このポリシリコン層906は、FinFETポリシリコンゲートエッチング中にエッチングされる層である。ポリシリコン層906の上に、パターン形成マスクの層908があり、この層908は、様々な場合に、窒化ケイ素、酸化物、または窒化ケイ素の層を有する酸化物でよい。エッチングプロセス中、上部サブチャンバ内でプラズマが発生し、下部サブチャンバ内でイオン-イオンプラズマが生じる。イオン-イオンプラズマは、デバイス901と相互作用して、フォトレジストマスク908によって保護されていないポリシリコン層906のいくつかの部分を垂直にエッチングする。

#### 【0114】

図10は、従来のFinFETポリシリコンゲートエッチング後の、半製造された半導体デバイス1001の断面図（上図）および上面図（下図）を示している。図10は、デバイスのオンフィン領域とオフフィン領域の間の不均一なプロファイルローディングの問題を示している。下図での点線は、上図で用いられる断面を表す。デバイス1001は、シリコン基板1002の上にフィン1010を含む。フィン1010とシリコン基板1002は、保護酸化物層1004によってカバーされる。図10の上図に示されるフィン1010は、図面の紙面よりも奥にある。フィンの前に、紙面の平面内に、上に重なったマスク層1008を有するポリシリコン1006から形成されたエッチングされたゲート構造がある。保護酸化物層1004は、ポリシリコンゲート構造1006の下では紙面の平面内に示され、フィン構造1010の上では紙面の平面よりも奥に示されている。上述したように、マスク層1008は、様々な場合に窒化ケイ素でよい。フィン1010の位置は、オンフィン領域1012と、オフフィン領域1014とを画定する。

#### 【0115】

FinFETポリシリコンゲートエッチングを行うときに生じる1つの問題は、不揮発性の副生成物（例えば、SiBr<sub>x</sub>およびSiO<sub>x</sub>Br<sub>y</sub>）の生成であり、これらの不揮発性の副生成物は、エッチングされた領域の側壁に付着し、それにより、側壁を幾分不動態化する。これらの副生成物は、1つには、基板の離散領域と密集領域とに異なる形で影響を及ぼすので問題となる。例えば、図10の文脈で、不均一な副生成物の生成および吸着は、オンフィン領域1012とオフフィン領域1014との大きなエッチングプロファイルの相違を生じることがある。この図に示されるように、オンフィン領域1012内のポリシリコン1006は、オーバーエッチングされることがあり、それにより、残ったポリシリコン1006は、所望の垂直エッチングプロファイルではなく、湾曲したエッチングプロファイルを有する。対照的に、オフフィン領域1014でのエッチングプロファイルは垂直である。

#### 【0116】

オンフィン領域とオフフィン領域の相違を減少させるための一方法は、エッチング中に、チャンバをバージするために非常に高いガス流量を使用することである。しかし、ウェハ全体にわたってそのようなバージを効果的に行うことができる現在利用可能なポンプは存在しない。別の方法は、副生成物の生成の速度がより低くなるようにエッチングレートを減少させ、それにより、高流量バージガスを用いて副生成物をより良くバージできるよ

10

20

30

40

50

うにすることである。この方策は、スループットを減少させて望ましくない。オンフィン領域とオフフィン領域の相違を最小限に抑える、またはなくすための別の方法は、イオン・イオンプラズマでエッティングすることである。この技法を使用することによって、エッティングによって生成される副生成物は揮発性のままとなる。なぜなら、それらの副生成物は、上部サブチャンバ内に存在する厳しいプラズマ条件から遮蔽され、したがって、下部サブチャンバ内で分解されて不揮発性の副生成物にならないからである。したがって、不揮発性の副生成物が生じず、側壁が不動態化されず、揮発性の副生成物を効果的に除去することができ、ウェハのすべての領域にわたって均一なエッティングプロファイルが得られる。

## 【0117】

イオン・イオンプラズマレジームの下でFinFETポリシリコンゲートエッティングを行うために、上部サブチャンバ内で、例えばHBrとO<sub>2</sub>またはHBrとCO<sub>2</sub>を含有するプラズマ発生ガスからプラズマが発生する。プラズマ発生ガスは、さらに、HeSTGを含むことがある。グリッドの下で、イオン・イオンプラズマが生じ、基板と相互作用して、ポリシリコンをエッティングしてゲート構造を形成する。HBrの流量は、約100~500 sccm、例えば約100~300 sccmの間でよい。O<sub>2</sub>の流量は、約2~12 sccmの間、例えば約3~6 sccmの間でよい。HeSTGの流量は、約200~400 sccmの間でよい。チャンバ圧力は、約5~25 mTorr (約0.667~3.33 Pa) の間、例えば約10~20 mTorr (約1.33~2.67 Pa) の間でよい。基板温度は、約20~100 の間でよい。プラズマを発生させるために使用される電力は、約300~1800 ワット/ステーションの間、例えば約1000~1600 W/ステーションの間でよい。基板は、約100~500 Vの間、例えば約200~400 Vの間にバイアスされることがある。TCTは、約0.25~0.75 の間、例えば約0.4~0.6 の間でよい。

## 【0118】

ポリゲートFinFETは、提案された1ステップ化学反応を用いてエンドポイント(EP)までエッティングされ、その後の時間で、数パーセント、オーバーエッティングされる。エッティング性能をさらに改良するために、以下のパラメータを調整することができる。圧力(5~20 mT)、総流量(1x~3x)、O<sub>2</sub>流量、静電チャック温度(20~100)、TCPパワー(300 W~1800 W)、バイアス電圧、バイアス電圧パルスデューティサイクル(100~200 Hz、25~50 %)、CO<sub>2</sub>流量。

## 【0119】

代替のプロセス条件は、低いTCPおよびバイアスパルシングを利用することがある。バイアスは、約100~500 Hzの間、例えば約150~300 Hzの間の周波数でパルスされることがある。

## 【0120】

別の代替条件は、低いTCP、低いバイアス、およびCO<sub>2</sub>を利用する。CO<sub>2</sub>の流量は、約2~12 sccmの間、例えば約5~10 sccmの間でよい。

## 【0121】

様々な実施形態で、グリッドは、チャンバ壁に接地されることがある。他の実装形態では、本明細書の別の場所に記載するように、グリッドはバイアスされることがある。

## 【0122】

実験結果は、従来のエッティングで生じるオンフィンとオフフィンとのプロファイルの相違など望ましくない結果を生み出すことなく、FinFETゲートをエッティングするためにイオン・イオンプラズマを使用することができることを示している。非常に小さなCD空間(例えば、<2 nm)でさえ、エッティング後にシリコン残渣は見られない。さらに、ゲートは、最小限のマスク損失でエッティングすることができ、例えば、約70 nmよりも多くのマスクが残り、約5 nm以下のマスク高さが失われる(約10%未満の損失)。また、これらの結果は、オンフィン領域とオフフィン領域との間の最小のローディングを示し、どちらの場合にも垂直エッティングプロファイルとなる。

10

20

30

40

50

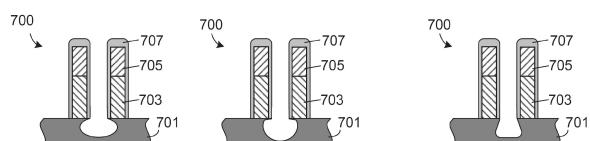

## 【0123】

## ダミーポリシリコン除去

図11A～図11Gは、製造の様々な段階での、半製造された半導体デバイスを示す。上の例で説明したFinFETポリシリコンゲートエッティング後、デバイス1101は、図11Aに示されるようになっており、Fin1110がシリコン基板1102の上に位置決めされている。Fin1110と基板1102はどちらも、保護酸化物層1104によってカバーされることがある。保護酸化物層1104は、SiO<sub>2</sub>などの材料から形成されることがある。次いで、図11Bに示されるように、プラズマエッティングによってマスク層1108が除去されることがある。次に、図11Cに示されるように、前のポリシリコンゲートエッティング中にエッティングされた領域内に誘電体材料1112が堆積される。次いで、最終的なゲートが形成されるキャビティを形成するために、ダミーポリシリコン材料1106が除去されることがある。図11Dは、ダミーポリシリコン材料1106の除去後のデバイス1101を示す。この除去プロセスは、ダミーポリシリコン除去と呼ばれることがある、この例の焦点である。ダミーポリシリコンが除去された後、ウェットエッティングを行って、図11Eに示されるように、下にある保護酸化物層1104（例えば、二酸化ケイ素層）を除去することができる。ウェットエッティング後、新たな保護酸化物層1114（例えば、酸化ハフニウム層1114）が堆積されることがある。次いで、図11Gに示されるように、ダミーポリシリコンが除去されたときに形成されたキャビティ内に、最終的な所望のゲート材料1116（例えば、タンタル、チタン、タングステン、およびそれらの組み合わせの1つまたは複数）が堆積されることがある。ダミーポリシリコン除去を表す別の方法は、ポリシリコンがエッティングされて、完成された集積回路においてFinFETゲートが位置される位置にキャビティを形成するというものである。上記の位置は、（ポリシリコン層全体、またはエッティングされたキャビティの間の空間ではなく）エッティングされたキャビティの実際の位置である。

## 【0124】

FinFETポリシリコンゲートエッティングに関して上述したのと同様の不揮発性副生成物の生成の問題が、ダミーポリシリコン除去プロセスでも生じる。特に、従来のプラズマプロセスは、HBr/O<sub>2</sub>化学物質を利用してダミーポリシリコンを除去する。これは、揮発性副生成物を生成させる。しかし、揮発性副生成物が従来のプラズマと接触すると、分子の多くは分解して、より小さな不揮発性の分子になり、これらの分子が、半製造されたデバイスの側壁および他の部分に付着する。これらの不揮発性の分子は、側壁を実質的に不動態化して、垂直でないエッティングプロファイルの一因となる。

## 【0125】

代わりにイオン-イオンプラズマレジームでこのエッティングを行うことによって、不揮発性副生成物の生成が2つの様式で避けられる。第1に、イオン-イオンプラズマの低いイオン濃度および低い電子密度の特性により、異なる化学物質を使用して、Finを覆っていることがある下にある保護酸化ケイ素材料を除去することなく、ダミーポリシリコンを除去できるようになる。様々な場合に、ダミーポリシリコン除去は、2ステッププロセスで達成されることがある、各ステップがイオン-イオンプラズマを採用する。第1のステップは、第1のプラズマ（例えば、HBrベースのプラズマ）で基板をエッティングして、ダミーポリシリコンのバルクを除去することを含むことがある。この第1のエッティングステップ後、基板上、特にFinの近くのフィーチャの隅に、いくらかの材料が残ることがある。しばしば、この残りの材料は、ポリシリコン残渣である。プロセスの第2のステップは、隅の残渣を除去するために、第2のプラズマ（例えば、NF<sub>3</sub>/Cl<sub>2</sub>ベースのプラズマ）で基板をエッティングすることを含むことがある。

## 【0126】

様々な場合に、ダミーポリシリコンは、酸素含有エッチャントを含まない、または実質的に含まないプロセスガスを使用して除去されることがある。本明細書で使用するとき、「酸素含有反応物を実質的に含まない」は、微量以下の酸素含有反応物を意味する。第2のステップでCl<sub>2</sub>ベースの化学物質を使用することによって、特定の不揮発性副生成物

(例えば、 $\text{SiO}_x\text{Br}_y$ )の生成を回避することができる。なぜなら、そのような副生成物を生成するために利用可能な酸素がないからである。

#### 【0127】

さらに、イオン-イオンプラズマは、従来のHBr/O<sub>2</sub>化学物質が使用される場合でさえ、不揮発性副生成物の生成を減少または回避する。なぜなら、下部サブチャンバ内で生じる副生成物(例えば、揮発性副生成物)が、上部サブチャンバの厳しいプラズマ条件に露出されないからである。下部サブチャンバ内のイオン-イオンプラズマは、十分に穏やかであり(すなわち、低い電子温度、低い電子密度など)、それにより、揮発性副生成物は、実質的に分解されて不揮発性物質になることがなく、したがって、副生成物は、基板上に再び堆積することなく、反応チャンバから除去することができる。

10

#### 【0128】

図12は、従来のプラズマおよびイオン-イオンプラズマに関する電子エネルギー分布関数を示している。イオン-イオンプラズマは、従来のプラズマよりも実質的に低い電子密度(約3桁低い)、および低いエネルギーを有する。これらの穏やかな条件は、揮発性副生成物が分解して不揮発性副生成物になるのを防止する助けとなる。

#### 【0129】

ダミー・ポリシリコン除去の文脈で、不揮発性副生成物の再付着が特に問題である。なぜなら、そのような副生成物の存在は、上述したように、後続のウェットエッチングプロセスを大きく妨害することがあるからである。このウェットエッチングプロセスは、酸化ケイ素材料を除去するために行われ、周囲の/隣接するシリコン材料を除去すべきではない。様々な場合に、ウェットエッチングは、フッ化水素酸を用いて行われる。HFは、純粋なSiO<sub>2</sub>を除去するのには非常に良好であるが、ダミー・ポリシリコンの除去中に生じる不揮発性副生成物物質など、十分な量の酸素を有さないシリコンベースの物質を除去するには効果的でない。したがって、副生成物が存在する場合、それらは、ウェットエッチングによって除去されことが多い。簡潔に言うと、デバイス性能のために必要とされる、(例えばフィン内で)周囲のシリコン材料を除去することなくシリコンベースの不揮発性副生成物を除去することができる既知の化学物質/プロセスは存在しない。したがって、まず、そのような不揮発性副生成物の生成を減少または回避することが望ましい。

20

#### 【0130】

上述したように、特定の実施形態では、ダミー・ポリシリコン除去は、2つのステップで達成される。すなわち、メインエッチングと、オーバーエッチングである。メインエッチングは、HBr/Heプラズマを用いたエッチングを含むことがあり、オーバーエッチングは、NF<sub>3</sub>/Cl<sub>2</sub>プラズマを用いたエッチングを含むことがある。メインエッチング後に、基板上、例えばエッチングされた領域の底部の隅に、いくらかの量のポリシリコンベースの残渣が存在することがある。ポリシリコンベースの残渣をすべて除去するために、オーバーエッチングが行われることがある。イオン-イオンプラズマの低いプラズマ密度により、基板の表面へのイオン流束は低い。したがって、オーバーエッチングプロセスは、主に、化学的に駆動されるプロセスでよく、これは、非常に高い選択性を有し、したがって、フィンを損傷することなく残渣を効果的に除去するために使用することができる。

30

#### 【0131】

イオン-イオンプラズマレジームでのメインエッチング中、HBrは、約300~850sccmの間、例えば約400~600sccmの間の流量で提供されることがある、Heは、約500~1000sccmの間、例えば約700~900sccmの間のHe流量で提供されることがある。上部サブチャンバ内で、HBr/Heからプラズマが発生する。イオン-イオンプラズマが、下部サブチャンバ内で生じ、基板と相互作用して、ポリシリコンを除去して、最終的なゲート構造が位置されるキャビティを形成する。チャンバ圧力は、約20~80mTorr(約2.67~10.7Pa)の間、例えば約60~80mTorr(約8.00~10.7Pa)の間でよい。チャンバ温度は、約40~60の間でよい。基板温度は、約30~80の間、例えば約50~75の間でよい。

40

50

プラズマを発生させるために使用される電力は、約 200 ~ 1500 ワット / ステーションの間、例えば約 1000 ~ 1500 W / ステーションの間でよい。プラズマを発生させるために使用される R F 周波数は、約 13.56 MHz でよい。基板は、約 40 ~ 150 V の間、例えば約 80 ~ 130 V の間にバイアスされることがある。FinFET ダミー ポリシリコン除去プロセスのための 1 回のメインエッチングは、約 30 ~ 100 秒の間の継続時間有することがある。

#### 【 0132 】

ダミー ポリシリコン除去のオーバーエッチング部分において、上部サブチャンバ内で、 $NF_3$  および  $Cl_2$  などのエッティング化学物質からプラズマが発生する。また、プラズマ発生ガスの一部として、不活性ガスが反応チャンバに提供されることもある。イオン - イオン プラズマが、下部サブチャンバ内で生じ、基板と相互作用して、エッティングされた領域内に存在するポリシリコン残渣を除去する。 $NF_3$  は、約 0 ~ 60 sccm の間、例えば約 20 ~ 50 sccm の間の流量で流れることがあり、 $Cl_2$  は、約 10 ~ 100 sccm の間、例えば約 40 ~ 70 sccm の流量で流れることがある。Ar などの不活性ガスは、約 30 ~ 200 sccm の間、例えば約 40 ~ 100 sccm の間の Ar 流量で流れることがある。チャンバ圧力は、約 4 ~ 80 mTorr ( 約 0.533 ~ 10.7 Pa ) の間、例えば約 30 ~ 60 mTorr ( 約 4.00 ~ 8.00 Pa ) の間でよい。チャンバ温度は、約 40 ~ 60 の間でよい。基板温度は、約 30 ~ 80 の間、例えば約 50 ~ 70 の間でよい。プラズマを発生させるために使用される電力は、約 200 ~ 1000 ワット / ステーションの間、例えば約 200 ~ 400 W / ステーションの間でよい。プラズマを発生させるために使用される R F 周波数は、約 13.56 MHz でよい。基板は、バイアスされないままであることがある。FinFET ダミー ポリシリコン除去プロセスに関する 1 回のオーバーエッチングは、約 10 ~ 60 秒、例えば約 30 ~ 60 秒の間の持続期間有することがある。

#### 【 0133 】

##### フォトレジスト・リフロー

フォトレジスト・リフロー プロセスは、フロントエンド ( F E O L ) プロセスとバックエンド ( B E O L ) プロセスとの両方で使用され、これらのプロセスは、幅が約 30 nm 未満のフィーチャ寸法 ( 例えば、ライン、空間 ) を要求する。従来の 193 nm フォトレジストを使用する現在のフォトリソグラフィパターン形成技法は、これらの寸法で良好なパターン形成を実現することができなかった。したがって、極端紫外線 ( E U V ) フォトレジストが、従来の 193 nm フォトレジストの代わりとなりつつある。E U V フォトレジストは、より小さなフィーチャをより良くパターン形成するために使用することができるが、E U V フォトレジストプロセスは、依然として、193 nm フォトレジストで見られる他の問題を抱えている。例えば、F E O L 用途でのエッティングされたフォトレジストは、典型的には、約 5 ~ 10 nm の範囲内の比較的大きな初期線幅粗さ ( L W R ) を示す。フォトレジスト・リフローの 1 つの目標は、エッティング後にこの L W R を約 3.0 nm 未満に減少させることである。F E O L 用途に伴う別の問題は、しばしば、下層に対する不十分なエッティング抵抗 / 選択性しか存在しないことである。この不十分なエッティング抵抗は、E U V フォトレジストが使用される場合、193 nm フォトレジストで使用される厚さよりもフォトレジストの厚さが 50 ~ 70 % 小さいことにより、さらに悪くなる。すなわち、下にある層を保護するために利用可能なフォトレジストがあまり存在しないので、下にある層のエッティング抵抗が不十分になる。

#### 【 0134 】

B E O L 用途は、小さなフィーチャ寸法を有することに加えて、凹 / 凸 パターンの同時転写を要求することがある。上記の F E O L 用途と同様に、エッティング後にライン / 空間の L W R が約 3.0 nm 以下に減少されることが望まれる。さらに、ウェハ上のすべてのパターンが、約 10 ~ 30 % 縮小されることがしばしば望まれ、かつそのような縮小がすべてのパターンに関して均一に行われることが重要である。ライン / 凸 / 凹 パターンの不均等な縮小は、クローディングと呼ばれる。従来のプラズマで処理するとき、L W R の改

良と×ローディングの改良との間の大きな妥協が存在する。

【0135】

図13は、フォトレジスト・リフロー・プロセスを受けたときの半導体デバイスの一部を示している。フォトレジスト1302が、下にある材料1301の上に位置決めされる。プラズマフォトレジスト・リフロー方法は、この図に示されるように、典型的には、2ステッププラズマ前処理プロセスを含む。プロセスの開始時、フォトレジストは、比較的粗い。フォトレジストを平滑化するために、リフロー・プロセスの第1のステップは、(例えばH<sub>2</sub>から) プラズマを発生させて、フォトレジストをリフローすることを含む。フォトレジスト・リフロー・プロセスでの次のステップは、(例えばArから) プラズマを発生させて、フット領域内に流れた余剰のフォトレジストを除去することである。その結果、比較的滑らかなフォトレジストが得られ、フォトレジストフットはほとんどまたは全く残らない。

10

【0136】

また、フォトレジストは、第1のプラズマ処理で、より滑らかになるにつれて、ゆっくりと溶融しているかのように下方向に流れ/弛み始める。これは、フォトレジストでの粗さを平滑化し、それによりLWRを改良するのに有益であるが、この流れ/弛みにより、フォトレジストがより短く/より薄くなり、図13に示されるように、レジストのフットに流れ出る。従来のプラズマによって実現されるフォトレジスト・リフローの比較的高い速度は、マスク高さを大幅に減少させ、これは、下にある層に対する不十分なエッチング選択性、下にある層への改良されたLWRの良好でない転写、および凹/凸フィーチャの良好でないパターン転写をもたらす。これらの因子はすべて、高い×ローディングを促し、これは望ましくない。

20

【0137】

代わりにイオン-イオンプラズマレジームで処理することによって、フォトレジスト・リフローの速度を遅くすることができ、LWRと×ローディングとの間の妥協を最小限にすることができる。イオン-イオンプラズマ処理は、従来のプラズマで見られるのと同等のLWR改良を実現するが、より遅いリフローの速度、フォトレジスト高さのより少ない消耗(すなわちより少ない弛み)、および異なるパターン形状間のより小さいCDバイアスローディングを含む。イオン-イオンプラズマによって消耗されるフォトレジスト高さがより少ないので、残っているフォトレジストの量が多くなり、下にある層の選択性が改良される。これは、より多くのフォトレジストが残っており、下にある層を保護する助けとなるからである。イオン-イオンプラズマは、EUVフォトレジストと193nmフォトレジストとの両方、ならびに適切であれば他のタイプのフォトレジストをリフローするために使用されることがある。

30

【0138】

イオン-イオンプラズマの低い電子密度は、フォトレジスト材料の局所加熱を防止する助けとなる。これは、フォトレジスト・リフローの速度を遅くし、フォトレジストフットが比較的穏やかに除去されるようにし、フォトレジスト損失の量を最小限にする。さらに、イオン-イオンプラズマの低い電子密度が、低い総イオン密度を可能にし、これは、表面に対する低いイオン流束に相關する。これは、イオン衝撃から生じるフォトレジスト損失の量を減少させる助けとなる。バイアスパルシングを使用して、イオン流束のさらなる制御を提供することができる。

40

【0139】

イオン-イオンプラズマを使用するとき、(下側電極を介して) 基板に印加される総バイアス電圧の範囲を高めることができる。低いイオン流束は、基板表面への総エネルギー流束を減少させる。したがって、従来は、<30Vのバイアス電圧(および合計のエネルギー流束)に制限されていた。バイアス電圧がイオンサイズにも依存することに留意されたい。イオンが大きければ大きいほど、印加することができるバイアスが小さくなる。バイアス電圧は、フォトレジストフットを切削する役割をする。しかし、バイアスが高すぎる場合、フォトレジストでの架橋を誘発することになる。架橋は、総エネルギー流束が増

50

加するにつれて、時間と共にフォトレジストを硬化させて崩す。したがって、高イオンエネルギー流束のシステムでは、バイアス電圧を低く保たなければならない。しかし、イオン-イオンプラズマシステムでは、総イオン流束が低く、したがって、印加される総バイアス電圧を増加させることができる。バイアス電圧（Vb）が高ければ高いほど、フォトレジストフットを切削するのに効果的になり、フォトレジスト架橋効果を誘発しない。バイアス電圧は、イオン-イオンプラズマを使用するとき、200Vb程の高さになることがある。

#### 【0140】

上述したように、フォトレジスト・リフロー・プロセスは、2つの主な操作を含むことがある。第1の操作は、リフローステップであり、第2の操作は、フット切削ステップである。イオン-イオンプラズマレジームで第1のステップを行うために、上部サブチャンバ内で、例えばH<sub>2</sub>を含有するプラズマ発生ガスからプラズマが発生する。いくつかの他の場合には、プラズマ発生ガスは、Ar、H<sub>2</sub> / HBr、Ar / HBr、またはHBrでよい。さらに、プラズマ発生ガスは、N<sub>2</sub>および/またはHeSTGなどの不活性ガスを含むこともある。H<sub>2</sub>の流量は、約100～500sccm、例えば約100～300sccmの間でよい。N<sub>2</sub>の流量は、約0～300sccmの間でよく、HeSTGの流量は、約0～100sccmの間でよい。グリッドの下で、イオン-イオンプラズマが生じ、基板と相互作用して、フォトレジストをリフローさせる。プラズマ発生ガスの総流量は、約100～500sccmの間でよい。チャンバ圧力は、約5～20mTの間でよい。基板温度は、約20～60の間でよい。プラズマを発生させるために使用される電力は、約300～1000ワット/ステーションの間でよい。基板は、約0～200Vの間、例えば約50～200Vの間でバイアスされることがある。1回のフォトレジスト・リフロー操作は、約5～45秒の間、例えば、約5～30秒の間の継続時間を持つことがある。TCTTは、約0.5～1.5の間、例えば約1～1.5の間でよい。

#### 【0141】

エッチング性能をさらに改良するために、以下のパラメータを調整することができる。圧力（5～20mT）、総流量（100～500sccm）、H<sub>2</sub>流量（0～300sccm）、静電チャック温度（20～60）、TCPパワー（300W～1000W）、基板上のバイアス電圧（0～200V）、バイアス電圧パルスデューティサイクル（100～200Hz、250=50%）、プロセス時間（5～30s）。

#### 【0142】

代替方法は、フォトレジスト・リフローとフット切削との両方を行うために、1ステップのH<sub>2</sub>条件を利用する。この場合、プラズマ発生ガスは、例えば、H<sub>2</sub>、N<sub>2</sub>、およびHeSTGを含むことがある。

#### 【0143】

2ステップリフロー・プロセスの実施形態に戻ると、フォトレジスト・リフロー・プロセスの第2のステップは、イオン-イオンプラズマレジームで行われることがある。上部サブチャンバ内で、例えばArを含有するプラズマ発生ガス（いくつかの場合には、このステップに関するプラズマ発生ガスは、HBrまたはHBr / Arを含む）から、プラズマが発生する。他のプロセス条件は、第1のフォトレジスト・リフロー・プロセスに関して上述したものと同じでよい。

#### 【0144】

一例では、基板は、最初は、パターン形成されたEUVフォトレジストを上に有する。パターン形成されたフォトレジストのLWRは、約6nmであり、フォトレジストは、約60nmの高さを有する。H<sub>2</sub>から発生するイオン-イオンプラズマで、フォトレジスト・リフロー操作が行われる。第2の操作では、Arから発生するイオン-イオンプラズマで、フォトレジストフット除去が行われる。これら2つのプラズマ処理により、LWRは、約3.7nmに減少され、フォトレジスト高さは、約40nmに減少される。

#### 【0145】

シャロートレンチ・アイソレーション・エッチング

10

20

30

40

50

シャロートレンチアイソレーション (S T I) を使用して、隣接するトランジスタの間で電流が漏れるのを防止することができる。トレンチは、トランジスタを互いに絶縁する働きをする。S T I構造を形成する際の重要なステップは、トレンチのパターンを基板(例えば、シリコン)にエッチングするステップと、トレンチを充填するために誘電体材料を堆積するステップと、化学機械研磨(C M P)などの技法を使用して余剰の誘電体を除去するステップとを含む。小さなフィーチャ寸法で、S T Iエッチングプロセスは、アスペクト比に依存するエッチング深さおよびプロファイル結果を示す。すなわち、高いアスペクト比の構造(しばしば、密集フィーチャ領域内に存在する)は、低いアスペクト比の構造(しばしば、より離散された領域内に存在する)とは異なるエッチング結果を示す。このアスペクト比依存性は、2つのタイプのフィーチャでの異なる濃度のエッチャントおよび副生成物により生じると考えられる。 10

#### 【0146】

図14は、プロファイルローディングの問題を示している。図14の左図は、基板1401に関する所望のエッチャントプロファイルを示している。基板1401は、トレンチがエッチングされる場所を画定するために使用されるマスク層1403を有する。高アスペクト比フィーチャ1405と低アスペクト比フィーチャ1407とは、どちらも垂直エッチングプロファイルを有するべきである。図14の右図は、従来のプラズマエッチングによって典型的に実現されるエッチャントプロファイルを示す。高アスペクト比のフィーチャ1405は、垂直エッチャントプロファイルを示すが、低アスペクト比のフィーチャ1407は、はるかに大きなテープ状のプロファイルを示す。これらの相違は、プロファイルローディングと呼ばれる。さらに、低アスペクト比のフィーチャ1407は、より大きな度合いでエッチャントされ、離散されたフィーチャ1407に関して、エッチャント深さはより低くなる。このエッチャント深さの差は、エッチャント深さローディングまたは深さローディングと呼ばれる。プロファイルローディングとエッチャント深さローディングとの両方を最小限にすべきである。 20

#### 【0147】

高アスペクト比の密集フィーチャと低アスペクト比の離散フィーチャとの間のエッチャント結果の不均一性を最小限にするための1つの技法は、バイアスパルシングを使用するものである。基板に印加されるバイアスをパルスさせることによって、フィーチャへのエッチャントの拡散が、2つのタイプのフィーチャの間でより均一になることがあり、これは、2つのタイプのフィーチャに対して、より同等のラジカル:イオン流束をもたらす。また、バイアスパルシングは、ウェハからバルクプラズマへの副生成物の総流束を減少させることができ、これは、チャンバ内の副生成物の総量を最小限にする。チャンバ内での副生成物の存在は、高いアスペクト比の密集フィーチャと、低いアスペクト比の離散フィーチャとの間のエッチャントプロファイル差(すなわちプロファイルローディング)の一因であるので、チャンバ内の副生成物の量の減少は、有利には、プロファイルローディングの量を最小限にする。 30

#### 【0148】

優れたS T Iエッチャント結果は、イオン-イオンプラズマレジームでエッチャントプロセスを行うことによって実現することができる。イオン-イオンプラズマは、いくつかの理由から有益である。第1に、イオン-イオンプラズマは、従来のプラズマよりも低い総イオン密度を有する。この低いイオン密度は、基板表面に対するより高いラジカル:イオン流束比を実現することによって、エッチャント深さのアスペクト比依存性を少なくとも一部減少させる。イオン-イオンプラズマの文脈で、バイアスパルシングを使用することができ、高いアスペクト比の密集構造と低いアスペクト比の離散構造との間でのより均一なラジカル:イオン流束比を実現する。ラジカル:イオン流束は、イオン-イオンプラズマが使用される場合、従来のプラズマに比べて、これら2つのタイプの構造の間で均一である。 40

#### 【0149】

さらに、イオン-イオンプラズマは、イオン-イオンプラズマの低いイオン流束が副生 50

成物の生成の速度を最小限にするので有益である。副生成物がよりゆっくりと生成される場合、それらは、解離されて不揮発性の副生成物になる前に、反応チャンバからより完全に除去することができる。これらの不揮発性の副生成物は、2つのタイプのフィーチャの間で見られるエッチングプロファイル差の一因となる。したがって、より遅い副生成物の生成が、より効率的な副生成物除去をもたらし、これはさらに、高アスペクト比と低アスペクト比のフィーチャとの間でのより均一なエッチングプロファイルをもたらす。

#### 【0150】

イオン-イオンプラズマの別の利点は、エッチング中に揮発性の副生成物が生じるとき、それらの副生成物が、イオン-イオンプラズマの低い電子密度および低い電子温度により、問題となる不揮発性の副生成物に解離する可能性がはるかに低いことである。これにより、揮発性の副生成物は、解離されて不揮発性の（「粘着性の」）副生成物になる前に、はるかに効率的に除去されるようになる。副生成物をチャンバからより良く除去することができる所以、高アスペクト比の密集フィーチャと低アスペクト比の離散フィーチャとの間でのプロファイルローディングが実質的に小さくなり、エッチング結果がより均一になる。

10

#### 【0151】

図15は、従来のプラズマ（左図）およびイオン-イオンプラズマ（右図）の下でのSTIエッチングプロセスを示す。従来のプラズマが使用される場合、比較的高い電子密度および高い電子温度により、例えば、揮発性のSiBr<sub>4</sub>が不揮発性のSiBr<sub>3</sub>に解離する。次いで、不揮発性のSiBr<sub>3</sub>は、基板1501上、しばしば低アスペクト比のフィーチャ1507内に付着する。対照的に、イオン-イオンプラズマが使用される場合、電子の温度および密度は、SiBr<sub>4</sub>が不揮発性の副生成物に実質的に解離しないほど十分に低く、揮発性の状態でチャンバから効果的に除去することができる。したがって、不揮発性の副生成物の問題がはるかに小さくなり、側壁があまり不動態化されず、エッチングプロファイルは、高アスペクト比のフィーチャ1505と低アスペクト比のフィーチャ1507との両方に関して垂直である。

20

#### 【0152】

一部の実施形態では、STIエッチングプロセスは、少なくとも2つの異なるタイプのフィーチャ、すなわち高アスペクト比のフィーチャと低アスペクト比のフィーチャとを同時にエッチングすることを含むことがある。高アスペクト比フィーチャは、約10以上のアスペクト比を有することがあり、一方、低アスペクト比フィーチャは、約1以下のアスペクト比を有することがある。プラズマ発生ガスは、HBrおよびCl<sub>2</sub>を含むことがある。イオン-イオンプラズマでのエッチング後、高アスペクト比のフィーチャのエッチング深さは、約150nmとなり、低アスペクト比のフィーチャのエッチング深さは、約155nmとなることがある。高アスペクト比のフィーチャのエッチング深さは、低アスペクト比のフィーチャのエッチング深さの少なくとも約95%となることがある。すなわち、2つのエッチング深さは、ほぼ同じとなることがある。一部の場合には、高アスペクト比のフィーチャと低アスペクト比のフィーチャのエッチング深さの差は、約5nm以下である。さらに、高アスペクト比のフィーチャのエッチングプロファイルは、少なくとも約88°（90°が、完全に垂直を表す）であることがあり、低アスペクト比のフィーチャのエッチングプロファイルは、少なくとも約85°であることがある。

30

#### 【0153】

イオン-イオンレジームでのシャロートレンチ・アイソレーション・エッチングプロセスを行うために、上部サブチャンバ内で、例えばHBrを含有するプラズマ発生ガスからプラズマが発生する。グリッドの下で、イオン-イオンプラズマが生じ、基板と相互作用して、基板材料をエッチングする。プラズマ発生ガスの流量は、約50～500sccmの間でよい。チャンバ圧力は、約2～100mTorr（約0.267～13.3Pa）の間、例えば約5～90mTorr（約0.667～12.0Pa）の間でよい。チャンバ温度は、約50～130の間でよい。基板温度は、約20～100の間でよい。プラズマを発生させるために使用される電力は、約300～1500ワット/ステーション

40

50

の間でよい。プラズマを発生させるために使用されるR F周波数は、約13MHzでよい。基板は、約300~1200Vの間でバイアスされることがある。1回のSTIエッチング操作は、約30~100秒の間の継続時間有することがある。

#### 【0154】

##### [装置]

本明細書で記載する方法は、任意の適切な装置によって実施することができる。適切な装置は、チャンバと、本明細書で記載するようなエッチング条件を提供および維持するための電子ハードウェアと、を備えるものである。適切な装置は、さらに、そのような条件を達成するようにハードウェアを制御するため、さらにはFETのゲート電極をエッチングするなどの応用に適した一連のプロセス工程を実行するための、命令を有するシステムコントローラを備える。いくつかの実施形態において、ハードウェアには、プロセスツールに含まれる1つ以上の処理ステーションを含むことができる。

#### 【0155】

図1に戻ると、これは、いくつかの実施形態による誘導結合型プラズマエッチング装置100の断面図を示している。前述のように、本明細書に記載の実施形態は、同じく誘導結合型以外のプラズマを用いて実施することもできる。誘導結合型プラズマエッチング装置100は、チャンバ壁101と窓111によって構造的に画成される全体エッチングチャンバを備える。チャンバ壁101は、典型的には、ステンレス鋼またはアルミニウムで製造される。窓111は、典型的には、石英または他の誘電材料で製造される。内部プラズマグリッド150によって、全体エッチングチャンバを、上部サブチャンバ102と下部サブチャンバ103とに分割している。他のいくつかの実現形態では、より複雑なプラズマグリッドアセンブリが用いられる。例えば、プラズマグリッドアセンブリは、図4および5に示すように、複数のグリッドと、さらに支持構造および駆動要素を含むことができる。図1の実施形態に戻って、下部サブチャンバ103内の内部底面の近くに、チャック117が配置されている。チャック117は、エッチングプロセスがその上で実施される半導体ウェハ（すなわち「ウェハ」）119を受けて、保持するように構成されている。チャック117は、ウェハがある場合にこれを支持するための静電チャックとすることができます。いくつかの実施形態において、エッジリング（図示せず）がチャック117を取り囲んでおり、それは、チャック117上にウェハがある場合にそのウェハ表面と略同一平面にある上面を有する。チャック117は、さらに、ウェハのチャッキングおよびデチャッキングを可能にするために、静電電極を有する。この目的のために、フィルタおよびDCクランプ電源を設けることができる。また、チャック117からウェハを持ち上げるための他の制御システムを設けることができる。チャック117は、R F電源123を用いて帯電させることができる。R F電源123は、接続127を介して整合回路121に接続されている。整合回路121は、接続125を介してチャック117に接続されている。このようにして、R F電源123は、チャック117に接続されている。

#### 【0156】

窓111の上方に、コイル133が配置されている。コイル133は、導電性材料で製造されており、少なくとも1ターンの完全なターンを含んでいる。図1に示す例示的なコイル133は、3ターンを含んでいる。コイル133の断面の記号「X」は、回転して紙面に入るようにコイル133が伸びていることを示している。逆に、コイル133の記号「・」は、回転して紙面から出るようにコイル133が伸びていることを示している。R F電源141は、コイル133にR F電力を供給するように構成されている。通常、R F電源141は、接続145を介して整合回路139に接続されている。整合回路139は、接続143を介してコイル133に接続されている。このようにして、R F電源141は、コイル133に接続されている。オプションのファラデーシールド149が、コイル133と窓111との間に配置される。ファラデーシールド149は、コイル133に対して離間した関係に維持される。ファラデーシールド149は、窓111の直ぐ上に配置される。コイル133、ファラデーシールド149、および窓111は、それぞれ、相互に略平行となるように構成されている。金属またはその他の種がプラズマチャンバの誘電

10

20

30

40

50

体窓に付着することを、ファラデーシールドによって防ぐことができる。

【0157】

上部チャンバに配置されたメイン注入口160を介して、さらに／またはSTGとも呼ばれるサイド注入口170を介して、処理ガスを供給することができる。ガス排出口は図示していない。また、操作的プラズマ処理中の、真空制御、およびチャンバからのガス状副生成物の除去を可能にするために、チャンバ101に接続されたポンプも、図示していない。

【0158】

装置の作動中には、注入口160および／または170を介して、1種以上の反応ガスを供給することができる。いくつかの実施形態において、ガスは、メイン注入口のみを介して、またはサイド注入口のみを介して供給することができる。いくつかの例では、注入口は、シャワー・ヘッドで置き換えることができる。ファラデーシールド149および／またはグリッド150は、チャンバへの処理ガスの送出を可能にする内部チャネルおよび孔を有することができる。すなわち、ファラデーシールド149およびグリッド150のいずれかまたは両方は、処理ガスを送出するためのシャワー・ヘッドとして機能することができる。

10

【0159】

高周波電力がRF電源141からコイル133に印加され、これにより、RF電流がコイル133に流れる。コイル133に流れるRF電流によって、コイル133の周りに電磁場が発生する。この電磁場によって、上部サブチャンバ102内に誘導電流が発生する。この誘導電流が、上部サブチャンバ102内にあるガスに作用することで、上部サブチャンバ102内に電子イオンプラズマが発生する。内部プラズマグリッド150によって、下部サブチャンバ103内の高温電子の量が制限される。いくつかの実施形態において、装置は、下部サブチャンバ内にあるプラズマがイオンイオンプラズマとなるように、設計され、操作される。

20

【0160】

上部の電子イオンプラズマと、下部のイオンイオンプラズマは、どちらも、正イオンと負イオンを含むが、イオンイオンプラズマのほうが、負イオン：正イオン比が大きい。種々のイオンおよびラジカルとウェハ119との物理的および化学的相互作用によって、ウェハのフィーチャが選択的にエッチングされる。揮発性のエッチング副生成物は、排出口（図示せず）を介して下部サブチャンバから除去される。重要なことは、このような揮発性副生成物が高温電子に曝されることは実質的ないので、それらが不揮発性の「粘着性」解離生成物に解離される恐れはない。

30

【0161】

典型的には、本明細書で開示するチャックは、約30～約250の範囲の、好みくは約30～150の範囲の高温で作動する。この温度は、エッチングプロセス処理および具体的なレシピに依存する。また、チャンバ101は、約1mTorr（約0.133Pa）～約95mTorr（約12.7Pa）の範囲、または約5～20mTorr（約0.667～2.67Pa）の範囲の圧力で作動する。

40

【0162】

図示はしていないが、チャンバ101は、通常、クリーンルームまたは製造施設に設置されると、様々な設備に連結される。それらの設備には、処理ガス、真空、温度制御、環境粒子制御を提供する配管設備が含まれる。チャンバ101がターゲット製造施設に設置されると、このような設備が連結される。さらに、チャンバ101を移送室に連結することができ、これによって、ロボット技術により、通常の自動操作を用いて、半導体ウェハをチャンバ101に出し入れする移送が可能となる。

【0163】

図2A、2Bおよび3A～3Dは、本明細書で記載する実施形態による内部プラズマグリッドの例を示している。いくつかの例では、各グリッドは、径方向外向きまたは略径方向外向きに延びるスロットを有することができる。これらまたは他の例において、スロッ

50

トは、図3C、3Dに示すように、より特異な非直線形状とすることができます。図2Bの実施形態では、3種類のスロットがある。3種類のスロットはそれぞれ、異なるスロット長を有する。図2Bに示すスロットは、上述のように、下部サブチャンバにおいてイオンイオンプラズマを生成するのに適したアスペクト比を有する。図2Aおよび3A～3Dに示すスロットは、縮尺通りに描かれていない場合がある。

#### 【0164】

##### 【システムコントローラ】

いくつかの実施形態において、システムコントローラ（1つ以上の物理コントローラまたは論理コントローラを含むことができる）により、エッチングチャンバの動作の一部またはすべてを制御する。システムコントローラは、1つ以上のメモリデバイスと、1つ以上のプロセッサとを備えることができる。プロセッサは、中央処理装置（CPU）またはコンピュータ、アナログおよび/またはデジタル入力/出力接続、ステッピングモータ・コントローラボード、および他の同様の構成要素を含むことができる。適切な制御動作を実現するための命令が、プロセッサ上で実行される。これらの命令は、コントローラに関連付けられたメモリデバイスに格納されていてもよいし、あるいはネットワークを介して提供されるものであってもよい。いくつかの実施形態において、システムコントローラは、システム制御ソフトウェアを実行する。

#### 【0165】

システム制御ソフトウェアは、以下のチャンバ動作条件のうち1つ以上の適用のタイミングおよび/または大きさを制御するための命令を含むことができる：ガスの混合および/または組成、チャンバ圧力、チャンバ温度、ウェハ温度、ウェハに印加するバイアス、コイルまたは他のプラズマ発生要素に印加する周波数および電力、ウェハ位置、ウェハ移動速度、グリッド位置、グリッド移動速度、ならびにツールによって実施される具体的なプロセスのその他パラメータ。システム制御ソフトウェアは、任意の適切な方法で構成することができる。例えば、種々のプロセスツール・プロセスを実施するために必要なプロセスツール構成要素の動作を制御するための、各種プロセスツール構成要素サブルーチンまたは制御オブジェクトを作成することができる。システム制御ソフトウェアは、任意の適切なコンピュータ可読プログラミング言語でコーディングすることができる。

#### 【0166】

いくつかの実施形態において、システム制御ソフトウェアは、上記の各種パラメータを制御するための入力/出力制御（I/O C）シーケンシング命令を含む。例えば、半導体製造プロセスの各段階は、システムコントローラで実行するための1つ以上の命令を含むことができる。例えば、エッチング段階のプロセス条件を設定するための命令は、対応するエッチングレシピ段階に含むことができる。一部の実施形態では、それらのレシピ段階は、あるプロセス段階のすべての命令がそのプロセス段階と同時に実行されるように、順に配列することができる。

#### 【0167】

いくつかの実施形態において、他のコンピュータソフトウェアおよび/またはプログラムを採用することができる。本目的のためのプログラムまたはプログラム部分の例には、基板位置決めプログラム、グリッドアセンブリ位置決めプログラム、処理ガス組成制御プログラム、圧力制御プログラム、ヒータ制御プログラム、およびRF電源制御プログラムが含まれる。

#### 【0168】

一部の例において、コントローラは、ガス濃度、ウェハの移動、グリッドの移動、さらに/またはコイルおよび/もしくは静電チャックに供給される電力、を制御する。コントローラは、例えば、必要な反応物質（複数の場合もある）を適切な濃度で供給する1種以上の流入ガス流を発生させるように、関連する弁を開閉することにより、ガス濃度を制御することができる。ウェハの移動は、例えば、所望の移動をウェハ位置決めシステムに指示することにより、制御することができる。グリッドの移動は、グリッドアセンブリの所望の位置決めを駆動要素（例えば、回転アクチュエータ、リフタ、および/または他の駆

10

20

30

40

50

動要素)に指示することにより、制御することができる。一例では、コントローラは、下部ゾーン・プラズマにおいて、いくつかのプラズマ条件(電子温度、電子密度、イオン密度、電子に対する正イオンの比率などが含まれるが、これらに限定されない)を達成するために、1つまたは複数のプラズマグリッドの回転を、回転アクチュエータに指示する。いくつかの実現形態において、コントローラは、ウェハの異なる部分で異なるプラズマ条件を実現するように構成される(例えば、径方向にわたって、プラズマ条件を調整することができる)。コイルおよび/またはチャックに供給される電力は、上部サブチャンバ内で所望の電子イオンプラズマを発生させるための特定のRF電力レベルを与えるように制御することができる。さらに、下部サブチャンバ内で電子イオンプラズマが形成されないような条件で、静電チャックに電力が供給されるように、コントローラを構成することができる。すなわち、コントローラは、下部サブチャンバ内でイオンイオンプラズマ(または、少なくとも、適切な低実効電子温度および密度を有するプラズマ)を維持するように構成される。コントローラは、これらまたはその他の側面を、センサ出力(例えば、電力、電位、圧力などが所定の閾値に達したとき)、操作のタイミング(例えば、プロセスの所定の時点で弁を開放する)に基づいて、またはユーザから受ける指示に基づいて、制御することができる。10

#### 【0169】

上記の種々のハードウェアおよび方法の実施形態は、例えば、半導体デバイス、ディスプレイ、LED、太陽電池パネルなどの作製または製造のために、リソグラフィパターニング・ツールまたはプロセスとともに用いることができる。一般に、そのようなツール/プロセスは、必ずしもそうではないが、共通の製造設備で一緒に使用または実施される。20

#### 【0170】

リソグラフィによる膜のパターニングは、通常、以下の工程の一部またはすべてを含み、各工程は、いくつかの考え得るツールによって実施可能となる。(1) 例えばシリコン窒化膜がその上に形成された基板であるワークピースの上に、スピンドルまたはスプレー式のツールを用いて、フォトレジストを塗布する；(2) ホットプレートまたは炉または他の適切な硬化ツールを用いて、フォトレジストを硬化させる；(3) ウェハステッパーなどのツールによって、可視光線または紫外線またはX線でフォトレジストを露光する；(4) ウェットベンチまたはスプレー式現像装置などのツールを用いて、選択的にレジストを除去するようにレジストを現像し、これによりパターンを形成する；(5) ドライまたはプラズマアシスト・エッチングツールを用いて、レジストパターンを下の膜またはワークピースに転写する；(6) RFまたはマイクロ波プラズマ・レジストストリッパーなどのツールを用いて、レジストを剥離する。一部の実施形態では、フォトレジストを塗布する前に、アッシャブル・ハードマスク層(アモルファスカーボン層など)および他の適切なハードマスク(反射防止層など)を成膜することができる。30

#### 【0171】

本明細書で記載した構成および/または手法は、当然のことながら、本質的に例示的なものであり、これらの具体的な実施形態または例は、限定的な意味で解釈されるべきではなく、数多くの変形が可能である。本明細書に記載の具体的なルーチンまたは方法は、多数の処理戦略のうちの1つまたは複数を提示し得るものである。従って、例示した種々の処理動作は、例示した順序で、他の順序で、並列に、実行することができ、あるいは場合によって、省略することもできる。同様に、上記のプロセスの順序を変更することができる。40

#### 【0172】

本開示の対象には、本明細書で開示した様々なプロセス、システムおよび構成の新規かつ非自明なすべての組み合わせおよび部分的組み合わせ、さらには、その他の特徴、機能、処理動作、および/または特性、ならびにそれらのあらゆる均等物が含まれる。

#### 【0173】

##### [実験]

本開示の方法および装置によって、半導体基板上の半製品のデバイスのエッチングが改50

善されることを、実験により確認した。プラズマグリッドを使用した場合には、エッティングされた製品は、良好な選択性、プロファイル角、疎／密ローディング、および全面エッティング均一性を示している。

【0174】

図16Aおよび図16Bは、従来の高圧技術(16A)と、プラズマグリッドを用いた本発明の実施形態(16B)により、エッティングされたFinFET構造の走査型電子顕微鏡(SEM: Scanning Electron Microscope)像を示している。図16Aに示すように、従来技術によると、ウェハの中心とエッジとの間に深刻な不均一性が認められる結果となる。I/Dローディングが大きく、材料間の選択性が低かった。一方、図16Bに示すように、プラズマグリッドを使用することで、中心からエッジへの均一性は、実質的に向上する。また、I/Dローディングは、はるかに低く、選択性が向上した。本実験は、FinFETの高さを表す厚さまで薄厚化し、フルパターンウェハのエッティングをシミュレートするために50%SiNクーポンで覆ったSiキャリアウェハ上で、実施した。FinFET構造は、プロファイルのテーパを最小限に抑えるように、65%でオーバーエッティングされた。

10

【0175】

図17Aおよび図17Bは、従来の低圧技術(17A)と、プラズマグリッドを用いた本発明の実施形態(17B)により、エッティングされたフィーチャのSEM像を示している。従来技術は、シリコンと酸化物との間の比較的低い選択性を示し、エッティングされたフィーチャはテーパ状のプロファイルを有し、また、I/Dローディングは良好ではなかった。一方、図17Bに示すように、ソースグリッドによって、向上した選択性(無限大の選択性)、より垂直なプロファイル角が得られ、また、I/Dローディングは略なくなつた。本実験は、パターンウェハから切り離されてキャリアウェハの中心に配置されたチップ上で、実施した。本実験は、FinFETの高さを表す厚さまで薄厚化し、フルパターンウェハのエッティングをシミュレートするために50%SiNクーポンで覆ったSiキャリアウェハ上で、実施した。

20

【0176】

図18は、プラズマグリッドを用いることなく、いくつかのレジームに従ってエッティングされたフィーチャの様々なSEM像を示している。2通りの異なる圧力と、4通りの異なる総流量とを用いた。実効電子温度(Te)は、圧力の増加に伴って低下する。滞留時間は、総流量の増加に伴って減少する。それぞれの圧力で、総流量を増加させると、エッティング結果が向上する。特に、高流量のケースは、より良好な(より垂直な)プロファイル角、および向上した選択性(より多いマスク残り)を示している。しかしながら、これらの改善は、より良好ではないI/Dローディングおよび中心からエッジへの均一性により、軽減される。この高流量での結果は、ガスの形態で掃去されない場合のいくつかの副生成物および/または解離生成物が、図6A~6Cに示すようにフィーチャの側壁および/または底部に付着し得ることで不良なエッティング結果となるという考えを裏付けるものである。総流量がより高いと、これらの副生成物が、より効果的に反応チャンバから掃去されて、エッティング不良が生じる可能性がより低くなる。

30

【0177】

図19は、ソース-ドレインリセスエッティングプロセスによってエッティングされたフィーチャのSEMを表す。実施例1に関して上述したように、ソース-ドレインリセスエッティングは、(1)垂直エッティング、(2)横方向エッティング、および(3)酸化ステップを含むマルチステッププロセスである。上図は、従来のプラズマを使用して処理した基板を示す。この場合、エッティング形状は、明瞭なスキヤロップエッジを示す。これらのスキヤロップエッジは、さらなる横方向エッティングを防止する厚い酸化層により生じる。対照的に、下図は、イオン-イオンプラズマを使用して処理した基板を示す。ここで、エッティングされた領域は、はるかに滑らかであり、非常に不明瞭なスキヤロップ、およびより丸まつた/滑らかなエッジを有する。イオン-イオンプラズマは、より加工しやすい酸化物層を生じ、これは、依然として側壁をオーバーエッティングから保護しながら、側壁を平滑

40

50

化し、所望の形状を形成するためにいくらかの量のエッティングを可能にする。イオン - イオンプラズマでの低い電子密度は、シリコン材料の比較的穏やかな酸化を可能にする。これは、スキヤロップを最小にし、プロファイル制御を向上させる。

【0178】

図20は、ソース - ドレインリセスエッティングプロセスによってイオン - イオンプラズマでエッティングしたフィーチャの様々なSEMを示す。図示されるように、イオン - イオンプラズマが使用される場合、多くの異なるフィーチャ形状を実現することができる。これは、多くの新規の異なるソース - ドレインリセス形状の可能性を開く。

【0179】

図21は、様々なプラズマレジームを使用して、シャロートレンチ・アイソレーション・エッティングプロセスの下で形成したフィーチャのSEMを表す。図の上側部分および中央部分は、従来のプラズマの下で処理した基板に関する。上側の基板は、約75%D Cの基板バイアスパルシングを有し、一方、中央の基板は、約25%D Cの基板バイアスパルシングを有していた。図の下側部分は、イオン - イオンプラズマレジームの下で処理した基板に関する、約60%D Cの基板バイアスパルシングを有していた。すべての基板が、高アスペクト比のフィーチャに関して良好な垂直プロファイルを示した。イオン - イオンプラズマで処理した基板は、低アスペクト比のフィーチャでの改良されたエッティングプロファイルを示した（従来のプラズマに関して見られる84°に対して85°）。さらに、イオン - イオンプラズマレジームで処理した基板は、はるかに良いエッティング深さローディングを示した。従来のプラズマは、約25nmおよび16nmのエッティング深さローディングを生じたが、イオン - イオンプラズマは、わずか約5nmのエッティング深さローディングを生じた。総エッティング深さは、約230nmであった。

10

20

30

【0180】

様々な実験によって、プラズマグリッドを使用した結果、極めて良好な選択性、プロファイル角、I / Dローディング、中心からエッジへの均一性を伴うエッティングプロセスが得られることが示された。いくつかの例において、選択性（すなわち、Siのエッティング速度：酸化物のエッティング速度）は、約10より大きいか、または約100よりも大きい。実際に、いくつかの例では、プラズマグリッドを用いることで、無限大の選択性が得られる場合がある。このような場合、酸化物材料がエッティングされることは略なく、むしろ、酸化物表面に少量の堆積が生じることがある。多くのケースにおいて得られるプロファイル角は、略垂直（例えば、約89°超）である。いくつかの実現形態において、I / Dローディングは、約2°未満であることが示された。また、いくつかの実現形態における中心からエッジへの均一性は、約2nm未満であった。

本発明は、たとえば、以下のような態様で実現することもできる。

適用例1：

プラズマを処理する方法であって、

反応チャンバ内に基板を受け取るステップであって、前記反応チャンバが、前記反応チャンバの内部を、プラズマ発生器の近傍の上部サブチャンバと、基板ホルダの近傍の下部サブチャンバと、に分割するグリッド構造を備えるステップと、

プラズマ発生ガスを前記上部サブチャンバに流すステップと、

40

前記上部サブチャンバ内で、前記プラズマ発生ガスから、第1の電子密度を有する第1のプラズマを発生させ、前記下部サブチャンバ内で、第2のプラズマを発生させるステップであって、前記第2のプラズマが、前記第1の電子密度の約10分の1未満の第2の電子密度を有するイオン - イオンプラズマであるステップと、

前記第2のプラズマを用いて前記基板を処理して、ソースドレインリセスエッティング、FinFETゲートエッティング、ダミーポリシリコン除去、シャロートレンチ・アイソレーション・エッティング、またはフォトレジスト・リフローでのステップを行うステップとを含む方法。

適用例2：

適用例1の方法であって、

50

前記第1のプラズマが、約2eV以上の中の第1の電子温度を有し、前記第2のプラズマが、約1eV以下の第2の実効電子温度を有する、方法。

適用例3：

適用例1または2の方法であって、

前記第2の電子密度が、約 $5 \times 10^9 \text{ cm}^{-3}$ 以下である、方法。

適用例4：

適用例1から3のいずれか一項の方法であって、

前記第2のプラズマ中の負イオン：正イオンの比が、約0.5～1の間である、方法。

適用例5：

適用例1から4のいずれか一項の方法であって、

10

ソースドレインリセスをエッティングするために行われ、

前記基板を垂直方向にエッティングするために第1のエッティングプロセスを行って、垂直エッティングフィーチャを形成するステップと、

前記垂直エッティングフィーチャの内部で前記基板を水平方向にエッティングするために、第2のエッティングプロセスを行うステップと、

前記垂直エッティングフィーチャ内部に酸化層を形成するために、酸化プロセスを行うステップと、

前記垂直エッティングフィーチャ内にソースドレインリセスを形成するために前記方法を繰り返すステップと、を含み、

前記第1のエッティングプロセス、第2のエッティングプロセス、および酸化プロセスがすべて、各プロセスでの前記第2のプラズマがイオン-イオンプラズマであるように、前記グリッド構造を有する前記反応チャンバ内で行われる、方法。

20

適用例6：

適用例5の方法であって、

前記第1のエッティングプロセスが、C<sub>1</sub>を含む第1のプラズマ発生ガスを用いて行われ、前記第2のエッティングプロセスが、N<sub>F</sub><sub>3</sub>およびC<sub>1</sub>を含む第2のプラズマ発生ガスを用いて行われ、前記酸化プロセスが、酸素を含む第3のプラズマ発生ガスを用いて行われる、方法。

適用例7：

適用例5の方法であって、

30

凹角形状を有する垂直エッティングフィーチャを形成するために、前記方法が繰り返される、方法。

適用例8：

適用例1から7のいずれか一項の方法であって、

シャロートレンチ・アイソレーション・エッティングを行うために行われ、

前記プラズマ発生ガスが、HBrを含み、

前記基板が、前記エッティング中に約300～1200Vの間にバイアスされる、方法。

適用例9：

適用例8の方法であって、

前記プラズマ発生ガスが、約50～500sccmの間の流量で流れ、さらに、C<sub>1</sub><sub>2</sub>を含む、方法。

40

適用例10：

適用例8の方法であって、

前記エッティングプロセスが、少なくとも第1のフィーチャ形状と第2のフィーチャ形状を同時にエッティングするステップを含み、前記第1のフィーチャ形状が、約10以上のアスペクト比を有し、前記第2のフィーチャ形状が、約1以下のアスペクト比を有し、

エッティング後、前記第1のフィーチャのエッティング深さが、前記第2のフィーチャの前記エッティング深さの少なくとも約95%である、方法。

適用例11：

適用例10の方法であって、

50

エッチング後、前記第1のフィーチャが、少なくとも約88°のエッチングプロファイルを有し、前記第2のフィーチャが、少なくとも約85°のエッチングプロファイルを有する、方法。

適用例12：

適用例1から11のいずれか一項の方法であって、

フォトレジスト・リフロープロセスを行うために行われ、

前記反応チャンバ内に受け取られる前記基板が、パターン形成されたフォトレジストを上に有し、

前記フォトレジスト・リフロープロセスが、

前記基板上の前記パターン形成されたフォトレジストをリフローするために、第1のプラズマプロセスを行うステップと、 10

前記基板上のフット領域内のフォトレジストの一部分を除去するために、第2のプラズマプロセスを行うステップと、を含み、

前記第1のプラズマプロセスと第2のプラズマプロセスがどちらも、前記グリッドを有する前記反応チャンバ内で行われ、

前記第1のプラズマプロセスおよび前記第2のプラズマプロセス中の前記第2のプラズマが、イオン-イオンプラズマである、方法。

適用例13：

適用例12の方法であって、

前記第1のプラズマプロセス中の前記プラズマ発生ガスが、H<sub>2</sub>を含み、前記第2のプラズマプロセス中の前記プラズマ発生ガスが、不活性ガスを含む、方法。

20

適用例14：