(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6873141号

(P6873141)

(45) 発行日 令和3年5月19日(2021.5.19)

(24) 登録日 令和3年4月22日(2021.4.22)

(51) Int.Cl.

A 6 1 B 8/14 (2006.01)

F 1

A 6 1 B 8/14

請求項の数 20 (全 17 頁)

(21) 出願番号 特願2018-533936 (P2018-533936)

(86) (22) 出願日 平成28年12月28日 (2016.12.28)

(65) 公表番号 特表2019-500148 (P2019-500148A)

(43) 公表日 平成31年1月10日 (2019.1.10)

(86) 國際出願番号 PCT/EP2016/082788

(87) 國際公開番号 WO2017/114872

(87) 國際公開日 平成29年7月6日 (2017.7.6)

審査請求日 令和1年12月27日 (2019.12.27)

(31) 優先権主張番号 62/272,732

(32) 優先日 平成27年12月30日 (2015.12.30)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 590000248

コーニンクレッカ フィリップス エヌ

ヴェ

KONINKLIJKE PHILIPS

N. V.

オランダ国 5656 アーヘー アイン

ドーフェン ハイテック キャンパス 5

2

(74) 代理人 110001690

特許業務法人M&Sパートナーズ

(72) 発明者 フリーマン スティーブン ラッセル

オランダ国 5656 アーヘー アイン

ドーフェン ハイ テック キャンパス

5

最終頁に続く

(54) 【発明の名称】ダイナミックフィルタリングシステム及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

トランステューサによって受信される音響信号から生成される入力アナログ電気波形を受信するステップと、

前記入力アナログ電気波形をアナログメモリに記憶するステップと、

前記入力アナログ電気波形に基づいて、1対の同一の中間アナログ電気波形を生成するよう、前記アナログメモリの第1の非破壊的読み取り操作及び第2の読み取り操作を行うステップと、

前記中間アナログ電気波形のうちの一方を、他方に対して遅延させるステップと、

フィルタリングされたアナログ電気波形を生成するように、遅延された前記中間アナログ電気波形を前記他方の中間アナログ電気波形と合計するステップと、

を含み、

前記遅延の量は、前記アナログメモリのサンプリングレート、及び、前記入力アナログ電気波形の基本周波数に少なくとも部分的に基づいている、方法。

## 【請求項 2】

前記遅延させるステップは、

前記トランステューサと電気的に通信する入力線に接続される複数の書き込みスイッチを動作させるように書き込みシフトレジスタを使用するステップと、

複数の出力をそれぞれ有する複数の容量素子に電荷を蓄積するステップと、

様々な出力において、前記量だけ遅延された時間において、前記電荷が読み取られるよ

10

20

うに、前記複数の出力に接続される複数の読み取りスイッチを動作させるように複数の読み出しシフトレジスタを使用するステップと、

を含む、請求項 1 に記載の方法。

【請求項 3】

前記フィルタリングされたアナログ電気波形は、前記基本周波数が減衰されている、請求項 1 に記載の方法。

【請求項 4】

前記フィルタリングされたアナログ電気波形は、前記基本周波数の高調波が減衰されていない、請求項 3 に記載の方法。

【請求項 5】

前記合計の前に、前記中間アナログ電気波形のうちの一方が、他方に対して重み付けされる、請求項 1 に記載の方法。

【請求項 6】

前記フィルタリングされたアナログ電気波形は、減衰されている DC 成分を有する、請求項 1 に記載の方法。

【請求項 7】

前記フィルタリングされたアナログ電気波形は、前記基本周波数の高調波が減衰されていない、請求項 6 に記載の方法。

【請求項 8】

前記重み付けは、重み付けされる前記中間アナログ電気波形に関連付けられる読み出しポートの出力インピーダンスを調整することを含む、請求項 5 に記載の方法。

【請求項 9】

前記入力アナログ電気波形の前記基本周波数は、前記音響信号の発生源の深度によって変化し、前記遅延の量は、前記基本周波数の変化に従って変化する、請求項 1 に記載の方法。

【請求項 10】

前記フィルタリングされたアナログ電気波形をデジタル信号に変換するステップを更に含む、請求項 1 に記載の方法。

【請求項 11】

前記変換するステップは、ダイナミックレンジを有するアナログ - デジタル変換器を使用するステップを含み、前記フィルタリングされたアナログ電気波形に適用される利得は、前記アナログ - デジタル変換器の前記ダイナミックレンジを飽和させず、同じ利得が、前記入力アナログ電気波形に適用されたならば、前記アナログ - デジタル変換器の前記ダイナミックレンジを飽和させる、請求項 10 に記載の方法。

【請求項 12】

請求項 1 に記載の方法を使用して、超音波音響信号をフィルタリングするステップを含む、超音波撮像操作を行う方法。

【請求項 13】

超音波撮像用の受信ビームフォーマであって、

少なくとも 1 つのトランステューサ素子からの受信音響信号から生成される入力アナログ電気波形を受信する入力線と、

前記入力アナログ電気波形を記憶し、

前記入力アナログ電気波形に基づいて、1 対の同一の中間アナログ電気波形を生成するように、第 1 の非破壊的読み取り操作が行われ、第 2 の読み取り操作が行われることを可能にし、

前記中間アナログ電気波形のうちの一方を、他方に対して遅延させる

アナログメモリと、

フィルタリングされたアナログ電気波形を生成するように、遅延された前記中間アナログ電気波形を他方の中間アナログ電気波形と合計する加算素子と、

を含み、

10

20

30

40

50

前記遅延の量は、前記アナログメモリのサンプリングレート、及び、前記入力アナログ電気波形の基本周波数に少なくとも部分的に基づいている、受信ビームフォーマ。

【請求項 14】

前記アナログメモリは、

前記入力線に接続される書き込みスイッチを動作させる書き込みシフトレジスタと、

様々な遅延時間において、複数の出力から読み出されることが可能である電荷を蓄積する容量素子と、

第 1 の時間において、前記複数の出力のうちの 1 つから電圧が読み取られ、遅延時間において、前記複数の出力のうちの別の 1 つから電圧が読み取られるように、前記複数の出力に接続される読み取りスイッチを動作させる読み取りシフトレジスタと、

を含み、

前記加算素子は、前記容量素子の出力と前記容量素子の遅延された出力とを合計する、請求項 13 に記載の受信ビームフォーマ。

【請求項 15】

前記中間アナログ電気波形のうちの対応する 1 つを受信し、前記中間アナログ電気波形のうちの対応する前記 1 つを前記加算素子の対応する入力にそれぞれ渡す複数のバッファを更に含む、請求項 13 に記載の受信ビームフォーマ。

【請求項 16】

対応するバッファから前記中間アナログ電気波形のうちの対応する 1 つをそれぞれ受信し、可変インピーダンスをそれぞれ含む 1 対のマルチプレクサを更に含み、前記可変インピーダンスは、前記中間アナログ電気波形に相対重み付けを適用するように、前記マルチプレクサの利得を変更するように調整可能である、請求項 15 に記載の受信ビームフォーマ。

【請求項 17】

前記遅延は、前記入力アナログ電気波形の基本周波数を減衰させ、前記入力アナログ電気波形の高調波周波数を通すように選択される、請求項 13 に記載の受信ビームフォーマ。

【請求項 18】

前記中間アナログ電気波形の前記遅延及び相対重み付けは、前記入力アナログ電気波形の D C 成分を減衰するように選択される、請求項 13 に記載の受信ビームフォーマ。

【請求項 19】

前記遅延は、前記入力アナログ電気波形によって表される前記受信音響信号の発生源の深度に従って変化するように選択される、請求項 13 に記載の受信ビームフォーマ。

【請求項 20】

超音波プローブ内に設置され、超音波撮像システムに結合される、請求項 13 に記載の受信ビームフォーマ。

【発明の詳細な説明】

【技術分野】

【0001】

[001] 本明細において説明されるシステム及び方法は、概して、医用診断超音波システムに関し、具体的には、ダイナミックアナログフィルタリング機能を有する診断システムに関する。

【背景技術】

【0002】

[002] 高調波撮像は、多くの超音波システムによく使用されるモードである。高調波撮像は、音響波と組織との相互作用が高調波周波数帯域内の情報を生成するので、例えば組織種類情報の決定（即ち、血液、心筋、肝臓組織等の特定）において有用である。マイクロバブルといった音響造影剤を使用して、音響信号と相互作用した後、高調波を生成することもできる。送信超音波がマイクロバブルと相互作用すると、非線形共鳴が生じ、これは、探査波の基本周波数の高調波における共鳴エネルギーの生成を含む。高調波成分

10

20

30

40

50

は、基本波よりも強度が低いが、トランスデューサにおける受信には十分に強い。組織高調波撮像の場合でも造影剤の使用の場合でも、基本周波数ではなく、高調波の受信に関する関心が高まっている。

【0003】

[003] 受信信号の高調波成分及び基本波成分の相対強度は、通常、様々である。高調波造影剤信号は、基本波信号に比べて強度が下がる傾向があるが、組織高調波信号は、依然として、パワーにおいてより低い傾向がある。信号源（信号がそこから反射される構造体）の深度が、受け取られるパワーに影響を及ぼす。組織高調波信号は、波が組織を通過することを必要とするので、当該信号は、通常、音響造影剤信号よりも相対的により深い相互作用からもたらされる。周波数及び強度は共に、深度が増加する結果、減衰される傾向がある。これらの作用は、高調波信号が20dB以上で基本波未満である可能性をもたらし、広ダイナミックレンジの受信器が必要となる。高調波発生がほとんどない近距離場、及び、減衰が支配する遠距離場では、高調波応答が、後方散乱により30~40dB下がることが珍しいことではない。

【0004】

[004] 高調波信号と基本波信号との強度差が大きいことを考慮して、高調波の相対パワーが、システムのノイズフロアに対して増加されるように、できるだけ基本波を除去することが有用である。場合によっては、ADCのSNRがシステム感度を制限し、デジタル処理前に適用されるアナログ利得を増加させ、これにより、センサの熱ノイズが支配できるようにすることが有益である。不都合なことに、このシナリオでは、基本波信号は、強いターゲットに関して簡単に飽和し、高調波撮像を行うことが困難となる。1つの救済手段は、ADCの前にアナログハイパスフィルタ又はバンドパスフィルタを含めて、低周波数の基本波信号の一部を抑制し、これにより、ADCを飽和させる可能性を少なくすることである。ADCのダイナミックレンジをより有効活用するために、よりフロントエンドのアナログ利得が適用されてもよい。不都合なことに、基本波から高調波を分離する現行の方法は、典型的に、固定周波数に適用可能であり、したがって、様々なトランスデューサ及び基本周波数をサポートするには、複数のフィルタが必要である。これは、システムの複雑さを増加させる。

【発明の概要】

【発明が解決しようとする課題】

【0005】

[005] したがって、高調波撮像に使用される改良されたフィルタリングアプローチが必要である。本発明は、このニーズ等を満たす。

【課題を解決するための手段】

【0006】

[006] 幾つかの態様において、本発明は、トランスデューサによって受信される音響信号から生成される入力アナログ電気波形を受信するステップと、入力アナログ電気波形に基づいて、1対の実質的に同一の中間アナログ電気波形を生成するステップと、中間アナログ電気波形のうちの一方を、他方に対して遅延させるステップと、フィルタリングされたアナログ電気波形を生成するように、遅延された中間アナログ電気波形を他方の中間アナログ電気波形と合計するステップとを含み、遅延量は、トランスデューサのサンプリングレート及び入力アナログ電気波形の基本周波数に少なくとも部分的に基づいている方法を提供する。

【0007】

[007] 特定の態様において、本発明は、少なくとも1つのトランスデューサ素子からの受信音響信号から生成される入力アナログ電気波形を受信する入力線と、入力アナログ電気波形に基づいて、1対の実質的に同一の中間アナログ電気波形を生成するように、第1の非破壊的読み取り操作が行われることを可能にし、また、時間遅延後に、第2の読み取り操作が行われることを可能にするアナログメモリと、フィルタリングされたアナログ電気波形を生成するように、遅延された中間アナログ電気波形を他方の中間アナログ電

10

20

30

40

50

気波形と合計する加算素子とを含み、遅延は、アナログメモリのサンプリングレート及び入力アナログ電気波形の基本周波数に少なくとも部分的に基づいている、超音波撮像用の受信ビームフォーマを含む超音波撮像システムを含む。

【図面の簡単な説明】

【0008】

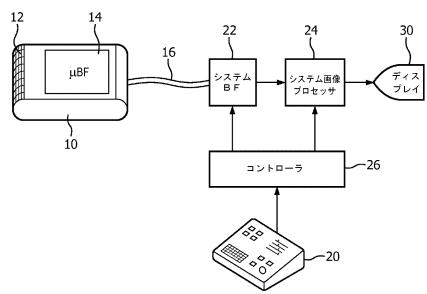

【図1】[008] 図1は、本発明の例示的な実施形態による超音波撮像システムの一実施形態の概略図である。

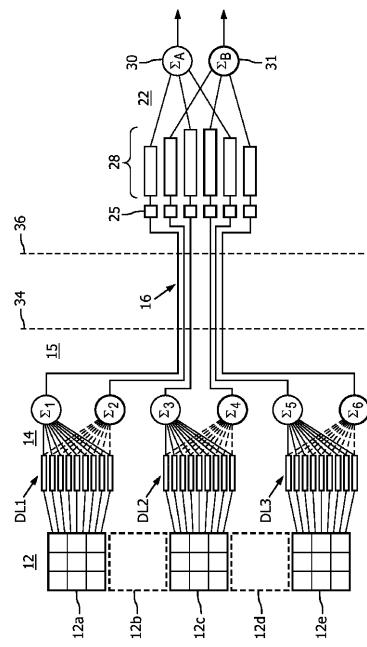

【図2】[009] 図2は、本発明の例示的な実施形態によるビーム形成アーキテクチャのプロック図を示す。

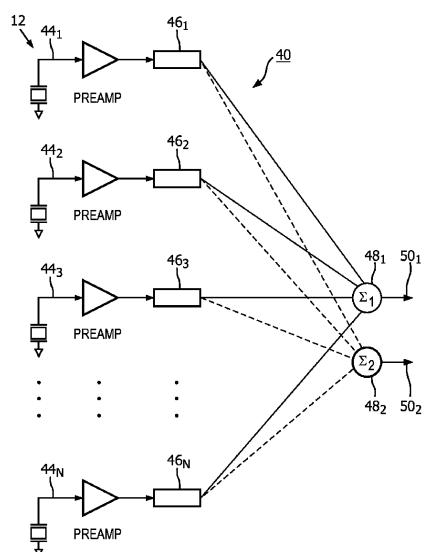

【図3】[010] 図3は、本発明の例示的な実施形態に従って、プログラマブル遅延線として使用されるアナログランダムアクセスメモリを示す。

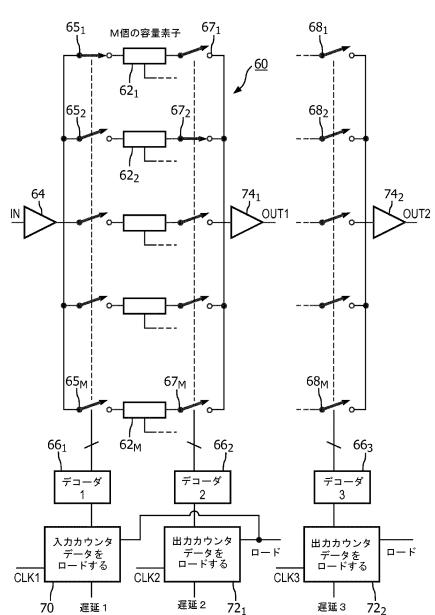

【図4】[011] 図4は、本発明の例示的な実施形態に従って、フィルタリングのためのデュアルポートアナログランダムアクセスメモリ及び他のアーキテクチャに含まれる回路を示す。

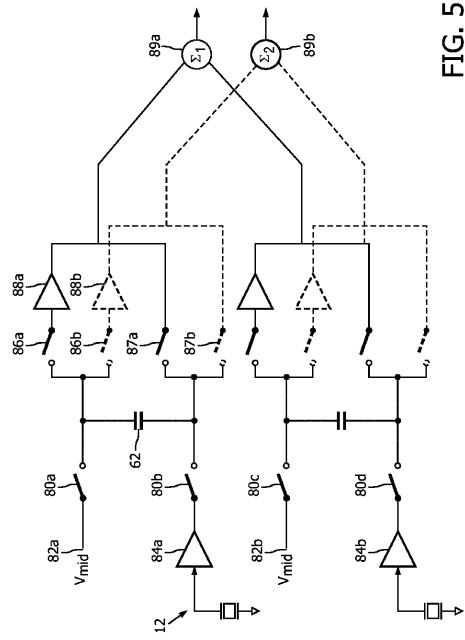

【図5】[012] 図5a及び図5bは、一実施形態によるデュアルポート読み取りRAM及び関連の加算回路を概略的に示す。

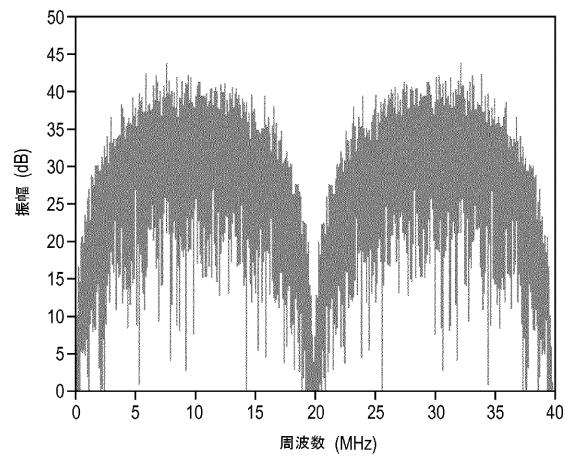

【図6】[013] 図6は、一実施形態に従って、フィルタリングされたサンプルベクトルのパワースペクトルの一例を示す。

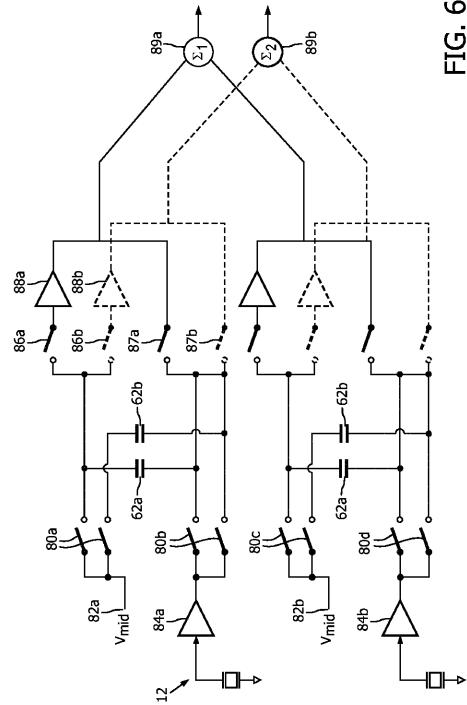

【図7】[014] 図7は、一実施形態にしたがって、図6とは違うフィルタを使用してフィルタリングされたサンプルベクトルのパワースペクトルの一例を示す。

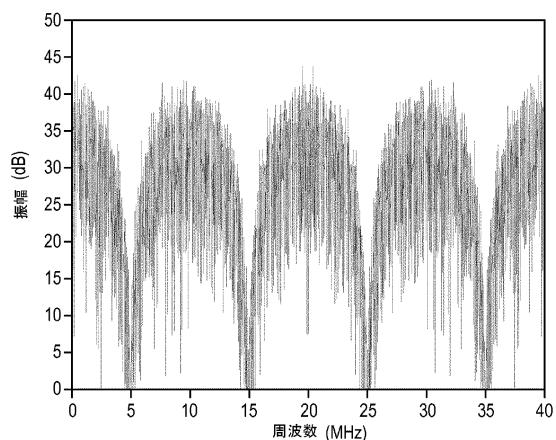

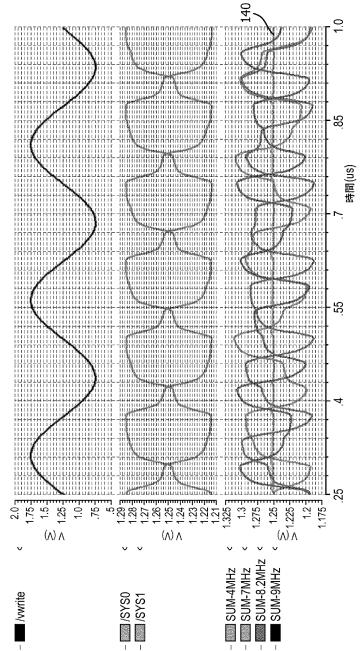

【図8】[015] 図8は、一実施形態によるデュアルポートRAMのシミュレーション出力のセットを示す。

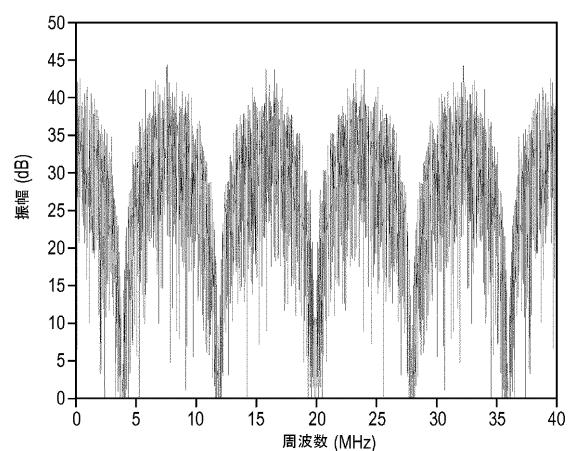

【図9】[016] 図9は、一実施形態によるデュアルポートRAMのシミュレーション出力の別のセットを示す。

【図10】[017] 図10は、一実施形態にしたがって、DCにおいてゼロを有するフィルタを実現するために反転を使用するフィルタリングされたサンプルベクトルのパワースペクトルの一例を示す。

【発明を実施するための形態】

【0009】

[018] 以下の詳細な説明において、限定ではなく説明のために、具体的な詳細を開示する例示的な実施形態が、本教示による実施形態の完全な理解を提供するために記載される。しかし、本開示を利用する当業者には、本明細書において開示される具体的な詳細から離れる本教示による他の実施形態も、添付の請求項の範囲内であることは明らかであろう。更に、周知の装置及び方法の説明は、例示的な実施形態の説明を曖昧としないために省略される。当該方法及び装置は、本教示の範囲内である。

【0010】

[019] したがって、以下の詳細な説明は、限定的な意味で解釈されるべきではなく、本システムの範囲は、添付の請求項によってのみ規定される。図面中の参照符号の先頭の桁は、図面の番号に対応するが、複数の図面に登場する同一のコンポーネントは、同じ参照符号によって示される。更に、明瞭するために、幾つかの特徴の詳細な説明は、当業者には明らかである場合は、本システムの説明を曖昧としないために記載されない。

【0011】

[020] フレームレートを向上させるためにマルチラインがしばしば使用されるが、多くのマイクロビームフォーマは、シングルリード機能しか提供しない。マイクロビームフォーマを動作させるためのマルチリード処理は、複数のリード操作が可能であるよう、非破壊的に出力バッファに亘って蓄積コンデンサを切り替えることを伴う。例えば関連出願：米国仮特許出願番号第62/109,103号(Koninklijke Philips社に譲渡され、参照することによりその全体が本明細書に組み込まれる)において説明される1つのこのようなアプローチは、単一のRAM遅延線を使用し、一意に遅延

10

20

30

40

50

延された各出力のサンプルを再読み取りする。具体的には、当該アプローチは、マイクロビームフォーマにおけるマルチライン受信をサポートするように、様々な量で遅延される複数の出力ストリームを遅延線が出力することを可能にするアナログ回路を提供する。遅延線からの各出力は、マルチライン受信ビーム形成用のビームの一構成要素である。例えば2つの出力は、2×マルチライン受信ビーム形成に対応し、4つの出力は、4×マルチライン受信ビーム形成に対応し、以下同様である。したがって、上記アプローチは、(第2、第3又は第4のシフトレジスタによって制御されて)後に同じコンデンサから再読み取り、それを第2、第3又は第4の出力バッファに接続することを可能にする。したがって、同じ单一の入力から、幾つかの階段状出力サンプルストリームが導出され、各出力ストリームは一意の遅延を有する。書き込み制御及びA R A M蓄積キャップ構造は、これらの一意の出力間で共有され、これにより、空間及びパワー効率が増加される。空間及びパワー効率の増加は、超音波プローブに幾つかの利点(例えばプローブ内で他のコンポーネントに利用可能な空間が増えること、走査中の発熱が少ないこと)をもたらす。

#### 【0012】

[021]マイクロビーム形成、即ち、サブアレイ処理は、それがケーブルを介する通信であろうとA D Cによるデジタル処理であろうと、後続の処理の複雑さを低減するために、遅延が適用された後の信号の総和を伴う。しかし、総和処理の1つの結果は、コヒーレント信号は線形に増えるが、ノイズは総和信号の平方根に応じて増えるため、総和信号の瞬間ダイナミックレンジが増加することである。したがって、信号のS N Rが量子化器のS N Rよりも大きいため、マイクロビーム形成されたシステムが、最新のA D Cによって事実上デジタル化できない信号を出力する可能性がある。基本波モードでは、基本波信号には適切な画像を作成するためのパワーが沢山あるので、通常、性能への著しい影響はない。しかし、(非線形伝搬効果又は造影剤からの再放射からの)弱い第2高調波信号が使用される高調波撮像では、A D CのS N Rが、適切な画像を作成するシステムの能力を制限してしまう。この場合、基本波信号の振幅を、当該信号がA D Cに到達する前に、減少させることが有益である。

#### 【0013】

[022]本明細書において更に説明されるように、本発明は、超音波システム内のアナログ-デジタル変換器(A D C)によってアナログ波形がサンプリングされる前に、2つの異なる時間遅延によって当該アナログ波形を遅延させ、遅延された波形を組み合わせて基本波成分を事実上相殺することによって、当該アナログ波形をフィルタリングすることに關し、これにより、受信エコー信号内の高調波成分がより感度良く検出される。このフィルタリングアプローチは、マルチラインビーム形成に使用されるアーキテクチャを利用して、時間フィルタリングを行う。時間フィルタリングでは、A R A Mが非破壊的読み取り操作を可能にする点を利用して、单一の音響信号が、A R A Mから2回、時間的に離されて読み出される。遅延された信号と元の信号とが合計されて、フィルタリングされた信号がもたらされる。したがって、例えば(2つの読み取り間の)遅延差が、搬送基本波の約半波長である場合、合計は、出力信号の基本波成分を事実上無にする一方で、第2高調波成分は通されるか又は増幅される。このようにすると、基本波の第2高調波信号成分に対する比率は下がり、これに応じたアナログ利得の量が、A D Cの前に適用され、アナログノイズフロアが量子化ノイズフロアよりも上(即ち、A D CのS N Rが決定的な制限ではないところ)に上げられる。

#### 【0014】

[023]幾つかの実施形態では、アナログ電気波形を使用して、2つの実質的に同一の波形が生成される。そのうちの1つは、ある時間量だけ遅延される。当該時間量は、サンプリングレートにおけるサンプル数に少なくとも部分的に基づく。「実質的に同一」とは、信号が基本的に同じではあるが、実際には、製造公差による僅かな違いが回路にあることによって信号も僅かな違いがあることを意味する。原則として、信号は、例えば数パーセント以内で可能な限り同一に近いべきである。しかし、最大約10%の違いでも、実質的なフィルタリングは生じ、ノッチの深度が幾分減少されるに過ぎない。

10

20

30

40

50

## 【0015】

[024] 本発明は、関心の高調波信号を捕捉するために、A D C のダイナミックレンジをより有効活用できるように、A D C の前の基本波信号成分の減少（又はフィルタリング）が望まれる高調波撮像において特に有用である。基本波は、デジタル領域において除去できるが、高調波信号から情報を最大限に得るために、デジタル処理前に、基本周波数成分をフィルタリングすることが特に有益である。信号のデジタル処理前に、基本波信号を除去することによって、例えばシステムがより多くのアナログ利得を適用する一方で、飽和を回避し、また、A D C の限られたダイナミックレンジをより効果的に利用することができ、これにより、超音波システムの感度が向上され、高調波情報を喪失することなく、全体のパワーを減少することができる。更に、本明細書において説明されるフィルタリングアプローチは、同じハードウェア構造を使用して様々な基本周波数をフィルタリング可能であるように動的に適用される。提案される発明の別の有用な特徴は、2つの読み取りポートの出力部にデマルチブレクサを含めるだけで、システムが、2つの別個の出力へと読み出すことによってマルチライン受信を行うか、又は、適切に制御された遅延を用いて単一の出力へと読み出すことによって基本波阻止フィルタを適用するように簡単に再構成できる点である。 10

## 【0016】

[025] 幾つかの態様では、一実施形態は、超音波トランスデューサプローブと、マルチライン受信ビーム形成及び基本波フィルタリングのための複数の出力を有する遅延線を含む超音波システムとを含む。図1を最初に参照するに、本発明の原理に従って構成される超音波システムがブロック図形式で示される。プローブ10が、2次元アレイトランスデューサ12といったトランスデューサを有する。アレイの素子は、プローブ内でトランスデューサアレイの背後に置かれるマイクロビームフォーマ14に結合される。マイクロビームフォーマは、時間が決められた送信パルスをアレイの素子に適用して、アレイの前の3次元像フィールド内で所望の方向で及び所望の焦点に向けてビームが送信される。送信されたビームからのエコーは、アレイ素子によって受信され、マイクロビームフォーマ14の遅延部に結合され、ここで個別に遅延される。本明細書において更に説明されるように、アレイからの受信信号は、マイクロビームフォーマに入力され、蓄積電荷の非破壊的読み取りを用いる本発明のアーキテクチャに従って、様々な遅延時間において、複数の出力が読み出される。本明細書において説明されるように、本発明の1つの利点は、2つの別個の出力へと読み出すことによってマルチライン受信を行うか、又は、適切に制御された遅延を用いて単一の出力へと読み出すことによって基本波阻止フィルタを適用するその能力である。幾つかの態様では、プローブ及びシステムは、マルチラインビーム形成を行うように構成される。1つのパッチを構成するトランスデューサ素子のグループの遅延された信号が組み合わされて、当該パッチの部分和信号が形成される。本実施形態におけるパッチの素子は共に動作させられ、それらの信号は基準との関連で個別に遅延され、マイクロビームフォーマによって組み合わされて、当該パッチからプローブ導体又は超音波システムビームフォーマチャネルへの1つの信号が形成される。遅延線からの複数の出力が異なる時間に読み出されるので、各出力に様々な遅延を使用して、単一の遅延線で様々なビームが形成される。幾つかの態様では、プローブ及びシステムは、基本波フィルタリングを行うように構成される。基本波フィルタリングでは、A R A M が非破壊的読み取り操作を可能にする点を利用して、単一の音響信号がA R A Mから2回、時間的に離されて読み出される。遅延された信号と元の信号とは合計され、フィルタリングされた信号がもたらされる。様々な信号の組み合わせは、遅延された信号を共通バス又は加算ノードに結合することによって行われる。加算回路又は他の回路が使用されてもよい。信号は、システムメインフレームに結合されるケーブル16の導体に結合される。システムメインフレームにおいて、信号はデジタル化され、システムビームフォーマ22のチャネルに結合される。次に、信号は、コヒーレントにステアリングされ、集束された受信ビームを形成するように組み合わされる。3 D 像フィールドからのビーム信号は、システム画像プロセッサ24によって処理され、画像ディスプレイ30に表示される2 D 又は3 D 画像が生成 20 30 40 50

される。プローブ選択、ビームステアリング及び集束、並びに、信号及び画像処理といった超音波システムパラメータの制御は、システムの様々なモジュールに結合されるコントローラ 26 の制御下で行われる。プローブ 10 の場合、この制御情報の一部は、システムメインフレームから、ケーブル 16 のデータ線を介してマイクロビームフォーマに提供される。ユーザは、制御パネル 20 を用いて、これらの動作パラメータの多くを制御する。

【0017】

【026】 本発明の1つの特有の利点は、マルチラインビーム形成と基本波フィルタリングとの両方に同様のアーキテクチャを使用できる点である。マルチラインビーム形成に関して、図2は、マルチラインビーム形成に使用されるマイクロビームフォーマの遅延素子の詳細図を示す。図3に関連して説明されるように、受信ビームフォーマ40のチャネル44<sub>1</sub>、44<sub>2</sub>、44<sub>3</sub>、…、44<sub>N</sub>は、アレイ12に結合され、遅延素子内の蓄積電荷の様々な遅延された読み取りに対応する複数の出力を有するプログラマブル遅延素子46<sub>1</sub>、46<sub>2</sub>、46<sub>3</sub>、…、46<sub>N</sub>を含む。ここでは、例として2つの出力が示される。各遅延線からの第1の出力は、第1の加算素子48<sub>1</sub>に結合される。各遅延線の第2の出力は、第2の加算素子48<sub>2</sub>に結合される。加算素子は、各出力からの遅延された信号を加算し、合計信号を受信ビームフォーマ40のチャネル出力部50<sub>1</sub>、50<sub>2</sub>に提供する。一実施形態では、加算素子は加算増幅器又は他のアナログ加算回路を含む。

【0018】

【027】 幾つかの実施形態では、ビームフォーマ40は、マイクロプロセッサと関連メモリとを含むシステムコントローラを使用して動作させられる。システムコントローラは、超音波撮像システムの動作を制御する。例えばシステムコントローラは、遅延コマンドを、バスを介して送信ビームフォーマのチャネルに提供する。遅延データは、生成された送信ビームを、くさび形の送信パターン、平行四辺形の送信パターン又は他のパターンの送信走査線上でステアリング及び集束する。システムコントローラは更に、遅延コマンドを、バスを介して受信ビームフォーマのチャネルに提供する。適用された相対遅延が、合成受信ビームのステアリング及び集束を制御する。図示されるように、各受信ビームフォーマチャネル44<sub>N</sub>は、受信した信号の深度の関数として利得を制御する可変利得増幅器(PREAMP)と、合成ビームのビームステアリング及びダイナミック集束を実現するように音響データを遅延させる遅延素子46<sub>N</sub>とを含む。ビームフォーマ信号は、受信走査線に沿って合成される受信超音波ビームを表す。

【0019】

【028】 図3を再び参照するに、各アナログ遅延線46<sub>N</sub>は、図4に関連して説明されるアナログRAMを含む。図4では、アナログランダムアクセスメモリ(ARAM)デバイス60は、プログラマブル遅延素子として構成される。アナログRAMデバイス60は、入力スイッチ65<sub>1</sub>、65<sub>2</sub>、…、65<sub>M</sub>に接続されるデコーダ66<sub>1</sub>を使用して入力信号をサンプリングするM個の蓄積容量素子(例えばコンデンサを含む)62<sub>1</sub>、62<sub>2</sub>、…、62<sub>M</sub>からなるグループを含む。アナログRAMデバイス60は更に、デコーダ66<sub>2</sub>、66<sub>3</sub>がそれぞれ第1の出力スイッチ67<sub>1</sub>、67<sub>2</sub>、…、67<sub>M</sub>及び第2の出力スイッチ68<sub>1</sub>、68<sub>2</sub>、…、68<sub>M</sub>を制御して、潜在的に異なる遅延で蓄積された信号を読み出す第1及び第2の読み取り機能も含む。入力バッファ64がトランスデューサ信号を受信する。トランスデューサ信号は、次に、デコーダ66<sub>1</sub>によって制御される入力スイッチ65<sub>N</sub>によって蓄積容量素子62<sub>N</sub>に送られる。本明細書において更に説明されるように、本発明の容量素子は、1つの読み取りが処理されると、蓄積電荷が留まり、違う時間において再び読み取られるように、非破壊的読み取り用に構成される。ここでは、容量素子から2つの出力が示される。出力スイッチ67<sub>M</sub>に結合されるデコーダ66<sub>2</sub>は、入力カウンタ70と第1の出力カウンタ72<sub>1</sub>とのタイミングの違いによって決定される遅延時間において、個々のコンデンサの電荷をサンプリングする。したがって、トランスデューサ信号は、入力バッファ64から第1の出力バッファ74<sub>1</sub>に伝達される間に、選択された遅延時間だけ遅延される。出力スイッチ68<sub>M</sub>に結合されるデコーダ66<sub>3</sub>は、入力カウンタ70と第2の出力カウンタ72<sub>2</sub>とのタイミングの違いによって決定さ

10

20

30

40

50

れる遅延時間において、個々のコンデンサの電荷をサンプリングする。したがって、トランステューサ信号は、入力バッファ<sub>6</sub>4から第2の出力バッファ<sub>7</sub>4<sub>2</sub>に伝達される間に、選択された遅延時間だけ遅延される。なお、第2の出力を示す破線は、容量素子が、容量素子から第2の出力に適用される様々な遅延時間のために、第2のデコーダ及び出力カウンタに結合することを暗に示す。容量素子の電荷を書き込む及び読み出すために他の構成が使用されることが考えられる。例えばカウンタ及びデコーダの代わりに、循環ソフトレジスタが使用される。

【0020】

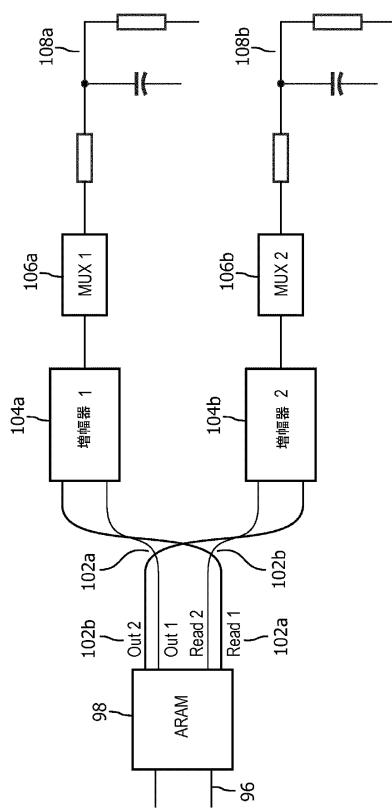

[029] 図4は、本発明に従って基本波フィルタリングのために使用され且つ動作させられる構造を示す。ここでは、2つの異なる増幅器及び出力マルチプレクサ構造によってバッファリングされるデュアルポートRAMが、例えば特定用途向け集積回路(ASIC)内に実装される。図9に示される実施形態では、RAM98は、図4に示され、マルチラインビーム形成に使用される実施形態と構造的に似ている。入力信号が、連続アナログ信号として到着し、入力線96上でサンプリングされ、階段状の連続出力が生成される。これを行う際、RAM98は、超音波トランステューサからサンプルを受信し、それらをアナログメモリ、例えば容量メモリ素子に蓄積する。アナログメモリは、次に、更なる処理のために非破壊的処理で読み出される。基本波フィルタリングでは、RAM98は、2つの出力(Out1、Out2)100a、100bと、2つの読み取り制御信号出力(Read1、Read2)102a、102bとを有する。これらの出力は、1対の増幅器104a、104bの対応する入力部に渡される。これらの4つの出力ノードは、RAM内でアクセスされる2つの異なるコンデンサの2つの側である。名目上、Out1及びRead1は、米国仮特許出願番号第62/109,103号に説明されるように、出力バッファに亘って切り替えられる1つのコンデンサの2つの側に対応する。増幅器からの出力は、対応するデマルチプレクサ106a、106bに供給され、デマルチプレクサはシステム内のADCに結合される。増幅器とバッファとの関連付けられる各ペアリングは、対応するバッファ構造を形成すると考えられる。この例では、デマルチプレクサ106aは、点線で示される展開に示されるように、4つのADCに結合される。スイッチを使用して、増幅器104aからの信号が4つのADCのうちの何れか1つに送信される。同様に、デマルチプレクサ106bからの4つのチャネルも4つのADCに結合され、これにより、増幅器104bがその信号を4つのADCのうちの1つに送信する。デマルチプレクサを有する他のチャネルも4つのADCに結合されてよい。他のチャネルも、それら自身の対応する増幅器を含み、RAMからの出力に結合される。ADC及びデマルチプレクサからの出力の数は、超音波システムにおいて使用されるビーム形成に求められる必要な仕様に応じて容易に変更される。更に、各デマルチプレクサ106a、106bは、図示されない利得選択素子を含んでもよい。一実施形態では、利得選択素子は、可変抵抗器(例えば110a、110b)を含む。ADC(又は前置増幅器)の入力インピーダンスと共に作動する可変抵抗器は、デバイスの各アームについて利得を規定するように使用される。この利得の1つの使用は、以下に更に詳細に説明されるように、フィルタに重みを加えることである。

【0021】

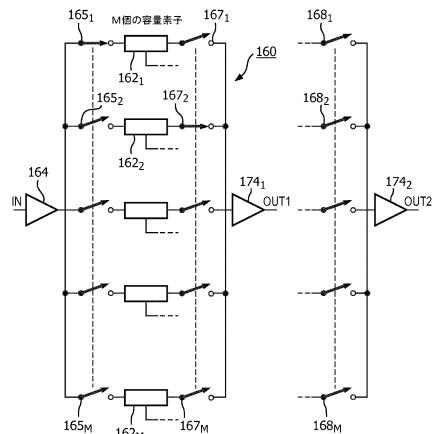

[030] 図10aは、RAM98のより詳細な構造的実施態様を示す。RAMデバイス160の図示される実施形態は、入力信号をサンプリングするM個の蓄積容量素子(例えばコンデンサを含む)162<sub>1</sub>、162<sub>2</sub>、…、162<sub>M</sub>からなるグループを含む。各容量蓄積素子は、対応する入力スイッチ165<sub>1</sub>、165<sub>2</sub>、…、165<sub>M</sub>と通信する。RAMデバイスは更に、潜在的に異なる遅延で蓄積された信号を読み出すために、第1の出力スイッチ167<sub>1</sub>、167<sub>2</sub>、…、167<sub>M</sub>及び第2の出力スイッチ168<sub>1</sub>、168<sub>2</sub>、…、168<sub>M</sub>からなるそれぞれのセットも含む。入力バッファ164がトランステューサ信号を受信する。トランステューサ信号は、次に、入力スイッチ165<sub>N</sub>によって、蓄積容量素子162<sub>N</sub>に送られる。上記されたように、各容量素子は、1つの読み取りが処理されると、蓄積電荷が留まり、違う時間において再び読み取られるように、

10

20

30

40

50

非破壊的読み取り用に構成される。ここでは、容量素子から 2 つの出力が示される。出力スイッチ 167<sub>M</sub> は、選択された遅延時間において、個々のコンデンサの電荷をサンプリングする。したがって、トランステューサ信号は、入力バッファ 164 から第 1 の出力バッファ 174<sub>1</sub> 及び第 2 の出力バッファ 174<sub>2</sub> に伝達される間に、選択された遅延時間だけ遅延される。

#### 【 0 0 2 2 】

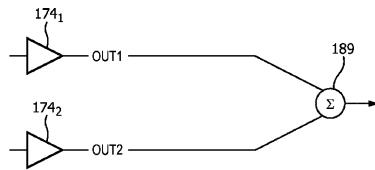

[ 031 ] 図 10 b は、filtratingされたアナログ波形を生成するために、加算素子 189 に渡される 2 つの出力バッファ 174<sub>1</sub>、174<sub>2</sub> のそれぞれの出力を示す。各增幅器 104a、104b は、ARAM 98 の出力（即ち、各容量素子 162<sub>M</sub> に蓄積される電圧）を受信する。一実施形態では、各增幅器は、読み出される容量素子に蓄積された電圧へと、対応する出力 (Out 1、Out 2) によって駆動される反転増幅器を含む。この読み取り操作は、上記されたように行われる。

#### 【 0 0 2 3 】

[ 032 ] 幾つかの態様では、基本波filtratingは、原信号と合計信号とに異なる遅延を適用し、基本周波数の近くにノッチを作成することにより、くし形フィルタのように行われる。更に、特定のフィルタ特性は調節可能である。例えば遅延を変えることによって、フィルタは、様々な異なる基本周波数に対して動作（ノッチアウト）するように調整される。フィルタノッチ周波数の選択は、サンプリングレート及び遅延量に依存する。一例として、40 Msps サンプルストリームでは、最初のストリームと合わされた 4 つのサンプルだけ遅延される信号ストリームは、5 MHz におけるノッチと、10 MHz におけるハイパスピークとをもたらす。有限インパルス応答 (FIR) 係数に関して、これは、[10001] フィルタであると見なされる。ランダムサンプルベクトルを用いたフィルタ係数の畳み込みの高速フーリエ変換 (FFT) は、遅延及び合計操作のこの例の周波数スペクトルを生成する。これは、図 7 に示される。図 6 のスペクトルから分かるように、5 MHz に明らかなノッチがある一方で、約 7.5 MHz から約 12.5 MHz までの高調波は比較的少ない減衰で通過する。

#### 【 0 0 2 4 】

[ 033 ] なお、フルサンプル遅延のみが可能である場合、ノッチの位置決めが幾分粗い。つまり、ノッチの間隔は、サンプリングレート及びサンプル数（フルサンプル遅延のみが可能である場合は整数）に依存するので、作成可能であるフィルタの数と、信号からノッチアウトしたい特定の基本周波数を選択する能力とに限りがある。図示されるような 5 タップフィルタを使用すると、ゼロとサンプリングレート（この例では 40 Msps）との間で等間隔である 4 つのノッチが提供される。つまり、5、15、25 及び 35 MHz においてノッチがある。

#### 【 0 0 2 5 】

[ 034 ] 基本波ノッチは、Fs / (2 \* N - 2) にある。N は、フィルタ長である。したがって、6 タップフィルタ [100001] を使用すると、図 8 に示されるように、5 つのノッチが生成される。同じ 40 Msps 信号に適用される 5 ノッチフィルタでは、基本波ノッチは、40 / (2 \* 6 - 2) MHz = 4 MHz にある。サンプルにおける遅延の長さは、適切なノッチ位置を得るために、理にかなった範囲内で調節される。

#### 【 0 0 2 6 】

[ 035 ] 更に、遅延選択性の分解能を増加させることによって、ノッチ位置はより微細に制御される。例えば 80 MHz の遅延分解能が利用可能である場合、ノッチ周波数は、40 MHz 信号の 2 倍の分解能で選択される。一般に、ノッチ周波数は、Fdly / (2 \* M - 2) と表現される。M は、（上で使用されたサンプリングレートとは対照的に）Fdly の遅延における違いであり、Fdly は、遅延の分解能である。

#### 【 0 0 2 7 】

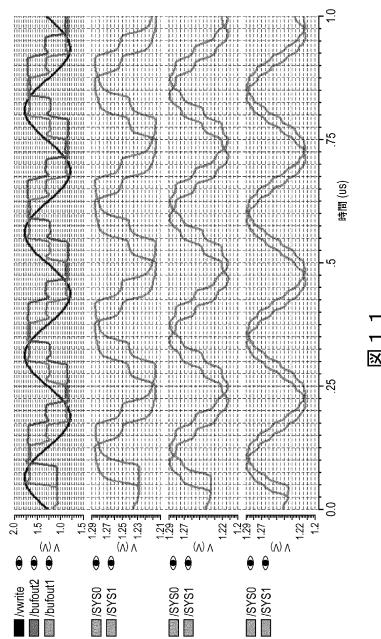

[ 036 ] 図 11 に、ARAM の出力のシミュレーション例が示される。一番上のトレースセットは、/vwrite 信号と、2 つの異なるバッファリングされた読み取り出力 /bufout2、/bufout1 を示す。第 2 のトレースセットは 24 Msps 読

10

20

30

40

50

み出しを表し、第3のセットは32M s p s読み出しを表し、第4のセットは48M s p s読み出しを表す。第2、第3及び第4のセットのそれにおける2つのトレース間には1サンプル差がある。図に示すように、トレース間の時間遅延は変化する。これは、サンプリングレートが上がるにつれて、単一のサンプルがより小さい時間間隔を表すからである。

#### 【0028】

[037] 図12は、上記された4MHzのノッチを生成するようにデザインされたシミュレーション信号を示す。具体的には、4サンプル遅延が、図8の1サンプル遅延と合計される。一番上のトレースは、/vwrit e信号を示し、第2のトレースセットは、1サンプルの遅延及び4サンプルの遅延をそれぞれ有する2つの読み取りチャネル/SYS0、/SYS1を示す。下側のトレースは、様々な周波数（具体的には、4、7、8.2及び9MHz）における2つの読み取りチャネルの合計を示す。図に示すように、4MHzのトーン140が、予想通り実質的に相殺されている。シミュレーション信号は、幾分不規則に見えるが、これは、シミュレーションのサンプリングレート(24M s p s)の結果に過ぎず、より高いサンプリングレートを使用して、フィルタリングの本質的な性質を変更することなく、所望通りにより滑らかな波形を生成することができる。

#### 【0029】

[038] 上記されたように、基本波のこの除去は、利得を飽和させることなく、高調波がより高度な増幅を受けることを可能にし、これにより、メインフレームにおけるA/D変換のダイナミックレンジをより有効に活用できる。同じハードウェアがマイクロビーム形成のために既に使用されているので、この解決策は、ソフトウェアの調節を行うだけで実現することができる。

#### 【0030】

[039] 当然ながら、同じ構造によって、マイクロビーム形成機能及びフィルタリング機能の両方が提供されるので、これらの機能は、オンザフライで切り替えられる。つまり、フィルタリング（遅延）された並列読み取りが、撮像システムのニーズに応じて、各入力線に対して異なるように行われる。このオプションは、2つの読み取りポートの出力部において、デマルチプレクサ（例えば図9の106a及び/又は106b）を含めることによって可能にされる。システムは、2つの別個の出力（ADC）へと読み出すことによってマルチライン受信を行うか、又は、適切に制御された遅延を用いて単一の出力へと読み出すことによって基本波阻止フィルタを適用するように簡単に再構成できる。

#### 【0031】

[040] 同様に、フィルタの長さを変えたり、重み付けを合計の前にサンプルの片方又は両方に適用したりしてもよい。例えば重み付けは、正の重み付け係数又は負の重み付け係数での重み付けを含む。したがって、物理的な構造を変更することなく、様々なフィルタデザインが様々な時間に実現することができる。例えば[10000.8]といったインパルス反応を有するフィルタが適用される。実際には、重み付けは、各読み取りポートの出力インピーダンスを調節することによって行われる。一実施形態では、各ポートは、別々に且つ一意に制御され、様々な加算抵抗が生成される。このタイプの別のフィルタは、重み付けされていないフィルタの場合ほど浅くはないノッチを有する傾向があるが、特定の信号条件下では、より優れた性能を提供する。例えば信号が短い包絡線を有する（したがって、広帯域）場合、重み付けされたフィルタは、重み付けされていないフィルタよりも優れた総合的性能を提供する。

#### 【0032】

[041] 一実施形態では、重み付けは、信号のうちの1つの信号の反転を含む。つまり、負のフィルタ重みが適用される。単に蓄積コンデンサを後方に接続するように、符号選択が増幅器入力に加えられる。これにより、この割り当ては、ソフトウェアを介して完全に選択可能にされる。つまり、読み取りポートのうちの1つに対する増幅器入力が逆転されると、信号は反転される。このアプローチでは、第2の出力ポートが、フィルタリング応用において、-1（又は、より一般的には適切なインピーダンス調節によって、-X

10

20

30

40

50

) 重みを適用することができる。このようにすると、単に [ 1 0 0 0 1 ] 状のフィルタを有するのではなく、図 10 に示される形式の特性周波数応答を有する [ 1 0 - 1 ] フィルタを使用することができる。当然ながら、この応答は、0 MHz 付近のノッチを生成する。これは、( 20 MHz といったより高い周波数におけるノッチと共に ) DC 成分が除去されることを意味する。これは、合計される + 1 サンプル及び - 1 のサンプルが平均して 0 になるからである。これは、そうでなければ A / D コンバータを飽和させてしまう受信経路における DC オフセットを除去するのに有用である。これは更に、高調波撮像には有用である周波数帯に亘ってハイパス特性を提供する。少なくとも原則的に、高周波ノイズ源を除去するように、高周波数ノッチが選択される。

【 0 0 3 3 】

10

[ 042 ] マイクロビーム形成のために構成される幾つかのシステムでは、受信経路における遅延は、ダイナミック受信集束ができるように、動的に変更可能である。この機能によって、周波数ノッチ位置が探査下の構造における様々な深度について異なるように、フィルタリングを変更することができる。つまり、システムは、ゼロが基本波信号の変動中心周波数を、当該基本波が減衰及び / 又は周波数分散により低周波数にシフトするにつれて追跡するように調節される。例えば小さいインクリメントで遅延を増加させることによって、フィルタリングノッチは、線の経過中において、より低い周波数にシフトする。実施では、1 / 深度の関係が適用されてこの周波数シフト機能が行われる。

【 0 0 3 4 】

20

[ 043 ] 本発明の幾つかの追加の利点及び特徴は、本開示を検討した後の当業者には明らかであろう。また、本発明の新規のシステム及び方法を採用する人々によって経験されるであろう。その主要の利点及び特徴は、2 倍の数の受信ビームが同時に形成され、したがって、撮像フレームレートが劇的に向上される点である。

【 0 0 3 5 】

[ 044 ] 当然ながら、上記実施形態又は処理の何れか 1 つが、本システム、デバイス及び方法にしたがって、1 つ以上の他の実施形態及び / 又は処理と組み合わせられても、分離されても、及び / 又は、別々のデバイス若しくはデバイス部間で行われてもよい。

【 0 0 3 6 】

[ 045 ] 最後に、上記説明は、本システムを説明するに過ぎず、添付の請求項を任意の特定の実施形態又は実施形態のグループに限定すると解釈されるべきではない。したがって、本システムは例示的な実施形態を参照して具体的に詳細に説明されているが、当然ながら、以下の請求項に記載される本システムのより広い及び意図する精神並びに範囲から逸脱することなく、多くの修正態様及び代替実施形態が当業者によって想到される。したがって、明細書及び図面は、例示と見なされるべきであり、また、添付の請求項の範囲を限定することを意図していない。

30

【図1】

図1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

図4

【図5】

【図6】

【図7】

【図8】

【図 9】

図9

【図 10 a】

図10a

【図 10 b】

FIG. 10b

【図 11】

図11

【図 12】

図12

【図 1 3】

図 1 3

---

フロントページの続き

審査官 姫島 あや乃

(56)参考文献 特開2012-139465(JP, A)

特表2008-514335(JP, A)

特開2002-301068(JP, A)

特開平03-173543(JP, A)

特開2001-340339(JP, A)

(58)調査した分野(Int.Cl., DB名)

A61B 8/00 - 8/14