# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 5:

G11C 11/40

A1 (11) International Publication Number: WO 93/04475

(43) International Publication Date: 4 March 1993 (04.03.93)

(21) International Application Number: PCT/US92/06947

(22) International Filing Date: 18 August 1992 (18.08.92)

(30) Priority data: 748,374 22 August 1991 (22.08.91) US

(71) Applicant: LATTICE SEMICONDUCTOR CORPORATION [US/US]; 5555 N.E. Moore Court, Hillsboro, OR 97124 (US).

(72) Inventor: JOSEPHSON, Gregg, R.; 18515 S.W. Mathew Court, Aloha, OR 97007 (US).

(74) Agents: HEID, David, W. et al.; Skjerven, Morrill, Mac-Pherson, Franklin & Friel, 25 Metro Drive, Suite 700, San Jose, CA 95110 (US). (81) Designated States: JP, KR, European patent (AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, SE).

Published

With international search report.

(54) Title: METHOD OF PROGRAMMING ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY

#### (57) Abstract

The apparent voltage used to program an EEPROM cell is increased by applying a negative voltage to the memory control gate (16) of the sense transistor (11) in the cell. This method is applicable to devices in which the substrate is negatively biased.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| ΑT | Austria                  | Fi | Finland                      | MN | Mongolia                 |

|----|--------------------------|----|------------------------------|----|--------------------------|

| ΑU | Australia                | FR | France                       | MR | Mauritania               |

| BB | Barbados                 | GA | Gabon                        | MW | Malawi                   |

| BE | Belgium                  | GB | United Kingdom               | NL | Netherlands              |

| BF | Burkina Faso             | GN | Guinea                       | NO | Norway                   |

| BG | Bulgaria                 | GR | Greece                       | NZ | New Zealand              |

| BJ | Benin                    | HU | Hungary                      | PL | Poland                   |

| BR | Brazil                   | ΙE | Ireland                      | PT | Portugal                 |

| CA | Canada                   | ΙT | Italy                        | RO | Romania                  |

| CF | Central African Republic | JP | Japan                        | RU | Russian Federation       |

| CG | Congo                    | KP | Democratic People's Republic | SD | Sudan                    |

| CH | Switzerland              |    | of Korea                     | SE | Sweden                   |

| CI | Côte d'Ivoire            | KR | Republic of Korea            | SK | Slovak Republic          |

| CM | Cameroon                 | LI | Liechtenstein                | SN | Senegal                  |

| CS | Czechoslovakia           | LK | Sri Lanka                    | SU | Soviet Union             |

| CZ | Czech Republic           | LU | Luxembourg                   | TD | Chad                     |

| DE | Germany                  | MC | Monaco                       | TG | Togo                     |

| DK | Denmark                  | MG | Madagascar                   | UA | Ukraine                  |

| ES | Spain                    | MI | Mali                         | US | United States of America |

# METHOD OF PROGRAMMING ELECTRICALLY ERASABLE PROGRAMMABLE READ-ONLY MEMORY

#### FIELD OF THE INVENTION

5 This invention relates to electrically erasable programmable read-only memories and in particular to such devices which employ floating gate technology.

#### BACKGROUND OF THE INVENTION

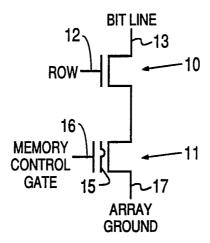

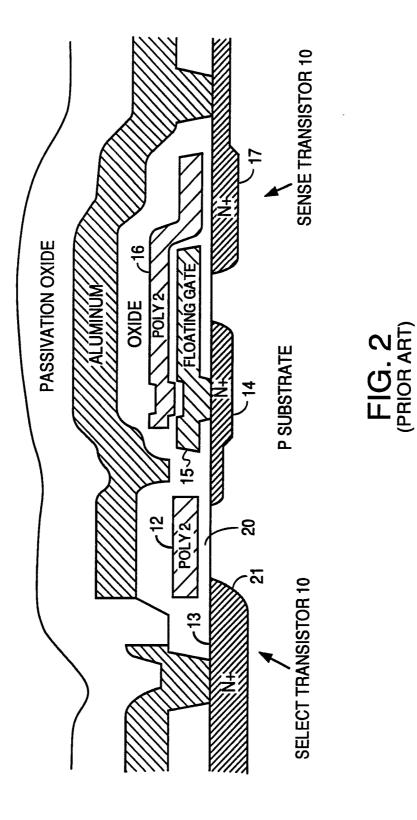

- A typical electrically erasable programmable 10 read-only memory (EEPROM) cell includes two MOS transistors connected in series. An EEPROM of this kind is shown schematically in Figure 1 and structurally in Figure 2. It includes a select transistor 10 and a sense transistor 11, which are connected in series between a bit 15 line 13 and an array ground 17. The gate of select transistor 10 is connected to a row line 12. Sense transistor 11 is controlled by a memory gate 16 and a floating gate 15. When the state of the cell is to be read, select transistor 10 is turned on via a voltage 20 applied to row line 12, and a read voltage is applied to bit line 13 to determine the conductive state of sense transistor 11. If sense transistor 11 is conductive (programmed) a current will flow; if it is non-conductive (erased) a current will not flow.

- Sense transistor 11 is programmed or erased by applying an appropriate voltage between memory control gate 16 and bit line 13, with select transistor 10 turned on. If memory control gate 16 is grounded and a positive programming voltage (typically about 14.5 V) is applied to 30 bit line 13, electrons tunnel from floating gate 15 through a very thin tunnel oxide layer 18 (shown in Figure 2) to the N<sup>+</sup> region designated 14 in Figure 2, leaving

WO 93/04475 PCT/US92/06947

- 2 -

floating gate 15 with a net positive charge. In this state, the cell is programmed. If bit line 13 is grounded and a positive programming voltage is applied to memory control gate 16, the reverse occurs. Electrons tunnel from N<sup>+</sup> region 14 through the very thin oxide layer 18 into floating gate 15, leaving floating gate 15 with a net negative charge. In this state, the cell is erased.

The charge on floating gate 15 determines the threshold voltage of sense transistor 11. If floating 10 gate 15 is positively charged, sense transistor 11 has a relatively low threshold voltage  $V_{TL}$ . If floating gate 15 is negatively charged, sense transistor 11 has a relatively high threshold voltage  $V_{TH}$ . Normally, a reference voltage  $V_{ref}$  about halfway between  $V_{TH}$  and  $V_{TL}$  is 15 applied to memory control gate 16. Thus, if sense transistor 11 has been programmed, it will be conductive; if it has been erased, it will be an open circuit.

It is desirable to have the margin between  $V_{\rm TH}$  and  $V_{\rm TL}$  be as large as possible because a large margin provides 20 for a strong cell current and longer data retention.

For a particular tunnel oxide layer thickness, the margin is primarily determined by two factors: (i) the coupling ratio and (ii) the voltage difference between memory control gate 16 and the common point between sense 25 transistor 10 and select transistor 11 when the cell is being programmed or erased. The latter in turn is proportional to the voltage difference applied between cell memory control gate 16 and bit line 13. With smaller cells and greater cell densities, both of these factors 30 have a tendency to reduce the margin. The coupling ratio is established by the layout of the cell, and a smaller layout tends to reduce the coupling ratio. As explained below, smaller cell dimensions also tend to limit the voltage difference that can be used in programming and 35 erasing the cell.

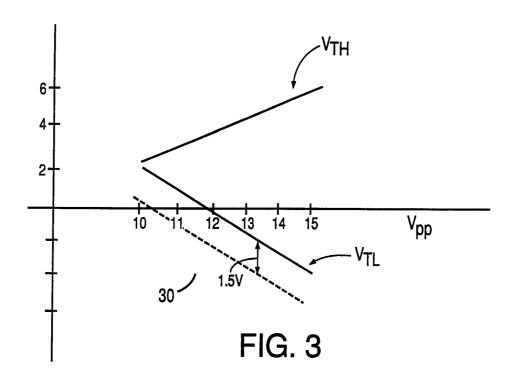

Figure 3 illustrates  $V_{TH}$  and  $V_{TL}$  as a function of the potential difference  $(V_{\rm pp})$  between the memory control gate

and the bit line during the erase and programming operations, respectively. As Figure 3 indicates,  $V_{TH}$  increases with increasing  $V_{pp}$  and  $V_{TL}$  decreases with increasing  $V_{pp}$ . Thus, the margin  $(V_{TH} - V_{TL})$  also 5 increases as  $V_{pp}$  increases.

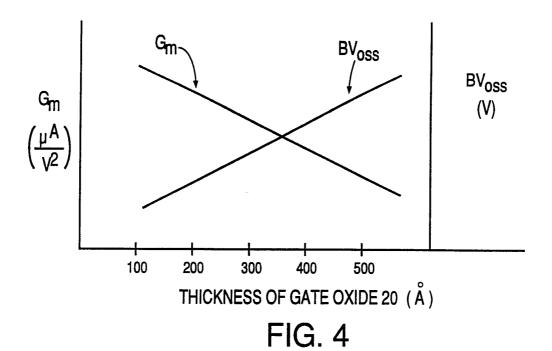

The desire for a large margin is in conflict with the increasing miniaturization of EEPROM cells. With thinner oxides, tighter design rules and more highly doped and shallower junctions, breakdown voltages such as punch 10 through, field-aided junction breakdown, and field device turn on tend to decrease. For example, referring to Figure 2, as the thickness of gate oxide 20 decreases, the field-aided junction breakdown voltage (BVDss) of select transistor 10 decreases as a result of breakdown at the PN 15 junction in the area designated 21 in Figure 2. while a thinner gate oxide has the beneficial effect, for example, of increasing the transconductance  $(G_m)$  in select transistor 10, the price of greater transconductance is a lower BVDss. This in turn limits the voltage which can be 20 used in programming or erasing the cell and makes it more difficult to obtain a wide margin. The relationship between  $G_m$  and  $BV_{DSS}$ , respectively, and the thickness of gate oxide 20 is illustrated in Figure 4.

#### SUMMARY OF THE INVENTION

The method of this invention allows the potential difference used in programming an EEPROM cell to be increased without raising the chances of voltage breakdown. This is accomplished using an EEPROM cell with a negatively biased substrate. The memory control gate of the sense transistor is pumped to a negative voltage using a charge pump. Because the substrate is negatively biased, this can be done without the risk of N-channel source-drain diffusion forward-biasing the associated PN junction, which could initiate latch up. The margin is increased one volt for every volt that the memory control gate is negatively biased.

- 4 -

## DESCRIPTION OF THE DRAWINGS

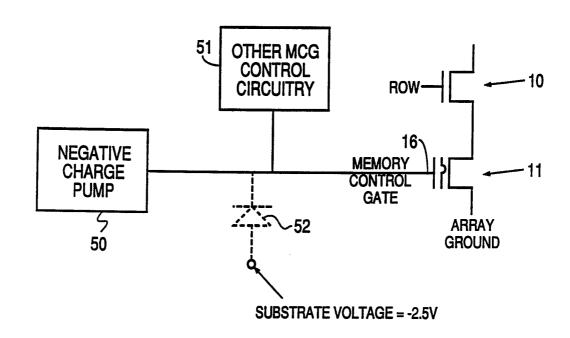

Figure 1 is a schematic diagram of a typical EEPROM cell.

Figure 2 illustrates the structure of the cell shown 5 in Figure 1.

Figure 3 is a graph of  ${\rm V}_{\rm TH}$  and  ${\rm V}_{\rm TL}$  as a function of the programming voltage.

Figure 4 is a graph of the transconductance and the source-to-drain breakdown voltage of select transistor 10 10 as a function of the thickness of the gate oxide.

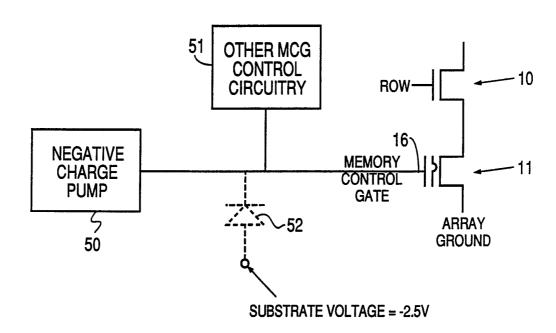

Figure 5 illustrates an arrangement in accordance with this invention.

# DESCRIPTION OF THE INVENTION

It is known in the art to back-bias the substrate of 15 an MOS device. The primary purpose of this is to reduce junction capacitance and thereby increase the speed of the cell. Typically, the substrate is biased to approximately -2.5 V.

The lower threshold voltage V<sub>TL</sub> of the sense

20 transistor in an EEPROM is determined by the coupling ratio and the potential difference between the memory control gate and the drain of the sense transistor during the programming operation. Since the select transistor is turned on during programming, the drain potential of the

25 sense transistor is essentially equal to the voltage applied to the bit line. Normally, the memory control gate is grounded, and thus V<sub>TL</sub> is proportional to the positive voltage applied to the bit line. As noted previously, this voltage cannot be increased beyond a

30 certain level without raising the risk of breakdown. The primary concern is field-aided junction breakdown in a select transistor contained in a cell other than the one being programmed.

With a back-biased substrate, the potential

35 difference between the memory control gate and the bit

line during programming may be increased by reducing the

- 5 -

voltage of the memory control gate. This has the same effect on  $V_{\text{TL}}$  as increasing the programming voltage on the bit line by an equivalent amount.

A structure for doing this is illustrated in Figure 5 5. The EEPROM cell consisting of select transistor 10 and sense transistor 11 is identical to the cell illustrated in Figure 1. A negative charge pump 50 is connected to memory control gate 16. The box labeled 51 represents other control circuitry, such as the circuitry which 10 controls memory gate 16 during the erase and read cycles.

The substrate of the cell pictured in Figure 5 is biased to a voltage of -2.5 V. The diode 52 shown in hatched form in Figure 5 represents a PN junction somewhere on the same chip which could be forward-biased 15 if the voltage of memory control gate 16 falls below the voltage of the substrate. Since diode 52 has a threshold voltage of 0.7 V, the voltage applied by negative charge pump 50 to memory control gate 16 could, in theory, be reduced to -3.2 V without creating a forward-biased PN 20 junction in diode 52 that could initiate latch-up. reality, there may be other parasitic devices which limit the degree to which the voltage at memory control gate 16 may be reduced.

Assuming that negative charge pump 50 applies a 25 voltage of -1.5 V to memory control gate 16, the hatched line 30 in Figure 3 illustrates the  $V_{\text{TL}}$  curve for the device shown in Figure 5. The  $\mathbf{V}_{\mathtt{TL}}$  curve for the cell shown in Figure 1 has been displaced downward approximately The margin has increased an equivalent amount.

Accordingly, using the method and structure of this 30 invention, the margin of an EEPROM cell may be increased, yielding a larger current in the cell and longer data retention, without increasing the programming voltage or increasing the risk of field-aided junction voltage 35 breakdown.

The foregoing description of an embodiment of this invention is intended to be illustrative and not limiting. WO 93/04475 PCT/US92/06947

- 6 -

Ę

Other embodiments and methods in accordance with this invention will be apparent, all of which are within the broad scope of this invention.

#### CLAIMS

#### I claim:

- A method of programming an EEPROM cell which includes a sense transistor formed in a substrate, said

substrate being negatively biased, the method comprising the step of maintaining a memory control gate of said sense transistor at a negative voltage during the programming of said cell.

- An arrangement for programming an EEPROM cell

comprising a means for negatively biasing a memory control gate of a sense transistor in said cell.

- 3. The arrangement of Claim 2 wherein said means comprises a negative charge pump.

- 4. The arrangement of Claim 3 wherein said sense 15 transistor is formed in a substrate, said substrate being maintained at a negative voltage.

- 5. An EEPROM cell comprising:

- a select transistor;

- a sense transistor having a memory control gate;

- 20 and

- a means for maintaining said memory control gate at a negative voltage.

- 6. The EEPROM cell of Claim 5 wherein said means comprises a negative charge pump.

FIG. 1 (PRIOR ART)

FIG. 5

# INTERNATIONAL SEARCH REPORT

nernational application No.

PCT/US92/06947

|                                                                                                                                                                                                                       | SSIFICATION OF SUBJECT MATTER                                                                                                      |                                                                                                                         |                           |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|

| , , ,                                                                                                                                                                                                                 | :G11C 11/40                                                                                                                        |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       | :365/185,189.09;307/296.2,469 to International Patent Classification (IPC) or to both                                              | national classification and IPC                                                                                         |                           |  |  |  |

| <del></del>                                                                                                                                                                                                           | LDS SEARCHED                                                                                                                       |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       | ocumentation searched (classification system followed                                                                              | by classification symbols)                                                                                              |                           |  |  |  |

|                                                                                                                                                                                                                       | 365/185,189.09;307/296.2,469                                                                                                       | · , · · · · ,                                                                                                           |                           |  |  |  |

| 0.5.                                                                                                                                                                                                                  | 303/103,107,07,30//220.2,707                                                                                                       |                                                                                                                         |                           |  |  |  |

| Documenta                                                                                                                                                                                                             | tion searched other than minimum documentation to the                                                                              | extent that such documents are included                                                                                 | in the fields searched    |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

| F                                                                                                                                                                                                                     |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

| Electronic                                                                                                                                                                                                            | lata base consulted during the international search (nat                                                                           | me of data base and, where practicable                                                                                  | , search terms used)      |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

| C. DOC                                                                                                                                                                                                                | UMENTS CONSIDERED TO BE RELEVANT                                                                                                   |                                                                                                                         |                           |  |  |  |

| Category*                                                                                                                                                                                                             | Citation of document, with indication, where app                                                                                   | propriate, of the relevant passages                                                                                     | Relevant to claim No.     |  |  |  |

| $ _{\mathbf{X}}$                                                                                                                                                                                                      | IBM TECHNICAL DISCLOSURE BU                                                                                                        | LLETIN, July 1973 Volume                                                                                                | 5                         |  |  |  |

| <u>X</u><br>Y                                                                                                                                                                                                         | 16, number2, James, "electronically Re                                                                                             | writable nonvolatice storage                                                                                            | 1-4,6                     |  |  |  |

|                                                                                                                                                                                                                       | having reduced write voltage" Pages 6                                                                                              | 690-691, See figure 1-3 and                                                                                             |                           |  |  |  |

|                                                                                                                                                                                                                       | biasing on page 691.                                                                                                               |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         | • • •                     |  |  |  |

| Y                                                                                                                                                                                                                     | US,A, 4,388,537 (KANUMA), 14 JUN                                                                                                   | IE 1983, See col 1, lines 16-                                                                                           | 3,4,6                     |  |  |  |

|                                                                                                                                                                                                                       | 20.                                                                                                                                |                                                                                                                         |                           |  |  |  |

| Y                                                                                                                                                                                                                     | IRM TECUNICAL DISCLOSIDE Bul                                                                                                       | letin January 1975 Vol. 17                                                                                              | 1-4                       |  |  |  |

|                                                                                                                                                                                                                       | IBM TECHNICAL DISCLOSURE Bulletin, January 1975, Vol. 17 1 - 4 November 8, R. Dockerty "Non-Volatice memory array with a           |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       | single famos device per cell, "Pages 23                                                                                            |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       | page 2315.                                                                                                                         |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       | r.e.                                                                                                                               |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

| X Further documents are listed in the continuation of Box C. See patent family annex.                                                                                                                                 |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

| Special categories of cited documents:  "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the                        |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       | nument defining the general state of the art which is not considered<br>be part of particular relevance                            | principle or theory underlying the inve                                                                                 |                           |  |  |  |

| *E" earlier document published on or after the international filing date  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

|                                                                                                                                                                                                                       | nument which may throw doubts on priority claim(s) or which is<br>d to establish the publication date of another citation or other | when the document is taken alone                                                                                        | 1.5 1.5                   |  |  |  |

| •                                                                                                                                                                                                                     | cial reason (as specified)                                                                                                         | "Y" document of particular relevance; the<br>considered to involve an inventive<br>combined with one or more other such | step when the document is |  |  |  |

| "O" doc                                                                                                                                                                                                               | ument referring to an oral disclosure, use, exhibition or other<br>nos                                                             | being obvious to a person skilled in th                                                                                 |                           |  |  |  |

| *P* document published prior to the international filing date but later than the priority date claimed document member of the same patent family                                                                      |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

| Date of the                                                                                                                                                                                                           | actual completion of the international search                                                                                      | Date of mailing of the international sea                                                                                | ren report                |  |  |  |

| 28 OCTO                                                                                                                                                                                                               | BER 1992                                                                                                                           | <b>30 NOV 190</b>                                                                                                       | 12                        |  |  |  |

|                                                                                                                                                                                                                       | nailing address of the ISA/ ner of Patents and Trademarks                                                                          | Authorized officer                                                                                                      | Lalemson                  |  |  |  |

| Box PCT                                                                                                                                                                                                               |                                                                                                                                    | JOSEPH CLAWSON                                                                                                          | - · ·                     |  |  |  |

| Washington, D.C. 20231  Faceimile No. NOT APPLICABLE  Telephone No. (703) 308-0593                                                                                                                                    |                                                                                                                                    |                                                                                                                         |                           |  |  |  |

Form PCT/ISA/210 (second sheet)(July 1992)\*

#### INTERNATIONAL SEARCH REPORT

alternational application No.

PCT/US92/06947

| Categoria   | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                      | Relevant to claim No |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Category* Y | IBM TECHNICAL DISCLOSURE Bulletin, January 1975, volume 15 number 8 N. Anantha et al. "Electrically erasable floating gate field effect transistor memory cell" pages 2311-2313, note $V_{sx}$ =-3 and $VG$ =-30 for write in figure 4, | 1-4                  |

| A           | note $V_{sx}$ =-3 and VG=-30 for write in figure 4,<br>US,A, 4,884,239 (ONO ET AL.), 28 NOVEMBER 1989, See<br>negative biasing, of substrate, gate in figures 5,6A,6B.                                                                  | 1-6                  |

|             |                                                                                                                                                                                                                                         |                      |