(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-5536

(P2007-5536A)

(43) 公開日 平成19年1月11日(2007.1.11)

(51) Int.C1.

HO1L 21/3205 (2006.01)

HO1L 23/52 (2006.01)

F 1

HO1L 21/88

HO1L 21/88

テーマコード(参考)

S

T

審査請求 未請求 請求項の数 12 O L (全 21 頁)

(21) 出願番号

特願2005-183264 (P2005-183264)

(22) 出願日

平成17年6月23日 (2005.6.23)

(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100089233

弁理士 吉田 茂明

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 富田 和朗

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】クラックの発生等を防止することができ、複数の層間絶縁膜内において、素子として機能する配線等を配設できる領域を広くとることができ、製造コストの削減を図ることができる、半導体装置を提供することを目的とする。

【解決手段】本発明に係わる半導体装置では、誘電率 $k$ が2.7未満である低誘電率膜4等を有している。そして、当該低誘電率膜4等において、パッド部47の下方部分には、低誘電率膜4等よりも硬度の高い材料(たとえば、第一のダミーパターン10等、第二のダミーパターン12等)が形成されている。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

半導体基板と、

前記半導体基板上に形成される、複数層の層間絶縁膜と、

前記層間絶縁膜の上面に形成されるパッド部とを、

備えており、

前記複数層の層間絶縁膜は、

誘電率が2.7未満である低誘電率膜の層を含んでおり、

前記複数層の層間絶縁膜の各層のうち、前記低誘電率膜の層のみにおいて、前記パッド部の下方部分には、前記低誘電率膜よりも硬度の高い材料が形成されている、

ことを特徴とする半導体装置。 10

**【請求項 2】**

前記硬度の高い材料は、

導電体であり、前記低誘電率膜の第一の主面の表面内に形成されている、

ことを特徴とする請求項1に記載の半導体装置。 20

**【請求項 3】**

前記導電体は、

配線のダミーパターンである、

ことを特徴とする請求項2に記載の半導体装置。 20

**【請求項 4】**

前記配線のダミーパターンは、

平面視において、メッシュ状である、

ことを特徴とする請求項3に記載の半導体装置。 20

**【請求項 5】**

前記配線のダミーパターンは、

平面視において、島状に点在して形成されている、

ことを特徴とする請求項3に記載の半導体装置。 20

**【請求項 6】**

前記配線のダミーパターンは、

平面視において、所定の方向に沿って、ストライプ状に複数形成されている、

ことを特徴とする請求項3に記載の半導体装置。 30

**【請求項 7】**

前記配線のダミーパターンは、

前記低誘電率膜の隣接する上下層に、各自形成されており、

上層に存する前記配線のダミーパターンと、下層に存する前記配線のダミーパターンと

を接続する、ビアのダミーパターンを、さらに備えている、

ことを特徴とする請求項3に記載の半導体装置。 30

**【請求項 8】**

前記配線のダミーパターンは、

平面視において、メッシュ状、島状、またはストライプ状のいずれかの形状であり、

前記ビアのダミーパターンは、

平面視において、所定の方向に沿って、ストライプ状に形成されている、

ことを特徴とする請求項7に記載の半導体装置。 40

**【請求項 9】**

前記導電体は、

ビアのダミーパターンである、

ことを特徴とする請求項2に記載の半導体装置。 40

**【請求項 10】**

前記ビアのダミーパターンは、

平面視において、第一の方向に沿って、ストライプ状に形成されている、 50

ことを特徴とする請求項 9 に記載の半導体装置。

**【請求項 11】**

前記層間絶縁膜内に形成されており、素子として機能する、複数のビアパターンを、さらに備えており、

ストライプ状に形成された前記ビアのダミーパターンのストライプ幅は、

前記複数のビアパターンの内で、最小の径寸法を有する前記ビアパターンの当該最小の径寸法の、1倍以上、10倍以下である、

ことを特徴とする請求項 10 に記載の半導体装置。

**【請求項 12】**

前記パッド部は、

10

平面視において、前記層間絶縁膜上に、第二の方向に沿って、複数配設されており、

前記ビアのダミーパターンの前記第一の方向は、

前記第二の方向と、略垂直である、

ことを特徴とする請求項 10 に記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

この発明は、半導体装置に係る発明であり、たとえば、パッド部、複数の層間絶縁膜および当該層間絶縁膜中に配設される多層配線構造を有する、半導体装置に適用することができる。

20

**【背景技術】**

**【0002】**

半導体基板上に、複数層の層間絶縁膜が堆積されており、最上層の層間絶縁膜上にパッド部を有する、半導体装置が存在している。ここで、層間絶縁膜には、多層配線と配線同士を接続するビアとが、形成されている。

**【0003】**

また、上記構成の半導体装置において、微細化が進み、これに伴いボンディングパッドも縮小化されてきている。また、当該微細化に伴い、信号遅延の問題も生じてきている。当該信号遅延防止等の観点から層間絶縁膜として、酸化シリコンの誘電率より誘電率が低い絶縁膜が適用されている。ここで、当該誘電率の低い絶縁膜として、一般的に、多孔質性の絶縁膜が多く適用されている。

30

**【0004】**

しかし、当該誘電率の低い絶縁膜の強度は、比較的弱い。したがって、当該誘電率の低い絶縁膜が適用された場合には、パッド部に対するボンディングの際に、当該誘電率の低い絶縁膜にクラックが発生する可能性がある。また、当該誘電率の低い絶縁膜は、一般的に他の部材との密着性は良くない。したがって、当該誘電率の低い絶縁膜が適用された場合には、パッド部に対するプローピングの際に、誘電率の低い絶縁膜の上面（または下面）において、膜剥がれが生じる可能性がある。

**【0005】**

当該クラック発生や膜剥がれを抑制する技術として、たとえば特許文献 1 がある。

40

**【0006】**

特許文献 1 に係わる技術では、パッド部下方の誘電率が低い絶縁膜には、全層において、ダミーパターンが形成されていた。ここで、特許文献 1 では、ダミーパターンは、酸化シリコン系の膜よりも機械的強度の弱い、誘電率の低い絶縁膜（たとえば、誘電率  $k$  が 4 未満の絶縁膜）の、全てにおいて形成されている。ここで、当該誘電率の低い絶縁膜は、一般的に、多孔質性の絶縁膜が多く適用されている。

**【0007】**

**【特許文献 1】特開 2001-267323 号公報**

**【発明の開示】**

**【発明が解決しようとする課題】**

50

## 【0008】

上記のように、特許文献1では、ダミーパターンは、酸化シリコン系の膜よりも機械的強度の弱い、誘電率の低い絶縁膜（たとえば、誘電率kが4未満の絶縁膜）の、全てにおいて形成されている。

## 【0009】

したがって、素子として機能する配線等の形成領域が減少してしまう。また、製造工程が複雑化し、製造コストが高くなるという問題が生じている。

## 【0010】

そこで、本発明では、素子として機能する配線等の配設のために、層間絶縁膜内をより有効利用することができ、また、製造コストの削減を図ることができる、半導体装置を提供することを目的とする。10

## 【課題を解決するための手段】

## 【0011】

上記の目的を達成するために、本発明に係る請求項1に記載の半導体装置は、半導体基板と、前記半導体基板上に形成される、複数層の層間絶縁膜と、前記層間絶縁膜の上面に形成されるパッド部とを、備えており、前記複数層の層間絶縁膜は、誘電率が2.7未満である低誘電率膜の層を含んでおり、前記複数層の層間絶縁膜の各層のうち、前記低誘電率膜の層のみにおいて、前記パッド部の下方部分には、前記低誘電率膜よりも硬度の高い材料が形成されている。20

## 【発明の効果】

## 【0012】

本発明の請求項1に記載の半導体装置は、半導体基板と、半導体基板と、前記半導体基板上に形成される、複数層の層間絶縁膜と、前記層間絶縁膜の上面に形成されるパッド部とを、備えており、前記複数層の層間絶縁膜は、誘電率が2.7未満である低誘電率膜の層を含んでおり、前記複数層の層間絶縁膜の各層のうち、前記低誘電率膜の層のみにおいて、前記パッド部の下方部分には、前記低誘電率膜よりも硬度の高い材料が形成されているので、パッド部に対してボンディング処理等を施したとしても、当該パッド部の下方に存する低誘電率膜において、クラックが発生する等の不具合を解消することができる。また、当該クラックの発生防止の観点等から、本当に必要な層間絶縁膜（低誘電率膜）にのみ他の部材を形成している。したがって、素子として機能する配線等の配設のために、層間絶縁膜内をより有効利用することができる。また、不要な部分には、当該高度の高い材料を形成しないので、製造は簡素化され、製造コストの削減も可能となる。30

## 【発明を実施するための最良の形態】

## 【0013】

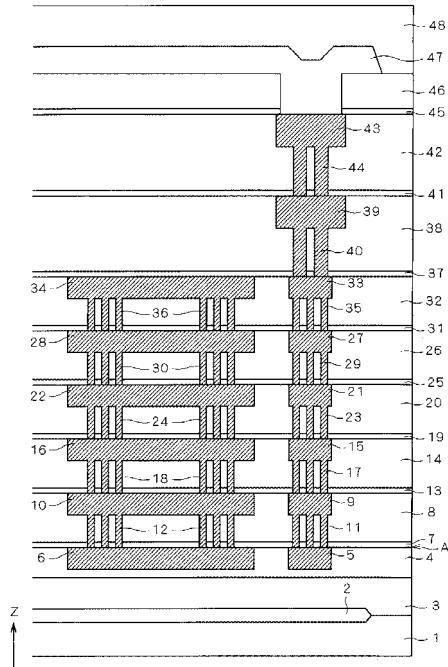

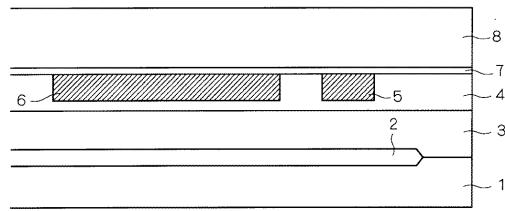

発明者は、図1に示す断面構造を有する半導体装置に対して、層間絶縁膜101の誘電率を変化させて、パッド部104に対してボンディング処理やプローピング処理等を施す実験をした。そして、層間絶縁膜101が幾らの誘電率の場合に、当該層間絶縁膜101において、クラックの発生や膜剥がれが発生するのかを、確認を行った。

## 【0014】

ここで、実験対象となった半導体装置は、図1に示すように、半導体基板100上に、複数層の層間絶縁膜101が形成されている。また、図1に示すように、層間絶縁膜101内には、配線102と上下層の配線102同士を接続するビアパターン103が形成されている。そして、最上層の層間絶縁膜101上には、配線102と接続されたパッド部104が形成されている。40

## 【0015】

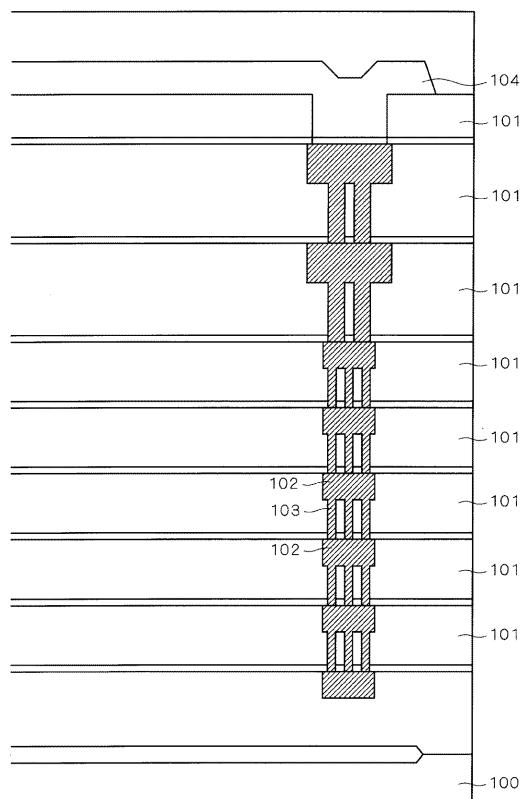

上記実験の結果（特に、クラック発生に関する実験結果）は、図2である。ここで、図2において、「OK」はクラック不発生を意味しており、「NG」はクラック発生を意味している。

## 【0016】

図2の実験結果を含む様々な実験結果より、発明者は、層間絶縁膜101の誘電率kが50

2.7未満の場合に（以下、誘電率kが2.7未満の層間絶縁膜101を、低誘電率膜と称する）、クラックの発生や膜剥がれの発生が起こることを発見した。つまり、誘電率kが2.7以上の層間絶縁膜101を採用した場合には、たとえパッド部104へのボンディング処理等を施したとしても、クラック等が生じないことを発見した。

#### 【0017】

以上により、本発明に係わる半導体装置では、誘電率が2.7未満の低誘電率膜の全てにおいて、パッド部の下方部分に、低誘電率膜よりも硬度の硬い材料を形成することを特徴とする。つまり、複数層の層間絶縁膜を備えている場合において、当該複数層の層間絶縁膜の各層のうち、誘電率が2.7未満の低誘電率膜の層のみに、パッド部の下方部分に、低誘電率膜よりも硬度の硬い材料を形成することを特徴とする。10

#### 【0018】

このように、低誘電率膜の所定箇所を、より硬度の硬い材料で置き換えることにより、たとえ、パッド部にボンディング等の処理を施したとしても、層間絶縁膜内においてクラックの発生が起こることを防止することができる。

#### 【0019】

以下、この発明をその実施の形態を示す図面に基づいて具体的に説明する。なお、以下の実施の形態では、上記硬度の硬い材料として、導電体（より具体的には、ダミーパターン）を適用する場合について言及している。しかし、これに限る必要は無く、当該より硬度の硬い材料として、絶縁膜を採用しても良い。

#### 【0020】

##### <実施の形態1>

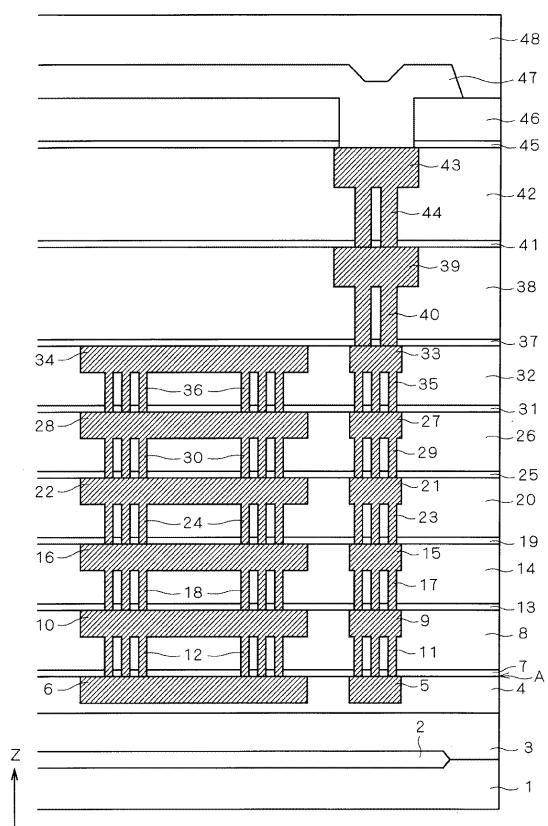

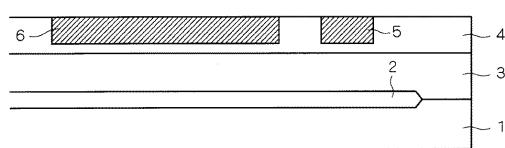

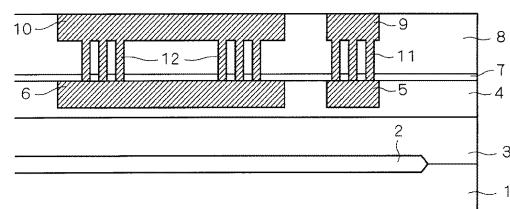

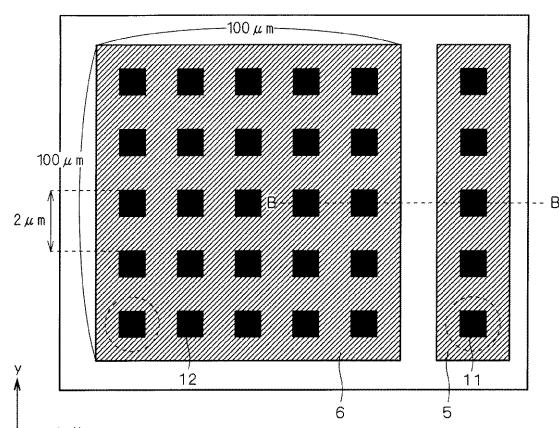

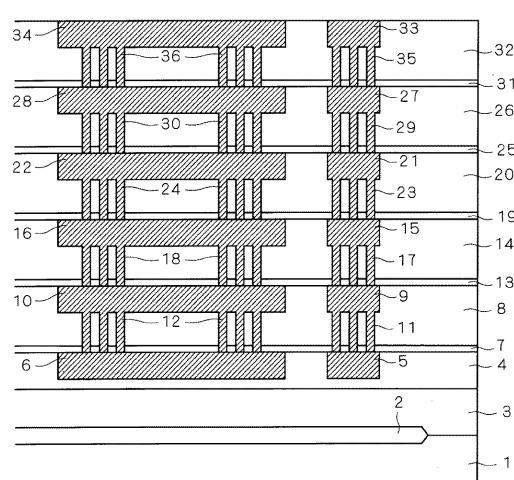

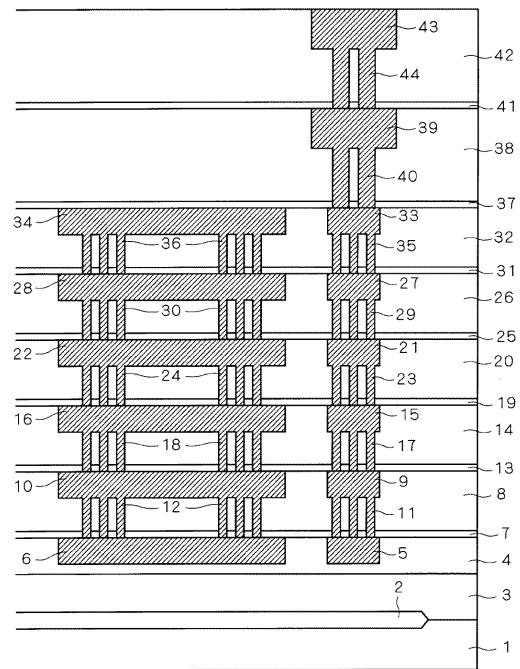

図3は、本実施の形態に係わる半導体装置の構成を示す、断面図である。また、図4は、図3に示した半導体装置において、「A」の層の平面構成を示す平面図である。ここで、図3の断面図は、図4で示したB-B断面線に沿って切断した場合の図であると、把握できる。20

#### 【0021】

なお、本説明において、配線パターンと同時形成されるダミーパターンを、配線のダミーパターンとする（以下では、当該配線のダミーパターンを第一のダミーパターンと称する）。また、ビアパターンと同時形成されるダミーパターンを、ビアのダミーパターンとする（以下では、当該ビアのダミーパターンを第二のダミーパターンと称する）。30

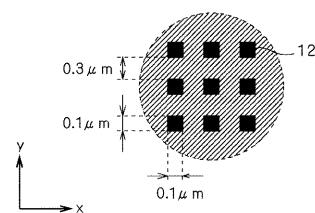

#### 【0022】

また、図4では、図面の都合上、ビアパターン11や第二のダミーパターン12が形成される領域を、黒く塗りつぶして図示している。しかし、図4の丸の点線領域を拡大した図5から分かるように、実際には、複数のビアパターン11（もしくは、複数の第二のダミーパターン12）が形成されている。

#### 【0023】

次に、図3～5に示した図を用いて、本実施の形態に係わる半導体装置の構成について、説明する。

#### 【0024】

図3に示すように、シリコン基板等の半導体基板1の表面内には、HDP(High Density Plasma)酸化膜等の分離酸化膜2が形成されている。ここで、分離酸化膜2の膜厚は、たとえば300nm程度である。40

#### 【0025】

また、分離酸化膜2が形成されている半導体基板1上には、USG(Un-doped Silicate Glass)酸化膜等のコンタクト層間膜3が形成されている。ここで、コンタクト層間膜3の膜厚は、たとえば400nm程度である。なお、当該コンタクト層間膜3には、ゲート電極やコンタクト等も形成される。しかし、図面では、ゲート電極やコンタクト等は省略している。

#### 【0026】

また、コンタクト層間膜3上には、誘電率kが2.7未満の層間絶縁膜（以後、誘電率

10

20

30

40

50

$k$  が 2 . 7 未満である層間絶縁膜を、低誘電率膜と称する) 4 が形成されている。ここで、低誘電率膜 4 の膜厚は、たとえば 1 5 0 nm 程度である。なお、当該低誘電率膜 4 の代わりに、TEOS 酸化膜を形成しても良い。

#### 【0027】

また、低誘電率膜 4 の表面内には、素子として機能する配線パターン 5 (以後、素子として機能する配線パターンを、単に配線パターンと称する) と、素子として機能しない第一のダミーパターン 6 (以後、素子として機能しない第一のダミーパターンを、単に第一のダミーパターンと称する) とが、形成されている。

#### 【0028】

ここで、第一のダミーパターン 6 は、配線パターン 5 と同種材料から成る導電体 (たとえば、銅を含む導電体) である。また、図 3 , 4 から分かるように、第一のダミーパターン 6 は、配線パターン 5 と同層に形成されている。また、第一のダミーパターン 6 の厚さと配線パターン 5 の厚さとは、略同一である。

#### 【0029】

第一のダミーパターン 6 は、図 4 に示すように、 $x$  ,  $y$  方向の寸法は、各々 1 0 0  $\mu m$  程度である。また、第一のダミーパターン 6 の $z$  方向の寸法は、1 5 0 nm 程度である。また、図示されていないが、第一のダミーパターン 6 は、パッド部 4 7 の下方の領域内において、1 2 0  $\mu m$  程度のピッチで、水平方向に複数形成されている。

#### 【0030】

また、第一のダミーパターン 6 は、低誘電率膜 4 の第一の主面の表面内に形成されている。上記までの第一のダミーパターン 6 の特徴は、下記の第一のダミーパターン 1 0 , 1 6 等においても共通する。

#### 【0031】

なお、配線パターン 5 および第一のダミーパターン 6 は各々、バリアメタル膜と Cu 膜とから構成されている。バリアメタル膜は、1 0 nm 程度の膜厚の TaN 上に、1 0 nm 程度の膜厚の Ta 膜を形成することにより、構成される。また、Cu 膜の膜厚は、1 5 0 nm 程度である。

#### 【0032】

さて、上記配線パターン 5 や第一のダミーパターン 6 が形成されている低誘電率膜 4 上には、SiC 膜等のライナー膜 7 が形成されている。ここで、ライナー膜 7 の膜厚は、たとえば 5 0 nm 程度である。また、ライナー膜 7 の機械的強度は強く、多孔質性でもない。当該ライナー膜 7 は、導電体の拡散防止やエッチングストッパー等として機能している。

#### 【0033】

また、ライナー膜 7 上には、3 5 0 nm 程度の膜厚の低誘電率膜 8 が形成されている。

#### 【0034】

また、低誘電率膜 8 には、配線パターン 9 および第一のダミーパターン 1 0 が形成されている。低誘電率膜 8 には、素子として機能するビアパターン 1 1 (以後、素子として機能するビアパターンを、単にビアパターンと称する) 、および素子として機能しない第二のダミーパターン 1 2 (以後、素子として機能しない第二のビアパターンを、単に第二のビアパターンと称する) が形成されている。

#### 【0035】

ここで、第二のダミーパターン 1 2 は、ビアパターン 1 1 と同種材料から成る導電体 (たとえば、銅を含む導電体) である。また、図 3 , 4 から分かるように、第二のダミーパターン 1 2 は、ビアパターン 1 1 と同層に形成されている。また、第二のダミーパターン 1 2 の高さとビアパターン 1 1 の高さとは、略同一である。

#### 【0036】

第二のダミーパターン 1 2 は、図 5 に示すように、 $x$  ,  $y$  方向の寸法は、0 . 1  $\mu m$  程度である。また、第二のダミーパターン 1 2 の $z$  方向の寸法は、3 5 0 nm 程度である。また、図 5 に示すように、第二のダミーパターン 1 2 は、0 . 3  $\mu m$  程度のピッチで、水

10

20

30

40

50

平方向に複数形成されている。また、図5で示した3×3配列の第二のダミーパターン12から構成される、第二のダミーパターン群同士は、図4に示すように、2μmピッチで形成されている。

#### 【0037】

ビアパターン11は、配線パターン5と配線パターン9とを接続している。また、第二のダミーパターン12は、第一のダミーパターン6と第一のダミーパターン10とを接続している。

#### 【0038】

上記までの第二のダミーパターン12の特徴は、下記の第二のダミーパターン18, 24等においても共通する。

#### 【0039】

なお、配線パターン9および第一のダミーパターン10は各々、バリアメタル膜とCu膜とから構成されている。バリアメタル膜は、10nm程度の膜厚のTaN上に、10nm程度の膜厚のTa膜を形成することにより、構成される。また、Cu膜の膜厚は、200nm程度である。

#### 【0040】

さて、低誘電率膜8上には、上記ライナー膜7から低誘電率膜8までの層形態（配線パターン9や第一のダミーパターン10等を含む）が繰り返し形成されている。

#### 【0041】

つまり、低誘電率膜8上には、ライナー膜13が形成されており、ライナー膜13上には、低誘電率膜14が形成されている。ここで、低誘電率膜14内には、上記と同じ構造にて、配線パターン15、第一のダミーパターン16、ビアパターン17、および第二のダミーパターン18が形成されている。

#### 【0042】

また、低誘電率膜14上には、ライナー膜19が形成されており、ライナー膜19上には、低誘電率膜20が形成されている。ここで、低誘電率膜20内には、上記と同じ構造にて、配線パターン21、第一のダミーパターン22、ビアパターン23、および第二のダミーパターン24が形成されている。

#### 【0043】

また、低誘電率膜20上には、ライナー膜25が形成されており、ライナー膜25上には、低誘電率膜26が形成されている。ここで、低誘電率膜26内には、上記と同じ構造にて、配線パターン27、第一のダミーパターン28、ビアパターン29、および第二のダミーパターン30が形成されている。

#### 【0044】

また、低誘電率膜26上には、ライナー膜31が形成されており、ライナー膜31上には、低誘電率膜32が形成されている。ここで、低誘電率膜32内には、上記と同じ構造にて、配線パターン33、第一のダミーパターン34、ビアパターン35、および第二のダミーパターン36が形成されている。

#### 【0045】

さて、低誘電率膜32上には、ライナー膜37が形成されており、ライナー膜37上には、TEOS(Tetraethoxysilane)膜等の層間絶縁膜38が形成されている。ここで、層間絶縁膜38の膜厚は、たとえば700nm程度である。また、層間絶縁膜38の誘電率kは、2.7以上である。

#### 【0046】

層間絶縁膜38内には、配線パターン39およびビアパターン40が形成されている。ここで、ビアパターン40は、配線パターン39と配線パターン33とを接続している。なお、配線パターン39は、バリアメタル膜とCu膜とから構成されている。バリアメタル膜は、10nm程度の膜厚のTa上に、10nm程度の膜厚のTaN膜を形成することにより、構成される。また、Cu膜の膜厚は、350nm程度である。

#### 【0047】

10

20

30

40

50

層間絶縁膜38上には、ライナー膜41が形成されており、ライナー膜41上には、TEOS(Tetraethoxysilane)膜等の層間絶縁膜42が形成されている。ここで、層間絶縁膜42の膜厚は、たとえば700nm程度である。また、層間絶縁膜42の誘電率kは、2.7以上である。

#### 【0048】

層間絶縁膜42内には、配線パターン43およびビアパターン44が形成されている。ここで、ビアパターン44は、配線パターン43と配線パターン39とを接続している。なお、配線パターン43は、バリアメタル膜とCu膜とから構成されている。バリアメタル膜は、10nm程度の膜厚のTa上に、10nm程度の膜厚のTaN膜を形成することにより、構成される。また、Cu膜の膜厚は、350nm程度である。

10

#### 【0049】

さて、層間絶縁膜42上には、ライナー膜45が形成されており、ライナー膜45上には、TEOS(Tetraethoxysilane)膜等の層間絶縁膜46が形成されている。ここで、層間絶縁膜46の膜厚は、たとえば500nm程度である。また、層間絶縁膜46の誘電率kは、2.7以上である。また、層間絶縁膜46には、配線パターン43が露出するような開口部が形成されている。

#### 【0050】

上記開口部を充填するように、層間絶縁膜46上には、パッド部47が形成されている。したがって、パッド部47は、配線パターン43と接続されている。ここで、パッド部47は、たとえばバリアメタル膜とAlCu膜とから構成されている。バリアメタル膜は、10nm程度の膜厚のTi上に、15nm程度の膜厚のTiN膜を形成することにより、構成される。また、AlCu膜の膜厚は、1000nm程度である。

20

#### 【0051】

なお、上記までの構成から明らかなように、パッド部47は、全ての配線パターン5, 9, 15等および全てのビアパターン11, 17, 23等と、電気的に接続されている。

#### 【0052】

さらに、図3に示すように、パッド部47を覆うように、層間絶縁膜46上には、パッシベーション膜48が形成されている。当該パッシベーション膜48として、p-SiN膜(プラズマ窒化膜)等を採用することができる。また、パッシベーション膜48の膜厚は、たとえば1000nm程度である。

30

#### 【0053】

上記まで構成において、パッド部47の下方の層間絶縁膜(低誘電率膜を含む)において、以下の点に注目すべきである。

#### 【0054】

つまり、誘電率kが2.7未満である全ての低誘電率膜4, 8, 14, 20, 26, 32のみ、第一のダミーパターン6, 10, 16, 22, 28, 34、および第二のダミーパターン12, 18, 24, 30, 36が形成されている。これに対して、誘電率kが2.7以上である層間絶縁膜38, 42内には、上記各ダミーパターンは形成されていない。

#### 【0055】

なお、低誘電率膜8, 14, 20, 26, 32は、単層である場合に言及した。しかし、SiOC膜、低誘電率膜、SiOC膜とが当該順に形成された、低誘電率膜を含む、積層の層間絶縁間を採用しても良い。

40

#### 【0056】

次に、本実施の形態に係わる半導体装置の製造方法を、工程断面図を用いて具体的に説明する。

#### 【0057】

まず、シリコン基板等の半導体基板1を用意する。そして、当該半導体基板1の表面に對して、STI(Shallow Trench Isolation)法を施す。これにより、図6に示すように、半導体基板1の所定の表面内に、分離酸化膜2が形成される

50

。なお、当該分離酸化膜2の膜厚は、たとえば300nm程度である。

#### 【0058】

次に、分離酸化膜2を覆うように、半導体基板1上にコンタクト層間膜3を形成する(図6参照)。ここで、当該コンタクト層間膜3の膜厚は、たとえば600nm程度である。

#### 【0059】

次に、コンタクト層間膜3の上面に対して、研磨処理を施す。これにより、コンタクト層間膜3を200nm程度、除去する。次に、図6に示すように、コンタクト層間膜3上に、150nm程度の膜厚の低誘電率膜4を形成する。なお、当該低誘電率膜4の代わりに、TEOS酸化膜を形成しても良い。

#### 【0060】

次に、低誘電率膜4に対して、フォトリソグラフィ工程を施す。これにより、低誘電率膜4の所定の表面内に、凹部を形成する。

#### 【0061】

次に、低誘電率膜4に対して、スパッタリング法を施す。これにより、低誘電率膜4の上面(凹部の側面および底面を含む)にTa(10nm程度)/TaN(10nm程度)のバリアメタル膜(図示せず)が形成される。

#### 【0062】

次に、銅めっき処理を施すことにより、バリアメタル膜上に、500nm程度の膜厚の銅めっきを形成する。その後、銅めっき等に対して、たとえばCMP(Chemical Mechanical Polishing)を施す。これにより、前記凹部に、図6に示すように、150nm程度の膜厚の、配線パターン5および第一のダミーパターン6が形成する。

#### 【0063】

次に、図7に示すように、低誘電率膜4上に、膜厚50nm程度のライナー膜7を形成する。ここで、図7に示すように、ライナー膜7は、配線パターン5および第一のダミーパターン6を覆うように、形成されている。次に、図7に示すように、当該ライナー膜7上に、膜厚350nm程度の低誘電率膜8を形成する。

#### 【0064】

なお、低誘電率膜8は、単層である場合に言及した。しかし、低誘電率膜を含む、積層の層間絶縁間を採用しても良い。以下、低誘電率膜14, 20, 26, 32についても同様である。

#### 【0065】

次に、低誘電率膜8に対して、フォトリソグラフィ工程を施す。これにより、低誘電率膜8の所定の表面内に、ビアパターン11形成のための開口部と、第二のダミーパターン12形成のための開口部とが形成される。さらに、低誘電率膜8に対して、別のフォトリソグラフィ工程を施す。これにより、低誘電率膜8の所定の表面内に、配線パターン9形成のための開口部と、第一のダミーパターン10形成のための開口部とが形成される。

#### 【0066】

次に、上記と同様に、低誘電率膜8に対して、バリアメタル形成のためのスパッタリング法、銅めっき法、および余分な銅めっき等を除去するためのCMP処理等を、施す。以上により、図8に示すように、低誘電率膜8の表面内に、配線パターン9、第一のダミーパターン10、ビアパターン11、および第二のダミーパターン12を、各々形成する。

#### 【0067】

なお、上述の通り、ビアパターン11は、配線パターン5と配線パターン9とを電気的に接続するように、形成される。また、第二のダミーパターン12は、第一のダミーパターン6と第一のダミーパターン10とを電気的に接続するように、形成される。なお、配線パターン9の膜厚は、200nm程度である。

#### 【0068】

次に、上記、ライナー膜7、低誘電率膜8、配線パターン9、第一のダミーパターン1

10

20

30

40

50

0、ビアパターン11、第二のダミーパターン12の形成方法を、繰り返し施す。つまり、ファイン工程を繰り返し実施する。ここで、ファイン工程とは、100 nm L/S、100 nm のパターンを形成する工程である。

#### 【0069】

当該ファイン工程を繰り返し施した後の様子を、図9に示す。なお、当該ファイン工程の繰り返しは、設計に依存して決定される。したがって、ファイン工程により形成される層数は、図9の場合に限定する必要は無い。

#### 【0070】

図9に示すように、誘電率kが2.7未満である低誘電率膜8等には、第一のダミーパターン10等および第二のダミーパターン12等が形成されている。特に、第一のダミーパターン10等および第二のダミーパターン12等は、後に形成されるパッド部47の下方において、形成される。

#### 【0071】

さて次に、低誘電率膜32上に、膜厚50 nm程度のライナー膜37を形成する。その後、ライナー膜37上に、膜厚1000 nm程度のTEOS膜を形成する。その後、当該TEOS膜を約30 nm程度研磨することにより、図10に示すように、層間絶縁膜38を形成する。ここで、層間絶縁膜38の誘電率kは、2.7以上である。

#### 【0072】

次に、層間絶縁膜38に対して、フォトリソグラフィ工程を施す。これにより、層間絶縁膜38の所定の表面内に、ビアパターン40形成のための開口部が形成される。さらに、層間絶縁膜38に対して、別のフォトリソグラフィ工程を施す。これにより、層間絶縁膜38の所定の表面内に、配線パターン39形成のための開口部が形成される。

#### 【0073】

次に、上記と同様に、層間絶縁膜38に対して、バリアメタル形成のためのスパッタリング法、銅めっき法、および余分な銅めっき等を除去するためのCMP処理等を、施す。以上により、図10に示すように、層間絶縁膜38の表面内に、配線パターン39、ビアパターン40が形成される。

#### 【0074】

なお、上述の通り、ビアパターン40は、配線パターン39と配線パターン33とを電気的に接続するように、形成される。なお、配線パターン39の膜厚は、350 nm程度である。

#### 【0075】

次に、上記、ライナー膜37、層間絶縁膜38、配線パターン39、およびビアパターン40の形成方法を、繰り返し施す。つまり、セミグローバル工程および/またはグローバル工程を繰り返し実施する。ここで、セミグローバル工程とは、200 nm L/S、200 nm のパターンを形成する工程である。また、グローバル工程とは、800 nm L/S、600 nm のパターンを形成する工程である。

#### 【0076】

当該セミグローバル工程、グローバル工程を繰り返し施した後の様子を、図10に示す。なお、当該セミグローバル工程、グローバル工程の繰り返しは、設計に依存して決定される。したがって、セミグローバル工程等により形成される層数は、図10の場合に限定する必要は無い。

#### 【0077】

図10に示すように、誘電率kが2.7以上である層間絶縁膜38等には、第一のダミーパターンおよび第二のダミーパターンは、形成されていない。

#### 【0078】

さて次に、誘電率kが2.7以上である層間絶縁膜42上に、膜厚50 nm程度のライナー膜45を形成する。その後、ライナー膜45上に、TEOS膜等の層間絶縁膜46を形成する。ここで、当該層間絶縁膜46の膜厚は、500 nm程度である。

#### 【0079】

10

20

30

40

50

次に、層間絶縁膜46に対して、フォトリソグラフィ工程を施す。これにより、層間絶縁膜46の所定の表面内に、開口部が形成される。なお、当該開口部からは、配線パターン43が露出している。

#### 【0080】

次に、層間絶縁膜46上に（上記開口部の底面部および側面部も含む）、たとえばTiN(15nm)/Ti(10nm)の積層膜から成る、バリアメタル膜を形成する。その後、当該バリアメタル膜上に、AlCu膜等を成膜する。その後、所定の形状にパターンングすることにより、たとえば当該バリアメタル膜とAlCu膜とから成る、引き出し電極パッドとなるパッド部47が形成される。

#### 【0081】

ここで、図3に示したように、パッド部47は、層間絶縁膜46に形成された開口部を充填しており、配線パターン43と電気的に接続している。

#### 【0082】

最後に、パッド部47を覆うように、層間絶縁膜46上に、パッシベーション膜48を形成する。そして、一部においてパッド部47を露出させるために、当該パッシベーション膜48の一部に開口部（図示せず）を設ける。

#### 【0083】

以上までの工程により、図3に示した半導体装置が完成する。なお、パッシベーション膜48として、p-SiN膜（プラズマ窒化膜）等を採用することができる。また、パッシベーション膜48の膜厚は、1000nm程度である。

#### 【0084】

以上のように、本実施の形態に係わる半導体装置では、パッド部47の下方に注目すると、誘電率kが2.7未満である低誘電率膜8等内に、当該低誘電率膜8等よりも硬度の硬い部材（本実施の形態では、第一のダミーパターン10等および第二のダミーパターン12等）が形成されている。つまり、低誘電率膜8の一部を、当該より硬い部材により置き換えている。

#### 【0085】

したがって、当該パッド部47に対して、ワイヤーボンディング処理等を施したとしても、低誘電率膜8等においてクラックが発生することを防止することができる。

#### 【0086】

また、本実施の形態に係わる半導体装置では、誘電率kが2.7未満である低誘電率膜8等内にのみ、上記より硬い部材を形成している。つまり、誘電率kが2.7以上である層間絶縁膜38等内には、上記より硬い部材は形成されていない。

#### 【0087】

したがって、特許文献1に係わる半導体装置よりも、本実施の形態に係わる半導体装置の方が、より層間絶縁膜内を配線等の配設として、有効利用することができる。また、余分な、第一のダミーパターン等を形成する必要が無いので、製造の簡略化および低コスト化を図ることができる。

#### 【0088】

また、本実施の形態に係わる半導体装置では、上記の硬度のより硬い材料は、導電体（たとえば、銅を含む導電体）であり、低誘電率膜4等の第一の主面の表面内に形成されている。

#### 【0089】

したがって、たとえば、パッド部47に対してプローピング処理を施したとしても、また、製造途中にCMP処理を施したとしても、より下層に存する、低誘電率膜4等と、当該低誘電率膜4の第一の主面側と接する他の絶縁膜等との間で、膜ズレまたは膜剥がれ等の発生を防止することができる。

#### 【0090】

また、低誘電率膜4等内に形成される上記導電体として、平面視における面積が比較的大きな、第一のダミーパターン6等採用している。

10

20

30

40

50

## 【0091】

したがって、低誘電率膜4と、当該低誘電率膜4と接する他の絶縁膜等との間での密着性を、より向上させることができる。よって、上記膜ズレや膜剥がれ等を完全に防止することができる。さらに、配線パターン5等の形成の際に、同時に第一のダミーパターン6等を形成することも可能となる。

## 【0092】

また、低誘電率膜4等内に形成される上記導電体として、層間絶縁膜の堆積方向に伸びて形成された、柱状の第二のダミーパターン12等採用している。

## 【0093】

したがって、パッド部47に対してワイヤーボンディング処理等を施したとしても、上記同様に、低誘電率膜4等内においてクラックが発生することを防止することができる。さらに、第二のダミーパターン12等は、上記の通り、柱状であるので、上記ボンディング処理等の際の緩衝材的機能を有する。よって、ワイヤーボンディング処理等の際に生じる、上下層に存在する他の低誘電率膜等へのダメージを、より緩和することができる。さらに、ビアパターン11等の形成の際に、同時に第二のダミーパターン12等を形成することも可能となる。

## 【0094】

なお、上記では、低誘電率膜4等内において、第一のダミーパターン6等および第二のダミーパターン12等が形成されている。しかし、第一のダミーパターン6等のみ、または、第二のダミーパターン12等のみを、低誘電率膜4等内に形成する形態を採用しても良い。

## 【0095】

また、パッド部47の下方において、低誘電率膜4等内的一部分に、導電体（第一のダミーパターン6等）を形成する場合に言及した。しかし、パッド部47下方の低誘電率膜4の全てを上記導電体等で置換することも可能である。

## 【0096】

なお、誘電率kが2.7未満である低誘電率膜として、たとえば、誘電率kが2.0～2.5の範囲内のポーラスSiOC(CVD系、または塗布型MSQ(Methylsilsesquioxane：メチルシリセスキオキサン）膜、もしくはポーラス有機ポリマー膜等を採用することができる。

## 【0097】

また、ライナー膜として、SiC膜以外に、SiCN膜、SiCO膜、SiN膜、およびこれらの積層膜であっても良い。これらの膜は、多孔質性でなく、また強度も比較的硬い。

## 【0098】

## &lt;実施の形態2&gt;

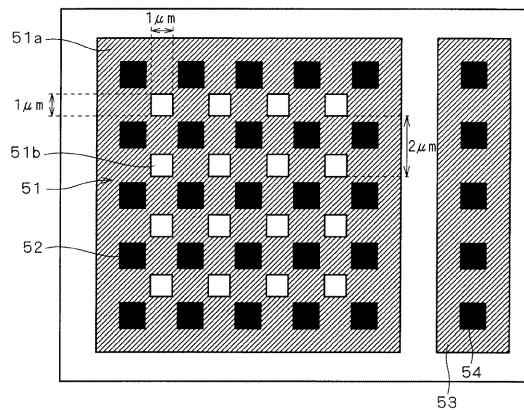

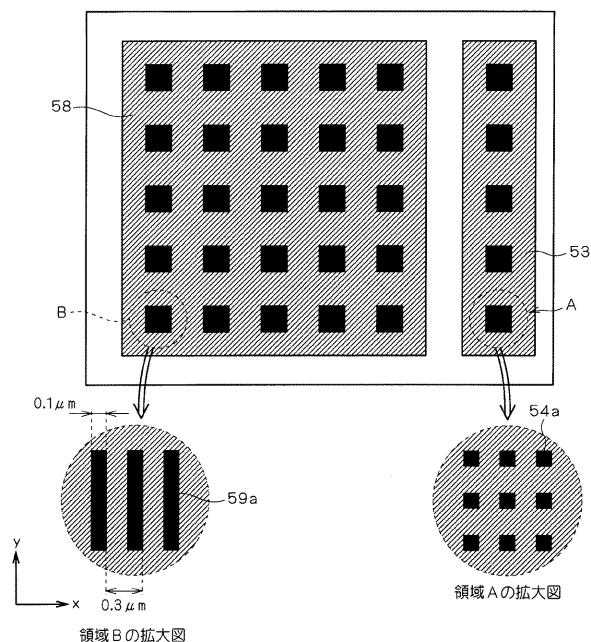

本実施の形態に係わる半導体装置では、上記第一のダミーパターンが、平面視においてメッシュ状であることを、特徴としている。図11に、本実施の形態に係わる第一のダミーパターンの平面図を示す。なお、第一のダミーパターン以外の構成は、実施の形態1と同様であるので、説明は省略する。

## 【0099】

図11に示すように、メッシュ状の第一のダミーパターン51に隣接して、素子として機能する、配線パターン53と当該配線パターン53と電気的に接続されているビアパターン54が形成されている。

## 【0100】

第一のダミーパターン51に注目すると、当該第一のダミーパターン51は、ダミーパターン領域51aと、メッシュの目領域51bとから構成されている。ここで、メッシュの目領域51bの目幅角は、たとえば1μm程度であり、メッシュの目領域51bの形成ピッチは、たとえば2μm程度である。

## 【0101】

10

20

30

40

50

なお、第一のダミーパターン 5 1 と接続している、第二のダミーパターン 5 2 の構成は、実施の形態 1 と同様であるので、ここでの説明は省略する。

#### 【0102】

以上のように、本実施の形態では、第一のダミーパターン 5 1 は、メッシュ状である。したがって、平面視における第一のダミーパターン 5 1 の面積を大きく設計し、さらに当該第一のダミーパターン 5 1 に対して C M P 处理を施したとしても、第一のダミーパターン 5 1 のディッキングの発生を防止することができる。

#### 【0103】

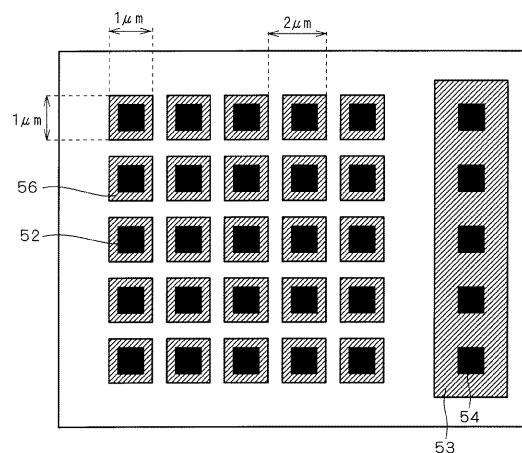

##### <実施の形態 3 >

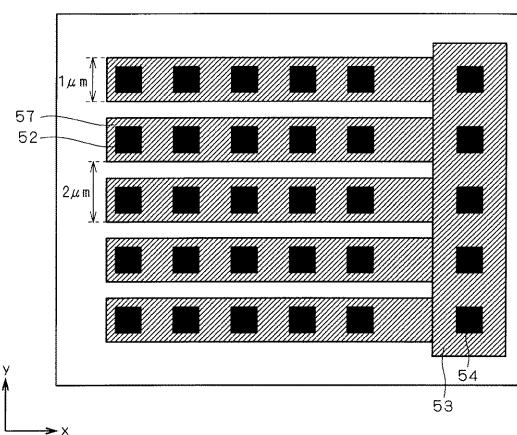

本実施の形態に係わる半導体装置では、実施の形態 1 で説明した第一のダミーパターン 10 が、平面視において島状に点在して形成されていることを、特徴としている。図 1 2 に、本実施の形態に係わる第一のダミーパターンの平面図を示す。なお、第一のダミーパターン以外の構成は、実施の形態 1 と同様であるので、説明は省略する。

#### 【0104】

図 1 2 に示すように、複数の第一のダミーパターン 5 6 が形成されている領域に隣接して、素子として機能する、配線パターン 5 3 と当該配線パターン 5 3 と電気的に接続されているピアパターン 5 4 が形成されている。

#### 【0105】

第一のダミーパターン 5 6 に注目すると、当該第一のダミーパターン 5 6 は、島状に点在して、複数形成されている。図 1 2 では、島状の第一のダミーパターン 5 6 は、 $5 \times 5$  のマトリクス状に、点在して形成されている。ここで、第一のダミーパターン 5 6 は、たとえば  $1 \mu m$  幅角程度であり、当該第一のダミーパターン 5 6 の形成ピッチは、たとえば  $2 \mu m$  程度である。

#### 【0106】

なお、各第一のダミーパターン 5 6 は、実施の形態 2 で説明した第二のダミーパターン群と、各々接続されている。第二のダミーパターン 5 2 の構成は、実施の形態 1 と同様であるので、ここでの説明は省略する。

#### 【0107】

以上のように、本実施の形態では、第一のダミーパターン 5 6 は、島状に点在して形成されている。したがって、平面視における、複数の第一のダミーパターン 5 6 の形成する範囲の面積を大きく設計し、さらに当該範囲内に形成された複数の第一のダミーパターン 5 6 に対して C M P 处理を施したとしても、第一のダミーパターン 5 6 においてディッキングが発生することは無い。

#### 【0108】

つまり、実施の形態 1 で説明した第一のダミーパターン 4 等では、その面積を大きくした場合には、当該第一のダミーパターン 4 等に対して C M P 处理を施すと、ディッキングの発生が起こり得る。

#### 【0109】

しかし、上記第一のダミーパターン 4 等が形成されていた、面積の範囲内において、本実施の形態に係わる第一のダミーパターン 5 6 を、島状に点在して複数形成することにより、上記ディッキングの発生を防止することができる。

#### 【0110】

##### <実施の形態 4 >

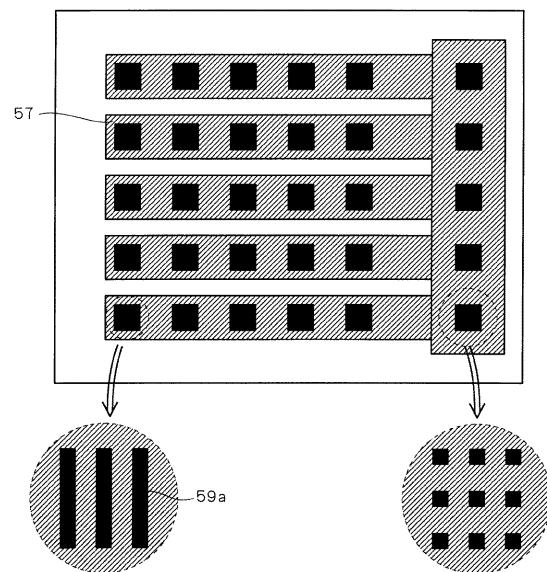

本実施の形態に係わる半導体装置では、上記第一のダミーパターンが、平面視において、所定の方向に沿って、ストライプ状に複数形成されていることを、特徴としている。図 1 3 に、本実施の形態に係わる第一のダミーパターンの平面図を示す。なお、第一のダミーパターン以外の構成は、実施の形態 1 と同様であるので、説明は省略する。

#### 【0111】

図 1 3 に示すように、ストライプ状に形成された第一のダミーパターン 5 7 に隣接して、素子として機能する、配線パターン 5 3 と当該配線パターン 5 3 と電気的に接続されて

10

20

30

40

50

いるビアパターン 5 4 が形成されている。

【0112】

第一のダミーパターン 5 7 に注目すると、当該第一のダミーパターン 5 7 は、平面視において、所定の方向（本実施の形態では、図 13 における x 方向）に沿って、ストライプ状に複数形成されている。ここで、第一のダミーパターン 5 7 の、当該ストライプ方向に垂直な方向（図 13 における y 方向）の幅は、たとえば 1  $\mu\text{m}$  程度である。また、第一のダミーパターン 5 7 の形成ピッチは、たとえば 2  $\mu\text{m}$  程度である。

【0113】

なお、各第一のダミーパターン 5 7 は、実施の形態 2 で説明した、複数の第二のダミーパターン群と接続している。第二のダミーパターンの構成は、実施の形態 1 と同様であるので、ここでの説明は省略する。

【0114】

以上のように、本実施の形態では、第一のダミーパターン 5 7 は、ストライプ状に形成されている。したがって、実施の形態 2, 3 と同様に、第一のダミーパターン 5 7 に対して CMP 処理を施したとしても、第一のダミーパターン 5 7 のディッシングの発生を防止することができる。

【0115】

< 実施の形態 5 >

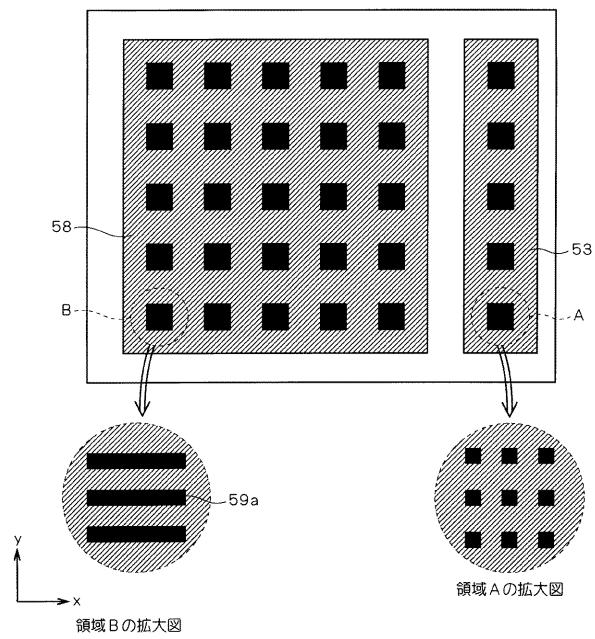

本実施の形態に係わる半導体装置では、上記第二のダミーパターンが、平面視において、第一の方向に沿って、ストライプ状に形成されていることを、特徴としている。図 14 に、本実施の形態に係わる第二のダミーパターンの平面図等を示す。

【0116】

図 14 において、素子として機能する配線パターン 5 3 と電気的に接続する、ビアパターン 5 4 a は、実施の形態 1 で説明したように、所定の寸法および所定の形成ピッチで、複数点在して形成されている（点線円の領域 A の拡大図参照）。

【0117】

しかし、図 14 において、第一のダミーパターン 5 8 と接続する、第二のダミーパターン 5 9 a は、図 14 の点線円の領域 B の拡大図に示すように、平面視において、第一の方向（図 14 では、y 方向）沿って、ストライプ状に形成されている。

【0118】

ここで、第二のダミーパターン 5 9 a のストライプ幅（つまり、第二のダミーパターン 5 9 a の x 方向の幅）は、たとえば 0.1  $\mu\text{m}$  程度であり、第二のダミーパターン 5 9 a の形成ピッチは、たとえば 0.3  $\mu\text{m}$  程度である。

【0119】

なお、上記以外の構成は、実施の形態 1 と同様であるので、説明は省略する。また、第二のダミーパターン 5 9 a のストライプの方向は、図 14 の方向（図面 y 方向）に限る必要は無い。たとえば、図 15 の点線円の領域 B の拡大図に示すように、第二のダミーパターン 5 9 a のストライプの方向は、図面の x 方向であっても良い。

【0120】

つまり、第二のダミーパターン 5 9 a のストライプ方向は、任意に設定することができる。

【0121】

第二のダミーパターン 5 9 a は上記のように構成されているので、実施の形態 1 に記載した効果に加えて、以下の効果をも奏する。

【0122】

本実施の形態では、第二のダミーパターン 5 9 a は、ストライプ状に形成されている。また、実施の形態 1 で説明したように、第二のダミーパターン 5 9 a は、導電体である。また、第二のダミーパターン 5 9 a は、低誘電率膜の第一の主面の表面内に形成されている。

【0123】

10

20

30

40

50

したがって、当該第二のダミーパターン 59a が無い場合比べて、本実施の形態に係わる半導体装置の方が、低誘電率膜と当該低誘電率膜と接する他の絶縁膜との密着性を、向上させることができる。

#### 【0124】

ところで、パッド部 47 に対するプローピングの際の当該プローピングの方向が、上から下に向かう垂直方向（つまり、図 3 における層間絶縁膜の堆積方向であり、z 軸の方向と把握できる）成分に加えて、当該垂直方向に垂直な水平方向成分（つまり、図 14 等の x 方向または y 方向等と把握できる）を有しているとする。ここで、第二のダミーパターン 59a のストライプの方向を、前記水平方向成分と略平行に配置したとする。

#### 【0125】

もし、第二のダミーパターン 59a のストライプの向きを、上記のように配置させたなら、たとえ上記当接方向からのプローピングを行ったとしても（つまり、水平方向成分を含むプローピング動作を行ったとしても）、当該プローピングの際に加わる力によって、低誘電率膜の上下面における膜剥がれ等を防止することができる。

#### 【0126】

なお、実施の形態 1 で説明したように、層間絶縁膜（低誘電率膜も含む）内には、第二のダミーパターン 59a の他に、素子として機能する複数のビアパターン（図 14 の 54a 等）も形成されている。

#### 【0127】

当該構造の半導体装置の製造方法において、ビアパターンと第二のダミーパターン 59a とを同時に形成する工程に注目すると、上記第二のダミーパターン 59a のストライプ幅（たとえば、図 14 に示す第二のダミーパターン 59a の x 方向の幅）は、以下の範囲であることが望ましい。

#### 【0128】

つまり、ビアパターンと第二のダミーパターンとの同時製造の観点から、上記第二のダミーパターン 59a のストライプ幅は、上記複数のビアパターンの内、最小径を有するビアパターンの当該最小径寸法の、1 倍以上、10 倍以下であることが、望ましい。

#### 【0129】

また、図 14, 15 で示した点線円の領域 B の拡大図において、ストライプ形状の第二のダミーパターン 59a の占有率は、任意に設定できる。たとえば、ライン（ストライプ）幅とスペース幅とが同程度の場合には、第二のダミーパターン 59a の上記領域 B の占有率は、1 ~ 50 % の範囲で任意に設定可能である。なお、いずれの占有率を選択したとしても、本実施の形態で説明した効果を有することは、言うまでも無い。

#### 【0130】

##### < 実施の形態 6 >

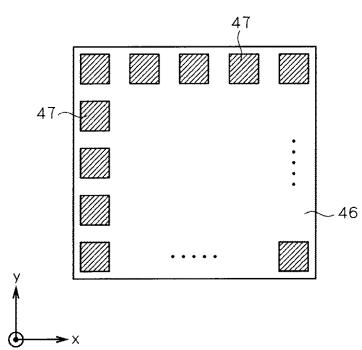

実施の形態 5 において、プローピング動作の水平方向と、第二のダミーパターンのストライプ方向とを、略平行にする場合について言及した。本実施の形態では、当該ケースの応用例について説明する。

#### 【0131】

最上層の層間絶縁膜 46 上の外周部において、パッド部 47 は、下記のように配置されることがある。つまり、平面図である図 16 に示すように、パッド部 47 は、層間絶縁膜 46 上に、第二の方向に沿って、複数配設されることがある。ここで、第二の方向とは、図 16 の x 方向または y 方向と把握できる。

#### 【0132】

このように、配置されたパッド部 47 に対して、プローピングを行う場合には、当該プローピングの方向は、一般的に、以下の方向にて行われる。

#### 【0133】

たとえば、図面の x 方向に沿って配設されているパッド部 47 に対しては、プローピングの方向には、図面の表裏方向（図面の z 方向）成分に加えて、図面の y 方向成分を有する。これに対して、図面の y 方向に沿って配設されているパッド部 47 に対しては、プロ

ーピングの方向には、図面の表裏方向（図面の z 方向）成分に加えて、図面の x 方向成分を有する。

**【 0 1 3 4 】**

つまり、パッド部 4 7 の配列方向（第二の方向）と、プローピングの水平方向成分とは、一般的に、垂直である。

**【 0 1 3 5 】**

以上のことから、第二のダミーパターン（図 1 4 , 1 5 の符号 5 9 a ）の第一の方向（ストライプ方向）を、上記第二の方向と、略垂直となるように、当該第二のダミーパターン 5 9 a を形成する。

**【 0 1 3 6 】**

このように、パッド部 4 7 の配設方向に依存して、第二のダミーパターン 5 9 a のストライプ方向を規定することにより、実施の形態 5 で説明した効果を奏すことができる。つまり、たとえ上記当接方向からのプローピングを行ったとしても（つまり、水平方向成分を含むプローピング動作を行ったとしても）、当該プローピングの際に加わる力によって、低誘電率膜の上下面における膜剥がれ等を防止することができる。

**【 0 1 3 7 】**

なお、実施の形態 2 ~ 5 において、第一のダミーパターンおよび第二のダミーパターンの具体的な構成について言及してきた。

**【 0 1 3 8 】**

ここで、実施の形態 2 ないし 4 のいずれかにおいて説明した第一のダミーパターンの構成と、実施の形態 5 において説明した第二のダミーパターンの構成とを、組み合わせても良いことは、言うまでも無い。

**【 0 1 3 9 】**

たとえば、図 1 7 に示すように、実施の形態 4 に係わる第一のダミーパターン 5 7 と、実施の形態 5 に係わる第二のダミーパターン 5 9 a とを、組み合わせた構成を採用しても良い。

**【 0 1 4 0 】**

なお、以上までの構成の半導体装置は、たとえば、誘電率  $k$  が 2 . 7 未満である低誘電率膜を有する、CMOS ( C o m p l e m e n t a r y M e t a l O x i d e S e m i c o n d u c t o r ) 、 SOI ( S i l i c o n O n I n s u l a t i n g s u b s t r a t e ) 構造、および e R A M ( e m b e d d e d R a n d o m A c c e s s M e m o r y ) 等に、適用することができる。

**【 図面の簡単な説明 】**

**【 0 1 4 1 】**

【図 1】測定対象となった半導体装置の一部を示す断面図である。

【図 2】測定結果示す図である。

【図 3】実施の形態 1 に係わる半導体装置の構成を示す断面図である。

【図 4】実施の形態 1 に係わる半導体装置の構成を示す透視平面図である。

【図 5】ピアパターンおよび第二のダミーパターンの構成を示す拡大平面図である。

【図 6】実施の形態 1 に係わる半導体装置の製造方法を説明するための工程断面図である。

【図 7】実施の形態 1 に係わる半導体装置の製造方法を説明するための工程断面図である。

【図 8】実施の形態 1 に係わる半導体装置の製造方法を説明するための工程断面図である。

【図 9】実施の形態 1 に係わる半導体装置の製造方法を説明するための工程断面図である。

【図 1 0】実施の形態 1 に係わる半導体装置の製造方法を説明するための工程断面図である。

【図 1 1】実施の形態 2 に係わる第一のダミーパターンの構成を示す平面図である。

10

20

30

40

50

【図12】実施の形態3に係わる第一のダミーパターンの構成を示す平面図である。

【図13】実施の形態4に係わる第一のダミーパターンの構成を示す平面図である。

【図14】実施の形態5に係わる第二のダミーパターンの構成を示す平面図である。

【図15】実施の形態5に係わる第二のダミーパターンの他の構成を示す平面図である。

【図16】層間絶縁膜の外周部に配設された、パッド部の様子を示す平面図である。

【図17】所定の第一のダミーパターンと、所定の第二のダミーパターンとの組み合わせの一例を示す図である。

#### 【符号の説明】

##### 【0142】

1 半導体基板、2 分離酸化膜、3 コンタクト層間膜、4 , 8 , 14 , 20 , 26 10

, 32 低誘電率膜、5 , 9 , 15 , 21 , 27 , 33 , 39 , 43 , 53 配線パターン、6 , 10 , 16 , 22 , 28 , 34 , 51 , 56 , 57 , 58 第一のダミーパターン、7 , 13 , 19 , 25 , 31 , 37 , 41 , 45 ライナー膜、11 , 17 , 23 ,

29 , 35 , 40 , 44 , 54 , 54a ビアパターン、12 , 18 , 24 , 30 , 36 , 52 , 59a 第二のダミーパターン、38 , 42 , 46 層間絶縁膜、47 パッド部、48 パッシベーション膜。

【図1】

【図2】

| Low-k 層間膜種 | A   | B   | C   | D   |

|------------|-----|-----|-----|-----|

| 誘電率: k     | 3.0 | 2.8 | 2.6 | 2.5 |

| クラック       | OK  | OK  | NG  | NG  |

【図3】

〔 四 6 〕

【 図 7 】

【 図 8 】

【 図 4 】

【 5 】

〔 9 〕

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

## フロントページの続き

F ターム(参考) 5F033 HH09 HH11 HH18 HH21 HH32 HH33 JJ11 KK11 KK21 KK32

MM01 MM02 MM13 MM21 MM22 PP15 PP27 PP28 QQ25 QQ48

RR01 RR06 RR21 RR25 RR29 SS04 TT01 VV01 VV07 XX12

XX17 XX28 XX34