# CORRECTED VERSION

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 4 September 2014 (04.09.2014)

(10) International Publication Number WO 2014/133974 A9

(51) International Patent Classification: H01L 27/14 (2006.01) H01L 31/00 (2006.01)

(21) International Application Number:

PCT/US2014/018084

(22) International Filing Date:

24 February 2014 (24.02.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/768,523 24 February 2013 (24.02.2013)

US

- (71) Applicant: PELICAN IMAGING CORPORATION [US/US]; 451 El Camino Real, Suite 100, Santa Clara, CA 95050 (US).

- (72) Inventors: VENKATARAMAN, Kartik; 1736 Indigo Oak Avenue, San Jose, CA 95121 (US). GALLAGHER, Paul; 15110 Herring Avenue, San Jose, CA 95124 (US). LELESCU, Dan; 18325 Serra Avenida, Morgan Hill, CA 95037 (US). MCMAHON, Andrew; 628 Alameda de las Pulgas, San Carlos, CA 94070 (US). DUPARRE, Jacques; Buchaer Str. 12C, 07745 Jena (DE). BEDABRATA, Pain; 828 N. Crescent Heights Blvd., Los Angeles, CA 90046 (US).

- (74) Agent: WADHWANI, Rishi, H.; KPPB LLP, 2400 E. Katella, Suite 1050, Anaheim, CA 92806 (US).

- 1) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

- with international search report (Art. 21(3))

- (48) Date of publication of this corrected version:

9 April 2015

(15) Information about Correction: see Notice of 9 April 2015

#### (54) Title: THIN FORM COMPUTATIONAL AND MODULAR ARRAY CAMERAS

FIG. 3

(57) Abstract: Systems and methods in accordance with embodiments of the invention implement one-dimensional array cameras, as well as modular array cameras using sub-array modules. In one embodiment, a 1xN array camera module includes: a 1xN arrangement of focal planes, where N is greater than or equal to 2, each focal plane includes a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane not including pixels from another focal plane; and a 1 xN arrangement of lens stacks, the arrangement of lens stacks being disposed relative to the arrangement of focal planes so as to form a 1xN arrangement of cameras, each configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to that of each other lens stack so that each shift includes a sub-pixel shifted view of the scene.

### THIN FORM COMPUTATIONAL AND MODULAR ARRAY CAMERAS

# FIELD OF THE INVENTION

**[0001]** The present invention generally relates to one-dimensional array cameras and also relates to the construction of modular array cameras using one-dimensional sub-array modules.

# **BACKGROUND**

**[0002]** In response to the constraints placed upon a traditional digital camera based upon the camera *obscura*, a new class of cameras that can be referred to as array cameras has been proposed. Array cameras are characterized in that they include an imager array that has multiple arrays of pixels, where each pixel array is intended to define a focal plane, and each focal plane has a separate lens stack. Typically, each focal plane includes a plurality of rows of pixels that also forms a plurality of columns of pixels, and each focal plane is contained within a region of the imager that does not contain pixels from another focal plane. An image is typically formed on each focal plane by its respective lens stack. In many instances, the array camera is constructed using an imager array that incorporates multiple focal planes and an optic array of lens stacks.

# SUMMARY OF THE INVENTION

**[0003]** Systems and methods in accordance with embodiments of the invention implement one-dimensional array cameras, as well as modular array cameras using sub-array modules. In one embodiment, a 1xN array camera module includes: a 1xN arrangement of focal planes, where N is greater than or equal to 2, each focal plane includes a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and a 1xN arrangement of lens stacks, the 1xN arrangement of lens stacks being disposed relative to the 1xN arrangement of focal planes so as to form a 1xN arrangement of cameras, each of which being configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene.

[0004] In another embodiment, N is greater than or equal to 3.

[0005] In yet another embodiment, N is 5.

**[0006]** In still another embodiment, the 1xN arrangement of cameras includes a green camera that is configured to image light corresponding with the green band of the visible spectrum.

[0007] In still yet another embodiment, the green camera is centrally disposed relative to the 1xN arrangement of cameras.

**[0008]** In a further embodiment, the lens stack of the green camera is adapted to image light corresponding with the green band of the visible spectrum.

**[0009]** In a still further embodiment, a red camera that is configured to image light corresponding with the red band of the visible spectrum and a blue camera that is configured to image light corresponding with the blue band of the visible spectrum are each disposed on either side of the centrally disposed green camera.

[0010] In a yet further embodiment, N is 7.

**[0011]** In a still yet further embodiment, the 1xN arrangement of cameras includes a green camera that is configured to image light corresponding with the green band of the visible spectrum, and that is centrally disposed relative to the 1xN arrangement of cameras.

**[0012]** In another embodiment, a red camera that is configured to image light corresponding with the red band of the visible spectrum and a blue camera that is configured to image light corresponding with the blue band of the visible spectrum are each disposed on either side of the centrally disposed green camera.

[0013] In yet another embodiment, N is 9.

**[0014]** In still another embodiment, the 1xN arrangement of cameras includes a green camera that is configured to image light corresponding with the green band of the visible spectrum, and that is centrally disposed relative to the 1xN arrangement of cameras.

**[0015]** In still yet another embodiment, a red camera that is configured to image light corresponding with the red band of the visible spectrum and a blue camera that is configured to image light corresponding with the blue band of the visible spectrum are each disposed on either side of the centrally disposed green camera.

**[0016]** In a further embodiment, the 1xN arrangement of focal planes is embodied within a monolithic structure.

[0017] In a still further embodiment, the 1xN arrangement of lens stacks is embodied within a monolithic structure.

[0018] In a yet further embodiment, the 1xN arrangement of focal planes and the 1xN arrangement of lens stacks are each embodied within the same monolithic structure.

**[0019]** In a still yet further embodiment, at least one camera is embodied within a single sub-array module, the sub-array module including: a 1xX arrangement of focal planes, where X is greater than or equal to 1, each focal plane comprises a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and a 1xX arrangement of lens stacks, the 1xX arrangement of lens stacks being disposed relative to the 1xX arrangement of focal planes so as to form a 1xX arrangement of cameras, each of which being configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene.

**[0020]** In another embodiment, the sub-array module further includes interface circuitry that can allow the sub-array module to interface with another sub-array module so that it can at least transmit image data to another sub-array module or receive image data from another sub-array module.

**[0021]** In yet another embodiment, the 1xX arrangement of cameras is embodied within a single monolithic structure.

[0022] In still another embodiment N is 9 and X is 3.

[0023] In still yet another embodiment, the 1x9 arrangement of cameras are embodied within three 1x3 sub-array modules, each 1x3 sub-array module including: a 1x3 arrangement of focal planes, where each focal plane comprises a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and a 1x3 arrangement of lens stacks, the 1x3 arrangement of lens stacks being disposed relative to the 1x3 arrangement of focal planes so as to form a 1x3 arrangement of cameras, each of which being configured to

independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene.

**[0024]** In a further embodiment, each sub-array module further includes interface circuitry that can allow the sub-array module to interface with another sub-array module so that it can at least transmit image data to another sub-array module or receive image data from another sub-array module.

[0025] In a still further embodiment, an array camera module further includes at least two sub-array modules, where each sub-array module includes: a 1xX arrangement of focal planes, where X is greater than or equal to 1, each focal plane comprises a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and a 1xX arrangement of lens stacks, the 1xX arrangement of lens stacks being disposed relative to the 1xX arrangement of focal planes so as to form a 1xX arrangement of cameras, each of which being configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene; where each of the at least two sub-array modules are adjoined to the interconnects of a single substrate, and can thereby interface with at least one other sub-array module.

**[0026]** In a yet further embodiment, each of the at least two sub-array modules further includes interface circuitry that can allow the respective sub-array module to interface with another sub-array module so that it can at least transmit image data to another sub-array module or receive image data from another sub-array module.

[0027] In a still yet further embodiment, the substrate is optically transparent.

[0028] In another embodiment, the substrate is glass.

[0029] In yet another embodiment, the substrate is ceramic.

**[0030]** In a further embodiment, a 1xX sub-array module includes: a 1xX arrangement of focal planes, where X is greater than or equal to 1, each focal plane comprises a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and a 1xX arrangement of lens stacks, the 1xX arrangement of lens stacks being disposed relative

to the 1xX arrangement of focal planes so as to form a 1xX arrangement of cameras, each of which being configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene.

**[0031]** In a yet further embodiment, the 1xX sub-array module further includes interface circuitry that can allow the sub-array module to interface with another sub-array module so that it can at least transmit image data to another sub-array module or receive image data from another sub-array module.

[0032] In a still further embodiment, the interface circuitry implements a MIPI CSI 2 interface.

[0033] In another embodiment, a 1xN array camera includes: a 1xN arrangement of focal planes, where N is greater than or equal to 2, each focal plane comprises a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and a 1xN arrangement of lens stacks, the 1xN arrangement of lens stacks being disposed relative to the 1xN arrangement of focal planes so as to form a 1xN arrangement of cameras, each of which being configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene; and a processor that is configured to construct an image of the scene using image data generated by the 1xN array camera module.

[0034] In a further embodiment, an XxY sub-array module includes: an XxY arrangement of focal planes, where X and Y are each greater than or equal to 1, each focal plane includes a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and an XxY arrangement of lens stacks, the XxY arrangement of lens stacks being disposed relative to the XxY arrangement of focal planes so as to form an XxY arrangement of cameras, each of which being configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene; and image data output circuitry that is configured to output image data from the XxY

sub-array module that can be aggregated with image data from other sub-array modules so that an image of the scene can be constructed.

[0035] In a yet further embodiment, X is 1.

[0036] In a still further embodiment, X and Y are each greater than 1.

[0037] In a still yet further embodiment, the arrangement of cameras are embodied within a single monolithic structure

[0038] In another embodiment, an MxN array camera includes: a plurality of XxY sub-array modules, each including: an XxY arrangement of focal planes, where X and Y are each greater than or equal to 1, each focal plane includes a plurality of rows of pixels that also form a plurality of columns of pixels, and each focal plane does not include pixels from another focal plane; and an XxY arrangement of lens stacks, the XxY arrangement of lens stacks being disposed relative to the XxY arrangement of focal planes so as to form an XxY arrangement of cameras, each of which being configured to independently capture an image of a scene, where each lens stack has a field of view that is shifted with respect to the field-of-views of each other lens stack so that each shift includes a sub-pixel shifted view of the scene; and image data output circuitry that is configured to output image data from the sub-array module that can be aggregated with image data from other sub-array modules so that an image of the scene can be constructed; where the plurality of XxY sub-array modules define at least some of the cameras in an MxN arrangement of cameras; and a processor; where the processor is configured to construct an image of the scene using image data generated by each of the sub-array modules.

[0039] In yet another embodiment, X is 1 and M is 1.

[0040] In still another embodiment, the plurality of XxY sub-array modules define an MxN arrangement of cameras.

**[0041]** In still yet another embodiment, an MxN array camera further includes circuitry that aggregates the image data generated by each of the sub-array modules into a single MIPI output, and provides the MIPI output to the processor so that the processor can construct an image of the scene.

[0042] In a further embodiment, an MxN array camera further includes a parallax disparity resolution module, where the parallax disparity resolution module is configured

to receive image data captured by each sub-array module, implement a parallax detection and correction process on the received image data, and output the result for further processing.

**[0043]** In a still further embodiment, an MxN array camera further includes circuitry that converts the output of the parallax disparity resolution module into a single MIPI output, and provides the MIPI output to the processor so that the processor can construct an image of the scene.

**[0044]** In a still yet further embodiment, the parallax disparity resolution module includes a processor and memory, where the memory contains software to configure the processor to act as a parallax disparity resolution module.

**[0045]** In another embodiment, the parallax disparity resolution module is a hardware parallax disparity resolution module.

[0046] In still another embodiment, M and N are each greater than or equal to 2.

**[0047]** In yet another embodiment, at least two of the plurality of sub-array modules are adjoined to the interconnects of a single substrate, and can thereby output image data through the interconnects.

**[0048]** In still yet another embodiment, each of the plurality of sub-array modules are adjoined to the interconnects of a single substrate, and can thereby output image data through the interconnects.

[0049] In a further embodiment, the substrate is optically transparent.

[0050] In a still further embodiment, the substrate is glass.

[0051] In a still yet further embodiment, the substrate is ceramic.

[0052] In another embodiment, at least one sub-array module is embodied within a single monolithic structure.

[0053] In yet another embodiment, each sub-array module is embodied within a single respective monolithic structure.

[0054] In still another embodiment, an array camera further includes: a plurality of I/O devices, where each of the plurality of I/O devices interfaces with at least one camera: and a separate I/O block that includes circuitry configured to receive image data, aggregate the received image data, and output the aggregated image data to the

processor so that the processor can construct an image of the scene; and where each of the plurality of I/O devices interfaces with the I/O block.

[0055] In still yet another embodiment, the number of I/O devices equals the number of sub-array modules, and each I/O device interfaces with a corresponding sub-array module.

#### BRIEF DESCRIPTION OF THE DRAWINGS

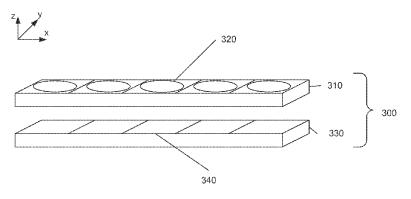

[0056] FIG. 1 conceptually illustrates an array camera architecture in accordance with an embodiment of the invention.

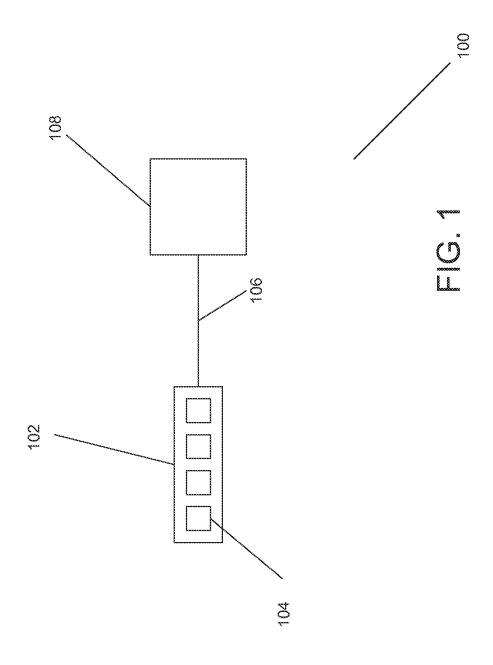

**[0057]** FIG. 2 conceptually illustrates an imager array architecture in accordance with an embodiment of the invention.

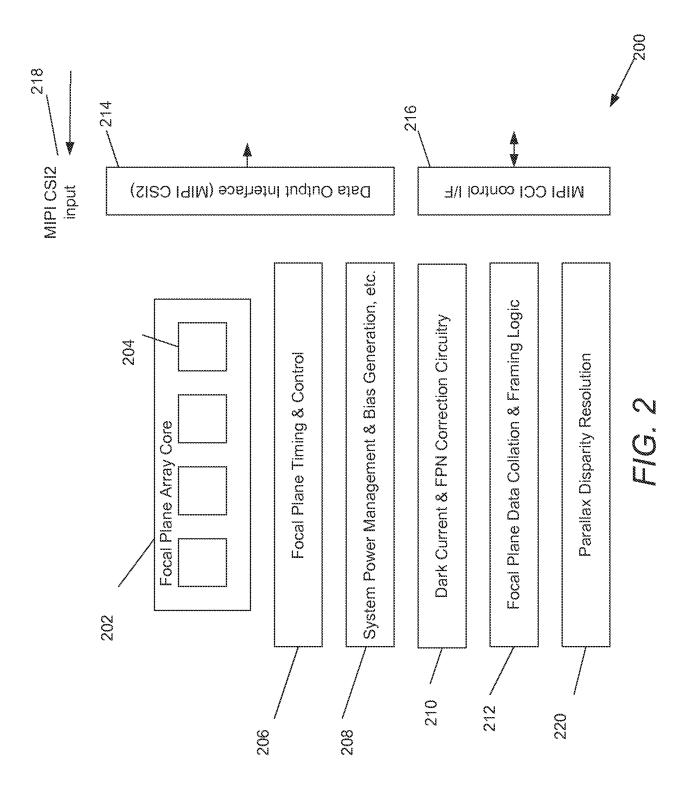

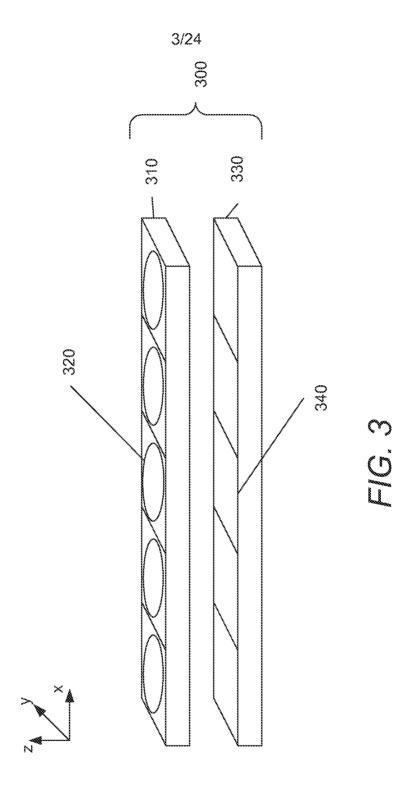

[0058] FIG. 3 conceptually illustrates the construction of an array camera module in accordance with an embodiment of the invention.

[0059] FIGS. 4A and 4B illustrate 1x5 array camera modules in accordance with embodiments of the invention.

**[0060]** FIGS. 5A-5C illustrate 1x7 array camera modules in accordance with embodiments of the invention.

[0061] FIGS. 6A-6F illustrate 1x9 array camera modules in accordance with embodiments of the invention.

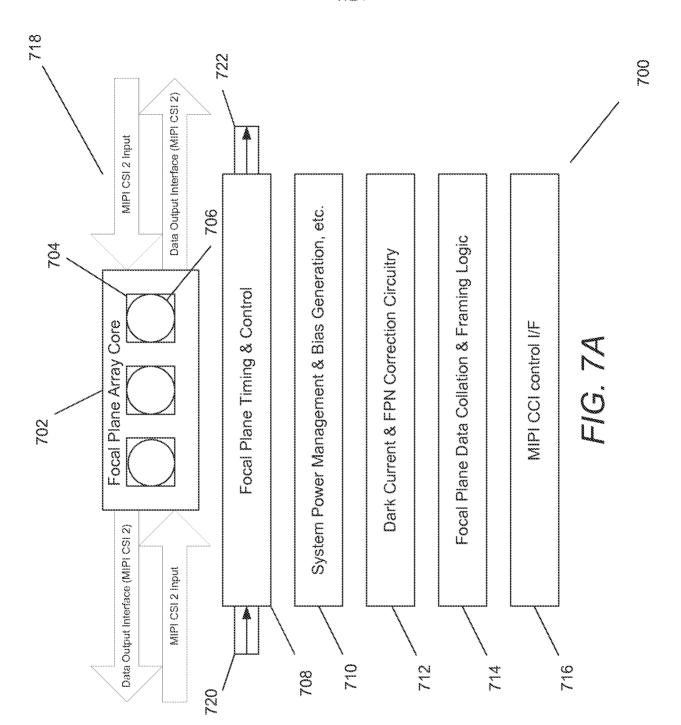

[0062] FIG. 7A illustrates a 1 x 3 sub-array module in accordance with an embodiment of the invention.

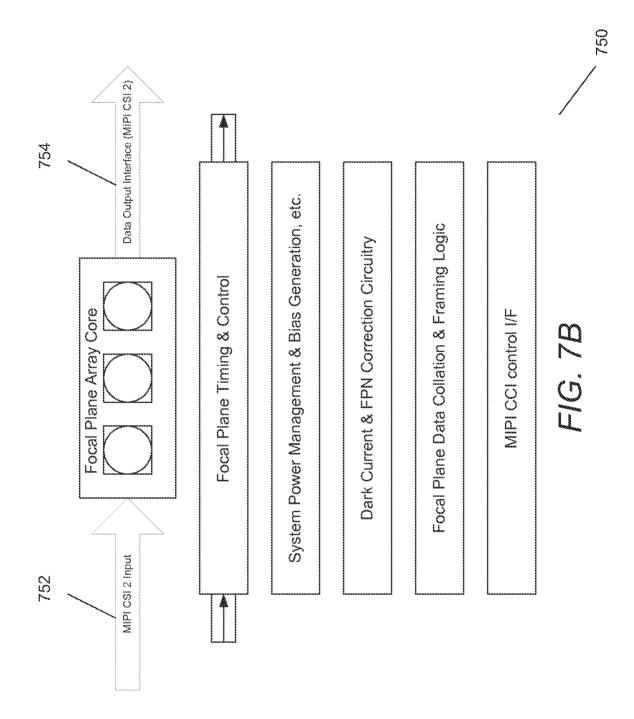

[0063] FIG. 7B illustrates another 1 x 3 sub-array module in accordance with another embodiment of the invention

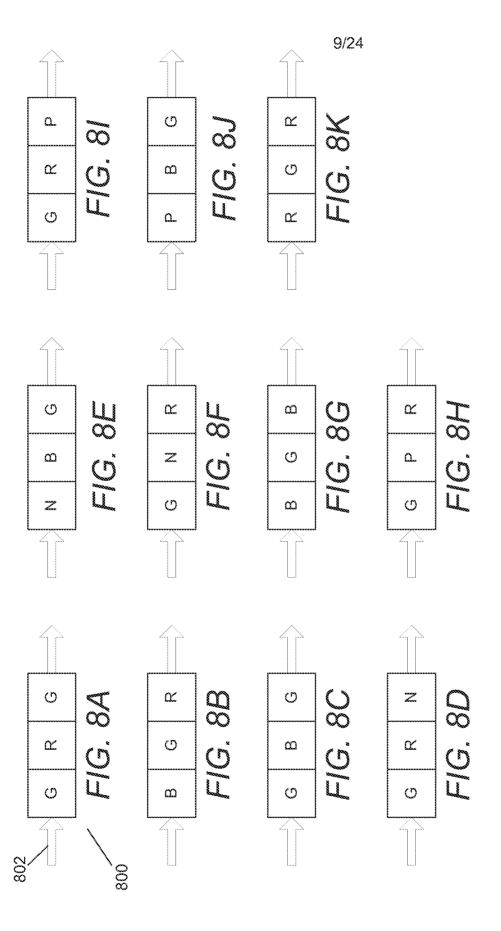

[0064] FIGS. 8A-8K illustrate 1x3 sub-array modules in accordance with embodiments of the invention.

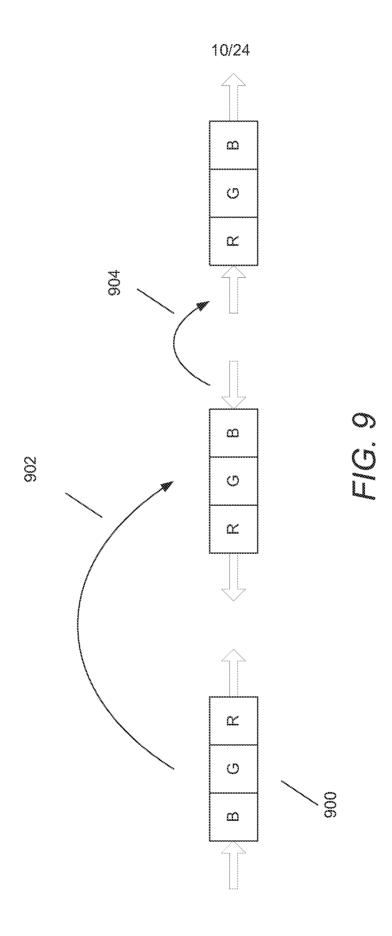

[0065] FIG. 9 illustrates how sub-array modules may be reconfigured in accordance with an embodiment of the invention.

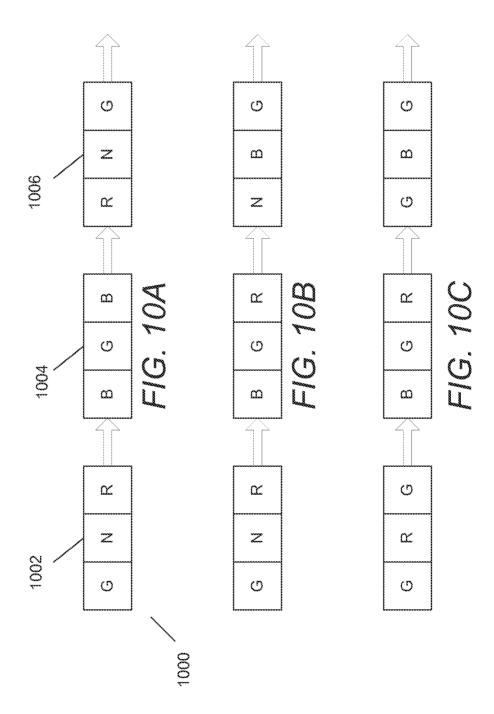

[0066] FIGS. 10A-10C illustrate how 1x3 sub-array modules may be coupled to form array camera modules in accordance with embodiments of the invention.

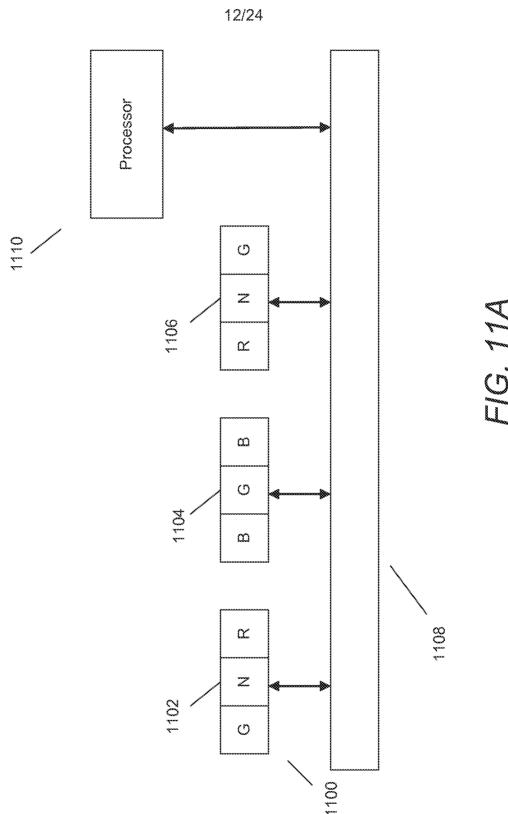

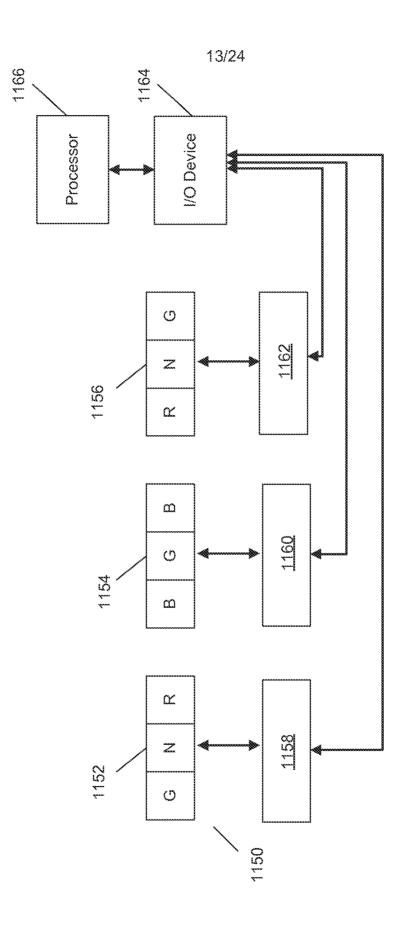

**[0067]** FIGS. 11A-11B illustrates how 1x3 sub-array modules may interface with a receiving device and thereby implement an array camera in accordance with embodiments of the invention

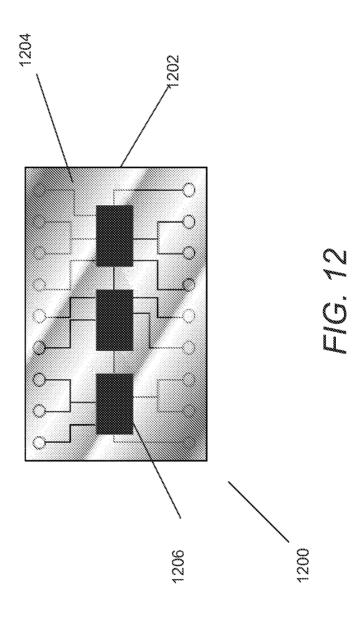

**[0068]** FIG. 12 illustrate how sub-array modules may be coupled via a glass substrate with interconnects to form an array camera module in accordance with embodiments of the invention.

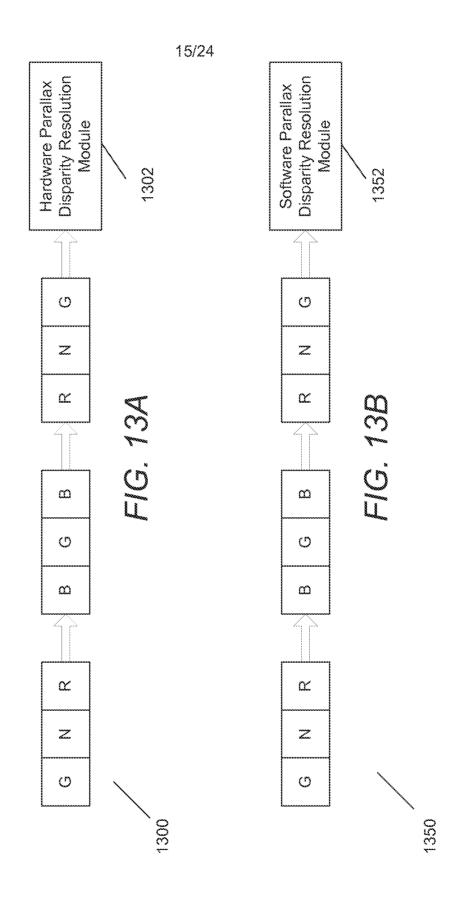

**[0069]** FIGS. 13A-13B illustrate how array camera modules formed from sub-array modules may utilize a parallax disparity resolution module in accordance with embodiments of the invention.

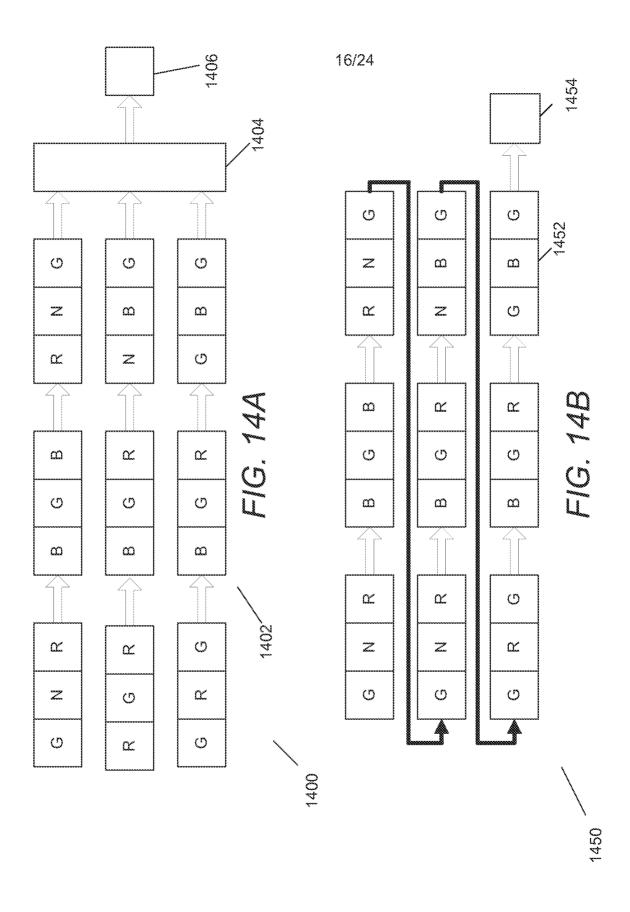

**[0070]** FIGS. 14A-14B illustrate how sub-array modules may be coupled to form an MxN array camera in accordance with embodiments of the invention.

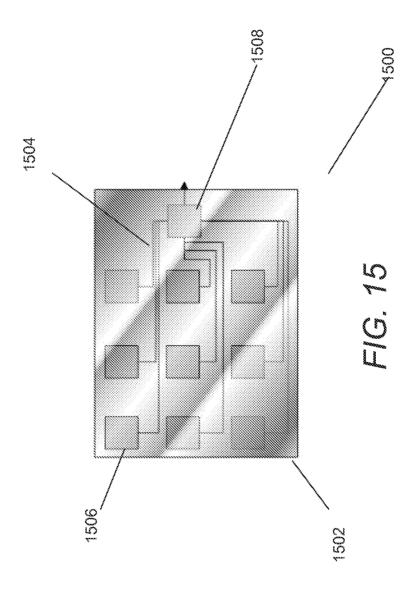

**[0071]** FIG. 15 illustrates how sub-array modules may be coupled via a glass substrate with interconnects to form a two-dimensional array camera in accordance with embodiments of the invention

**[0072]** FIG. 16 illustrates a Pi filter group that may be utilized in accordance with embodiments of the invention.

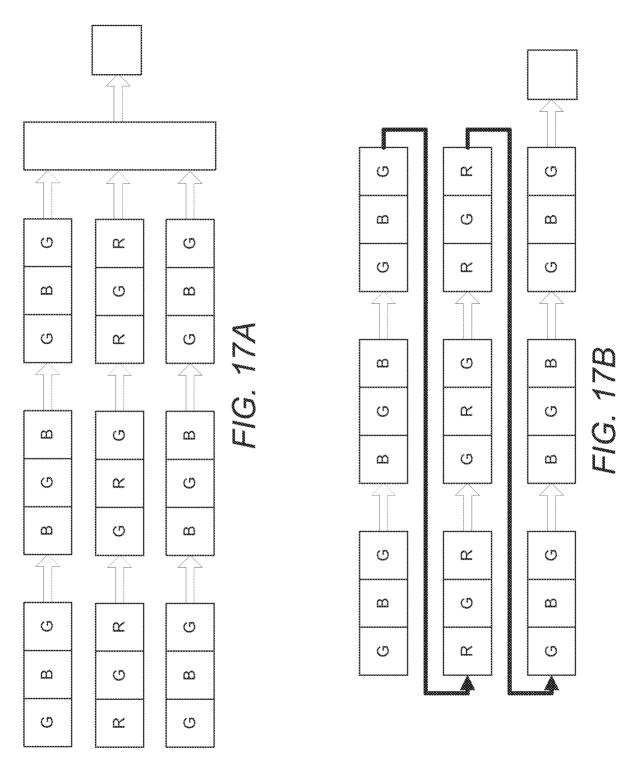

**[0073]** FIGS. 17A-17B illustrates how sub-array modules may be coupled to form an array camera that employs Pi filter groups.

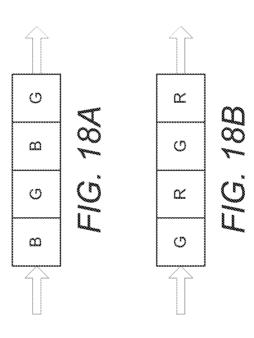

**[0074]** FIGS. 18A-18B illustrate 1x4 sub-array modules in accordance with embodiments of the invention.

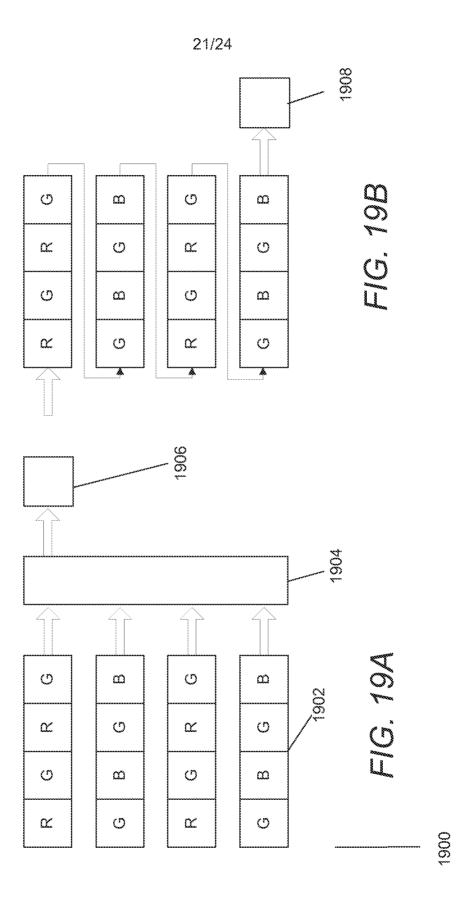

[0075] FIGS. 19A-19B illustrate how 1x4 sub-array modules may be coupled to form an MxN array camera in accordance with embodiments of the invention

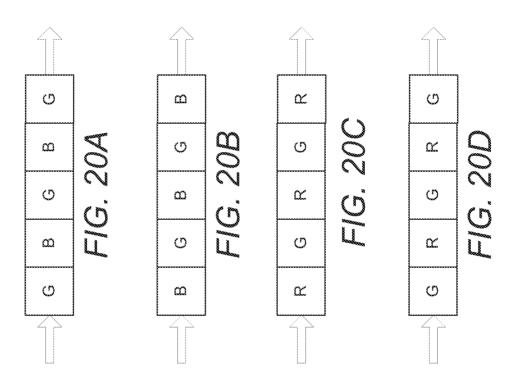

**[0076]** FIGS. 20A-20D illustrate 1x5 sub-array modules in accordance with embodiments of the invention.

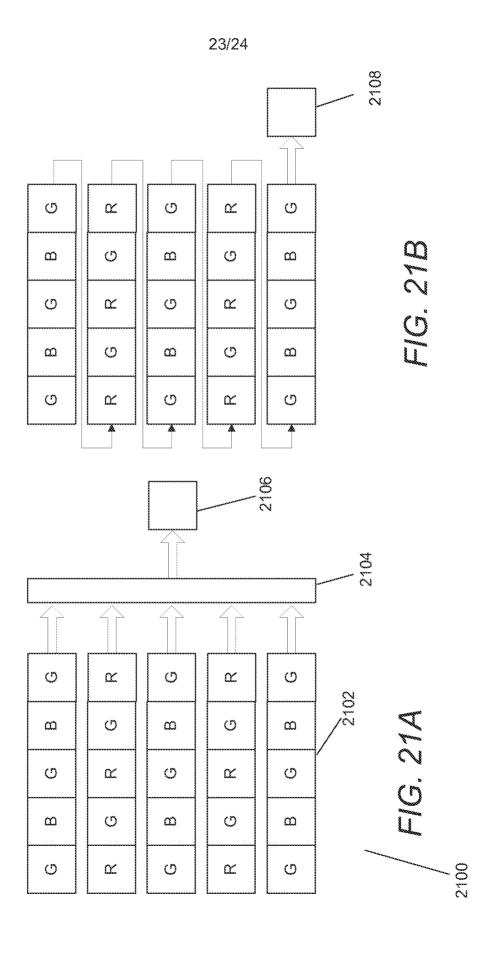

**[0077]** FIGS. 21A-21B illustrate how 1x5 sub-array modules may be coupled to form an MxN array camera in accordance with embodiments of the invention.

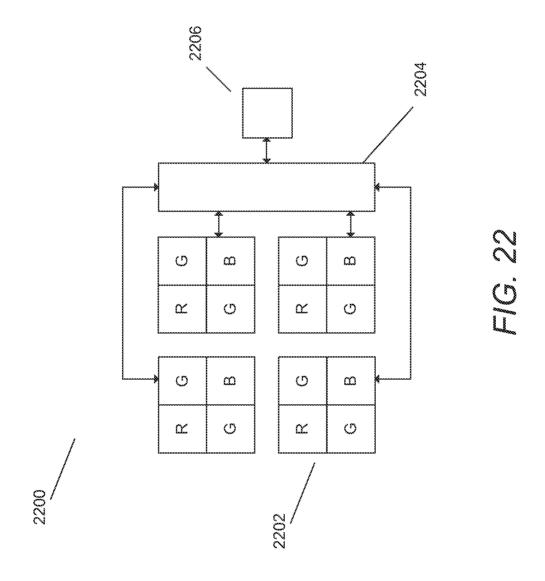

**[0078]** FIG. 22 illustrates a two-dimensional array camera fabricated from multiple two-dimensional sub-array modules.

#### **DETAILED DESCRIPTION**

**[0079]** Turning now to the drawings, systems and methods for implementing one-dimensional array cameras and modular array cameras are disclosed. Processes for constructing array cameras using lens stack arrays are described in U.S. Patent Application Serial No. 12/935,504, entitled "Capturing and Processing of Images Using Monolithic Camera Array with Heterogeneous Imagers", Venkataraman et al., which is incorporated herein by reference in its entirety. The monolithic array camera modules illustrated in U.S. Patent Application Serial No. 12/935,504 can be constructed from an optic array of lens stacks – each lens stack in the array defining an optical channel – and an imager array including a plurality of focal planes corresponding to the optical channels in the optic array. The combination of a lens stack and its corresponding focal plane can be understood to be a 'camera' (as opposed to an 'array camera'). Typically, array cameras capture image data that can be used to form multiple images of a single scene using their constituent cameras, and process the image data to yield a single image of the scene with improved image properties.

**[0080]** U.S. Patent Application Serial No. 12/935,504 discloses many two-dimensional array camera schemes. However, such two-dimensional embodiments may be inapplicable in a number of desirable applications. For example, a consumer electronics device, such as a tablet or smartphone, may benefit from the use of an array camera with a distinctly thin form factor such that it would be able to fit within the device's bezel.

**[0081]** Many embodiments of the invention utilize one-dimensional array camera modules. One-dimensional array camera modules are advantageous insofar as they may accommodate distinct form factor requirements, and are further advantageous in that they may ease processing requirements as compared with two-dimensional array cameras (e.g. they simplify parallax disparity resolution calculations). In many embodiments, 1x5 array camera modules are utilized in the construction of an array camera. In several embodiments, a 1x5 array camera module is utilized that includes a central narrow spectral band green camera (i.e. a camera configured to image light that falls within the 'green' band of the visible spectrum, which can be achieved, for example, where the corresponding lens stack is configured to focus light that falls within

the 'green' band of the visible spectrum onto the corresponding focal plane), and adjacent narrow spectral band blue and red cameras on either side of the central narrow spectral band green camera. In a number of embodiments, 1x7 array camera modules are utilized in the construction of array cameras. In several embodiments, a 1x7 array camera module includes a central narrow spectral band green camera, adjacent narrow spectral band blue and red cameras on either side of the central narrow spectral band green camera, and two periphery narrow spectral band green cameras.

[0082] In many embodiments, 1x9 array camera modules are utilized in the construction of an array camera. A 1x9 array camera module can be preferable to either a 1x7 or a 1x5 array camera module since a 1x9 array camera module can capture more image data. 1x9 array camera modules may include narrow spectral band green, blue, and red cameras, full visual spectrum cameras, and/or near-infrared (near-IR) cameras, which are useful for imaging in low lighting conditions. In many embodiments, a 1x9 array camera module includes more narrow spectral band green cameras than either narrow spectral band blue, narrow spectral band red, or near-IR cameras.

**[0083]** In many embodiments, one-dimensional array camera modules are constructed that do not use narrow spectral band cameras; in many embodiments one-dimensional array camera modules are constructed that employ Bayer filters to facilitate the imaging of a scene.

[0084] Although one-dimensional array cameras may be beneficial in numerous applications, their manufacture can be challenging. Specifically, components for one-dimensional array cameras (e.g. the lenses and the corresponding sensor) are typically manufactured on wafers, but the elongated nature of the components may not be conducive to optimizing wafer space. For example, in the manufacture of a one-dimensional lens array, the periphery of the wafer used in the manufacture may contain significant unused space that, because of the elongated shape of lens array, cannot accommodate further lens arrays. In other words, wafers may be more efficient in the manufacture of components that are more 'square' in shape than 'elongated.'

[0085] In many embodiments of the invention, array cameras are constructed using sub-array modules. Each of the sub-array modules are configured to interface with other

sub-array modules so that data can pass between the sub-array modules, enabling a processor to communicate with multiple sub-array modules via an interface with one of the sub-array modules. The dies used in the construction of sub-array modules may be less elongated as compared with the dies utilized in the construction of the aforementioned one-dimensional array camera modules, and can therefore better utilize wafer space. In several embodiments, a 1x3 sub-array module is utilized that includes input and output interface circuitry, which allow the sub-array module to couple with other sub-array modules. In many embodiments, a sub-array module including a single camera is utilized. The interface circuitry can further allow coupled sub-array modules to transmit and receive data including image data and/or instructions from a processor with one another. The image data from one of the sub-array modules may be read out by a processor. The interface circuitry may employ any interface protocol including Mobile Industry Processor Interface Alliance (MIPI) Camera Serial Interface 2(c) interface format (the "MIPI interface format") or a Standard Mobile Imaging Architecture ("SMIA") format. The 1x3 modular array cameras may include constituent narrow spectral band green, blue, or red cameras and may also include near-IR cameras.

[0086] Using sub-array modules to construct array cameras can provide numerous advantages. First, the manufacture of sub-array modules can result in a greater yield as compared with the manufacturing yield of longer one-dimensional array camera modules since sub-array module components may more efficiently utilize wafer space. Additionally, their manufacture can also result in comparatively greater homogeneity between sub-array modules since sub-array modules are less intricate as compared with longer one-dimensional array camera modules or two-dimensional array camera modules. Moreover, sub-array modules are versatile insofar as they can be used to construct array cameras of any specified dimension.

**[0087]** One-dimensional array camera modules and sub-array modules in accordance with embodiments of the invention are discussed further below.

#### ARRAY CAMERA ARCHITECTURE

[0088] Array cameras in accordance with many embodiments of the invention can include an array camera module and a processor. The array camera module can

include an array of cameras. An array camera module can include an imager array, which is a sensor that includes an array of focal planes. Each focal plane includes an array of pixels used to capture an image formed on the focal plane by a lens stack. The focal plane can be formed of, but is not limited to, traditional CIS (CMOS Image Sensor), CCD (charge-coupled device), quantum film image sensors, high dynamic range sensor elements, multispectral sensor elements and various alternatives thereof. In many embodiments, the pixels of each focal plane have similar physical properties and receive light through the same lens stack. Furthermore, the pixels in each focal plane may be associated with the same color filter. In a number of embodiments, at least one of the focal planes includes a Bayer-pattern filter. In several embodiments, the focal planes are independently controlled. In other embodiments, the operation of the focal planes in the imager array is controlled via a single set of controls. Array cameras are discussed in U.S. patent application Ser. No. 13/106,797 entitled "Architectures for imager arrays and array cameras" and U.S. patent application Ser. No. 12/952,106 entitled "Capturing and processing of images using monolithic camera array with heterogenous imagers" the disclosure of both applications is hereby incorporated by reference in its entirety.

[0089] An array camera architecture that can be used in a variety of array camera configurations in accordance with embodiments of the invention is illustrated in FIG. 1. The array camera 100 includes an array camera module 102 that is configured to transmit 106 image data to a receiving device 108 via an interface format involving the transmission of additional data describing the transmitted image data. The array camera module 102 includes an array of cameras 104. The cameras 104 in the array camera module 102 are formed from the combination of a lens stack and a focal plane. The array camera module 102 can include an optic array of lens stacks and an imager array of focal planes. These multiple cameras 104 may be active or inactive at any given time. The image data captured by these multiple cameras may be transmitted from the focal planes of each camera to a processor. The focal planes may have different imaging characteristics, such as varying exposure times, start times, and end times. Therefore, the timing of the transmission of the image data captured by each focal plane can vary. Accordingly, the imager array can transmit additional data describing the image data to

enable a device receiving the image data to appropriately reconstruct images from the received image data. The transmission of array camera image data is disclosed in U.S. Patent Application Serial No. 13/470,252, entitled "Systems and Methods for Transmitting and Receiving Array Camera Image Data," the disclosure of which is hereby incorporated by reference.

In many embodiments, the array camera 100 captures images using a [0090] plurality of cameras 104, which can have different imaging characteristics. The array camera 100 can separately control each of the cameras to obtain enhanced image capture and/or to enhance processes such as (but not limited to) super-resolution processes that may be applied to the captured images. For example, each pixel of a focal plane may capture different wavelengths of light, or may capture the intensity of light, varying exposure times, start times, or end times. Once the array camera 100 has commenced capturing image data using the pixels on the imager array, the focal planes can commence transmitting the image data captured using the pixels to a receiving device 108. The image data captured by different cameras can be interleaved for transmission to a receiving device 108 that includes interface circuitry configured to receive image data. In many embodiments, the interface circuitry is implemented in hardware and/or using a processor. The receiving device 108 can then organize the captured image data from the received packet and appropriately combine the image data to process and/or reconstruct the image(s) captured by one or more of the focal planes in the imager array.

[0091] In the illustrated embodiment, image data from multiple images of a scene can be captured by the array camera module 102. As the image data is captured, the array camera module 102 transmits 106 the image data to a receiving device 108. The array camera module 102 transmits the image data using a small number of local data storage cells on the array camera module 102 that store the captured image data following capture by the cameras. In the illustrated embodiment, the array camera module 102 manages the capture and transmission of image data so that the captured image data stored in the storage cells is transmitted by the imager array of the array camera module 102 in the time taken to capture and load the next set of image data into the storage cells. In this way, the array camera module can continuously buffer and

transmit image data using a number of local data storage cells that is less than the total number of pixels in the array camera module.

[0092] In many embodiments, a line of image data transmitted by an imager array can be considered to equal the number of pixels in a row of a focal plane multiplied by the number of focal planes. In several embodiments, the clock frequency of transmitter circuitry on the imager array is set to a desired output data rate and the internal focal plane pixel rate is set to 1/N the desired output data rate (where N is the total number of focal planes). In many image transmission protocols, once a start of line condition is sent, all of image data is transmitted without interrupt until the end of line. Accordingly, a sufficient number of data storage cells and a buffering mechanism can be developed that starts transmission of pixels once there are sufficient pixels stored such that all of the pixels will have been captured and transmitted by the time the end of the line of image data is reached. If, for example, an imager array including 4 focal planes (as in a 1 x 4 array) transmits image data from all focal planes, then there is very little data storage utilized prior to the start of focal plane readout, because the data is transmitted at approximately the rate that at which it is being read. If, however, the same imager array only has one active imager, then almost all of the pixels from a row of the focal plane are stored since the buffer is being read 4 times as fast as it is being written. Therefore, the data storage requirement would be one row of pixels (i.e. 1/4th of a line of image data). When three focal planes are active, 1/ the data from the three focal planes is buffered before transmission commences to avoid underflow. Therefore, the total number of data storage cells utilized is equal to the number of pixels in three quarters of a row of one of the focal planes in this example. The above examples illustrate how the data storage requirements of an imager array can vary based upon the number of active focal planes. In many embodiments, the total number of storage cells within an imager array is less than a quarter of a line of image data. In several embodiments, the total number of storage cells within an imager array is equal to a line of image data. In several embodiments, the total number of data storage cells is between a quarter of a line of image data and a full line of image data. In a number of embodiments, the total number of storage cells is equal to or greater than a line of image data. When the array camera module transmits the captured image data, the

incorporation of additional data describing the image data enables a peripheral device receiving the image data to reconstruct the images captured by each active camera in the imager array 102.

[0093] Imager arrays in accordance with many embodiments of the invention are configured to output image data via an interface format that accommodates the transfer of image data captured via multiple focal planes. In several embodiments, the imager array is configured to transmit captured image data in accordance with an interface format that is compatible with standard interface formats, such as (but not limited to) the MIPI CSI-2 interface format (MIPI interface format), the Camera Link interface format, and any of the Universal Serial Bus (USB) interface formats or FireWire interface formats. When image data captured from multiple focal planes is output by the imager array, the device receiving the image data is faced with the task of assembling the image data into a plurality of images of a scene.

**[0094]** Although specific array camera system architectures are discussed above for constructing array cameras including 1 x N arrays of cameras, any of a variety of system architectures for array cameras including 1 x N arrays of cameras can be utilized as appropriate to the requirements of a specific application in accordance with embodiments of the invention. Imager array architectures are discussed below in greater detail.

# **IMAGER ARRAY ARCHITECTURES**

**[0095]** An imager array in accordance with an embodiment of the invention is illustrated in FIG. 2. The imager array 200 includes a focal plane array core 202 that includes a 1 x N array of focal planes 204 and all analog signal processing, pixel level control logic, signaling, and analog-to-digital conversion circuitry. The imager array also includes focal plane timing and control circuitry 206 that is responsible for controlling the capture of image information using the pixels. For example, in some embodiments, the focal plane timing and control circuitry 206 can synchronize the capture of image data by the focal planes such that active focal planes capture image data from a scene simultaneously. In many embodiments, the focal plane timing and control circuitry 206 causes the active focal planes to capture image data from a scene in a particular

controlled sequence. In a number of embodiments, the focal plane timing and control circuitry 206 utilizes reset and read-out signals to control the integration time of the pixels. In several embodiments, any of a variety of techniques can be utilized to control integration time of pixels and/or to capture image information using pixels. In many embodiments, the focal plane timing and control circuitry 206 provides flexibility of image information capture control, which enables features including (but not limited to) high dynamic range imaging, high speed video, and electronic image stabilization. In various embodiments, the imager array 200 includes power management and bias generation circuitry 208. The power management and bias generation circuitry 208 provides current and voltage references to analog circuitry such as the reference voltages against which an ADC would measure the signal to be converted against. In many embodiments, the power management and bias circuitry also includes logic that turns off the current/voltage references to certain circuits when they are not in use for power saving reasons. In several embodiments, the imager array includes dark current and fixed pattern (FPN) correction circuitry 210 that increases the consistency of the black level of the image data captured by the imager array and can reduce the appearance of row temporal noise and column fixed pattern noise. In several embodiments, each focal plane includes reference pixels for the purpose of calibrating the dark current and FPN of the focal plane and the control circuitry can keep the reference pixels active when the rest of the pixels of the focal plane are powered down in order to increase the speed with which the imager array can be powered up by reducing the need for calibration of dark current and FPN. In many embodiments, the SOC imager includes focal plane framing circuitry 212 that packages the data captured from the focal planes into a container file and can prepare the captured image data for transmission. In several embodiments, the focal plane framing circuitry 212 includes information identifying the focal plane and/or group of pixels from which the captured image data originated. In a number of embodiments, the imager array 200 also includes an interface for transmission of captured image data to external devices. In the illustrated embodiment, the interface is a MIPI CSI 2 output interface supporting four lanes that can support read-out of video at 30 fps from the imager array and incorporating data output interface circuitry 214, interface control circuitry 216 and

interface input circuitry 218. Typically, the bandwidth of each lane is optimized for the total number of pixels in the imager array and the desired frame rate. The use of various interfaces including the MIPI CSI 2 interface to transmit image data captured by an array of imagers within an imager array to an external device in accordance with embodiments of the invention is described in in U.S. patent application Ser. No. 13/470,252, cited to and incorporated by reference above.

**[0096]** An imager array in accordance with embodiments of the invention can include a single controller that can separately sequence and control each focal plane. Having a common controller and I/O circuitry can provide important system advantages including lowering the cost of the system due to the use of less silicon area, decreasing power consumption due to resource sharing and reduced system interconnects, simpler system integration due to the host system only communicating with a single controller rather than M x N controllers and read-out I/O paths, simpler array synchronization due to the use of a common controller, and improved system reliability due to the reduction in the number of interconnects.

[0097] Additionally, an imager array in accordance with embodiments of the invention may include a parallax disparity resolution module 220 that can determine disparity between pixels in different images captured by the camera array using parallax detection processes similar to those described in U.S. Provisional Patent Application Serial No. 61/691,666 entitled "Systems and Methods for Parallax Detection and Correction in Images Captured Using Array Cameras" to Venkataraman et al., the disclosure of which is incorporated by reference herein in its entirety. In particular, as will be elaborated on below in the section on "One-Dimensional Array Camera Modules", in some embodiments, the processing requirements for a parallax disparity resolution calculation may be sufficiently low that the process may be computed by the imager array circuitry.

**[0098]** Although specific components of an imager array architecture are discussed above with respect to FIG. 2, any of a variety of imager arrays can be constructed in accordance with embodiments of the invention that enable the capture of images of a scene at a plurality of focal planes in accordance with embodiments of the invention. Array camera modules that utilize imager arrays are discussed below.

#### ARRAY CAMERA MODULES

Arrav camera modules in accordance with many embodiments of the [0099] invention include the combination of an optic array including a 1 x N array of lens stacks and an imager array that includes a 1 x N array of focal planes. Each lens stack in the optic array defines a separate optical channel. The optic array may be mounted to an imager array that includes a focal plane for each of the optical channels, where each focal plane includes an array of pixels or sensor elements configured to capture an image. When the optic array and the imager array are combined with sufficient precision, the array camera module can be utilized to capture image data from multiple images of a scene that can be read out to a processor for further processing, e.g. to synthesize a high resolution image using super-resolution processing. For example, each of the cameras in an array camera module can capture image data of a scene reflecting a sub-pixel shifted view of the scene – i.e. relative to the corresponding image formed by at least one other camera (e.g. the lens stack of each camera can have a field-of-view that is shifted with respect to the field-of-view of each other camera so that each shift includes a sub-pixel shifted view of the scene); hence, the aggregated image data can embody sufficient sampling diversity to enable the implementation of superresolution processes that can be used construct an enhanced image of the scene using the aggregated image data. In other words, each lens stack can form an image of a scene onto a corresponding focal plane, and thereby generate image data, from a slightly different viewpoint relative to an image formed by each of the other lens stacks, such that the images formed of the scene by each of the lens stacks contain nonredundant information of about the scene. Hence, the non-redundant information can be used in the construction of a super-resolved image.

**[00100]** In many embodiments, the optics in an array camera module are designed to be able to resolve images to a sufficient extent such that the super-resolution processes can be implemented. For example, in many instances, the MTF of the optics is able to resolve variation in intensity at the spatial resolution of the image that is to result from implemented super-resolution processes (e.g. as opposed to the spatial resolution of

the image that can be formed by a single respective camera within an array camera module).

[00101] It should be noted that although 'arrays of lens stacks' and 'arrays of focal planes' are referenced, it is not meant to be suggested that such arrays are necessarily monolithic structures. In many instances a plurality of distinct lens stacks are disposed relative to one-another to form a 1xN array of lens stacks; similarly, in many instances a plurality of distinct focal planes are disposed relative to one-another to form a 1xN array of focal planes. In general, a plurality of lens stacks, and a plurality of focal planes can be adjoined in any suitable way to construct a 1xN array camera module in accordance with embodiments of the invention. In some instances, the focal planes and/or lens stacks are embodied within monolithic structures.

[00102] An exploded view of an array camera module formed by combining a lens stack array with a monolithic sensor including an array of focal planes in accordance with an embodiment of the invention is illustrated in FIG. 3. The array camera module 300 includes an optic array 310 including 1 x N distinct lens stacks forming N separate apertures and an imager array 330 that includes a 1 x N array of focal planes 340. Each lens stack 320 in the optic array 310 creates an optical channel that resolves an image on one of the focal planes 340 on the imager array 330. Each of the lens stacks 320 may be of a different type. In several embodiments, the optical channels are used to capture images of different portions of the wavelength of light spectrum (e.g. using color filters, located either within the lens stack or on the sensor) and the lens stack in each optical channel is specifically optimized for the portion of the spectrum imaged by the focal plane associated with the optical channel.

**[00103]** In many embodiments, the array camera module 300 includes lens stacks 320 having one or multiple separate optical lens elements axially arranged with respect to each other. Optic arrays of lens stacks 310 in accordance with several embodiments of the invention include one or more adaptive optical elements that can enable the independent adjustment of the focal length of each lens stack and/or later shifting of the centration of the refractive power distribution of the adaptive optical element. The use of adaptive optical elements is described in U.S. Patent Application No. 13/650,039,

entitled "Lens Stack Arrays Including Adaptive Optical Elements", filed October 11, 2012, the disclosure of which is incorporated by reference herein in its entirety.

[00104] In several embodiments, the array camera module employs wafer level optics (WLO) technology. WLO is a technology that encompasses a number of processes, including, for example, molding of lens arrays on glass wafers, stacking of those wafers (including wafers having lenses replicated on either side of the substrate) with appropriate spacers, followed by packaging of the optics directly with the imager into a monolithic integrated module. The WLO procedure may involve, among other procedures, using a diamond-turned mold to create each plastic lens element on a glass substrate. More specifically, the process chain in WLO generally includes producing a diamond turned lens master (both on an individual and array level), then producing a negative mold for replication of that master (also called a stamp or tool), and then finally forming a polymer replica on a glass substrate, which has been structured with appropriate supporting optical elements, such as, for example, apertures (transparent openings in light blocking material layers), and filters. Although the construction of lens stack arrays using WLO is discussed above, any of a variety of techniques can be used to construct lens stack arrays, for instance those involving precision glass molding, polymer injection molding or wafer level polymer monolithic lens processes.

**[00105]** Although certain array camera module configurations have been discussed above, any of a variety of array camera modules that utilize lens stacks and focal planes may be implemented in accordance with embodiments of the invention. One-dimensional array camera modules are discussed below.

# ONE-DIMENSIONAL ARRAY CAMERA MODULES

**[00106]** In many embodiments, one-dimensional (or 1 x N) array camera modules are utilized in the construction of array cameras. One-dimensional array camera modules can provide a number of benefits. For instance, one-dimensional array camera modules can enable the construction of array cameras having distinctly thin form factors. Such array cameras may be useful in a host of applications. For example, array cameras having a thin form factor may be incorporated within the bezel of a consumer electronics

device such as a laptop, a tablet, or a smart phone, and may further be incorporated within a pair of eye glasses.

[00107] Additionally, array cameras that incorporate one-dimensional array camera modules are advantageous insofar as they may require less processing and/or memory requirements as compared to two-dimensional (or M x N) array cameras. For example, array cameras typically employ a parallax detection and correction process in order to facilitate the imaging of a scene. Generally, the process is meant to address the fact that the relative positioning of objects in a scene may appear to vary from the respective viewpoints of different cameras within an array camera module. In two-dimensional array cameras, this technique can be processor intensive and involve significant data storage requirements related to searches for corresponding pixels along epipolar lines (other than just horizontal or vertical) between cameras located in different rows and/or columns within the array camera module. Array camera modules typically pass image data to a processor by starting with image data captured by pixels in a first row of a focal plane and then advancing to the next row of pixels and reading out image data from pixels within the next row of pixels. The read out of image data from pixels within a focal plane can also be interspersed with the readout of image data from pixels within other focal planes. Note that with this technique, because image data is being passed to the processor along the rows of the focal planes, searches for corresponding pixels along vertical or diagonal epipolar lines, for example during a parallax detection and correction process of a two-dimensional array camera, involve the processor storing substantial amounts of image data across multiple rows of image data captured by a focal plane. In other words, whereas a parallax detection and correction process may be employed along the 'row' direction as soon as the image data from a respective row of focal planes has been read out to a processor, the parallax detection and correction process along the column direction cannot be employed until multiple rows of image data has been read out to the processor. Consequently, image data across multiple rows of pixels must be stored in order to complete parallax detection and correction processes. This may result in larger storage requirements that may be prohibitive of a system-on-a-chip (SOC) type solution, e.g. where the parallax disparity resolution is built into the imager array. However, because one-dimensional array cameras do not

necessarily employ parallax correction and detection processes in two directions, the processing and/or memory requirements can be substantially reduced. Thus, with lesser processing and/or memory requirements, system-on-a-chip (SOC) type solutions may be enabled.

**[00108]** Additionally, one-dimensional array camera modules may provide greater manufacturing yield as compared with two dimensional array camera modules, because one-dimensional array camera modules may have less cameras. Generally, the more cameras an array camera module has, the more difficult it is to directly manufacture because it is more likely to have faulty sensors and/or faulty lens stacks.

[00109] A 1 x 5 array camera module in accordance with embodiments of the invention is illustrated in FIG. 4A. In particular, the array camera module includes a central narrow spectral band green camera (G), adjacent narrow spectral band blue cameras (B), and periphery narrow spectral band red cameras (R). Color filters may be employed to achieve the respective narrow spectral band cameras. The color filters may be located either within the lens stack or on the sensor. A narrow spectral band green camera may be centrally placed to accommodate the fact that humans are most sensitive to green light. Narrow spectral band red and blue cameras may be placed on either side of the central narrow spectral band green camera - this configuration may counteract any occlusion that may occur as a result of any obstructing foreground objects. For example, in the case of an obstructing foreground object, areas of the scene immediately surrounding the foreground object as seen by the central camera may not be seen by the cameras on one of the two sides of the central green camera. However, if both narrow spectral band red and blue cameras are placed on either side of the central green camera, color imaging data can be obtained from the scene irrespective of such obstruction caused by the foreground object, and uniform spectral coverage is thereby provided. FIG. 4B is similar to FIG. 4A except that the narrow spectral band red cameras are adjacent to a central narrow spectral band green camera, and narrow spectral band blue cameras enclose the configuration. Note that although two particular configurations of 1 x 5 array camera modules are illustrated, any number of configurations may be employed all in accordance with embodiments of the invention. For example, in some embodiments near-IR cameras (N), which facilitate the

imaging of scenes with low-lighting, may be employed, and in a number of embodiments, full visual spectrum cameras (P) are employed. Note that where full visual spectrum cameras are employed, Bayer filters, which are typically implemented on the sensor, may be utilized to obtain color information.

[00110] By increasing the number of a particular type of narrow spectral band camera (e.g. Green), super-resolution processes can be employed to greater effect. A 1 x 7 array camera module in accordance with embodiments of the invention is illustrated in FIGS. 5A – 5C. As illustrated, a 1 x 7 array camera module may employ more narrow spectral band green cameras than narrow spectral band blue or narrow spectral band red cameras. This may be to accommodate the fact that humans are most sensitive to green light. In the illustrated embodiments, the array camera module includes a central narrow spectral band green camera and periphery narrow spectral band green cameras, and narrow spectral band red and blue cameras. The cameras may be symmetrically distributed or they may be asymmetrically distributed. In the embodiments illustrated in FIGS. 5A and 5B, the narrow spectral band cameras are symmetrically distributed. In the embodiment illustrated in FIG. 5C, the narrow spectral band cameras are asymmetrically distributed. The inclusion of multiple red and blue cameras uniformly distributed around the central green camera reduces the likelihood of color artifacts related to occlusions by foreground objects. The presence of multiple green cameras in an array having sub-pixel shifted views of the scene to provide sampling diversity enables the application of super-resolution processes to the captured image data to recover a higher resolution image of the scene. As before, although three particular configurations of 1 x 7 array camera modules are illustrated, any number of configurations may be employed all in accordance with embodiments of the invention. For example, in some embodiments near-IR cameras may be employed, and in a number of embodiments, full visual spectrum cameras are employed. As before, where full visual spectrum cameras are employed, Bayer filters may be utilized to obtain color information.

**[00111]** A 1 x 9 array camera module in accordance with embodiments of the invention is illustrated in FIGS. 6A - 6F. A 1 x 9 array camera module may be more preferable than either a 1 x 7 array camera module or a 1 x 5 array camera module

since it provides more image data. As before, a 1 x 9 array camera module may employ more narrow spectral band green cameras than narrow spectral band blue or narrow spectral band red cameras. The inclusion of multiple red and blue cameras distributed around the central green camera reduces the likelihood of color artifacts related to occlusions by foreground objects. The presence of multiple green cameras in an array having sub-pixel shifted views of the scene to provide sampling diversity enables the application of super-resolution processes to the captured image data to recover a higher resolution image of the scene. Also as before, although six particular configurations of 1 x 9 array camera modules are illustrated, any number of configurations may be employed all in accordance with embodiments of the invention. For example, in some embodiments, narrow spectral band green cameras are not disposed along the periphery of the array camera module.

**[00112]** Although particular one-dimensional array camera modules have been discussed, an array camera module with any number of cameras may be implemented in accordance with embodiments of the invention. For instance, 1 x 4 array camera modules and 1 x 5 array camera modules may be implemented. Sub-array modules that may be used to construct one-dimensional array camera modules are discussed below.

#### **SUB-ARRAY MODULES**

**[00113]** Much of the discussion above describes the construction of array cameras using a single monolithic array camera module. In many embodiments, sub-array modules are used in the construction of array cameras. Sub-array modules may be configured to interface with other sub-array modules so that data can pass between the sub-array modules, thereby enabling a processor to interact with multiple coupled sub-array modules via an interface with one of the sub-array modules. In this way, sub-array modules can couple with other sub-array modules to enable the fabrication of array cameras of any number of specified dimensions and characteristics. In many embodiments, sub-array modules do not couple with one-another, but instead interact directly or indirectly (e.g. via a bus) with a receiving device (e.g. a processor). Accordingly, sub-array modules of this variety can also enable the modular construction of an array camera of any number of specified dimensions and characteristics.

**[00114]** The use of sub-array modules in the construction of array cameras can provide a number of benefits. For example, the use of sub-array modules to construct array cameras can improve manufacturing yield relative to the direct fabrication of an array camera module. In particular, although one-dimensional array camera modules may be beneficial in numerous applications, their manufacture can be challenging. Specifically, components for one-dimensional array cameras (e.g. the lenses and the corresponding sensor) are typically manufactured on wafers, but the elongated nature of the components may not be conducive to optimizing wafer space. In many instances, in the manufacture of a one-dimensional lens array, the periphery of the wafer used in the manufacture may contain significant unused space that, because of the elongated shape of a lens array, cannot accommodate further lens arrays. In other words, wafers are may be more efficient in the manufacture of components that are more 'square' in shape than 'elongated.' However, sub-array modules that are used in the construction of an array camera module may be less elongated than the array camera module. Hence, sub-array modules can better optimize wafer space during manufacture.

**[00115]** Moreover, the manufacture of sub-array modules is also beneficial since they comprise a relatively fewer number of cameras compared to an array camera module: the more cameras an array camera module has, the more difficult it is to directly manufacture since it is more likely to have a critical number of faulty cameras. Furthermore, the manufacturing processes disclosed in prior U.S. Patent Application Ser. No. 13/050,429 disclosure entitled "Fabrication process for mastering imaging lens arrays" can be more beneficially applied if the array to be generated is smaller like those discussed in this application. The 1 x N master structure, for the sub-array, can be more optimally fine-tuned for homogeneity either by multiple attempts to directly diamond-turn the 1 x N arrays of the template or by multiple attempts to step-and-repeat the 1 x N array of the template from single lens pins before using the final small-variation 1 x N template to fully populate, for example, a 8" wafer scale master. As a result, the array-internal performance variation and in particular BFL-variation can be reduced. Resulting variations from array to array on the full wafer scale master can be compensated by the approach presented under the method described above.

[00116] Moreover, array camera modules constructed from sub-array modules may be further advantageous in that each individual sub-array module may incorporate custom spacers to counteract back focal length variation. U.S. Patent Application Ser. No. 61/666,852 entitled "Systems and Methods for Manufacturing Camera Modules Using Active Alignment of Lens Stack Arrays and Sensors" discusses the issues related to back focal length (BFL) misalignment in the construction of array camera modules, and is hereby incorporated by reference. In many embodiments, the distribution of the average BFL for a 1 x N sub-array module fabricated in a wafer stack is determined over a sufficient number of stacks to establish the repeatable array-average BFL variation. A spacer wafer may then be machined with steps in thickness that correspond to the pattern of the average-BFL over the wafer stack, and the spacers may thereafter be incorporated into the sub array module. The standard deviation of the BFL of subarray modules within a wafer stack is expected to be small given the relatively small number of cameras in a sub-array module; accordingly, the incorporation of the customized spacers into the sub-array modules is expected to result in sufficient focusing.

[00117] A sub-array module architecture in accordance with embodiments of the invention is illustrated in FIG. 7A. The sub-array module 700 includes a focal plane array core 702 that includes a 1 x 3 array of focal planes 704 and all analog signal processing, pixel level control logic, signaling, and analog-to-digital conversion circuitry. Although a 1 x 3 array of focal planes is illustrated, any number of focal planes can be used in accordance with embodiments of the invention. The sub-array module includes lens stacks 706, and the combination of a lens stack 706 and its corresponding focal plane 704 can be configured to implement any type of camera including but not limited to narrow spectral band red cameras, narrow spectral band blue cameras, narrow spectral band green cameras, near-IR cameras, and full visual spectrum cameras. Bayer-filters may be employed to facilitate imaging. The sub-array module may utilize focal plane timing and control circuitry 708 that is responsible for controlling the capture of image information using the focal plane's constituent pixels. In a number of embodiments, the focal plane timing and control circuitry 708 provides flexibility of image information capture control which enables features including, but not limited to,

high dynamic range imaging, high speed video, and electronic imaging stabilization. The focal plane timing and control circuitry can have inputs 720 and outputs 722 related to the timing of image capture, so that the sub-array module timing can be controlled by an external device (e.g. a processor, or alternatively another sub-array module). In various embodiments, the sub-array module 700 includes power management and bias generation circuitry 710. The power management and bias generation circuitry 710 provides current and voltage references to analog circuitry such as the reference voltages against which an ADC would measure the signal to be converted against. In many embodiments, the power management and bias circuitry 710 also includes logic that turns off the current/voltage references to certain circuits when they are not in use for power saving reasons. In several embodiments, the imager array includes dark current and fixed pattern (FPN) correction circuitry 712 that increases the consistency of the black level of the image data captured by the imager array and can reduce the appearance of row temporal noise and column fixed pattern noise. In several embodiments, each focal plane includes reference pixels for the purpose of calibrating the dark current and FPN of the focal plane and the control circuitry can keep the reference pixels active when the rest of the pixels of the focal plane are powered down in order to increase the speed with which the imager array can be powered up by reducing the need for calibration of dark current and FPN. In many embodiments, the sub-array module includes focal plane framing circuitry 714 that packages the data captured from the focal planes into a container file and can prepare the captured image data for transmission. In several embodiments, the focal plane framing circuitry 714 includes information identifying the focal plane and/or group of pixels from which the captured image data originated. In a number of embodiments, the sub-array module 700 also includes an interface for transmission and reception of data to and from external device(s). For example, the interface can allow for the transmission and reception of image data. In the illustrated embodiment, the interface is a MIPI CSI 2 output interface supporting four lanes that can support read-out of video at 30 fps from the imager array and incorporating interface control circuitry 716, and two sets of data input/output interface circuitry 718. In the illustrated embodiment, each set of interface circuitry is capable of both sending and receiving data. The interface circuitry, the

interface control circuitry, and the focal plane timing and control inputs/outputs can allow the sub-array module to be controlled by a processor (either directly or indirectly). and/or can also allow the sub-array module to receive/transmit captured image data. Typically, the bandwidth of each input/output lane is optimized for the total number of pixels in the imager array and the desired frame rate. The input/output interface circuitry is configured to interface with any receiving device such as another sub-array module or a processor. Note that although the illustrated embodiment depicts a MIPI CSI 2 protocol, any interface protocol may be used including a Standard Mobile Imaging Architecture ("SMIA") format. The use of various interfaces including the MIPI CSI 2 interface to transmit image data captured by an array of imagers within an imager array to an external device in accordance with embodiments of the invention is described in in U.S. Patent Application Serial No. 13/470,252, cited to and incorporated by reference above. The sub-array module may also include pins that can be used to establish a unique slave address for the sub-array module in the case where the sub-array module interfaces with a master device (e.g. a processor, or a master sub-array module) via a bus as discussed below. In this way, each slave device can be independently controlled by the master device.

**[00118]** A sub-array module in accordance with several embodiments of the invention is illustrated in FIG. 7B. The sub-array module 750 is similar to that seen in FIG. 7A, except that it does not include two sets of interface circuitry that allow both the transmission and reception of data; instead the illustrated embodiment depicts a sub-array module that includes receive interface circuitry 752 configured to receive image data from another sub-array module for forwarding, and transmit interface circuitry 754 configured to transmit forwarded image data and image data captured by the sub-array module. Such a design may be more efficiently manufactured.

**[00119]** As alluded to above, in many embodiments, sub-array modules are implemented that are not required to couple with other sub-array modules; instead they each interface – either directly or indirectly – with a receiving device, such as a processor, and thereby provide image data. As can be appreciated, any suitable way for transmitting the data can be implemented. For example, image data can be transmitted in parallel, or it can be transmitted in a serial fashion. In many embodiments, sub-array

modules are configured to output image data to a bus; subsequently, the image data carried by the bus (e.g. from each of many sub-array modules) can be processed into a single MIPI output that can be more easily handled by a receiving device. The image data can be transmitted to the bus in a parallel fashion, or as serial data, e.g. via low voltage differential signaling. Additionally, any suitable I/O device may be used to relay image data to a receiving device, not just a conventional bus. In this way, sub-array modules can be implemented that do not have to have, for example, distinct MIPI processing circuitry; instead, the processing of image data from many sub-array modules into a single MIPI output can be accomplished separately and more efficiently. Accordingly, the manufacture of sub-array modules can become less intricate, and their manufacturing yield may increase as a result. Further, with this modular construction, I/O devices can be easily swapped if desired. Although a particular architecture is described above, any suitable architecture can be implemented in accordance with embodiments of the invention.

**[00120]** Although particular sub-array modules have been illustrated and discussed, any of a variety of sub-array modules that can allow for transmission and reception of data may be implemented in accordance with embodiments of the invention. For example, 1 x 4, 1 x 2, and even 1 x 1 sub-array modules may be implemented. Furthermore, 2-dimensional sub-array modules may also be implemented in accordance with embodiments of the invention; for example 2 x 3, 2 x 2, and 3 x 3 sub-array modules may be implemented. Two-dimensional sub-array modules may be used to construct two-dimensional array camera modules. Sub-array module lens configurations and the construction of one-dimensional array camera modules using sub-array modules are discussed below.

# SUB-ARRAY MODULE CONFIGURATIONS AND THE CONSTRUCTION OF ONE-DIMENSIONAL ARRAY MODULES

**[00121]** Sub-array modules may include cameras arranged in a variety of configurations in accordance with embodiments of the invention. The exact configurations employed in sub-array modules depend on the particular design of the array camera to be formed. For example, in the case where a GNRBGBRNG 1 x 9 array

camera is desired (like the one illustrated in FIG. 6E), three 1 x 3 sub-array modules may be used to form the corresponding array camera module having the following respective camera arrangement configurations: GNR, BGB, and RNG. FIGS. 8A-8K depict ten examples of sub-array module configurations that are similar to those shown in FIG. 7B in accordance with embodiments of the invention. Although ten examples are provided in FIGS. 8A-8K, any number of configurations of sub-array modules using any of a variety of color filter patterns may be implemented in accordance with embodiments of the invention. The sub-array modules 800 are illustrated as having corresponding interface circuitry 802, represented by arrows. The direction of the arrows is meant to indicate the direction in which image data is passed when the interface circuitry is operational.

[00122] The direction in which image data is passed in a sub-array module is configurable in accordance with many embodiments of the invention. For instance, a BGR sub-array module may be reconfigured so that it acts as a RGB sub-array module. FIG. 9 illustrates how a BGR sub-array module may be reconfigured to act as a RGB sub-array module. In particular, the BGR sub-array module 900 may be rotated 180° 902, and its corresponding interface circuitry may be reconfigured 904 such that the transmission/reception protocols in the interface circuitry are reversed. Where subarray modules are rotated 180° the data read from the sub-array module can include a flag and/or additional data indicating the orientation of the sub-array module to enable a processor to map the relative position of pixel addresses to corresponding locations in other cameras in an array camera. Alternatively, in the case where a BGR sub-array module is mounted on a printed circuit board (PCB), the BGR sub-array module may be rotated 180° and positioned on a PCB (or laminated chip carrier or other similar such interconnector), and the configuration of the PCB (or laminated chip carrier or other similar such interconnector) may invert the routing of the data transmitted to/from the sub-array module, such that the sub-array module acts as a RGB sub-array module. Of course, the above description does not apply only to 1 x 3 BGR sub-array modules; the direction in which data is passed in any sub-array module may be reconfigured in accordance with embodiments of the invention.