(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3563298号

(P3563298)

(45) 発行日 平成16年9月8日(2004.9.8)

(24) 登録日 平成16年6月11日(2004.6.11)

(51) Int.CI.<sup>7</sup>

F 1

G 11 C 16/06

G 11 C 17/00 632 A

G 11 C 16/02

G 11 C 17/00 611 G

G 11 C 17/00 634 E

請求項の数 4 (全 15 頁)

(21) 出願番号

特願平11-165214

(22) 出願日

平成11年6月11日(1999.6.11)

(65) 公開番号

特開2000-353392(P2000-353392A)

(43) 公開日

平成12年12月19日(2000.12.19)

審査請求日

平成13年2月28日(2001.2.28)

(73) 特許権者 591049893

株式会社 沖マイクロデザイン

宮崎県宮崎郡清武町大字木原7083番地

(73) 特許権者 000000295

沖電気工業株式会社

東京都港区虎ノ門1丁目7番12号

(74) 代理人 100086807

弁理士 植本 恒成

(72) 発明者 泊 伸広

宮崎県宮崎郡清武町大字木原7083番地

株式会社 沖マイクロデザイン宮崎内

審査官 長島 孝志

最終頁に続く

(54) 【発明の名称】電圧検出回路

## (57) 【特許請求の範囲】

## 【請求項1】

発振回路の出力信号に基づき電源電圧の昇圧を行って高電圧を出力するチャージポンプ回路と、前記チャージポンプ回路が出力した高電圧をメモリセルに供給して書き込みを行う記憶回路とを有する装置に設けられた電圧検出回路であって、

前記発振回路の前記出力信号に基づき前記チャージポンプ回路が前記昇圧を開始してから所定期間が経過するまで該チャージポンプ回路が出力する前記高電圧の前記メモリセルへの供給を遮断するスイッチと、

基準電圧を発生する基準電圧発生回路と、

前記基準電圧との比較で前記チャージポンプ回路の出力する前記高電圧が所望電圧値に到達したか否かを示す信号を出力する電圧比較手段と、

前記チャージポンプ回路が前記昇圧を開始してから前記所定期間が経過したときに前記電圧比較手段の前記出力信号に応答して、前記高電圧が前記所望電圧値に到達したか否かの判定信号を出力する検出手段と、

前記判定信号が、前記高電圧が前記所望電圧値に到達していないことを示す場合には前記発振回路の発振動作を停止させ、到達していることを示す場合には該発振動作を継続させる停止手段とを、備えたことを特徴とする電圧検出回路。

## 【請求項2】

電源電圧の昇圧を行って高電圧を出力するチャージポンプ回路を有し、前記チャージポンプ回路が出力した高電圧を対象素子に供給して該対象素子を機能させる装置に設けられた

10

20

電圧検出回路であって、

前記チャージポンプ回路が前記昇圧を開始してから所定期間が経過するまで該チャージポンプ回路が出力する前記高電圧の前記対象素子への供給を遮断するスイッチと、

前記電源電圧の昇圧を行って前記高電圧と対比するための対比用電圧を前記チャージポンプ回路とは独立に生成する対比用チャージポンプ回路と、

前記対比用電圧との比較で前記チャージポンプ回路が出力する前記高電圧が所望電圧値に到達したか否かを示す信号を出力する電圧比較手段と、

前記チャージポンプ回路が前記昇圧を開始してから前記所定期間が経過したときに前記電圧比較手段の前記出力信号に応答して、前記高電圧が前記所望電圧値に到達したか否かの判定信号を出力する検出手段と、

前記判定信号が、前記高電圧が前記所望電圧値に到達していないことを示す場合には前記チャージポンプ回路の前記昇圧を停止し、到達していることを示す場合には該昇圧を継続させる停止手段とを、備えたことを特徴とする電圧検出回路。

**【請求項 3】**

電源電圧の昇圧を行って高電圧を出力するチャージポンプ回路と、前記チャージポンプ回路が出力した高電圧をメモリセルに供給して書き込みを行う記憶回路とを有する装置に設けられた電圧検出回路であって、

前記チャージポンプ回路が前記昇圧を開始してから所定期間が経過するまで該チャージポンプ回路が出力する前記高電圧の前記メモリセルへの供給を遮断するスイッチと、

請求項 2 記載の対比用チャージポンプ回路、電圧比較手段、検出手段及び停止手段とを備えたことを特徴とする電圧検出回路。

**【請求項 4】**

前記判定信号は、外部にモニタ用として出力する構成にしたことを特徴する請求項 1、2 または 3 記載の電圧検出回路。

**【発明の詳細な説明】****【0001】****【産業上の利用分野】**

本発明は、記憶回路を持つ半導体集積装置等に設けられる電圧検出回路に関するものである。

**【0002】****【従来の技術】**

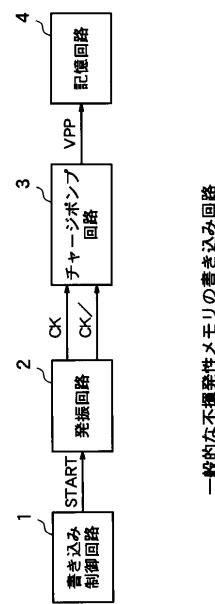

図2は、従来の一般的な不揮発性メモリの書き込み回路を示す構成図である。

この書き込み回路は、書き込み制御回路1と、該書き込み制御回路1の出力側に接続された発振回路2と、該発振回路2の出力側に接続されたチャージポンプ回路3とを備え、半導体集積装置中の記憶回路4にチャージポンプ回路3で生成された高電圧VPPを用いて書き込むものである。

**【0003】**

書き込みを行う場合には、書き込み制御回路1が発振開始を示す発振指示信号STARTをアクティブの“H”にする。書き込み制御回路1からのアクティブな信号STARTを入力した発振回路2は発振し、例えば5MHzのクロックCKと該クロックCKに逆相のクロックCK/とを発生し、チャージポンプ回路3に与える。チャージポンプ回路3は、2つのクロックCK, CK/を用い、電源電圧を上昇させて高電圧VPPを生成する。記憶回路4が例えばEEPROM等の不揮発性メモリの場合には、高電圧VPPは、20V程度である。

記憶回路4はデータを記憶させる回路であり、高電圧VPPを利用し、EEPROMの場合にはメモリセルにトンネル現象を起こさせ、不揮発性メモリの記憶を行う。高電圧VPPの値はある程度の電圧以上が必要であり、EEPROMでは15V以上ないとトンネル現象が発生せず、記憶ができない。

**【0004】****【発明が解決しようとする課題】**

10

20

30

40

50

しかしながら、従来の図2の書き込み回路により、記憶回路4の書き込みを行う半導体集積装置では、次のような課題があった。

チャージポンプ回路3が生成する高電圧VPPのレベルが不明のまま、書き込みを行おうとするので、書き込みができたかどうかは、書き込み終了後のデータを確認するまで判断できなかった。また、高電圧VPPが中途半端な値のときには、書き込みが行われたり、行われなかったりするので、データが修復困難に破壊される事があった。さらに、第3者が、故意に電圧VPPの値を下げるにより、書き込みをできないようにすることもでき、次のような問題も発生する。

例えば、ICカード等において、カードへ不正アクセスをした回数を記憶回路4に保持させ、3回以上の不正アクセスが行われたカードを使用できないようなアプリケーションにしたものがある。このようなICカードでは、不正アクセスが仮に発生したときに、記憶回路4の専用領域に不正アクセスの回数を書き込むことになるが、電圧VPPの値を故意に下げておけば、記憶回路4に対する書き込みが実施できないので、何回でも不正アクセスが可能になる。

#### 【0005】

##### 【課題を解決するための手段】

前記課題を解決するために、本発明のうちの第1の発明は、発振回路の出力信号に基づき電源電圧の昇圧を行って高電圧を出力するチャージポンプ回路と、前記チャージポンプ回路が出力した高電圧をメモリセルに供給して書き込みを行う記憶回路とを有する装置に設けられた電圧検出回路において、次のようなスイッチ、基準電圧を発生する基準電圧発生回路、電圧比較手段、検出手段、及び停止手段を用いて構成している。

前記スイッチは、発振回路の出力信号に基づきチャージポンプ回路が昇圧を開始してから所定期間が経過するまで該チャージポンプ回路が出力する高電圧のメモリセルへの供給を遮断するものである。電圧比較手段は、基準電圧との比較でチャージポンプ回路の出力する高電圧が所望電圧値に到達したか否かを示す信号を出力するものである。検出手段は、チャージポンプ回路が昇圧を開始してから所定期間が経過したときに電圧比較手段の出力信号に応答して、高電圧が所望電圧値に到達したか否かの判定信号を出力するものである。停止手段は、判定信号が、高電圧が所望電圧値に到達していないことを示す場合には発振回路の発振動作を停止させ、到達していることを示す場合には発振動作を継続させるものである。

#### 【0008】

このような構成を採用したことにより、発振回路の出力信号に基づきチャージポンプ回路が昇圧を開始してから所定期間が経過するまでは、メモリセルには、スイッチによる遮断で高電圧が与えられず、書き込みは行われない。その所定期間が経過するまでに、基準電圧との比較でチャージポンプ回路の出力する高電圧が所望電圧値に到達したか否かを示す信号が電圧比較手段から出力される。検出手段は、所定期間が経過したときに高電圧がメモリセルを機能させるのに必要な所望電圧値に到達したか否かの判定信号を出力する。ここで、高電圧が所望電圧値に到達していない場合には、停止手段によって発振回路の発振動作が停止し、これによってチャージポンプ回路の動作も停止するので、所定期間が経過した後にも、メモリセルには所望電圧値に満たない高電圧は与えられず、書き込みが行われない。メモリセルに供給されるのは所望電圧値以上に昇圧された高電圧だけとなる。

#### 【0009】

第2の発明では、電源電圧の昇圧を行って高電圧を出力するチャージポンプ回路を有し、チャージポンプ回路が出力した高電圧を対象素子に供給して対象素子を機能させる装置に設けられた電圧検出回路において、次のようなスイッチ、対比用チャージポンプ回路、電圧比較手段、検出手段及び停止手段を用いて構成している。

前記スイッチは、チャージポンプ回路が昇圧を開始してから所定期間が経過するまでそのチャージポンプ回路が出力する高電圧の対象素子への供給を遮断するものである。対比用チャージポンプ回路は、電源電圧を昇圧して高電圧と対比するための対比用電圧をチャージポンプ回路とは独立に生成する回路である。電圧比較手段は、対比用電圧との比較でチ

10

20

30

40

50

チャージポンプ回路が出力する高電圧が所望電圧値に到達したか否かを示す信号を出力する手段である。検出手段は、チャージポンプ回路が昇圧を開始してから所定期間が経過したときに電圧比較手段の出力信号に応答して、高電圧が所望電圧値に到達したか否かの判定信号を出力する手段である。停止手段は、判定信号が、高電圧が所望電圧値に到達していないことを示す場合にはチャージポンプ回路の昇圧を停止し、到達していることを示す場合には昇圧を継続させる手段である。

#### 【0010】

このような構成を採用したことにより、第1の発明における基準電圧の代わりに、対比用チャージポンプ回路が出力する対比用電圧が高電圧と比較され、高電圧が所望電圧値に到達したか否かを示す信号が電圧比較手段から出力される。以下は、第1の発明とほぼ同様であり、高電圧が所望電圧値に到達していない場合には、チャージポンプ回路の昇圧が停止手段によって停止するので、所定期間が経過した後にも、対象素子には所望電圧値に満たない高電圧は与えられず、対象素子に供給されるのは所望電圧値以上に昇圧された高電圧だけとなる。

10

#### 【0011】

第3の発明では、電源電圧の昇圧を行って高電圧を出力するチャージポンプ回路を有し、チャージポンプ回路が出力した高電圧をメモリセルに供給して書き込みを行う記憶回路とを有する装置に設けられた電圧検出回路において、次のようなスイッチ、対比用チャージポンプ回路、電圧比較手段、検出手段及び停止手段を用いて構成している。

前記スイッチは、チャージポンプ回路が昇圧を開始してから所定期間が経過するまでこのチャージポンプ回路が出力する高電圧のメモリセルへの供給を遮断するものである。対比用チャージポンプ回路は、電源電圧の昇圧を行って高電圧と対比するための対比用電圧を前記チャージポンプ回路とは独立に生成する回路である。電圧比較手段は、対比用電圧との比較でチャージポンプ回路が出力する前記高電圧が所望電圧値に到達したか否かを示す信号を出力する手段である。検出手段は、チャージポンプ回路が昇圧を開始してから所定期間が経過したときに電圧比較手段の出力信号に応答して、高電圧が所望電圧値に到達したか否かの判定信号を出力する手段である。停止手段は、判定信号が、高電圧が所望電圧値に到達していないことを示す場合にはチャージポンプ回路の昇圧を停止し、到達していることを示す場合には該昇圧を継続させる手段である。

20

#### 【0012】

このような構成を採用したことにより、第2の発明における基準電圧の代わりに、対比用チャージポンプ回路が出力する対比用電圧が高電圧と比較され、高電圧が所望電圧値に到達したか否かを示す信号が電圧比較手段から出力される。以下は、第2の発明とほぼ同様であり、高電圧が所望電圧値に到達していない場合には、チャージポンプ回路の昇圧が停止手段によって停止するので、所定期間が経過した後にも、メモリセルには所望電圧値に満たない高電圧は与えられず、メモリセルに供給されるのは所望電圧値以上に昇圧された高電圧だけとなる。

30

#### 【0013】

第4の発明では、第1、第2または第3の発明の電圧検出回路において、判定信号は、外部にモニタ用として出力するようにしている。

40

このような構成を採用したことにより、対象素子或いはメモリセルに、昇圧によって所望電圧値以上にまで高められた高電圧が供給されたか否かが、外部に出力される。

#### 【0014】

##### 【発明の実施の形態】

###### 第1の実施形態

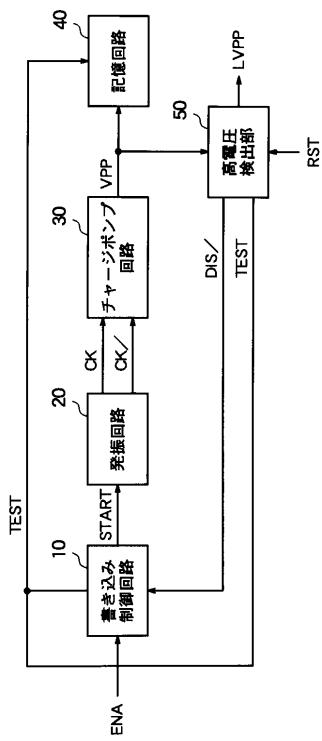

図1は、本発明の第1の実施形態を示す半導体集積装置の要部の構成図である。

この半導体集積装置は、書き込み制御回路10と、該書き込み制御回路10の出力側に接続された発振回路20と、該発振回路20の出力側に接続されたチャージポンプ回路30と、チャージポンプ回路30の出力側に接続された記憶回路40と、高電圧検出部50とを備えている。記憶回路40内には、後述するメモリセル41が配置され、書き込み制御

50

回路10、発振回路20、チャージポンプ回路30及び高電圧検出部50が書き込み回路として動作し、該チャージポンプ回路30が昇圧によって生成した高電圧VPPにより、該メモリセル41に書き込みが行われる構成になっている。さらに、書き込み制御回路10、発振回路20、チャージポンプ回路30及び高電圧検出部50には、高電圧検出回路が組み込まれ、書き込みにマージンを持つ高電圧VPPが生成されたことを検出し、そのときのみ該高電圧をメモリセル41に供給し、書き込みの成否を示すために判定信号LVPを外部に出力する構成になっている。次の図3から図7を参照しつつ、図1の各部の詳細と機能を説明する。

#### 【0015】

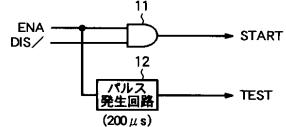

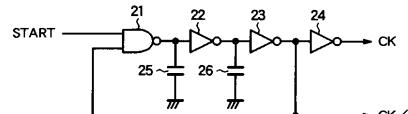

図3は、図1中の書き込み制御回路10の構成例を示す回路図であり、図4は、図1中の発振回路20の構成例を示す回路図である。図5は、図1中のチャージポンプ回路30の構成例を示す回路図であり、図6は、図1中の記憶回路40の構成例を示す回路図である。図7は、図1中の高電圧検出部50の構成例を示す回路図である。

書き込み制御回路10は、図3のように、書き込み開始を示す開始信号ENAと、後述する高電圧VPPが正常か異常を示す判定信号のうちの判定信号DIS/を入力する停止手段であるANDゲート11と、該開始信号ENAを入力し、該開始信号ENAが“H”になると1ショットのパルスを発生するパルス発生回路12とで構成されている。この書き込み制御回路10では、ANDゲート11が、開始信号ENAが“H”になったことを検出し、発振回路20に発振スタートを指示する発振指示信号STARTを“H”的有効にする。ただし、判定信号DIS/が“L”的とき、つまり高電圧VPPが異常のときには、発振指示信号STARTを“L”にして発振を停止させるように機能する。

#### 【0016】

パルス発生回路12は、開始信号ENAの立上がりをトリガとし、所定の期間の例えば200μsの間“H”となる1パルスの期間設定信号TESTを発生させる。この期間設定信号TESTは、高電圧VPPが所望の電圧値に達するまでの待ち時間を設定するための信号である。

発振回路20は、図4のように、発振指示信号STARTを一方の入力端子に入力する2入力NANDゲート21を有している。NANDゲート21の出力端子には、3段インバータ22, 23, 24が直列に接続され、該インバータ23の出力端子がNANDゲート21の他方の入力端子に帰還接続されている。また、NANDゲート21の出力端子とグランドとの間には、遅延時間設定用キャパシタ25が接続され、インバータ22の出力端子とグランドとの間には、遅延時間設定用キャパシタ26が接続されている。

#### 【0017】

この発振回路20では、発振指示信号STARTが“H”になることにより、NANDゲート21の出力が“L”となる。この“L”がキャパシタ25の容量によって時間遅延してインバータ22に与えられ、該インバータ22の出力が“H”になる。この“H”がキャパシタ26によって遅延されてインバータ23に与えられ、該インバータ23の出力が“L”になる。これにより、インバータ24の出力が“H”になるとと共にNANDゲート21の出力が“H”に遷移する。以下、同様の動作を繰り返す。同様の動作を繰り返すことにより、NANDゲート21の出力端子から入力端子に論理レベルの遷移が一巡して戻るまでの遅延時間を半周期とする発信動作を行うことになる。ここで、キャパシタ25, 26の容量を適当に選択することにより、その発振周波数も設定することが可能である。即ち、この発振回路20は、“H”的発振指示信号STARTをトリガとしてインバータ24からクロックCKを出力し、インバータ23から、それとは逆位相のクロックCK/を出力する。

#### 【0018】

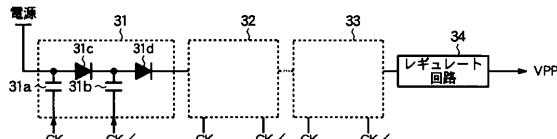

チャージポンプ回路30は、電源電圧を昇圧して高電圧VPPを生成する回路であり、図5のように、複数段に直列に接続されたポンプ31, 32, ..., 33と、レギュレート回路34とを備えている。各ポンプ31~33は共通の構成である。例えばポンプ31は、一方の電極にクロックCKが入力されたキャパシタ31aと、一方の電極にクロックC

10

20

30

40

50

K / が入力されたキャパシタ 3 1 b と、アノードが電源に接続されたダイオード 3 1 c と、該ダイオード 3 1 c のカソードにアノードが接続されたダイオード 3 1 d とで構成されている。ダイオード 3 1 c のアノードにキャパシタ 3 1 a の他方の電極が接続され、ダイオード 3 1 d のアノードにキャパシタ 3 1 b の他方の電極が接続されている。ダイオード 3 1 d のカソードがポンプ 3 1 の出力端子になっている。

#### 【0019】

レギュレート回路 3 4 は、ポンプ 3 1 ~ 3 3 で生成した高電圧 VPP の電圧値が所望の値を越えた場合にも、出力する高電圧 VPP を所望電圧値に抑える回路であり、例えばツェナーダイオードを適当数直列に接続して出力電圧値を所望電圧値にクランプするようにしてもよい。

10

このチャージポンプ回路 3 0 では、クロック CK が “H” になると、ポンプ 3 1 のキャパシタ 3 1 a がチャージされて電源電圧と加算され、これがダイオード 3 1 c の出力電圧となる。クロック CK / が “H” になると、ポンプ 3 1 のキャパシタ 3 1 b がチャージされてダイオード 3 1 c の出力電圧に加算されてダイオード 3 1 d の出力電圧となる。同様の昇圧動作をポンプ 3 2 , 3 3 が行うことにより、電源電圧を昇圧した高電圧 VPP を生成する。

#### 【0020】

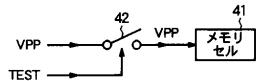

記憶回路 4 0 には、EEPROM 等の不揮発性メモリセル 4 1 が配置されている。チャージポンプ回路 3 0 で生成された高電圧 VPP を、メモリセル 4 1 に印加させることにより、メモリセル 4 1 のトランジスタの閾値を変更させてデータを記憶するようになっているが、図 6 のように、該メモリセル 4 1 は、スイッチ 4 2 を介して高電圧 VPP が印加される接続になっている。スイッチ 4 2 は、期間設定信号 T E S T が “H” のときにはオフし、高電圧 VPP のメモリセル 4 1 への供給を停止し、“L” のときに該高電圧 VPP をメモリセル 4 1 に印加する機能を有している。

20

#### 【0021】

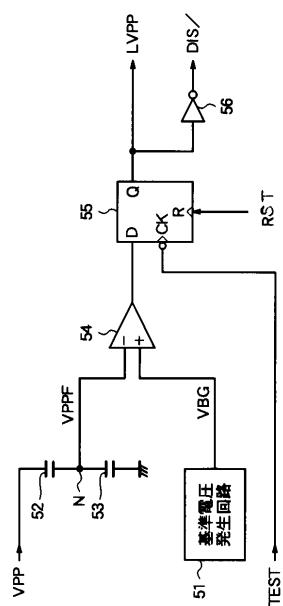

高電圧検出部 5 0 は、図 7 のように、例えばバンドギャップ基準電圧発生源等で構成された基準電圧発生回路 5 1 と、キャパシタ 5 2 , 5 3 を有している。基準電圧発生回路 5 1 は、基準電圧 VBG を発生するものである。キャパシタ 5 2 , 5 3 は、高電圧 VPP を参照用電圧 VPPF に変換するものであり、該キャパシタ 5 2 , 5 3 は、チャージポンプ回路 3 0 の出力端子とグランドとの間に直列に接続され、このキャパシタ 5 2 とキャパシタ 5 3 の接続点 N から参照用電圧 VPPF が出力されるようになっている。例えば、キャパシタ 5 2 , 5 3 の容量比を 1 : 9 とすると、参照用電圧 VPPF と高電圧 VPP の関係を  $VPPF = 1 / 10 VPP$  とすことができ、基準電圧発生回路 5 1 で発生する基準電圧 VBG を低くしても、両者の比較ができるようになる。例えば、高電圧 VPP が 20 [V] のときには参照用電圧 VPPF が 2.0 [V] となり、基準電圧 VBG を 1.2 [V] 程度に低くしても、比較が可能になる。接続点 N は、演算增幅器等で形成された電圧比較手段である電圧比較回路 5 4 の反転入力端子 ( - ) に接続されている。電圧比較回路 5 4 の非反転入力端子 ( + ) には、基準電圧発生回路 5 1 の出力端子が接続されている。

30

#### 【0022】

電圧比較回路 5 4 の出力端子は、検出手段である遅延型フリップフロップ 5 5 のデータ入力端子 D に接続されている。フリップフロップ 5 5 のクロック端子 CK には、書き込み制御回路 1 0 からの期間設定信号 T E S T が入力され、リセット端子 R には、外部からのリセット信号 RST が入力される構成になっている。フリップフロップ 5 5 は、電圧比較回路 5 4 の出力信号をラッチし、これを 1 つの判定信号 LVP として出力するものである。フリップフロップ 5 5 のデータ出力端子 Q には、さらに、インバータ 5 6 が接続され、判定信号 LVP のレベルを反転した前記判定信号 DIS / も出力する構成になっている。

40

この高電圧検出部 5 0 では、参照用電圧 VPPF が基準電圧 VBG の電圧レベルよりも高いと、電圧比較回路 5 4 が “L” を出力し、逆の関係の場合には “H” を出力する。例えば、基準電圧 VBG が 1.2 [V] の場合に、参照電圧 VPPF が 1.2 [V] よりも低

50

いとき、つまり高電圧VPPが所望電圧値の12[V]よりも低いときに、電圧比較回路54が“H”を出力する。

#### 【0023】

フリップフロップ55は、期間設定信号TESTの立下がりに同期して電圧比較回路54の出力信号をラッチする。もし、参照用電圧VPPFが基準電圧VBGよりも低いときには、フリップフロップ55は“H”をラッチし、この“H”を判定信号LVPPIとして出力する。よって、判定信号LVPPIが“H”的ときは、高電圧VPPが所望電圧値になつていいないことを示す。このときインバータ56から出力される判定信号DIS/は、“L”になる。逆に、高電圧VPPが所望電圧値になっているときには、判定信号LVPPIが“L”、判定信号DIS/が“H”になる。10

#### 【0024】

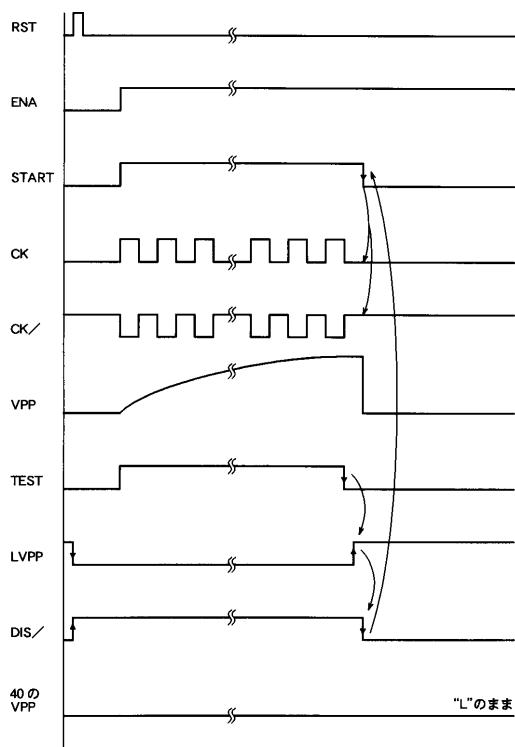

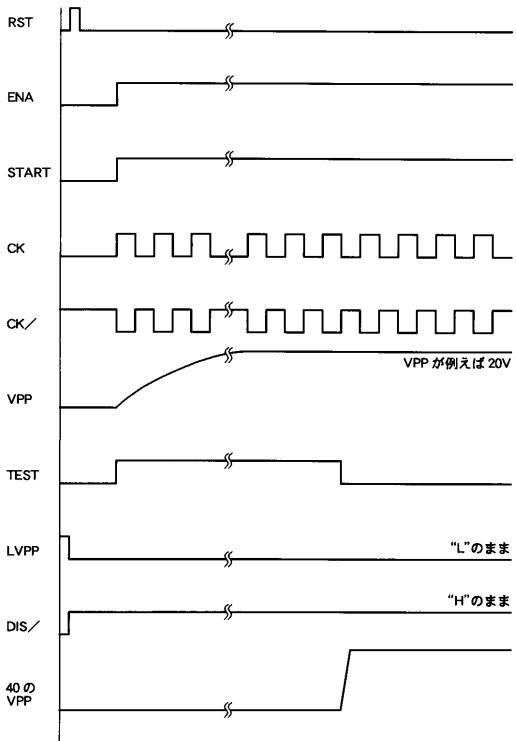

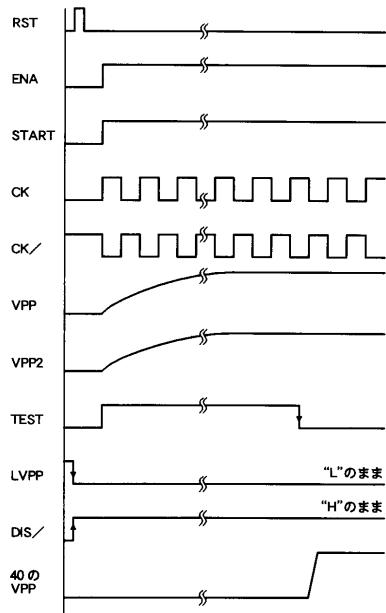

図8は、図1の動作波形(その1)を示すタイムチャートであり、図9は、図1の動作波形(その2)を示すタイムチャートである。これらの図8及び図9を参照しつつ、図1の半導体集積装置の動作を説明する。

まず、高電圧VPPが所望電圧値に昇圧されない場合の動作を説明する。

図8のように、外部からパルス状のリセット信号RSTを与えると、フリップフロップ55がリセットされ、それまでの状態にかかわらず、強制的に判定信号LVPPIが“L”となり、判定信号DIS/が“H”になる。

この状態で、書き込み開始を指示する書き込み開始信号ENAを有効の“H”にすると、これをトリガとし、書き込み制御回路10が例えば200μsの間が“H”となる1パルスの期間設定信号TESTを発生すると共に、“H”に有効化された発振指示信号STARTを発振回路20に与える。20

“H”的発振指示信号STARTが与えられた発振回路20は、発振を開始し、互いに逆相のクロックCK, CK/を発生する。チャージポンプ回路30は、そのクロックCK, CK/を用いて電源電圧を昇圧していく。このとき“H”的期間設定信号TESTが与えられた記憶回路40のスイッチ42は、オフ状態である。

#### 【0025】

200μsが経過し、期間設定信号TESTが“H”から“L”に立下がると、これに同期して高電圧検出部50中のフリップフロップ55が、電圧比較回路54の比較結果をラッチする。チャージポンプ回路30の高電圧VPPが所望電圧値に昇圧されていない場合には、フリップフロップ55が“H”をラッチする。この結果、判別信号LVPPIのレベルが“H”に、判別信号DIS/のレベルが“L”にそれぞれ遷移する。判別信号LVPPIは外部に出力され、この判別信号LVPPIがモニタされ、書き込みに異常があったか否か提示される。30

一方、“L”的判別信号DIS/は、書き込み制御回路10のANDゲート11に入力され、発振指示信号STARTが“L”になる。発振指示信号STARTが“L”になることにより、発振回路20の発振が停止し、チャージポンプ回路30における昇圧が停止する。よって、期間設定信号TESTが“L”になってスイッチ42がオンしても、記憶回路40中のメモリセル41には所望電圧値に昇圧されていない高電圧VPPが印加されるだけなので、書き込みが行われない。40

#### 【0026】

次に、高電圧VPPが所望電圧値に昇圧される場合の動作を説明する。

図9のように、リセット信号RSTを与え、さらに開始信号ENAを“H”にすると、書き込み制御回路10、発振回路20及びチャージポンプ回路30が前述と同様に動作し、チャージポンプ回路30が高電圧VPPを出力する。高電圧検出部50は、参照用電圧VPPFが基準電圧VBGよりも高い場合に、フリップフロップ55が期間設定信号TESTが“L”になったときに“L”をラッチし、判定信号LVPPI及び判定信号DIS/のレベルがそれぞれ“L”及び“H”に維持されて変化しない。よって、各書き込み制御回路10、発振回路20及びチャージポンプ回路30の動作は継続され、記憶回路40では、スイッチ42を介してメモリセル41に、所望電圧値に昇圧された高電圧VPPが印加50

され、書き込みが行われる。

#### 【0027】

以上のように、この第1の実施形態では、記憶回路40に設けられ、期間設定信号T E S Tで設定される期間にメモリセル41への高電圧V P Pの供給を停止するスイッチ42と、高電圧検出部50中の基準電圧発生回路51、電圧比較回路54、フリップフロップ55及びインバータ56とで電圧検出回路を形成し、高電圧V P Pが所望電圧値に昇圧されたかどうかを判定して判定信号L V P Pを外部に出力すると共に、その高電圧V P Pが所望電圧値になつてない場合には、判定信号D I S /に基づき発振指示信号S T A R Tを“L”にすることにより、発振回路20の発振を止めてチャージポンプ回路30の昇圧を停止するようにしている。そのため、高電圧V P Pが所望電圧値になつてない場合には書き込みを行わず、その情報が外部でモニタ可能になっているので、一々、メモリセル41のデータを確認する必要がない。10

その上、基準電圧発生回路51の発生する基準電圧V B Gをマージンを持つ適切な値にすれば、誤った書き込みを行う等の問題を起こさない。つまり、高電圧V P Pが中途半端な電圧で、ピットによって書き込みが行われたり、行われなかつたりしてデータが破壊されることが防止される。

#### 【0028】

さらに、高電圧V P Pが所望電圧値になつてない場合には、判別信号L V P Pにより、外部に出力されてモニタできるので、例えば、故意に第3者が高電圧V P Pを下げて不揮発性メモリに書き込みができないようにした場合でも、判別信号L V P PをC P U(中央処理装置)のリセット入力とすれば、リセットさせる等の対策を打つことができる。20

#### 【0029】

##### 第2の実施形態

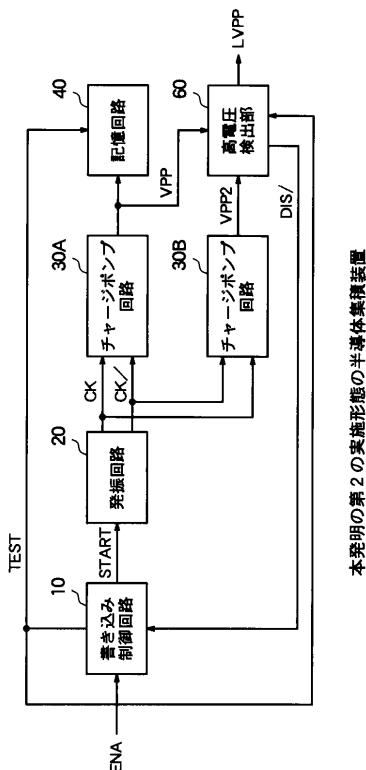

図10は、本発明の第2の実施形態を示す半導体集積装置の構成図であり、第1の実施形態を示す図1中の要素と共に通の要素には共通の符号が付されている。この半導体集積装置は、第1の実施形態と同様の書き込み制御回路10と発振回路20とを有している。発振回路20の出力側には、第1の実施形態とは異なり、チャージポンプ回路30Aと対比用チャージポンプ回路30Bの2つのチャージポンプ回路が接続されている。チャージポンプ30Aの出力側が第1の実施形態と同様の記憶回路40に接続されている。この半導体集積装置には、さらに、第1の実施形態とは異なる高電圧検出部60が設けられ、該高電圧検出部60に、チャージポンプ回路30A, 30Bの出力端子が接続されている。30

#### 【0030】

チャージポンプ回路30A, 30Bは、図5のようにポンプを複数段に接続することによって構成されているが、その段数が異なる。接続段数によって電源電圧を昇圧した電圧のレベルが違ってくる。例えば、5段に接続すると12[V]になり、10段に接続すると20[V]になる。チャージポンプ回路30Aは、10段に図5のポンプ31~33を接続し、記憶回路40における書き込みに必要な20[V]の高電圧V P Pを出力するようになっている。これに対し、チャージポンプ回路30Bは、チャージポンプ回路30Aの高電圧V P Pと電圧比較するための対比用電圧V P P2を昇圧で生成できればよいので、例えば5段に図5のポンプ31~33が接続されている。40

#### 【0031】

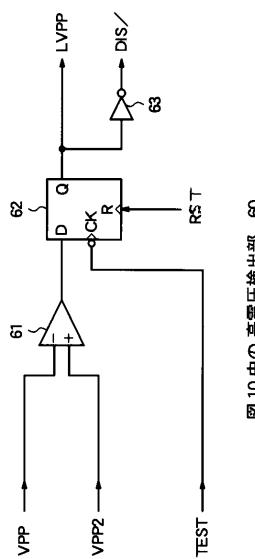

図11は、図10中の高電圧検出部60の構成例を示す回路図である。

この高電圧検出部60は、演算増幅器等で構成された電圧比較手段である電圧比較回路61と、検出手段である遅延型フリップフロップ62とインバータ63とで構成されている。

電圧比較回路61の反転入力端子(-)にはチャージポンプ回路30Aからの高電圧V P Pが入力され、該電圧比較回路61の非反転入力端子(+)には、チャージポンプ回路30Bからの対比用電圧V P P2が入力されるようになっている。電圧比較回路61の出力端子は、フリップフロップ62のデータ入力端子Dに接続されている。フリップフロップ62のクロック端子c kには、書き込み制御回路10から期間設定信号T E S Tが入力さ50

れ、該フリップフロップ 6 2 のリセット端子 R には、外部からリセット信号 R S T が入力されるようになっている。フリップフロップ 6 2 のデータ出力端子 Q には、インバータ 6 3 が接続され、第 1 の実施形態と同様に、判別信号 L V P P とそれとは逆相の判別信号 D I S / の両方を出力する構成になっている。

#### 【 0 0 3 2 】

この高電圧検出部 6 0 では、高電圧 V P P が対比用電圧 V P P 2 よりも大きければ、電圧比較回路 6 1 が “ L ” を出力し、それ以外の場合には “ H ” を出力する。そのため、昇圧が正常で高電圧 V P P が対比用電圧 V P P 2 よりも大きいときには、判別信号 L V P P が “ L ” 、判別信号 D I S / が “ H ” をそれぞれ継続する。昇圧が異常で、高電圧 V P P が対比用電圧 V P P 2 と等しいかまたは該対比用電圧 V P P 2 よりも低ければ、期間設定信号 T E S T が立下がったときに、判定信号 L V P P が “ H ” に、判定信号 D I S / が “ L ” にそれぞれ遷移する。10

#### 【 0 0 3 3 】

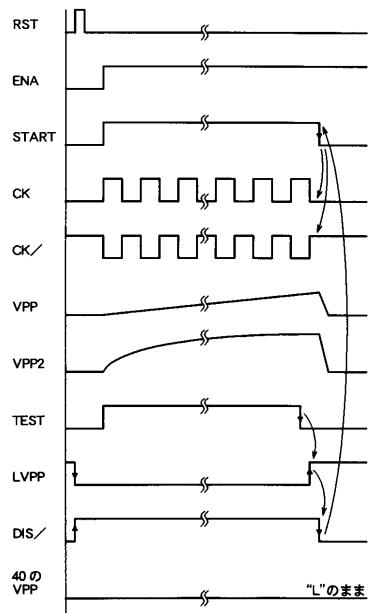

図 1 2 は、図 1 0 の動作波形（その 1）を示すタイムチャートであり、図 1 3 は、図 1 0 の動作波形（その 2）を示すタイムチャートである。これらの図 1 2 及び図 1 3 を参照しつつ、図 1 0 の半導体集積装置の動作を説明する。

まず、チャージポンプ回路 3 0 A の昇圧で生成される高電圧 V P P が所望電圧値にならず、対比用電圧 V P P 2 より低くなる場合の動作を説明する。

図 1 2 のように、外部からパルス状のリセット信号 R S T を与えると、フリップフロップ 6 2 がリセットされ、それまでの状態にかかわらず、強制的に判定信号 L V P P が “ L ” となり、判定信号 D I S / が “ H ” になる。20

この状態で、書き込み開始を指示する書き込み開始信号 E N A を有効の “ H ” にすると、これをトリガとし、書き込み制御回路 1 0 が例えば 2 0 0  $\mu$  s の間が “ H ” となる 1 パルスの期間設定信号 T E S T を発生すると共に、“ H ” に有効化された発振指示信号 S T A R T を発振回路 2 0 に与える。“ H ” の期間設定信号 T E S T が与えられた記憶回路 4 0 のスイッチ 4 2 は、オフ状態になる。

“ H ” の発振指示信号 S T A R T が与えられた発振回路 2 0 は、発振を開始し、互いに逆相のクロック C K , C K / を発生する。ここまで動作は、第 1 の実施形態と同様である。30

#### 【 0 0 3 4 】

クロック C K , C K / が与えられたチャージポンプ回路 3 0 A , 3 0 B は、該クロック C K , C K / を用いて電源電圧に対する昇圧を独立して行う。ここで、昇圧が正常に行われた場合には、高電圧 V P P が対比用電圧 V P P 2 よりも高くなるが、何等かの理由で高電圧 V P P が所望電圧値にならず、例えば 1 0 [ V ] になったとする。これに対し、対比用電圧 V P P 2 は正常であり、1 2 [ V ] であるとする。高電圧 V P P と対比用電圧 V P P 2 とは、電圧比較回路 6 1 に入力されて比較される。電圧比較回路 6 1 は、“ H ” の信号を出力してフリップフロップ 6 2 に与える。フリップフロップ 6 2 は、期間設定信号 T E S T の立下がりに同期して、電圧比較回路 6 1 が出力する “ H ” の信号をラッチし、これを判定信号 L V P P として外部へ出力する。このときインバータ 6 3 が出力する判定信号 D I S / は “ L ” となり、書き込み制御回路 1 0 に与えられる。書き込み制御回路 1 0 及び発振回路 2 0 は、第 1 の実施形態と同様に動作し、該発振回路 2 0 の発振が停止し、チャージポンプ回路 3 0 A , 3 0 B の昇圧が停止する。よって、記憶回路 4 0 中のメモリセル 4 1 には書き込みが行われない。40

#### 【 0 0 3 5 】

次に、高電圧 V P P が所望電圧値に昇圧される場合の動作を説明する。

図 1 3 のように、リセット信号 R S T を与え、さらに開始信号 E N A を “ H ” にすると、書き込み制御回路 1 0 、発振回路 2 0 及びチャージポンプ回路 3 0 A , 3 0 B が前述と同様に動作する。チャージポンプ回路 3 0 A が例えば 2 0 [ V ] の高電圧 V P P を出力し、チャージポンプ回路 3 0 B が 1 2 [ V ] の対比用電圧 V P P 2 を出力する。このときには、電圧比較回路 6 1 が “ L ” を出力する。よって、期間設定信号 T E S T が立下がってフ50

リップフロップ 6 2 がラッチしたときに、判定信号 L V P P 及び D I S / が、“ L ”及び“ H ”を保つ。そのため、記憶回路 4 0 中のメモリセル 4 1 には、スイッチ 4 2 を介して正常な所望電圧値の高電圧 V P P が与えられて書き込みが行われる。

#### 【 0 0 3 6 】

以上のように、この第 2 の実施形態では、チャージポンプ回路 3 0 A とチャージポンプ回路 3 0 B とを設け、基準電圧 V B G を用いずに、チャージポンプ回路 3 0 B で生成した対比用電圧 V P P 2 を用いて高電圧 V P P が正常化かどうかを判定し、正常で所望電圧値になるときだけに書き込みが行える構成とし、高電圧 V P P が正常でないときには判定信号 L V P P でそれを示すようにしたので、第 1 の実施形態と同様に、高電圧 V P P が所望電圧になつてない場合には書き込みを行わず、その情報を示す判定信号 L V P P を外部でモニタすることにより、メモリセル 4 1 のデータを確認する必要がない。さらに、同様の構成のチャージポンプ回路 3 0 A , 3 0 B を用意するだけでよいので、基準電圧 V B G を精度よく発生する基準電圧発生回路 5 1 等が不要となり、構成が第 1 の実施形態よりも簡単にできる。

#### 【 0 0 3 7 】

なお、本発明は、上記実施形態に限定されず種々の変形が可能である。

例えば、第 1 及び第 2 の実施形態では、高電圧 V P P によって書き込みが行える不揮発性メモリの記憶回路 4 0 を持つ半導体記憶装置に適した電圧検出回路を説明したが、高電圧 V P P が必要な他の対象素子を持つ半導体集積装置にも適用が可能である。この場合には、対象素子に不完全な高電圧 V P P が供給されないので、誤動作等が防止できる等の効果が得られる。

#### 【 0 0 3 8 】

##### 【発明の効果】

以上詳細に説明したように、第 1 の発明によれば、所定期間が経過するまで高電圧のメモリセルへの供給を遮断するスイッチと、基準電圧発生回路と、基準電圧との比較で高電圧が所望電圧値に到達したか否かを示す信号を出力する電圧比較手段と、検出手段と、高電圧が所望電圧値に到達していない場合には発振回路の発振動作を停止し、到達している場合に発振動作を継続させる停止手段とで構成した電圧検出回路を、発振回路の出力信号に基づき電源電圧の昇圧を行って高電圧を出力するチャージポンプ回路からその高電圧をメモリセルに供給して書き込みを行う装置に設けたので、基準電圧を適切な値にすれば、メモリセルへは所望電圧値に満たない高電圧が供給されなくなり、誤った書き込みを行う等の問題を起こさない。特に、チャージポンプ回路の出力電圧が所望電圧値に到達していない場合、記憶回路へ出力される信号の発生源である発振回路の発振動作自体を停止させて、記憶回路への書き込み動作を高精度で抑制することが可能となり、これにより、記憶回路への書き込み動作の信頼性を大幅に向上させることが可能となる。

#### 【 0 0 3 9 】

第 2 の発明によれば、第 1 の発明におけるメモリセルに代えて高電圧を対象素子に供給すると共に、基準電圧発生回路に代えて対比用チャージポンプ回路を設けたので、簡単な構成で第 1 の発明とほぼ同様の効果を奏する電圧検出回路を実現できる。

#### 【 0 0 4 0 】

第 3 の発明によれば、第 1 の発明における基準電圧発生回路の代わりに、対比用チャージポンプ回路を設けたので、簡単な構成で第 1 の発明と同様の効果を奏する電圧検出回路を実現できる。

第 4 の発明によれば、第 1 、第 2 または第 3 の発明において、判定信号を外部にモニタ用に出力する構成にしたので、対象素子やメモリセルに所望電圧値の高電圧が供給されたか供給されなかつたかが、外部に知らされる。そのため、例えば、メモリセルの書き込み状態を確認する必要がなくなる。また、例えば、故意に第 3 者が高電圧を下げて不揮発性メモリに書き込みができないようにした場合等でも、判別信号を C P U のリセット入力とすれば、リセットさせる等の対策を打つこともできる。

#### 【図面の簡単な説明】

10

20

30

40

50

- 【図1】本発明の第1の実施形態を示す半導体集積装置の構成図である。

- 【図2】従来の一般的な不揮発性メモリの書き込み回路を示す構成図である。

- 【図3】図1中の書き込み制御回路10の構成例を示す回路図である。

- 【図4】図1中の発振回路20の構成例を示す回路図である。

- 【図5】図1中のチャージポンプ回路30の構成例を示す回路図である。

- 【図6】図1中の記憶回路40の構成例を示す回路図である。

- 【図7】図1中の高電圧検出部50の構成例を示す回路図である。

- 【図8】図1の動作波形(その1)を示すタイムチャートである。

- 【図9】図1の動作波形(その2)を示すタイムチャートである。

- 【図10】本発明の第2の実施形態を示す半導体集積装置の構成図である。

- 【図11】図10中の高電圧検出部60の構成例を示す回路図である。

- 【図12】図10の動作波形(その1)を示すタイムチャートである。

- 【図13】図10の動作波形(その2)を示すタイムチャートである。

## 【符号の説明】

|            |              |    |

|------------|--------------|----|

| 10         | 書き込み制御回路     |    |

| 12         | 期間設定用パルス発生回路 |    |

| 20         | 発振回路         |    |

| 30, 30A    | チャージポンプ回路    | 10 |

| 30B        | 対比用チャージポンプ回路 |    |

| 31~33      | ポンプ          | 20 |

| 40         | 記憶回路         |    |

| 41         | メモリセル        |    |

| 42         | スイッチ         |    |

| 50, 60     | 高電圧検出部       |    |

| 51         | 基準電圧発生回路     |    |

| 54, 61     | 電圧比較回路       |    |

| 55, 62     | 遅延型フリップフロップ  |    |

| 56, 63     | インバータ        |    |

| VPP        | 高電圧          |    |

| VPP2       | 対比用電圧        | 30 |

| VBG        | 基準電圧         |    |

| START      | 発振指示信号       |    |

| TEST       | 期間設定信号       |    |

| CK, CK/    | クロック         |    |

| LVPP, DIS/ | 判定信号         |    |

【図1】

本発明の第1の実施形態の半導体集積装置

【図2】

一般的な不揮発性メモリの書き込み回路

【図3】

図1中の書き込み制御回路10

【図4】

図1中の発振回路20

【図7】

図1中の高電圧検出部50

【図5】

図1中のチャージポンプ回路30

【図6】

図1中の記憶回路40

【図 8】

図1の動作波形(その1)

【図 9】

図1の動作波形(その2)

【図 10】

本発明の第2の実施形態の半導体検査装置

【図 11】

図10中の高電圧検出部 60

【図 1 2】

図 10 の動作波形(その 1)

【図 1 3】

図 10 の動作波形(その 2)

---

フロントページの続き

(56)参考文献 特開平06-203584(JP,A)

特開平11-095849(JP,A)

特開平10-208489(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G11C 16/00-16/34

G06F 12/16