(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2011-0132598

(43) 공개일자 2011년12월08일

(51) Int. Cl.

*H04L 1/06* (2006.01) *H03M 13/27* (2006.01)

*H04B 7/04* (2006.01) *H04J 11/00* (2006.01)

(21) 출원번호 10-2011-7024345

(22) 출원일자(국제출원일자) 2010년03월16일

심사청구일자 없음

(85) 번역문제출일자 2011년10월14일

(86) 국제출원번호 PCT/US2010/027461

(87) 국제공개번호 WO 2010/107779

국제공개일자 2010년09월23일

(30) 우선권주장

61/160,594 2009년03월16일 미국(US)

(뒷면에 계속)

(71) 출원인

인터넷디지탈 패튼 홀딩스, 인크

미국 렐라웨어 19810 월밍턴 실버사이드 로드

3411 콩코드 플라자 스위트 105 해글리 빌딩

(72) 발명자

벨루리 미하엘라 씨

미국 뉴욕주 11743 헨팅턴 웨스트 넥 로드 239

장 구동미국 뉴욕주 11791 싸이오셋 월넛 드라이브 14

(뒷면에 계속)

(74) 대리인

신정건, 김태홍

전체 청구항 수 : 총 20 항

(54) 반송파 집적 및 클러스터된 D F T를 갖는 업링크 M I M O용 데이터 및 제어 다중화

**(57) 요 약**

본 발명은 무선 송수신 유닛(WTRU)에서의 신호 처리를 위한 방법 및 장치에 관한 것으로서, 복수의 데이터 비트 및 복수의 제어 비트를 생성하고, 상기 데이터 비트 및 제어 비트를 하나 이상의 코드워드로 매핑하며, 상기 데이터 비트 및 제어 비트를 다중화하고, 상기 비트들을 계층으로 분할하여, 각각의 코드워드의 채널 품질 및 각각의 계층의 채널 품질에 기초하여 상기 제어 비트를 각각의 계층에 할당하고, 하나 이상의 안테나로의 출력을 위해 각각의 계층을 채널 인터리빙하는 것을 포함한다.

**대 표 도**

(72) 발명자

피트라스키 필립 제이

미국 뉴욕주 11746 헌팅턴 스테이션 탈봇 플레이스

7

신 성혁

미국 뉴저지주 07647 노스베일 이드너 웨이 104

발라 어덤

미국 뉴욕주 11735 파밍데일 아파트먼트 12비 세카

도그 에비뉴 150

판 카일 정-린

미국 뉴욕주 11787 스미스타운 아발론 셔클 43

구 창수

미국 뉴욕주 11747 멜빌 알테사 볼르바르 281

스턴버코비츠 자넷 에이

미국 뉴욕주 11363 리틀 넥 글렌우드 스트리트

41-20

(30) 우선권주장

61/160,599 2009년03월16일 미국(US)

61/304,376 2010년02월12일 미국(US)

## 특허청구의 범위

### 청구항 1

무선 송수신 유닛(WTRU; wireless transmit receive unit)의 신호 처리 방법에 있어서,

복수의 데이터 비트를 생성하고;

복수의 제어 비트를 생성하고;

복수의 다중화된 비트를 생성하기 위해, 상기 제어 비트를 상기 데이터 비트와 다중화하고;

제어 비트를 포함하는 적어도 하나의 논리적 계층에 상기 다중화된 비트를 할당하고;

각각의 논리적 계층을 복수의 인터리빙된 계층 - 각각의 인터리빙된 계층은 적어도 하나의 안테나에 대응함 -

으로 인터리빙하며;

각각의 인터리빙된 계층을 대응하는 안테나에서 송신하는 것

을 포함하는 무선 송수신 유닛의 신호 처리 방법.

### 청구항 2

제1항에 있어서,

채널 품질 파라미터에 기초하여, 상기 복수의 제어 비트를 상기 복수의 계층 사이에 할당하는 것을 더 포함하는

무선 송수신 유닛의 신호 처리 방법.

### 청구항 3

제1항에 있어서,

복수의 논리적 계층 각각이 상기 복수의 제어 비트 모두를 포함하도록, 상기 다중화된 비트를 상기 복수의 논리

적 계층에 할당하는 것을 더 포함하는 무선 송수신 유닛의 신호 처리 방법.

### 청구항 4

제1항에 있어서,

복수의 데이터 비트/코드워드 매핑을 생성하기 위해, 복수의 코드워드로 매핑된 복수의 데이터 비트를

생성하고;

각각의 데이터 비트/코드워드 매핑에 대하여 채널 품질을 결정하며;

상기 채널 품질에 기초하여, 제어 비트를 각각의 데이터 비트/코드워드 매핑에 할당하는 것을 더 포함하는 무선

송수신 유닛의 신호 처리 방법.

### 청구항 5

제1항에 있어서,

복수의 데이터 비트/코드워드 매핑을 생성하기 위해, 복수의 코드워드로 매핑된 복수의 데이터 비트를

생성하고;

모든 제어 비트를 각각의 데이터 비트/코드워드 매핑에 할당하는 것을 더 포함하는 무선 송수신 유닛의 신호

처리 방법.

### 청구항 6

제4항에 있어서,

각각의 논리적 계층에 대하여 채널 품질을 결정하고;

상기 각각의 논리적 계층의 상기 채널 품질에 기초하여, 제어 비트를 상기 각각의 논리적 계층에 할당하는 것을

더 포함하는 무선 송수신 유닛의 신호 처리 방법.

#### 청구항 7

무선 송수신 유닛(WTRU)의 신호 처리 방법에 있어서,

복수의 코드워드로 매핑된 복수의 데이터 비트를 생성하고;

각각의 코드워드에 대하여 채널 품질 메트릭(metric)에 기초하여, 상기 복수의 코드워드로 매핑된 복수의 제어 비트를 생성하고;

각각의 계층에 대하여 상기 채널 품질 메트릭에 기초하여, 상기 복수의 코드워드로 매핑된 상기 제어 비트를 복수의 논리적 계층에 할당하고;

각각의 논리적 계층을 복수의 인터리빙된 계층 - 각각의 인터리빙된 계층은 적어도 하나의 안테나에 대응함 - 으로 인터리빙하며;

각각의 인터리빙된 계층을 대응하는 안테나에서 송신하는 것

을 포함하는 무선 송수신 유닛의 신호 처리 방법.

#### 청구항 8

제7항에 있어서,

상기 채널 품질 메트릭은 변조 및 코드화 기법(MCS; Modulation and Coding Scheme)인 것인, 무선 송수신 유닛의 신호 처리 방법.

#### 청구항 9

제7항에 있어서,

상기 채널 품질 메트릭은 신호 및 간섭대 잡음비(SINR; Signal and Interference to Noise Ratio)인 것인, 무선 송수신 유닛의 신호 처리 방법.

#### 청구항 10

제7항에 있어서,

제1 다중 입력/다중 출력(MIMO; Multiple Input/Multiple Output) 코드화 기법에 따라 상기 제어 비트를 코드화하고, 제2 MIMO 코드화 기법에 따라 상기 데이터 비트를 코드화하는 것을 더 포함하는 무선 송수신 유닛의 신호 처리 방법.

#### 청구항 11

업링크(UL) 신호를 처리하도록 구성된 무선 송수신 유닛(WTRU)에 있어서,

복수의 다중화된 비트를 생성하기 위해, 제어 비트를 데이터 비트와 다중화하도록 구성된 데이터 및 제어 다중화기;

복수의 데이터 비트 및 복수의 제어 비트를 생성하고, 제어 비트를 포함하는 적어도 하나의 논리적 계층에 상기 다중화된 비트를 할당하도록 구성된 프로세서;

적어도 하나의 안테나;

각각의 논리적 계층을 복수의 인터리빙된 계층 - 각각의 인터리빙된 계층은 적어도 하나의 안테나에 대응함 - 으로 인터리빙하도록 구성된 채널 인터리버(channel interleaver); 및

각각의 인터리빙된 계층을 대응하는 안테나에서 송신하도록 구성된 송신기

를 포함하는 무선 송수신 유닛.

#### 청구항 12

제11항에 있어서,

상기 프로세서는 또한, 채널 품질 파라미터에 기초하여, 상기 복수의 제어 비트를 상기 복수의 계층 사이에 할당하도록 구성되는 것인, 무선 송수신 유닛.

### 청구항 13

제11항에 있어서,

상기 프로세서는 또한, 복수의 논리적 계층 각각이 상기 복수의 제어 비트 모두를 포함하도록, 상기 다중화된 비트를 상기 복수의 논리적 계층에 할당하도록 구성되는 것인, 무선 송수신 유닛.

### 청구항 14

제11항에 있어서,

상기 프로세서는 또한,

복수의 데이터 비트/코드워드 매핑을 생성하기 위해, 복수의 코드워드로 매핑된 복수의 데이터 비트를 생성하고,

각각의 데이터 비트/코드워드 매핑에 대하여 채널 품질을 결정하며,

상기 채널 품질에 기초하여, 제어 비트를 각각의 데이터 비트/코드워드 매핑에 할당하도록 구성되는 것인, 무선 송수신 유닛.

### 청구항 15

제11항에 있어서,

상기 프로세서는 또한,

복수의 데이터 비트/코드워드 매핑을 생성하기 위해, 복수의 코드워드로 매핑된 복수의 데이터 비트를 생성하고,

모든 제어 비트를 각각의 데이터 비트/코드워드 매핑에 할당하도록 구성되는 것인, 무선 송수신 유닛.

### 청구항 16

제14항에 있어서,

상기 프로세서는 또한,

각각의 논리적 계층에 대하여 채널 품질을 결정하고,

상기 각각의 논리적 계층의 상기 채널 품질에 기초하여, 제어 비트를 상기 각각의 논리적 계층에 할당하도록 구성되는 것인, 무선 송수신 유닛.

### 청구항 17

업링크(UL) 신호의 신호 처리를 수행하도록 구성된 무선 송수신 유닛(WTRU)에 있어서,

복수의 코드워드로 매핑된 복수의 데이터 비트를 생성하고, 각각의 코드워드에 대하여 채널 품질 메트릭에 기초하여, 상기 복수의 코드워드로 매핑된 복수의 제어 비트를 생성하며, 각각의 계층에 대하여 상기 채널 품질 메트릭에 기초하여, 상기 복수의 코드워드로 매핑된 상기 제어 비트를 복수의 논리적 계층에 할당하도록 구성된 프로세서;

적어도 하나의 안테나;

각각의 논리적 계층을 복수의 인터리빙된 계층 - 각각의 인터리빙된 계층은 적어도 하나의 안테나에 대응함 - 으로 인터리빙하도록 구성된 채널 인터리버; 및

각각의 인터리빙된 계층을 대응하는 안테나에서 송신하도록 구성된 송신기

를 포함하는 무선 송수신 유닛.

**청구항 18**

제17항에 있어서,

상기 채널 품질 메트릭은 MCS인 것인, 무선 송수신 유닛.

**청구항 19**

제7항에 있어서,

상기 채널 품질 메트릭은 SINR인 것인, 무선 송수신 유닛.

**청구항 20**

제17항에 있어서,

상기 프로세서는 또한, 제1 MIMO 코드화 기법에 따라 상기 제어 비트를 코드화하고, 제2 MIMO 코드화 기법에 따라 상기 데이터 비트를 코드화하도록 구성되는 것인, 무선 송수신 유닛.

**명세서****기술분야**

[0001]

관련 출원의 교차 참조

[0002]

본 출원은 2009년 3월 16일 출원된 미국 가출원 제61/160,594호, 2009년 3월 16일 출원된 미국 가출원 제61/160,599호 및 2010년 2월 12일 출원된 미국 가출원 제61/304,376호의 우선권을 주장하며, 이들 문헌의 개시 내용은 참조로서 본 명세서에 포함된다.

[0003]

기술분야

[0004]

본 발명은 무선 통신에 관한 것이다.

**배경기술**

[0005]

무선 통신 시스템은 처리량 및 사용자 서비스를 증가시키기 위해 많은 기술을 사용할 수 있다. 이러한 하나의 기술이 반송파 집적(carrier aggregation)이다. 다른 기술은 유연한 대역폭의 지원이다. 또 다른 기술은 업링크 데이터 및 제어 채널을 동시에 송신하는 것이다. 예를 들어, LTE-A(Advanced Long Term Evolution) 호환 시스템에서, 물리적 업링크 공유 채널(PUSCH) 및 물리적 업링크 제어 채널(PUCCH)과 같은 업링크(UL) 채널은 동시에 송신될 수 있다.

[0006]

또 다른 기술은, 예를 들어, 업링크(UL) 통신에서 송신 다이버시티 및 공간 다이버시티와 같은 다중 입력/다중 출력(MIMO) 구성을 사용하는 것을 포함한다. MIMO가 업링크(UL) 통신에서 사용된다면, 데이터 비트 및 제어 비트의 처리는 복잡하게 될 수 있다.

**발명의 내용****해결하려는 과제**

[0007]

본 발명은 MIMO용 데이터 비트 및 제어 비트의 다중화를 목적으로 한다.

**과제의 해결 수단**

[0008]

무선 송수신 유닛(WTRU)에서 신호를 처리하기 위한 방법 및 장치가 개시된다. 이는 복수의 데이터 비트 및 복수의 제어 비트를 생성하는 것을 포함한다. 데이터 비트 및 제어 비트는 하나 이상의 코드워드(codeword)로 매핑될 수 있다. 데이터 비트 및 제어 비트는 다중화될 수 있다. 데이터 비트 및 제어 비트는 계층(layer)으로 분할될 수 있다. 제어 비트는 각각의 코드워드의 채널 품질 및 각각의 계층의 채널 품질에 기초하여 계층에 할당될 수 있다. 각각의 계층은 채널 인터리빙되어 하나 이상의 안테나로 출력될 수 있다.

**발명의 효과**

[0009] 본 발명에 따르면, MIMO 코드화 기법으로 데이터 비트 및 제어 비트의 다중화하는 것을 가능하게 한다.

### 도면의 간단한 설명

[0010] 첨부된 도면과 관련하여 실시예로서 다음의 설명으로부터 보다 자세히 이해될 수 있다.

도 1은 발전된 UMTS(Universal Mobile Telecommunication System) 지상 무선 접속 네트워크(E-UTRAN)의 개략도를 나타낸다.

도 2는 복수의 무선 송수신 유닛(WTRU) 및 하나의 e 노드 B(eNB)를 포함하는 무선 통신 시스템을 나타낸다.

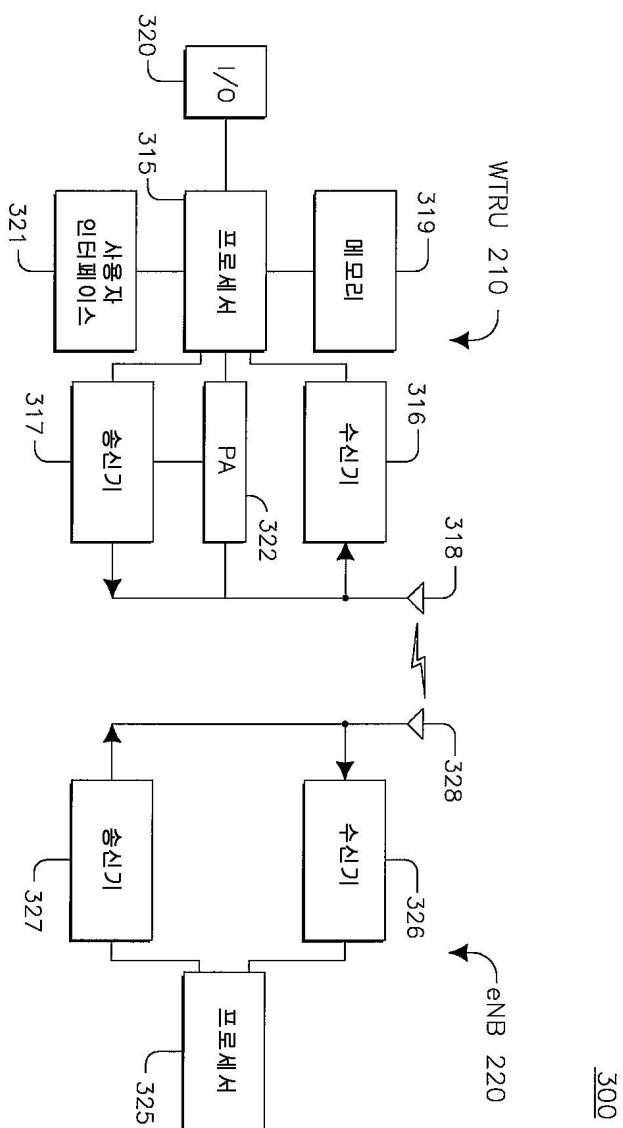

도 3은 도 2의 무선 통신 시스템의 WTRU 및 eNB의 기능적인 블록도이다.

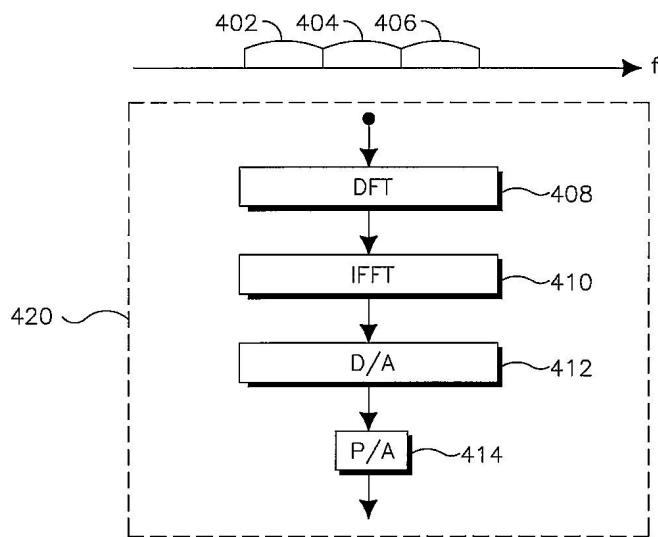

도 4는 일 실시예에 따른 연속 반송파를 갖는 반송파 집적을 사용하는 무선 통신 시스템의 개략도를 나타낸다.

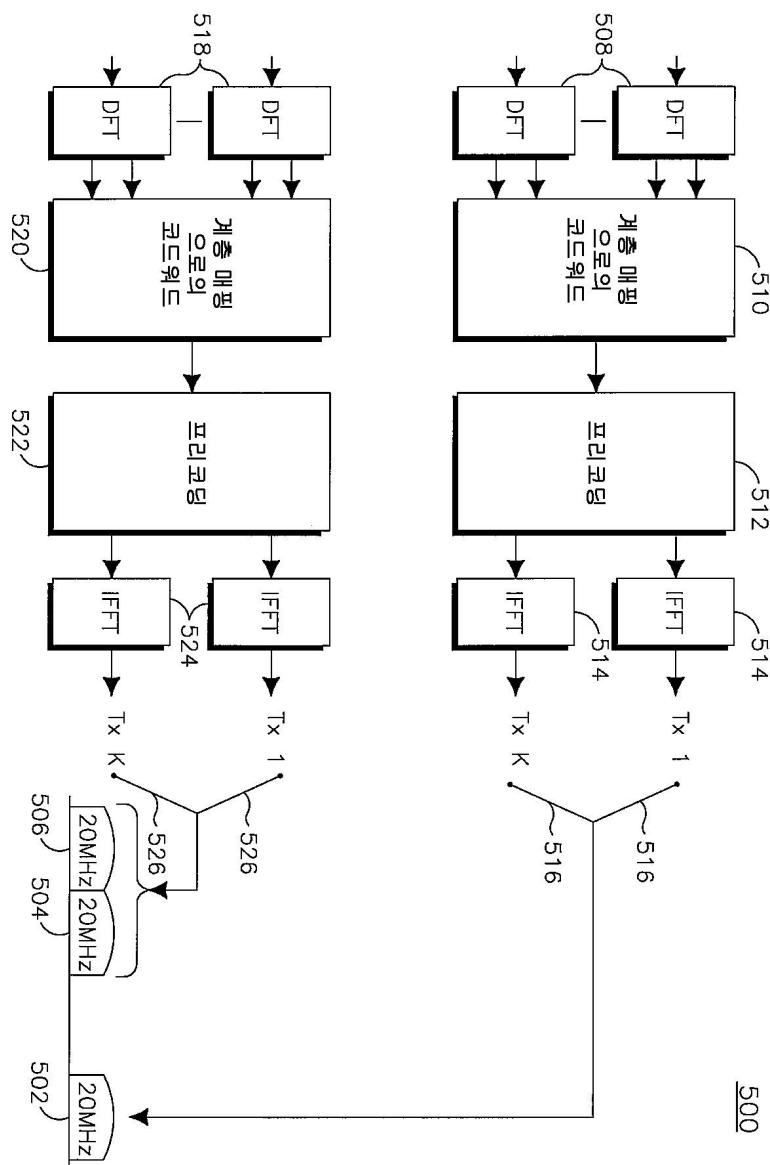

도 5는 다른 실시예에 따른 불연속 반송파를 갖는 반송파 집적을 사용하는 무선 통신 시스템의 개략도를 나타낸다.

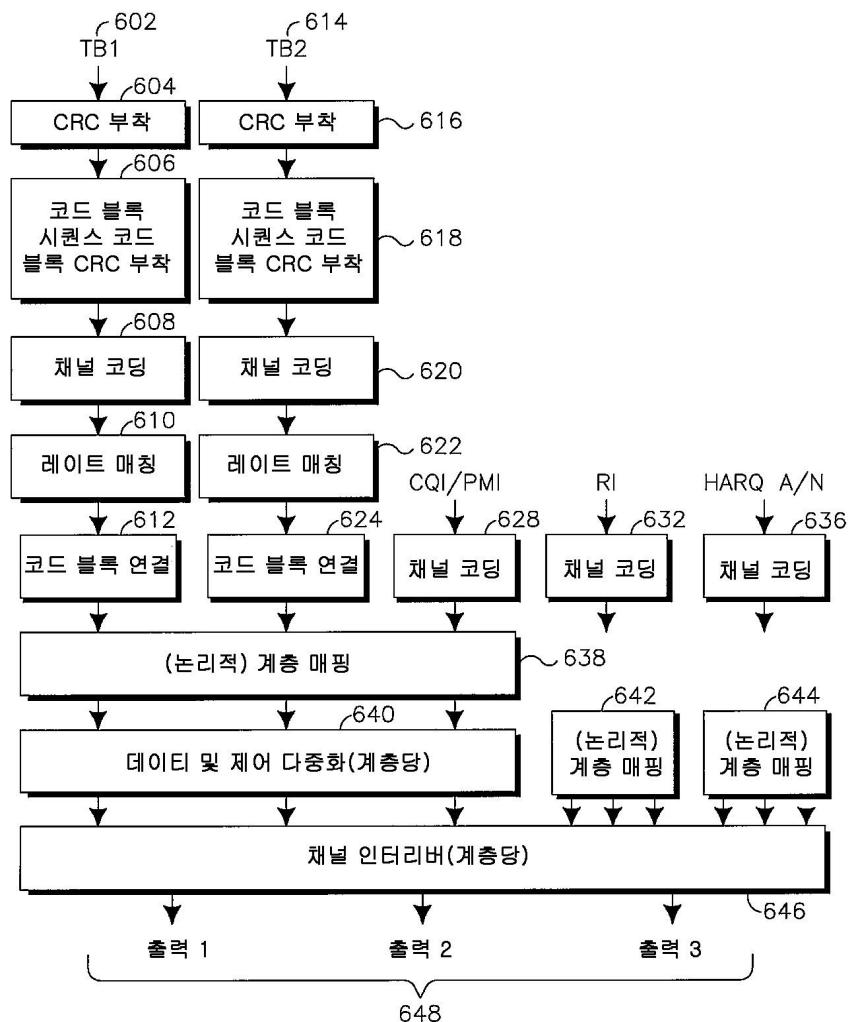

도 6은 일 실시예에 따른 이송 블록 처리 방법의 블록도이다.

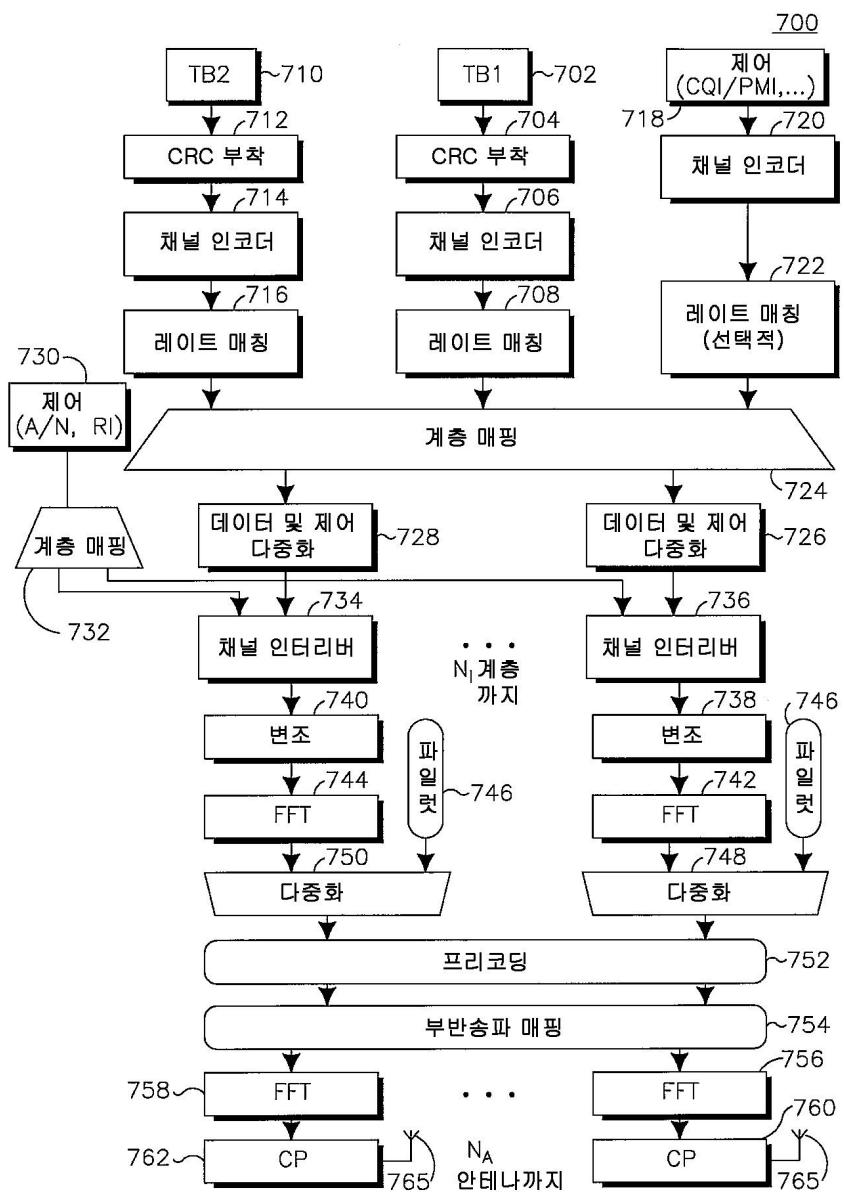

도 7은 일 실시예에 따른 송신기의 블록도를 나타낸다.

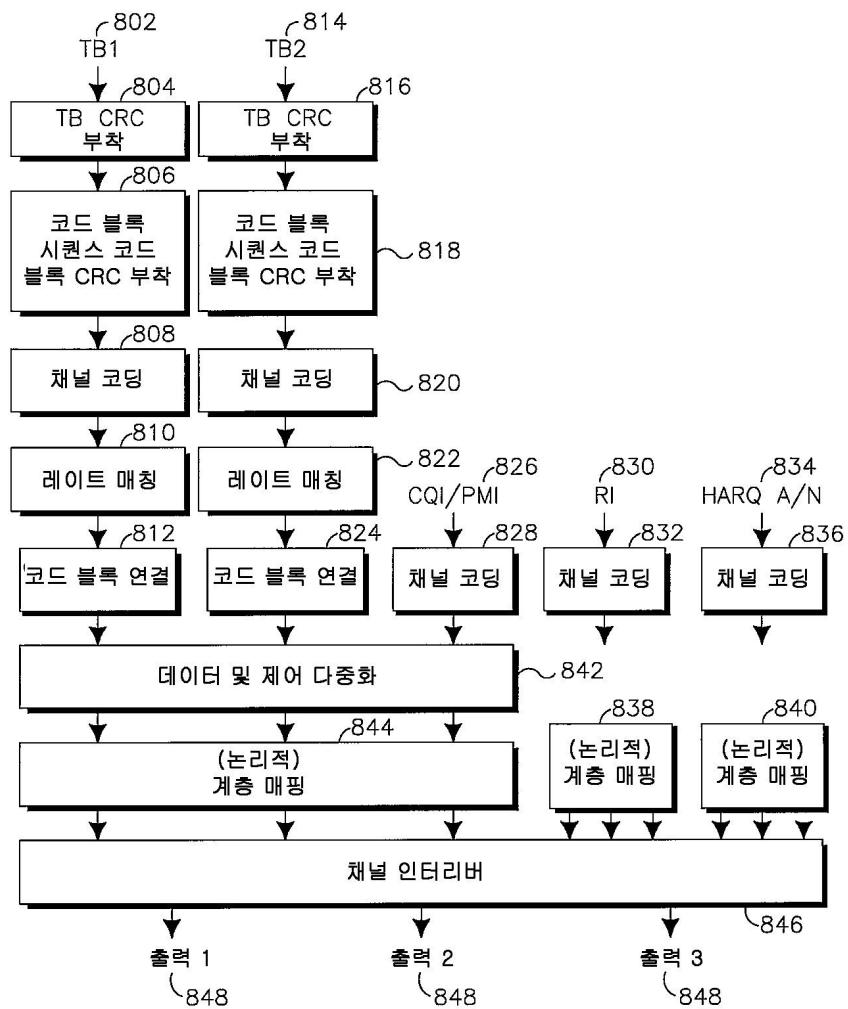

도 8은 다른 실시예에 따른 이송 블록 처리 방법의 블록도이다.

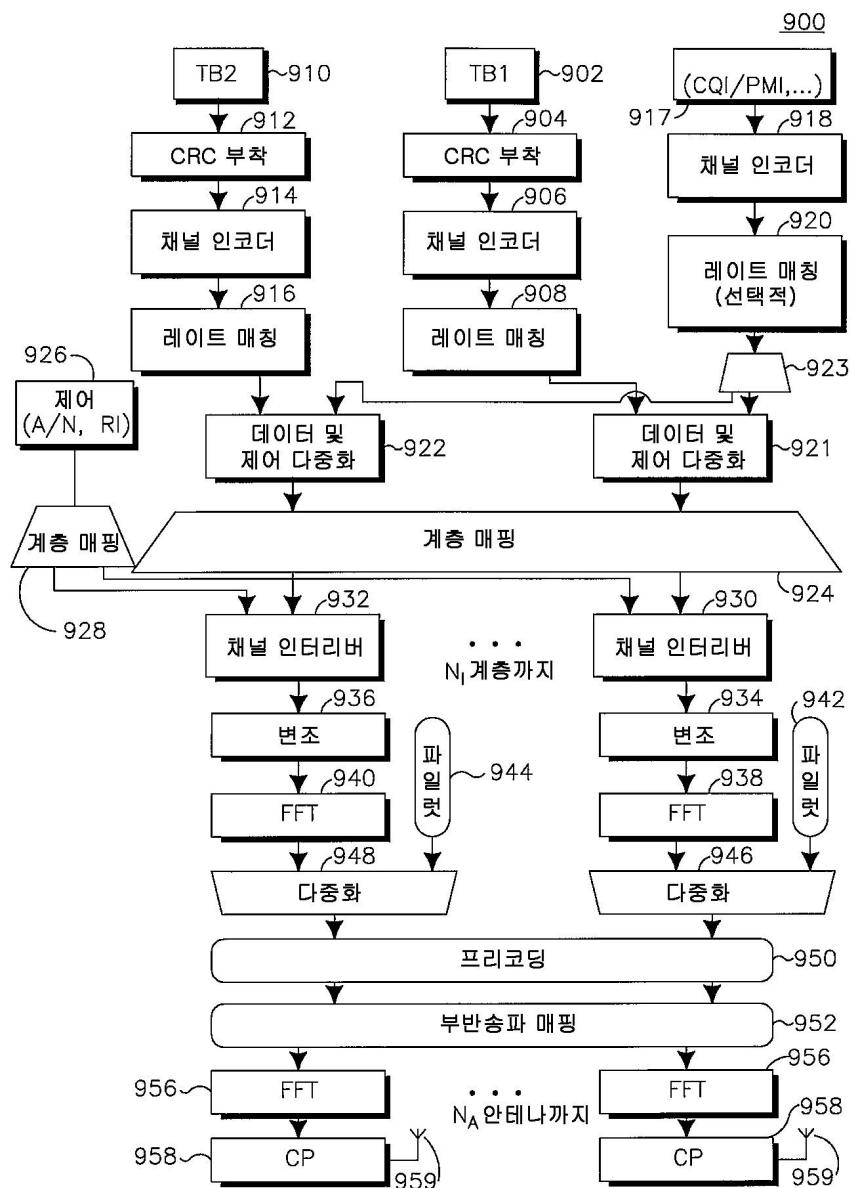

도 9는 다른 실시예에 따른 송신기의 블록도를 나타낸다.

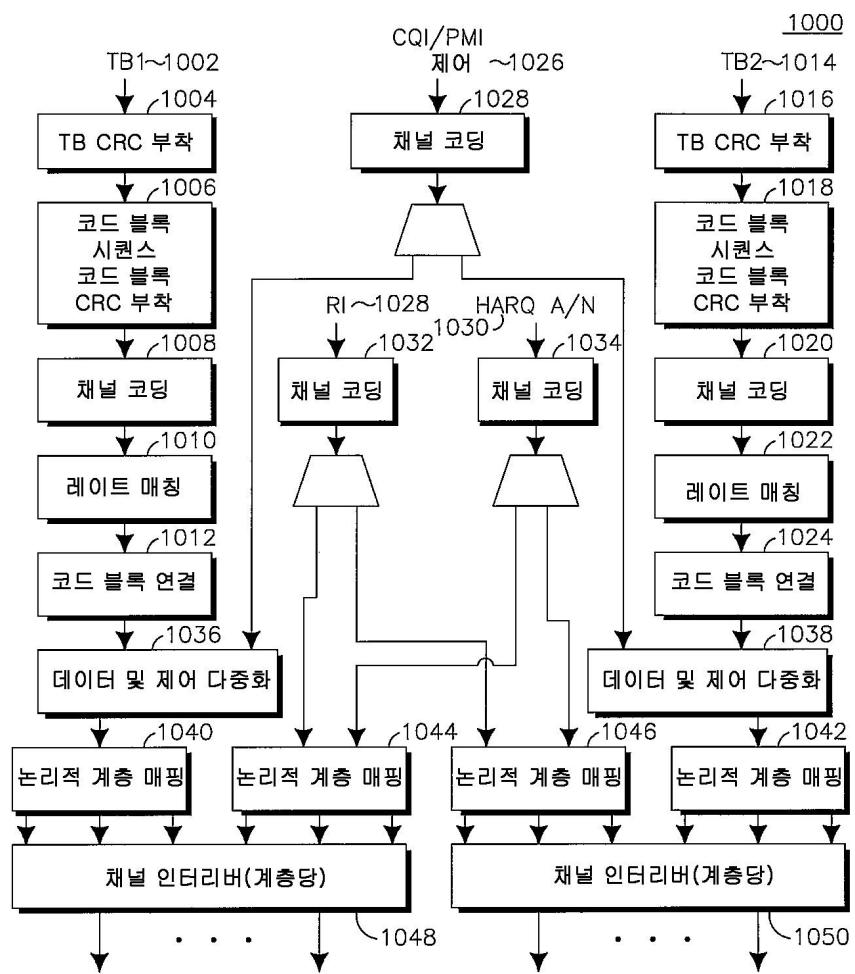

도 10은 또 다른 실시예에 따른 이송 블록 처리 방법의 블록도이다.

도 11은 대안적인 실시예에 따른 이송 블록 처리 방법의 블록도이다.

도 12는 일 실시예에 따른 다중 계층 및 코드워드에 대한 제어 및 데이터 다중화를 나타내는 블록도이다.

도 13은 일 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

도 14는 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

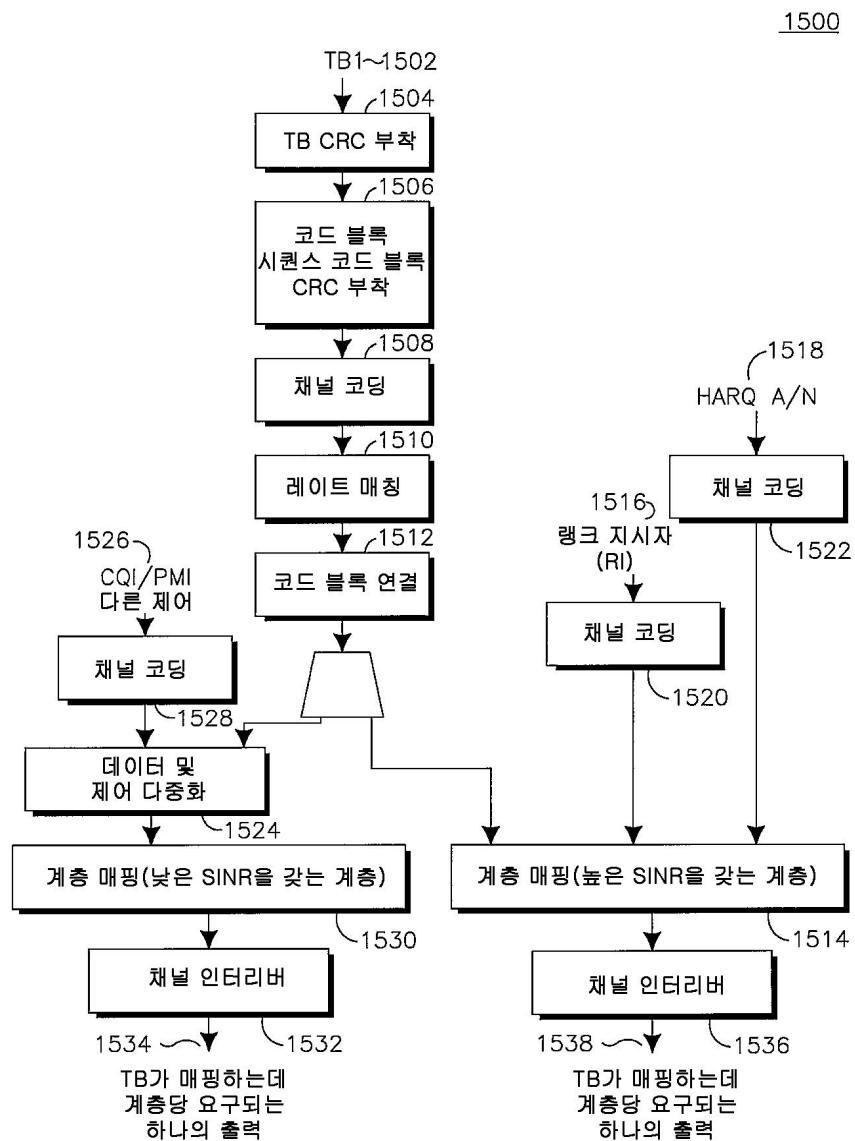

도 15는 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

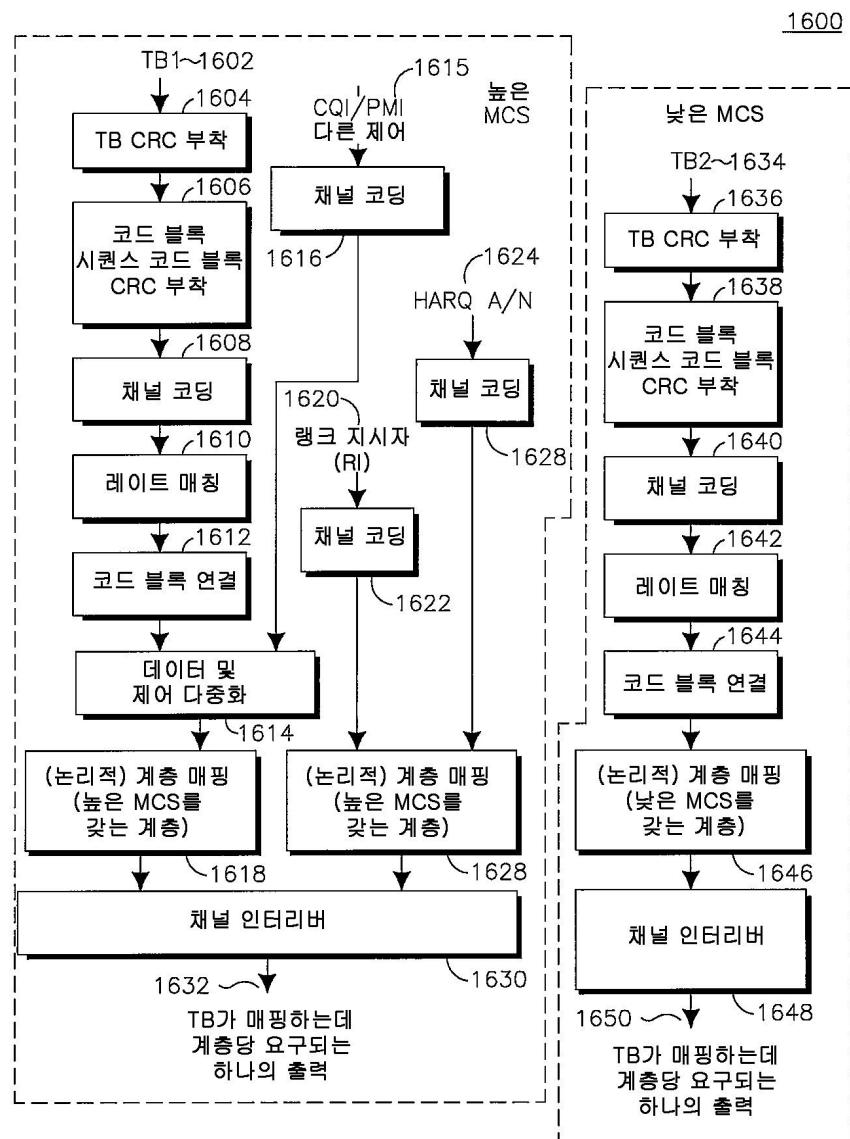

도 16은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

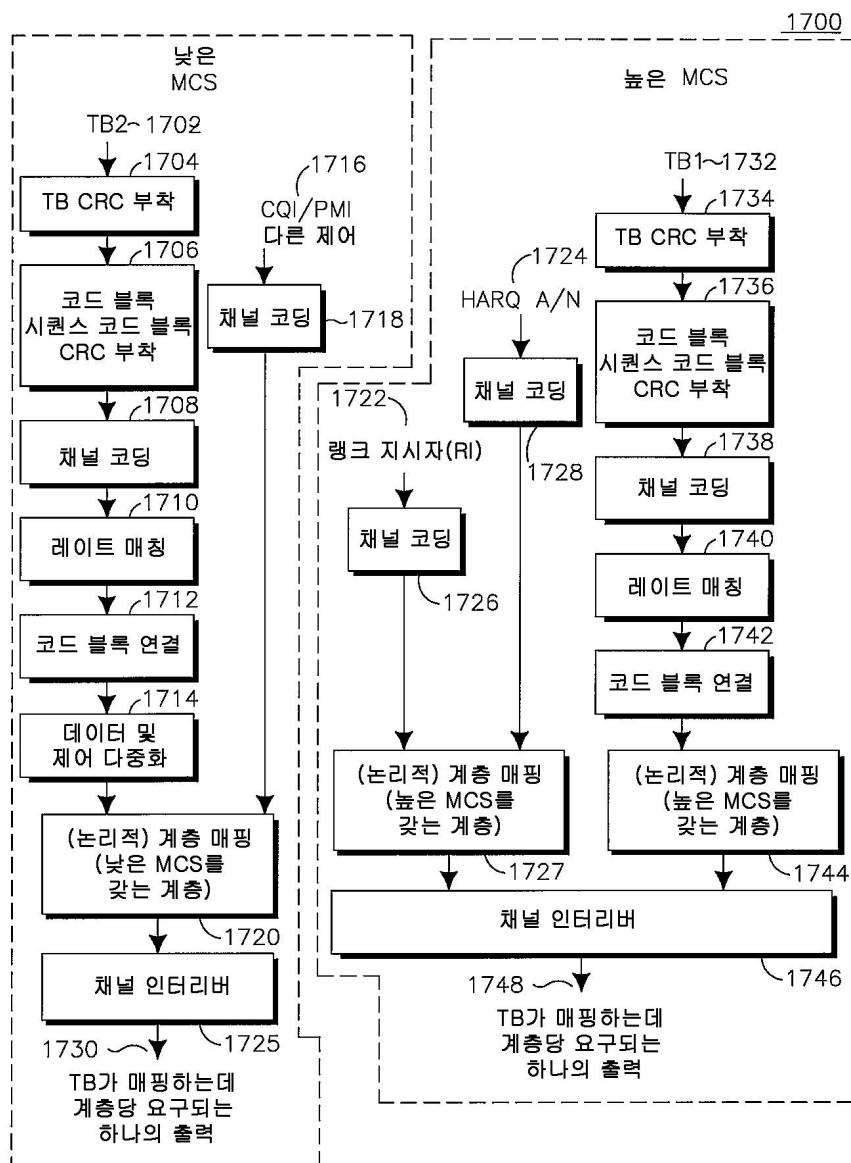

도 17은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

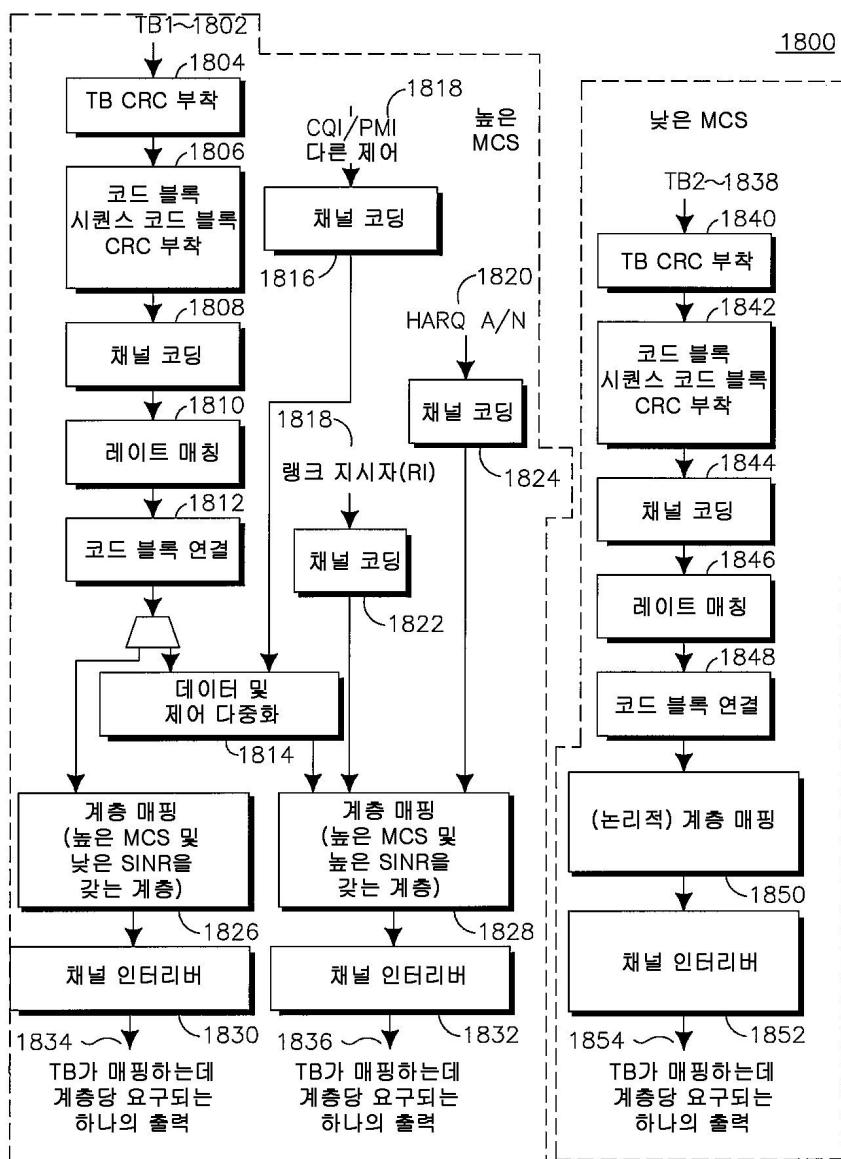

도 18은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

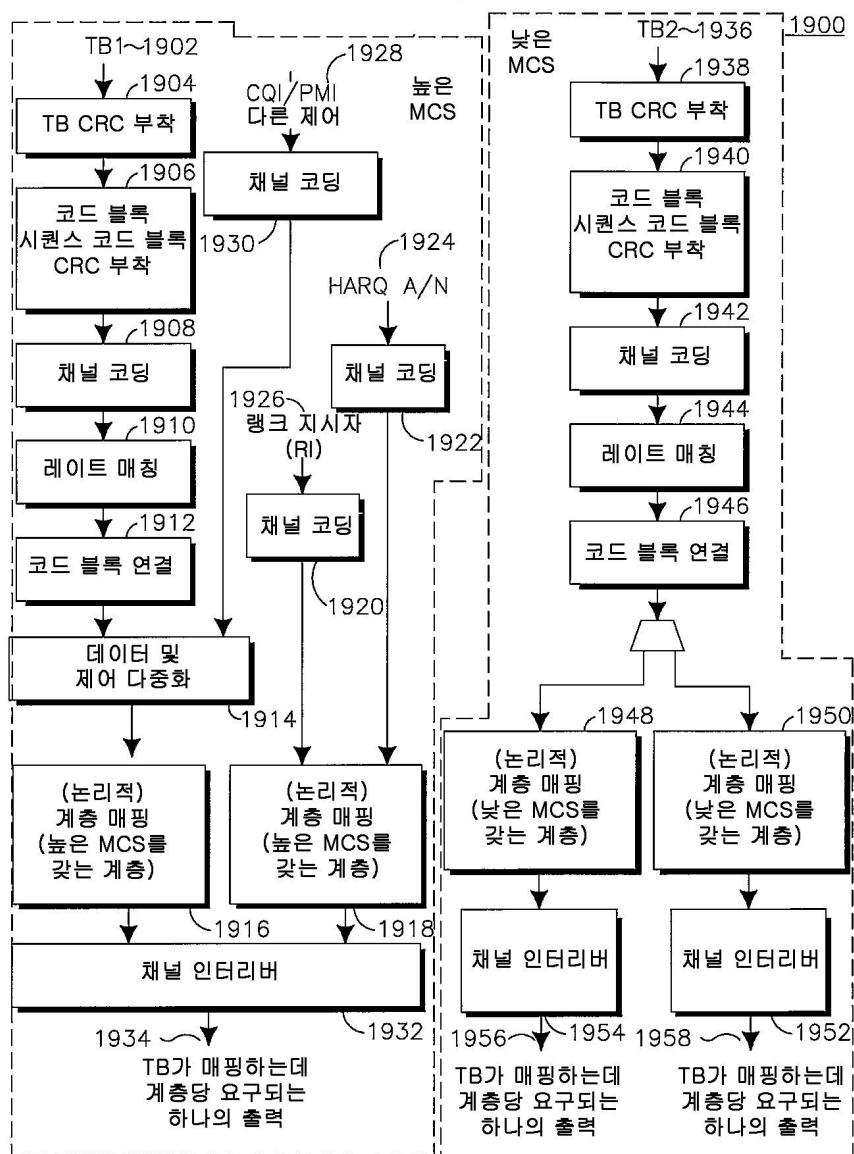

도 19는 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

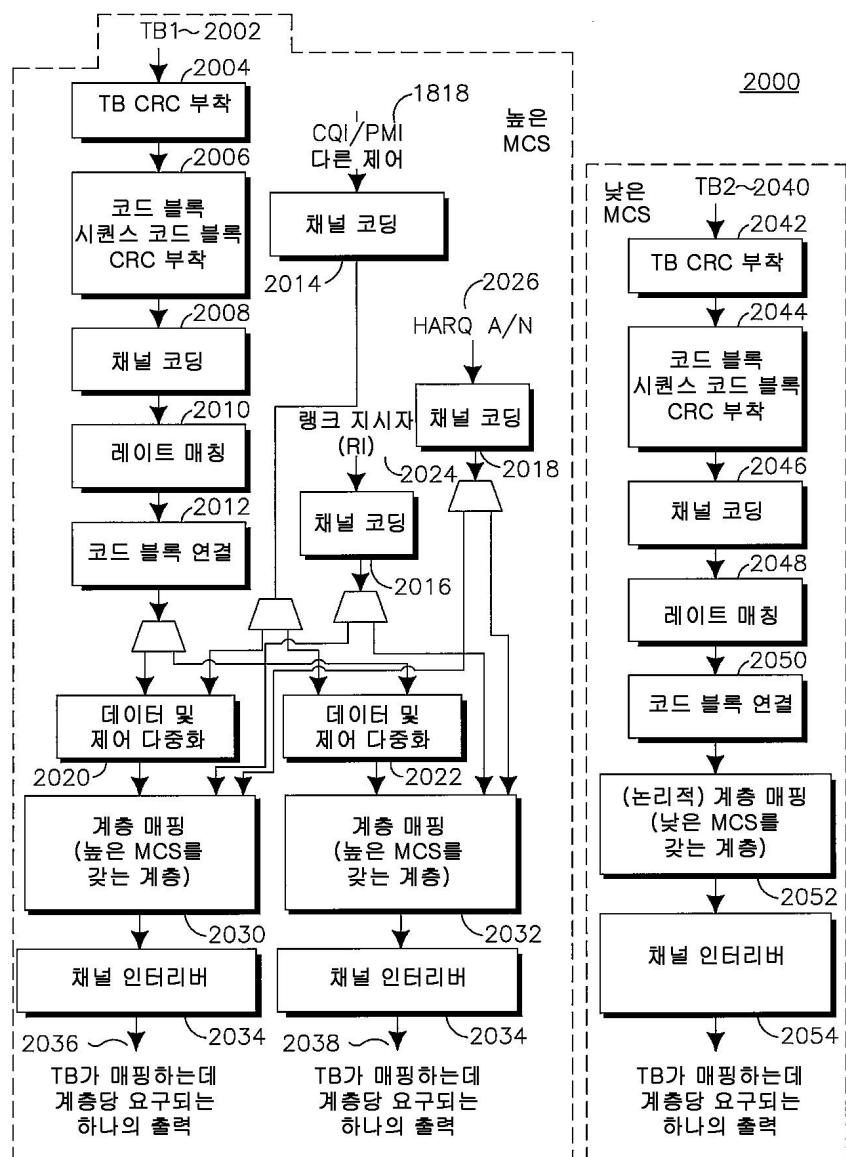

도 20은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

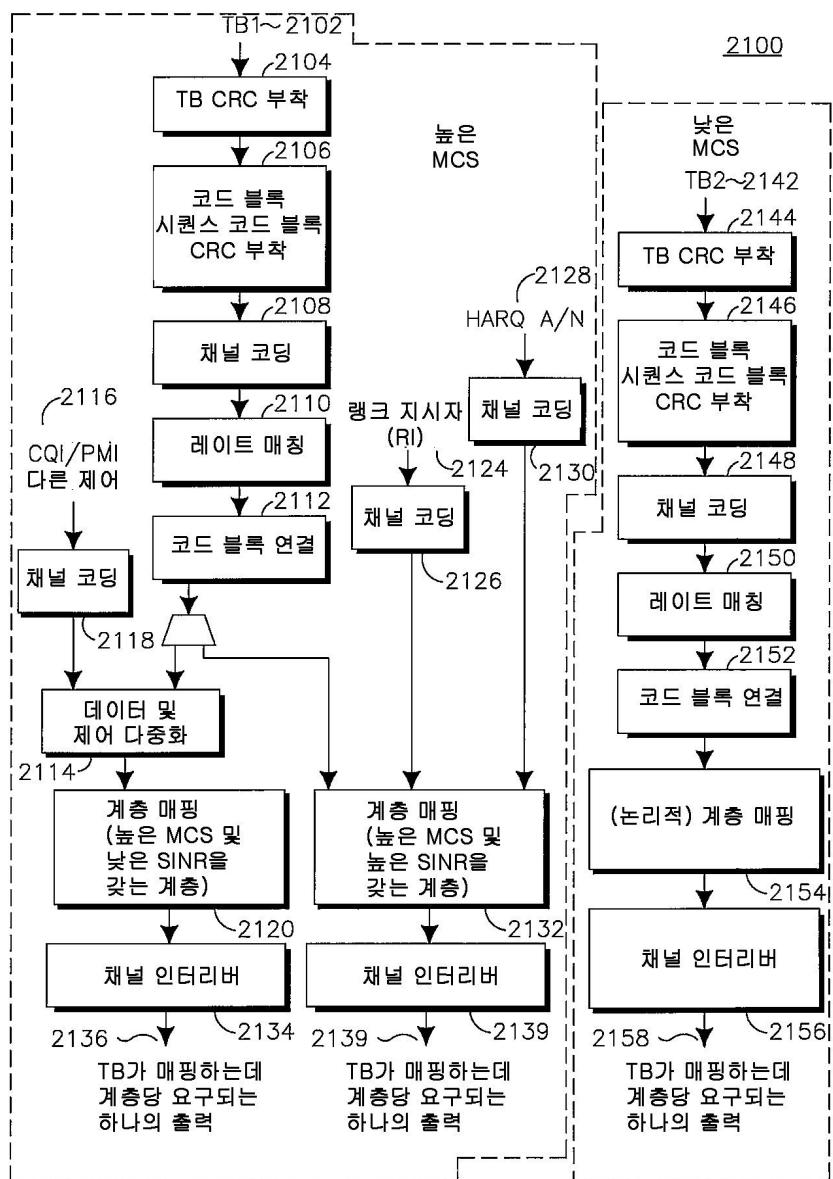

도 21은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

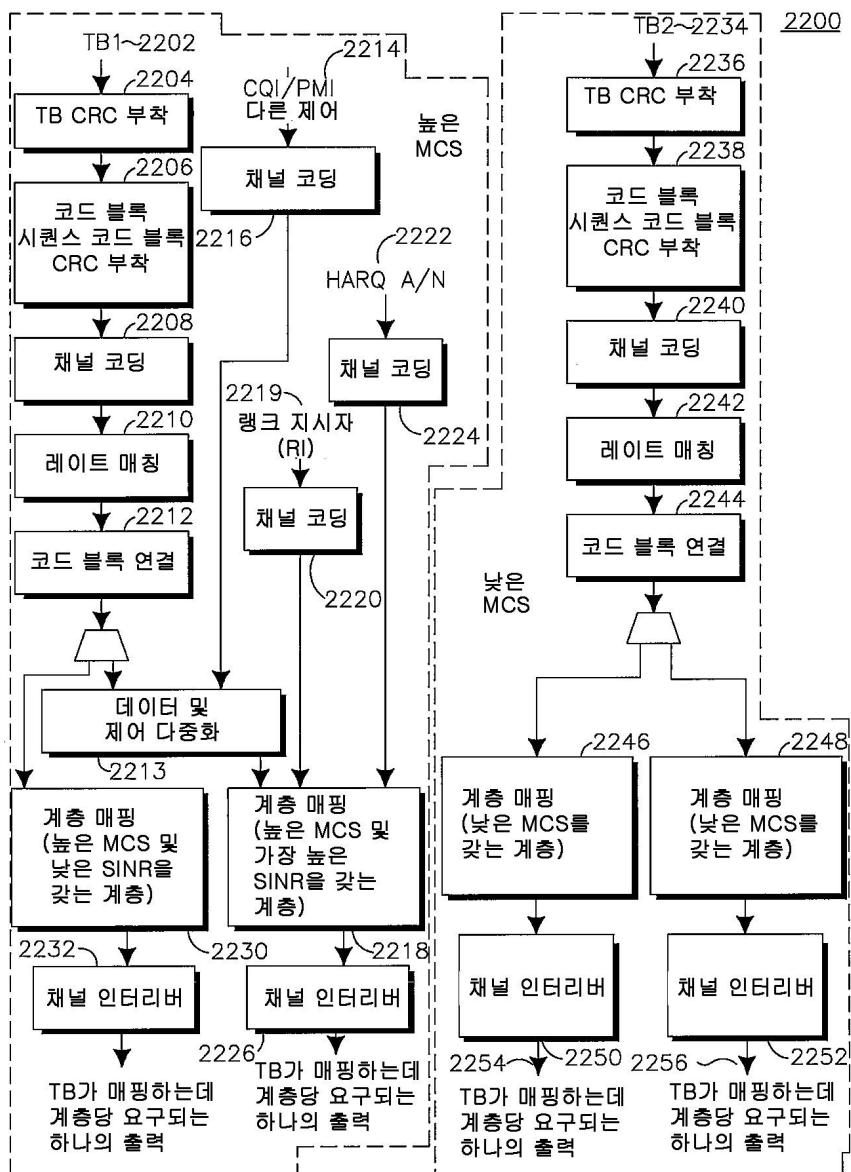

도 22는 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

도 23은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

도 24는 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

도 25는 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

도 26은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

도 27은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

도 28은 또 다른 실시예에 따른 UCI 비트 매핑 방법의 블록도이다.

### 발명을 실시하기 위한 구체적인 내용

[0011] 이후 참조할 때, "무선 송수신 유닛(WTRU)"이라는 용어는 사용자 장비(UE), 이동국, 고정 또는 이동 가입자 유닛, 페이저, 셀룰러 전화기, PDA, 컴퓨터, 또는 무선 환경에서 동작할 수 있는 임의의 다른 형태의 장치를 포함

하지만 이에 제한되는 것은 아니다. 이후 참조할 때, "기지국"이라는 용어는 노드 B, 사이트 제어기, 액세스 포인트(AP; Access Point), 또는 무선 환경에서 동작할 수 있는 임의의 다른 형태의 인터페이싱 장치를 포함하지만 이에 제한되는 것은 아니다.

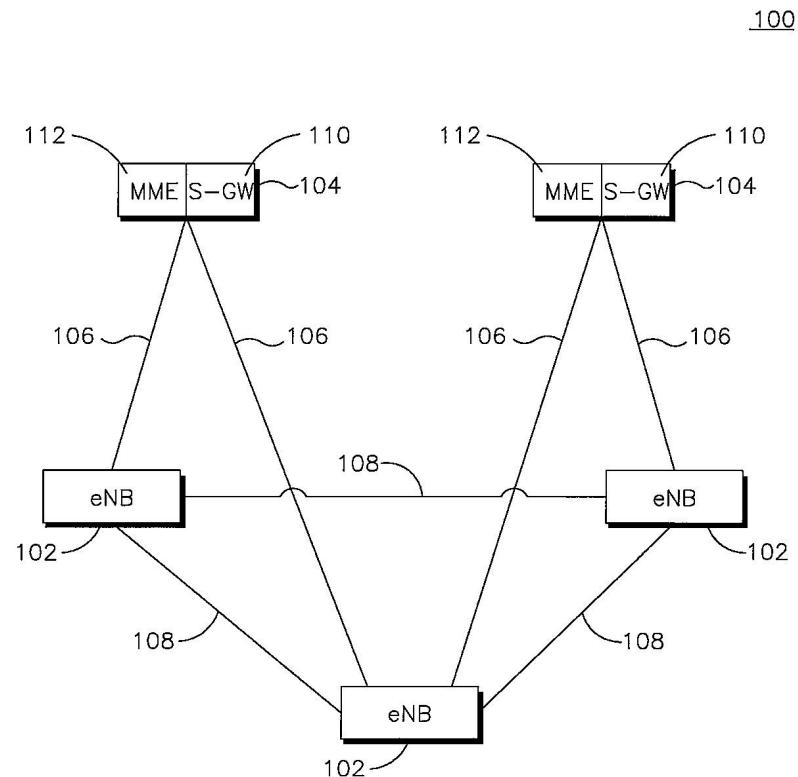

[0012] 도 1은 종래 기술에 따른 발전된 UMTS 지상 무선 접속 네트워크(E-UTRAN; 100)의 개략도를 나타낸다. 도 1에 도시된 바와 같이, E-UTRAN(100)은 3개의 e 노드 B(eNBs; 102)를 포함하지만, 어떤 개수의 eNB도 E-UTRAN(100)에 포함될 수 있다. eNB(102)는 X2 인터페이스(108)에 의해 서로 연결된다. eNB(102)는 또한 S1 인터페이스(106)에 의해 진화된 패킷 코어(EPC; Evolved Packet Core)(104)에 연결된다. EPC(104)는 이동성 관리 엔티티(MME; Mobility Management Entity)(112) 및 서빙 게이트웨이(S-GW; Serving Gateway)(110)를 포함한다. 다른 네트워크 구성도 사용될 수 있고, 여기에 개시된 어떤 것도 임의의 하나의 특정 네트워크 구성이나 구조에 제한되지는 않는다.

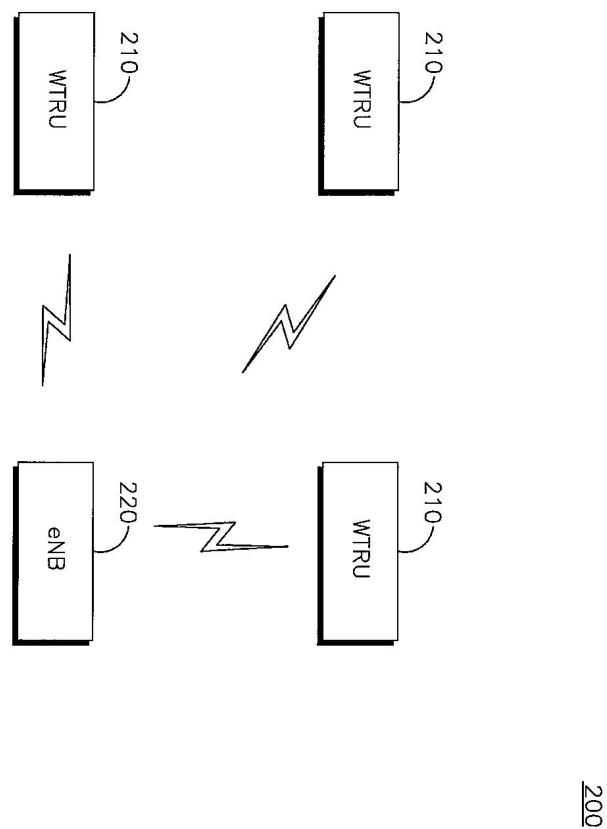

[0013] 무선 통신 시스템에서, 무선 송수신 유닛(WTRU)은 하나의 e 노드 B(eNB)와 통신할 수 있다. 도 2는 복수의 WTRU들(210) 및 eNB(220)를 포함하는 무선 통신 시스템(200)을 도시한다. 도 2에 도시된 바와 같이, WTRU(210)는 eNB(220)와 통신하고 있다. 3개의 WTRU들(210)과 하나의 eNB(220)가 도 2에 도시되어 있지만, 무선 및 유선 장치의 어떠한 결합도 무선 통신 시스템(200)에 포함될 수 있음을 주지해야 한다.

[0014] 도 3은 도 2의 무선 통신 시스템(200)의 WTRU(210) 및 eNB(220)의 기능적인 블록도(300)이다. 도 2에 도시된 바와 같이, WTRU(210)는 eNB(220)와 통신하고 있다. WTRU(210)는 단일 반송파 또는 다중 반송파로 송신/수신하도록 구성된다. 반송파는 연속 또는 불연속일 수 있다.

[0015] 전형적인 WTRU에서 발견될 수 있는 구성요소 이외에, WTRU(210)는 프로세서(315), 수신기(316), 송신기(317) 및 안테나 모듈(318)을 포함한다. WTRU(210)는 또한 사용자 인터페이스(321)를 포함할 수 있고, 이 사용자 인터페이스는 LCD나 LED 스크린, 터치 스크린, 키보드, 스타일러스, 또는 임의의 다른 전형적인 사용자 인터페이스 장치를 포함할 수 있지만 여기에 제한되는 것은 아니다. WTRU(310)는 또한 휘발성 또는 비휘발성 메모리(319)와, USB 포트, 시리얼 포트 등과 같은 다른 WTRU로의 입출력 인터페이스(320)를 포함할 수 있다. 수신기(316) 및 송신기(317)는 프로세서(315)와 통신하고 있다. 안테나 모듈(318)은 무선 데이터의 송신 및 수신을 용이하게 하기 위해 수신기(316) 및 송신기(317) 모두와 통신하고 있다. 안테나 모듈(318)은 하나 이상의 안테나를 포함할 수 있다. WTRU(210)는 또한 프로세서(315) 및 송신기(317)와 통신하고 있는 파워 증폭기 모듈(322)을 포함할 수 있다. 파워 증폭기 모듈(322)은 단일 또는 다중 파워 증폭기를 포함할 수 있다. 파워 증폭기 모듈(322)은 대안적으로 송신기(317)에 위치할 수도 있다.

[0016] 전형적인 eNB에서 발견될 수 있는 구성요소 이외에, eNB(220)는 프로세서(325), 수신기(326), 송신기(327) 및 안테나 모듈(328)을 포함한다. 수신기(326) 및 송신기(327)는 프로세서(325)와 통신하고 있다. 안테나 모듈(328)은 무선 데이터의 송신 및 수신을 용이하게 하기 위해 수신기(326) 및 송신기(327) 모두와 통신하고 있다. 안테나 모듈(328)은 하나 이상의 다중 안테나를 포함할 수 있다.

[0017] 도 4는 일 실시예에 따른 연속 반송파(400)를 갖는 반송파 집적의 개략도이다. 개개의 반송파(402, 404, 406)는 가용 대역폭을 증가시키기 위해 결합될 수 있다. 각각의 반송파(402, 404, 406)에서 변조된 데이터는 단일 WTRU(420)에서 이산 푸리에 변환(DFT) 유닛(408), 역 고속 푸리에 변환(IFFT) 유닛(410), 디지털 아날로그(D/A) 변환기 유닛(412) 및 파워 증폭기(PA) 유닛(414)에 의해 처리될 수 있다.

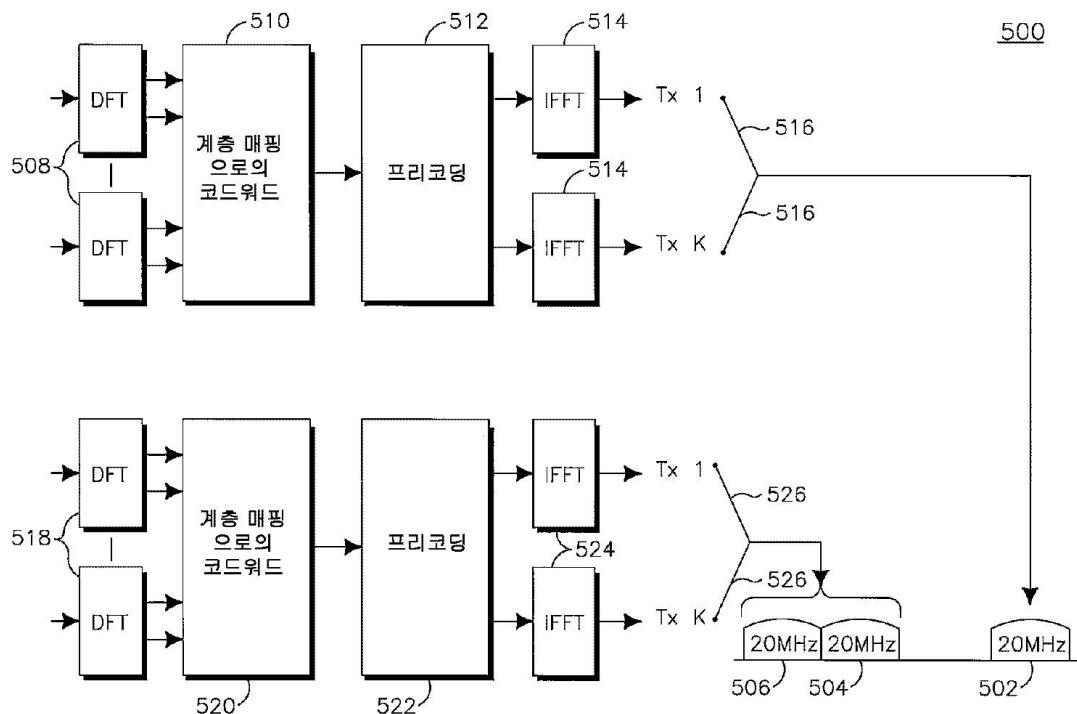

[0018] 도 5는 일 실시예에 따른 반송파 집적(500)을 이용하는 업링크 MIMO의 개략도를 나타낸다. 도 5에 도시된 바와 같이, 제1 반송파(502)는 제2 반송파(504) 및 제3 반송파(506)와 주파수적으로 분리된다. 제1 반송파(502)를 통해 송신되는 데이터는 이산 푸리에 변환(DFT) 쌍(508)에 의해 처리되고, 계층 매핑 유닛으로의 코드워드(510)에 의해 처리된다. 매핑된 데이터는 프리코딩(precoding) 유닛(512)에서 프리코딩되고, 역 고속 푸리에 변환(IFFT) 쌍(514)에서 처리되어, 다중 안테나(516)를 통해 송신된다. 제2 반송파(504) 및 제3 반송파(506)는 서로 인접되어 있어, DFT 쌍(518)을 공유할 수 있다. 제2 반송파(504) 및 제3 반송파(506)에 매핑되는 정보는 DFT 쌍(518)에 의해 우선 처리되고, 계층 매핑 유닛으로의 코드워드(520)에서 처리된다. 매핑된 정보는 프리코딩 유닛(522)에서 프리코딩되고, 다중 안테나(526)에서 송신되기 전에 IFFT 쌍(524)에서 처리된다.

[0019] 다중 송신 안테나 및 다중 코드워드를 사용하는 업링크(UL) 통신에서, 데이터 비트 및 제어 비트는 최적 성능을 위해 다중화될 수 있다. 하이브리드 자동 재전송 요구(HARQ) 송인/비송인(ACK/NACK) 비트는 시간적으로 임의의 복조 참조 신호로 매핑될 수 있지만, 제어 정보 및 데이터 정보는 다른 변조 심볼로 매핑될 수 있다. 다중 송신 안테나를 갖는 WTRU는, 예를 들어, MIMO 프리코딩 또는 송신 다이버시티 구성과 같은 여러 MIMO 기법을 사용

할 수 있다.

[0020] 도 5에 도시된 바와 같이, 각각의 코드워드는 분리된 DFT 동작을 사용할 수 있다. WTRU가 다중 코드워드 및 다중 안테나를 갖는 하나 이상의 DFT 동작을 사용할 때, 코드화된 제어 정보 및 코드화된 데이터 정보는 N개의 계층에 대응하는 N개의 비트 그룹으로 분리될 수 있는데, 여기서 N개의 계층 각각은 제어 정보를 송신하기 위해 사용되고,  $1 \leq N \leq$ (데이터 송신을 위해 사용되는 계층 수)이다. N=1일 때, 제어 비트는 모두 하나의 계층에 있다.

[0021] 변수 N은 제어 비트가 코드워드들 중 하나로서 동일 계층에 매핑되도록 구성될 수 있다. 예를 들어, 3개의 계층이 데이터 비트를 위해 사용될 수 있다. 2개의 코드워드가 사용되면, 제1 코드워드는 3개의 계층 중 제1 계층에 매핑될 수 있고, 제2 코드워드는 3개의 계층 중 제2 및 제3 계층에 매핑될 수 있다. 제어 비트는 제2 코드워드에 의해 사용되는 계층들 모두에 매핑될 수 있다.

[0022] 데이터 및 제어 비트 다중화는 각 계층(per layer)을 기초로 수행될 수 있다. 제어 비트는 하나의 계층으로 매핑될 수 있거나, 다중 계층으로 분산될 수 있다. 랭크 지시자(RI) 비트 및 HARQ ACK/NACK 비트도 또한 계층으로 처리될 수 있다. 데이터 및/또는 제어 비트를 포함하는 각각의 계층은 계층 하나씩(layer by layer)을 기초로 채널 인터리버에 의해 처리될 수 있다.

[0023] 도 6은 일 실시예에 따른 이송 블록 처리 방법의 블록도이다. 코드화된 데이터 비트는, 계층들이 각 계층(per layer)을 기초로 다중화되기 전에 계층 매핑 기능부에서 코드화된 제어 비트와 함께 처리된다. 다중 코드워드가 사용된다면, 제어 비트는 모든 계층으로 매핑되거나 코드워드에 의해 분리될 수 있다.

[0024] 도 6에 도시된 바와 같이, 제1 코드워드의 코드화된 데이터 비트 세트를 포함하는 제1 이송 블록(TB1; 602)은 순환 잉여 검사(CRC; Cycle Redundancy Check) 부착 유닛(604)으로 입력된다. CRC 부착 유닛(604)의 출력은 코드 블록 분할 및 코드 블록 CRC 부착 유닛(606)으로 입력된다. 이후 신호는 채널 코딩 유닛(608)에서 채널 코드화되어, 레이트 매칭 유닛(610)으로 입력된다. 레이트 매칭 유닛으로부터의 신호는 코드 블록 연결 유닛(612)에서 연결된다.

[0025] 제2 코드워드의 코드화된 데이터 비트 세트를 포함하는 제2 이송 블록(614)은 TB1(602)에서와 같은 방법으로 처리된다. 데이터는 CRC 부착 유닛(616), 코드 블록 분할 및 코드 블록 CRC 부착 유닛(618), 채널 코딩 유닛(620), 레이트 매칭 유닛(622) 및 코드 블록 연결 유닛(624)에 의해 처리된다.

[0026] CQI 및 PMI 비트(626)는 채널 코딩 유닛(628)에서 개별적으로 코드화된다. RI 비트(630)는 다른 채널 코딩 유닛(632)에서 개별적으로 코드화된다. HARQ ACK/NACK 비트(634)는 또 다른 채널 코딩 유닛(636)에서 코드화된다. 코드화된 데이터 비트 및 코드화된 제어 비트는 논리적 계층 매핑 기능부(638)에 의해 처리된다. 논리적 계층 매핑 기능부는 입력 스트림(즉, 데이터 및/또는 제어 비트)을, 예를 들어, 높은 MCS나 SINR과 같은 특정 규칙이나 기준에 따라 하나 이상의 계층으로 매핑한다. 코드화된 데이터 비트 및 코드화된 제어 비트는 N개의 그룹으로 나누어지고, 각 그룹(per group)을 기초로 하나의 코드워드 및 계층으로 매핑되는데, 여기서 N은 정수 값이다. N개의 비트 그룹은 N개의 계층에 대응한다.

[0027] 데이터 및 제어 다중화는 데이터 및 제어 다중화 유닛(640)에서 데이터 및 제어 비트의 각 그룹이나 계층에 대하여 수행된다. 이러한 처리는 각 계층(per layer)을 기초로 수행된다. 데이터 및 제어 다중화 기능은 계층에 특정될 수 있고, 계층당 다른 수의 제어 및 데이터 비트를 처리할 수 있다.

[0028] 이와 유사하게, 코드화된 RI 비트는 논리적 계층 매핑 기능부(642)에 의해 처리된다. 또한, 코드화된 HARQ 비트는 논리적 계층 매핑 기능부(644)에서 처리된다.

[0029] 각 계층의 모든 비트는 채널 인터리빙 기능부(646)에 의해 처리된다. 도 6에 도시된 바와 같이, 논리적 계층 매핑 기능부는 모든 비트를 3개의 계층 중 하나에 매핑한다. 인터리빙된 각 계층은 이후 개별적으로 출력된다(648).

[0030] 도 7은 일 실시예에 따른 송신기(700)의 블록도를 나타낸다. 도 7에 도시된 바와 같이, TB1(702)로부터의 데이터는 CRC 부착 유닛(706)으로 입력되고, 이후 제1 채널 코딩 유닛(704)으로 입력된다. 코드화된 데이터는 이후 제1 레이트 매칭 유닛(708)에 의해 처리된다.

[0031] TB2(710)은 제2 CRC 부착 유닛으로 입력된 후, 제2 채널 코딩 유닛(712)으로 입력된다. 코드화된 데이터는 이후 제2 레이트 매칭 유닛(716)에 의해 처리된다.

- [0032] 예를 들어, PMI 및 CQI와 같은 제어 정보(718)는 채널 코딩 유닛(720)에 의해 채널 코드화되고, 레이트 매칭 유닛(722)에서 레이트 매칭이 이루어진다. 처리된 제어 정보, TB1으로부터의 처리된 데이터 및 TB2로부터의 처리된 데이터는 계층 매핑 유닛(724)에서 계층으로 처리된다.

- [0033] 제1 데이터 및 제어 다중화기(726)와 제2 데이터 및 제어 다중화기(728)는 각각 처리된 제어 및 데이터 정보의 계층을 다중화한다. 예를 들어, RI 및 HARQ ACK/NACK과 같은 제2 제어 정보 세트(730)는 제2 계층 매핑 유닛(732)에서 하나의 계층으로 매핑된다. 제1 채널 인터리버(734) 및 제2 채널 인터리버(736)는 각각 계층화되고 처리된 데이터 및 제어 정보를 인터리빙한다. 제1 변조 유닛(738) 및 제2 변조 유닛(740)은 각각 인터리빙된 데이터 및 제어 정보를 변조시킨다. 변조된 데이터 및 제어 정보는 제1 FFT 유닛(742) 및 제2 FFT 유닛(744)에 의해 처리된다. 파일럿 신호(746)는 이후 다른 다중화기(748) 및 또 다른 다중화기(750)에서 변환된 데이터 및 제어 신호와 다중화된다.

- [0034] 프리코딩 유닛(752)은 다중화된 데이터를 처리하고 코드화한다. 프리코딩된 데이터는 부반송파 매핑 유닛(754)에서 eNodeB에 의해 지정되는 부반송파로 매핑된다. 부반송파 매핑 유닛은 안테나 매핑부를 위해 매핑된 부반송파를 출력한다. 각각의 출력은 역 FFT 유닛(756, 758) 및 주기적 전치 부호(Cyclic Prefix) 유닛(760, 762)에 의해 처리되어, 각각의 안테나에서 송신된다.

- [0035] 도 8은 다른 실시예에 따른 이송 블록 처리 방법(800)의 블록도이다. 제어 및 데이터 비트는 계층 처리 유닛에서 처리되기 전에 다중화된다. 제어 비트는 하나 이상의 코드워드의 데이터 비트와 다중화될 수 있다. 제어 및 데이터 비트는 이후 하나 이상의 계층으로 매핑되는데, 이들 계층 각각은 제어 및 데이터 비트를 모두 갖고 있다.

- [0036] 도 8에 도시된 바와 같이, TB1(802)은 CRC 부착 유닛(804)으로 입력된다. CRC 부착 유닛(804)의 출력은 코드 블록 분할 및 코드 블록 CRC 부착 유닛(806)으로 입력된다. 데이터 비트는 이후 채널 코딩 유닛(808)에서 채널 코드화되어, 레이트 매칭 유닛(810)으로 입력된다. 레이트 매칭 유닛(810)으로부터의 코드화된 비트는 코드 블록 연결 유닛(812)에서 연결된다.

- [0037] TB2(814)는 제2 코드워드의 코드화된 제2 비트 세트를 포함하고, TB1(802)과 동일한 방법으로 처리된다. TB2(814)는 CRC 부착 유닛(816), 코드 블록 분할 및 코드 블록 CRC 부착 유닛(818), 채널 코딩 유닛(820), 레이트 매칭 유닛(822) 및 코드 블록 연결 유닛(824)에 의해 처리된다.

- [0038] CQI/PMI 비트(826)는 채널 코딩 유닛(828)에서 개별적으로 코드화된다. RI 비트(830)는 다른 채널 코딩 유닛(832)에서 개별적으로 코드화된다. HARQ ACK/NACK 비트(834)는 또 다른 채널 코딩 유닛(836)에서 코드화된다. 코드화된 RI 비트 및 코드화된 HARQ ACK/NACK 비트는 각각의 논리적 매핑 기능부(838, 840)에 의해 각각 처리된다.

- [0039] 논리적 매핑을 하기 전에, 처리된 CQI/PMI 비트 및 처리된 데이터 비트는 데이터 및 제어 다중화 유닛(842)에서 다중화된다. 다중화된 데이터 및 CQI/PMI 비트는 이후 논리적 계층 매핑 기능부(844)에 의해 처리된다. 논리적 매핑 기능부(844)는 코드화된 데이터 비트 및 코드화된 제어 비트를 N개의 그룹으로 나누는데, 여기서 N은 정수 값이다. N개의 비트 그룹은 N개의 계층에 대응한다. 이러한 처리는 각 계층(per layer)을 기초로 수행된다. 모든 계층의 모든 비트가 채널 인터리빙 기능부(846)에 의해 처리된다. 도 8에 도시된 바와 같이, 논리적 계층 매핑 기능부(838, 840, 844)는 모든 비트를 각각 적절한 계층으로 매핑한다. 인터리빙된 각 계층은 이후 개별적으로 출력된다(848).

- [0040] 도 9는 다른 실시예에 따른 송신기(900)의 블록도를 나타낸다. TB1(902)은 CRC 부착 유닛(906)으로 입력된 후, 제1 채널 코딩 유닛(904)으로 입력된다. 코드화된 데이터는 이후 제1 레이트 매칭 유닛(908)에 의해 처리된다.

- [0041] TB2(910)는 제2 CRC 부착 유닛(914)으로 입력된 후, 제2 채널 코딩 유닛(912)으로 입력된다. 코드화된 데이터는 이후 제2 레이트 매칭 유닛(916)에 의해 처리된다.

- [0042] 예를 들어, PMI 및 CQI와 같은 제어 데이터(916)는 채널 코딩 유닛(918)에 의해 채널 코드화되고, 레이트 매칭 유닛(920)에서 레이트 매칭이 이루어진다. 제1 데이터 및 제어 다중화기(920)와 제2 데이터 및 제어 다중화기(922)는 각각 처리된 제어 및 데이터 정보를 다중화한다. 다중화된 정보는 계층 매핑 유닛(924)에서 계층으로 처리된다. 예를 들어, RI 및 HARQ ACK/NACK과 같은 제2 제어 정보 세트(926)는 계층 매핑 유닛(928)에서 계층으로 매핑된다. 제1 채널 인터리버(930) 및 제2 채널 인터리버(932)는 각각 계층화되고 처리된 데이터 및 제어 정보를 인터리빙한다. 제1 변조 유닛(934) 및 제2 변조 유닛(936)은 각각 인터리빙된 데이터 및 제어 정보를

변조시킨다. 변조된 데이터 및 제어 정보는 제1 FFT 유닛(938) 및 제2 FFT 유닛(940)에 의해 처리된다. 파일럿 신호(942, 944)는 이후 제1 다중화기(946) 및 제2 다중화기(948)에서 변환된 데이터 및 제어 신호와 다중화된다.

[0043] 프리코딩 유닛(950)은 다중화된 데이터를 처리하고 코드화한다. 프리코딩된 데이터는 부반송파 매핑 유닛(952)에서 eNodeB에 의해 지정되는 부반송파로 매핑된다. 부반송파 매핑 유닛은 안테나 매핑부(954)를 위해 매핑된 부반송파를 출력한다. 각각의 출력은 IFFT 유닛(956) 및 CP(Cyclic Prefix) 유닛(958)에 의해 처리되어, 각각의 안테나(954)에서 송신된다.

[0044] 도 10은 또 다른 실시예에 따른 이송 블록 처리 방법(1000)의 블록도이다. 2개의 코드워드가 사용되고, CQI/PMI 비트는 코드워드로 매핑되어 계층 매핑을 하기 전에 데이터 비트와 다중화된다. 논리적 계층 기능부는 각 코드워드의 코드화된 데이터 및 제어 비트를 코드워드당 적어도 하나의 계층에 할당한다. 제어 비트를 포함하는 각 계층에 대하여, 채널 인터리버는 계층 하나씩(layer by layer) 방식으로 비트를 처리한다.

[0045] 도 10에 도시된 바와 같이, 제1 코드워드에 대한 코드화된 비트 세트를 포함하는 제1 이송 블록(TB1; 1002)은 CRC 부착 유닛(1004)으로 입력된다. CRC 부착 유닛의 출력은 코드 블록 분할 및 코드 블록 CRC 부착 유닛(1006)으로 입력된다. 신호는 이후 채널 코딩 유닛(1008)에서 채널 코드화되고, 레이트 매칭 유닛(1010)으로 입력된다. 레이트 매칭 유닛으로부터의 신호는 코드 블록 연결 유닛(1012)에서 연결된다.

[0046] 제2 코드워드의 코드화된 비트 세트를 포함하는 제2 이송 블록(TB2; 1014)은 TB1(1002)와 동일한 방법으로 처리된다. 데이터는 CRC 부착 유닛(1016), 코드 블록 분할 및 코드 블록 CRC 부착 유닛(1018), 채널 코딩 유닛(1020), 레이트 매칭 유닛(1022) 및 코드 블록 연결 유닛(1024)에 의해 처리된다.

[0047] CQI/PMI 비트(1026)는 채널 코딩 유닛(1028)에서 개별적으로 코드화되어 2개의 코드워드로 매핑된다. RI 비트(1028)는 다른 채널 코딩 유닛(1032)에서 개별적으로 코드화되어 2개의 코드워드로 매핑된다. HARQ ACK/NACK 비트(1030)는 또 다른 채널 코딩 유닛(1034)에서 코드화되어 2개의 코드워드로 매핑된다.

[0048] 코드화된 데이터 비트 및 코드화된 CQI/PMI 비트는 데이터 및 제어 다중화 유닛에서 다중화된다. TB1(1002)으로부터의 처리된 데이터 비트는, TB2(1014)로부터의 처리된 데이터 비트를 제2 코드워드로 매핑/처리된 CQI/PMI 비트와 다중화하기 위해 사용되는 코드 및 데이터 다중화기(1038)와 분리되는 제어 및 데이터 다중화기(1036)에서 제1 코드워드로 매핑/처리된 CQI/PMI 비트와 다중화된다.

[0049] 제1 코드워드로 매핑된 CQI/PMI 비트 및 TB1으로부터의 다중화된 데이터는 제1 논리적 계층 매핑 기능부(1040)에서 처리된다. 제2 코드워드로 매핑된 CQI/PMI 비트 및 TB2로부터의 다중화된 데이터는 제2 논리적 계층 매핑 기능부(1042)에서 처리된다. 제1 코드워드로 매핑된 코드화된 HARQ 비트 및 코드화된 RI 비트는 논리적 계층 매핑 기능부(1044)에서 처리된다. 제2 코드워드로 매핑된 코드화된 HARQ 비트 및 코드화된 RI 비트는 다른 논리적 계층 매핑 기능부(1046)에서 처리된다.

[0050] 제1 코드워드로 매핑된 모든 비트는 채널 인터리버(1048)에 의해 처리되고, 인터리빙된 데이터는 계층당(per layer) 출력된다. 제2 코드워드로 매핑된 비트는 제2 채널 인터리버(1050)에 의해 처리되고, 계층당(per layer) 출력된다.

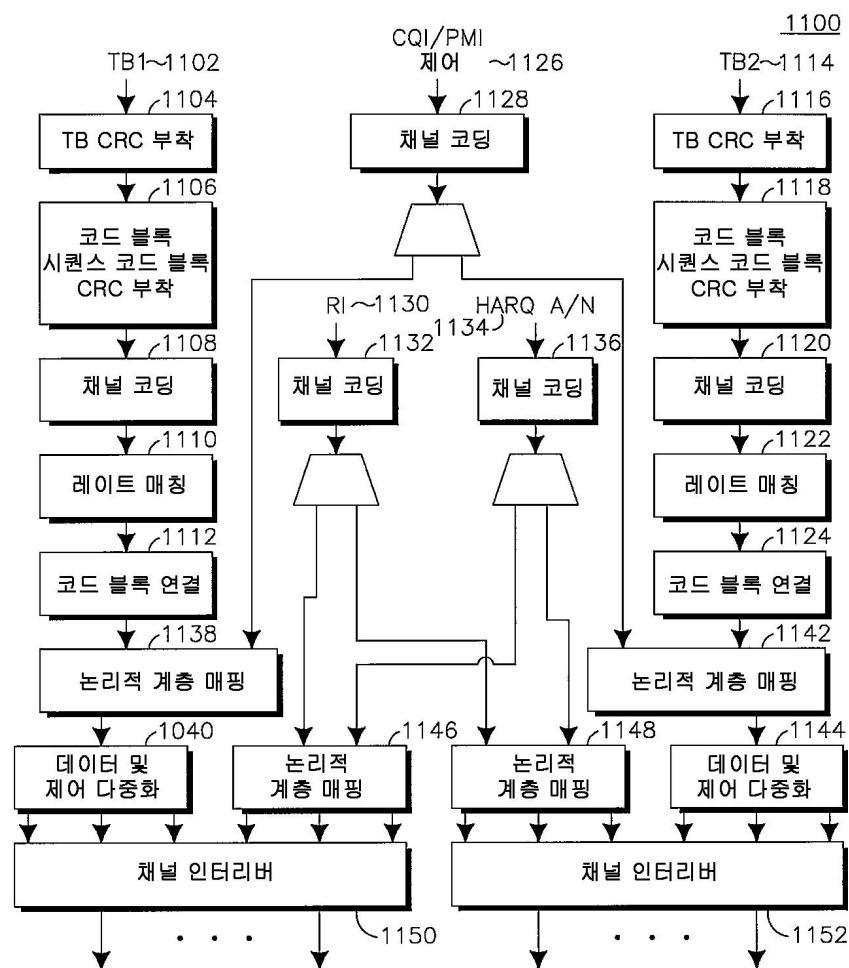

[0051] 도 11은 대안적인 실시예에 따른 이송 블록 처리 방법(1100)의 블록도이다. 코드화된 제어 비트는 적어도 2개의 코드워드로 매핑된다. 각 코드워드에 대하여, 계층 기능부는 비트를 논리적 계층으로 나눈다. 다중화는 각 계층(per layer)을 기초로 수행되고, 계층 각각은 채널 인터리버 기능부에 의해 처리된다. 제어 비트는 데이터 비트와 다중화하기 전에 계층 기능부에 의해 처리된다.

[0052] 제1 코드워드의 코드화된 제1 비트 세트를 포함하는 제1 이송 블록(TB1; 1102)은 CRC 부착 유닛(1104)으로 입력된다. CRC 부착 유닛의 출력은 코드 블록 분할 및 코드 블록 CRC 부착 유닛(1106)으로 입력된다. 신호는 이후 채널 코딩 유닛(1108)에서 채널 코드화되고, 레이트 매칭 유닛(1110)으로 입력된다. 레이트 매칭 유닛으로부터의 신호는 코드 블록 연결 유닛(1112)에서 연결된다.

[0053] 제2 코드워드의 코드화된 제2 비트 세트를 포함하는 제2 이송 블록(TB2; 1114)은 TB1(1102)과 동일한 방법으로 처리된다. 데이터는 CRC 부착 유닛(1116), 코드 블록 분할 및 코드 블록 CRC 부착 유닛(1118), 채널 코딩 유닛(1120), 레이트 매칭 유닛(1122) 및 코드 블록 연결 유닛(1124)에 의해 처리된다.

[0054] CQI/PMI 비트(1126)는 채널 코딩 유닛(1128)에서 개별적으로 코드화되어 2개의 코드워드로 매핑된다. RI 비트(1130)는 다른 채널 코딩 유닛(1132)에서 개별적으로 코드화되어 2개의 코드워드로 매핑된다. HARQ ACK/NACK

비트(1134)는 또 다른 채널 코딩 유닛(1136)에서 코드화되어 2개의 코드워드로 매핑된다.

[0055] 제1 코드워드로 매핑된 CQI/PMI 비트 및 TB1으로부터의 다중화된 데이터는 제1 논리적 계층 매핑 기능부(1138)에서 처리되고, 각 계층은 데이터 및 제어 다중화 유닛(1140)에서 다중화된다. 제2 코드워드로 매핑된 CQI/PMI 비트 및 TB2로부터의 다중화된 데이터는 제2 논리적 계층 매핑 기능부(1142)에서 처리되고, 각 계층은 제2 데이터 및 제어 다중화 유닛(1144)에서 다중화된다. 제1 코드워드로 매핑된 RI 비트 및 제1 코드워드로 매핑된 HARQ 비트는 논리적 계층 매핑 기능부(1146)에서 처리된다. 제2 코드워드로 매핑된 RI 비트 및 제2 코드워드로 매핑된 HARQ 비트는 다른 논리적 계층 매핑 기능부(1148)에서 처리된다.

[0056] 제1 코드워드로 매핑된 모든 비트는 채널 인터리버(1150)에 의해 처리되고, 인터리빙된 데이터는 계층당(per layer) 출력된다. 제2 코드워드로 매핑된 비트는 제2 채널 인터리버(1152)에 의해 처리되고, 계층당(per layer) 출력된다.

[0057] 서브 프레임이 물리적 업링크 공유 채널 리소스를 사용하여 송신될 때, 데이터 및 제어 비트는 동일한 업링크(UL) 서브 프레임에서 송신될 수 있다. 데이터 및 제어 비트가 모두 DFT에 의해 처리되지만, 동일한 DFT를 사용하지 않을 수도 있다. 일 실시예로서, 데이터 및 제어 비트가 모두 랭크 1 프리코딩(rank 1 precoding)을 사용할 수 있다. WTRU는, 예를 들어, 다른 업링크(UL) 정보에 더하여 랭크 및 프리코딩 구성과 같은 업링크(UL) 송신 모드에 관한 정보를 수신할 수 있다.

[0058] 데이터 및 제어 비트가 개별 DFT 프로세서를 사용하면, WTRU는 데이터 비트에 대하여는 제1 업링크 송신 구성을, 제어 비트에 대하여는 제2 업링크 송신 구성을 사용할 수 있다. 예를 들어, 제어 비트는 업링크 송신 다이버시티를 사용하여 송신될 수 있고, 업링크 데이터 비트는 예를 들어 공간 다중화와 같은 다른 구성을 사용할 수 있다.

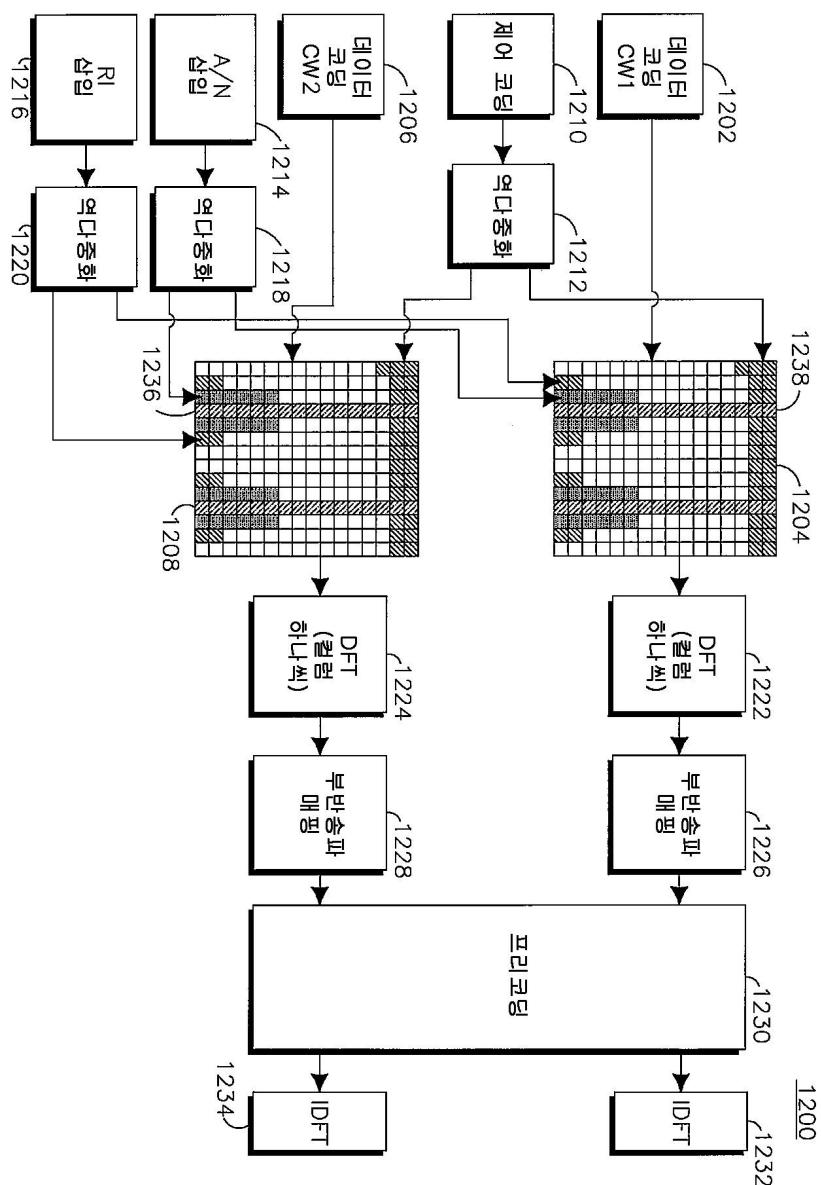

[0059] 도 12는 일 실시예에 따른 다중 계층 및 코드워드에 대한 제어 및 데이터 다중화 방법(1200)의 블록도이다. 도 12에서, 2개의 이송 블록 및 2개의 계층이 있다. 그러나 이러한 방법은 임의의 이송 블록의 수 및 임의의 계층의 수에 적용될 수 있다. 제어 비트는 각 리소스 블록에서 반복되고, 리소스 블록 사이에서 다중화되거나 단 하나의 리소스 블록과 다중화될 수 있다. 여기서 사용된 "리소스 블록"이라는 용어는 동일한 무선 리소스의 다중 계층에 매핑될 수 있는 가상의 리소스 블록을 가리킨다.

[0060] 도 12에 도시된 바와 같이, 제1 코드워드에 매핑된 데이터(1202)는 제1 리소스 블록(1204)으로 매핑된다. 제2 코드워드에 매핑된 데이터(1206)는 제2 리소스 블록(1208)으로 매핑된다. 코드화된 제어 정보(1210)는 역다중화되거나, 또는 반복되어 제1 리소스 블록(1204) 및 제2 리소스 블록(1208)으로 매핑된다. 대안적으로는, 코드화된 제어 정보는 (도시되지 않은) 리소스 블록들 중 단 하나로 매핑될 수 있다. 코드화된 HARQ ACK/NACK 정보(1214) 및 코드화된 RI 정보(1216)는 또한 역다중화되거나 또는 반복되어(1218, 1220), 제1 리소스 블록(1204) 및 제2 리소스 블록(1208)의 각각으로 매핑된다. 대안적으로는, 코드화된 HARQ ACK/NACK 정보(1214) 및 코드화된 RI 정보(1216)는 (도시되지 않은) 리소스 블록들 중 단 하나로 매핑될 수 있다. 각 리소스 블록(1204, 1208)에서의 정보는 제1 DFT(1222) 및 제2 DFT(1224), 제1 부반송파 매핑 블록(1226) 및 제2 부반송파 매핑 블록(1228)에 의해 처리될 수 있는데, 여기서 데이터 비트, 제어 비트, HARQ 비트 및 RI 비트는 하나 이상의 부반송파로 매핑된다. 이후, 정보는 프리코딩되고(1230), 제1 역 DFT(1232) 및 제2 역 DFT(1234)에서 처리된다.

[0061] 도 12에 도시된 바와 같이, 각각의 계층에 대하여, HARQ 정보는 리소스 블록(1204, 1208) 모두에 존재할 수 있어, 업링크 복조 참조 신호(1236, 1238) 주변의 리소스로 매핑된다. 제어 및 데이터 정보는 각 리소스 블록(1204, 1208) 내의 상이한 변조 심볼로 매핑된다.

[0062] 업링크 제어 정보(UCI) 비트는 대안적으로 다중 코드워드 및 계층을 사용하는 시스템에 대하여 코드워드들 사이에 분산될 수 있다. UCI 비트는 대안적으로 단일 코드워드로 매핑될 수 있다. 각 제어 비트는 역다중화되거나 또는 반복되어, 각 코드워드로 매핑되고, 계층화 처리는 계층들 사이에 제어 비트를 분산시킬 수 있다. 대안적으로, 각 계층은 각각의 제어 비트를 포함할 수 있고, 각 제어 비트는 각각의 코드워드에 대하여 뿐만 아니라 각각의 계층에 대하여도 한번 반복될 수 있다. 도 12가 2개의 코드워드와 2개의 계층을 사용하는 방법을 도시하고 있지만, 도 12에 도시된 방법은 2 이상의 계층으로 확장될 수 있다. 예를 들어, 이러한 방법은 하나의 코드워드가 2개의 계층으로 나뉘어진 3개의 계층을 포함할 수 있다. 제어 정보는 이후 3개의 리소스 블록 상의 데이터와 다중화되고, 유사하게 ACK/NACK 및 RI는 제1, 제2, 제3 리소스 블록으로 매핑된다.

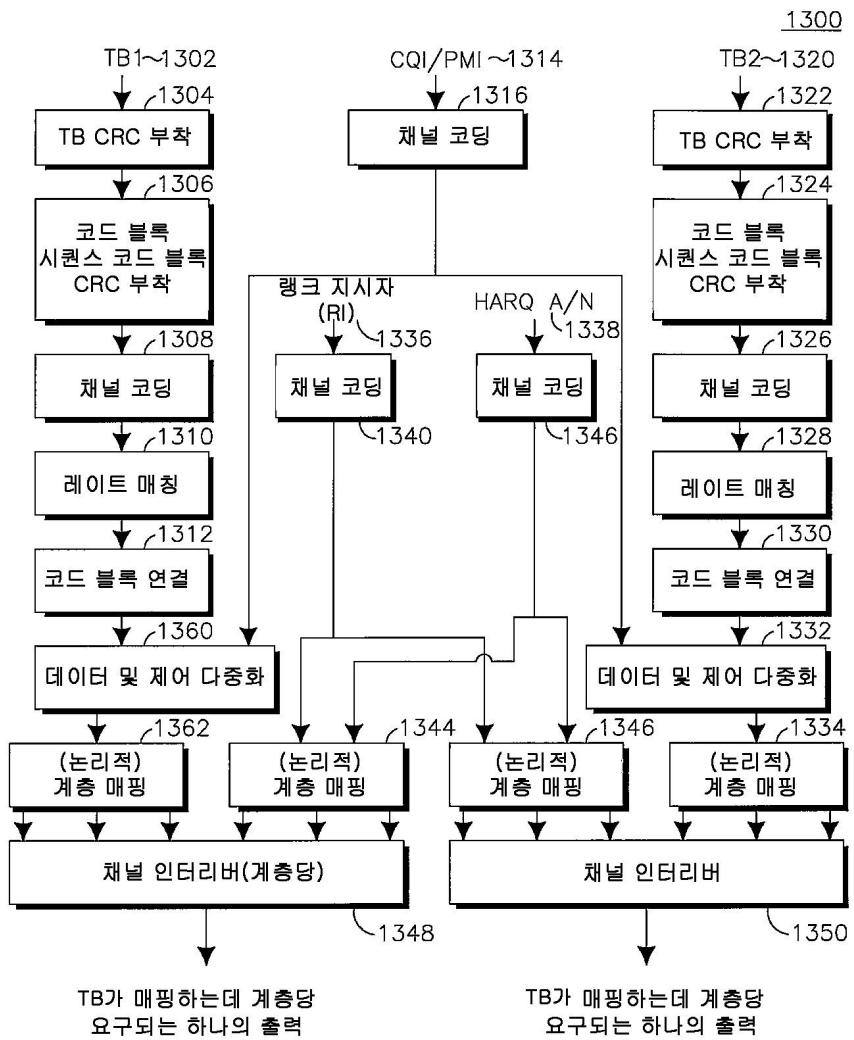

[0063] 도 13은 다른 실시예에 따른 UCI 비트 송신 방법(1300)의 블록도이다. 도 13은 2개 이상의 안테나, 2개의 코드워드 및 모든 계층에 걸쳐 매핑된 UCI 비트에 대하여 2개의 계층, 즉 랭크 2를 사용하는 시스템을 도시한다.

- [0064] 도 13에 도시된 바와 같이, TB1(1302)은 CRC 부착 기능부(1304)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1306)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(1308)에 의해 채널 코드화되고, 레이트 매칭 유닛(1310)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1312)에서 연결된다. CQI/PMI 비트(1314)는 채널 코딩 유닛(1316)에 의해 채널 코드화되고, 2개의 스트림으로 반복된다. 처리된 TB1 비트는 이후 CQI/PMI 비트의 (제1) 스트림과 함께 제어 및 데이터 다중화기(1360)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(1362)에서 하나의 계층으로 매핑된다.

- [0065] TB2(1320)는 CRC 부착 기능부(1322)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1324)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(1326)에 의해 채널 코드화되고, 레이트 매칭 유닛(1328)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1330)에서 연결된다. 처리된 TB2 비트는 제2 데이터 및 제어 다중화기(1332)에서 CQI/PMI 비트의 다른 (제2) 스트림과 다중화된다. 다중화된 비트는 제2 계층 매핑 유닛(1334)에서 매핑된다.

- [0066] RI 비트(1336) 및 HARQ ACK/NACK 비트(1338)는 채널 코드화되고(1340, 1342), 2개의 스트림으로 반복되며, 제3 및 제4 계층 매핑 유닛(1344, 1346)에서 2개의 계층으로 매핑된다. 매핑된 TB1 비트, CQI/PMI 비트의 제1 스트림, RI 비트의 제1 스트림 및 HARQ ACK/NACK 비트의 제1 스트림은 제1 채널 인터리버 유닛(1348)에서 인터리빙되고, (도시하지 않은) 안테나 매핑 유닛으로 출력된다. 안테나 매핑 유닛은 변조, 부반송파 매핑, 프리코딩 및 안테나 매핑 기능부를 포함한다. 매핑 된 TB2 비트, CQI/PMI 비트의 제2 스트림, RI 비트의 제2 스트림 및 HARQ ACK/NACK 비트의 제2 스트림은 제2 채널 인터리버 유닛(1350)에서 인터리빙되고, (도시하지 않은) 안테나 매핑 유닛으로 출력된다.

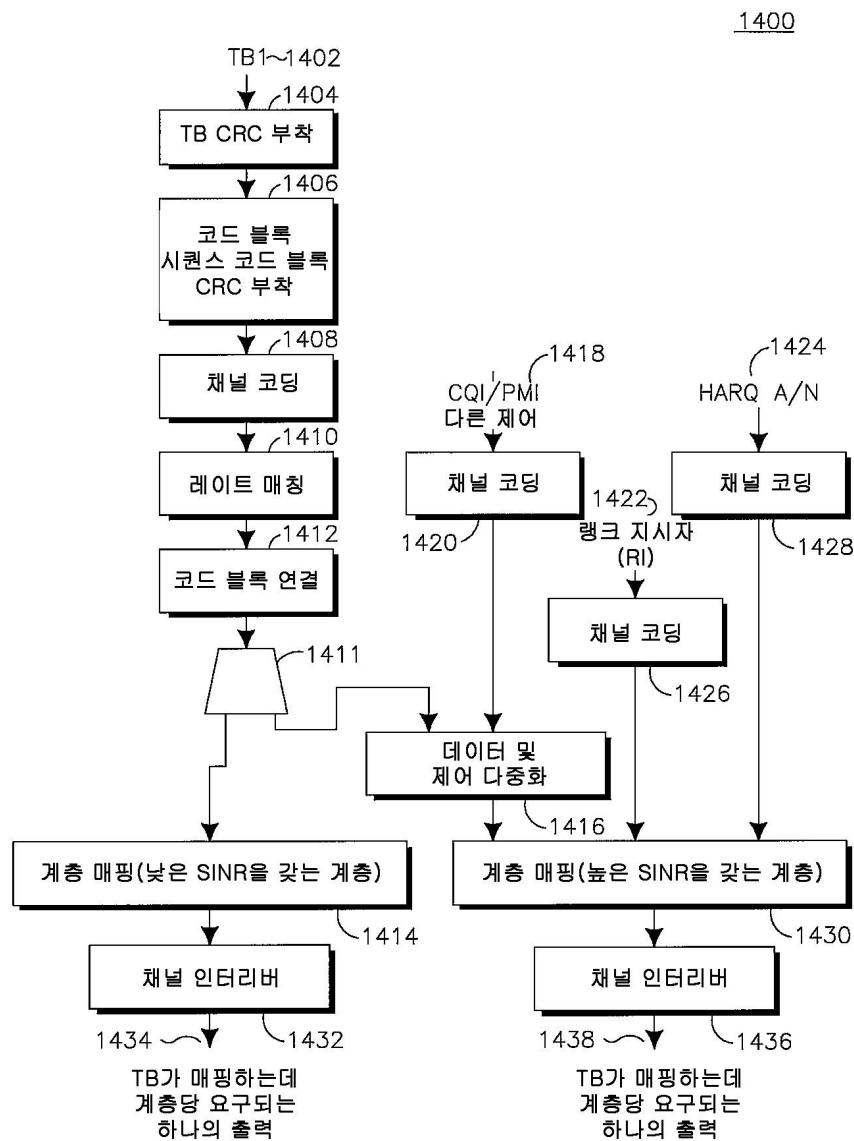

- [0067] 도 14는 일 실시예에 따른 UCI 비트 매핑 방법(1400)의 블록도이다. 도 14는 하나의 코드워드 및 2개의 계층을 사용하는 방법을 도시한다. 이 방법은 하나의 계층으로 매핑된 UCI 비트를 갖는 2 이상의 안테나에 대하여 랭크 2 코딩을 사용한다. TB1(1402)은 CRC 부착 기능부(1404)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1406)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(1408)에 의해 채널 코드화되고, 레이트 매칭 유닛(1410)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1412)에서 연결된다. 코드 블록 연결 유닛의 출력은 UCI 비트와의 다중화를 확인하기 위해 산출된 길이로 분할기(1411)에서 2개의 스트림으로 분할된다. 길이가 긴 스트림인 제1 스트림은 계층 매핑 유닛(1414)에서 비교적 낮은 SINR을 갖는 제1 계층으로 매핑된다. 제2 스트림은 데이터 및 제어 다중화 유닛(1416)에서 채널 코딩 유닛(1420)에서 채널 코드화된 CQI/PMI 비트(1418)와 다중화된다. RI 비트(1422) 및 HARQ ACK/NACK 비트(1424)는 또한 각 채널 코딩 유닛(1426, 1428)에서 채널 코드화되고, 제2 계층 매핑 유닛(1430)에서 처리된 TB1 비트 및 다중화된 CQI/PMI 비트와 함께 비교적 높은 SINR을 갖는 제2 계층으로 매핑된다. 제1 계층 매핑 유닛으로부터 매핑된 비트는 채널 인터리버 유닛(1432)에 의해 계층당(per layer) 처리되어, 제1 안테나 매핑 유닛(1434)으로 출력된다. 안테나 매핑 유닛은 변조, 부반송파 매핑, 프리코딩 및 안테나 매핑 기능부를 포함한다. 제2 계층 매핑 유닛으로부터 매핑된 비트는 제2 채널 인터리버 유닛(1436)에 의해 처리되어, (도시하지 않은) 제2 안테나 매핑 유닛으로 출력된다.

- [0068] 도 15는 대안적인 실시예에 따른 UCI 비트 매핑 방법(1500)의 블록도이다. 도 14에서, 2개의 계층 사이에 분할된 UCI 비트, 하나의 코드워드 및 적어도 2개의 송신 안테나를 갖는 랭크 2 시스템에 대응하는 2개의 계층이 있다. CQI/PMI 비트는 비교적 낮은 신호 및 간섭 대 잡음비(SINR)를 갖는 계층에서 송신되고, RI 및 ACK/NACK 비트는 비교적 높은 SINR을 갖는 계층에서 송신된다.

- [0069] TB1(1502)은 CRC 부착 기능부(1504)와 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1506)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(1508)에 의해 채널 코드화되고, 레이트 매칭 유닛(1510)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1512)에서 연결된다. 코드 블록 연결 유닛의 출력은 각 채널 코딩 유닛(1520, 1522)에서 채널 코드화된 HARQ ACK/NACK 비트(1518) 및 RI 비트(1516)와 함께 계층 매핑 유닛(1514)에서 비교적 낮은 SINR을 갖는 계층으로 매핑된다. 코드 블록 연결 유닛(1512)의 출력은 또한 데이터 및 제어 다중화 유닛(1524)에서 채널 코딩 유닛(1528)에서 채널 코드화된 CQI/PMI 비트(1526)와 다중화된다. 다중화된 비트는 계층 매핑 유닛(1530)에서 비교적 높은 SINR을 갖는 제1 계층으로 매핑된다. 제1 계층 매핑 유닛(1530)으로부터 매핑된 비트는 채널 인터리버 유닛(1532)에 의해 계층당(per layer) 처리되어, 제1 안테나 매핑 유닛(1534)으로 출력된다. 제2 계층 매핑 유닛(1514)으로부터 매핑된 비트는 제2 채널 인터리버(1536)에 의해 처리되어, (도시되지 않은) 제2 안테나 매핑 유닛으로 출력된다.

- [0070] 도 16은 다른 실시예에 따른 UCI 비트 송신 방법(1600)의 블록도이다. 도 16은 적어도 2개의 송신 안테나, 코

드워드당 하나의 계층으로 배열된 2개의 코드워드 및 하나의 계층으로 매핑된 UCI 비트를 포함하는 랭크 2 시스템에 대응하는 2개의 계층을 사용하는 시스템을 도시한다. UCI 비트는 높은 MCS 지수를 갖는 계층으로 매핑된다.

[0071] 도 16에 도시된 바와 같이, TB1(1602)은 CRC 부착 기능부(1604)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1606)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(1608)에 의해 채널 코드화되고, 레이트 매칭 유닛(1610)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1612)에서 연결된다. 처리된 TB1 비트는 이후 채널 코딩 유닛(1616)에서 채널 코드화된 CQI/PMI 비트(1615)와 함께 제어 및 데이터 다중화기(1614)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(1618)에서 비교적 높은 SINR, 즉 높은 MCS를 갖는 계층으로 매핑된다. RI 비트(1620)는 채널 코드화되고(1622), HARQ ACK/NACK 비트(1624)는 채널 코드화된다(1626). 코드화된 RI 비트 및 HARQ ACK/NACK 비트는 또한 제2 계층 매핑 유닛(1628)에서 비교적 높은 SINR, 즉 높은 MCS를 갖는 계층으로 매핑된다. 매핑된 TB1 비트 및 UCI 비트는 채널 인터리버 유닛(1630)에서 매핑된 RI 비트 및 HARQ ACK/NACK 비트와 함께 인터리빙되어, 단일 계층 출력력이 (도시하지 않은) 제1 안테나 매핑 유닛으로 보내진다.

[0072] TB2(1634)는 제2 코드워드로 매핑된 데이터를 포함하고, CRC 부착 기능부(1636)와 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1638)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(1640)에 의해 채널 코드화되고, 레이트 매칭 유닛(1642)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1644)에서 연결된다. 처리된 TB2 비트는 계층 매핑 유닛(1646)에서 비교적 낮은 SINR, 즉 낮은 MCS를 갖는 계층으로 계층 매핑되고, 채널 인터리버 유닛(1648)에서 인터리빙된다. 처리된 TB2 비트는 (도시하지 않은) 제2 안테나 매핑 유닛으로 출력된다.

[0073] 도 17은 다른 실시예에 따른 UCI 비트 송신 방법(1700)의 블록도이다. 도 17은 적어도 2개의 송신 안테나, 2개의 코드워드를 포함하는 랭크 2 시스템에 대응하는 2개의 계층을 사용하는 시스템을 도시한다. CQI/PMI 비트는 비교적 낮은 SINR, 즉 낮은 MCS를 갖는 계층으로 매핑되고, RI 및 ACK/NACK 비트는 비교적 높은 SINR, 즉 높은 MCS를 갖는 계층으로 매핑된다. 이러한 방법으로, RI 및 ACK/NACK 비트의 신뢰도가 향상될 수 있다.

[0074] 도 17에 도시된 바와 같이, TB1(1702)은 CRC 부착 기능부(1704)와 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1706)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(1708)에 의해 채널 코드화되고, 레이트 매칭 유닛(1710)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1712)에서 연결된다. 처리된 TB1 비트는 이후 채널 코딩 유닛(1718)에서 채널 코드화된 CQI/PMI 비트(1716)와 함께 제어 및 데이터 다중화기(1714)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(1720)에서 비교적 낮은 SINR, 즉 낮은 MCS를 갖는 계층으로 매핑된다. 매핑된 TB1 비트 및 CQI/PMI 비트는 채널 인터리버 유닛(1725)에서 인터리빙되어, 채널 인터리버 출력이 (도시하지 않은) 제1 안테나 매핑 유닛으로 보내진다.

[0075] TB2(1732)는 제2 코드워드로 매핑되고, CRC 부착 기능부(1734)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1736)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(1738)에 의해 채널 코드화되고, 레이트 매칭 유닛(1740)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1742)에서 연결된다. 처리된 TB2 비트는 계층 매핑 유닛(1744)에서 계층 매핑된다. 채널 코드화된 RI 비트(1722) 및 HARQ ACK/NACK 비트(1724)는 처리된 TB2 데이터 비트와 결합되어, 제2 계층 매핑 유닛(1727)에 의해 비교적 높은 SINR, 즉 높은 MCS를 갖는 계층으로 매핑된다. 이후 매핑된 비트는 채널 인터리버 유닛(1746)에서 인터리빙된 후, (도시하지 않은) 제2 안테나 매핑 유닛으로 출력된다.

[0076] 도 17의 대안적인 실시예에서, CQI/PMI 비트는 비교적 높은 SINR, 즉 높은 MCS를 갖는 계층으로 매핑된다. RI 및 ACK/NACK 비트는 비교적 낮은 SINR, 즉 낮은 MCS를 갖는 계층으로 매핑된다. 이러한 방법으로, CQI 비트의 신뢰도가 향상될 수 있다.

[0077] 도 18은 다른 실시예에 따른 UCI 비트 송신 방법의 블록도이다. 도 18은 적어도 3개의 송신 안테나, 2개의 코드워드 및 하나의 계층으로 매핑된 UCI 비트를 갖는 랭크 3의 시스템에 대응하는 3개의 계층을 사용하는 시스템을 도시한다. UCI 비트는 계층당(per layer) 높은 MCS 및 높은 SINR을 갖는 계층에서 송신된다. 제1 코드워드는 2개의 계층으로 매핑된다. 높은 SINR도 갖는 제1 코드워드에 의해 사용된 계층은 UCI 비트를 포함한다.

[0078] 코드화된 TB1(1802)은 CRC 부착 기능부(1804)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1806)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(1808)에 의해 채널 코드화되고, 레이트 매칭 유닛(1810)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1812)에서 연결된다. 처리된 TB1 비트는 2개의 스

트림으로 분할되고, 하나의 스트림은 이후 채널 코딩 유닛(1816)에서 채널 코드화된 UCI 비트(1818)와 함께 제어 및 데이터 다중화기(1814)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(1826)에서 비교적 높은 MCS 및 높은 SINR을 갖는 계층으로 매핑된다. 채널 코드화된 RI 비트 및 HARQ ACK/NACK 비트는 또한 제2 계층 매핑 유닛(1828)에서 비교적 높은 MCS 및 높은 SINR을 갖는 계층으로 매핑된다. 매핑된 TB1 비트 및 UCI 비트(CQI/PMI, RI 및 HARQ ACK/NACK 비트) 그룹은 채널 인터리버 유닛(1832)에서 인터리빙된 후, (도시하지 않은) 안테나 매핑 유닛으로 출력된다. 안테나 매핑 유닛은 도 7 및 도 9에 도시된 바와 같이 변조, 부반송파 매핑, 프리코딩 및 안테나 매핑 기능부를 포함한다.

[0079] TB2(1838)는 제2 코드워드로 매핑되고, CRC 부착 기능부(1840)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1842)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(1844)에 의해 채널 코드화되고, 레이트 매칭 유닛(1846)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1848)에서 연결된다. 처리된 TB2 비트는 매핑 유닛(1850)에서 비교적 낮은 MCS를 갖는 계층으로 매핑되고, 채널 인터리버 유닛(1852)에서 인터리빙된다. 제2 코드워드로 매핑되어 처리된 TB2 비트는 이후 (도시하지 않은) 안테나 매핑 유닛으로 출력된다.

[0080] 도 19는 다른 실시예에 따른 UCI 비트 송신 방법(1900)의 블록도이다. 도 19에서, 이 시스템은 2개의 코드워드 및 3개의 계층(즉, 3 이상의 송신 안테나를 위한 랭크 3)을 사용한다. TB1 비트와 다중화된 UCI 비트는 높은 MCS를 갖는 제1 코드워드로 매핑된다. 제1 코드워드에는 단 하나의 계층만이 할당되기 때문에, CQI/PMI 비트는 제1 코드워드의 하나의 계층으로 매핑되고, RI 및 ACK/NACK 비트 또한 제1 코드워드의 동일 계층으로 매핑된다.

[0081] 도 19에 도시된 바와 같이, TB1(1902)은 CRC 부착 기능부(1904)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1906)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(1908)에 의해 채널 코드화되고, 레이트 매칭 유닛(1910)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1912)에서 연결된다. 처리된 TB1 비트는 이후 채널 코딩 유닛(1930)에서 채널 코드화된 UCI 비트(1928)와 함께 제어 및 데이터 다중화기(1914)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(1916)에서 비교적 높은 MCS를 갖는 계층으로 매핑된다. RI 비트(1926) 및 HARQ ACK/NACK 비트(1924)는 각각의 채널 코딩 유닛(1920, 1922)에 의해 각각 코드화된다. 채널 코드화된 RI 비트 및 HARQ ACK/NACK 비트는 또한 제2 계층 매핑 유닛(1918)에서 비교적 높은 MCS를 갖는 계층으로 매핑된다. 매핑된 TB1 비트 및 UCI 비트(CQI/PMI, RI 및 HARQ ACK/NACK 비트)는 채널 인터리버 유닛(1932)에서 인터리빙된 후, 단일 계층 출력이 (도시되지 않은) 안테나 매핑 유닛으로 보내진다.

[0082] TB2(1936)는 제2 코드워드로 매핑되고, CRC 부착 기능부(1938)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(1940)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(1942)에 의해 채널 코드화되고, 레이트 매칭 유닛(1944)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(1946)에서 연결된다. 처리된 TB2 비트는 분할기(1947)에서 2개의 스트림으로 분할되고, 계층 매핑 유닛(1948, 1950)에서 각각 계층 매핑된다. 이후 매핑된 비트는 각각의 채널 인터리버 유닛(1952, 1954)에서 인터리빙된다. 2개의 계층을 갖는 제2 코드워드로 매핑되어 처리된 TB2 비트는 이후 (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

[0083] 도 20은 다른 실시예에 따른 UCI 비트(CQI/PMI, RI 및 HARQ ACK/NACK 비트) 송신 방법(2000)의 블록도이다. 도 20은 3 이상의 안테나, 2개의 코드워드 및 제1 코드워드의 2개의 계층으로 매핑된 UCI 비트에 대하여 3개의 계층을 사용하는 시스템을 도시한다. UCI 비트는 제1 코드워드의 2개의 계층에 걸쳐 반복된다. 또는 UCI 비트는 2개의 그룹으로 분할되고, 각 그룹의 비트는 비교적 높은 MCS를 갖는 코드워드의 하나의 계층으로 각각 분산된다. 각 그룹의 비트 크기는 동일하거나 계층의 SINR에 기초하여 대안적으로 결정될 수 있다.

[0084] TB1(2002)은 CRC 부착 기능부(2004)에 의해 처리된 후, 코드 블록 시퀀스 및 코드 블록 CRC 부착 기능부(2006)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2008)에 의해 채널 코드화되고, 레이트 매칭 유닛(2010)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2012)에서 연결된 후, 2개의 그룹으로 분할된다. 채널 코딩 유닛(2014)에서 채널 코드화된 반복된 CQI/PMI 비트(2013) (또는 2개의 그룹으로 분할된 CQI/PMI 비트) 및 처리된 TB1 비트의 각 그룹은 제1 데이터 및 제어 다중화기(2020) 및 제2 데이터 및 제어 다중화기(2022)로 입력된다. 제3 채널 코딩 유닛(2016)에서 채널 코드화된 반복된 RI 비트(2024)와 함께 다중화된 비트 및 제4 채널 코딩 유닛(2018)에서 코드화된 HARQ ACK/NACK 비트(2026) (또는 2개의 그룹으로 분할된 HARQ ACK/NACK 비트 및 채널 코드화된 RI 비트)는 이후 제1 계층 매핑 유닛(2030) 및 제2 계층 매핑 유닛(2032)에서 비교적 높은 MCS를 갖는 계층으로 매핑된다.

[0085] 매핑된 TB1 비트, CQI/PMI 비트, RI 비트 및 HARQ ACK/NACK 비트는 제1 및 제2 채널 인터리버 유닛(2033, 2034)에서 인터리빙되어, 각 계층의 출력이 (도시되지 않은) 안테나 매핑 유닛으로 보내진다.

- [0086] TB2(2040)는 단 하나의 계층만을 갖는 제2 코드워드로 매핑되고, CRC 부착 기능부(2042)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2044)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2046)에 의해 채널 코드화되고, 레이트 매칭 유닛(2048)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2050)에서 연결된다. 처리된 TB2 비트는 계층 매핑 유닛(2052)에서 비교적 낮은 MCS를 갖는 계층으로 매핑되고, 채널 인터리버 유닛(2054)에서 인터리빙된다. 제2 코드워드로 매핑되어 처리된 TB2 비트는 이후 (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

- [0087] 도 21은 다른 실시예에 따른 UCI 비트 송신 방법(2100)의 블록도이다. 도 21은 3 이상의 안테나, 2개의 코드워드 및 높은 MCS를 갖는 코드워드로 매핑된 UCI 비트에 대하여 3개의 계층을 사용하는 시스템을 도시한다. 높은 MCS를 갖는 코드워드는 2개의 계층으로 매핑된다. CQI/PMI 비트는 높은 MCS를 갖는 코드워드에서 낮은 SINR을 갖는 계층으로 매핑된다. RI 및 ACK/NACK 비트는 높은 MCS를 갖는 코드워드에서 높은 SINR을 갖는 계층으로 매핑된다. RI 및 ACK/NACK 비트를 (높은 MCS를 갖는 코드워드에서) 높은 SINR을 갖는 계층에 매핑시키면, RI 및 ACK/NACK 비트의 수신 신뢰도가 증가된다.

- [0088] 도 20에 도시된 바와 같이, TB1은 CRC 부착 기능부(2104)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2106)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2108)에 의해 채널 코드화되고, 레이트 매칭 유닛(2110)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2112)에서 연결된다. 처리된 TB1 비트는 2개의 스트림으로 분할된 후, 하나의 스트림은 채널 코딩 유닛(2118)에서 채널 코드화된 CQI/PMI 비트(2116)와 함께 제어 및 데이터 부호화기(2114)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(2120)에서 비교적 높은 MCS를 갖는 코드워드에서 비교적 낮은 SINR을 갖는 계층으로 매핑된다. RI 비트(2124)는 제2 채널 코딩 유닛(2126)에서 채널 코드화된다. HARQ ACK/NACK 비트(2128)는 제3 채널 코딩 유닛(2130)에서 채널 코드화된다. 채널 코드화된 RI 비트, HARQ ACK/NACK 비트 및 처리된 TB1 비트의 다른 스트림은 제2 계층 매핑 유닛(2132)에서 비교적 높은 MCS를 갖는 코드워드에서 비교적 높은 SINR을 갖는 계층으로 매핑된다. 제1 그룹의 매핑된 TB1 비트 및 CQI/PMI 비트는 제1 채널 인터리버 유닛(2134)에서 인터리빙되어, 단일 계층 출력이 제1 안테나 매핑 유닛(2136)으로 보내진다. 제2 그룹의 매핑된 TB1 비트, RI 및 HARQ ACK/NACK 비트는 제2 채널 인터리버 유닛(2138)에서 인터리빙되어, 단일 계층 출력이 (도시하지 않은) 안테나 매핑 유닛으로 보내진다.

- [0089] TB2(2142)는 제2 코드워드로 매핑되고, CRC 부착 기능부(2144)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2146)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2148)에 의해 채널 코드화되고, 레이트 매칭 유닛(2150)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2152)에서 연결된다. 처리된 TB2 비트는 계층 매핑 유닛(2154)에서 비교적 낮은 MCS를 갖는 제2 코드워드의 계층으로 매핑되고, 채널 인터리버 유닛(2156)에서 인터리빙된다. 제2 코드워드로 매핑되어 처리된 TB2 비트는 이후 (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

- [0090] 도 22는 다른 실시예에 따른 UCI 비트 송신 방법(2200)의 블록도이다. 도 22는 4 이상의 안테나, 2개의 코드워드 및 높은 MCS 및 SINR을 갖는 계층으로 매핑된 UCI 비트에 대하여 4개의 계층, 즉 랭크 4를 사용하는 시스템을 도시한다.

- [0091] 도 22에 도시된 바와 같이, TB1은 CRC 부착 기능부(2204)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2206)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2208)에 의해 채널 코드화되고, 레이트 매칭 유닛(2210)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2212)에서 연결된다. 처리된 TB1 비트는 2개의 스트림으로 분할된 후, 하나의 스트림은 채널 코딩 유닛(2216)에서 채널 코드화된 CQI/PMI 비트(2214)와 함께 제어 및 데이터 다중화기(2213)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(2218)에서 비교적 높은 MCS 및 가장 높은 SINR을 갖는 계층으로 매핑된다. RI 비트(2219)는 다른 채널 코딩 유닛(2220)에서 채널 코드화되고, HARQ ACK/NACK 비트(2222)는 또 다른 채널 코딩 유닛(2224)에서 채널 코드화된다. 채널 코드화된 RI 비트 및 HARQ ACK/NACK 비트는 또한 제1 계층 매핑 유닛(2218)에서 비교적 높은 MCS 및 높은 SINR을 갖는 동일 계층으로 매핑된다. 매핑된 TB1 비트, CQI/PMI 비트, RI 비트 및 HARQ ACK/NACK 비트는 채널 인터리버 유닛(2226)에서 인터리빙되어, 단일 계층 출력이 안테나 매핑 유닛(2228)으로 보내진다. 처리된 TB1 비트의 다른 스트림은 또한 제2 계층 매핑 유닛(2230)에서 높은 MCS지만, 비교적 낮은 SINR을 갖는 계층으로 매핑된다. 매핑된 비트는 채널 인터리버 유닛에서 인터리빙되어, (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

- [0092] TB2(2234)는 제2 코드워드로 매핑되고, CRC 부착 기능부(2236)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2238)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2240)에 의해 채널 코드화되고,

레이트 매칭 유닛(2242)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2244)에서 연결된다. 처리된 TB2 비트는 2개의 그룹으로 분할된다. 2개의 그룹의 비트는 각각의 계층 매핑 유닛(2246, 2248)에서 낮은 MCS를 갖는 2개의 계층으로 각각 매핑되고, 채널 인터리버 유닛(2250, 2252)에서 인터리빙된다. 제2 코드워드로 매핑되어 처리된 TB2 비트는 이후 (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

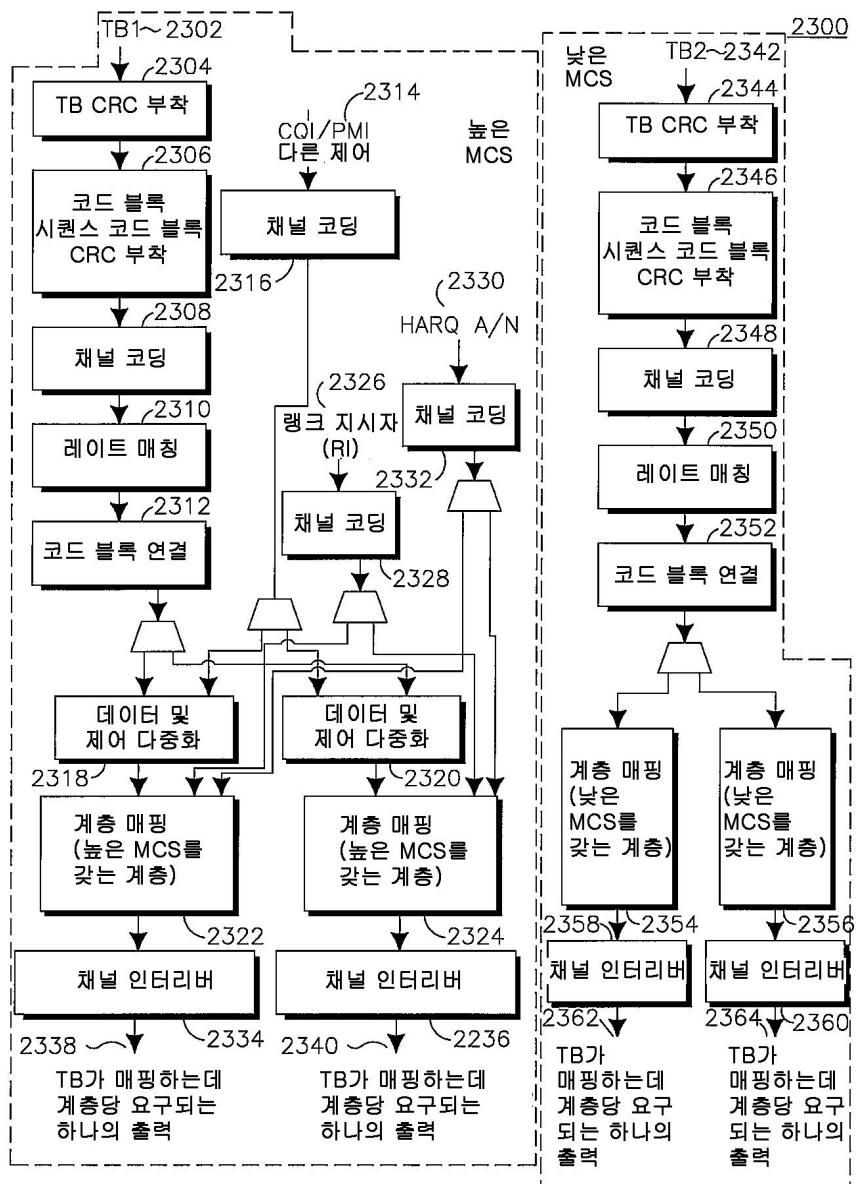

[0093] 도 23은 다른 실시예에 따른 UCI 비트 (CQI/PMI, RI 및 HARQ ACK/NACK 비트) 송신 방법(2300)의 블록도이다. 도 23은 4 이상의 안테나 및 하나의 코드워드 및 2개의 계층으로 매핑된 UCI 비트에 대하여 2개의 코드워드, 4 개의 계층, 즉 랭크 4를 사용하는 시스템을 도시한다. UCI 비트는 반복되고, 비교적 높은 MCS를 갖는 코드워드의 2개의 계층으로 매핑된다. 또는 UCI 비트는 2개의 스트림으로 분할되고, 각 스트림의 비트는 높은 MCS를 갖는 코드워드의 계층으로 각각 분산된다. 스트림은 동일한 길이이거나 또는 대안적으로 스트림의 길이는 계층의 SINR에 기초하여 결정될 수 있다.

[0094] 도 23에 도시된 바와 같이, TB1(2302)은 CRC 부착 기능부(2304)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2306)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2308)에 의해 채널 코드화되고, 레이트 매칭 유닛(2310)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2312)에서 연결된 후, 2개의 그룹으로 분할된다. 채널 코딩 유닛(2316)에서 채널 코드화된 반복된 CQI/PMI 비트(2314) (또는 2개의 그룹으로 분할된 CQI/PMI 비트) 및 처리된 TB1 비트의 각 그룹은 이후 제1 제어 및 데이터 다중화기(2318) 및 제2 제어 및 데이터 다중화기(2320)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(2322) 및 제2 계층 매핑 유닛(2324)에서 비교적 높은 MCS를 갖는 2개의 계층으로 매핑된다. RI 비트(2326)는 다른 채널 코딩 유닛(2328)에서 채널 코드화되고, HARQ ACK/NACK 비트(2330)는 또 다른 채널 코딩 유닛(2332)에서 채널 코드화된다. 채널 코드화된 RI 비트 및 HARQ ACK/NACK 비트는 또한 제1 및 제2 계층 매핑 유닛(2322, 2324)에서 비교적 높은 MCS를 갖는 각 계층으로 매핑된다. 매핑된 TB1 비트, UCI 비트, RI 비트 및 HARQ ACK/NACK 비트는 제1 인터리빙 유닛(2334) 및 제2 채널 인터리버 유닛(2336)에서 인터리빙되고, 각 채널 인터리버 유닛의 출력이 (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

[0095] TB2(2342)는 제2 코드워드로 매핑되고, CRC 부착 기능부(2344)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2346)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2348)에 의해 채널 코드화되고, 레이트 매칭 유닛(2350)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2352)에서 연결된다. 처리된 TB2 비트는 2개의 그룹으로 분할된 후, 각각 제1 및 제2 계층 매핑 유닛(2354, 2356)에서 비교적 낮은 MCS를 갖는 계층으로 매핑되고, 제1 및 제2 채널 인터리버 유닛(2358, 2360)에서 인터리빙된다. 제2 코드워드로 매핑되어 처리된 TB2 비트는 (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

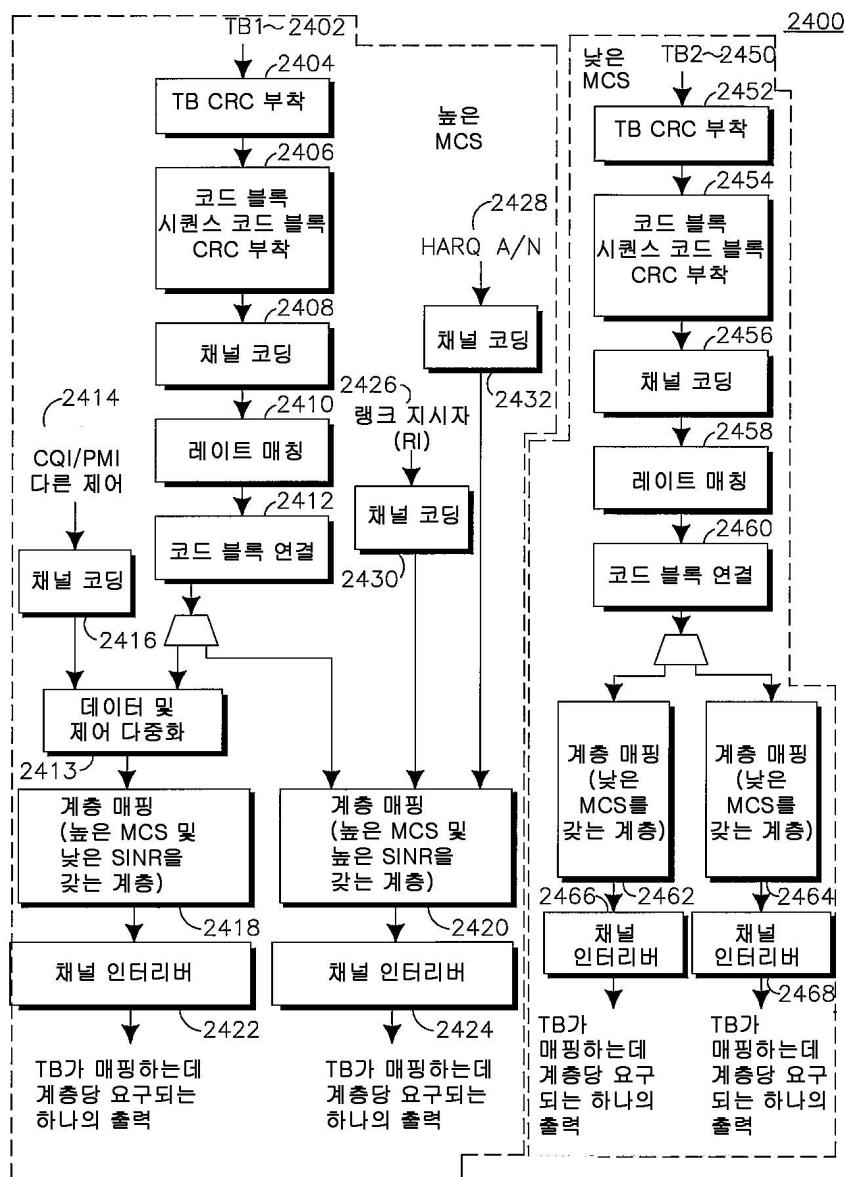

[0096] 도 24는 다른 실시예에 따른 UCI 비트 송신 방법의 블록도이다. 도 24는 4 이상의 안테나, 2개의 코드워드 및 가장 높은 MCS를 갖는 코드워드의 2개의 계층 사이에 분할된 UCI 비트에 대하여 4개의 계층을 사용하는 시스템을 도시한다. CQI/PMI 비트는 낮은 SINR을 갖는 제1 계층으로 매핑된다. RI 비트 및 ACK/NACK 비트는 높은 SINR을 갖는 제2 계층으로 매핑된다. TB의 데이터 비트는 2개의 그룹으로 분할되고, 2개의 계층으로 매핑된다. 제어 비트의 HARQ ACK/NACK 및 RI 그리고 데이터 비트는 상이한 프리코딩 구성으로 처리될 수 있다.

[0097] 도 24에 도시된 바와 같이, TB1(2402)은 CRC 부착 기능부(2404)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2406)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2408)에 의해 채널 코드화되고, 레이트 매칭 유닛(2410)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2412)에서 연결된다. 처리된 TB1 비트는 2개의 그룹으로 분할되고, 한 그룹의 비트는 채널 코딩 유닛(2416)에서 채널 코드화된 CQI/PMI 비트(2414)와 함께 제어 및 데이터 다중화기(2413)로 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(2418)에서 비교적 높은 MCS 및 낮은 SINR을 갖는 계층으로 매핑된다. 다른 채널 코딩 유닛(2430, 2432)에서 채널 코드화된 RI 비트(2426) 및 HARQ ACK/NACK 비트(2428)는 또한 다른 그룹의 처리된 TB1 비트와 함께 제2 계층 매핑 유닛(2420)에서 비교적 높은 MCS지만 높은 SINR을 갖는 계층으로 매핑된다. 제1 그룹의 매핑된 TB1 비트 및 CQI/PMI 비트는 제1 채널 인터리버 유닛(2422)에서 인터리빙된다. RI 및 HARQ ACK/NACK 비트를 갖는 제2 그룹의 매핑된 TB1 비트는 제2 채널 인터리버 유닛(2424)에서 인터리빙된다. 각 채널 인터리버 유닛(2422, 2424)의 출력은 (도시되지 않은) 안테나 매핑 유닛으로 보내진다.

[0098] TB2(2450)는 제2 코드워드로 매핑되고, CRC 부착 기능부(2452)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2454)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2456)에 의해 채널 코드화되고, 레이트 매칭 유닛(2458)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2460)에서 연결된다. 처리된 TB2 비트는 2개의 그룹으로 분할되고, 제1 계층 매핑 유닛(2462) 및 제2 계층 매핑 유닛(2464)에서 낮은 MCS를 갖는

2개의 계층으로 계층 매핑되고, 제1 인터리빙 유닛(2466) 및 제2 채널 인터리버 유닛(2468)에서 인터리빙된다. 인터리빙된 TB2 비트는 (도시되지 않은) 안테나 매핑 유닛으로 출력된다.

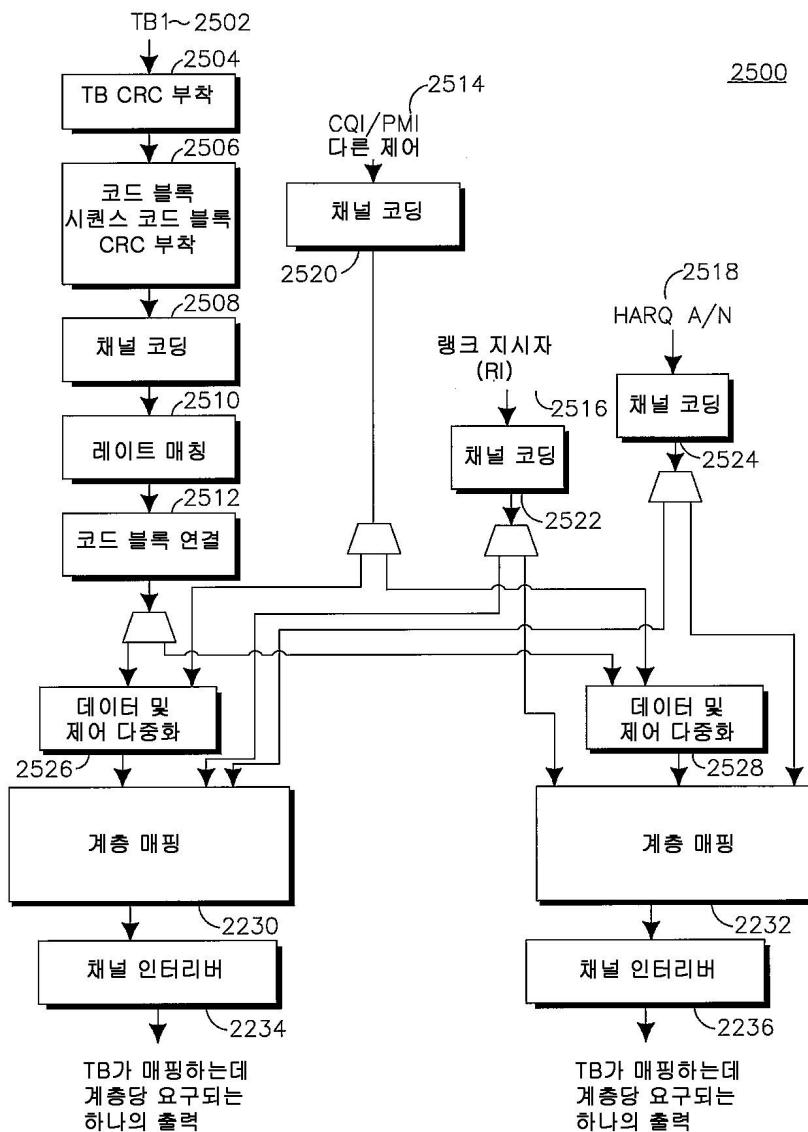

[0099] 도 25는 다른 실시예에 따른 UCI 비트 송신 방법(2500)의 블록도이다. 도 25는 2 이상의 안테나, 하나의 코드워드 및 2개의 계층에 걸쳐 매핑된 UCI 비트에 대하여 2개의 계층, 즉 랭크 2를 사용하는 시스템을 도시한다. UCI 비트는 모든 계층 및 모든 코드워드에 걸쳐 반복되거나 분산된다. 분산 구성은 코드워드당 또는 계층당, 또는 예를 들어, MCS, 이송 블록 크기나 SINR과 같은 파라미터에 기초하여 코드워드나 각 계층에 복수의 제어비트를 할당함으로써, 동일한 양의 제어 비트를 사용할 수 있다.

[0100] 도 25에 도시된 바와 같이, TB1(2502)은 CRC 부착 기능부(2504)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2506)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2508)에 의해 채널 코드화되고, 레이트 매칭 유닛(2510)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2512)에서 연결된다. UCI 비트(2514, 2516, 2518)는 각각 채널 코딩 유닛(2520, 2522, 2524)에서 채널 코드화된다. 처리된 TB1 비트는 2개의 스트림으로 분할된다. UCI 비트는 반복되거나 또는 2개의 스트림으로 각각 분할된다. TB1 비트의 하나의 스트림은 반복되거나 분할된 CQI/PMI 비트의 하나의 스트림과 함께 제1 및 제2 제어 및 데이터 다중화기(2526, 2528)로 입력된다. 다중화된 비트는 이후 제1 및 제2 계층 매핑 유닛(2530, 2532)에서 반복되거나 분할되어 코드화된 HARQ ACK/NACK 비트 및 코드화된 RI 비트와 함께 2개의 계층으로 매핑된다. 매핑된 TB1 비트, CQI/PMI 비트, RI 비트 및 HARQ ACK/NACK 비트는 제1 및 제2 채널 인터리버 유닛(2534, 2536)에서 처리된 후, (도시하지 않은) 안테나 매핑 유닛으로 출력된다.

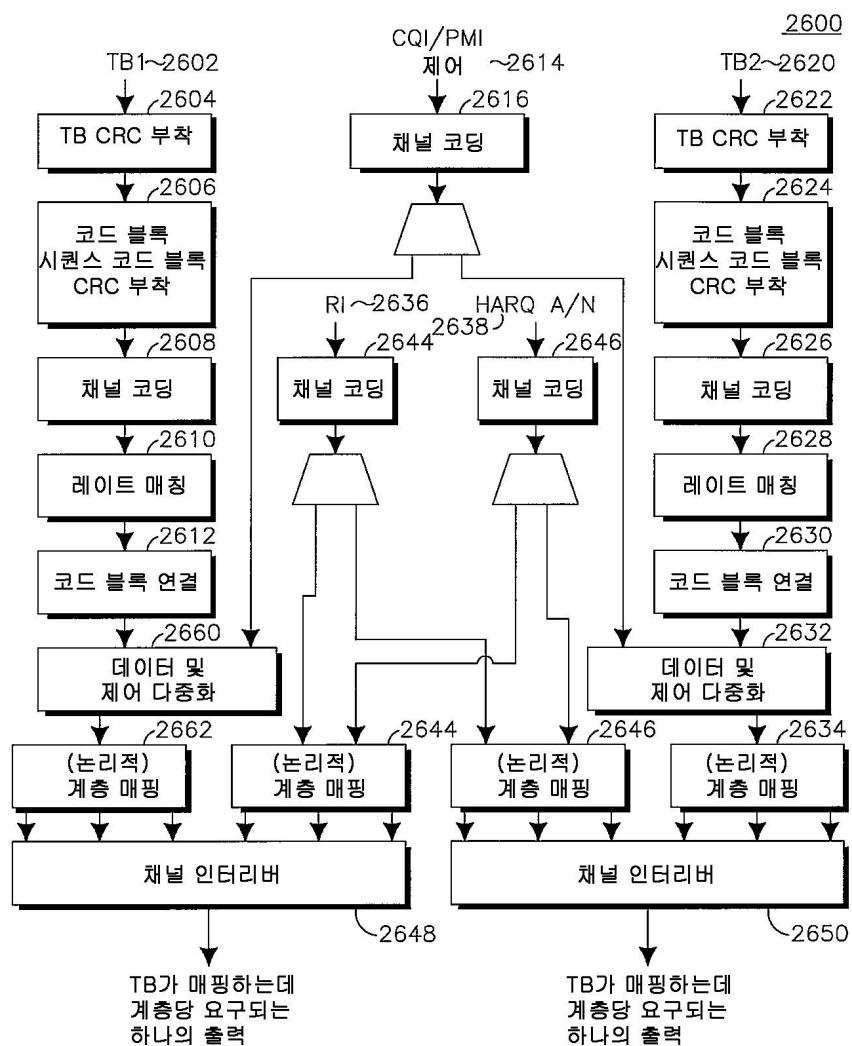

[0101] 도 26은 다른 실시예에 따른 UCI 비트 송신 방법(2600)의 블록도이다. 도 26은 2 이상의 안테나, 2개의 코드워드 및 모든 계층에 걸쳐 매핑된 UCI 비트에 대하여 2개의 계층, 즉 랭크 2를 사용하는 시스템을 도시한다.

[0102] 도 26에 도시된 바와 같이, TB1(2602)은 CRC 부착 기능부(2604)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2606)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2608)에 의해 채널 코드화되고, 레이트 매칭 유닛(2610)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2612)에서 연결된다. CQI/PMI 비트(2614)는 채널 코딩 유닛(2616)에서 채널 코드화되어, 2개의 스트림으로 분할된다. 처리된 TB1 비트는 이후 CQI/PMI 비트의 (제1) 스트림과 함께 제어 및 데이터 다중화기(2660)에 입력된다. 다중화된 비트는 이후 제1 계층 매핑 유닛(2662)에서 하나의 계층으로 매핑된다.

[0103] TB2(2620)는 제2 코드워드로 매핑되고, CRC 부착 기능부(2622)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2624)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2626)에 의해 채널 코드화되고, 레이트 매칭 유닛(2628)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2630)에서 연결된다. 처리된 TB2 비트는 제2 데이터 및 제어 다중화기(2632)에서 CQI/PMI 비트의 다른 (제2) 스트림과 다중화된다. 다중화된 비트는 제2 계층 매핑 유닛(2634)에서 매핑된다.

[0104] RI 비트(2636) 및 HARQ ACK/NACK 비트(2638)는 채널 코드화되어(2640, 2642), 2개의 스트림으로 분할되고, 제3 및 제4 계층 매핑 유닛(2644, 2646)에서 각각 2개의 계층으로 매핑된다. 매핑된 TB1 비트, CQI/PMI 비트의 제1 스트림, RI 비트의 제1 스트림 및 HARQ ACK/NACK 비트의 제1 스트림은 제1 채널 인터리버 유닛(2648)에서 인터리빙되어, (도시하지 않은) 안테나 매핑 유닛으로 출력된다. 매핑된 TB2 비트, CQI/PMI 비트의 제2 스트림, RI 비트의 제2 스트림 및 HARQ ACK/NACK 비트의 제2 스트림은 제2 채널 인터리버 유닛(2650)에서 인터리빙되어, (도시하지 않은) 안테나 매핑 유닛으로 출력된다.

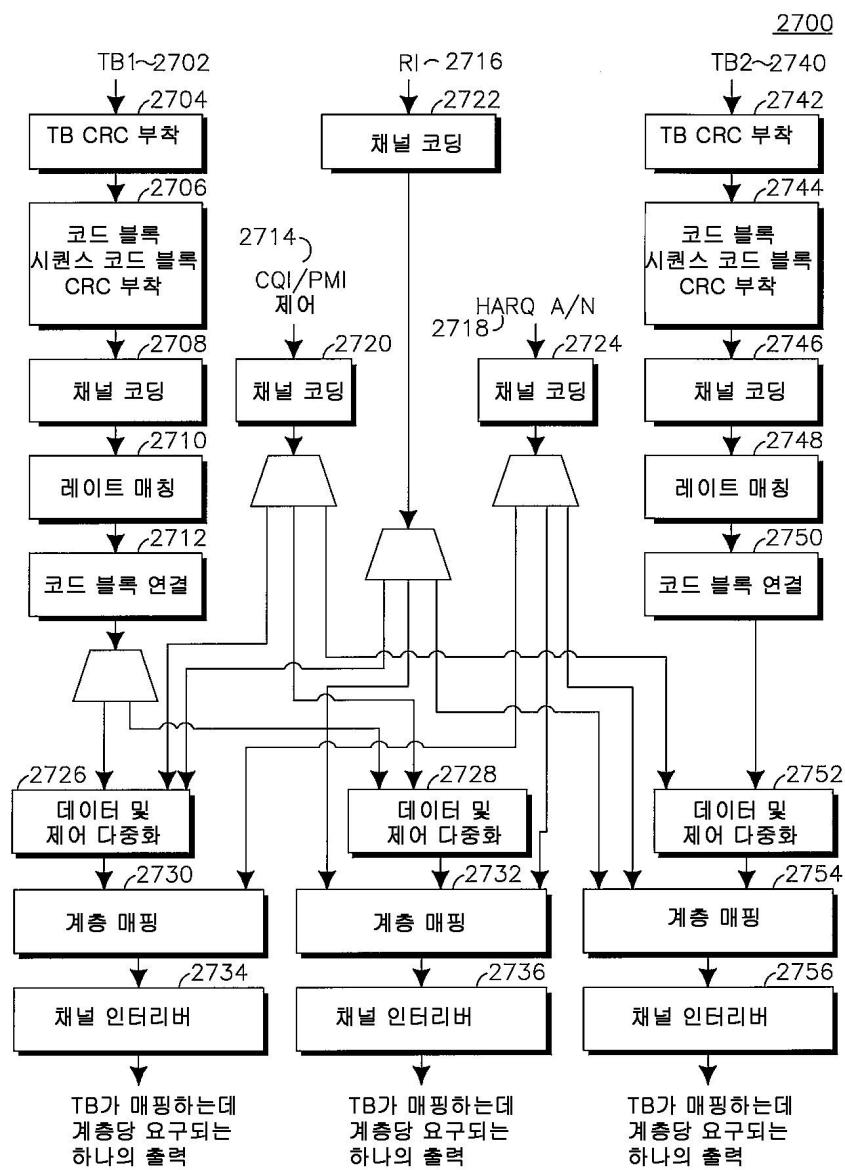

[0105] 도 27은 다른 실시예에 따른 UCI 비트 송신 방법(2700)의 블록도이다. 도 27은 3 이상의 안테나, 2개의 코드워드 및 3개의 계층에 걸쳐 매핑된 UCI 비트에 대하여 3개의 계층, 즉 랭크 3을 갖는 시스템을 도시한다.

[0106] 도 27에 도시된 바와 같이, TB1(2702)은 CRC 부착 기능부(2704)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2706)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2708)에 의해 채널 코드화되고, 레이트 매칭 유닛(2710)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2712)에서 연결된다. 처리된 TB1 비트는 2개의 스트림으로 분할된다. UCI 비트(2714, 2716, 2718)는 채널 코딩 유닛(2720, 2722, 2724)에서 각각 채널 코드화되고, 각각 반복되거나 3개의 스트림으로 분할된다. TB1 비트의 2개의 그룹은 CQI/PMI 비트의 2개의 그룹과 함께 제1 및 제2 제어 및 데이터 다중화기(2726, 2728)로 입력된다. 다중화된 비트는 이후 코드화된 HARQ ACK/NACK 비트 및 코드화된 RI 비트의 2개의 스트림과 함께 제1 및 제2 계층 매핑 유닛(2730, 2732)에서 2개의 계층으로 매핑된다. 각 계층 매핑 유닛의 출력은 채널 인터리빙 유닛(2734, 2736)에 의해 처리된 후, (도시되지 않은) 안테나 매핑 유닛으로 보내진다.

- [0107] TB2(2740)는 제2 코드워드로 매핑되고, CRC 부착 기능부(2742)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2744)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2746)에 의해 채널 코드화되고, 레이트 매칭 유닛(2748)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2750)에서 연결된다. 처리된 TB2 비트는 제3 데이터 및 제어 다중화기(2752)에서 코드화된 CQI/PMI 비트의 나머지/제3 스트림과 다중화된다. 다중화된 TB2 및 CQI/PMI 비트는 코드화된 RI 비트 및 HARQ ACK/NACK 비트의 나머지/제3 스트림과 함께 계층 매칭 유닛(2754)에서 매핑된다. 각 계층 매핑 유닛의 출력은 채널 인터리빙 유닛(2756)에 의해 처리된 후, (도시하지 않은) 안테나 매핑 유닛으로 보내진다.

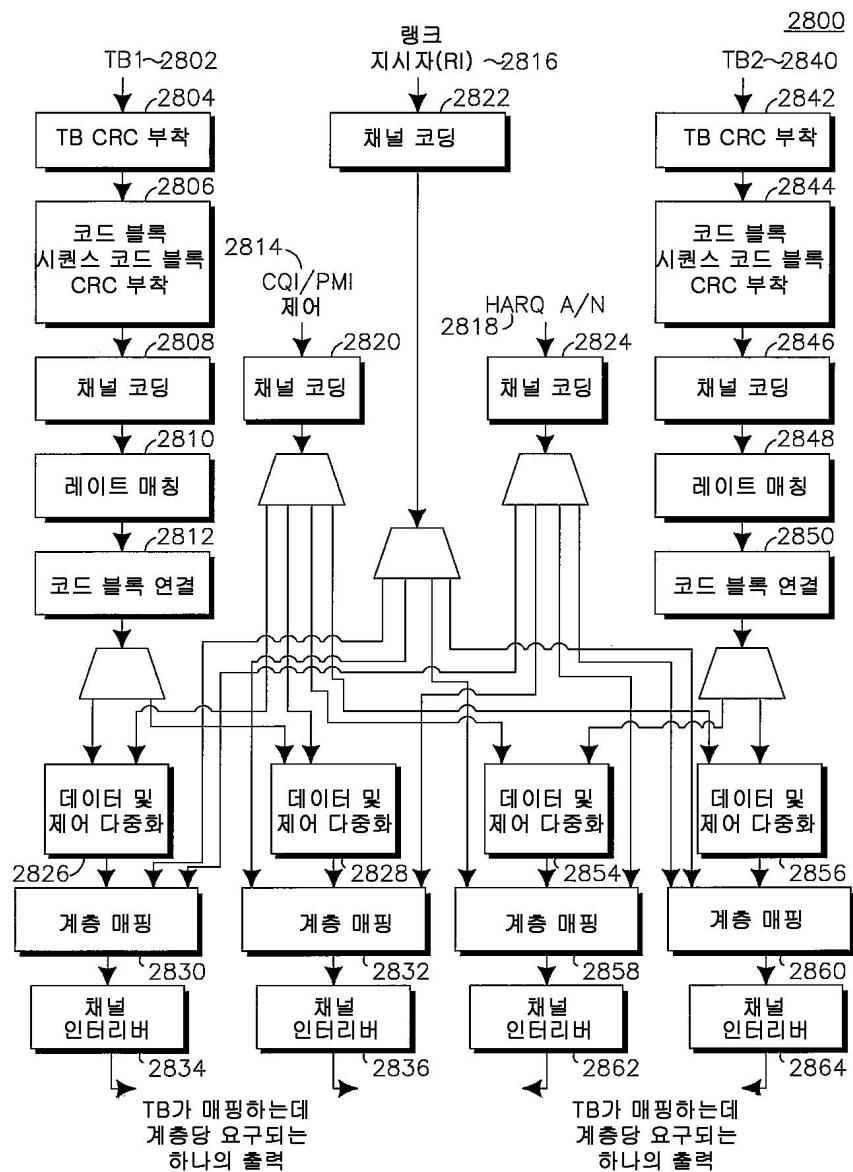

- [0108] 도 28은 다른 실시예에 따른 UCI 비트 송신 방법(2800)의 블록도이다. 도 28은 4 이상의 안테나, 2개의 코드워드 및 4개의 계층에 걸쳐 매핑된 UCI 비트에 대하여 4개의 계층, 즉 랭크 4를 갖는 시스템을 도시한다.

- [0109] 도 28에 도시된 바와 같이, TB1(2802)은 CRC 부착 기능부(2804)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2806)에 의해 처리된다. 처리된 TB1 비트는 채널 코딩 유닛(2808)에 의해 채널 코드화되고, 레이트 매칭 유닛(2810)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2812)에서 연결된다. 처리된 TB1 비트는 2개의 스트림으로 분할된다. UCI 비트(2814, 2816, 2818)는 각각 채널 코딩 유닛(2820, 2822, 2818)에서 채널 코드화되고, 각각 반복되거나 4개의 스트림으로 분할된다. TB1 비트의 2개의 스트림은 CQI/PMI 비트의 2개의 스트림과 함께 제1 및 제2 제어 및 데이터 다중화기(2826, 2828)로 입력된다. 이후 각각 다중화된 비트 스트림은 코드화된 RI 비트의 하나의 스트림 및 코드화된 HARQ ACK/NACK 비트의 하나의 스트림과 함께 계층 매핑 유닛(2830, 2832)에서 제1 및 제2 계층 중 하나의 계층으로 매핑된다. 제1 및 제2 계층 매핑 유닛(2830, 2832)의 각각의 출력은 각각의 채널 인터리빙 유닛(2834, 2836)에 의해 처리된 후, (도시하지 않은) 안테나 매핑 유닛으로 보내진다.

- [0110] TB2(2840)는 제2 코드워드로 매핑되고, CRC 부착 기능부(2842)에 의해 처리된 후, 코드 블록 분할 및 코드 블록 CRC 부착 기능부(2844)에 의해 처리된다. 처리된 TB2 비트는 채널 코딩 유닛(2846)에 의해 채널 코드화되고, 레이트 매칭 유닛(2848)에서 레이트 매칭이 이루어지며, 코드 블록 연결 유닛(2850)에서 연결된다. 처리된 TB2 비트는 2개의 스트림으로 분할된다. 처리된 TB2 비트는 이후 CQI/PMI 비트의 2개의 나머지 스트림과 함께 제3 및 제4 제어 및 데이터 다중화기(2854, 2856)로 입력된다. 각각 다중화된 비트 스트림은 이후 코드화된 RI 비트의 하나의 스트림 및 코드화된 HARQ ACK/NACK 비트의 하나의 스트림과 함께 제3 및 제4 계층 매핑 유닛(2858, 2860)에서 하나의 계층으로 매핑된다. 각각의 계층 매핑 유닛의 출력은 제3 및 제4 채널 인터리빙 유닛(2862, 2864)에 의해 처리된 후, (도시하지 않은) 안테나 매핑 유닛으로 보내진다.

- [0111] 제어 비트가 데이터 비트와 다중화될 때, 제어 비트는 데이터 비트와는 상이한 MIMO 모드를 사용하여 송신될 수 있다. 이는 비트가 하나의 서브 프레임에서 송신되더라도 일어날 수 있다. 예를 들어, 프리코딩 MIMO 모드가 데이터 비트에 대하여 사용되는 동안, 제어 비트는 송신 다이버시티를 사용하여 송신될 수 있다. WTRU는, 예를 들어, 계층 1이나 계층 2 메시지 중의 하나의 eNodeB로부터 어떤 형태의 비트에 대하여 어떤 MIMO 모드를 사용할지에 관한 정보를 수신할 수 있다.

- [0112] 특징 및 구성요소가 특정 조합으로 위에서 설명되었지만, 각 특징이나 구성요소는 다른 특징이나 구성요소 없이 단독으로, 또는 다른 특징 및 구성요소와의 다양한 조합이나 다른 특징 및 구성요소 없이 다양한 조합으로 사용될 수 있다. 여기서 제공된 방법이나 흐름도는 컴퓨터 프로그램, 소프트웨어, 또는 범용 컴퓨터나 프로세서에 의해 구동되는 컴퓨터 관독가능 저장 매체에 내재된 펌웨어로 구현될 수 있다. 컴퓨터 관독가능 저장 매체의 예는 ROM, RAM, 레지스터, 캐시 메모리, 반도체 메모리 장치, 내부 하드디스크 및 탈착가능 디스크와 같은 자기 매체, 광자기 매체 및 CD-ROM 및 DVD와 같은 광학 매체를 포함한다.

- [0113] 적합한 프로세서는 예컨대 범용 프로세서, 특수 목적용 프로세서, 종래의 프로세서, DSP, 다수의 마이크로프로세서, DSP 코어와 관련된 하나 이상의 마이크로 프로세서, 제어기, 마이크로제어기, ASIC, FPGA 회로, 다른 형태의 IC 및/또는 상태 머신을 포함한다.

- [0114] 소프트웨어와 관련된 프로세서는 무선 송수신 유닛(WTRU), 사용자 장비(UE), 단말기, 기지국, 무선 네트워크 제어기(RNC), 또는 임의의 호스트 컴퓨터에서 사용되는 RF 송수신기를 구현하기 위해 사용될 수 있다. WTRU는 카메라, 비디오 카메라 모듈, 비디오폰, 스피커폰, 진동 장치, 스피커, 마이크, 텔레비전 송수신기, 핸즈 프리 헤드셋, 키보드, 블루투스 모듈, FM 라디오 유닛, LCD 디스플레이 유닛, OLED 디스플레이 유닛, 디지털 음악 재생기, 미디어 재생기, 비디오 게임 재생기 모듈, 인터넷 브라우저, 및/또는 임의의 WLAN이나 UWB(Ultra Wide Band) 모듈과 같은 하드웨어 및/또는 소프트웨어로 구현되는 모듈과 결합되어 사용될 수 있다.

실시예

[0115] 1. 본 발명은 LTE-A 물리적 업링크 공유 채널(PUSCH)에 대하여 데이터 및 제어 다중화를 수행하는 방법에 관한 것으로, 이 방법은 하나 이상의 코드워드의 적어도 하나의 코드화된 데이터 비트 및 적어도 하나의 코드화된 제어 비트를 처리하는 단계를 포함하고, 코드화된 데이터 비트 및 코드화된 제어 비트는 그룹으로 분할된다.

[0116] 2. 실시예 1의 방법으로서, 코드화된 데이터 비트 및 코드화된 제어 비트는 N개의 계층에 대응하는 N개의 비트 그룹으로 분할된다.

[0117] 3. 실시예 1 또는 2 중 어느 하나의 방법으로서, 각 계층(per layer)을 기초로 코드화된 데이터 비트 및 코드화된 제어 비트를 다중화하는 단계를 더 포함한다.

[0118] 4. 실시예 3의 방법으로서, 다중화는 계층에 특정되어 있고, 상이한 수의 제어 비트 및 데이터 비트가 처리된다.

[0119] 5. 실시예 1 내지 4 중 어느 하나의 방법으로서, 논리적 계층 매핑 기능을 사용하여 코드화된 RI 및 코드화된 HARQ ACK/NACK를 처리하는 단계를 더 포함한다.

[0120] 6. 실시예 1 내지 5 중 어느 하나의 방법으로서, 하나의 계층에 대하여 모든 비트를 인터리빙하는 단계를 더 포함한다.

[0121] 7. 실시예 6의 방법으로서, 인터리빙은 계층에 특정되어 있고, 상이한 수의 제어 비트 및 데이터 비트가 처리된다.

[0122] 8. 실시예 6의 방법으로서, 비트는 데이터, CQI/PMI, RI 및 ACK/NACK 비트를 포함한다.

[0123] 9. 실시예 1 내지 8 중 어느 하나의 방법으로서, 비트들을 연결한 후 코드화된 데이터 및 코드화된 제어 비트를 다중화하는 단계를 더 포함한다.

[0124] 10. 실시예 1 내지 9 중 어느 하나의 방법으로서, 코드화된 제어 비트는 2개의 코드워드로 분산된다.

[0125] 11. 실시예 10의 방법으로서, 코드화된 데이터 및 코드화된 제어 비트를 다중화하는 것은 2개의 코드워드 각각에 대하여 수행된다.

[0126] 12. 실시예 10 또는 11 중 어느 하나의 방법으로서, 2개의 코드워드의 적어도 하나의 코드화된 데이터 비트 및 각 코드워드에 대하여 적어도 하나의 코드화된 제어 비트를 N개의 비트 그룹으로 처리하는 단계를 더 포함하고, N개의 비트 그룹은 N개의 계층에 대응한다.

[0127] 13. 실시예 10 내지 12 중 어느 하나의 방법으로서, RI 및 코드화된 HARQ ACK/NACK 비트는 2개의 코드워드로 분산된다.

[0128] 14. 실시예 10 내지 13 중 어느 하나의 방법으로서, 코드화된 제어 비트는 논리적 계층 매핑 기능을 사용하여 2개의 코드워드로 분산된다.

[0129] 15. 실시예 1 내지 14 중 어느 하나의 방법으로서, 다중화는 HARQ ACK/NACK가 각 계층/스트림에 대하여 양 슬롯에 있는 것을 보장한다.

[0130] 16. 실시예 15의 방법에서, HARQ ACK/NACK는 적어도 하나의 업링크 복조 참조 신호 주변의 리소스로 매핑한다.

[0131] 17. 실시예 15 또는 16 중 어느 하나의 방법으로서, 다중화는 제어 및 데이터 정보가 상이한 변조 심볼로 매핑되는 것을 보장한다.

[0132] 18. 실시예 1 내지 17 중 어느 하나의 방법으로서, 제어 비트는 N번 반복되어, N개의 코드워드로 매핑된다.

[0133] 19. 실시예 18의 방법으로서, 제어 비트는 동일한 코드워드의 계층들 사이에 동등하게 분산된다.

[0134] 20. 실시예 1 내지 19 중 어느 하나의 방법으로서, 제어 비트는 N번 반복되어, N개의 계층/스트림으로 매핑된다.

[0135] 21. 실시예 20의 방법으로서, 제어 비트는 하나의 코드워드, 스트림, 또는 계층으로 송신된다.

[0136] 22. 실시예 1 내지 21 중 어느 하나의 방법으로서, 제어 비트는 모든 코드워드 또는 계층/스트림에 걸쳐 분산된다.

- [0138] 23. 실시예 22의 방법으로서, 코드워드당 또는 계층/스트림당 같은 양의 제어 비트가 있다.

- [0139] 24. 실시예 22 또는 23 중 어느 하나의 방법으로서, 하나의 코드워드 또는 계층/스트림 상에 매핑된 제어 비트의 양은 코드워드 또는 계층/스트림의 변조 및 코드화 기법(MCS)에 의해 결정된다.

- [0140] 25. 실시예 22 내지 24 중 어느 하나의 방법으로서, 코드워드 또는 계층/스트림 상에 매핑된 제어 비트의 양은 코드워드 또는 계층/스트림의 이송 블록 크기에 의해 결정된다.

- [0141] 26. 실시예 1 내지 25 중 어느 하나의 방법에 따라 구성된 무선 송수신 유닛(WTRU).

- [0142] 27. 실시예 1 내지 25 중 어느 하나의 방법에 따라 구성된 NodeB.

- [0143] 28. 실시예 1 내지 25 중 어느 하나의 방법에 따라 구성된 IC.

### 부호의 설명

|        |                       |                  |

|--------|-----------------------|------------------|

| [0144] | 100: E-UTRAN          | 102, 220: eNB    |

|        | 108: X2 인터페이스         | 106: S1 인터페이스    |

|        | 104: EPC              | 112: MME         |

|        | 110: S-GW             | 200: 무선 통신 시스템   |

|        | 210, 420: WTRU        | 300: 기능적인 블록도    |

|        | 315, 325: 프로세서        | 316, 326: 수신기    |

|        | 317, 327: 송신기         | 318, 328: 안테나 모듈 |

|        | 319: 메모리              | 320: 입출력 인터페이스   |

|        | 321: 사용자 인터페이스        | 322: 전력 증폭기 모듈   |

|        | 402, 404, 406: 단일 반송파 |                  |

도면

도면1

도면2

도면3

## 도면4

400

도면5

## 도면6

600

## 도면7

## 도면8

800

## 도면9

## 도면10

## 도면11

도면12

## 도면13

## 도면14

## 도면15

## 도면16

## 도면17

도면18

도면19

## 도면20

## 도면21

## 도면22

## 도면23

## 도면24

## 도면25

## 도면26

도면27

## 도면28