(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3552972号

(P3552972)

(45) 発行日 平成16年8月11日(2004.8.11)

(24) 登録日 平成16年5月14日(2004.5.14)

(51) Int.C1.<sup>7</sup>

F 1

H03K 3/03

// G09G 3/20H03K 3/03

G09G 3/20 612K

請求項の数 38 (全 36 頁)

(21) 出願番号 特願平11-362900

(22) 出願日 平成11年12月21日(1999.12.21)

(65) 公開番号 特開2000-236234(P2000-236234A)

(43) 公開日 平成12年8月29日(2000.8.29)

審査請求日 平成14年1月11日(2002.1.11)

(31) 優先権主張番号 9828510.9

(32) 優先日 平成10年12月22日(1998.12.22)

(33) 優先権主張国 英国(GB)

(73) 特許権者 000005049

シャープ株式会社

大阪府大阪市阿倍野区長池町22番22号

(74) 代理人 100078282

弁理士 山本 秀策

(72) 発明者 グラハム アンドリュー カーンズ

イギリス国 オーエックス2 8エヌエイ

チ オックスフォード, カッテスロウ,

パーン クローズ 22

(72) 発明者 マイケル ジェイムズ ブラウンロー

イギリス国 オーエックス4 4ワイピー

オックスフォード, サンドフォード

オン テムズ, チャーチ ロード 12

4

最終頁に続く

(54) 【発明の名称】スタティッククロックパルス発振器、空間光変調器、およびディスプレイ

## (57) 【特許請求の範囲】

## 【請求項1】

クロック入力およびN個の段を含むスタティッククロックパルス発振器であって、該スタティッククロックパルス発振器は、

該段の各i番目の段が、第(i-1)段のゲート回路出力からセット信号を受け取るセット入力および第(i+a)段(ここでaは1以上)からリセット信号を受け取るリセット入力を有するリセット-セットフリップフロップと、

該フリップフロップがセットされた場合に、該クロック入力に接続された該ゲート回路の少なくとも一つのクロック信号入力から該ゲート回路の出力へとクロックパルスを渡すゲート回路( $1 < i \leq N - a$ )とを含み、各々のゲート回路の各々のクロック信号入力は、該ゲート回路のバスゲートの主要伝導経路の末端に、該ゲート回路内で、排他的に接続されている、スタティッククロックパルス発振器。

## 【請求項2】

前記ゲート回路は、前記フリップフロップがリセットされた場合に、該ゲート回路の出力をインアクティブな状態に維持するように構成されている、請求項1に記載の発振器。

## 【請求項3】

各i番目の段の前記フリップフロップの前記リセット入力は、第(i+2)段のフリップフロップの出力からリセット信号を受け取るように構成されている、請求項1に記載の発振器。

## 【請求項4】

各  $i$  番目の段の前記フリップフロップの前記リセット入力は、第  $(i + 1)$  段のゲート回路の出力からリセット信号を受け取るように構成されている、請求項 1 に記載の発振器。

**【請求項 5】**

各  $i$  番目の段のゲート回路の出力は、遅延回路を介して、第  $(i + 1)$  段のフリップフロップのセット入力に接続されている、請求項 1 に記載の発振器。

**【請求項 6】**

前記遅延回路の各々が、複数の縦列接続されたインバータを含む、請求項 5 に記載の発振器。

**【請求項 7】**

第 1 段が、

前記第  $(1 + a)$  段からスタートパルスを受け取るセット入力、および該第  $(1 + a)$  段からリセット信号を受け取るリセット入力を有するリセット - セットフリップフロップと、

該フリップフロップがセットされた場合に、前記クロック入力から次の段へとクロックパルスを渡すゲート回路と、

を含む、請求項 1 に記載の発振器。

**【請求項 8】**

前記第 1 段が、第 2 段のゲート回路出力からのセット入力信号を前記フリップフロップセット入力に選択的に受け取らせ、かつ、第 1 段のゲート回路からのクロックパルスを前記フリップフロップリセット入力に選択的に受け取らせる第 2 のスイッチ装置を含む、請求項 7 に記載の発振器。

**【請求項 9】**

第  $N$  段が、

前記第  $(N - 1)$  段の前記ゲート回路出力からセット信号を受け取るセット入力とリセット入力とを有するリセット - セットフリップフロップと、

前記クロック入力から第  $N$  段および第  $(N - 1)$  段の該フリップフロップのリセット入力へとクロックパルスを渡すゲート回路と、

を含む、請求項 1 に記載の発振器。

**【請求項 10】**

前記第  $N$  段が、第  $(N - 1)$  段からのスタートパルスを前記フリップフロップセット入力に選択的に受け取らせ、かつ、第  $(N - 1)$  段からのリセット信号を前記フリップフロップリセット入力に選択的に受け取らせる第 3 のスイッチ装置を含む、請求項 8 に記載の発振器。

**【請求項 11】**

各第  $i$  段が、第  $(i + 1)$  段のゲート回路からのセット信号を前記フリップフロップセット入力に選択的に受け取らせ、かつ、第  $(i - a)$  段からのリセット信号を前記フリップフロップリセット入力に選択的に受け取らせる第 1 のスイッチ装置を含む、請求項 1 に記載の発振器。

**【請求項 12】**

前記ゲート回路出力の少なくともいくつかが、前記発振器の出力を構成する、請求項 1 に記載の発振器。

**【請求項 13】**

前記フリップフロップの出力の少なくともいくつかが、前記発振器の出力を構成する、請求項 1 に記載の発振器。

**【請求項 14】**

前記ゲート回路の各々が、バスゲートと、前記フリップフロップがリセットされた場合に該バスゲートの出力をインアクティブな状態に保持する保持デバイスとを含む、請求項 1 に記載の発振器。

**【請求項 15】**

前記バスゲートの各々が、ソース - ドレインパスがアンチパラレルに接続され、かつ、ゲ

10

20

30

40

50

ートが前記フリップフロップの直接出力および補完出力に接続された、相反する導電型の金属酸化膜シリコン電界効果トランジスタを含むトランスマッシュゲートである、請求項1\_4に記載の発振器。

【請求項16】

連続する段の前記バスゲートを通過した前記クロックパルスが、相反する極性を有する、請求項1\_4に記載の発振器。

【請求項17】

前記段の前記保持デバイスが、交互にプルダウントランジスタとプルアップトランジスタとを有し、各プルダウントランジスタの前記制御電極が前記関連するフリップフロップの前記補完出力に接続され、かつ、各プルアップトランジスタの前記制御電極が該関連するフリップフロップの前記直接出力に接続される、請求項1\_6に記載の発振器。10

【請求項18】

前記クロック入力が2相クロック入力である、請求項1に記載の発振器。

【請求項19】

連続する段のバスゲート入力が、異なるクロック入力相に接続される、請求項1に記載の発振器。

【請求項20】

前記段の前記バスゲートを通過した前記クロックパルスが、同じ極性を有する、請求項1\_9に記載の発振器。20

【請求項21】

各段の前記保持デバイスが、制御電極が前記フリップフロップの出力または前記補完出力に接続されたプルダウントランジスタを含む、請求項2\_0に記載の発振器。

【請求項22】

各段の前記保持デバイスは、制御電極が前記フリップフロップの出力または前記直接出力に接続されたプルアップトランジスタを含む、請求項2\_0に記載の発振器。

【請求項23】

前記クロック入力が単相クロック入力である、請求項1に記載の発振器。

【請求項24】

前記ゲート回路の各々が、前記バスゲートまたはバスゲートの各々を備えるゲート型センス增幅器を含む、請求項1に記載の発振器。30

【請求項25】

前記ゲート回路の各々が、前記バスゲートまたはバスゲートの各々を備えるゲート型レベルシフタを含む、請求項1に記載の発振器。

【請求項26】

前記フリップフロップの各々が、

第1のインバータであって、該第1のインバータの入力および出力の一方が前記フリップフロップの出力を構成する、第1のインバータと、

第2の制御可能インバータであって、該第2の制御可能インバータの入力および出力が該第1のインバータの入力および出力にそれぞれ接続された、第2の制御可能インバータと、40

該フリップフロップの入力を構成する第1および第2の入力を有する入力回路と、

を含み、

該入力回路は、該第1のインバータの該入力に、該第1および第2の入力の状態に対応する信号を供給し、かつ、該第1または第2の入力がアクティブ信号を受け取る場合に、該第2のインバータの該出力を高インピーダンス状態に切り換えるように該第2のインバータを制御するように構成されている、

請求項1に記載の発振器。

【請求項27】

前記第1の入力がアクティブハイ入力であり、かつ、前記第2の入力がアクティブロー入力である、請求項2\_6に記載の発振器。50

**【請求項 2 8】**

前記入力回路が、

第1の電源入力と前記第1のインバータの前記入力との間に接続され、前記第2の入力を構成する制御電極を有する、第1のアクティブデバイスと、

該第1のアクティブデバイスと反対の導電型を有し、第2の電源入力と該第1のインバータの該入力との間に接続され、前記第1の入力を構成する制御電極を有する、第2のアクティブデバイスと、

を含む入力回路である、請求項2 7に記載の発振器。

**【請求項 2 9】**

前記第1および第2のアクティブデバイスが、逆の構成に接続される、請求項2 8に記載の発振器。 10

**【請求項 3 0】**

前記入力回路が、前記第1および第2のアクティブデバイスのうちの一方のアクティブデバイスと同じ導電型を有し、該第1および第2のアクティブデバイスのうちの一方のアクティブデバイスと直列に接続され、かつ、該第1および第2のアクティブデバイスのうちの他方のアクティブデバイスの前記制御電極に接続された制御電極を有するさらなるアクティブデバイスを含む、請求項2 8に記載の発振器。

**【請求項 3 1】**

前記第2のインバータが、

第1の電源入力または前記第1の電源入力と該第2のインバータの出力との間に直列に接続された、第1の導電型を有する第3および第4のアクティブデバイスと、 20

第2の電源入力または前記第2の電源入力と該第2のインバータの出力との間に直列に接続された、第1の導電型を有する第5および第6のアクティブデバイスと、

を含む第2のインバータであって、

該第3および第5のアクティブデバイスが、該第2のインバータの入力に接続された制御電極を有し、

該第4および第6のアクティブデバイスが、該第1および第2の入力に接続された制御電極を有する、

請求項2 7に記載の発振器。

**【請求項 3 2】**

前記第3および第5のアクティブデバイスの少なくとも一方の前記制御電極が、さらなるアクティブデバイスを介して、前記第2のインバータの入力に接続される、請求項3 1に記載の発振器。 30

**【請求項 3 3】**

前記さらなるアクティブデバイスまたは各さらなるアクティブデバイスが、前記第1または第2の電源入力に接続された制御電極を有する、請求項3 2に記載の発振器。

**【請求項 3 4】**

前記第1のインバータが、

第1の電源入力または前記第1の電源入力と前記第1のインバータの出力との間に接続された第7のアクティブデバイスと、 40

該第7のアクティブデバイスと反対の導電型を有し、第2の電源入力または前記第2の電源入力と前記第1のインバータの出力との間に接続された、第8のアクティブデバイスと、

を含み、

第7および第8のアクティブデバイスは、該第1のインバータの入力に接続された制御電極を有する、

請求項2 6に記載の発振器。

**【請求項 3 5】**

C M O S内蔵回路をさらに含む、請求項1に記載の発振器。

**【請求項 3 6】**

10

30

40

50

請求項 1 に記載の発振器をさらに含む、空間光変調器。

【請求項 3 7】

液晶デバイスをさらに含む、請求項 3 6 に記載の変調器。

【請求項 3 8】

請求項 3 6 に記載の変調器をさらに含むディスプレイ。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、スタティッククロックパルス発振器に関する。このような発振器は、高速低電力制御回路、例えばデジタル信号処理（D S P）を含む複雑な超大規模集積回路（V L S I）設計、において使用され得る。クロックパルス発振器は、ドライバ回路が空間光変調器およびディスプレイ、例えば、高速ビデオデータのサンプリングを行う回路に正確に規定されたパルスのシーケンスを供給する必要のある、ピクセル化されたマトリクス型のディスプレイ、にアドレスするのに有利に使用され得る。10

【0 0 0 2】

【従来の技術】

公知のタイプのクロックパルス発振器は、シフトレジスタに基づく。シフトレジスタは、Dタイプのフリップフロップの縦列鎖を含む。このフリップフロップの縦列鎖は、クロックパルスに応答して単一の格納された論理状態（l o g i c s t a t e）を、1つのフリップフロップから次のフリップフロップの鎖へと渡す。通常のクロックパルス発振アプリケーションについて、フリップフロップの状態のうち、1つを除いて全ての状態が論理ロー（0）状態に初期値化されるのに対して、残りのフリップフロップが論理ハイ（1）状態に初期値化される。シフトレジスタは公知の周波数でクロックされ、そして、シフトレジスタ内の循環する1状態を使用して、フリップフロップの出力において連続パルスを生成する。この周知の技術は、例えば米国特許第4,542,301号および米国特許第4,612,659号に開示されている。この技術を改良したものが、米国特許第4,785,297号に開示されている。この場合、各フリップフロップの「マスター」出力および「スレーブ」出力を、A N D ゲートまたはN A N D ゲート等の組合せ論理ゲートと共に使用して、所定の数の出力パルスについてのシフトレジスタのクロック速度を低減する。20

【0 0 0 3】

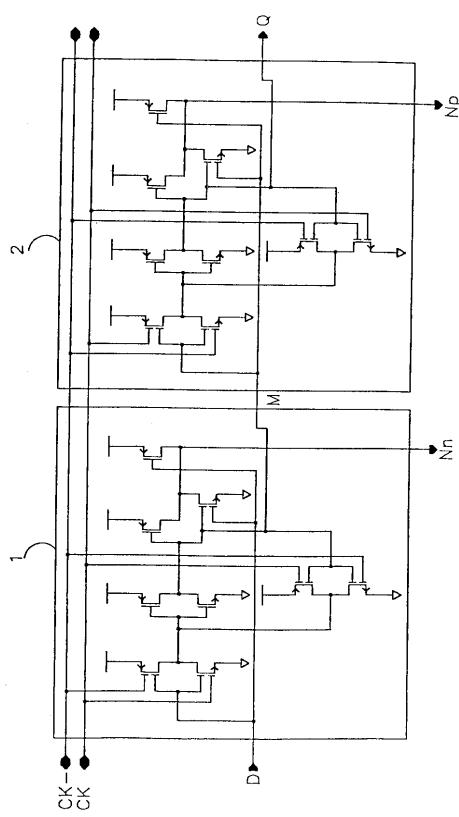

クロックパルス発振回路を、鎖状につながれたDタイプラッチ回路から形成することもまた公知である。添付した図面の図1は、ラッチ1および2を含む通常のC M O S回路を示す。このような構成の構造および動作は、詳細には説明しない。ラッチ1および2等の連続するラッチは、C K およびC K - で示される2相クロックの相反するクロック相に対して透明である。各ラッチの入力および出力は、添付した図面の図2に示すクロックパルスN n およびN p を生成するために、一緒に「N A N D 化」される。図2はまた、2相クロック波形、第1ラッチ1へのD入力、第2ラッチ2の入力でもある第1ラッチ1の出力M 、および第2ラッチ2の出力Q を示す。30

【0 0 0 4】

【発明が解決しようとする課題】

この構成の欠点は、出力パルスN n およびN p がオーバーラップするのを確實に防ぐことができない点にある。2つのパルスのオーバーラップが起こると、所定のアプリケーションにおいて、例えば、ピクセルマトリクスディスプレイドライバにおいてビデオデータをサンプリングするのに出力パルスが使用される場合、問題が生じる。40

【0 0 0 5】

動作の最大周波数を増加し、かつ、クロック電力消費を低減するために、クロックラインまたは複数のクロックラインの容量負荷を低減するためのさまざまな技術が開示されている。例えば、クロックパルス発振回路において使用する、状態制御されたクロッキング技術が提案されている。この技術の例が、米国特許第4,746,915号に開示されている。この例では、シフトレジスタがフリップフロップまたはラッチからなる複数のサブレ

50

ジスタに分割され、そして、低い周波数で動作する別のシフトレジスタが、クロック信号を各サブレジスタに選択的に供給するために使用される。

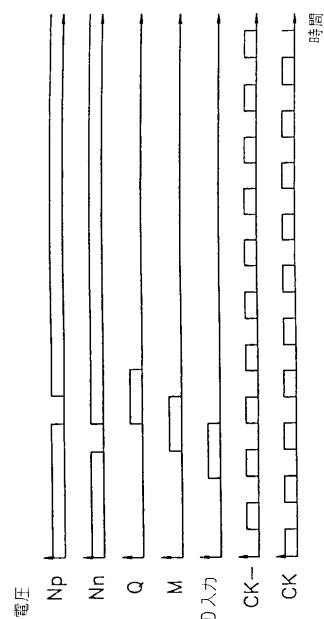

#### 【0006】

必要条件が単一の循環する1状態についてのものであるアプリケーションについて、1状態を含む、または入力において1状態を有するフリップフロップまたはラッチのみがクロックを要求する。図3に示すように、このようなアプリケーションについて、各フリップフロップの入力および出力を「OR」することによって生成される信号は、フリップフロップのクロック入力に供給されたクロック信号をゲートするのに用いられ得る。このような構成は、米国特許第5,128,974号に開示されている。しかし、このような構成は、段毎に完全なフリップフロップおよび複数のさらなるトランジスタを要求する。また、フリップフロップ出力は、比較的大きな負荷を駆動する必要があり、そして、このことが動作の最大速度を制限する。

#### 【0007】

本明細書中で使用する「バスゲート」という語句は、入力信号を通過させるかまたはプロックするように制御され得るメイン導通パスを有する半導体構成を意味するものと定義されている。

#### 【0008】

##### 【課題を解決するための手段】

本発明の第一の局面による、スタティッククロックパルス発振器は、クロック入力およびN個の段を含み、該スタティッククロックパルス発振器は、該段の各*i*番目の段が、第(*i*-1)段のゲート回路出力からセット信号を受け取るセット入力および第(*i*+*a*)段(ここで*a*は1以上)からリセット信号を受け取るリセット入力を有するリセット-セットフリップフロップと、該フリップフロップがセットされた場合に、該クロック入力に接続された該ゲート回路の少なくとも一つのクロック信号入力から該ゲート回路の出力へとクロックパルスを渡すゲート回路(1<*i*<(N-a))とを含み、各々のゲート回路の各々のクロック信号入力は、該ゲート回路のバスゲートの主要伝導経路の末端に、該ゲート回路内で、排他的に接続されているスタティッククロックパルス発振器であって、そのことにより上記目的が達成される。

#### 【0009】

ゲート回路は、フリップフロップがリセットされた場合に、ゲート回路の出力をインアクティブな状態に維持するように構成されてもよい。

#### 【0010】

各*i*番目の段のフリップフロップのリセット入力は、第(*i*+2)段のフリップフロップの出力からリセット信号を受け取るように構成されてもよい。

#### 【0011】

各*i*番目の段のフリップフロップのリセット入力は、第(*i*+1)段のゲート回路の出力からリセット信号を受け取るように構成されてもよい。

#### 【0012】

各*i*番目の段のゲート回路の出力は、遅延回路を介して、第(*i*+1)段のフリップフロップのセット入力に接続されてもよい。

#### 【0013】

遅延回路の各々が、複数の縦列接続されたインバータを含んでもよい。

#### 【0014】

第1段が、第(1+a)段からスタートパルスを受け取るセット入力、および第(1+a)段からリセット信号を受け取るリセット入力を有するリセット-セットフリップフロップと、フリップフロップがセットされた場合に、クロック入力から次の段へとクロックパルスを渡すゲート回路とを含んでもよい。

#### 【0015】

第N段が、第(N-1)段のゲート回路出力からセット信号を受け取るセット入力とリセット入力とを有するリセット-セットフリップフロップと、クロック入力から第N段およ

10

20

40

50

び第(  $N - 1$  )段のフリップフロップのリセット入力へとクロックパルスを渡すゲート回路とを含んでもよい。

**【 0 0 1 6 】**

各第 $i$ 段が、第( $i + 1$ )段のゲート回路からのセット信号をフリップフロップセット入力に選択的に受け取らせ、かつ、第( $i - a$ )段からのリセット信号をフリップフロップリセット入力に選択的に受け取らせる第1のスイッチ装置を含んでもよい。

**【 0 0 1 7 】**

第1段が、第2段のゲート回路出力からのセット入力信号をフリップフロップセット入力に選択的に受け取らせ、かつ、第1段のゲート回路からのクロックパルスをフリップフロップリセット入力に選択的に受け取らせる第2のスイッチ装置を含んでもよい。 10

**【 0 0 1 8 】**

第 $N$ 段が、第( $N - 1$ )段からのスタートパルスをフリップフロップセット入力に選択的に受け取らせ、かつ、第( $N - 1$ )段からのリセット信号をフリップフロップリセット入力に選択的に受け取らせる第3のスイッチ装置を含んでもよい。

**【 0 0 1 9 】**

あるいは、第 $N$ 段が、第( $N - 1$ )段からのスタートパルスをフリップフロップセット入力に選択的に受け取らせ、かつ、第( $1 + a$ )段からのリセット信号をフリップフロップリセット入力に選択的に受け取らせる第3のスイッチ装置を含んでもよい。

**【 0 0 2 0 】**

ゲート回路出力の少なくともいくつかが、発振器の出力を構成してもよい。 20

**【 0 0 2 1 】**

フリップフロップの出力の少なくともいくつかが、発振器の出力を構成してもよい。

**【 0 0 2 2 】**

ゲート回路が、クロック入力に接続された入力を有してもよい。

**【 0 0 2 3 】**

ゲート回路の各々が、パスゲートと、フリップフロップがリセットされた場合にパスゲートの出力をインアクティブな状態に保持する保持デバイスとを含んでもよい。

**【 0 0 2 4 】**

パスゲートの各々が、ソース - ドレインパスがアンチパラレルに接続され、かつ、ゲートがフリップフロップの直接出力および補完出力に接続された、相反する導電型の金属酸化膜シリコン電界効果トランジスタを含むトランスマッショングートであってもよい。 30

**【 0 0 2 5 】**

クロック入力が2相クロック入力であってもよい。

**【 0 0 2 6 】**

連続する段のパスゲート入力が、異なるクロック入力相に接続されてもよい。

**【 0 0 2 7 】**

あるいは、連続する段のパスゲートが、異なるクロック入力相に接続されてもよい。

**【 0 0 2 8 】**

段のパスゲートを通過したクロックパルスが、同じ極性を有してもよい。

**【 0 0 2 9 】**

各段の保持デバイスが、制御電極がフリップフロップの出力または補完出力に接続されたプルダウントランジスタを含んでもよい。

**【 0 0 3 0 】**

各段の保持デバイスは、制御電極がフリップフロップの出力または直接出力に接続されたプルアップトランジスタを含んでもよい。

**【 0 0 3 1 】**

クロック入力が単相クロック入力であってもよい。

**【 0 0 3 2 】**

連続する段のパスゲートを通過したクロックパルスが、相反する極性を有してもよい。

**【 0 0 3 3 】**

40

50

段の保持デバイスが、交互にプルダウントランジスタとプルアップトランジスタとを有し、各プルダウントランジスタの制御電極が関連するフリップフロップの補完出力に接続され、かつ、各プルアップトランジスタの制御電極が関連するフリップフロップの直接出力に接続されてもよい。

**【0034】**

ゲート回路の各々が、パスゲートまたはバスゲートの各々を備えるゲート型センス増幅器を含んでもよい。

**【0035】**

前記ゲート回路の各々が、前記パスゲートまたはバスゲートの各々を備えるゲート型レベルシフタを含んでもよい。 10

**【0036】**

フリップフロップの各々が、第1のインバータであって、第1のインバータの入力および出力の一方がフリップフロップの出力を構成する、第1のインバータと、第2の制御可能インバータであって、第2の制御可能インバータの入力および出力が第1のインバータの入力および出力にそれぞれ接続された、第2の制御可能インバータと、フリップフロップの入力を構成する第1および第2の入力を有する入力回路とを含み、入力回路は、第1のインバータの入力に、第1および第2の入力の状態に対応する信号を供給し、かつ、第1または第2の入力がアクティブ信号を受け取る場合に、第2のインバータの出力を高インピーダンス状態に切り換えるように第2のインバータを制御するように構成されててもよい。 20

**【0037】**

第1の入力がアクティブハイ入力であり、かつ、第2の入力がアクティブロー入力であってもよい。

**【0038】**

入力回路が、第1の電源入力と第1のインバータの入力との間に接続され、第2の入力を構成する制御電極を有する、第1のアクティブデバイスと、第1のアクティブデバイスと反対の導電型を有し、第2の電源入力と第1のインバータの入力との間に接続され、第1の入力を構成する制御電極を有する、第2のアクティブデバイスとを含む入力回路であってもよい。

**【0039】**

第1および第2のアクティブデバイスが、逆の構成に接続されてもよい。 30

**【0040】**

入力回路が、第1および第2のアクティブデバイスのうちの一方のアクティブデバイスと同じ導電型を有し、第1および第2のアクティブデバイスのうちの一方のアクティブデバイスと直列に接続され、かつ、第1および第2のアクティブデバイスのうちの他方のアクティブデバイスの制御電極に接続された制御電極を有するさらなるアクティブデバイスを含んでもよい。

**【0041】**

第2のインバータが、第1の電源入力または第1の電源入力と第2のインバータの出力との間に直列に接続された、第1の導電型を有する第3および第4のアクティブデバイスと、第2の電源入力または第2の電源入力と第2のインバータの出力との間に直列に接続された、第1の導電型を有する第5および第6のアクティブデバイスとを含む第2のインバータであって、第3および第5のアクティブデバイスが、第2のインバータの入力に接続された制御電極を有し、第4および第6のアクティブデバイスが、第1および第2の入力に接続された制御電極を有してもよい。 40

**【0042】**

第3および第5のアクティブデバイスの少なくとも一方の制御電極が、さらなるアクティブデバイスを介して、第2のインバータの入力に接続されてもよい。

**【0043】**

さらなるアクティブデバイスまたは各さらなるアクティブデバイスが、第1または第2の 50

電源入力に接続された制御電極を有してもよい。

**【0044】**

第1のインバータが、第1の電源入力または第1の電源入力と第1のインバータの出力との間に接続された第7のアクティブデバイスと、第7のアクティブデバイスと反対の導電型を有し、第2の電源入力または第2の電源入力と第1のインバータの出力との間に接続された、第8のアクティブデバイスとを含み、第7および第8のアクティブデバイスは、第1のインバータの入力に接続された制御電極を有してもよい。

**【0045】**

本発明の発振器は、CMOS集積回路をさらに含んでもよい。

**【0046】**

本発明の第2の局面による空間光変調器は、本発明の第1の局面による発振器をさらに含み、そのことにより上記目的が達成される。10

**【0047】**

本発明の変調器は、液晶デバイスをさらに含んでもよい。

**【0048】**

本発明の第3の局面によるディスプレイは、本発明の第2の局面による変調器をさらに含み、そのことにより上記目的が達成される。

**【0049】**

従って、完全に静的なクロックパルス発振器を提供することができる。このような発振器は、容量性の緩衝および充電漏れに対して頑強であり、非常に低い周波数で動作し得る。20

**【0050】**

また、非常に高い最大動作周波数を有するクロックパルス発振器を提供することもできる。特に、(ゲート回路が発振器の出力を構成する場合に)クロックパルスが、(任意の外部負荷に加えて)ある時点で2つのトランジスタゲートのみを充電する必要がある発振器を提供することができる。また、クロック信号を完全にゲートすることができる。このことは、2つの理由から重要である。第1に、クロック信号のトランジスタローディングは、その立ち上がり時間および立ち下がり時間を制限するので、従って、最大周波数を制限することになる。本発明の構成で、クロックのローディングは、主に寄生素子に起因するので、比較的大きなクロックパルス発振器についても高速を維持することができる。

**【0051】**

第2に、トランジスタゲートによるクロック信号の容量ローディングが、最小化され得る。特に、切り換え状態にある段内のトランジスタのゲートのみが充電される。この結果、クロック信号を搬送する回路トラックのトラック抵抗における電力損失が低減される。

**【0052】**

出力パルスは、(ゲート回路の通過路によってのみ低下される)クロック信号の正確なコピーであり得る。ゲート回路は、パスゲートの形態である。パスゲートは、駆動能力が高くなるように比較的大きく形成される。出力パルスは、パスゲートから取られた場合には、確実にオーバーラップしないようにされている。

**【0053】**

いくつかの実施形態は2相クロックを要求するが、他の実施形態は、単相クロックのみを要求する。40

**【0054】**

さまざまな有用な信号が、連続する各対から生成され得、これらの信号は以下のものを含む：

(i) クロックパルスハイ期間に実質的に等しい持続時間を持つ、かつ、クロック立ち上がりエッジと同期の、独立した、オーバーラップしない(正または負)パルス

(ii) クロックパルスロー期間に実質的に等しい持続時間を持つ、かつ、クロック立ち下がりエッジと同期の、独立した、オーバーラップしない(正または負)パルス

(iii) クロック期間に実質的に等しい持続時間を持つ、かつ、クロック立ち上がりエッジと同期の、独立した、オーバーラップする正負のパルス

50

(i v) クロック期間に実質的に等しい持続時間を有し、かつ、クロック立ち下がりエッジと同期の、独立した、オーバーラップする正負のパルス

オーバーラップしないパルスの場合、単に、クロックパルス発振器を駆動するのに使用されるクロック信号のマーク - スペース比を変更することによって、相対的なパルス幅が変更され得る。

#### 【0055】

いくつかの実施形態において、電圧レベルのシフトが提供され得る。特に、クロック信号は、発振器供給電圧よりも低い電圧であり得るので、電力消費の低減が達成され得る。いくつかの実施形態において、出力パルスは、実質的に低い振幅のクロック信号で動作するにも関わらず、実質的に完全な供給電圧に実質的に対応する振幅を有し得る。また、いくつかの実施形態において、発振器は、いずれかの方向（「順方向」または「逆方向」）を選択して動作し得る。このことは、表示された画像を空間的に逆転する必要があり得る表示駆動等の、いくつかのアプリケーションにおいて有利である。10

#### 【0056】

##### 【発明の実施の形態】

以下、特定的な実施形態を示して、添付の図面を参照しつつ本発明をより詳細に説明する。図中、同じ参照符号は同じ部材を示すものである。なお、以下の説明において、4つのタイプのパルスを次のような符号を用いて示す：

P<sub>p</sub>： 正のパルス： クロック信号CKと一致する正状態パルス（positive-going pulse）。20

#### 【0057】

P<sub>n</sub>： 正のパルス： クロック信号CKと一致する負状態パルス（negative-going pulse）。

#### 【0058】

N<sub>p</sub>： 負のパルス： クロック信号CKと一致する正状態パルス。

#### 【0059】

N<sub>n</sub>： 負のパルス： クロック信号CKと一致する負状態パルス。

#### 【0060】

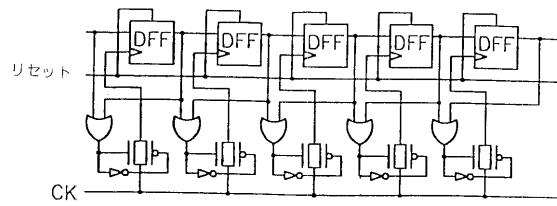

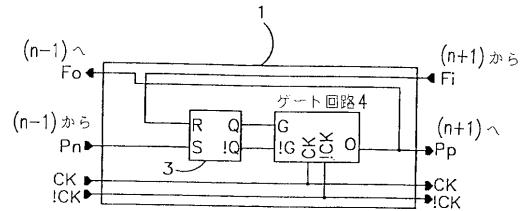

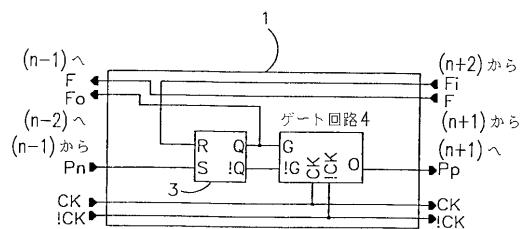

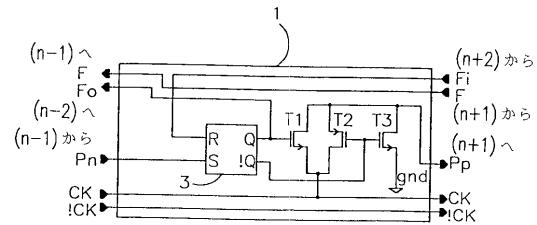

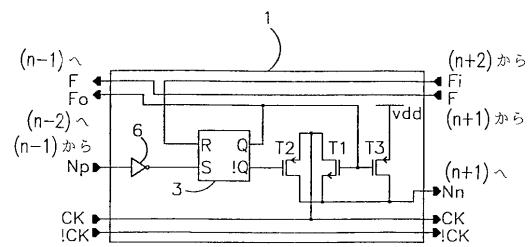

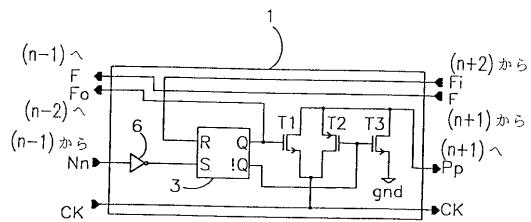

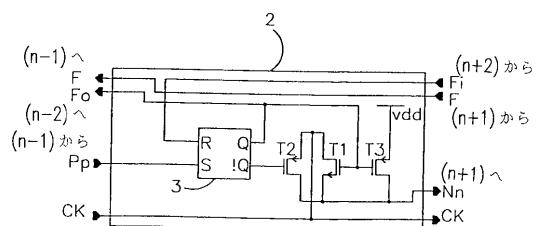

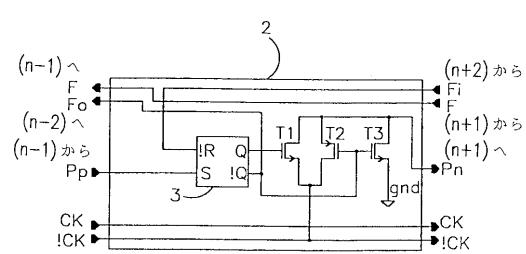

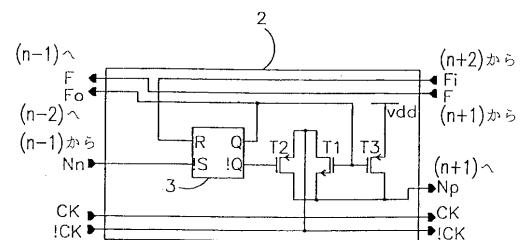

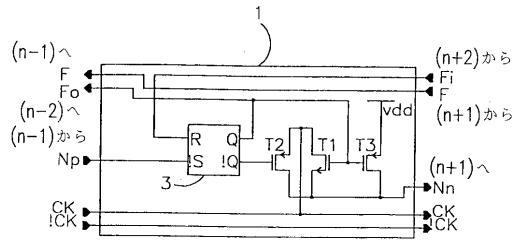

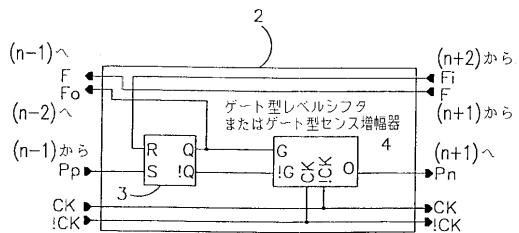

図4はスタティッククロックパルス発振器の2つの段、段1および段2を示す。段1は、リセット入力R、セット入力S、直接出力Q、ならびに補完的または逆転した出力!Qを有するリセット - セット（RS）フリップフロップ3を含む。セット入力Sは、前段または第（n-1）段からセット信号P<sub>n</sub>を受け取るために、この段の入力に接続される。この信号はまた、前段の出力信号でもある。リセット入力Rは、第（n+1）段からリセット信号を受け取るために入力F<sub>i</sub>に接続される。30

#### 【0061】

フリップフロップ3の出力Qおよび!Qは、それぞれゲート回路4のゲート入力Gおよび!Gに接続される。ゲート回路4は補完クロック入力CKおよび!CKを有し、補完クロック入力CKおよび!CKは、それぞれ2相クロック入力CKおよび!CKの補完相（complementary phase）に接続される。しかし、ゲート回路4の実際の構成に基づくと、フリップフロップの出力のうち1つの出力のみが、単一のゲート入力を有するゲート回路4のために使用され得る。同様に、ゲート回路4は、クロック相の1つまたは単一のクロック相に接続された単一のクロック入力を有してもよい。ゲート回路4の出力Oは、セット信号を後段または第（n+1）段に供給するために段1の出力P<sub>p</sub>に接続される。また、ゲート回路4の出力Oは、リセット信号を前段または第（n-1）段に供給するために、出力F<sub>o</sub>に接続される。40

#### 【0062】

図4の下側の図に示す段2は、段2が第（n-1）段からセット信号P<sub>p</sub>を受け取り、セット信号P<sub>n</sub>を第（n+1）段へと供給するという点で、段1とは異なる。また、段1のゲート回路4が、クロック信号CKの正状態パルスと一致する正のパルスP<sub>p</sub>を供給するように構成されているのに対して、段2は、その出力において、クロック信号CKの負状50

態パルスと一致する正のパルス  $P_n$  を供給するように構成されている。（なお、クロック信号  $C_K$  は、補完クロック信号  $\neg C_K$  の正状態パルスに一致する。）

ゲート回路 4 は、クロック入力  $C_K$  および  $\neg C_K$  の一方から單一のクロックパルスを送信するように、各段のフリップフロップ 3 の出力  $Q$  および  $\neg Q$  のいずれかまたは両方によって制御される。回路 4 へのゲート入力信号が不活性である場合、つまり、フリップフロップ 3 がリセットされる場合、回路 4 の、つまり段 1 または段 2 の、出力  $O$  はローに維持される。

#### 【0063】

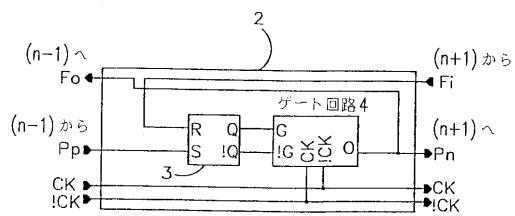

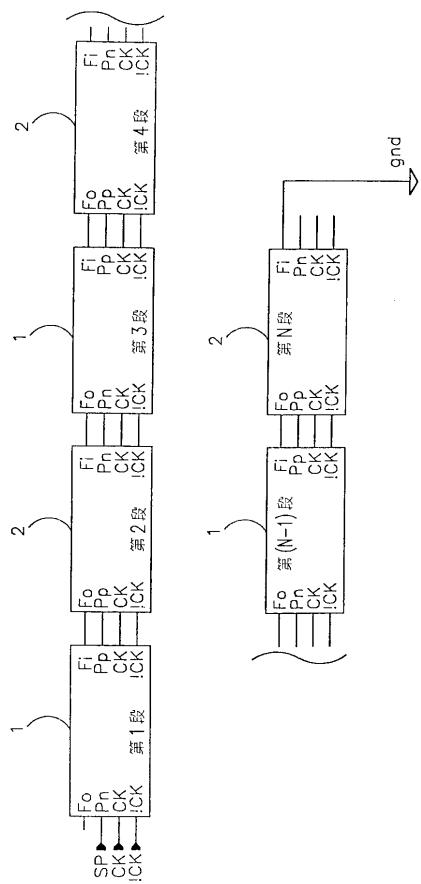

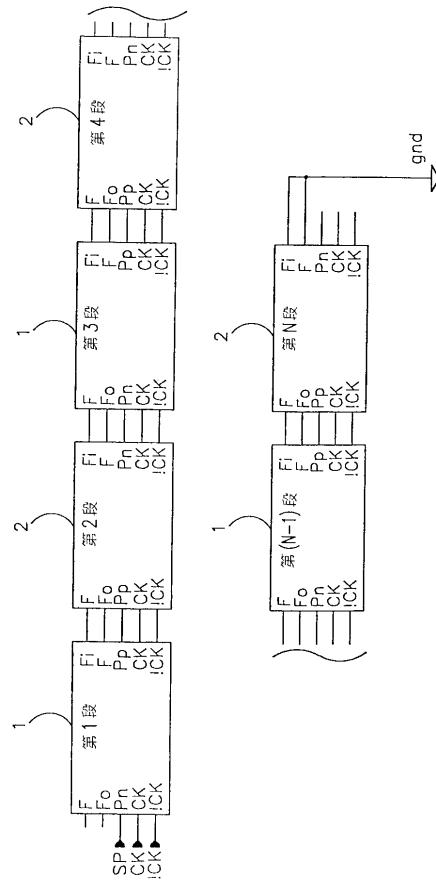

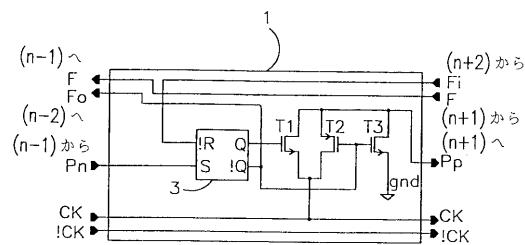

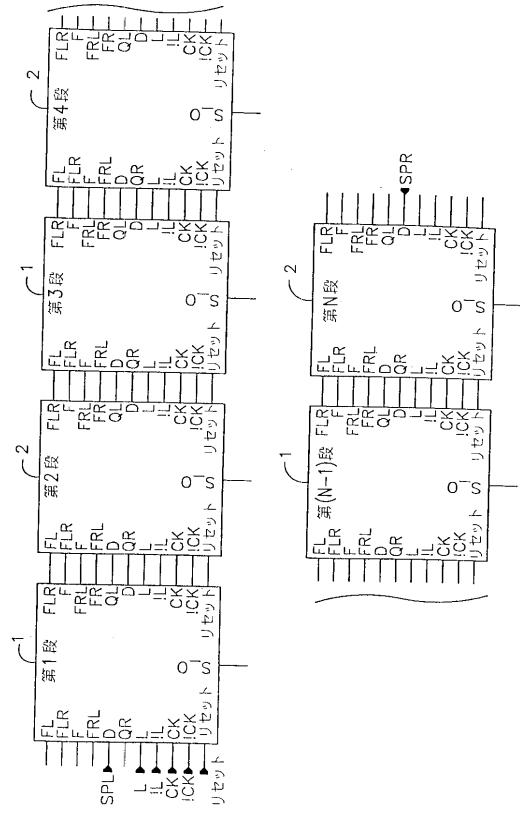

図 5 は、縦列に接続された段 1 および段 2 を  $N$  個含むスタティッククロックパルス発振器の一部を示す。段 1 は、段 2 と交互に配置されている。第 1 段のセット信号入力  $P_n$  がスタートパルス  $S_P$  を受け取るように構成されているのに対して、クロック入力は 2 相クロック入力から補完的クロック信号  $C_K$  および  $\neg C_K$  を受け取るように接続されている。段 1 および段 2 の各々の入力  $F_i$  は、後段の出力  $F_o$  に接続されている。最終段または第  $N$  段の入力  $F_i$  は、グラウンド  $gnd$  に接続される。

#### 【0064】

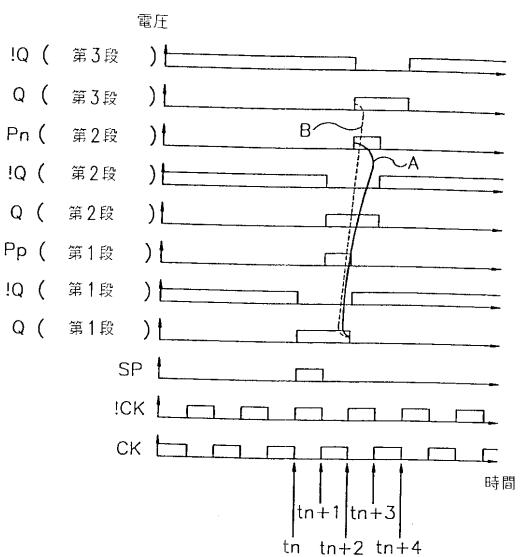

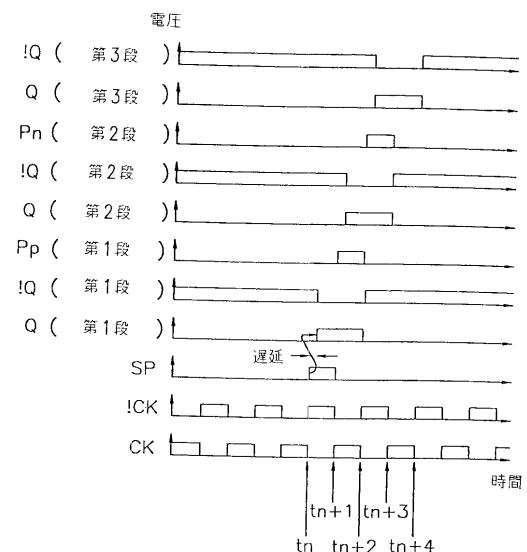

スタティッククロックパルス発振器の動作を、図 5 の発振器の第 1 の 3 つの段において発生するさまざまな波形を示した図 6 のタイミング図によって説明する。まず、直接出力  $Q$  がローとなり、補完出力  $\neg Q$  がハイとなり、そして、出力  $P_n$  および  $P_p$  が全てローとなるように、段 1 および段 2 の全てのフリップフロップ 3 がリセット状態にある。

#### 【0065】

時間  $t_n$  において、スタートパルス  $S_P$  は、第 1 段 1 の入力  $P_n$  に供給される。この段のフリップフロップ 3 は、出力  $Q$  がハイになり、かつ、補完出力  $\neg Q$  がローになるようにセットされる。従って、ゲート回路 4 はスイッチオンされ、そして、第 1 段 1 の出力信号  $P_p$  はクロック信号  $C_K$  に続く。

#### 【0066】

時間  $t_{n+1}$  において、クロック信号  $C_K$  がハイになると、第 1 段 1 の出力信号  $P_p$  がハイになる。第 2 段 2 のフリップフロップ 3 は、その出力  $Q$  および  $\neg Q$  がそれぞれハイおよびローになるようにセットされる。第 2 段 2 のゲート回路 4 がオンにスイッチされると、第 2 段 2 の出力信号  $P_n$  が補完クロック信号  $\neg C_K$  に続く。

#### 【0067】

時間  $t_{n+2}$  において、補完クロック信号  $\neg C_K$  はハイになり、従って、第 2 段 2 の出力信号  $P_n$  もハイになる。第 3 段 1 のフリップフロップがそのようにセットされると、出力  $Q$  はハイになる。信号  $P_n$  は第 1 段 1 のフリップフロップ 3 のリセット入力  $R$  にフィードバックされ、従って、第 1 段 1 は（図 6 の A に示すように）リセットされる。第 1 段 1 のゲート回路 4 がオフにスイッチされると、第 1 段 1 の出力  $P_p$  は、別のスタートパルスが受け取られるまで、接地電位に維持されたままである。

#### 【0068】

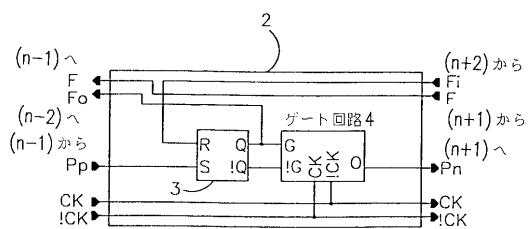

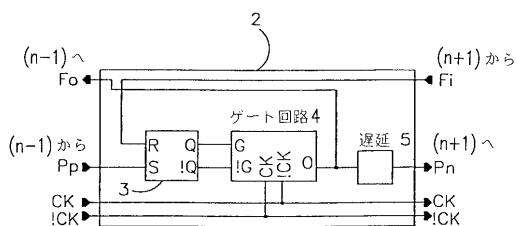

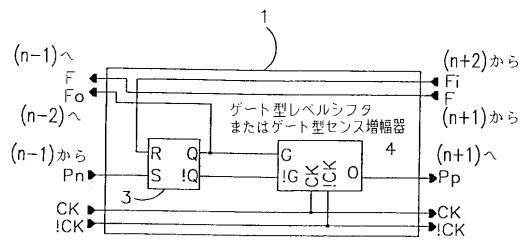

図 7 に示す段 1 および段 2 は、リセッティングパルスのフィードバック構成の点で、図 4 に示した段 1 および段 2 とは異なる。段 1 および段 2 の各々が、第  $(n+1)$  段からのリセット信号を受け取り、この受け取った信号を出力  $F$  にルーティングして、それにより、リセット信号を第  $(n-1)$  段に供給するための入力  $F$  を有する。段 1 および段 2 の各々において、フリップフロップ 3 の  $Q$  出力により、リセット信号が出力  $F_o$  を介して第  $(n-1)$  段へと供給される。同様に、入力  $F_i$  に接続されたフリップフロップ 3 のリセット入力  $R$  が、第  $(n+2)$  段からリセット信号を受け取る。

#### 【0069】

フリップフロップ出力は、ゲート回路 4 によって生成されたパルスに応答するので、ゲートされたパルスの各々とフリップフロップの応答との間の遅延は小さい。従って、図 7 に示す段 1 および段 2 を含む、図 8 に示したクロックパルス発振器内に発生する信号のタイミングは、図 5 に示したクロックパルス発振器内に発生する信号と同様であるので、波形は、図 6 に示した波形とほぼ同じである。しかし、図 6 の波線 B で示すように、第 3 段の

10

20

30

40

50

フリップフロップ出力 Q の立ち上がりエッジは、第 1 段の信号 Q をリセットするので、これらの信号は確実にオーバーラップする。組合せ論理によってフリップフロップ 3 の出力 Q から所定のタイプのさらなる論理信号を生成することが要求される場合、このことは重要な特徴であり得る。

#### 【0070】

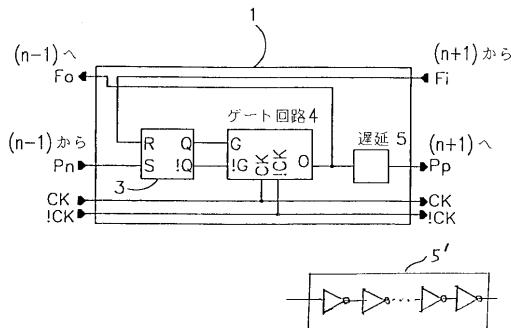

逆に、いくつかのアプリケーションでは、2 段おきに出力 Q がオーバーラップしないよう 10 にする必要があり、このような場合、図 9 に示す段 1 および段 2 が使用され得る。図 9 に示す段 1 および段 2 は、各段の出力が遅延回路 5 を介してゲート回路 4 の出力 O に接続される点で、図 4 に示す段 1 および段 2 と異なる。ここで、遅延回路 5 は、具体的には、5' で示されるように偶数個の直列または縦列に接続されたインバータとして設けられ得る。しかし、前段へのフィードバックリセット信号は、ゲート回路 4 の出力 O から出力 F o を介して直接供給されるので、遅延されない。このことにより、前段のフリップフロップは、次の段のフリップフロップがセットされる前に確実にリセットされる。図 10 は、このことが、連続する段のフリップフロップの出力 Q および !Q に及ぼす影響を示す。このことは、適切な組合せ論理によって使用され、さらなる論理信号を生成し得る。

#### 【0071】

図 11 は、図 7 に示したタイプの段 1 および段 2 を示す。ここで、ゲート回路はトランスマッシュョンゲートの形態で設けられている。詳細には、各フリップフロップ 3 の出力 Q および !Q は、トランジスタ T 1 および T 2 のゲートにそれぞれ接続され、トランジスタ T 1 および T 2 のソース - ドレインパスは、アンチパラレルに接続されて、トランスマッシュョンゲートを形成する。トランスマッシュョンゲート T 1 および T 2 の入力は、段 1 および段 2 内の 2 相クロック入力の相 C K および相 !C K にそれぞれ接続される。トランスマッシュョンゲート T 1 および T 2 の出力は、段 1 および段 2 の出力 P p および P n にそれぞれ接続される。プルダウントランジスタ T 3 は、グラウンドまたは電源入力 g n d に接続されたソース、段 1 の出力 P p または段 2 の P n に接続されたドレイン、および、フリップフロップ 3 の補完出力 !Q に接続されたゲートを有する。

#### 【0072】

フリップフロップ 3 がリセット状態にある場合、トランスマッシュョンゲート T 1 および T 2 はオフにスイッチされ、トランジスタ T 3 はこの段の出力を接地電位に維持される。フリップフロップ 3 がセット状態にある場合、トランスマッシュョンゲート T 1 および T 2 は 30 オンにスイッチされ、段出力を適当なクロックパルスに接続し、そしてプルダウントランジスタ T 3 がディスエーブルされる。

#### 【0073】

図 4、図 7、図 9、および図 11 に示す段 1 および段 2 は、出力 P p および P n において、クロックパルス C K および !C K の立ち上がりエッジと同期した正のパルスを供給する。しかし、負の出力パルス N n および N p を供給するスタティッククロックパルス発振器を提供することもできる。図 12 は、このようなパルスを提供し、かつ、図 8 のように一緒に接続されて、スタティッククロックパルス発振器を形成し得る、段 1 および段 2 を示す。

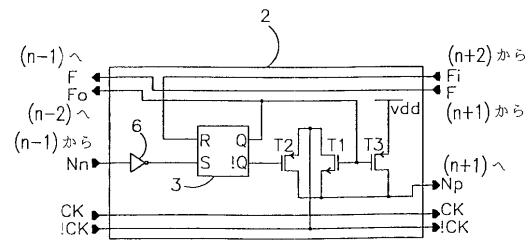

#### 【0074】

図 12 に示す段 1 は、インバータ 6 が入力 N p とフリップフロップ 3 のセット入力 Sとの間に接続され、出力 N n が、ソースが電源入力 v d d に接続され、かつ、ゲートがフリップフロップ 3 の直接出力 Q に接続されたプルアップトランジスタ T 3 を提供される点で、図 11 に示した段 1 とは異なる。同様に、図 12 に示した段 2 は、インバータ 6 が入力 N n とフリップフロップ 3 のセット入力 Sとの間に接続され、出力 N p が、ゲートがフリップフロップ 3 の直接出力 Q に接続されたプルアップトランジスタ T 3 を提供される点で、図 11 に示す段 2 とは異なる。

#### 【0075】

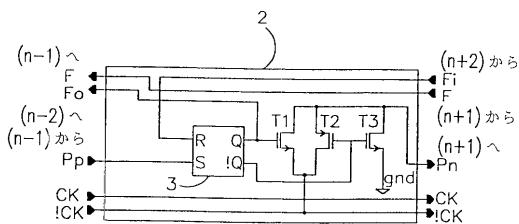

図 13 は、図 8 に示すように一緒に接続され得る段 1 および段 2 を示す。段 1 は、正状態出力信号 P p を供給するのに対して、段 2 は負状態出力信号 N n を供給する。段 1 は、図 50

11に示した段1とは、インバータ6が入力Nnとフリップフロップ3のセット入力Sとの間に提供される点で異なる。段2は、図12に示した段2とは、インバータ6が省略され、トランスマッシュゲートT1およびT2の入力が単一相クロック入力CKに接続される点で異なる。したがって、スタティッククロックパルス発振器全体で1つの単一相クロック入力CKを要求し、かつ、異なる段が反対の極性の出力信号またはパルスを提供する。

#### 【0076】

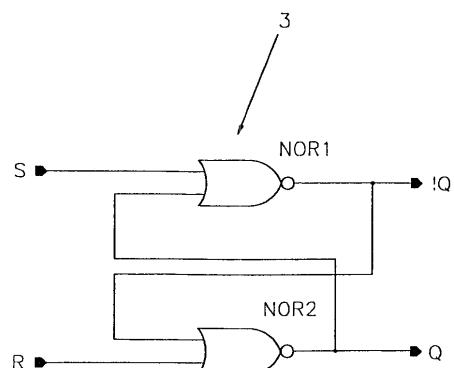

フリップフロップ3は、任意の適切な方法で具体化され得る。例えば、公知のタイプのRSフリップフロップは、図14に示し、かつ、F. HillおよびG. Petersonの”Digital Logic and Microprocessors”, John Wiley and Sons, 1984に開示されているように、1対の交差結合NORゲートを含む。フリップフロップは、1対になった2つの入力ゲートNOR1およびNOR2を含む。ゲートNOR1の入力の1つはセット入力Sを含むのに対して、ゲートNOR2の入力の1つはリセット入力Rを含む。ゲートNOR1の出力は、フリップフロップの補完出力!Qを含み、かつ、ゲートNOR2の第2の入力に接続されている。ゲートNOR2の出力は、フリップフロップの出力Qを含み、かつ、ゲートNOR1の第2の入力に接続されている。出力Qおよび補完出力!Qは、以下の真理値表に基づいて、セット信号およびリセット信号に応答する。

#### 【0077】

【表1】

20

| S | R | Qt   | !Qt   |

|---|---|------|-------|

| 0 | 0 | Qt-1 | !Qt-1 |

| 0 | 1 | 0    | 1     |

| 1 | 0 | 1    | 0     |

| 1 | 1 | 不定   |       |

30

#### 【0078】

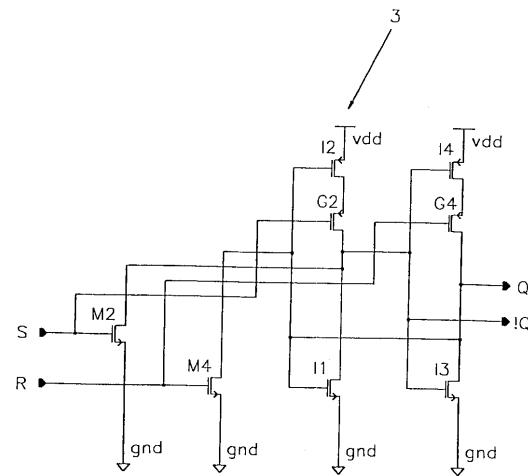

ここで、0および1は、論理ローレベルおよび論理ハイレベルを示し、Qtおよび!Qtは現在の出力状態を示し、そして、Qt-1および!Qt-1は前の出力状態を示す。従って、セット信号Sおよびリセット信号Rが両方とも0である場合、出力Qおよび!Qは、その前の状態を維持し、従ってラッチされている。セット入力Sがハイになる場合、フリップフロップはセットされ、かつ、出力Qはハイになる。リセット入力Rがハイになる場合、フリップフロップはリセットされ、かつ、出力Qはローになる。セット入力およびリセット入力が両方ハイである場合の出力状態は不定であり、設計者は、決してこの状態が起こらないように設計する必要がある。図14に示すRSフリップフロップは、図15に示すような公知のタイプの8トランジスタCMOS集積回路として具体化され得る。ゲートNOR1は、P型トランジスタI2およびG2と、N型トランジスタM2およびI1を含むのに対して、ゲートNOR2は、P型トランジスタI4およびG4と、N型トランジスタM4およびI3を含む。

40

#### 【0079】

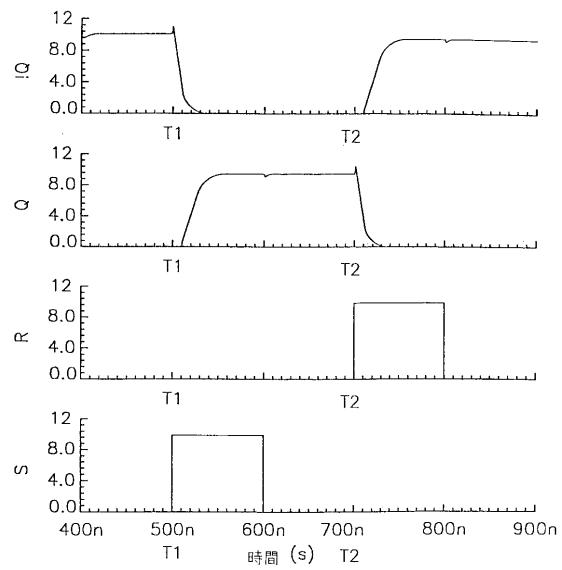

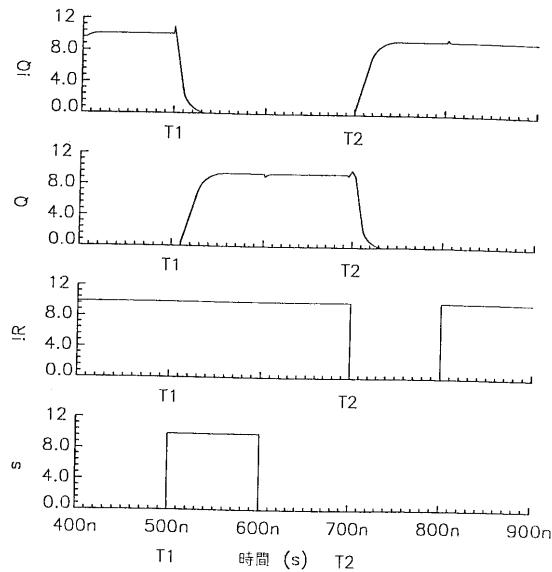

添付の図面の図16は、入力RおよびS、ならびに出力Qおよび!Qにおいて起こる信号を共通の時間軸上に4つの波形図を示したグラフである。波形は、信号のエッジの相対的なタイミングを強調するために任意の電圧レベルおよび脆弱なトランジスタ性能を用いた、図15に示したフリップフロップのシミュレーションを示す。シミュレーションを目的として、全てのトランジスタは、同じサイズであり、かつ、出力Qおよび!Qはそれぞれ

50

ユニットインバータを備えている。

**【0080】**

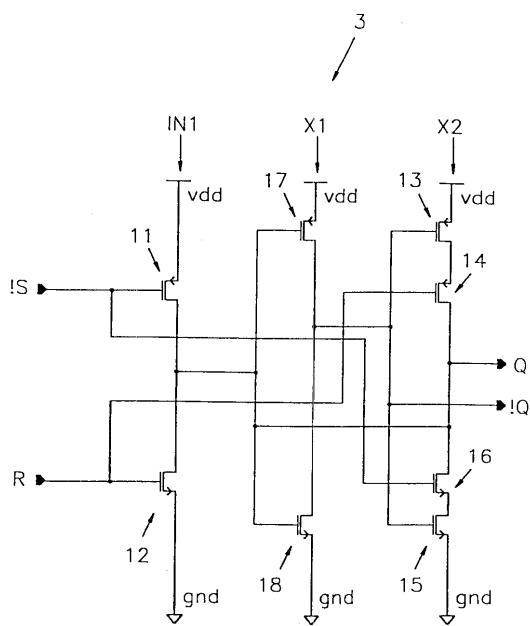

図17に示す段1および段2は、図11に示した段1および段2とは、フリップフロップ3がアクティブローリセット入力!Rを有する点で異なる。また、前段がフリップフロップ3の補完出力!Qによって供給される前に、リセット信号は各段からこの段へとフィードバックされる。

**【0081】**

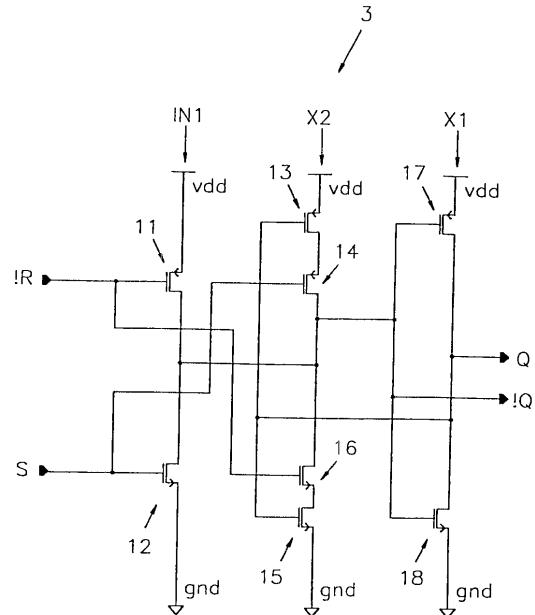

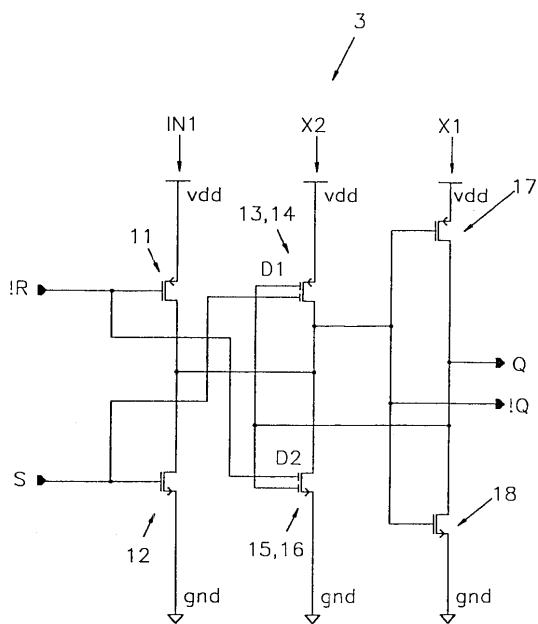

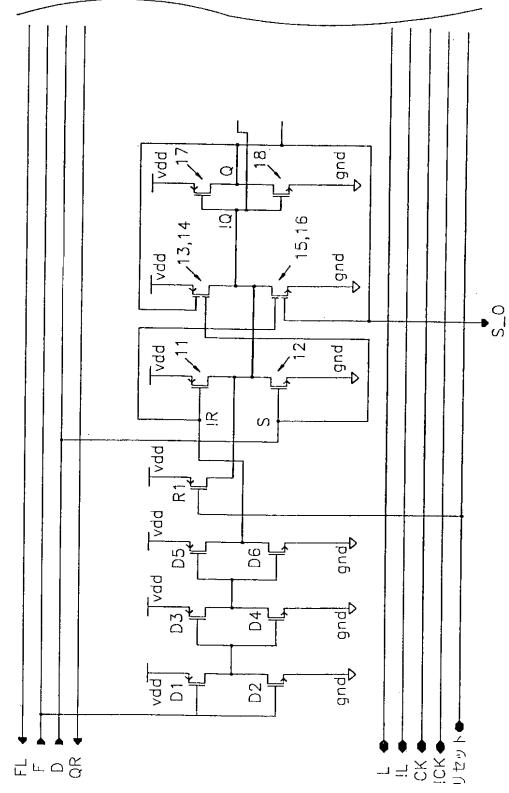

図17に示す段1および段2では、フリップフロップ3を、図18に示すような改良されたタイプのフリップフロップによって具体化することができる。フリップフロップ3は、第1の電源入力またはラインvddとグラウンドもしくは第2の電源入力またはラインgndとの間に直列に接続された第1のP型トランジスタT11およびN型トランジスタT12を含む入力回路IN1を含む。第1のトランジスタT11は、アクティブローリセット入力!Rに接続されたゲートを有する。従って、入力!Rに供給されたリセット信号は、通常、論理ハイまたは1、例えば供給ラインvddの電圧、にあり、フリップフロップがリセットされた場合に、0または接地電源などの論理ローまたは0に切り換わる。第2のトランジスタT12のゲートは、同様に、アクティブハイである、つまり、通常は論理ローであるが、フリップフロップがセットされた場合に論理ハイへと切り換わるセット入力Sに接続されている。

**【0082】**

フリップフロップは、第1のインバータX1および第2の制御可能インバータX2をさらに含む。第2のインバータX2は、供給ラインvddとgndとの間に直列に接続された第3および第4のp型トランジスタT13およびT14ならびに第5および第6のN型トランジスタT15およびT16を含む。第3および第5のトランジスタT13およびT15のソースは、供給ラインvddおよびgndにそれぞれ接続されるのに対して、ゲートは一緒に接続されて、インバータX2の入力を形成する。第3のおよび第5のトランジスタT13およびT15のドレインは第4および第6のトランジスタT14およびT16のソースにそれぞれ接続される。第4および第6のトランジスタT14およびT16のドレインは一体に接続されて、第2のインバータX2の出力を形成する。第4のトランジスタT14のゲートがセット入力Sに接続されるのに対して、第6のトランジスタT16のゲートはリセット入力!Rに接続される。

**【0083】**

第1のインバータX1は、供給ラインvddとgndとの間に直列に接続された第7のP型トランジスタT17および第8のN型トランジスタT18を含む。トランジスタT17およびT18のゲートは一緒に接続されて、第1のインバータX1の入力を形成するのに対して、トランジスタT17およびT18のドレインは一緒に接続されてフリップフロップの出力Qを形成する。第1のインバータX1の入力は、第2のインバータX2の出力およびフリップフロップの補完出力!Qに接続される。第1のインバータX1の出力は、第2のインバータX2の入力に接続される。第1のインバータX1の入力は、トランジスタT11およびT12のドレインによって形成された入力回路IN1の出力に接続される。

**【0084】**

図18に示すフリップフロップはアクティブハイセット入力Sおよびアクティブローリセット入力!Rを有するので、フリップフロップの論理レベル信号に対する応答は、図14および図15に示した構成とは異なる。論理レベル入力信号のさまざまな組み合わせに対する応答を以下に示す。

**【0085】**

**【表2】**

| S | !R | Q <sub>t</sub>   | !Q <sub>t</sub>   |

|---|----|------------------|-------------------|

| 0 | 1  | Q <sub>t-1</sub> | !Q <sub>t-1</sub> |

| 0 | 0  | 0                | 1                 |

| 1 | 1  | 1                | 0                 |

| 1 | 0  | 不定               |                   |

10

**【 0 0 8 6 】**

ここで、各記号は表1について上で説明した通りである。セット信号がアクティブでない（論理0）であり、かつ、リセット信号がインアクティブ（論理1）である場合、トランジスタ11および12はオフに切り換わるのに対して、トランジスタ14および16は導通している。従って、インバータX2は、その出力における信号がその入力における信号の論理的補完であるインバータとして機能する。従って、フリップフロップは、フリップフロップがより最近にセットされたかまたはリセットされたかに基づいて相反する論理状態にロックされた出力Qおよび!Qを有する交差結合インバータを含む。

**【 0 0 8 7 】**

出力Qが論理レベル0となり、かつ、出力!Qが論理レベル1となるように、フリップフロップがより最近にリセットされた場合、リセット入力!Rを論理レベル1に維持した状態でアクティブセット信号（論理1）をセット入力Sに与えることによって、フリップフロップがセットされ得る。従って、第2のトランジスタ12がオンになるのに対して、第4のトランジスタ14はオフになり、それにより、第2のインバータX2の出力は第1の供給ラインvddから絶縁される。第2のインバータX2の出力に接続された第1のインバータX1の入力は、トランジスタ12によってローに下がり、それにより出力Qが論理1にセットされる。これがトランジスタ15にフィードバックされ、セット信号が停止され、かつ、トランジスタ12がオフに切り換わった後は、インバータX1の入力が論理0に確実に維持される。同様に、トランジスタ13は、フィードバック信号によってオフに切り換えられる。

20

**【 0 0 8 8 】**

出力Qが論理1となり、かつ、出力!Qが論理0となるように、フリップフロップがより最近にリセットされた場合、フリップフロップはインアクティブセット信号（論理0）およびアクティブリセット信号（論理0）によってリセットされ得る。この場合、第1のトランジスタ11はアクティブリセット信号によってオンされるのに対して、トランジスタ16はオフされる。論理レベル1はインバータX1の入力に供給され、従って、インバータX1は出力Qにおいて論理0信号を供給する。これが、第2のインバータX2の入力にフィードバックされ、それにより、トランジスタ13が導通し、かつ、トランジスタ15がオフに切り換えられる。リセット信号がインアクティブ（論理1）レベルに戻った場合、交差結合されたインバータX1およびX2はリセット状態に維持される。

30

**【 0 0 8 9 】**

これまでに説明したように、セット信号およびリセット信号の両方についての出力状態は、アクティブであるか、または不定である。もし両方の信号がアクティブとなった場合には、両トランジスタ11および12が供給ラインvddとgndとの間を導通し、かつ、入力回路IN1の出力が不定となる。従って、フリップフロップの入力信号の両方が同時にアクティブとなり得ないように確実にすることが設計者にとって重要である。

40

**【 0 0 9 0 】**

図19は、セット動作およびリセット動作についての、図18の回路の入力波形および出力波形を示す。これらの波形は、図16に示す波形を得るために用いたパラメータを用いた

50

シミュレーションによって得られた。時間  $T_1$ において、図 18 のフリップフロップがセットされ、補完出力  $!Q$  は出力  $Q$  の前に応答する。同様に、時間  $T_2$ において、フリップフロップはリセットされ、補完出力  $!Q$  は出力  $Q$  の前に応答する。従って、フリップフロップはより望ましい対称なスイッチのふるまいを提供する。これは、高速論理回路において有利である。

#### 【0091】

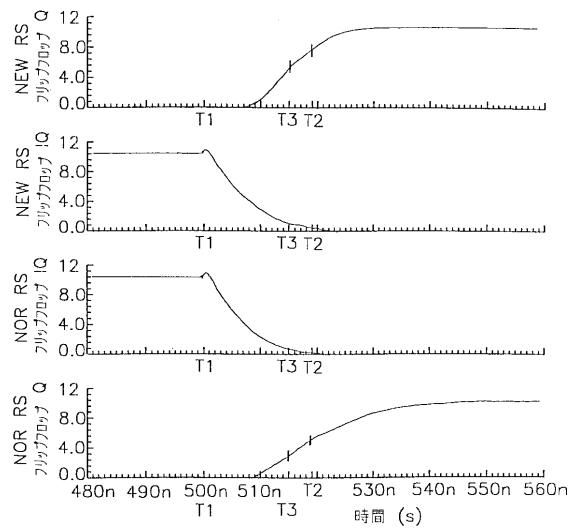

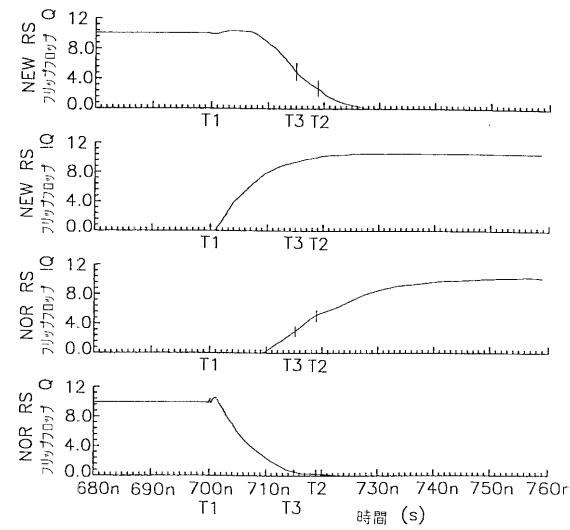

図 20 および図 21 は、それぞれ、セットおよびリセットの遷移について、図 18 のフリップフロップの性能を、図 15 のフリップフロップの性能と比較する。これらの波形は、同じパラメータを用いた、つまり同じ性能の等しいサイズのトランジスタを用いたシミュレーションによって得られた。ここで、各出力がユニットインバータを駆動し、電圧波形はこれらのインバータの入力で測定した。

10

#### 【0092】

図 20 に示すように、フリップフロップは時間  $T_1$ においてセットされる。図 18 の「新たな R S フリップフロップ」および図 15 の「N O R R S フリップフロップ」の出力  $!Q$  は、ほぼ同じ速度で放電する。しかし、出力  $Q$  の応答速度は、実質的に異なる。「新たな」フリップフロップの出力  $Q$  は、時間  $T_3$ において論理ハイ状態に達し、これは、公知の回路の出力  $Q$  が（時間  $T_2$ ）において同じ論理レベルに達するのに要する時間よりも約 20 % 速い。

#### 【0093】

図 21 に示すように、フリップフロップは時間  $T_1$ においてリセットされる。図 15 のフリップフロップの出力  $Q$  および図 18 のフリップフロップの出力  $!Q$  はそれぞれ、ほぼ同じ速度で放電および充電を行なう。しかし、図 18 のフリップフロップの出力  $Q$  は、図 15 のフリップフロップの出力  $!Q$  が時間  $T_2$ において論理ハイ状態に達するよりも実質的に早く、時間  $T_3$ において論理ロー状態に達する。

20

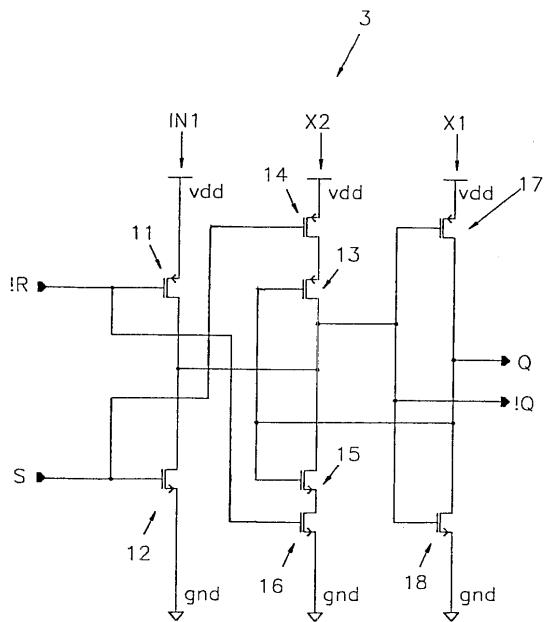

#### 【0094】

図 22 は、段 1 および段 2 を示すが、この段 1 および段 2 は、図 12 に示した段 1 および段 2 とは、インバータ 6 が省略され、かつ、フリップフロップ 3 がアクティブローセット入力  $!S$  を有するという点で異なる。これらの段は、図 18 に示すような実質的に同じアーキテクチャを有するフリップフロップを利用し得る。このタイプの適切なフリップフロップを図 23 に示す。ここで、入力と出力とが入れ換えられている。この場合、第 1 のトランジスタ 1 のゲートがアクティブローセット入力  $!S$  に接続されるのに対して、第 2 のトランジスタ 2 のゲートはアクティブハイリセット入力  $R$  に接続される。インバータ X 1 の出力が補完出力  $!Q$  に接続されるのに対して、インバータ X 2 の出力は出力  $Q$  に接続される。この構成で、出力  $Q$  における状態変化は、出力  $!Q$  における対応する状態変化に対して、常に先行する。そうでない場合には、図 23 のフリップフロップの動作は、図 18 のそれと実質的に同じである。図 23 のフリップフロップについての対応する真理値表を以下に示す。

30

#### 【0095】

#### 【表 3】

| $!S$ | $R$ | $Q_t$     | $!Q_t$     |

|------|-----|-----------|------------|

| 1    | 0   | $Q_{t-1}$ | $!Q_{t-1}$ |

| 1    | 1   | 0         | 1          |

| 0    | 0   | 1         | 0          |

| 0    | 1   | 不定        |            |

40

50

## 【0096】

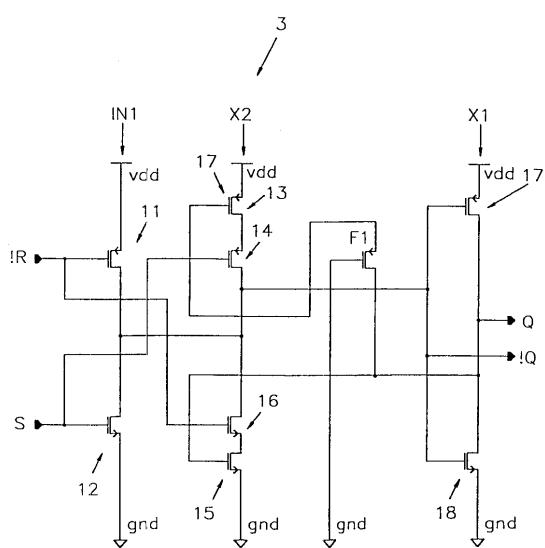

第2のインバータ内のトランジスタ13および14の相対的な位置、およびトランジスタ15および16の相対的な位置は、フリップフロップの正確な動作にとって重要でない。例えば、図24に示すように、トランジスタ14は、第1の供給ラインvddとトランジスタ13との間に配置され得、トランジスタ16は、第2の供給ラインgndとトランジスタ15との間に配置され得る。また、ソース-ドレインパスが直列に接続された一対のトランジスタは、多重ゲートデバイスと置き換え得る。例えば、図25に示すように、トランジスタ13および14は、デュアルゲートトランジスタD1と置き換えられ、トランジスタ15および16がデュアルゲートトランジスタD2と置き換えられる。

## 【0097】

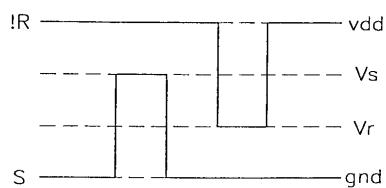

図18および図23～図25を参照してこれまでに説明したフリップフロップは、論理レベル1信号が第1の電源ラインvdd上の電圧の値を有し、かつ、論理レベル0信号が第2の供給ラインgnd上の電圧を有するような標準的な論理レベル信号で動作するように意図されているが、これらの実施形態は、より低い電圧入力信号で動作することができ、従って、レベルシフティングを実行し得る。例えば、図26に示すように、セット入力Sは、（接地電位に比例する）供給電圧vddよりも低いVsである電圧を有するアクティブハイセット信号に応答することができる。同様に、図18の実施形態のアクティブローリセット入力!Rは、その電圧Vrが接地電位よりも大きなりセット信号に応答することができる。例えば、図18のフリップフロップのセット動作の間に、トランジスタ12は、供給電圧よりも低いゲート-ソース電圧でオンし得る。しかし、ゲート-ソース電圧が供給電圧とセット信号の電圧との差分に等しいので、トランジスタ14は完全にオフされ得ない。したがって、トランジスタ12とトランジスタ13および14との間には瞬間に衝突が起こり得、そして、セット信号の実際の大きさおよびトランジスタの閾値電圧に基づいて、フリップフロップは状態を変え得る、または変え得ない。フリップフロップが状態を変え、かつ、セットされるのに要求されるセット信号の大きさの最小値は、トランジスタ13および14と比較して、トランジスタ12を大きく形成することによって増加し得る。これは、高い駆動能力出力を有する高速回路にとって、通常の構成である。

## 【0098】

図27に示すフリップフロップは、図18に示したフリップフロップの改変例であり、低い入力電圧での動作にさらに適している。さらに、パストランジスタとして構成されたP型トランジスタが、第1のインバータX1とトランジスタ13のゲートとの間に接続される。トランジスタF1のゲートは、第2の供給ラインgndに接続される。

## 【0099】

図27のフリップフロップの動作は、トランジスタF1は閾値電圧によって低下された論理レベル0を通過させるのみであるという事実に依存する。従って、リセット動作に引き続いて、フリップフロップの条件は、トランジスタ13のゲートが、トランジスタF1の閾値電圧に対して閉となる電位になるように与えられる。これにより、トランジスタ13が弱々しく（weakly）オンされるのみで、かつ、トランジスタ13および14の結合されたプルアップドライブが低減されることが確実になる。結果的に、引き続くセッティング動作の間に、フリップフロップは、それ以外の場合に得られるより低い入力電圧Vsでセットされ得る。

## 【0100】

最小アクティブローリセット電圧を向上するために、同じ技術を適用し得る。この場合、パスマージゲートとして構成されたN型トランジスタは、インバータX1の出力とトランジスタ15のゲートとの間に接続される。なお、トランジスタ15のゲート電極は、第1の供給ラインvddに接続されている。

## 【0101】

図24、図25、および図27に示す改変例は、図18および図23に示すフリップフロップにも同様に用い得る。

## 【0102】

10

20

30

40

50

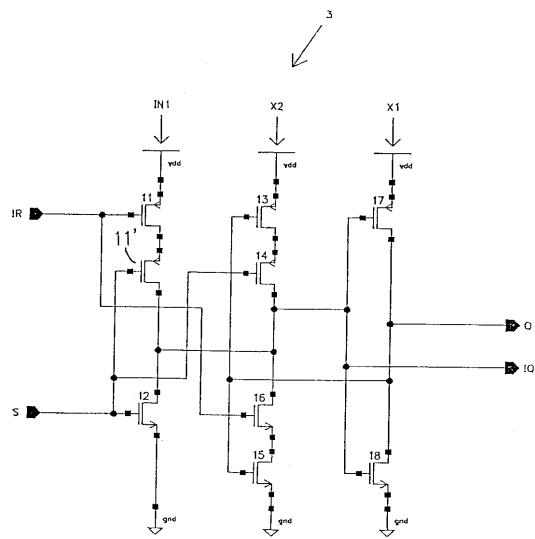

図28に示すフリップフロップは、セット・オーバーライド型であり、かつ、図18に示したフリップフロップとは、さらなるトランジスタ11'が提供されている点で異なる。トランジスタ11'はP型であり、かつ、トランジスタ11と直列に接続される。トランジスタ11のドレインは、トランジスタ11'のソースに接続され、トランジスタ11'のドレインは、トランジスタ12のドレインに接続され、そして、トランジスタ11'のゲートはセット入力Sに接続される。あるいは、トランジスタ11'のソース-ドレンパスが、トランジスタ11と供給ラインvddとの間に接続され得るか、もしくは、トランジスタ11および11'が、デュアルゲートトランジスタとして具体化され得る。

#### 【0103】

図28に示すフリップフロップの動作は、図18に示したフリップフロップの動作と同様であるが、主に、不定状態が無いという点で異なる。図28のフリップフロップについての真理値表を以下に示す。

#### 【0104】

【表4】

| S | !R | Qt   | !Qt   |

|---|----|------|-------|

| 0 | 1  | Qt-1 | !Qt-1 |

| 0 | 0  | 0    | 1     |

| 1 | 1  | 1    | 0     |

| 1 | 0  | 1    | 0     |

10

20

#### 【0105】

図18のフリップフロップは、セット入力およびリセット入力の両方が同時にアクティブである場合、不定状態を有する。しかし、図28のフリップフロップは、セット入力およびリセット入力の両方が同時にアクティブである場合にセットされるように構成されている。従って、真理値表に示すように、この状況において、セット入力Sはリセット入力!Rをオーバーライドする。詳細には、セット入力Sが論理レベル1である場合、トランジスタ11'はオフされて、そして、トランジスタ11のドレインをトランジスタ12のドレインから切断する。それにより、フリップフロップは強制的にセット状態にされる。スタティッククロックパルス発振器において図28のフリップフロップを用いることは、複数の利点を有する。不定状態が無いので、クロックパルス発振器を不定状態にすることができない。また、スタートアップ時にクロックパルス発振器内で起こる任意の偽の(surious)状態は、発振器がクロックされる場合に効果的に除去されるので、スタートアップ時にクロックパルス発振器をリセットするために、独立したリセット信号および関連する回路を提供する必要はない。さらに、要求される場合には、クロックパルス発振器を介してより長いパルスを送信することができる。複数の連続するスタートパルスを供給することができ、そして、これらのパルスは発振器を介してクロックされ、かつ、連続する段を占め得る。

30

40

#### 【0106】

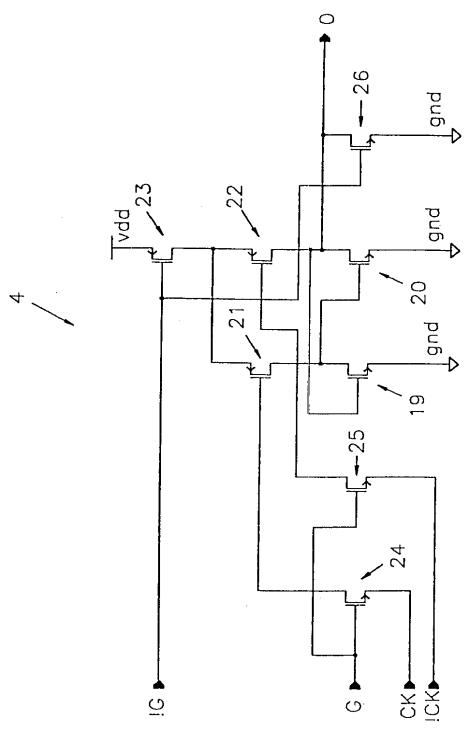

図29は、低電圧での動作を提供する異なる技術を用いる、改変された段1および段2を示す。この技術は、電源電圧よりも実質的に低い振幅を有する単一相または2相のクロック信号で使用され得る。図29に示す段1および段2は、図4に示した段1および段2とは、ゲート回路4の各々が、ゲート型レベルシフタまたはゲート型センス増幅器として具体化される点で異なる。従って、ゲート回路は、クロックパルスの電圧レベルシフティングを実行する。

#### 【0107】

50

図30は、ゲート回路4として使用され得るゲート型センス増幅器を、より詳細に説明する。増幅器は、例えば、A. BellalourとM. Elmasryの”low-power digital VLSI design circuits and systems”, Kluwer Academic Publishers, 1995(この文献の内容を本明細書中で参考として援用する)に開示されたタイプの、交差結合されたセンス増幅器として構成された、第9および第10のN型トランジスタ19および22、ならびに、第11および第13P型トランジスタ21~23を含む。トランジスタ19および20のソースがグラウンドに接続されるのに対して、トランジスタ19および20のドレインはトランジスタ21および22のドレインとトランジスタ20および19のゲートとにそれぞれ接続される。トランジスタ21および22のソースは、トランジスタ23のドレインに接続される。なおトランジスタ23のソースは供給入力vddに接続される。トランジスタ23のゲートは、補完ゲート入力!Gに接続される。

#### 【0108】

増幅器は、第14~第16のN型トランジスタ24~26をさらに含む。トランジスタ24および25のソースが直接クロック入力CKおよび補完クロック入力!CKに接続されるのに対して、トランジスタ24および25のゲートは、一緒にゲート入力Gに接続される。トランジスタ24および25のドレインは、それぞれトランジスタ21および22のゲートに接続される。トランジスタ26のソース-ドレインパスが出力Oおよびグラウンドgndに接続されるのに対して、トランジスタ26のゲートは補完ゲート入力!Gに接続される。

10

#### 【0109】

ゲート信号Gおよび!Gがそれぞれハイおよびローになるようにゲート型センス増幅器4がイネーブルされた場合、トランジスタ24および25は、クロック信号をトランジスタ21および22のゲートに渡す。トランジスタ23は、センス増幅器がハイテール電流(hightail current)で動作するようにグラウンドされる。トランジスタ26がオフに切り換えられると、出力Oは、適切なレベルシフトで、クロック入力CKの論理状態に続く。

20

#### 【0110】

信号Gおよび!Gがそれぞれローおよびハイである場合、増幅器がディスエーブルされるので、トランジスタ24および25は、クロック入力を絶縁する。トランジスタ23がオフされると、増幅器中を流れる電流が停止される。プルダウントランジスタ26がオンされると、出力Oはデフォルト論理ロー状態に維持される。

30

#### 【0111】

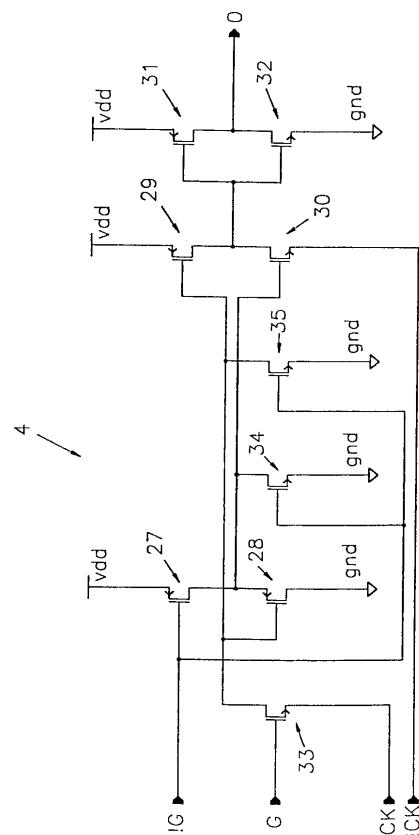

図31は、ゲート回路4として使用され得るゲート型レベルシフタを示す。レベルシフタは、第17~第19のP型トランジスタ27~29および第20のN型トランジスタ30を含む。トランジスタ27および29のソースは、電源入力vddに接続される。トランジスタ27のゲートが補完ゲート入力!Gに接続されるのに対して、トランジスタ27のドレインは、トランジスタ28のソースに接続される。トランジスタ28のドレインはグラウンドに接続される。トランジスタ29のドレインはトランジスタ30のドレインに接続され、トランジスタ30のソースは補完クロック入力!CKに接続され、補完クロック入力!CKのゲートはトランジスタ28のソースに接続される。

40

#### 【0112】

トランジスタ29および30のドレインは、第21のP型トランジスタ31および第22のN型トランジスタ32に接続される。トランジスタ31および32のソースは電源入力vddおよびgndにそれぞれ接続されるのに対して、トランジスタ31および32のドレインは、一緒に接続され、かつ、出力Oに接続される。

#### 【0113】

第23のN型トランジスタ33は、トランジスタ28および29のゲートに接続されたドレイン、クロック入力CKに接続されたソース、およびゲート入力Gに接続されたゲートを有する。第24および第25のN型トランジスタ34および35は、補完ゲート入力!

50

Gに接続されたゲート、グラウンドに接続されたソース、およびトランジスタ30および29のゲートに接続されたドレインをそれぞれ有する。

#### 【0114】

レベルシフタがハイゲート信号Gおよびローゲート信号!Gによってそれぞれイネーブルされた場合、トランジスタ33は、クロック信号をトランジスタ29および30のゲートに渡す。トランジスタ27および28はソースフォロワーとして動作する。ここで、トランジスタ27は、入力信号に最大ブーストを提供するように激しくオンに切り換えられる。トランジスタ34および35はオフに切り換えられ、そして、回路は差動入力レベルシフタとして動作し、それにより、出力OがクロックパルスCKの論理状態に従う。

#### 【0115】

レベルシフタがロー入力Gおよびハイ入力!Gによってそれぞれディスエーブルされた場合、トランジスタ30が確実にオフされ、トランジスタ29が確実にオンされ、かつ、トランジスタ31および32によって形成されるインバータの出力が確実にローに維持されるように、トランジスタ34および35がオフされる。トランジスタ33はクロックパルスCKを絶縁する。

#### 【0116】

図29および図30に示す構成において、クロック相CKおよび!CKは、トランジスタゲートを直接に駆動しないが、その代わり、バスゲートとして機能するトランジスタ24、25、30、および33によってゲートされる。

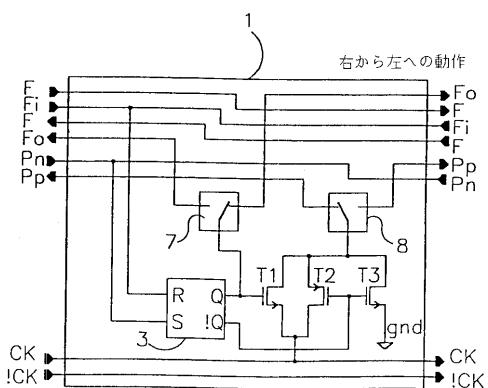

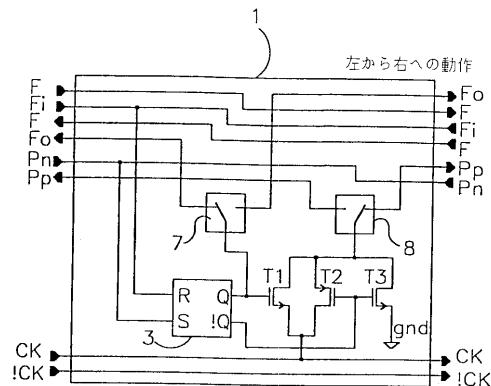

#### 【0117】

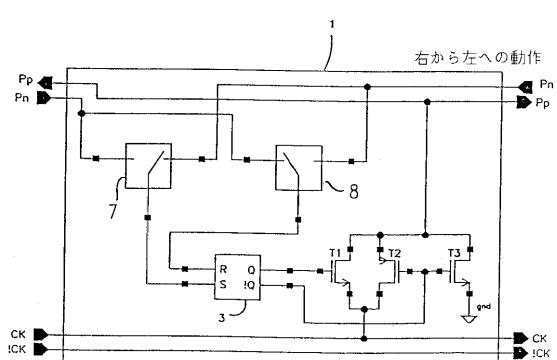

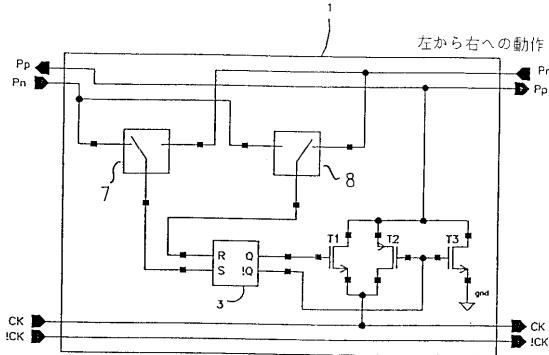

図32は、双方向動作のために改変された、図11に示すタイプの段1を示す。図32の上の図は、左から右へと連続してパルスを生成するための構成を示し、それに対して、図32の下の図は、右から左へ連続してパルスを生成する構成を示す。ここまでに説明した他のタイプの段において、同様の改変をなし得る。

#### 【0118】

段から段へとセットパルスおよびリセットパルスが渡される方向を制御するために、例えばトランスマッシュショングートの形態で電子スイッチ7および8を提供することも改変の1つに含まれる。従って、段1は、スイッチ7によってフリップフロップの出力Qに選択的に接続された左から右へのフィードバックコネクションFOを有する。同様に、この段は、スイッチ8の位置に応じてトランスマッシュショングートT1およびT2の出力から供給されたパルスをセットするための左と右の出力Ppを有する。図32の上部に示すように、左から右への動作について、スイッチ7は、フリップフロップをリセットするのにこのようなパルスを用いる前段の前に、フリップフロップの出力Qから左へと、かつ、前段を介してこの段へと、リセットパルスを方向付ける。トランスマッシュショングートT1およびT2からの出力パルスは、そのフリップフロップをセットするために、次段に供給される。

#### 【0119】

図32の下の図に示すように、スイッチ7および8が交互の位置にある場合、右から左への動作が起こる。この場合、フリップフロップの出力Qからのリセットパルスは、右側へ、次段を介してそのフリップフロップをリセットする次段の後の段へと供給される。スイッチ8は、出力信号を左側へ、そのフリップフロップをセットする次段へと方向付ける。

#### 【0120】

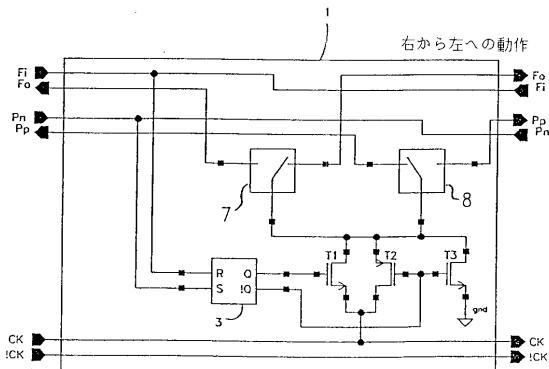

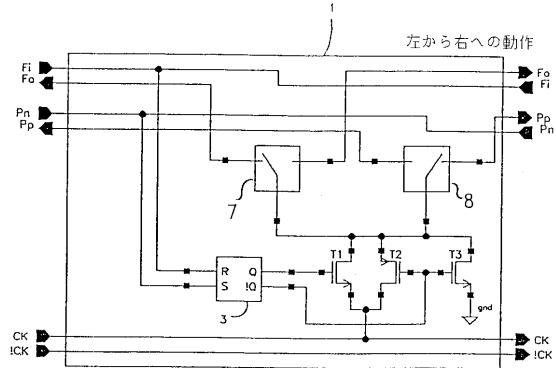

図33は、図32に示した双方向段1と同様であるが、段の間の道順を決める必要のある、信号の数を低減するように改変された、双方向の段1を示す。図33の段は、左右のフィードバックコネクションFOがスイッチ7によって、トランジスタT1およびT2を含むトランスマッシュショングートの出力に選択的に接続される点で、図32の段とは異なる。このことにより、図32に示す段の2つの信号通路を省略できる。

#### 【0121】

図34は、段の間を送られる信号がさらにいっそう低減される、別の双方向の段を示す。この場合、セット入力Sはスイッチ7を介して選択的に接続され、前段または次段からのパルスPnを受けとり、それに対して、フリップフロップ3のリセット入力Rは、スイッ

10

20

30

40

50

チ 8 を介して選択的に接続され、前段または次段からのパルス  $P_n$  をそれぞれ受け取る。

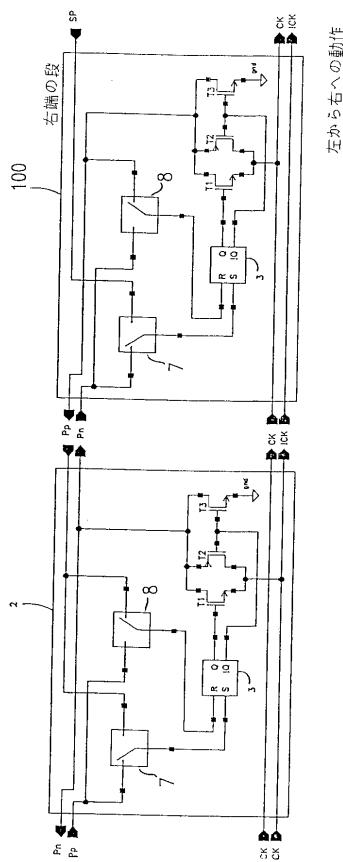

#### 【 0 1 2 2 】

図 3 5 は、クロック信号発振器の最終段 100 に接続された、最後から 2 番目の右側段 2 を示す。図 3 5 に示す左から右への動作において、最終段 100 によって伝送されるクロックパルスは、この段および最後から 2 番目の段もリセットする。右から左への動作の間、スイッチ 7 および 8 が切り換えられ、それにより、最終段 100 のフリップフロップ 3 がスタートパルス  $S_P$  によってセットされる。この段によって伝送されるクロックパルスは、最後から 2 番目の段 2 のフリップフロップ 3 をセットし、そして、最後から 2 番目の段 2 を通過した次のクロックパルスが、最後から 3 番目の段または前段（1）（図示せず）のフリップフロップをセットし、かつ、最終段 100 のフリップフロップをリセットする。

10

#### 【 0 1 2 3 】

最終段 100 は、1 対の段 1 および段 2 の代わりに用い得るが、1 対の段 1 および段 2 の複雑さは必要でない。段 100 は、双方向スタティッククロックパルス発振器の第 1 段としても用い得る。単方向スタティッククロックパルス発振器の場合、第 1 および最終の段は、図 3 5 に参照符号 100 で示すタイプであり得るが、スイッチ 7 および 8 が、その段が発振器の第 1 段として用いられるのか、あるいは、最終段として用いられるのかに応じて、適切なハードウェイアと置き換えられる。

#### 【 0 1 2 4 】

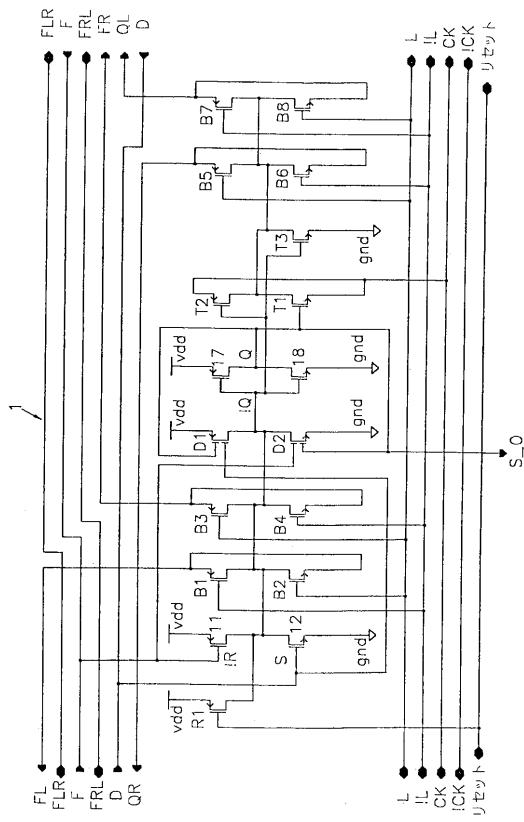

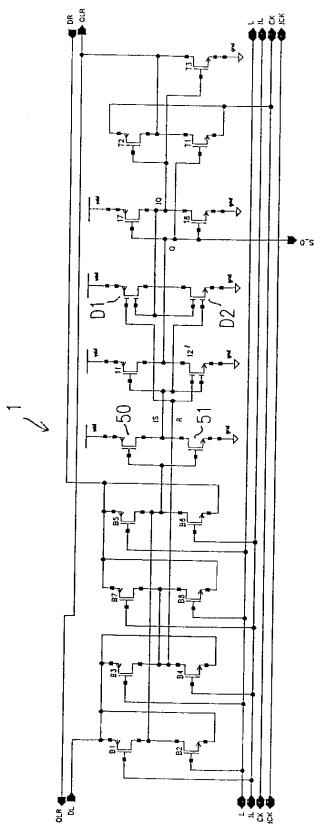

図 3 6 は、図 3 2 に示したタイプの双方向の段を示すが、図 2 5 に示したタイプのフリップフロップ 3 と一緒に使用するためにわずかに再構成されている。スイッチ 7 がトランジスタ  $B_1 \sim B_4$  によって形成された 2 つのトランスマッシュゲートによって具体化されるのに対して、スイッチ 8 は、トランジスタ  $B_5 \sim B_8$  によって形成されたトランスマッシュゲートによって具体化されている。動作の方向は、ライン  $L$  および  $\bar{L}$  上の方向制御信号によって制御される。段の出力を、 $S_O$  に示す。

20

#### 【 0 1 2 5 】

左から右への動作のために、トランジスタ  $B_1$ 、 $B_2$ 、 $B_7$ 、および  $B_8$  がオンされ、かつ、トランジスタ  $B_3$ 、 $B_4$ 、 $B_5$ 、および  $B_6$  がオフされる。逆に、右から左への動作のために、トランジスタ  $B_3$ 、 $B_4$ 、 $B_5$ 、および  $B_6$  がオンされ、かつ、トランジスタ  $B_1$ 、 $B_2$ 、 $B_7$ 、および  $B_8$  がオフされる。トランスマッシュゲート  $B_5$ 、 $B_6$ 、 $B_7$ 、および  $B_8$  は、動作の方向に基づいて、クロックパルス出力を出力端子  $Q_R$  および  $Q_L$  にそれぞれ供給する。トランスマッシュゲート  $B_1$ 、 $B_2$ 、 $B_3$ 、および  $B_4$  は、それぞれ補完出力  $Q$  から 2 つ左または 2 つ右の段に信号を通して、適切な時間にそのフリップフロップをリセットする。リセットトランジスタ  $R_1$  は、供給ライン  $v_{dd}$  とトランジスタ  $11$  および  $12$  のドレインとの間に接続され、かつ、リセットライン  $RESET$  に接続されたゲートを有する。この構成により、例えば電力が発振器に供給された場合に、段の全てのフリップフロップが 1 つの信号に応答して確実にリセットされる。さまざまな入力および出力  $D$ 、 $FRL$ 、 $F$ 、 $FLR$ 、 $FL$ 、および  $FR$  が、さまざまな信号に段と段との間のルートを提供する。

30

#### 【 0 1 2 6 】

図 3 6 に示す段 1 は、クロック信号  $CK$  の立ち上がりエッジと同期した正の出力パルス  $P_p$  を提供するタイプである。補完クロック信号  $\bar{CK}$  の立ち上がりエッジと同期の正の出力パルス  $P_n$  を提供する段 2 は、トランスマッシュゲート  $T_1$  および  $T_2$  の入力が補完クロックライン  $\bar{CK}$  に接続されている点で、図 3 6 に示した段とは異なる。

40

#### 【 0 1 2 7 】

図 3 7 は、縦列に構成されたこのタイプの段を含むスタティッククロックパルス発振器を示す。この図面は、連続する段と段との間の相互接続を示す。左から右への動作のためのスタートパルス  $SPL$  に加えて、右から左への動作のために、第  $N$  段にスタートパルス  $SPR$  が要求される。方向制御ライン  $L$  および  $\bar{L}$  は、動作が左から右へと行われるのか、または、右から左へと行われるのかを決定するために、補完信号を受け取る。共通のリセ

50

ットラインが、動作を開始する前に、全ての段のフリップフロップ3をセットするために、共通のリセット信号RESETを受け取る。

#### 【0128】

図36に示すタイプの段が、低い電圧クロック入力で動作される場合、複数のトランジスタが冗長になり、従ってそれらを省略し得る。例えば、クロックパルスが電源電圧よりもかなり低い電圧の場合、P型デバイスT2は不要であり、かつ、N型デバイスT1がより低い電圧信号を簡単に通し得る。クロック信号がgndとvddとの間でスイングする場合、デバイスT1は、その閾値電圧によって低下された論理ハイ状態を、次段のトランジスタ11および12に渡すだけである。しかし、フリップフロップデバイスは最適化され得るので、フリップフロップは依然このような信号でセットされ得る。トランジスタT2が省略される場合、P型デバイスB5およびB7は要求されない。

10

#### 【0129】

トランスミッショングートB1、B2、B3、およびB4を通過したフィードバック信号は、負状態パルスである。P型デバイスB1およびB3が、おそらく許容できる低下を伴って、フリップフロップのリセットを行わせるのに十分な論理ロー信号を通し得るので、全てのトランジスタを必要としなくてもよい。

#### 【0130】

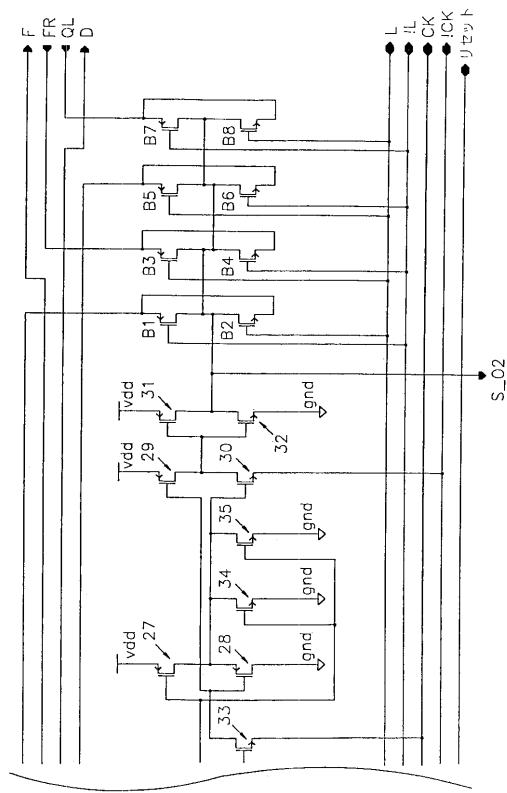

図38は、図28に示したフリップフロップと同様のフリップフロップを用いた、図34に示した段と同様の段をより詳細に示す。図38のフリップフロップは、アクティブハイリセット入力Rおよびアクティブルーセット入力!Sを有する点で、図28のフリップフロップとは異なる。

20

#### 【0131】

トランジスタ50および51を含むインバータが、アクティブルーセット入力とトランジスタB1、B2、B5、およびB6を含むスイッチ7との間に接続され、それにより、フリップフロップを、図34に示した構成で用いることができる。なお、図34の構成は、アクティブハイ入力RおよびSを有するフリップフロップを要求する。スイッチ8は、トランジスタB3、B4、B7、およびB8を含む。

#### 【0132】

図38に示すフリップフロップは、トランジスタ13～16がデュアルゲートトランジスタD1およびD2と置き換えられている点で、図28に示したフリップフロップとは異なる。また、トランジスタ11'は省略され、かつ、トランジスタ12はデュアルゲートトランジスタ12'に置き換えられている。デュアルゲートトランジスタ12'のゲートは、入力Rおよび!Sに接続される。従って、フリップフロップは、アクティブハイリセット入力Rおよびアクティブルーセット入力!Sを有する、セット・オーバーライド・リセット・セット型フリップフロップとして機能する。

30

#### 【0133】

図39Aおよび図39Bは、スタティッククロックパルス発振器のための、別のタイプの双方向段を示す。この段は、図25に示したトランジスタ11～18によって形成されたフリップフロップと、図31に示したトランジスタ27～35によって形成されたゲート型レベルシフタとを含む。トランスミッショングートトランジスタB1～B8は、図36に示したトランジスタB1～B8と同じ機能に対応し、かつ、その同じ機能を実行する。トランジスタD1～D6は、図9の参照符号5に示したタイプの遅延回路を形成し、それにより、2段毎の出力S\_Oがオーバーラップするのを確実に防ぐ。図36に示したリセットトランジスタR1もまた提供される。この段が出力信号S\_OおよびS\_O2を提供するのを示す。出力信号S\_OおよびS\_O2のいずれか一方または両方が、回路アプリケーションに基づいて使用され得る。

40

#### 【0134】

図39Aおよび39Bに示す段は、クロック信号CKの正状態パルスと同期の正のパルスPpを提供する。しかし、クロック信号CKの負状態パルスに一致する正のパルスPnを提供するために、クロック入力コネクションCKおよび!CKを交換するだけでよい。

50

**【0135】**

スタティッククロックパルス発振器は、C M O S集積回路としてまたはC M O S集積回路の一部として具体化され得る。画素( pixel )マトリクスディスプレイで用いるために、このような発振器は、任意のS O I ( s i l i c o n - o n - i n s u l a t o r )技術を用いて、L S I ( 大規模集積 ) ドライバ集積回路内、または、ディスプレイ基板上に設けられ得る。

**【0136】**

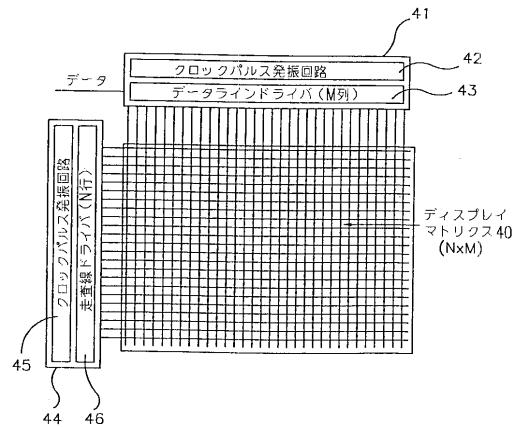

図40は、例えば、液晶素子を含む空間光変調器の形態の、N行×M列からなるディスプレイマトリクス40を含むディスプレイを示す。ディスプレイは、クロックパルス発振回路42および1組のデータラインドライバ43を含むアドレス信号発振器41をさらに含む。クロックパルス発振回路42は、これまでに説明し、かつ、図4～図39Bに示した、任意のタイプの発振器を含む。走査信号発振器44は、画素の行に走査信号を供給し、かつ、クロックパルス発振回路45および1組の走査線ドライバ46を含む。クロックパルス発振回路45は、これまでに説明し、かつ、図4～図39Bに示した、任意のタイプの発振器を含む。クロックパルス発振回路は、回路42のために画素データレートでクロックパルスを発振し、かつ、回路45のためにラインデータレートでクロックパルスを発振する。

**【0137】****【発明の効果】**

完全に静的なクロックパルス発振器を提供することができる。このような発振器は、容量性の緩衝および充電漏れに対して頑強であり、非常に低い周波数で動作し得る。また、非常に高い最大動作周波数を有するクロックパルス発振器を提供することもできる。特に、(ゲート回路が発振器の出力を構成する場合に)クロックパルスが、(任意の外部負荷に加えて)ある時点で2つのトランジスタゲートのみを充電する必要がある発振器を提供することができる。また、クロック信号を完全にゲートすることができる。

**【図面の簡単な説明】**

【図1】2段分の公知のタイプのシフトレジスタを含む回路図である。

【図2】図1に示した段において起こる波形を示す図である。

【図3】公知のタイプのクロックパルス発振器のブロック回路図である。

【図4】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図5】図4に示した段を有するクロックパルス発振器のブロック図である。

【図6】図4および図5に示すクロックパルス発振器内に起こる波形を示すタイミング図である。

【図7】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図8】図7に示した段を有するクロックパルス発振器のブロック図である。

【図9】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図10】図9に示すクロックパルス発振器内に起こる波形を示すタイミング図である。

【図11】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図12】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図13】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図14】図4、図7、図9、および図11～図13に示した段において使用され得るリセット-セットフリップフロップの模式図である。

【図15】図14に示したフリップフロップの回路図である。

【図16】図15のフリップフロップ内に起こる波形を示すタイミング図である。

10

20

30

40

50

【図17】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図18】図17に示した段において使用され得るリセット・セットフリップフロップの回路図である。

【図19】図18のフリップフロップにおいて起こる波形を示すタイミング図である。

【図20】セット動作の間の、図15および図18のフリップフロップの出力波形を示すタイミング図である。

【図21】リセット動作の間の、図15および図18のフリップフロップの出力波形を示すタイミング図である。

【図22】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。 10

【図23】図22に示した段において使用され得るリセット・セットフリップフロップの回路図である。

【図24】図18および図23に示したタイプの改変型フリップフロップの回路図である。 20

【図25】図18および図23に示したタイプの、別の改変型フリップフロップの回路図である。

【図26】ロー入力電圧動作を示す図である。

【図27】ロー入力電圧動作のために改変された、図18および図23に示したタイプのフリップフロップの回路図である。 20

【図28】セットオーバーライド動作のために改変された図18に示すタイプのフリップフロップの回路図である。

【図29】本発明のある実施形態を構成する、2段分のスタティッククロックパルス発振器の回路図である。

【図30】図29に示した段において使用され得る、ゲート型センス増幅器の回路図である。

【図31】図29に示した段において使用され得る、ゲート型差動電圧レベルシフタの回路図である。

【図32】本発明の実施形態を構成する双方向スタティッククロックパルス発振器の、ある段の回路図である。 30

【図33】本発明の実施形態を構成する双方向スタティッククロックパルス発振器の、ある段の回路図である。

【図34】本発明の実施形態を構成する双方向スタティッククロックパルス発振器の、ある段の回路図である。

【図35】本発明の実施形態を構成する、双方向スタティッククロックパルス発振器の、図34に示したタイプの後ろから2番目の段、ならびに、最後または最終の段の回路図である。

【図36】図32に示した段と同様の双方向の段のより詳細な回路図である。

【図37】1つの段を図36に示した、クロックパルス発振器のブロック図である。

【図38】本発明の実施形態を構成する別の双方向スタティッククロックパルス発振器の、ある段の回路図である。 40

【図39A】本発明の実施形態を構成する、さらなる双方向スタティックパルス発振器の、ある段の回路図である。

【図39B】本発明の実施形態を構成する、さらなる双方向スタティックパルス発振器の、ある段の回路図である。

【図40】本発明の実施形態を構成する空間光変調器の模式的なブロック図である。

#### 【符号の説明】

1 段

2 段

3 フリップフロップ

## 4 ゲート回路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39A】

【図39B】

【図40】

---

フロントページの続き

審査官 石井 研一

(56)参考文献 特開平07-248741(JP,A)

特開平06-204809(JP,A)

米国特許第5128974(US,A)

米国特許第4746915(US,A)

米国特許第4785297(US,A)

米国特許第4612659(US,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H03K 3/03

G09G 3/20 612