(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6180882号

(P6180882)

(45) 発行日 平成29年8月16日(2017.8.16)

(24) 登録日 平成29年7月28日(2017.7.28)

(51) Int.Cl.

F 1

|             |              |                  |      |       |     |

|-------------|--------------|------------------|------|-------|-----|

| <b>H04N</b> | <b>9/07</b>  | <b>(2006.01)</b> | H04N | 9/07  | A   |

| <b>G02B</b> | <b>5/20</b>  | <b>(2006.01)</b> | G02B | 5/20  | 101 |

| <b>H01L</b> | <b>27/14</b> | <b>(2006.01)</b> | H01L | 27/14 |     |

| <b>H04N</b> | <b>5/367</b> | <b>(2011.01)</b> | H04N | 5/367 |     |

請求項の数 11 (全 29 頁)

(21) 出願番号

特願2013-226299 (P2013-226299)

(22) 出願日

平成25年10月31日(2013.10.31)

(65) 公開番号

特開2015-88947 (P2015-88947A)

(43) 公開日

平成27年5月7日(2015.5.7)

審査請求日

平成28年1月7日(2016.1.7)

(73) 特許権者 316005926

ソニーセミコンダクタソリューションズ株式会社

神奈川県厚木市旭町四丁目14番1号

100121131

弁理士 西川 孝

100082131

弁理士 稲本 義雄

(72) 発明者 山本 敦彦

東京都港区港南1丁目7番1号 ソニー株式会社内

審査官 西谷 憲人

最終頁に続く

(54) 【発明の名称】 固体撮像装置、信号処理装置、および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、

前記複数画素群がペイヤ配列されてなるカラーフィルタと

を備え、

前記画素共有の単位内で発生した欠陥画素は、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正される

固体撮像装置。

## 【請求項 2】

前記複数画素群は、互いに画素共有のない画素で構成されている

請求項 1 に記載の固体撮像装置。

## 【請求項 3】

前記画素共有の単位は、 $2 \times 2$  画素である

請求項 2 に記載の固体撮像装置。

## 【請求項 4】

前記複数画素群は、互いに画素共有のない画素を、その構成の少なくとも半分含むよう構成されている

請求項 1 に記載の固体撮像装置。

## 【請求項 5】

10

20

前記画素共有の単位は、 $2 \times 4$  画素である

請求項 4 に記載の固体撮像装置。

**【請求項 6】**

前記画素共有の単位は、 $1 \times 4$  画素である

請求項 4 に記載の固体撮像装置。

**【請求項 7】**

前記複数画素群は、4 画素で構成される

請求項 1 に記載の固体撮像装置。

**【請求項 8】**

前記色コーディングは、原色市松のコーディングである

請求項 1 に記載の固体撮像装置。 10

**【請求項 9】**

前記色コーディングは、WRGBのコーディングである

請求項 1 に記載の固体撮像装置。

**【請求項 10】**

同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がペイヤ配列されてなるカラーフィルタとを備える固体撮像装置から出力される出力信号において、前記画素共有の単位内で発生した欠陥画素を、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正する補正処理部を 20

備える信号処理装置。

**【請求項 11】**

同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がペイヤ配列されてなるカラーフィルタとを備え、前記画素共有の単位内で発生した欠陥画素は、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正される固体撮像装置と、

入射光を前記固体撮像装置に入射する光学系と、

前記固体撮像装置から出力される出力信号を処理する信号処理回路と

を有する電子機器。

**【発明の詳細な説明】**

30

**【技術分野】**

**【0001】**

本開示は、固体撮像装置、信号処理装置、および電子機器に関し、特に、白点補正における解像度の劣化を抑えることができるようとした固体撮像装置、信号処理装置、および電子機器に関する。

**【背景技術】**

**【0002】**

同一画素共有の固体撮像装置において、4 画素同色のカラーフィルタを付ける場合、同一画素共有で同じカラーコーディングを行っていた（特許文献 1 参照）。

**【先行技術文献】**

40

**【特許文献】**

**【0003】**

**【特許文献 1】特開 2010 - 28423 号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

しかしながら、画素共有内のフローティングディフュージョン部のリークなどで、白点が発生した場合、例えば、2 画素分離れた 4 画素同色の画素から補正することになり、補正対象の画素の位置に対して、補正に用いる画素の位置が空間的に離れてしまっていた。このため、補正後の解像度が劣化してしまうことがあった。

50

**【0005】**

本開示は、このような状況に鑑みてなされたものであり、白点補正における解像度の劣化を抑えることができるものである。

**【課題を解決するための手段】****【0006】**

本技術の第1の側面の固体撮像装置は、同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとを備え、前記画素共有の単位内で発生した欠陥画素は、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正される。

**【0007】**

前記複数画素群は、互いに画素共有のない画素で構成されている。

**【0008】**

前記画素共有の単位は、 $2 \times 2$ 画素である。

**【0009】**

前記複数画素群は、互いに画素共有のない画素を、その構成の少なくとも半分含むように構成されている。

**【0010】**

前記画素共有の単位は、 $2 \times 4$ 画素である。

**【0011】**

前記画素共有の単位は、 $1 \times 4$ 画素である。

**【0013】**

前記複数画素群は、4画素で構成される。

**【0014】**

前記色コーディングは、原色市松のコーディングである。

**【0015】**

前記色コーディングは、WRGBのコーディングである。

**【0016】**

本技術の第2の側面の信号処理装置は、同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとを備える固体撮像装置から出力される出力信号において、前記画素共有の単位内で発生した欠陥画素を、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正する補正処理部を備える。

**【0020】**

本技術の第3の側面の電子機器は、同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとを備え、前記画素共有の単位内で発生した欠陥画素は、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正される固体撮像装置と、入射光を前記固体撮像装置に入射する光学系と、前記固体撮像装置から出力される出力信号を処理する信号処理回路とを有する。

**【0021】**

本技術の第1の側面においては、同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとが備えられる。そして、前記画素共有の単位内で発生した欠陥画素が、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正される。

**【0022】**

本技術の第2の側面においては、同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとを備える固体撮像装置から出力される出力信号において、前記画素共有の単位内で発生した欠陥画素が、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正される。

10

20

30

40

50

画素群内の画素を用いて補正される。

**【0023】**

本技術の第3の側面においては、固体撮像装置に、同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとを備えられ、前記画素共有の単位内で発生した欠陥画素が、前記複数画素内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正される。そして、入射光が前記固体撮像装置に入射され、前記固体撮像装置から出力される出力信号が処理される。

**【発明の効果】**

**【0024】**

本技術によれば、白点補正を行うことができる。また、本技術によれば、白点補正における解像度の劣化を抑えることができる。

**【0025】**

なお、本明細書に記載された効果は、あくまで例示であり、本技術の効果は、本明細書に記載された効果に限定されるものではなく、付加的な効果があつてもよい。

**【図面の簡単な説明】**

**【0026】**

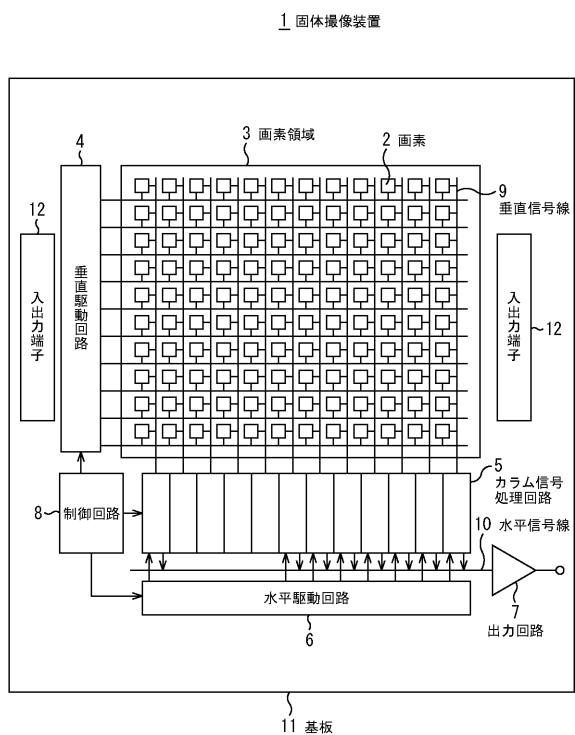

【図1】本技術を適用した固体撮像装置の概略構成例を示すブロック図である。

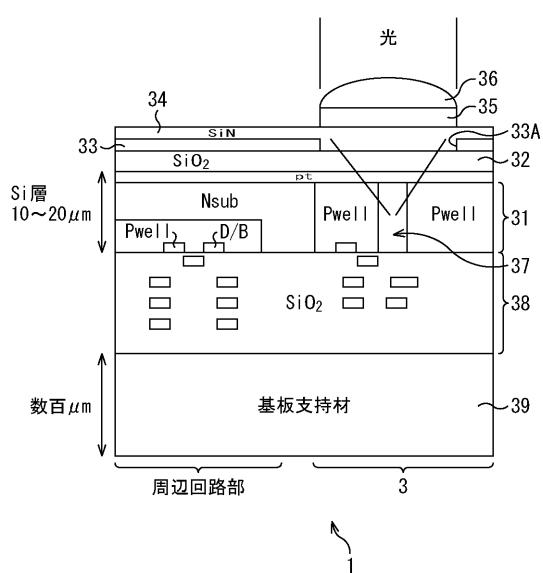

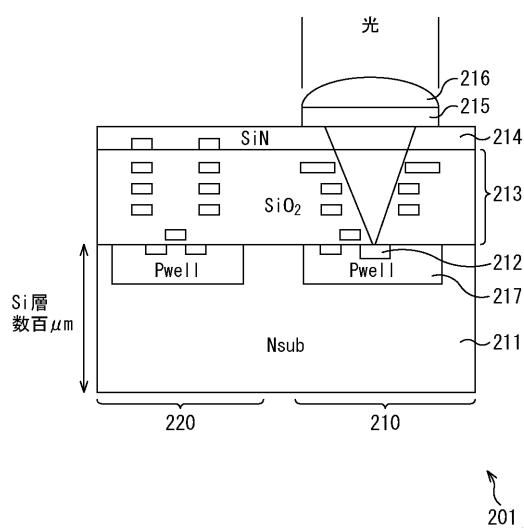

【図2】本技術の一実施の形態に係る固体撮像装置の断面図を示す図である。

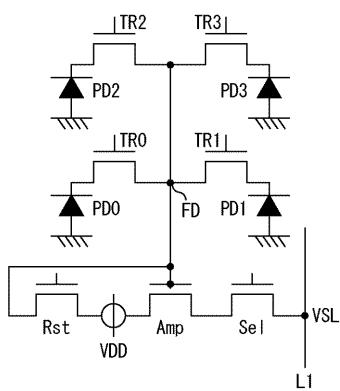

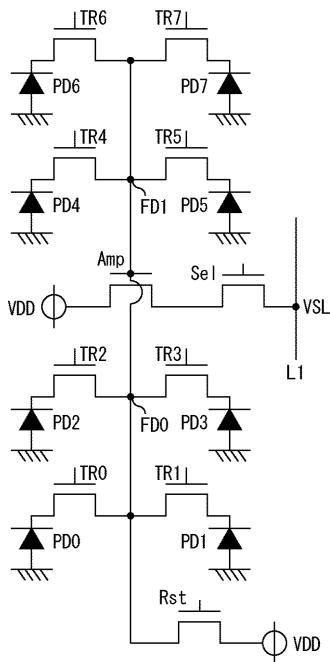

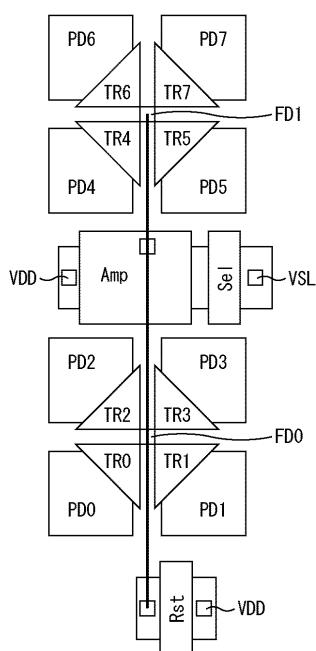

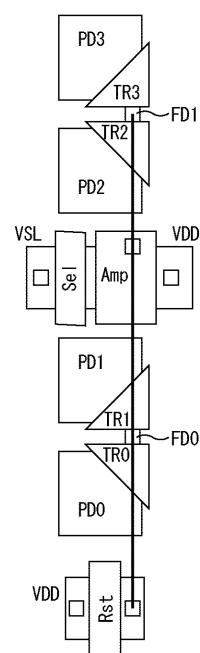

【図3】 $2 \times 2$ 画素共有単位の回路構成の一例を示す回路図である。

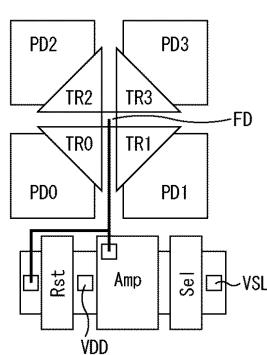

【図4】 $2 \times 2$ 画素共有単位の回路構成の一例を示す平面図である。

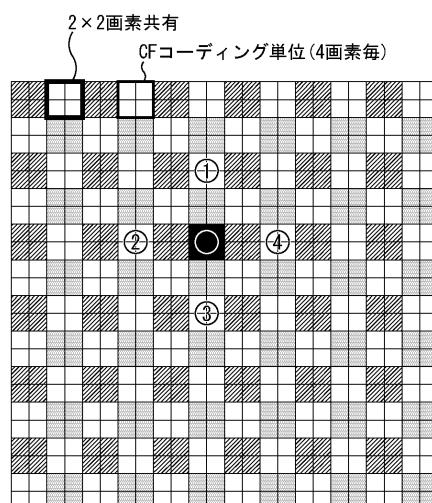

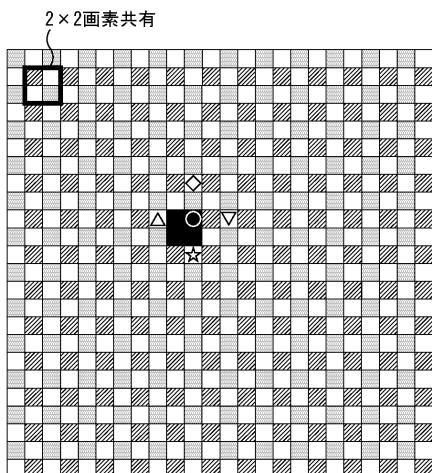

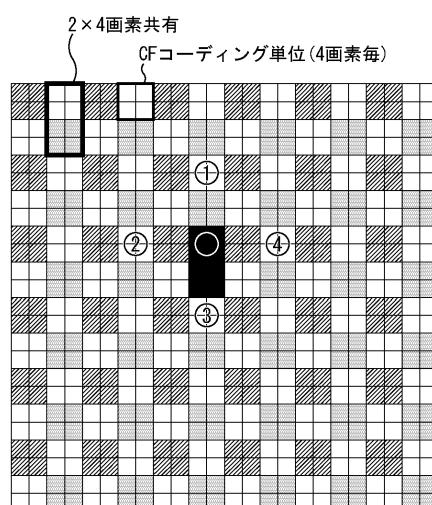

【図5】 $2 \times 2$ 画素共有単位とカラーフィルタのコーディングの単位との関係の例を示す図である。

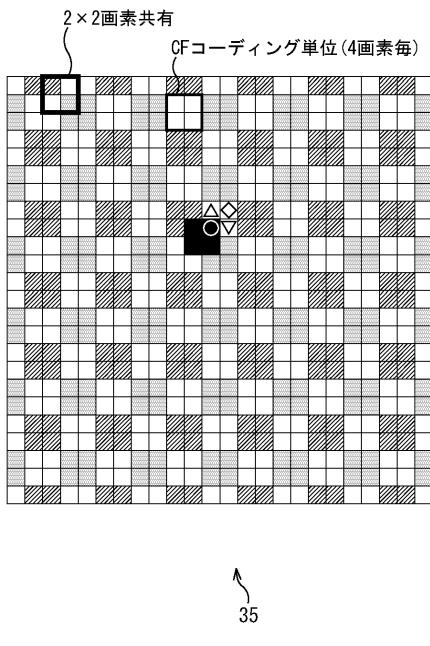

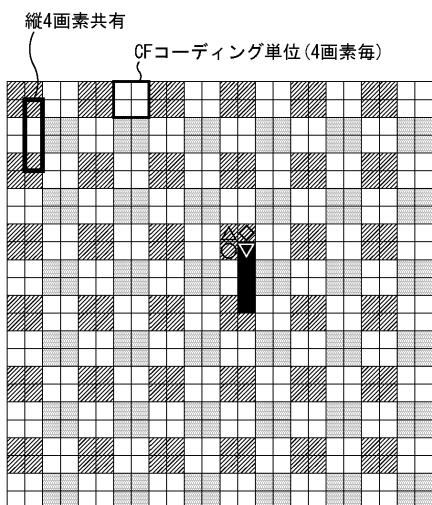

【図6】本技術の $2 \times 2$ 画素共有単位とカラーフィルタのコーディングの単位との関係を示す図である。

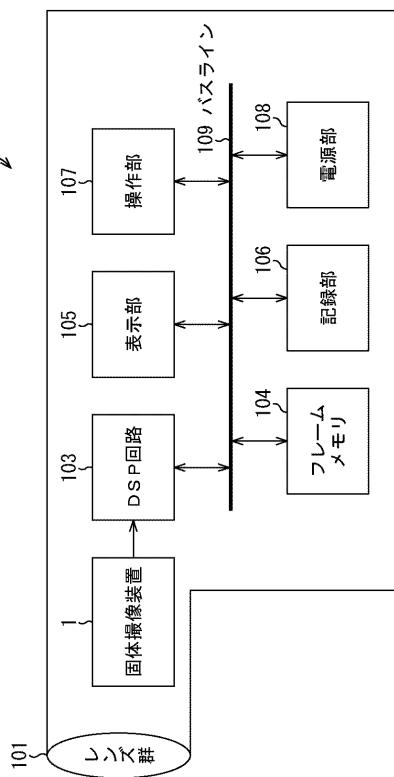

【図7】本技術の電子機器の構成例を示すブロック図である。

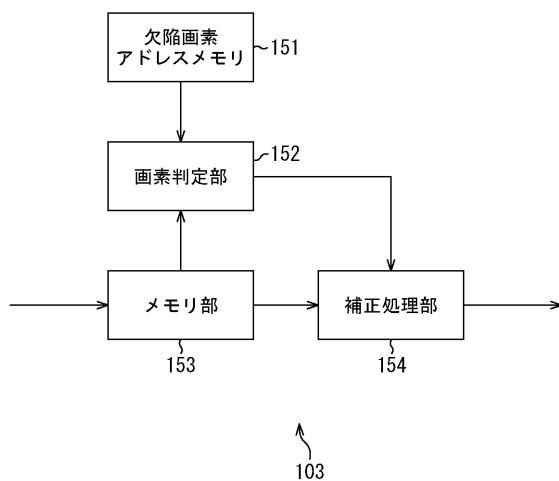

【図8】DSP回路の構成例を示す図である。

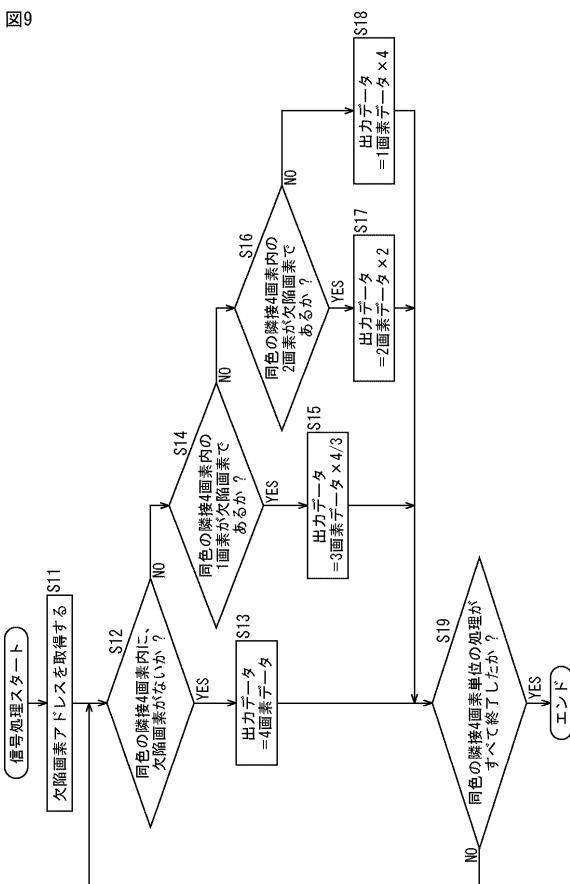

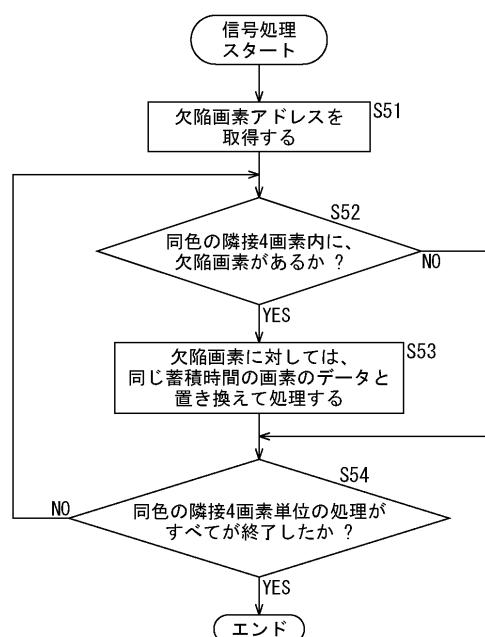

【図9】図8のDSP回路の信号処理の例を説明するフローチャートである。

【図10】DSP回路の構成例を示す図である。

【図11】図10のDSP回路の信号処理の例を説明するフローチャートである。

【図12】DSP回路の構成例を示す図である。

【図13】図12のDSP回路の信号処理の例を説明するフローチャートである。

【図14】画素毎の市松RGBベイヤ配列の例を示す図である。

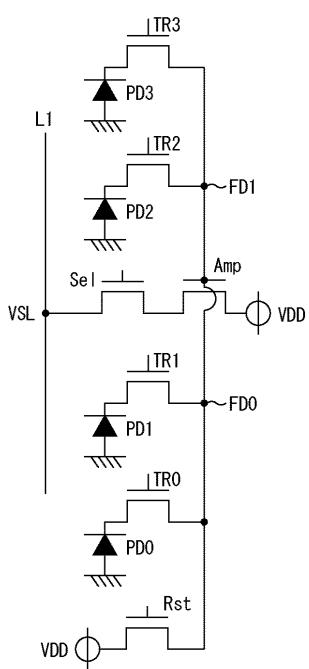

【図15】 $2 \times 4$ 画素共有単位の回路構成の一例を示す回路図である。

【図16】 $2 \times 4$ 画素共有単位の回路構成の一例を示す平面図である。

【図17】 $2 \times 4$ 画素共有単位とカラーフィルタのコーディングの単位との関係の例を示す図である。

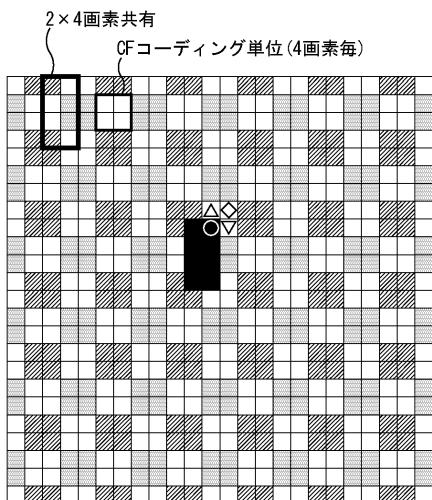

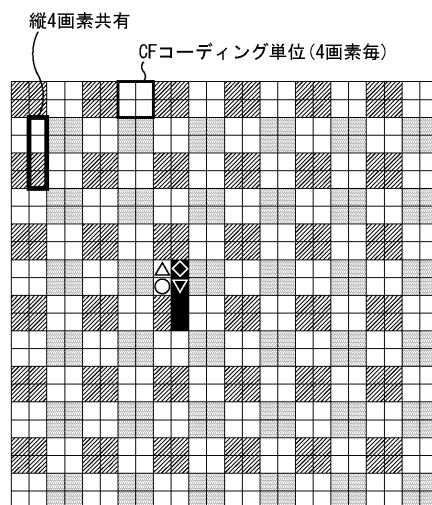

【図18】本技術の $2 \times 4$ 画素共有単位とカラーフィルタのコーディングの単位との関係を示す図である。

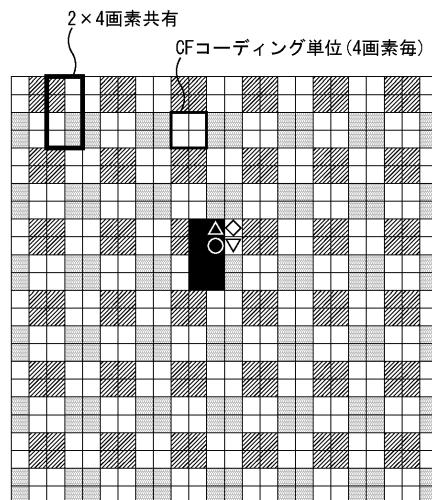

【図19】本技術の $2 \times 4$ 画素共有単位とカラーフィルタのコーディングの単位との関係を示す図である。

【図20】 $1 \times 4$ 画素共有単位の回路構成の一例を示す回路図である。

【図21】 $1 \times 4$ 画素共有単位の回路構成の一例を示す平面図である。

【図22】本技術の $1 \times 4$ 画素共有単位とカラーフィルタのコーディングの単位との関係を示す図である。

【図23】本技術の $1 \times 4$ 画素共有単位とカラーフィルタのコーディングの単位との関係を示す図である。

【図24】本技術の他の実施の形態に係る固体撮像装置の断面図を示す図である。

【図25】コンピュータの構成例を示すブロック図である。

**【発明を実施するための形態】**

10

20

30

40

50

## 【0027】

以下、本開示を実施するための形態（以下実施の形態とする）について説明する。なお、説明は以下の順序で行う。

- 0．固体撮像装置の概略構成例

- 1．第1の実施の形態（ $2 \times 2$ 画素共有の例）

- 2．第2の実施の形態（ $2 \times 4$ 画素共有の例）

- 3．第3の実施の形態（ $1 \times 4$ 画素共有の例）

- 4．第4の実施の形態（固体撮像装置の他の構成例）

- 5．第5の実施の形態（コンピュータ）

## 【0028】

10

- <0．固体撮像装置の概略構成例>

<固体撮像装置の概略構成例>

図1は、本技術の各実施の形態に適用されるCMOS（Complementary Metal Oxide Semiconductor）固体撮像装置の概略構成例を示している。

## 【0029】

図1に示されるように、固体撮像装置（素子チップ）1は、半導体基板11（例えばシリコン基板）に複数の光電変換素子を含む画素2が規則的に2次元的に配列された画素領域（いわゆる撮像領域）3と、周辺回路部とを有して構成される。

## 【0030】

20

画素2は、光電変換素子（例えばフォトダイオード）と、複数の画素トランジスタ（いわゆるMOSトランジスタ）を有してなる。複数の画素トランジスタは、例えば、転送トランジスタ、リセットトランジスタ、および増幅トランジスタの3つのトランジスタで構成することができ、さらに選択トランジスタを追加して4つのトランジスタで構成することもできる。各画素2（単位画素）の等価回路は一般的なものと同様であるので、ここでは詳細な説明は省略する。

## 【0031】

また、画素2は、画素共有構造とすることもできる。画素共有構造は、例えば、図3を参照して後述されるが、複数のフォトダイオード、複数の転送トランジスタ、共有される1つのフローティングディフュージョン、および、共有される1つずつの他の画素トランジスタから構成される。

30

## 【0032】

周辺回路部は、垂直駆動回路4、カラム信号処理回路5、水平駆動回路6、出力回路7、および制御回路8から構成される。

## 【0033】

制御回路8は、入力クロックや、動作モード等を指令するデータを受け取り、また、固体撮像装置1の内部情報等のデータを出力する。具体的には、制御回路8は、垂直同期信号、水平同期信号、およびマスタクロックに基づいて、垂直駆動回路4、カラム信号処理回路5、および水平駆動回路6の動作の基準となるクロック信号や制御信号を生成する。そして、制御回路8は、これらの信号を垂直駆動回路4、カラム信号処理回路5、および水平駆動回路6に入力する。

40

## 【0034】

垂直駆動回路4は、例えばシフトレジスタによって構成され、画素駆動配線を選択し、選択された画素駆動配線に画素2を駆動するためのパルスを供給し、行単位で画素2を駆動する。具体的には、垂直駆動回路4は、画素領域3の各画素2を行単位で順次垂直方向に選択走査し、垂直信号線9を通して各画素2の光電変換素子において受光量に応じて生成した信号電荷に基づいた画素信号をカラム信号処理回路5に供給する。

## 【0035】

カラム信号処理回路5は、画素2の例えれば列毎に配置されており、1行分の画素2から出力される信号を画素列毎にノイズ除去等の信号処理を行う。具体的には、カラム信号処理回路5は、画素2固有の固定パターンノイズを除去するためのCDS（Correlated Double

50

Sampling) や、信号増幅、A/D (Analog/Digital) 変換等の信号処理を行う。カラム信号処理回路 5 の出力段には、水平選択スイッチ (図示せず) が水平信号線 10 との間に接続されて設けられる。

#### 【0036】

水平駆動回路 6 は、例えばシフトレジスタによって構成され、水平走査パルスを順次出力することによって、カラム信号処理回路 5 の各々を順番に選択し、カラム信号処理回路 5 の各々から画素信号を水平信号線 10 に出力させる。

#### 【0037】

出力回路 7 は、カラム信号処理回路 5 の各々から水平信号線 10 を通して順次に供給される信号に対し、信号処理を行って出力する。出力回路 7 は、例えば、バッファリングだけを行う場合もあるし、黒レベル調整、列ばらつき補正、各種デジタル信号処理等を行う場合もある。10

#### 【0038】

入出力端子 12 は、外部と信号のやりとりをするために設けられる。

#### 【0039】

< 固体撮像装置の断面例 >

図 2 は、固体撮像装置の画素領域 3 および周辺回路部の構造の一例を示す断面図である。図 2 の例においては、裏面照射型の固体撮像装置の例が示されている。

#### 【0040】

図 2 の例の固体撮像装置 1においては、ウエハを CMP(Chemical Mechanical Polishing) によって研磨することにより、10乃至20 μm 程度の厚さの Si (シリコン) 層 (素子層) 31 が形成される。その厚さの好ましい範囲は、可視光に対して 5乃至15 μm、赤外光に対して 5乃至50 μm、紫外光に対して 3乃至 7 μm である。この Si 層の一方の面側には、SiO<sub>2</sub> 膜 32 を挟んで遮光膜 33 が形成されている。20

#### 【0041】

遮光膜 33 は、配線と異なり、光学的な要素だけを考慮してレイアウトされる。この遮光膜 33 には開口部 33A が形成されている。遮光膜 33 の上には、パッシベーション膜としてシリコン窒化膜 (SiN) 34 が形成され、さらに、開口部 33A の上方にカラーフィルタ 35 および OCL(On Chip Lens) 36 が形成されている。

#### 【0042】

すなわち、Si 層 31 の一方の面側から入射する光は、OCL 36 およびカラーフィルタ 35 を経由し、Si 層 31 に形成されるフォトダイオード 37 の受光面に導かれる画素構造となっている。Si 層 31 の他方の面側には、トランジスタや金属配線が形成される配線層 38 が形成され、その下には、さらに、基板支持材 39 が貼り付けられている。30

#### 【0043】

< 1. 第 1 の実施の形態 (2 × 2 画素共有の例) >

< 画素共有単位の構成例 >

まず、図 3 および図 4 を参照して、2 × 2 画素共有単位の回路構成例について説明する。図 3 は、2 × 2 画素共有単位の回路構成の一例を示す回路図である。図 4 は、2 × 2 画素共有単位の回路構成の一例を示す平面図である。40

#### 【0044】

図 3 および図 4 で示されるように、2 × 2 画素共有単位は、4 つの光電変換素子、例えば、フォトダイオード P D 0 乃至 P D 3、およびそれらに対応する 4 つの転送トランジスタ T R 0 乃至 T R 3、並びに、リセットトランジスタ R s t、増幅トランジスタ A m p、および選択トランジスタ S e l の 3 つのトランジスタを有する構成となっている。

#### 【0045】

フォトダイオード P D 0 乃至 P D 3 は、アノード電極が負側電源 (例えば、グランド) に接続されており、受光した光をその光量に応じた電荷量の光電荷 (ここでは、光電子) に光電変換する。フォトダイオード P D 0 乃至 P D 3 のカソード電極は、対応する各転送トランジスタ T R 0 乃至 T R 3 を介して増幅トランジスタ A m p のゲート電極と電気的に50

接続されている。増幅トランジスタ A m p のゲート電極と 4 つの転送トランジスタ T R 0 乃至 T R 3 とが電気的に繋がったノードをフローティングディフュージョン F D と称する。

#### 【 0 0 4 6 】

転送トランジスタ T R 0 乃至 T R 3 は、対応するフォトダイオード P D 0 乃至 P D 3 のカソード電極とフローティングディフュージョン F D との間に接続されている。転送トランジスタ T R 0 乃至 T R 3 のゲート電極には、高レベル（例えば、V D D レベル）がアクティブ（以下、「H i g h アクティブ」と記述する）の転送パルス T R F が、図示せぬ転送線を介して与えられる。転送パルス T R F が与えられることで、転送トランジスタ T R 0 乃至 T R 3 はオン状態となってフォトダイオード P D 0 乃至 P D 3 で光電変換された光電荷をフローティングディフュージョン F D に転送する。

#### 【 0 0 4 7 】

リセットトランジスタ R s t は、ドレイン電極が画素電源 V D D に、ソース電極がフローティングディフュージョン F D にそれぞれ接続されている。リセットトランジスタ R s t のゲート電極には、フォトダイオード P D 0 乃至 P D 3 からフローティングディフュージョン F D への信号電荷の転送に先立って、H i g h アクティブのリセットパルス R S T が図示せぬリセット線を介して与えられる。リセットパルス R S T が与えられることで、リセットトランジスタ R s t はオン状態となり、フローティングディフュージョン F D の電荷を画素電源 V D D に捨てるこことによってフローティングディフュージョン F D をリセットする。

#### 【 0 0 4 8 】

増幅トランジスタ A m p は、ゲート電極がフローティングディフュージョン F D に、ドレイン電極が画素電源 V D D にそれぞれ接続されている。そして、増幅トランジスタ A m p は、リセットトランジスタ R s t によってリセットした後のフローティングディフュージョン F D の電位をリセット信号（リセットレベル）V r e s e t として出力する。増幅トランジスタ A m p はさらに、転送トランジスタ T R 0 乃至 T R 3 によって信号電荷を転送した後のフローティングディフュージョン F D の電位を光蓄積信号（信号レベル）V s i g として出力する。

#### 【 0 0 4 9 】

選択トランジスタ S e 1 は、例えば、ドレイン電極が増幅トランジスタ A m p のソース電極に、ソース電極が垂直信号線 L 1 にそれぞれ接続されている。選択トランジスタ S e 1 のゲート電極には、H i g h アクティブの選択パルス S E L が図示せぬ選択線を介して与えられる。選択パルス S E L が与えられることで、選択トランジスタ S e 1 はオン状態となって単位画素を選択状態とし、増幅トランジスタ A m p から出力される信号を垂直信号線 L 1 に中継する。

#### 【 0 0 5 0 】

なお、選択トランジスタ S e 1 については、画素電源 V D D と増幅トランジスタ A m p のドレインとの間に接続した回路構成を探ることも可能である。

#### 【 0 0 5 1 】

< 画素共有単位と CF コーディング単位との関係 >

図 5 は、 $2 \times 2$  画素共有単位とカラーフィルタ(CF)のコーディングの単位との関係を示す図である。図 5 の例においては、ハッチなしの緑(GREEN)画素、斜線のハッチが赤(RED)画素、残りのハッチが青(BLUE)画素を示している。これらの記載は、以下の他の図においても同様である。また、図 5 の例においては、太線に示されるように、 $2 \times 2$  画素共有の例が示されており、また、実線に示されるように、4 画素毎に同じカラーフィルタをRGB 市松コーディング(ベイヤ配列)した例が示されている。

#### 【 0 0 5 2 】

すなわち、図 5 の例においては、画素共有単位と、同じカラーフィルタのコーディング単位とが 1 対 1 対応しており、画素共有単位の $2 \times 2$  画素の各画素は、同じカラーフィルタでコーディングされている。

10

20

30

40

50

**【0053】**

このため、中央の黒い $2 \times 2$ 画素部分に、フローティングディフュージョンのリークなどで白点が発生した場合、その縁画素の補正は、図中1乃至4の数字が示される最周辺の位置の縁画素を使用して行うことが考えられる。すなわち、図5の例の場合、単位画素で、2画素空間的に離れたデータで補正することになる。

**【0054】**

<本技術の画素共有単位とCFコーディング単位との関係>

図6は、本技術を適用した画素共有単位とカラーフィルタ(CF)のコーディングの単位との関係を示す図である。図6の例においては、太線に示されるように、 $2 \times 2$ 画素共有の例が示されており、また、実線に示されるように、4画素毎に同じカラーフィルタをRGB市松コーディング(ベイヤ配列)した例が示されている。10

**【0055】**

図6の例において、画素共有単位の $2 \times 2$ 画素の各画素は、太線に示されるように、それぞれ異なるカラーフィルタでコーディングされている。換言するに、同一カラーフィルタのコーディング単位の4画素は、異なる画素共有単位の画素で構成されている。すなわち、同一カラーフィルタのコーディング単位の4画素(以下、適宜、同色の隣接4画素とも称する)は、互いに画素共有のない画素で構成されている。

**【0056】**

なお、図6のカラーフィルタ35は、図5のカラーフィルタを、例えば、上に1画素、かつ、右に1画素移動させて形成されたものである。20

**【0057】**

このようにすることで、中央の黒い画素部分に、フローティングディフュージョンのリークなどにより白点が発生した場合、黒い画素部分のうち、例えば、丸が示される縁画素の補正は、同一縁のカラーフィルタのコーディング単位の三角、菱形、および逆三角が示される縁画素の少なくとも1つを使用して行われる。なお、補正には、三角、菱形、および逆三角が示される縁画素のいずれか1つを用いてもよいし、そのうち、2つ、あるいはすべての画素を用いてもよい。

**【0058】**

すなわち、図6の例の場合、補正に使用される画素が、隣の画素なので、空間的に近いデータで補正可能であり、図5の例の場合よりも解像度劣化を抑えることができる。30

**【0059】**

以下、白点が発生した場合の画素の補正方法について具体的に説明していく。

**【0060】**

<電子機器の構成例>

図7は、本技術を適用した電子機器としての、カメラ装置の構成例を示すブロック図である。図7の電子機器においては、白点発生のために、上述したような補正が行われる。

**【0061】**

図7のカメラ装置100は、レンズ群などからなる光学部101、図1に示された画素2の各構成が採用される固体撮像装置(撮像デバイス)1、およびカメラ信号処理回路であるDSP(Digital Signal Processor)回路103を備える。また、カメラ装置100は、フレームメモリ104、表示部105、記録部106、操作部107、および電源部108も備える。DSP回路103、フレームメモリ104、表示部105、記録部106、操作部107および電源部108は、バスライン109を介して相互に接続されている。40

**【0062】**

光学部101は、被写体からの入射光(像光)を取り込んで固体撮像装置1の撮像面上に結像する。固体撮像装置1は、光学部101によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。DSP回路103は、図1の出力回路7から出力された信号に対して、上述したフローティングディフュージョンのリークなどによる白点の発生のための補正を行う。DSP回路103は、補正された信号50

を、例えば、フレームメモリ 104 に記憶させる。

**【0063】**

表示部 105 は、例えば、液晶パネルや有機 E L (Electro Luminescence) パネル等のパネル型表示装置からなり、固体撮像装置 1 で撮像された動画または静止画を表示する。記録部 106 は、固体撮像装置 1 で撮像された動画または静止画を、ビデオテープや D V D (Digital Versatile Disk) 等の記録媒体に記録する。

**【0064】**

操作部 107 は、ユーザによる操作の下に、カメラ装置 100 が有する様々な機能について操作指令を発する。電源部 108 は、D S P 回路 103、フレームメモリ 104、表示部 105、記録部 106 および操作部 107 の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

10

**【0065】**

< D S P 回路の構成例 >

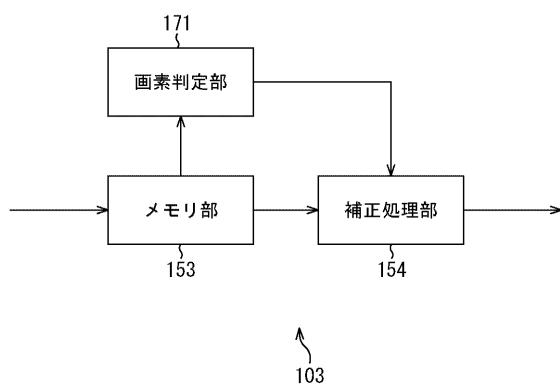

図 8 は、白点が発生した場合の画素の補正を行う、D S P 回路の第 1 の構成例を示すブロック図である。

**【0066】**

図 8 の例において、D S P 回路 103 は、欠陥画素アドレスメモリ 151、画素判定部 152、メモリ部 153、および補正処理部 154 を含むように構成される。

**【0067】**

欠陥画素アドレスメモリ 151 は、工場出荷時に欠陥画素として判定された欠陥画素のアドレスを記憶している。欠陥画素の判定は、次のように行われる。例えば、白点については、工場出荷時にOPB基準のダーク状態である出力以上が白点と判定される。一方、HL 点欠陥ならば、工場出荷時においては、感度光量程度の光を入れて同色で出力の割合がある割合以上多い（カラーフィルタ（CF）抜け）、またはある割合以上少ないもの（ゴミ）が欠陥画素として判定される。このようにして判定された欠陥画素のアドレスが、欠陥画素アドレスメモリ 151 に書き込まれている。

20

**【0068】**

画素判定部 152 は、欠陥画素アドレスメモリ 151 に記憶される欠陥画素アドレスを参照し、メモリ部 153 に記憶される画像における同色の隣接 4 画素（CF のコーディング）単位に欠陥画素が含まれるか否かを判定する。画素判定部 152 は、判定結果（すなわち、同色の隣接 4 画素単位における欠陥画素の含まれる個数（割合））に応じて、補正処理部 154 の補正処理を制御する。

30

**【0069】**

メモリ部 153 は、例えば、フレームメモリで構成される。メモリ部 153 は、固体撮像装置 1 の出力回路 7 から出力される信号（画像）を一旦記憶している。

**【0070】**

補正処理部 154 は、メモリ部 153 から同色の隣接 4 画素毎に読み出し、画素判定部 152 からの制御に応じて、画素データを補正処理し、出力する。

**【0071】**

< 信号処理の例 >

次に、図 9 のフローチャートを参照して、図 8 の D S P 回路 103 による信号処理の例を説明する。この信号処理は、CF のコーディング単位である同色の隣接 4 画素毎に行われる。また、例えば、この信号処理は、同色の隣接 4 画素単位の画素データを加算データとして後段に出力する処理である。なお、図 6 を適宜参照し、 $2 \times 2$  画素共有単位を例に説明する。

40

**【0072】**

固体撮像装置 1 の出力回路 7 から出力される信号（画像）がメモリ部 153 に記憶される。補正処理部 154 は、メモリ部 153 から処理対象の同色の隣接 4 画素（CF のコーディング単位）を読み出す。

**【0073】**

50

ステップS11において、画素判定部152は、欠陥画素アドレスメモリ151から、画像の欠陥画素アドレスを取得する。なお、欠陥画素アドレスは、処理対象の同色の隣接4画素毎に取得するようにすることも可能である。

#### 【0074】

ステップS12において、画素判定部152は、ステップS11により取得された欠陥画素アドレスを参照し、処理対象の同色の隣接4画素内に欠陥画素がないか否かを判定する。ステップS12において、欠陥画素がないと判定された場合、処理は、ステップS13に進む。

#### 【0075】

ステップS13において、補正処理部154は、画素判定部152の制御のもと、補正することなく、メモリ部153から読み出した同色の隣接4画素の4画素データを出力データとして、例えば、フレームメモリ104に出力する。10

#### 【0076】

ステップS12において、欠陥画素があると判定された場合、処理は、ステップS14に進む。ステップS14において、画素判定部152は、ステップS11により取得された欠陥画素アドレスを参照し、同色の隣接4画素内の1画素が欠陥画素であるか否かを判定する。

#### 【0077】

ステップS14において、同色の隣接4画素内の1画素が欠陥画素であると判定された場合、処理は、ステップS15に進む。ステップS15において、補正処理部154は、画素判定部152の制御のもと、同色の隣接4画素の欠陥画素以外の3画素データに4/3を乗算したものを出力データとして、フレームメモリ104に出力する。20

#### 【0078】

例えば、図6に示される丸が示される緑画素が欠陥画素の場合は、同一緑のカラーフィルタのコーディング単位の三角、菱形、および逆三角が示される緑画素のデータが用いられる。具体的には、三角、菱形、および逆三角が示される緑画素のデータを足したものに対して、4/3が乗算され、その結果が、この同色の隣接4画素の出力データとして出力される。

#### 【0079】

ステップS14において、同色の隣接4画素内の1画素が欠陥画素ではないと判定された場合、処理は、ステップS16に進む。ステップS16において、画素判定部152は、ステップS11により取得された欠陥画素アドレスを参照し、同色の隣接4画素内の2画素が欠陥画素であるか否かを判定する。30

#### 【0080】

ステップS16において、同色の隣接4画素内の2画素が欠陥画素であると判定された場合、処理は、ステップS17に進む。ステップS17において、補正処理部154は、画素判定部152の制御のもと、同色の隣接4画素の欠陥画素以外の2画素データに2を乗算したものを出力データとして、フレームメモリ104に出力する。

#### 【0081】

例えば、図6に示される丸および三角が示される緑画素が欠陥画素の場合は、同一緑のカラーフィルタのコーディング単位の菱形および逆三角が示される緑画素のデータが用いられる。具体的には、菱形および逆三角が示される緑画素のデータを足したものに対して、2が乗算され、その結果が、この同色の隣接4画素の出力データとして出力される。40

#### 【0082】

ステップS16において、同色の隣接4画素内の2画素が欠陥画素ではないと判定された場合、すなわち、同色の隣接4画素内の3画素が欠陥画素である場合、処理は、ステップS18に進む。ステップS18において、補正処理部154は、画素判定部152の制御のもと、同色の隣接4画素の欠陥画素以外の1画素データに4を乗算したものを出力データとして、フレームメモリ104に出力する。なお、この例において、同色の隣接4画素内すべての画素が欠陥画素である場合は非常に稀であるので、そのような場合はCMOSイ50

メージセンサの出荷時の選別を行って出荷しないようにしている。

**【0083】**

例えば、図6に示される丸、三角、菱形が示される緑画素が欠陥画素の場合は、同一緑のカラーフィルタのコーディング単位の逆三角が示される緑画素のデータが用いられる。具体的には、逆三角が示される緑画素のデータに対して4が乗算され、その結果が、この同色の隣接4画素の出力データとして出力される。

**【0084】**

ステップS19において、画素判定部152は、画像における同色の隣接4画素単位の処理がすべて終了したか否かを判定する。ステップS19において、同色の隣接4画素単位の処理がまだ終了していないと判定された場合、処理は、ステップS12に戻り、次の処理対象の同色の隣接4画素単位についての処理が繰り返し行われる。ステップS19において、同色の隣接4画素単位の処理が終了したと判定された場合、この信号処理は終了する。10

**【0085】**

以上のように、同色の隣接4画素内において欠損画素がある場合、欠損画素データの補正には、欠損画素についての同一カラーフィルタのコーディング単位の画素データが用いられる。

**【0086】**

なお、機器によっては、図8の欠陥画素アドレスメモリ151の容量が十分に取ることが困難である機器もある。そのような機器に対応する処理例について、次に説明する。20

**【0087】**

<DSP回路の構成例>

図10は、白点が発生した場合の画素の補正を行う、DSP回路の第2の構成例を示すブロック図である。

**【0088】**

図10のDSP回路103は、欠陥画素アドレスメモリ151が除かれた点、画素判定部152が画素判定部171に入れ替わった点が、図8のDSP回路103と異なっている。図10のDSP回路103は、メモリ部153および補正処理部154を備える点が、図8のDSP回路103と共通している。

**【0089】**

すなわち、画素判定部171は、補正処理部154に対して、同色の隣接4画素の全画素を、メディアン処理させることで、動的に点欠陥を行わせる。なお、加算出力の場合は、全画素をメディアン処理させ、その全画素の数を乗算して出力データとすればよい。

**【0090】**

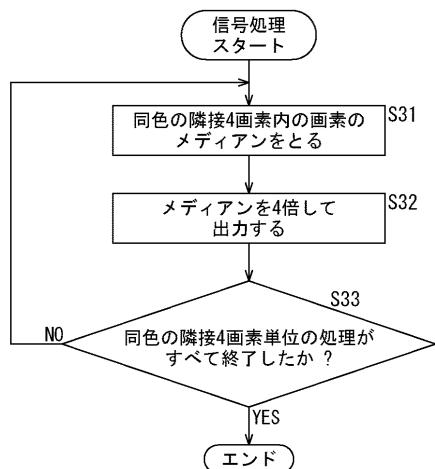

<信号処理の例>

次に、図11のフローチャートを参照して、図10のDSP回路103による信号処理の例を説明する。この信号処理は、同色の隣接4画素単位で行われる。また、例えば、この信号処理は、同色の隣接4画素の画素データを加算データとして後段に出力する処理である。なお、図6を適宜参照し、2×2画素共有単位を例に説明する。

**【0091】**

固体撮像装置1の出力回路7から出力される信号(画像)がメモリ部153に記憶される。補正処理部154は、メモリ部153から処理対象の同色の隣接4画素を読み出す。

**【0092】**

ステップS31において、補正処理部154は、画素判定部171の制御のもと、メモリ部153から読み出した同色の隣接4画素内の画素のメディアンをとる。ステップS32において、補正処理部154は、画素判定部171の制御のもと、メディアンを4倍して、出力データとして出力する。なお、加算データとして出力しない処理の場合は、ステップS32の処理は省略され、メディアンが後段に出力される。

**【0093】**

ステップS33において、画素判定部171は、画像における同色の隣接4画素単位の

10

20

30

40

50

処理がすべて終了したか否かを判定する。ステップ S 3 3において、同色の隣接 4 画素単位の処理がまだ終了していないと判定された場合、処理は、ステップ S 3 1に戻り、次の処理対象の同色の隣接 4 画素単位についての処理が繰り返し行われる。ステップ S 3 3において、同色の隣接 4 画素単位の処理が終了したと判定された場合、この信号処理は終了する。

#### 【0094】

以上のように、CFのコーディング単位である同色の隣接 4 画素内においてメティアン処理を行うことにより、白点が簡単に補正可能である。なお、HL点欠陥も補正可能である。したがって、欠陥画素アドレスメモリ 151 の容量が十分にとることが難しい機器であっても、白点補正における解像度の劣化を抑えることができる。

10

#### 【0095】

次に、高ダイナミックレンジを確保するために、蓄積時間を変えて画像処理する場合の例について説明する。

#### 【0096】

##### < DSP 回路の構成例 >

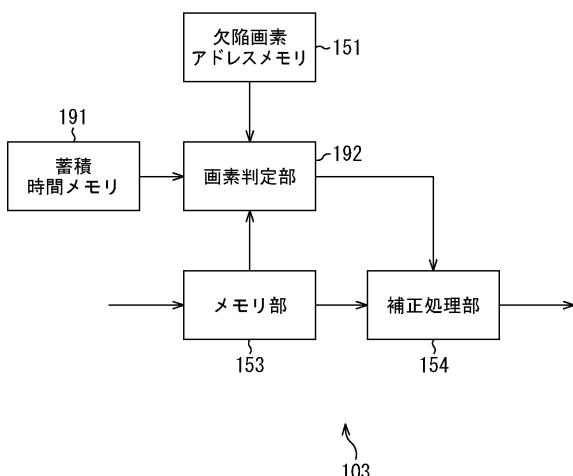

図 12 は、白点が発生した場合の画素の補正を行う、DSP 回路の第 3 の構成例を示すブロック図である。

#### 【0097】

図 12 の DSP 回路 103 は、蓄積時間メモリ 191 が追加された点、画素判定部 152 が画素判定部 192 に入れ替わった点が、図 8 の DSP 回路 103 と異なっている。図 12 の DSP 回路 103 は、欠陥画素アドレスメモリ 151、メモリ部 153、および補正処理部 154 を備える点が、図 8 の DSP 回路 103 と共通している。

20

#### 【0098】

固体撮像装置 1においては、画素毎に光(電荷)の蓄積時間を変えることで、高ダイナミックレンジが可能となる。例えば、図 12 の例の場合、2種類の蓄積時間 A および B が定められており、蓄積時間メモリ 191 は、各画素の蓄積時間(A, B どちらであるか)を記憶している。なお、蓄積時間メモリ 191 は、画素判定部 192 に内蔵されていてよい。

#### 【0099】

画素判定部 192 は、欠陥画素アドレスメモリ 151 に記憶される欠陥画素アドレスを参照し、メモリ部 153 に記憶される画像における同色の隣接 4 画素内に欠陥画素が含まれるか否かを判定する。欠陥画素が含まれる場合、画素判定部 192 は、蓄積時間メモリ 191 を参照し、欠陥画素と、同色の隣接 4 画素内において同じ蓄積時間内の画素を判定し、判定結果(蓄積時間)に応じて、補正処理部 154 の補正処理を制御する。

30

#### 【0100】

##### < 信号処理の例 >

次に、図 13 のフローチャートを参照して、図 12 の DSP 回路 103 による信号処理の例を説明する。この信号処理は、同色の隣接 4 画素単位で行われる。また、例えば、この信号処理は、同色の隣接 4 画素内の各画素データを後段に出力する処理である。なお、図 6 を適宜参照し、2×2 画素共有単位を例に説明する。

40

#### 【0101】

固体撮像装置 1 の出力回路 7 から出力される信号(画像)がメモリ部 153 に記憶される。補正処理部 154 は、メモリ部 153 から処理対象の同色の隣接 4 画素単位を読み出す。

#### 【0102】

ステップ S 5 1において、画素判定部 192 は、欠陥画素アドレスメモリ 151 から、画像の欠陥画素アドレスを取得する。なお、欠陥画素アドレスは、処理対象の同色の隣接 4 画素毎に取得するようにすることも可能である。

#### 【0103】

ステップ S 5 2において、画素判定部 192 は、ステップ S 5 1 により取得された欠陥

50

画素アドレスを参照し、処理対象の同色の隣接4画素内に欠陥画素があるかを判定する。ステップS52において、欠陥画素があると判定された場合、処理は、ステップS53に進む。

#### 【0104】

ステップS53において、補正処理部154は、画素判定部192の制御のもと、欠陥画素に対しては、同じ蓄積時間の画素のデータと置き換えて処理を行う。

#### 【0105】

すなわち、画素判定部192は、欠陥画素と、同色の隣接4画素内において同じ蓄積時間内の画素を判定し、欠陥画素に対しては、同じ蓄積時間の画像のデータに置き換えて、処理を行う。

10

#### 【0106】

図6の例において、丸および逆三角が示される緑画素が蓄積時間Aであり、三角および菱形が示される緑画素が蓄積時間Bである場合に、丸が示される緑画素が欠陥画素のとき、逆三角が示される画素のデータに置き換えて、丸が示される緑画素についての処理が行われる。例えば、図6の例において、蓄積時間の組をかえて、丸および菱形が示される緑画素が蓄積時間Aであり、三角および逆三角が示される緑画素が蓄積時間Bである場合に、丸が示される緑画素が欠陥画素のとき、菱形が示される画素のデータに置き換えて、丸の緑画素についての処理が行われる。

#### 【0107】

また、ステップS53において行われる処理の例としては、例えば、1画素出力であれば、置き換えたデータが出力データとして出力される。加算データ出力であれば、置き換えたデータが用いられて、出力データが加算されて出力される。

20

#### 【0108】

以上のように、高ダイナミックレンジを確保する場合にも、白点補正における解像度の劣化を抑えることができる。

#### 【0109】

##### <効果の説明>

なお、図6の例において、 $2 \times 2$ 画素共有単位内の $2 \times 2$ 画素のみのカラーフィルタ配置を見ると、図14の例に示される通常（すなわち、画素毎）の市松RGBペイヤ配列と同じであり、 $2 \times 2$ 画素共有単位内だけでもみると、これらの画素はメモリから別々に読み出されている。

30

#### 【0110】

しかしながら、図14のペイヤ配列においては、丸が示される緑画素が含まれる共有単位に欠陥があった場合、別々に読み出される、丸が示される緑画素の1画素離れた隣接の三角、菱形、逆三角、星が示される緑画素のどれかとデータの置き換えがなされる。あるいは、丸が示される緑画素の1画素離れた隣接の三角、菱形、逆三角、星が示される緑画素のデータの平均値で欠陥補正する必要がある。

#### 【0111】

これに対して、図6の例の場合、例えば、メモリから、同色の隣接4画素（CFのコーディング）単位を読み出しているので、その同色の隣接4画素単位での補正をすぐに行うことができる。以上のように、図14の例の場合は、図6の例の場合と信号処理が異なっている。

40

#### 【0112】

以上のように、画素共有単位内でフローティングディフュージョン部のリークなどで白点が発生しても、異画素共有単位の同じ色の画素で白色補正が可能になる。空間的に近いので、空間的に遠い場合よりも、画像劣化を抑えることができる。

#### 【0113】

なお、上記説明においては、画素共有単位が $2 \times 2$ 画素の場合について説明したが、画素共有単位は、 $2 \times 2$ 画素だけに限らず、 $2 \times 2$ 画素以外の共有単位であってもよい。以下、他の画素共有単位について説明していく。

50

## 【0114】

<2. 第2の実施の形態(2×4画素共有の例)>

## &lt;画素共有単位の構成例&gt;

まず、図15および図16を参照して、2×4画素共有単位の回路構成例について説明する。図15は、2×4画素共有単位の回路構成の一例を示す回路図である。図16は、2×4画素共有単位の回路構成の一例を示す平面図である。なお、図3および図4を参照して説明した2×2画素共有単位の例と数が異なるだけであり、トランジスタなどの基本的な機能は同じである。

## 【0115】

図15および図16で示されるように、2×4画素共有単位は、8つの光電変換素子、

10

例えば、フォトダイオードP D 0乃至P D 7、およびそれらに対応する8つの転送トランジスタT R 0乃至T R 7、並びに、リセットトランジスタR s t、増幅トランジスタA m p、および選択トランジスタS e lの3つのトランジスタを有する構成となっている。

## 【0116】

フォトダイオードP D 0乃至P D 7は、アノード電極が負側電源(例えば、グランド)に接続されており、受光した光をその光量に応じた電荷量の光電荷(ここでは、光電子)に光電変換する。フォトダイオードP D 0乃至P D 7のカソード電極は、対応する各転送トランジスタT R 0乃至T R 7を介して増幅トランジスタA m pのゲート電極と電気的に接続されている。増幅トランジスタA m pのゲート電極と4つの転送トランジスタT R 0乃至T R 3とが電気的に繋がったノードをフローティングディフュージョンF D 0と称する。増幅トランジスタA m pのゲート電極と4つの転送トランジスタT R 4乃至T R 7とが電気的に繋がったノードをフローティングディフュージョンF D 1と称する。

20

## 【0117】

転送トランジスタT R 0乃至T R 3は、対応するフォトダイオードP D 0乃至P D 3のカソード電極とフローティングディフュージョンF D 0との間に接続されている。また、転送トランジスタT R 4乃至T R 7は、対応するフォトダイオードP D 4乃至P D 7のカソード電極とフローティングディフュージョンF D 1との間に接続されている。

## 【0118】

転送トランジスタT R 0乃至T R 7のゲート電極には、高レベル(例えば、V D D レベル)がアクティブ(以下、「H i g h アクティブ」と記述する)の転送パルス T R Fが、図示せぬ転送線を介して与えられる。転送パルス T R Fが与えられることで、転送トランジスタT R 0乃至T R 3はオン状態となってフォトダイオードP D 0乃至P D 3で光電変換された光電荷をフローティングディフュージョンF D 0に転送する。同様に、転送パルス T R Fが与えられることで、転送トランジスタT R 4乃至T R 7はオン状態となってフォトダイオードP D 4乃至P D 7で光電変換された光電荷をフローティングディフュージョンF D 1に転送する。

30

## 【0119】

リセットトランジスタR s tは、ドレイン電極が画素電源V D Dに、ソース電極がフローティングディフュージョンF D 0にそれぞれ接続されている。リセットトランジスタR s tのゲート電極には、フォトダイオードP D 0乃至P D 3からフローティングディフュージョンF D 0およびフォトダイオードP D 4乃至P D 7からフローティングディフュージョンF D 1への信号電荷の転送に先立って、H i g h アクティブのリセットパルス R S Tが図示せぬリセット線を介して与えられる。リセットパルス R S Tが与えられることで、リセットトランジスタR s tはオン状態となり、フローティングディフュージョンF D 0およびF D 1の電荷を画素電源V D Dに捨てるによってフローティングディフュージョンF D 0およびF D 1をリセットする。

40

## 【0120】

増幅トランジスタA m pは、ゲート電極がフローティングディフュージョンF D 0およびF D 1に、ドレイン電極が画素電源V D Dにそれぞれ接続されている。そして、増幅トランジスタA m pは、リセットトランジスタR s tによってリセットした後のフローティ

50

ングディフュージョン F D 0 および F D 1 の電位をリセット信号(リセットレベル) V r e s e t として出力する。増幅トランジスタ A m p はさらに、転送トランジスタ T R 0 乃至 T R 3 によって信号電荷を転送した後のフローティングディフュージョン F D 0 の電位と、転送トランジスタ T R 4 乃至 T R 7 によって信号電荷を転送した後のフローティングディフュージョン F D 1 の電位とを光蓄積信号(信号レベル) V s i g として出力する。

#### 【0121】

選択トランジスタ S e 1 は、例えば、ドレイン電極が増幅トランジスタ A m p のソース電極に、ソース電極が垂直信号線 L 1 にそれぞれ接続されている。選択トランジスタ S e 1 のゲート電極には、H i g h アクティブの選択パルス S E L が図示せぬ選択線を介して与えられる。選択パルス S E L が与えられることで、選択トランジスタ S e 1 はオン状態となって単位画素を選択状態とし、増幅トランジスタ A m p から出力される信号を垂直信号線 L 1 に中継する。

#### 【0122】

なお、選択トランジスタ S e 1 については、画素電源 V D D と増幅トランジスタ A m p のドレインとの間に接続した回路構成を探ることも可能である。

#### 【0123】

##### <画素共有単位とCFコーディング単位との関係>

図 17 は、 $2 \times 4$  画素共有単位とカラーフィルタ(CF)のコーディングの単位との関係を示す図である。図 17 の例においては、太線に示されるように、 $2 \times 4$  画素共有の例が示されており、また、実線に示されるように、4 画素毎に同じカラーフィルタをRGB市松コーディング(ペイヤ配列)した例が示されている。

#### 【0124】

すなわち、図 17 の例においては、画素共有単位の $2 \times 4$  画素における上半分の4 画素と下半分の4 画素は、それぞれ、同じカラーフィルタでコーディングされている。

#### 【0125】

このため、中央の黒い $2 \times 4$  画素部分に、フローティングディフュージョンのリークなどによる白点が発生した場合、丸印が付された緑画素の補正は、図中 1 乃至 4 の数字が示される最周辺の位置の緑画素を使用して行うことが考えられる。すなわち、図 17 の例の場合、単位画素で、2 画素空間的に離れたデータで補正することになる。

#### 【0126】

##### <本技術の画素共有単位とCFコーディング単位との関係>

図 18 は、本技術を適用した画素共有単位とカラーフィルタ(CF)のコーディングの単位との関係を示す図である。図 18 の例においては、太線に示されるように、 $2 \times 4$  画素共有の例が示されており、また、実線に示されるように、4 画素毎に同じカラーフィルタをRGB市松コーディング(ペイヤ配列)した例が示されている。

#### 【0127】

図 18 の例において、画素共有単位の $2 \times 4$  画素の上 2 つの画素と下 2 つの画素は、図 18 の太線に示されるように、それぞれ異なるカラーフィルタでコーディングされている。画素共有単位の $2 \times 4$  画素の中央 4 つの画素は、図 18 の太線に示されるように、2 画素ずつ同じカラーフィルタでコーディングされている。換言するに、同一カラーフィルタのコーディング単位の 4 画素は、互いに画素共有のない画素を含むように構成されている。すなわち、同一カラーフィルタのコーディング単位の 4 画素は、異なる画素共有単位の画素を、その構成の少なくとも半分含むように構成されている。

#### 【0128】

なお、図 18 のカラーフィルタ 35 は、図 17 のカラーフィルタを、例えば、上に 1 画素、かつ、右に 1 画素移動させて形成されたものである。

#### 【0129】

このようにすることで、中央の黒い画素部分に、フローティングディフュージョンのリークなどにより白点が発生した場合、黒い画素部分のうち、丸が示される緑画素の補正は、同一緑のカラーフィルタのコーディング単位の三角、菱形、および逆三角が示される緑

10

20

30

40

50

画素の少なくとも 1 画素を使用して行われる。

**【 0 1 3 0 】**

すなわち、図 18 の例の場合、隣の画素なので、空間的に近いデータで補正可能であり、図 17 の例の場合よりも解像度劣化を抑えることができる。

**【 0 1 3 1 】**

なお、白点が発生した場合の画素の補正を行う電子機器の構成は、図 7 を参照して上述した図 6 の例の場合の電子機器と基本的に同じであるので、その説明は省略される。また、白点が発生した場合の画素の補正を行う信号処理の例も、図 9、図 11、図 13 を参照して上述した信号処理と基本的に同様であるので、その説明は省略される。

**【 0 1 3 2 】**

すなわち、図 9 および図 13 の例の信号処理は、画素共有単位の  $2 \times 4$  画素の上 2 つの画素および下 2 つの画素については、図 6 の例の場合と基本的に同様に行われる。一方、画素共有単位の  $2 \times 4$  画素の中央 4 つの画素については、それぞれ 2 画素が同じ画素共有単位に含まれているので、後述する図 19 の場合と同様に行うことができる。

**【 0 1 3 3 】**

なお、 $2 \times 4$  画素共有単位においては、CF コーディング単位との関係が次に示される場合もあり得る。

**【 0 1 3 4 】**

< 本技術の画素共有単位と CF コーディング単位との関係 >

図 19 は、本技術を適用した画素共有単位とカラーフィルタ(CF)のコーディングの単位の関係を示す図である。図 19 の例においては、太線に示されるように、 $2 \times 4$  画素共有の例が示されており、また、実線に示されるように、4 画素毎に同じカラーフィルタを RGB 市松コーディング(ペイヤ配列)した例が示されている。

**【 0 1 3 5 】**

図 19 の例において、画素共有単位の  $2 \times 4$  画素の各画素は、図 18 の画素共有単位の中央 4 つの画素の場合と同様に、図 19 の太線に示されるように、2 画素ずつ、同じカラーフィルタでコーディングされている。換言するに、同一カラーフィルタのコーディング単位の 4 画素は、互いに画素共有のない画素を含むように構成されている。すなわち、同一カラーフィルタのコーディング単位の 4 画素は、異なる画素共有単位の画素を、その構成の少なくとも半分含むように構成されている。

**【 0 1 3 6 】**

なお、図 19 のカラーフィルタ 35 は、図 17 のカラーフィルタを、例えば、右に 1 画素移動させて形成されたものである。

**【 0 1 3 7 】**

このようにすることで、中央の黒い画素部分に、フローティングディフュージョンのリーケなどにより白点が発生した場合、黒い画素部分のうち、三角と丸が示される緑画素の補正是、同一緑のカラーフィルタのコーディング単位の菱形および逆三角が示される緑画素を使用して行われる。

**【 0 1 3 8 】**

すなわち、図 19 の例の場合、隣の画素なので、空間的に近いデータで補正可能であり、図 17 の例の場合よりも解像度劣化を抑えることができる。

**【 0 1 3 9 】**

なお、白点が発生した場合の画素の補正を行う電子機器の構成は、図 7 を参照して上述した図 6 の例の場合の電子機器と基本的に同じであるので、その説明は省略される。また、白点が発生した場合の画素の補正を行う信号処理の例も、図 9、図 11、図 13 を参照して上述した信号処理と基本的に同様であるので、その説明は省略される。

**【 0 1 4 0 】**

すなわち、画素共有単位の  $2 \times 4$  画素の画素については、それぞれ 2 画素（例えば、図 19 の三角と丸が示される画素）が同じ画素共有単位に含まれているので、特に、図 9 の例であれば、ステップ S 17 の処理のように、画素共有単位内に 2 画素が欠陥画素である

10

20

30

40

50

場合の信号処理が行われる。

#### 【0141】

また、図13の例であれば、丸が示される画素と逆三角が示される画素が蓄積時間Aであり、三角が示される画素と菱形が示される画素が蓄積時間Bの2種類であるとすると、丸が示される欠陥画素は、逆三角が示される画素のデータと置き換えることができる。また、三角が示される欠陥画素は、菱形が示される画素のデータと置き換えることができる。

#### 【0142】

以上のように、画素共有単位が $2 \times 4$ 画素の場合にも、白点補正における解像度の劣化を抑えることができる。

10

#### 【0143】

<3. 第3の実施の形態(1×4画素共有の例)>

##### <画素共有単位の構成例>

まず、図20および図21を参照して、 $1 \times 4$ 画素共有単位の回路構成例について説明する。図20は、 $1 \times 4$ 画素共有単位の回路構成の一例を示す回路図である。図21は、 $1 \times 4$ 画素共有単位の回路構成の一例を示す平面図である。なお、図3および図4を参照して説明した $2 \times 2$ 画素共有単位の例と数が異なるだけであり、トランジスタなどの基本的な機能は同じである。

#### 【0144】

図20および図21で示されるように、 $1 \times 4$ 画素共有単位は、4つの光電変換素子、例えば、フォトダイオードPD0乃至PD3、およびそれらに対応する4つの転送トランジスタTR0乃至TR3、並びに、リセットトランジスタRst、増幅トランジスタAmp、および選択トランジスタSelの3つのトランジスタを有する構成となっている。

20

#### 【0145】

フォトダイオードPD0乃至PD3は、アノード電極が負側電源(例えば、グランド)に接続されており、受光した光をその光量に応じた電荷量の光電荷(ここでは、光電子)に光電変換する。フォトダイオードPD0乃至PD3のカソード電極は、対応する各転送トランジスタTR0乃至TR3を介して増幅トランジスタAmpのゲート電極と電気的に接続されている。増幅トランジスタAmpのゲート電極と2つの転送トランジスタTR0およびTR1とが電気的に繋がったノードをフローティングディフュージョンFD0と称する。増幅トランジスタAmpのゲート電極と2つの転送トランジスタTR2およびTR3とが電気的に繋がったノードをフローティングディフュージョンFD1と称する。

30

#### 【0146】

転送トランジスタTR0乃至TR3は、対応するフォトダイオードPD0乃至PD3のカソード電極とフローティングディフュージョンFD0またはFD1との間に接続されている。転送トランジスタTR0乃至TR3のゲート電極には、高レベル(例えば、VDDレベル)がアクティブ(以下、「Highアクティブ」と記述する)の転送パルスTRFが、図示せぬ転送線を介して与えられる。転送パルスTRFが与えられることで、転送トランジスタTR0乃至TR3はオン状態となってフォトダイオードPD0乃至PD3で光電変換された光電荷をフローティングディフュージョンFD0またはFD1に転送する。

40

#### 【0147】

リセットトランジスタRstは、ドレイン電極が画素電源VDDに、ソース電極がフローティングディフュージョンFD0およびFD1にそれぞれ接続されている。リセットトランジスタRstのゲート電極には、フォトダイオードPD0およびPD1からフローティングディフュージョンFD0への、フォトダイオードPD2およびPD3からフローティングディフュージョンFD1への信号電荷の転送に先立って、HighアクティブのリセットパルスRSTが図示せぬリセット線を介して与えられる。リセットパルスRSTが与えられることで、リセットトランジスタRstはオン状態となり、フローティングディフュージョンFD0およびFD1の電荷を画素電源VDDに捨てることによってフロ

50

ーティングディフュージョン F D 0 および F D 1 をリセットする。

【 0 1 4 8 】

増幅トランジスタ A m p は、ゲート電極がフローティングディフュージョン F D 0 および F D 1 に、ドレイン電極が画素電源 V D D にそれぞれ接続されている。そして、増幅トランジスタ A m p は、リセットトランジスタ R s t によってリセットした後のフローティングディフュージョン F D 0 および F D 1 の電位をリセット信号（リセットレベル） V r e s e t として出力する。増幅トランジスタ A m p はさらに、転送トランジスタ T R 0 および T R 1 によって信号電荷を転送した後のフローティングディフュージョン F D 0 および 転送トランジスタ T R 2 および T R 3 によって信号電荷を転送した後のフローティングディフュージョン F D 1 の電位を光蓄積信号（信号レベル） V s i g として出力する。 10

【 0 1 4 9 】

選択トランジスタ S e 1 は、例えば、ドレイン電極が増幅トランジスタ A m p のソース電極に、ソース電極が垂直信号線 L 1 にそれぞれ接続されている。選択トランジスタ S e 1 のゲート電極には、H i g h アクティブの選択パルス S E L が図示せぬ選択線を介して与えられる。選択パルス S E L が与えられることで、選択トランジスタ S e 1 はオン状態となって単位画素を選択状態とし、増幅トランジスタ A m p から出力される信号を垂直信号線 L 1 に中継する。

【 0 1 5 0 】

なお、選択トランジスタ S e 1 については、画素電源 V D D と増幅トランジスタ A m p のドレインとの間に接続した回路構成を探ることも可能である。 20

【 0 1 5 1 】

<本技術の画素共有単位とCFコーディング単位との関係>

図 2 2 は、本技術を適用した画素共有単位とカラーフィルタ(CF)のコーディングの単位との関係を示す図である。図 2 2 の例においては、太線に示されるように、 $1 \times 4$  画素共有の例が示されており、また、実線に示されるように、4 画素毎に同じカラーフィルタをRGB市松コーディング(ペイヤ配列)した例が示されている。

【 0 1 5 2 】

図 2 2 の例において、画素共有単位の $1 \times 4$  画素の上1つの画素と下1つの画素は、図 2 2 の太線に示されるように、異なるカラーフィルタでコーディングされている。画素共有単位の $1 \times 4$  画素の中央2つの画素は、図 2 2 の太線に示されるように、同じカラーフィルタでコーディングされている。換言するに、同一カラーフィルタのコーディング単位の4 画素は、互いに画素共有のない画素を含むように構成されている。すなわち、同一カラーフィルタのコーディング単位の4 画素は、異なる画素共有単位の画素を、その構成の少なくとも半分含むように構成されている。 30

【 0 1 5 3 】

このようにすることで、中央の黒い画素部分に、フローティングディフュージョンのリーケなどにより白点が発生した場合、黒い画素部分のうち、逆三角が示される赤画素の補正是、同一赤のカラーフィルタのコーディング単位の三角、菱形、または丸が示される赤画素を使用して行われる。

【 0 1 5 4 】

すなわち、補正に用いられる画素は、隣の画素なので、空間的に近いデータで補正可能であり、よって解像度劣化を抑えることができる。 40

【 0 1 5 5 】

なお、 $1 \times 4$  画素共有単位においては、CFコーディング単位との関係が次に示される場合もあり得る。

【 0 1 5 6 】

<本技術の画素共有単位とCFコーディング単位との関係>

図 2 3 は、本技術を適用した画素共有単位とカラーフィルタ(CF)のコーディングの単位との関係を示す図である。図 2 3 の例においては、太線に示されるように、 $1 \times 4$  画素共有の例が示されており、また、実線に示されるように、4 画素毎に同じカラーフィルタを 50

RGB市松コーディング(ペイヤ配列)した例が示されている。

**【0157】**

図23の例において、画素共有単位の $1 \times 4$ 画素の各画素は、図22の画素共有単位の中央2つの画素の場合と同様に、図23の太線に示されるように、2画素ずつ、同じカラーフィルタでコーディングされている。換言するに、同一カラーフィルタのコーディング単位の4画素は、互いに画素共有のない画素を含むように構成されている。すなわち、同一カラーフィルタのコーディング単位の4画素は、異なる画素共有単位の画素を、その構成の少なくとも半分含むように構成されている。

**【0158】**

このようにすることで、中央の黒い画素部分に、フローティングディフュージョンのリーケなどにより白点が発生した場合、黒い画素部分のうち、菱形および逆三角が示される緑画素の補正は、同一緑のカラーフィルタのコーディング単位の三角と丸が示される緑画素を使用して行われる。

**【0159】**

すなわち、補正に用いられる画素は、隣の画素なので、空間的に近いデータで補正可能であり、よって解像度劣化を抑えることができる。

**【0160】**

以上のように、画素共有単位が $1 \times 4$ 画素の場合にも、白点補正における解像度の劣化を抑えることができる。

**【0161】**

なお、上記説明においては、画素共有単位が $2 \times 2$ 画素、 $2 \times 4$ 画素、 $1 \times 4$ 画素の場合について説明したが、その他の画素共有単位でも同様に行うことができる。

**【0162】**

また、上記説明においては、RGB市松カラーコーディングについて説明してきたが、本技術は、4画素同じカラーコーディングであれば、Wを入れたRGBWにも適用することができる。また、本技術は、RGBW以外の多色コーディングにも適用することができる。

**【0163】**

さらに、上記説明においては、裏面照射型の固体撮像装置について説明したが、本技術は、表面照射型の固体撮像装置にも適用することができる。

**【0164】**

<4. 第4の実施の形態>

<固体撮像装置の断面例>

図24は、本技術の固体撮像装置の画素領域および周辺回路部の構造の一例を示す断面図を示す。図24の例においては、表面照射型の固体撮像装置の例が示されている。

**【0165】**

図24の例の固体撮像装置201は、入射した光を光電変換する画素領域210と、画素を駆動して信号を読み出し、これに対して信号処理を施して出力する周辺回路部220とが同一チップ(基板)に集積された構成となっている。また、画素領域210を構成するトランジスタと周辺回路部220を構成するトランジスタとは、その配線の一部を共通にしている。画素領域210には、図1の画素領域3が適用される。

**【0166】**

画素領域210は、数百 $\mu m$ 程度の厚さを持つN型シリコン基板211の表面側に形成されたフォトダイオード212を有するとともに、その上方に配線層213およびパッケージーション膜214を介してカラーフィルタ215およびOCL(On Chip Lens)216が配された構造となっている。カラーフィルタ215は、色の信号を得るために設けられている。なお、カラーフィルタ215には、図2のカラーフィルタ35が適用される。

**【0167】**

この画素領域210において、フォトダイオード212とカラーフィルタ215との間には、トランジスタや配線が存在するので、画素領域210への入射光に対するフォトダイオード212への入射光の比、即ち開口率を上げるために、入射光をOCL216よって

10

20

30

40

50

配線の間を通してフォトダイオード 212 へ集光するようにしている。

#### 【0168】

このような固体撮像装置 201 は、固体撮像装置 1 と同様に、画素共有単位とカラーフィルタ 215 のコーディングの単位とについて上述した関係性を有する。これにより、空間的に近いデータで白色補正を行うことができるので、解像度劣化を抑えることができる。

#### 【0169】

なお、本技術は、例えば、イメージセンサのような固体撮像装置への適用に限られるものではない。即ち、本技術は、デジタルスチルカメラやビデオカメラ等の撮像装置や、撮像機能を有する携帯端末装置や、画像読取部に固体撮像装置を用いる複写機など、画像取込部（光電変換部）に固体撮像装置を用いる電子機器全般に対して適用可能である。

#### 【0170】

<5. 第5の実施の形態>

<コンピュータの構成例>

上述した一連の処理は、ハードウェアにより実行することもできるし、ソフトウェアにより実行することもできる。一連の処理をソフトウェアにより実行する場合には、そのソフトウェアを構成するプログラムが、コンピュータにインストールされる。ここで、コンピュータには、専用のハードウェアに組み込まれているコンピュータや、各種のプログラムをインストールすることで、各種の機能を実行することが可能な、例えば汎用のパーソナルコンピュータなどが含まれる。

10

#### 【0171】

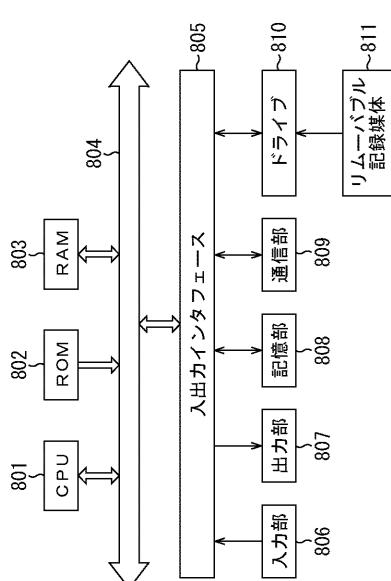

図 25 は、上述した一連の処理をプログラムにより実行するコンピュータのハードウェアの構成例を示すブロック図である。

#### 【0172】

コンピュータ 800において、CPU (Central Processing Unit) 801, ROM (Read Only Memory) 802, RAM (Random Access Memory) 803 は、バス 804 により相互に接続されている。

20

#### 【0173】

バス 804 には、さらに、入出力インターフェース 805 が接続されている。入出力インターフェース 805 には、入力部 806、出力部 807、記憶部 808、通信部 809、及びドライブ 810 が接続されている。

30

#### 【0174】

入力部 806 は、キーボード、マウス、マイクロホンなどよりなる。出力部 807 は、ディスプレイ、スピーカなどよりなる。記憶部 808 は、ハードディスクや不揮発性のメモリなどよりなる。通信部 809 は、ネットワークインターフェースなどよりなる。ドライブ 810 は、磁気ディスク、光ディスク、光磁気ディスク、又は半導体メモリなどのリムーバブル記録媒体 811 を駆動する。

#### 【0175】

以上のように構成されるコンピュータでは、CPU 801 が、例えば、記憶部 808 に記憶されているプログラムを、入出力インターフェース 805 及びバス 804 を介して、RAM 803 にロードして実行することにより、上述した一連の処理が行われる。

40

#### 【0176】

コンピュータ 800 (CPU 801) が実行するプログラムは、例えば、パッケージメディア等としてのリムーバブル記録媒体 811 に記録して提供することができる。また、プログラムは、ローカルエリアネットワーク、インターネット、デジタル衛星放送といった、有線または無線の伝送媒体を介して提供することができる。

#### 【0177】

コンピュータでは、プログラムは、リムーバブル記録媒体 811 をドライブ 810 に装着することにより、入出力インターフェース 805 を介して、記憶部 808 にインストールすることができる。また、プログラムは、有線または無線の伝送媒体を介して、通信部 8

50

09で受信し、記憶部808にインストールすることができる。その他、プログラムは、ROM802や記憶部808に、あらかじめインストールしておくことができる。

#### 【0178】

なお、コンピュータが実行するプログラムは、本明細書で説明する順序に沿って時系列に処理が行われるプログラムであっても良いし、並列に、あるいは呼び出しが行われたとき等の必要なタイミングで処理が行われるプログラムであっても良い。

#### 【0179】

また、本明細書において、記録媒体に記録されるプログラムを記述するステップは、記載された順序に沿って時系列的に行われる処理はもちろん、必ずしも時系列的に処理されなくとも、並列的あるいは個別に実行される処理をも含むものである。

10

#### 【0180】

また、本明細書において、システムとは、複数のデバイス（装置）により構成される装置全体を表すものである。

#### 【0181】

さらに、本開示における実施の形態は、上述した実施の形態に限定されるものではなく、本開示の要旨を逸脱しない範囲において種々の変更が可能である。

#### 【0182】

また、上述のフローチャートで説明した各ステップは、1つの装置で実行する他、複数の装置で分担して実行することができる。

#### 【0183】

さらに、1つのステップに複数の処理が含まれる場合には、その1つのステップに含まれる複数の処理は、1つの装置で実行する他、複数の装置で分担して実行することができる。

20

#### 【0184】

また、以上において、1つの装置（または処理部）として説明した構成を分割し、複数の装置（または処理部）として構成するようにしてもよい。逆に、以上において複数の装置（または処理部）として説明した構成をまとめて1つの装置（または処理部）として構成されるようにしてもよい。また、各装置（または各処理部）の構成に上述した以外の構成を付加するようにしてもちろんよい。さらに、システム全体としての構成や動作が実質的に同じであれば、ある装置（または処理部）の構成の一部を他の装置（または他の処理部）の構成に含めるようにしてもよい。つまり、本技術は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

30

#### 【0185】

以上、添付図面を参照しながら本開示の好適な実施形態について詳細に説明したが、開示はかかる例に限定されない。本開示の属する技術の分野における通常の知識を有するのであれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例また修正例に想到し得ることは明らかであり、これらについても、当然に本開示の技術的範囲に属するものと了解される。

#### 【0186】

なお、本技術は以下のよう構成も取ることができる。

40

(1) 同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、

前記複数画素群がベイヤ配列されてなるカラーフィルタと

を備える固体撮像装置。

(2) 前記複数画素群は、互いに画素共有のない画素で構成されている

前記(1)に記載の固体撮像装置。

(3) 前記画素共有の単位は、 $2 \times 2$ 画素である

前記(1)または(2)に記載の固体撮像装置。

(4) 前記複数画素群は、互いに画素共有のない画素を、その構成の少なくとも半分含むように構成されている

50

前記(1)に記載の固体撮像装置。

(5) 前記画素共有の単位は、 $2 \times 4$ 画素である

前記(1)または(4)に記載の固体撮像装置。

(6) 前記画素共有の単位は、 $1 \times 4$ 画素である

前記(1)または(4)に記載の固体撮像装置。

(7) 前記画素共有内で発生した欠陥画素は、前記複数画素群内の画素を用いて補正される

前記(1)乃至(6)のいずれかに記載の固体撮像装置。

(8) 前記複数画素群は、4画素で構成される

前記(1)乃至(7)のいずれかに記載の固体撮像装置。

10

(9) 前記色コーディングは、原色市松のコーディングである

前記(1)乃至(8)のいずれかに記載の固体撮像装置。

(10) 前記色コーディングは、WRGBのコーディングである

前記(1)乃至(8)のいずれかに記載の固体撮像装置。

(11) 同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとを備える固体撮像装置から出力される出力信号において、前記画素共有内で発生した欠陥画素を、前記複数画素群内の画素を用いて補正する補正処理部を

備える信号処理装置。

(12) 前記補正処理部は、前記画素共有内で発生した欠陥画素を、前記画素共有内で発生した欠陥画素の個数に応じて、前記複数画素群内の画素を用いて補正する

20

前記(11)に記載の信号処理装置。

(13) 前記補正処理部は、前記画素共有内で発生した欠陥画素を、前記複数画素群内のすべての画素を用いて補正する

前記(11)に記載の信号処理装置。

(14) 前記補正処理部は、前記画素共有内で発生した欠陥画素を、前記画素共有内で発生した欠陥画素の蓄積時間に応じて、前記複数画素群内のデータを用いて補正する

前記(11)に記載の信号処理装置。

(15) 同色コーディングで、かつ、互いに画素共有のない画素を含むように構成された複数画素群と、前記複数画素群がベイヤ配列されてなるカラーフィルタとを備える固体撮像装置と、

30

入射光を前記固体撮像装置に入射する光学系と、

前記固体撮像装置から出力される出力信号を処理する信号処理回路と

を有する電子機器。

#### 【符号の説明】

##### 【0187】

1 固体撮像装置， 2 画素， 3 画素領域， 100 カメラ装置， 101

光学部， 103 DSP回路， 104 フレームメモリ， 151 欠陥画素アド

レスメモリ， 152 画素判定部， 153 メモリ部， 154 補正処理部， 1

71 画素判定部， 191 蓄積時間メモリ， 192 画素判定部， 201 固体

撮像装置

40

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

35

35

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

35

35

【図24】

図24

【図25】

図25

---

フロントページの続き

(56)参考文献 特開2010-153511(JP,A)

特開2011-049446(JP,A)

特開2010-010760(JP,A)

特開2012-044452(JP,A)

国際公開第2013/046827(WO,A1)

特開2010-239337(JP,A)

特開2007-124056(JP,A)

米国特許出願公開第2010/0148037(US,A1)

特開2011-004370(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| H 04 N | 9 / 07  |

| G 02 B | 5 / 20  |

| H 01 L | 27 / 14 |

| H 04 N | 5 / 367 |