(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4310864号

(P4310864)

(45) 発行日 平成21年8月12日(2009.8.12)

(24) 登録日 平成21年5月22日(2009.5.22)

(51) Int.Cl.

H03D 3/00 (2006.01)

F 1

H03D 3/00

A

請求項の数 1 (全 14 頁)

(21) 出願番号 特願平11-258587

(22) 出願日 平成11年9月13日(1999.9.13)

(65) 公開番号 特開2001-85950(P2001-85950A)

(43) 公開日 平成13年3月30日(2001.3.30)

審査請求日 平成18年9月12日(2006.9.12)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 100097445

弁理士 岩橋 文雄

(74) 代理人 100109667

弁理士 内藤 浩樹

(74) 代理人 100109151

弁理士 永野 大介

(72) 発明者 竹谷 信夫

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

(72) 発明者 毛利部 宏

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

最終頁に続く

(54) 【発明の名称】アーカタンジェント回路

## (57) 【特許請求の範囲】

## 【請求項 1】

直交信号のY軸信号を整流する第1の全波整流回路と、

直交信号のX軸信号を整流する第2の全波整流回路と、

前記第1の全波整流回路の出力を切り替える第1の切り替え回路と、

前記第2の全波整流回路の出力を切り替える第2の切り替え回路と、

前記第1の切り替え回路の出力と前記第2の切り替え回路の出力を比較して比較制御信号

を出力する比較回路と、

タイミングパルス制御信号を発生させるタイミング発生回路と、

前記比較回路からの比較制御信号に基づいて前記第1の切り替え回路の出力と前記第2の

切り替え回路の出力と前記タイミングパルス制御信号とでCORDICアルゴリズムを用

いし直交信号の位相成分を出力するCORDICアルゴリズム回路と、

タイミングパルス制御信号に基づいて前記CORDICアルゴリズム回路の出力をホール

ドさせて第1の切り替え回路へ出力する第1のロードホールド回路と、

タイミングパルス制御信号に基づいて前記CORDICアルゴリズム回路の出力をホール

ドさせて第2の切り替え回路へ出力する第2のロードホールド回路と、

前記Y軸信号と前記X軸信号を入力して前記直交信号の位相が4象限のうちどこに存在す

るかを検出する象限検出回路と、

タイミングパルス制御信号に基づいて前記象限検出回路の出力をホールドさせる第3のロ

ードホールド回路と、

10

20

前記タイミングパルス制御信号に基づいて固定データを切り替えて出力する固定データ切り替え回路と、

前記比較回路からの比較制御信号に基づいて前記固定データ切り替え回路の出力の極性を切り替える極性切り替え回路と、

前記タイミングパルス制御信号に基づいて前記極性切り替え回路の出力を累積加算する累積加算回路と、

累積加算回路の出力と前記第3のロードホールド回路の出力を加算する加算回路と、

前記タイミングパルス制御信号に基づいて前記加算回路の出力をホールドさせて出力する第4のロードホールド回路とを備えたことを特徴とするアーカンジエント回路。

#### 【発明の詳細な説明】

10

#### 【0001】

#### 【発明の属する技術分野】

本発明は、直交信号のアーカンジエントを計算する際に、演算回数が少なくかつ演算誤差を少なくできることを提供するためのアーカンジエント回路に関するものである。

#### 【0002】

#### 【従来の技術】

近年、アーカンジエント回路は、デジタルFM復調回路において、なくてはならない回路技術として重要視されている。

#### 【0003】

以下、図面を参照しながら、上述した従来のアーカンジエント回路の一例について説明を行う。

20

#### 【0004】

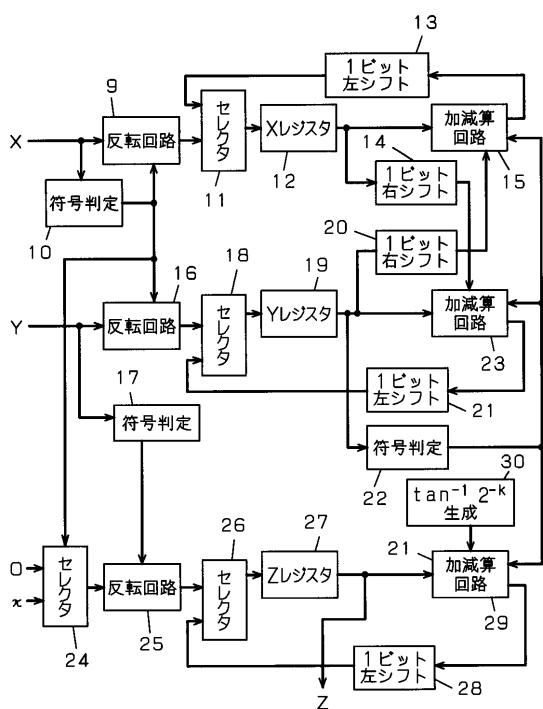

図4は、特開平6-77734号公報で提案されているアーカンジエント回路のブロック構成図を示すものであり、これを以下に説明する。

#### 【0005】

アーカンジエント回路は図4に示すように構成されており、CORDICとして知られる関数計算法を回路化したものである。信号Xは符号判定回路10および反転回路9に供給し、同様に、信号Yは反転回路16および符号判定回路17に供給し、符号判定回路10による信号Xの符号判定出力にもとづいて反転回路9において信号Xを選択的に正転、または反転すなわち(-1)倍し、符号判定回路10による信号Xの符号判定出力にもとづいて反転回路16において信号Yを選択的に正転、または反転すなわち(-1)倍する。定数値0および定数値 $\pi/4$ をセレクタ24に供給し、符号判定回路10による信号Xの符号判定出力にもとづいてセレクタ24において一方の入力を選択し、セレクタ24による選択出力は反転回路25に供給し、符号判定回路17による信号Yの符号判定出力にもとづいてセレクタ24からの出力を反転回路25において選択的に正転、または反転すなわち(-1)倍する。反転回路9からの出力および後記の1ビット左シフト回路13からの出力とはセレクタ11に供給し、セレクタ11の出力はXレジスタ12に供給してロードし、Xレジスタ12の出力は1ビット右シフト回路14および加減算回路15に供給し、加減算回路15において後記の符号判定回路22の出力にもとづいてXレジスタ12からの出力と後記の1ビット右シフト回路20からの出力と加算もしくは減算を行う。加減算回路15からの出力は1ビット左シフト回路13に供給して、1ビット左シフトする。

30

#### 【0006】

反転回路16からの出力および後記の1ビット左シフト回路21からの出力とはセレクタ18に供給し、セレクタ18の出力はYレジスタ19に供給してロードし、Yレジスタ19の出力は、1ビット右シフト回路20、符号判定回路22および加減算回路23に供給し、加減算回路23において符号判定回路22の出力にもとづいてYレジスタ19からの出力と1ビット右シフト回路14からの出力と加算もしくは減算を行う。

#### 【0007】

加減算回路23からの出力は1ビット左シフト回路21に供給する。反転回路25からの出力と後記の1ビット左シフト回路28からの出力とはセレクタ26に供給し、セレクタ

40

50

26からの出力はZレジスタ27に供給してロードし、Zレジスタ27の出力は加減算回路29に供給し、Zレジスタ21からの出力とアークタンジェント2の-k乗( $k = 0, 1, 2 \dots$ )の定数値生成回路30の出力とを加減算回路29において、符号判定回路22の出力にもとづいて加算もしくは減算を行う。加減算回路29からの出力は1ビット左シフト回路28に供給する。

#### 【0008】

Zレジスタ27からの出力は角度信号Zとして出力する。ここで、定数値生成回路30はアークタンジェント2の-k乗のそれぞれ $K = 0, 1, 2 \dots$ に対する定数値を格納したROMなどで構成することができる。また、アークタンジェント2の-k乗の値は定数値であるからROMに代わって論理回路で構成してもよい。

10

#### 【0009】

上記のように構成されたアークタンジェント演算回路を説明する。符号判定回路10において信号Xの符号が判定され、信号 $X < 0$ のときは反転回路9において信号Xが、反転回路16において信号Yが反転され、反転された信号Xはセレクタ11を介してレジスタ12にロードされ、反転された信号Yはセレクタ18を介してレジスタ19のロードされる。

。

#### 【0010】

信号X=0のときは反転回路9、16において信号X、信号Yが反転されずそのままレジスタ12、19にそれぞれロードされる。同時に、信号Xの正負に応じてセレクタ24によって定数0または定数が選択されて出力される。セレクタ24からの出力は、符号判定回路17において判定した信号Yの正負により、すなわち信号 $Y < 0$ のときはセレクタ24の出力を反転して、信号Y=0のときは反転せず、セレクタ26を介してZレジスタ27のロードされる。上記により初期設定が終了する。

20

#### 【0011】

次のクロックからセレクタ11、18、26はそれぞれ1ビット左シフト回路13、21、28の出力を選択する側に切替えられる。また、加減算回路15および29はYレジスタ19にロードされたデータが正のときは加算回路として作用し、負のときは減算回路として作用し、加減算回路23は逆にYレジスタ19にロードされたデータが正のときは減算回路として作用し、負のときは加算回路として作用する。加減算回路15、23、29の出力の各ビットは1ビット左シフト回路13、21、28によって1ビットシフトされてセレクタ11、18、26に接続される。

30

#### 【0012】

ここで、0ビットには0が入力される。同様にXレジスタ12のデータ、Yレジスタ19のデータは1ビット右シフト回路14、20によって各ビットが右に1ビットシフトされて加減算回路15、23に接続される。最上位ビットは符号拡張される。初期設定の終了に続いて、Xレジスタ12、Yレジスタ、Zレジスタ27、アークタンジェント2の-k乗( $k = 0, 1, 2 \dots$ )の定数値生成回路30に同時にクロックを必要回数与え、Zレジスタ27の出力Zからアークタンジェントの演算出力を得る。

#### 【0013】

【発明が解決しようとする課題】

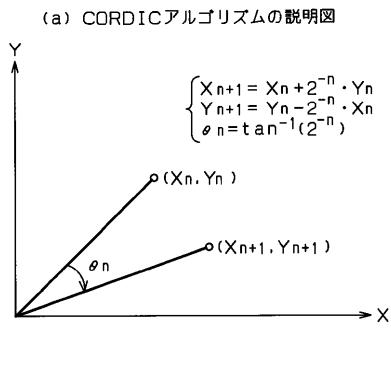

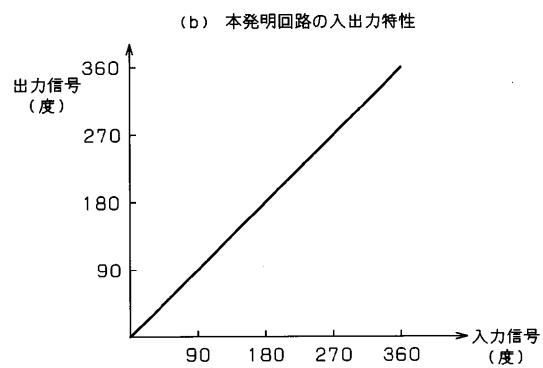

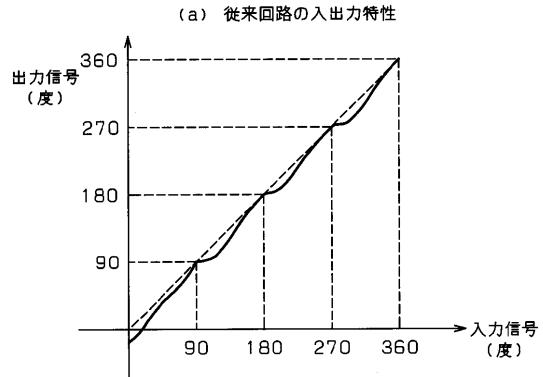

しかしながら上記のような構成では、次のような問題点を有している。CORDICアルゴリズム回路は図7(a)に示したように、ループをまわす回数が少ないと出力信号のアークタンジェント信号が非線型になるという問題点を有する。

40

#### 【0014】

#### 【課題を解決するための手段】

上記問題点を解決するために本発明のアークタンジェント回路は、第1の全波整流回路と、第2の全波整流回路と、第1の切り替え回路と、第2の切り替え回路と、第1のロードホールド回路と、CORDICアルゴリズムを利用し直交信号の位相成分を出力するCORDICアルゴリズム回路と、第2のロードホールド回路と、比較回路と、直交信号の位相が4象限のうちどこに存在するかを検出する象限検出回路と、第3のロードホールド回

50

路と、タイミング発生回路と、固定データ切り替え回路と、極性切り替え回路と、累積加算回路と、加算回路と、第4のロードホールド回路とを備えたものである。

#### 【0015】

##### 【発明の実施の形態】

本発明は、演算回数が少なくかつ演算誤差の少ないことを特徴とするアークタンジェント回路であり、収束させる基準の角度を0度ではなく、45度に設定するという作用を有する。

#### 【0016】

本発明は、第1の全波整流回路と、第2の全波整流回路と、第1の切り替え回路と、第2の切り替え回路と、第1のロードホールド回路と、CORDICアルゴリズムを利用し直交信号の位相成分を出力するCORDICアルゴリズム回路と、第2のロードホールド回路と、比較回路と、直交信号の位相が4象限のうちどこに存在するかを検出する象限検出回路と、第3のロードホールド回路と、タイミング発生回路と、固定データ切り替え回路と、極性切り替え回路と、累積加算回路と、加算回路と、第4のロードホールド回路とを備え、演算誤差回数が少なくかつ演算誤差の少ないことを特徴とするアークタンジェント回路であり、収束させる基準の角度を0度ではなく、45度に設定するという作用を有する。

10

#### 【0017】

本発明は、固定データ切り替え回路は固定データ値を容易に設定できる数式を使って算出していることを特徴とするアークタンジェント回路であり、1円周/360度を決まった値に設定するという作用を有する。

20

#### 【0018】

本発明は、固定データ切り替え回路は固定データ値を容易に設定できる数式を使って算出していることを特徴とするアークタンジェント回路であり、1円周/360度を決まった値に設定するという作用を有する。

#### 【0019】

以下本発明の実施の形態について、図面を参照しながら説明する。

#### 【0020】

##### (実施の形態)

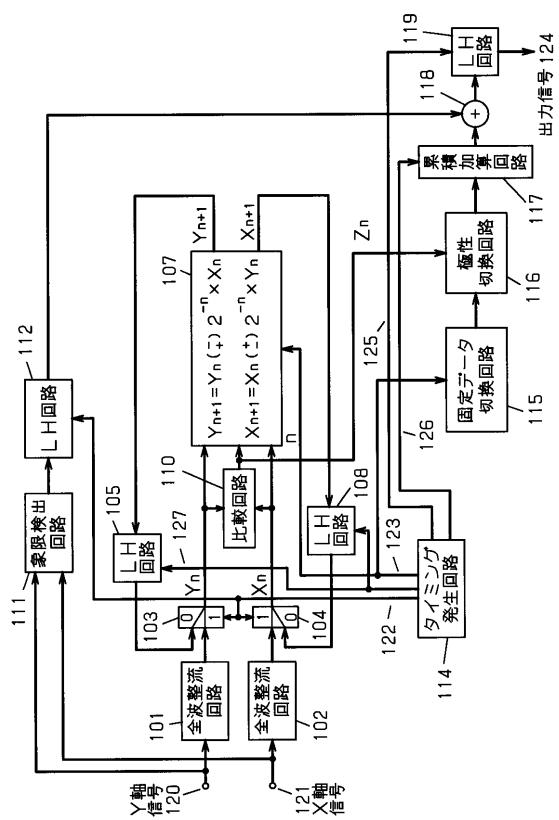

図1は本発明の第1の実施例におけるアークタンジェント回路のブロック構成図を示すものである。図1において、101は入力されたY軸信号が正の値の信号であればそのまま出力し、負の値の信号であれば反転して出力する、いわゆる全波整流回路である。

30

#### 【0021】

102は入力されたX軸信号が正の値の信号であればそのまま出力し、負の値の信号であれば反転して出力する、いわゆる全波整流回路であり、103はセレクタ制御信号が「1」ならば前記全波整流回路101の出力信号を出力し、「0」であれば後述するロードホールド回路105の出力信号を出力する切り替え回路である。

#### 【0022】

104はセレクタ制御信号が「1」ならば前記全波整流回路102の出力信号を出力し、「0」であれば後述するロードホールド回路108の出力信号を出力する切り替え回路であり、105は後述するタイミング発生回路114からの出力される制御信号が「1」のときに後述するCORDIC回路107からの出力信号( $Y_{n+1}$ 信号)を出力し(ロードし)、制御信号が「0」のときは出力している信号をそのまま変化させない(ホールド)、いわゆるロードホールド回路である。

40

#### 【0023】

107は前記切り替え回路103からの出力信号( $X_n$ 信号)と前記切り替え回路104からの出力信号( $Y_n$ 信号)と後述するタイミング発生回路114からの制御信号nを入力し、後述する比較回路110からの制御信号が「0」のときは( $Y_{n+1} = X_n - 2^{-n} \times Y_n$ 、 $X_{n+1} = Y_n + 2^{-n} \times X_n$ )の数式によって、制御信号が「1」のときは( $Y_{n+1} = X_n + 2^{-n} \times Y_n$ 、 $X_{n+1} = Y_n - 2^{-n} \times X_n$ )の数式によって得られる $Y_{n+1}$ 信号、 $X_{n+1}$ 信号を出

50

力する C O R D I C 回路である。

【 0 0 2 4 】

1 0 8 は後述するタイミング発生回路 1 1 4 から出力される制御信号が「 1 」のときに前記 C O R D I C 回路 1 0 7 からの出力信号 ( $X_{n+1}$  信号) を出力し (ロードし) 、制御信号が「 0 」のときは出力している信号をそのまま変化させない (ホールド) 、いわゆるロードホールド回路である。

【 0 0 2 5 】

1 1 0 は前記切り替え回路 1 0 3 、 1 0 4 からの出力信号 ( $X_n$  信号、  $Y_n$  信号) を入力し 、 ( $X_n$  信号  $>$   $Y_n$  信号) であれば「 0 」を出力し 、 ( $X_n$  信号  $>$   $Y_n$  信号) であれば「 1 」を出力する比較回路である。

10

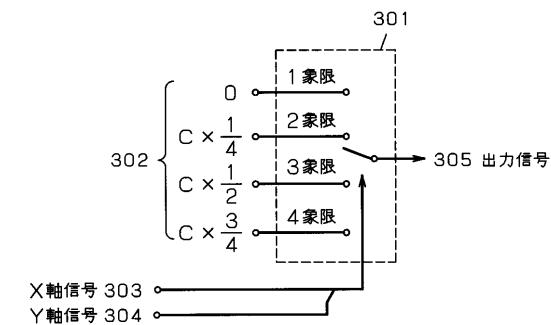

【 0 0 2 6 】

1 1 1 は入力される X 軸信号、 Y 軸信号の符号が ( X 軸信号 = 0 、 Y 軸信号 = 0 ) であれば 1 象限に位置する信号としてそれに相応する信号を出力し、 ( X 軸信号 < 0 、 Y 軸信号 = 0 ) であれば 2 象限に位置する信号としてそれに相応する信号を出力し、 ( X 軸信号 < 0 、 Y 軸信号 < 0 ) であれば 3 象限に位置する信号としてそれに相応する信号を出力し、 ( X 軸信号 = 0 、 Y 軸信号 < 0 ) であれば 4 象限に位置する信号としてそれに相応する信号を出力する象限検出回路である。

【 0 0 2 7 】

1 1 2 は前記象限回路 1 1 1 からの出力信号を入力信号とし、後述するタイミング発生回路 1 1 4 から出力される制御信号が「 1 」のときに前記象限回路 1 1 1 の出力信号を出力し (ロードし) 、制御信号が「 0 」のときは出力している信号をそのまま変化させない (ホールド) 、いわゆるロードホールド回路である。

20

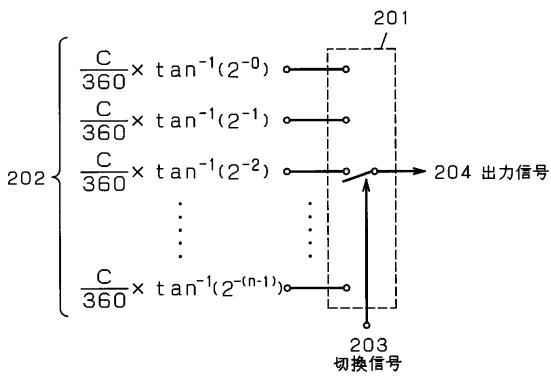

【 0 0 2 8 】

1 1 4 は各回路に必要なタイミングパルスを発生させるタイミング発生回路であり、 1 1 5 は  $\{ (C / 360) \times \tan^{-1}(2^{-n}) \}$  、 C は定数。 } により与えられる固定データを前記タイミング発生回路 1 1 4 からの制御信号 n によって切り替えて出力する固定データ切り替え回路である。

【 0 0 2 9 】

1 1 6 は前記固定データ切り替え回路 1 1 5 の出力信号を、前記比較回路 1 1 0 からの制御信号が「 0 」であればそのまま出力し、制御信号が「 1 」であれば反転して出力する極性切り替え回路であり、 1 1 7 は前記タイミング発生回路 1 1 4 からの制御信号に応じたタイミング期間に前記極性切り替え回路 1 1 6 の出力信号を累積加算したり、累積値をリセットしたりする累積加算回路である。

30

【 0 0 3 0 】

1 1 8 は前記累積加算回路 1 1 7 の出力信号と前記ロードホールド回路 1 1 2 の出力信号とを加算する加算回路であり、 1 1 9 は前記ロードホールド回路 1 1 8 の出力を入力信号とし、前記タイミング発生回路 1 1 4 から出力される制御信号が「 1 」のときに前記象限回路 1 1 1 の出力信号を出力し (ロードし) 、制御信号が「 0 」のときは出力している信号をそのまま変化させない (ホールド) 、いわゆるロードホールド回路である。

【 0 0 3 1 】

40

1 2 0 はデジタル信号で、かつ後述する X 軸信号と直交している Y 軸信号であり、 1 2 1 はデジタル信号で、かつ前記 Y 軸信号と直交している X 軸信号であり、 1 2 2 は前記タイミング発生回路から出力されるタイミングパルスであり、 1 2 3 は n と呼ばれる各回路の制御信号である、 1 2 4 はアークタンジェント回路からのデジタル出力信号である。

【 0 0 3 2 】

以上のように構成されたアークタンジェント回路について、以下図 1 、図 2 、図 3 、図 6 、図 8 を用いてその動作を説明する。

【 0 0 3 3 】

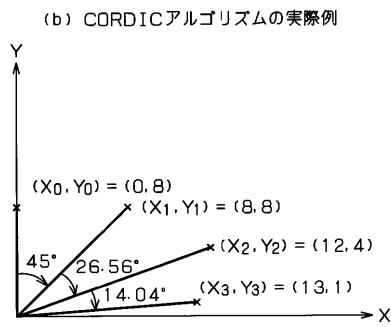

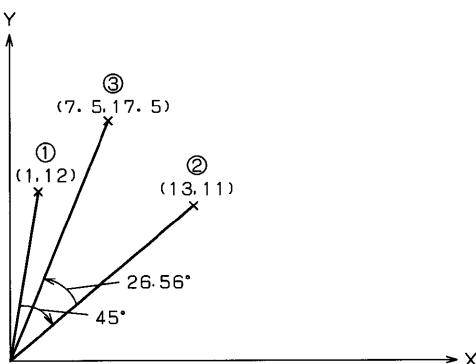

まず本発明のポイントとなる C O R D I C アルゴリズムを説明するが、その説明図が図 6 (a) である。図 6 (a) は直交信号 ( $X_n$  、  $Y_n$  ) を直交座標軸上に示したものである。

50

C O R D I C アルゴリズムとは ( $X_n$ 、 $Y_n$ ) の座標点から

$$X_{n+1} = X_n + 2^{-n} \times Y_n \dots \dots \dots \quad (1\text{式})$$

$$Y_{n+1} = Y_n - 2^{-n} \times X_n \dots \dots \dots \quad (2\text{式})$$

の数式によって示される新しい座標点 ( $X_{n+1}$ 、 $Y_{n+1}$ ) までの角度 が

$$\theta_n = \tan^{-1}(2^{-n}) \dots \dots \dots \quad (3\text{式})$$

によって得られるというアルゴリズムである。

例えば、図 6 (b) にその実際例があるが、初期値 ( $X_0$ 、 $Y_0$ ) = (0、8) であった場合の動作を示している。

$$n = 0 \text{ のときは } (X_1, Y_1) = (8, 8), \theta_0 = \tan^{-1}(2^0) = 45 \text{ 度}$$

$$n = 1 \text{ のときは } (X_2, Y_2) = (12, 4), \theta_1 = \tan^{-1}(2^{-1}) = 26.56 \text{ 度}$$

$$n = 2 \text{ のときは } (X_3, Y_3) = (13, 1), \theta_2 = \tan^{-1}(2^{-2}) = 14.04 \text{ 度}$$

というように決まった  $n$  の値では決まった角度だけ座標点が移動している事がわかる。これを用いて直交信号 ( $X_n$ 、 $Y_n$ ) の角度を検出するのが本発明だが、その説明図が図 8 にある。

#### 【0034】

ここで、X 軸信号 120 ( $X_n$  の初期値に相当する)、Y 軸信号 121 ( $Y_n$  の初期値に相当する) がビット数 10 ビットのデジタル信号だとする。その時、上記  $n$  の値は  $n = 10$  が最大値となるが、理由は (1 式)、(2 式) の中の  $2^{-n} \times Y_n$ 、 $2^{-n} \times X_n$  の項にて、 $X_n$ 、 $Y_n$  が 10 ビットデジタル信号であるため、 $2^{-n} \times Y_n$ 、 $2^{-n} \times X_n$  の計算が  $n = 11$  以上だと意味をなさなくなるからである。

#### 【0035】

さてここで、X 軸信号、Y 軸信号の入力値が ( $X_0$ 、 $Y_0$ ) = (1、12) として、CORDIC 回路 107 と固定データ切り替え回路 115 と極性切り替え回路 116 と累積加算回路 117 がどのように動作するのかを実際に見てみる。

#### 【0036】

(その角度 (アーカンジェント) を計算してみる。) まず、 $X_0$ 、 $Y_0$  であるため、比較回路 110 の出力制御信号は「0」になり、CORDIC 回路 107 の出力信号は ( $Y_{n+1} = X_n - 2^{-n} \times Y_n$ 、 $X_{n+1} = Y_n + 2^{-n} \times X_n$ ) の数式によって計算されるから、( $X_1$ 、 $Y_1$ ) = (13、11) となる。次に ( $X_2$ 、 $Y_2$ ) を計算するのだが、この時の比較回路 110 からの出力制御信号は「1」になるため、CORDIC 回路 107 の出力信号は ( $Y_{n+1} = X_n + 2^{-n} \times Y_n$ 、 $X_{n+1} = Y_n - 2^{-n} \times X_n$ ) の数式によって計算されるから、( $X_2$ 、 $Y_2$ ) = (7.5、17.5) となる。この計算を  $n = 10$  まで繰り返した結果は以下のようになる。

#### 【0037】

尚、比較制御 110 の出力制御信号を  $Z$  としている。

初期値、( $X_0$ 、 $Y_0$ ) = (1、12)

$$n = 0, (X_1, Y_1, Z_0) = (13, 11, 0)$$

$$n = 1, (X_2, Y_2, Z_1) = (7.5, 17.5, 1)$$

$$n = 2, (X_3, Y_3, Z_2) = (11.875, 15.625, 0)$$

$$n = 3, (X_4, Y_4, Z_3) = (13.828, 14.141, 0)$$

$$n = 4, (X_5, Y_5, Z_4) = (14.712, 13.276, 0)$$

$$n = 5, (X_6, Y_6, Z_5) = (14.297, 13.736, 1)$$

$$n = 6, (X_7, Y_7, Z_6) = (14.082, 13.960, 1)$$

$$n = 7, (X_8, Y_8, Z_7) = (13.973, 14.070, 1)$$

$$n = 8, (X_9, Y_9, Z_8) = (14.028, 14.015, 0)$$

$$n = 9, (X_{10}, Y_{10}, Z_9) = (14.001, 14.042, 1)$$

$$n = 10, (X_{11}, Y_{11}, Z_{10}) = (14.015, 14.029, 0)$$

$$n = 11, (Z_{11}) = (0)$$

になる。

#### 【0038】

10

20

30

40

50

ここで、各  $Z_n$  値に応じて固定データ切り替え回路 115 にて固定データを切り替え、更に比較回路 110 からの制御信号にてその極性を切り替えてやり、その結果を累積加算回路 117 にて累積してやると、欲しいデータが得られるが、それを実際に計算してみると、 $Z_0 = 0$  であるため、右回りに 45 度移動しているから移動角度を 45 度とする。

#### 【0039】

次に  $Z_1 = 1$  であるため、左回りに 26.565 度移動しているから移動角度を -26.565 度とする。これを  $n = 11$  まで続けたのが下の計算である。また、下の計算にて、移動角度は固定的に決まる値であり、これを各  $n$  によって切り替えているのが固定データ切り替え回路 115 であり、その符号を決定しているのが比較回路 110 であり、実際に固定データ切り替え回路 115 からのデータの極性を切り替えているのが極性切り替え回路 116 である。

10

#### 【0040】

$$n = 0, (Z_0, \text{移動角度}) = (0, 45)$$

$$n = 1, (Z_1, \text{移動角度}) = (1, -26.565)$$

$$n = 2, (Z_2, \text{移動角度}) = (0, 14.036)$$

$$n = 3, (Z_3, \text{移動角度}) = (0, 7.125)$$

$$n = 4, (Z_4, \text{移動角度}) = (0, 3.576)$$

$$n = 5, (Z_5, \text{移動角度}) = (1, -1.790)$$

$$n = 6, (Z_6, \text{移動角度}) = (1, -0.895)$$

$$n = 7, (Z_7, \text{移動角度}) = (1, -0.448)$$

20

$$n = 8, (Z_8, \text{移動角度}) = (0, 0.224)$$

$$n = 9, (Z_9, \text{移動角度}) = (1, -0.112)$$

$$n = 10, (Z_{10}, \text{移動角度}) = (0, 0.0560)$$

$$n = 11, (Z_{11}, \text{移動角度}) = (0, 0.0280)$$

(一般的には移動角度 =  $\tan^{-1}(2^{-n})$  で得られる。)

以上の計算は  $X_n = Y_n$  となるように ( $= 45$  度になるように) CORDIC アルゴリズムを計算しているため、上述した移動角度を全て加算すると(回路的には累積回路 117 にて行なう)  $X_n = Y_n$  となるまでの ( $= 45$  度となるまでの) 移動角度を得ることができるが、その結果は 40.236 度になる。

30

#### 【0041】

収束角度が 45 度であるため、出力角度は  $40.236 + 45 = 85.236$  度になるが、これは初期値 (1, 12) のアーカタンジェント値 ( $\tan^{-1}(12) = 85.236$  度) と同じ結果になる。

#### 【0042】

以上は CORDIC 回路 107 と固定データ切り替え回路 115 と極性切り替え回路 116 と累積加算回路 117 の一連の回路がどのように動作するのかを示したものであるが、これだけでは十分に回路動作を説明できていないため、残りの説明を行なう。

#### 【0043】

まず、全波整流回路 101、102 は入力された X 軸信号と Y 軸信号とを全波整流する。これは CORDIC 回路 107 に入力する信号を全て第 1 象限に移動させ、第 1 象限において入力信号のベクトル角を計算するのだが、これは計算のやり易さのためであり、また計算精度を高めるためでもある。

40

#### 【0044】

全波整流回路 101、102 の出力信号は切り替え回路 103、104 に入力されるが、切り替え回路 103、104 のセレクタ制御信号は図 9 (d) 122 の信号のタイミングで切り替わるり、「H」のときに X 軸信号 120、Y 軸信号 121 を取り込み CORDIC 回路 107 に信号を送る。そして、まず、比較回路 110 に入力され、制御信号  $Z_n$  を出力し、切り替え回路 103、104 からの出力信号  $X_n$ 、 $Y_n$  とともに CORDIC 回路 107 に入力される。

#### 【0045】

50

C O R D I C 回路 107 ではタイミング発生回路 114 から出力される n 信号 123 (図 9 (c) に示すタイミング波形) に応じて、次の計算を行なう。Z<sub>n</sub> が「0」のときは (Y<sub>n+1</sub> = X<sub>n</sub> - 2<sup>-n</sup> × Y<sub>n</sub>、 X<sub>n+1</sub> = Y<sub>n</sub> + 2<sup>-n</sup> × X<sub>n</sub>) の数式によって、「1」のときは (Y<sub>n+1</sub> = X<sub>n</sub> + 2<sup>-n</sup> × Y<sub>n</sub>、 X<sub>n+1</sub> = Y<sub>n</sub> - 2<sup>-n</sup> × X<sub>n</sub>) の数式によって得られる Y<sub>n+1</sub> 信号、 X<sub>n+1</sub> 信号を出力する。

#### 【0046】

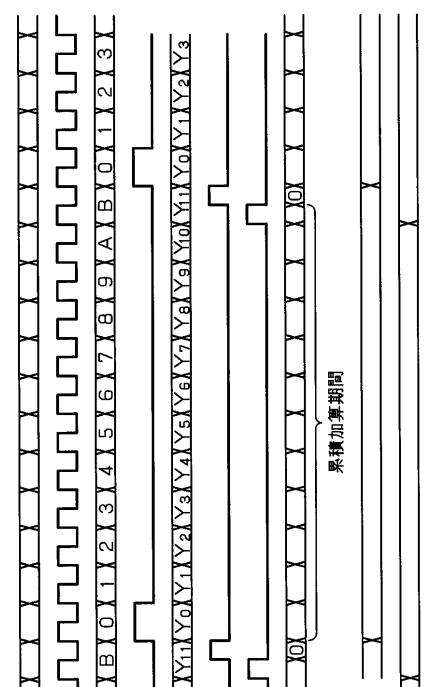

これらの信号をロードホールド回路 105、108 に入力し、切り替え回路 103、104 に戻す。そうすると Y<sub>n</sub> 信号は図 9 (e) に示したような Y<sub>0</sub> ~ Y<sub>10</sub> を繰り返す信号になる。次に比較回路 110 から出力された制御信号 Z<sub>n</sub> は極性切り替え回路 116 に入力され、固定データ切り替え回路 115 からの出力データの極性を切り替えるが、固定データ切り替え回路は前述した tan<sup>-1</sup>(2<sup>-n</sup>) という数式によって得られるデータをタイミング発生回路 114 からの n 信号 123 に応じた信号を切り替えて出力している。10

#### 【0047】

例えば前述した条件であれば、

$$\begin{aligned} Z_0 &= 45 \text{ 度}, 800 \text{ h} \\ Z_1 &= 26.565 \text{ 度}, 4B9 \text{ h} \\ Z_2 &= 14.036 \text{ 度}, 27E \text{ h} \\ Z_3 &= 7.125 \text{ 度}, 144 \text{ h} \\ Z_4 &= 3.576 \text{ 度}, A2 \text{ h} \\ Z_5 &= 1.790 \text{ 度}, 51 \text{ h} \\ Z_6 &= 0.895 \text{ 度}, 28 \text{ h} \\ Z_7 &= 0.448 \text{ 度}, 14 \text{ h} \\ Z_8 &= 0.224 \text{ 度}, A \text{ h} \\ Z_9 &= 0.112 \text{ 度}, 5 \text{ h} \\ Z_{10} &= 0.0560 \text{ 度}, 2 \text{ h} \\ Z_{11} &= 0.0280 \text{ 度}, 1 \text{ h} \end{aligned}$$

ということになるが、左側の値は tan<sup>-1</sup>(2<sup>-n</sup>) にて計算した値、右側の値は (C / 360) × tan<sup>-1</sup>(2<sup>-n</sup>) にて計算した値であり、ここでは C = 4000 h としているが、C とは 1 円周角 (360 度) を与える定数であり、16 進法にて 100、200、400、800 というように MSB を「1」にして残りは「0」にするように決める。理由は後述する。そしてそのブロック構成図は図 2 にある。20

#### 【0048】

また、極性切り替え回路 116 からの出力信号を累積加算回路 117 によって累積加算するが、この回路をリセットするタイミングが図 9 (f) 126 信号にあり、累積加算回路 117 の出力信号の状態が図 9 (h) に示してあるが、リセットした直後の出力信号が「0」になっており、このタイミング後に新たな累積加算が始まっていることがわかる。30

#### 【0049】

一方 X 軸信号 121、Y 軸信号 120 は象限検出回路 111 に入力され、入力された信号の正負情報から新しく作られたデータを選択し出力するように動作する。そのブロック構成図が図 3 に示されているが、40

$$\begin{aligned} (X, Y) = (\text{正}, \text{正}) &\text{ならば } 0(0 \text{ h}) \text{ を出力し,} \\ (X, Y) = (\text{負}, \text{正}) &\text{ならば } C/4(1000 \text{ h}) \text{ を出力し,} \\ (X, Y) = (\text{負}, \text{負}) &\text{ならば } C/2(2000 \text{ h}) \text{ を出力し,} \\ (X, Y) = (\text{正}, \text{負}) &\text{ならば } C \times 3/4(3000 \text{ h}) \text{ を出力する。} \end{aligned}$$

という切り替えを行ない、その出力をロードホールド回路 112 に入力するが、これは全波整流回路 101、102 にて入力された信号を全て第 1 象限に変換したため、元々存在していた象限のデータを後段にて付加する必要があるためだ。

#### 【0050】

そのデータを発生させるのが象限検出回路 111 であり、象限検出回路 111 からのデータと累積加算回路 117 からのデータとのタイミングを調整するのがロードホールド回路50

112である。そしてそれらのタイミングは図9(i)にある。ロードホールド回路112からの象限変換データと累積加算回路117からのアークタンジェントデータとを加算して最終のアークタンジェントデータにするのが加算回路118で、そのデータのタイミングを合わせるのがロードホールド回路119である。

#### 【0051】

そのタイミングは図9(j)にある。以上のようにして直交信号であるX軸信号とY軸信号のアークタンジェントである出力信号124を得ることができる。

#### 【0052】

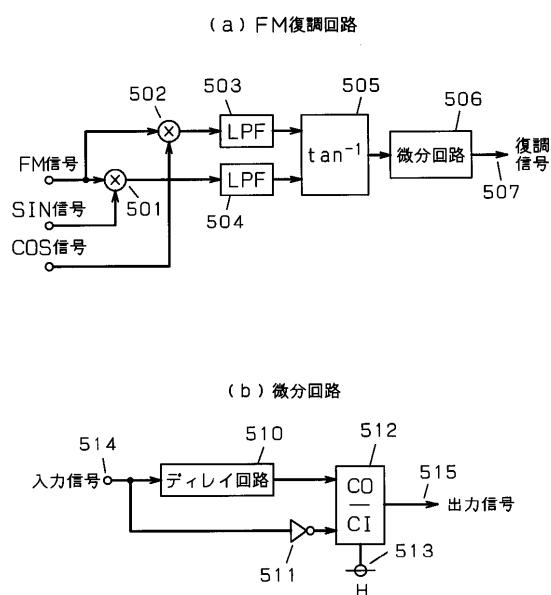

ここで、Cの値の決定方法であるが、その説明ブロック図が図5である。図5(a)にて501は掛け算回路、502は掛け算回路、503は高調波成分を取り除くためのローパスフィルター回路、504は高調波成分を取り除くためのローパスフィルター回路、505は本発明回路と同じ働きをするアークタンジェント回路、506は微分回路であり、このブロック構成図にてFM変調された信号を復調する事ができる。10

#### 【0053】

簡単に説明するとFM信号は周波数によって変調を受けた信号であるから、固定周波数(FM変調周波数に近い周波数)をもつSIN信号、COS信号を掛け算回路501、502によって入力信号に掛け算すると、そのビート成分が出力される。この信号に含まれる高調波成分をLPF503、504にて落とし、直交信号成分だけにして、アークタンジェント回路505に入力すると、前記ビート成分のアークタンジェント信号が得られる。20

#### 【0054】

ここで、入力信号の周波数が高くなると、ビート成分の周波数も高くなり、アークタンジェント回路505から出力される角度信号の変化量も大きくなるため、その信号の微分成分も大きくなる。つまり、アークタンジェント回路505からの出力信号を微分回路506にて微分した出力信号はFM復調した信号そのものになる。このようにアークタンジェント回路からの出力信号を微分するとFM復調信号が得られるが、アークタンジェント回路からの出力信号は0度～360度をぐるぐる繰り返す信号となるため、単純に微分すると0度/360度の境界にて非線形部分が出力され、正確な復調信号が得られない。20

#### 【0055】

そこで、一円周360度を16進法にて100、200、400、800というようにMSBを「1」にして残りは「0」にするように決める。そうすると、図5(b)に示す微分回路では正確な復調信号が得られることになるが、まず図5(b)を説明すると、510は入力信号をある一定時間遅らせるディレイ回路、511は入力信号を反転させる反転回路、512は入力信号をアダ-するアダ-回路であるが、この場合反転回路511にて片方の入力信号を反転させており、かつキャリーイン信号を「H」に設定しているため、アダ-回路512は引き算回路になる。次にこの微分回路で実際に演算を行なってみる。30

#### 【0056】

まず一円周360度を4000hとして、入力信号を図10(a)のように設定するが、これは360度(4000h)をまたがり、かつ単純増加(80h)する値にしている。この信号をディレイ回路510に通した信号が図10(b)とすると、出力信号515は図10(c)になるが、これをみると、全て80hになっており、非線型部分が無い事がわかる。このようにCの値を16進法にて100、200、400、800というようにMSBを「1」にして残りは「0」にするように決めると、FM復調には必要な微分回路を図5(b)に示すような簡単な回路で構成する事ができるが、これを実現するには固定データ切り替え回路115を図2に示すようなデータ設定にする事、かつ象限検出回路111を図3に示すようなデータ設定にする事が必要になる。40

#### 【0057】

以上のように本実施例によれば、比較回路110を設けて収束角度を45度にすること、また固定データ切り替え回路115を図2に示すようなデータ設定にする事、かつ象限検出回路111を図3に示すようなデータ設定にする事で、演算回数が少なくかつ演算誤差の少ないことを特徴とするアークタンジェント回路を提供することができる。50

## 【0058】

## 【発明の効果】

以上のように本発明は第1の全波整流回路と、第2の全波整流回路と、第1の切り替え回路と、第2の切り替え回路と、第1のロードホールド回路と、CORDICアルゴリズム回路と、第2のロードホールド回路と、比較回路と、象限検出回路と、第3のロードホールド回路と、タイミング発生回路と、固定データ切り替え回路と、極性切り替え回路と、累積加算回路と、加算回路と、第4のロードホールド回路を設ける事により、演算回数が少なくかつ演算誤差の少ないアークタンジェント回路を提供する事ができる。

## 【図面の簡単な説明】

【図1】本発明の実施例におけるアークタンジェント回路のブロック構成図

10

【図2】本発明の固定データ切り替え回路のブロック構成図

【図3】本発明の象限切り替え回路のブロック構成図

【図4】従来のアークタンジェント回路のブロック構成図

【図5】本発明の実施例におけるFM復調回路の動作説明図

【図6】本発明の実施例におけるCORDICアルゴリズムの動作説明図

【図7】従来及び本発明の実施例における入出力特性図

【図8】本発明の実施例におけるCORDICアルゴリズムの動作説明図

【図9】本発明の実施例におけるアークタンジェント回路の動作説明図

【図10】本発明の実施例における微分回路の動作説明図

## 【符号の説明】

20

101 全波整流回路

102 全波整流回路

103 切り替え回路

104 切り替え回路

105 ロードホールド回路

107 CORDIC回路

108 ロードホールド回路

110 比較回路

111 象限検出回路

112 ロードホールド回路

30

114 タイミング発生回路

115 固定データ切り替え回路

116 極性切り替え回路

117 累積加算回路

118 加算回路

119 ロードホールド回路

120 Y軸信号

121 X軸信号

122 タイミングパルス

123 n制御信号

40

124 出力信号

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

(a) X軸信号

(b) 127

(c) n信号

(d) 123

(e) 122

(f) 126

(g) 125

(h) 累積加算回路

(i) LH回路112の出力信号

(j) LH回路124の出力信号

【図 10】

|                        |                                                         |

|------------------------|---------------------------------------------------------|

| (a) 入力信号               | 0180h X 0100h Y 0080h X 4000h X 3f80h X 3f00h X 3e80h X |

| (b) ディレ1回路<br>510 出力信号 | X 0180h X 0100h X 0080h X 4000h X 3f80h X 3f00h X       |

| (c) 出力信号 515           | 80h X 80h Y 80h X 80h Y 80h X 80h X                     |

---

フロントページの続き

(72)発明者 森田 久雄

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 濵谷 竜一

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 安藤 仁

大阪府門真市大字門真1006番地 松下電器産業株式会社内

審査官 上田 智志

(56)参考文献 特開平11-251841(JP,A)

特開昭63-088905(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03D 3/00-3/34,

H04L 27/22