(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6080447号

(P6080447)

(45) 発行日 平成29年2月15日(2017.2.15)

(24) 登録日 平成29年1月27日(2017.1.27)

(51) Int.Cl.

H01L 31/10 (2006.01)

F 1

H01L 31/10

H01L 31/10G

A

請求項の数 19 (全 24 頁)

(21) 出願番号 特願2012-203185 (P2012-203185)

(22) 出願日 平成24年9月14日 (2012.9.14)

(65) 公開番号 特開2013-138174 (P2013-138174A)

(43) 公開日 平成25年7月11日 (2013.7.11)

審査請求日 平成27年9月10日 (2015.9.10)

(31) 優先権主張番号 特願2011-263704 (P2011-263704)

(32) 優先日 平成23年12月1日 (2011.12.1)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 小林 秀央

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 佐竹 政彦

最終頁に続く

(54) 【発明の名称】光電変換装置

(57) 【特許請求の範囲】

【請求項 1】

第1の端子と、

第1の電流出力端子と、

第1の光電変換素子と、

第1の検出手段と、

第1のフィードバック手段と、

電流供給手段とを有し、

前記第1の端子は、前記第1の光電変換素子と、前記第1の検出手段と、前記第1のフィードバック手段と、前記電流供給手段とに接続され、

10

前記第1のフィードバック手段は、さらに前記第1の電流出力端子に接続され、

前記第1の光電変換素子は、光電変換により電流を前記第1の端子に出力し、

前記第1の検出手段は、前記第1の端子の電位に基づく電位を前記第1のフィードバック手段に出力し、

前記第1のフィードバック手段は、前記第1の端子の電位に基づく電位を前記第1の端子にフィードバックし、前記第1の光電変換素子が出力する電流に基づく電流を前記第1の電流出力端子に出力し、

前記電流供給手段は、前記第1の端子へ電流を供給する電流源であって、

前記電流源が供給する電流と、光を受けた前記第1の光電変換素子が生成する電流とを加算した加算電流が、前記第1の端子に供給され、

20

前記加算電流によって前記第1の光電変換素子の光量が検出されることを特徴とする光電変換装置。

**【請求項2】**

前記第1の光電変換素子は、第1のフォトダイオードであり、

前記第1の端子は、前記第1のフォトダイオードのアノードに接続され、

前記第1の検出手段は、第1の電界効果トランジスタ及び第1の電流源を有し、

前記第1のフィードバック手段は、第1のバイポーラトランジスタ及び第2の電界効果トランジスタを有し、

前記第1のフォトダイオードのアノードは、前記第1の電界効果トランジスタのゲート及び前記第1のバイポーラトランジスタのベースに接続され、

前記第1の電界効果トランジスタは、ドレインが前記第1の電流源に接続され、

前記第2の電界効果トランジスタは、ソースが前記第1のバイポーラトランジスタのエミッタに接続され、ゲートが前記第1の電界効果トランジスタのドレインに接続され、ドレインが前記第1の電流出力端子に接続されることを特徴とする請求項1記載の光電変換装置。

**【請求項3】**

前記電流供給手段は、第1の期間には第1の電流値の電流を前記第1の端子に供給し、第2の期間には前記第1の電流値より小さい第2の電流値の電流を前記第1の端子に供給する又は電流を供給しないことを特徴とする請求項1又は2記載の光電変換装置。

**【請求項4】**

前記第1の期間は、光を受けた前記第1の光電変換素子が前記電流を生成する期間であり、

前記第2の期間は、光を受けた前記第1の電流出力端子が出力する電流を用いて前記光電変換装置が前記第1の光電変換素子の光量の検出を行う期間であることを特徴とする請求項3記載の光電変換装置。

**【請求項5】**

前記電流供給手段は、電源投入後の一定期間において、前記第2の電流値よりも多い電流値の電流を前記第1の端子に供給することを特徴とする請求項3記載の光電変換装置。

**【請求項6】**

前記第1の光電変換素子、前記第1の検出手段、前記第1のフィードバック手段及び前記電流供給手段の組みが複数設けられ、

複数の前記第1の光電変換素子は、第1の導電型の光電変換領域と、前記第1の導電型と逆の導電型である第2の導電型の領域を交互に複数積層することにより、深さ方向に積層されることを特徴とする請求項1又は2記載の光電変換装置。

**【請求項7】**

複数の前記電流供給手段のうちの一の電流供給手段は、少なくとも他の一の電流供給手段とは異なる電流値の電流を供給することを特徴とする請求項6記載の光電変換装置。

**【請求項8】**

さらに、前記第1の電流出力端子の電流を検出する電流検出手段を有し、

前記電流供給手段は、前記電流検出手段により検出される電流に応じて供給する電流値が変わることを特徴とする請求項1又は2記載の光電変換装置。

**【請求項9】**

前記第1の光電変換素子、前記第1の検出手段、前記第1のフィードバック手段及び前記電流供給手段の組みが複数設けられ、

さらに、複数の前記第1の電流出力端子の電流のうちの最小値の電流を検出する最小電流検出手段を有し、

複数の前記電流供給手段は、前記最小電流検出手段により検出される最小値の電流に応じて供給する電流値が変わることを特徴とする請求項1又は2記載の光電変換装置。

**【請求項10】**

第1の端子と、

10

20

30

40

50

第1の電流出力端子と、

第1の光電変換素子と、

第1の検出手段と、

第1のフィードバック手段と、

電流供給手段とを有し、

前記第1の端子は、前記第1の光電変換素子と、前記第1の検出手段と、前記第1のフィードバック手段と、前記電流供給手段とに接続され、

前記第1のフィードバック手段は、さらに前記第1の電流出力端子に接続され、

前記第1の光電変換素子は、光電変換により電流を前記第1の端子に出力し、

前記第1の検出手段は、前記第1の端子の電位に基づく電位を前記第1のフィードバック手段に出力し、

前記第1のフィードバック手段は、前記第1の端子の電位に基づく電位を前記第1の端子にフィードバックし、前記第1の光電変換素子が出力する電流に基づく電流を前記第1の電流出力端子に出力し、

前記電流供給手段は、前記第1の端子へ電流を供給し、

前記電流供給手段は、

第2の端子と、

光電変換により電流を前記第2の端子に出力可能な第2の光電変換素子と、

前記第2の端子の電位を検出する第2の検出手段と、

前記第2の検出手段により検出された電位に基づく信号を前記第2の端子にフィードバックし、前記第2の端子の電位に基づく電流を第2の電流出力端子に出力する第2のフィードバック手段と、

前記第2の光電変換素子で発生する電流を用いて前記第1の端子へ電流を出力する電流加算手段と

を有することを特徴とする光電変換装置。

#### 【請求項11】

前記第2の光電変換素子は、第2のフォトダイオードであり、

前記第2の検出手段は、第3の電界効果トランジスタ及び第3の電流源を有し、

前記第2のフィードバック手段は、第2のバイポーラトランジスタ及び第4の電界効果トランジスタを有し、

前記第2の端子は、前記第3の電界効果トランジスタのゲート及び前記第2のバイポーラトランジスタのベースに接続され、

前記第3の電界効果トランジスタは、ドレインが前記第3の電流源に接続され、

前記第4の電界効果トランジスタは、ソースが前記第2のバイポーラトランジスタのエミッタに接続され、ゲートが前記第3の電界効果トランジスタのドレインに接続され、ドレインが前記第2の電流出力端子に接続されることを特徴とする請求項10記載の光電変換装置。

#### 【請求項12】

前記第2の光電変換素子は、第2のフォトダイオードであり、

前記第2の検出手段は、第3の電界効果トランジスタ及び第3の電流源を有し、

前記第2のフィードバック手段は、第4の電界効果トランジスタを有し、

前記第2の端子は、前記第3の電界効果トランジスタのゲート及び前記第4の電界効果トランジスタのソースに接続され、

前記第3の電界効果トランジスタは、ドレインが前記第3の電流源に接続され、

前記第4の電界効果トランジスタは、ゲートが前記第3の電界効果トランジスタのドレインに接続され、ドレインが前記第2の電流出力端子に接続されることを特徴とする請求項10記載の光電変換装置。

#### 【請求項13】

前記電流加算手段は、第5の電界効果トランジスタ及び第6の電界効果トランジスタを有し、

10

20

30

40

50

前記第5の電界効果トランジスタは、ドレインが前記第2の端子に接続され、ソースが前記第2のフォトダイオードのアノードに接続され、

前記第6の電界効果トランジスタは、ドレインが前記第1の光電変換素子である第1のフォトダイオードのアノードに接続され、ソースが前記第2のフォトダイオードのアノードに接続されることを特徴とする請求項10記載の光電変換装置。

**【請求項14】**

前記電流加算手段は、前記第2の光電変換素子で発生する電流を増幅して、前記第1の端子へ電流を出力する電流を生成する電流増幅手段を有することを特徴とする請求項11記載の光電変換装置。

**【請求項15】**

前記電流増幅手段は、カレントミラー回路を有し、前記カレントミラー回路は、電圧バッファを有することを特徴とする請求項14記載の光電変換装置。

**【請求項16】**

前記第1及び第2の光電変換素子は、第1の導電型の光電変換領域と、前記第1の導電型と逆の導電型である第2の導電型の領域を交互に複数積層することにより、深さ方向に積層されることを特徴とする請求項13～15のいずれか1項に記載の光電変換装置。

**【請求項17】**

前記第2の光電変換素子の感度は、前記第1の光電変換素子の感度よりも高いことを特徴とする請求項14又は15記載の光電変換装置。

**【請求項18】**

前記第2の端子に付随する容量は、前記第1の端子に付隨する容量より小さいことを特徴とする請求項14又は15記載の光電変換装置。

**【請求項19】**

前記第1の電流出力端子から得られる電流に基づいた信号と前記第2の電流出力端子から得られる電流に基づいた信号を用いて、差分処理を行うことを特徴とする請求項14又は15記載の光電変換装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、光電変換装置に関する。

30

**【背景技術】**

**【0002】**

特許文献1は、フォトトランジスタとフィードバック手段を用いた光電変換装置を開示している。その光電変換装置は、定電流源とその定電流源によって駆動されるMOSFETでソース接地回路を構成しており、そのMOSFETのゲートとソース間の電圧で、フォトトランジスタのベース電位を定めている。また、その光電変換装置は、光量が変化した際、フォトトランジスタのコレクタ電流が変化するので、そのベースとエミッタ間の電圧が変化するが、この時、フォトトランジスタのベース電位ではなくエミッタ電位が主に変動する構成となっている。光電流でバイアスされたベースではなく、より大きな電流( $\sim hFE \times$ 光電流)でバイアスされたエミッタの電位が動くようにすることで光応答性を向上させている。すなわち、光量が変化してから、ベース電位とエミッタ電位の変化が完了するまでの時間の短縮を行っている。

40

**【先行技術文献】**

**【特許文献】**

**【0003】**

【特許文献1】特開2000-77644号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

本発明の目的は、光応答特性の良い光電変換装置を提供することである。

50

**【課題を解決するための手段】****【0005】**

本発明の光電変換装置は、第1の端子と、第1の電流出力端子と、第1の光電変換素子と、第1の検出手段と、第1のフィードバック手段と、電流供給手段とを有し、前記第1の端子は、前記第1の光電変換素子と、前記第1の検出手段と、前記第1のフィードバック手段と、前記電流供給手段とに接続され、前記第1のフィードバック手段は、さらに前記第1の電流出力端子に接続され、前記第1の光電変換素子は、光電変換により電流を前記第1の端子に出力し、前記第1の検出手段は、前記第1の端子の電位に基づく電位を前記第1のフィードバック手段に出力し、前記第1のフィードバック手段は、前記第1の端子の電位に基づく電位を前記第1の端子にフィードバックし、前記第1の光電変換素子が10出力する電流に基づく電流を前記第1の電流出力端子に出力し、前記電流供給手段は、前記第1の端子へ電流を供給する電流源であって、前記電流源が供給する電流と、光を受けた前記第1の光電変換素子が生成する電流とを加算した加算電流が、前記第1の端子に供給され、前記加算電流によって前記第1の光電変換素子の光量が検出されることを特徴とする。

**【発明の効果】****【0006】**

電流供給手段によって電流を第1の端子に供給することにより、光応答特性の良い光電変換装置を提供することができる。

**【図面の簡単な説明】****【0007】**

【図1】ソース接地回路の動作点を表す概念図である。

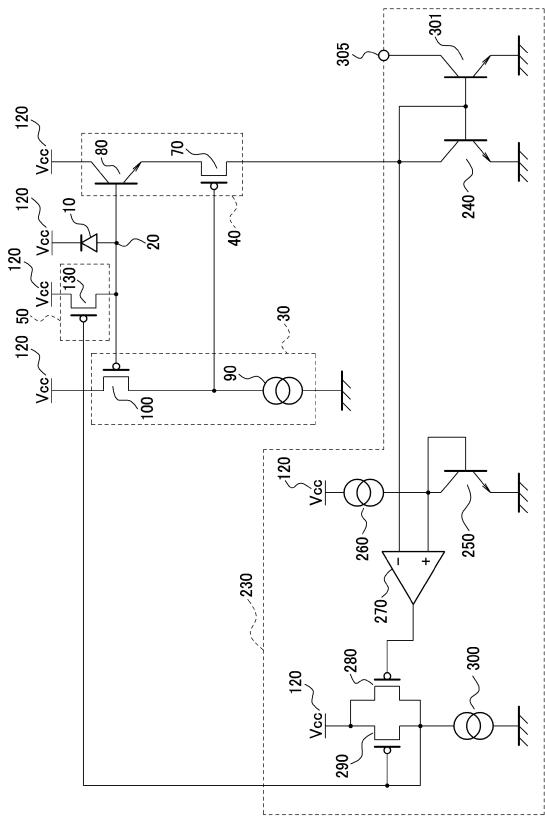

【図2】第1の実施形態の構成例を示す図である。

【図3】第1の実施形態の構成例を示す図である。

【図4】第1の実施形態の説明図である。

【図5】第2の実施形態の構成例を示す図である。

【図6】第2の実施形態の構成例を示す図である。

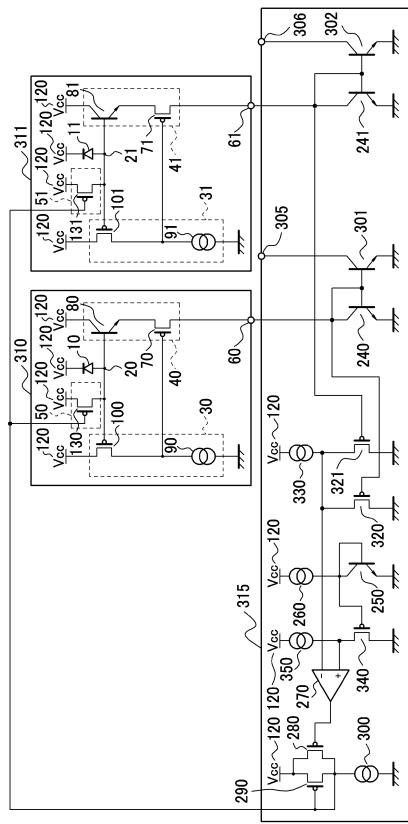

【図7】第3及び第4の実施形態の構成例を示す図である。

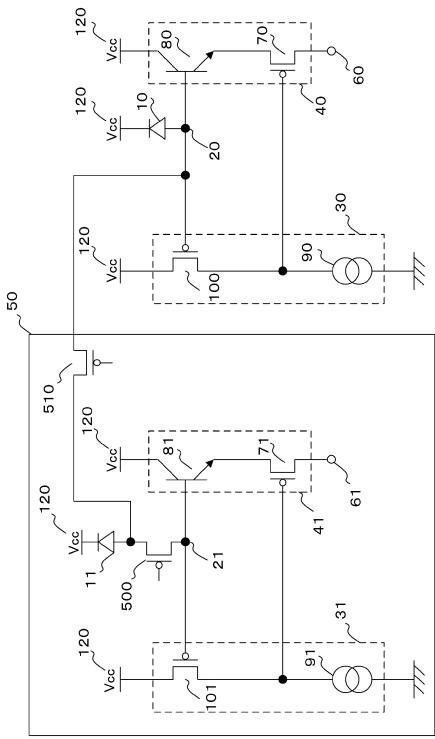

【図8】第5の実施形態の構成例を示す図である。

【図9】第5の実施形態の構成例を示す図である。

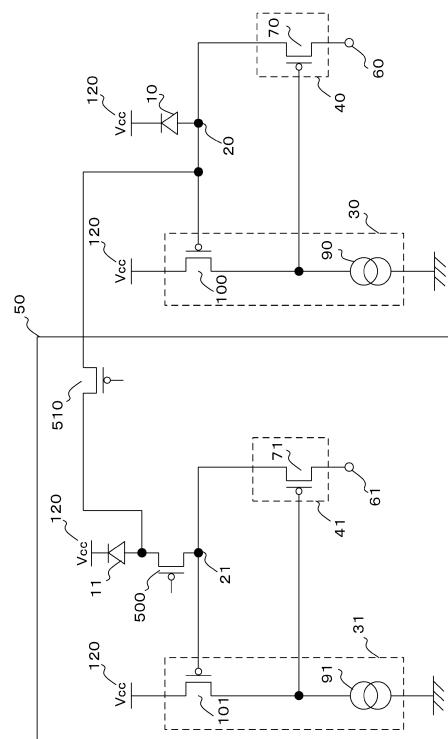

【図10】第6の実施形態の構成例を示す図である。

【図11】第7の実施形態の構成例を示す図である。

【図12】第8の実施形態の構成例を示す図である。

【図13】第8の実施形態の構成例を示す図である。

【図14】第9の実施形態の構成例を示す図である。

【図15】第10の実施形態の構成例を示す図である。

【図16】第11の実施形態の構成例を示す図である。

【図17】第12の実施形態の構成例を示す図である。

【図18】第13の実施形態の構成例を示す図である。

**【発明を実施するための形態】****【0008】****(第1の実施形態)**

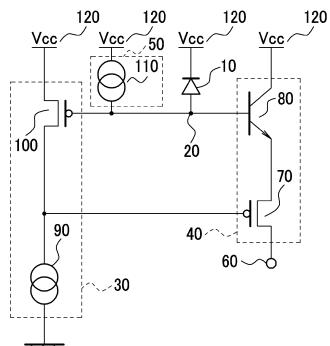

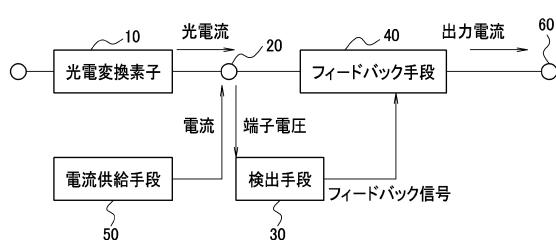

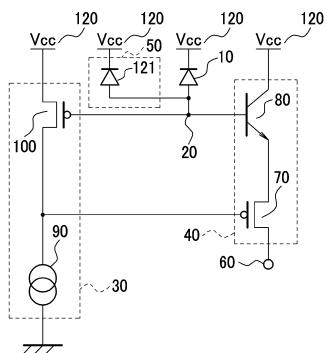

図2は、本発明の第1の実施形態に係る光電変換装置(センサ)の構成例を示す図である。光電変換装置は、第1の光電変換素子10と、第1の光電変換素子10で発生した光電流が入力される第1の端子20と、第1の検出手段30と、第1のフィードバック手段40と、電流供給手段50と、第1の電流出力端子60とを有する。光電変換素子10は、光電変換により電流を端子20に出力する。検出手段30は、光電変換素子10の端子20の電位を検出する。フィードバック手段40は、検出手段30により検出された電位に基づくフィードバック信号を光電変換素子10の端子20にフィードバックし、光電変換素子10の端子20の電位に基づく電流を電流出力端子60に出力する。電流供給手段50

50は、光電変換素子10の端子20へ電流を供給する。図2において、光電流が入力される端子20の電位を検出手段30で検出し、フィードバック手段40を用いてフィードバックをかけることによって、光電流が変化した際の端子20の電位変動を低減することができる。

#### 【0009】

本実施形態においては、電流供給手段50から端子20に電流を供給することにより、光応答性を改善することができる。

#### 【0010】

図3は、図2の光電変換装置の具体的な回路構成例を示す図である。まず、図2と図3の対応について説明する。第1の光電変換素子10は光電変換を行う第1のフォトダイオードであり、第1の光電変換素子10の第1の端子20は第1のフォトダイオード10のアノードである。第1の検出手段30は、第1の電界効果トランジスタ(MOSFET)100及び第1の電流源(定電流源)90を有する。第1のフィードバック手段40は、第1のバイポーラトランジスタ80及び第2の電界効果トランジスタ(MOSFET)70を有する。フォトダイオード10のアノード20は、第1の電界効果トランジスタ100のゲート及びバイポーラトランジスタ80のベースに接続される。フォトダイオード10のカソードは、電源電圧端子120に接続される。第1の電界効果トランジスタ100は、ソースが電源電圧端子120に接続され、ドレインが第1の電流源90を介してグランド端子に接続される。第2の電界効果トランジスタ70は、ソースがバイポーラトランジスタ80のエミッタに接続され、ゲートが第1の電界効果トランジスタ100のドレンに接続され、ドレインが電流出力端子60に接続される。バイポーラトランジスタ80は、コレクタが電源電圧端子120に接続される。電流供給手段50は、第2の電流源110を有し、電源電圧端子120及びフォトダイオード10のアノード20間に接続される。検出手段30は、定電流源90とMOSFET100のソース接地回路で構成されている。電源電圧端子120は電源Vccに接続されている。本実施形態においては、端子20での光電流が一定値以下となる場合に、電流源110から端子20に一定電流を供給することにより、端子20の電流を一定に保つことができるので、端子20の電位変動を抑えることが可能となる。例えば、露光状態から光電流が一定値以下となる検出動作開始前の暗い状態に変化した場合の端子20の電位変動をより低減できる。その結果、再び露光状態にして光が照射され、検出動作を開始する際の端子20の電流を用いてベースに付随する容量を充電する時間を低減することができる。その結果、光電流の小さい場合の光応答性を改善することができる。

#### 【0011】

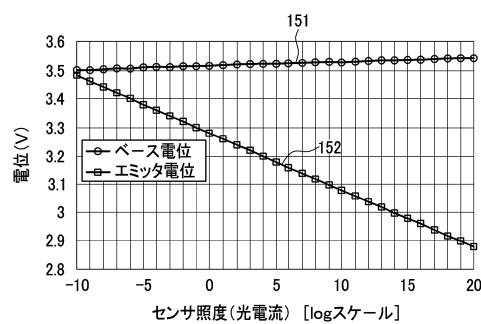

図3において、電流源110がない場合、バイポーラトランジスタ80のベース電位とエミッタ電位は、センサ照度(もしくは光電変換素子10の光電流値)に対して、図1のように変化する。図1は、ソース接地回路の動作点を表す概念図である。図1の横軸は、光量(もしくは、光電流=ベース電流)である。横軸は10gスケールであり、1目盛毎に光量が2倍になる。縦軸は電位である。光量の指数関数的な増加に対して、ベースとエミッタ間の電圧がリニアに増加していくことがわかる。これは、ベースとエミッタ間の電圧Vbeとコレクタ電流Icの間に次式(1)の関係が成り立つためである。

#### 【0012】

#### 【数1】

$$I_c = I_s \times \exp(qV_{be}/kT) \quad \dots (1)$$

#### 【0013】

ここで、Isは飽和電流、qは電気素量、kはボルツマン定数、Tは絶対温度である。光量が増加する際には、ベース電位151がわずかに上昇することで、ソース接地回路の出力が低下することにより、エミッタ電位152が低下する。よって、光量の変化の際には、ベース電位151にも多少の変動を生じる。今、光電変換素子10が検出すべき光量

10

20

30

40

50

の範囲が、図1において、横軸の目盛0～20であるとする。検出動作を開始する前の状態が、それよりも暗い状態（例えばほぼ遮光状態にして、横軸の目盛が-10）であった場合には、ベース電位151が不必要に低下してしまう。この状態から、再び露光状態にして光（光量は図1の横軸の目盛0～20の範囲）が照射され検出動作を開始した際には、光電流でベースに付随する容量を充電する。これにより、ベース電位151を目盛-10のベース電位151から、目盛0のベース電位151まで持ち上げる必要がある。この例のようにベース電位151の変動つまり低下分がわずかであっても、その低下分を持ち上げるためにベースに付随する容量を充電する光電流が小さい場合には、この持ち上げ動作に要する時間がかかり、光応答性が悪化してしまうという課題がある。

## 【0014】

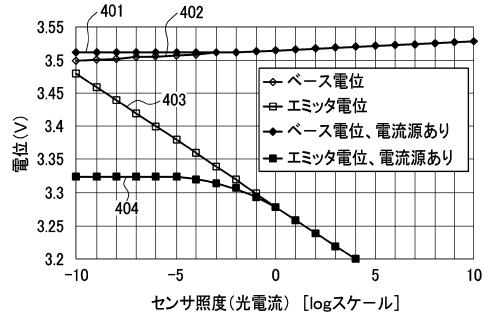

図3において、電流源110から電流を供給した場合に、それがどのように変化するかの一例を図4に示す。図4では、図1に対しての横軸と縦軸を拡大している。ベース電位402は、電流源110がない場合のバイポーラトランジスタ80のベース電位である。エミッタ電位403は、電流源110がない場合のバイポーラトランジスタ80のエミッタ電位である。ベース電位401は、電流源110を設けた場合のバイポーラトランジスタ80のベース電位である。エミッタ電位404は、電流源110を設けた場合のバイポーラトランジスタ80のエミッタ電位である。図4においては、電流源110から供給される電流値が、図4の横軸の目盛が-3相当の光量時に図3の光電変換素子10で発生する光電流値とおよそ等しい場合を表している。以下、電流源110がある時の電流-電圧特性が、図4のように変化する理由を説明する。

## 【0015】

図3において、バイポーラトランジスタ80のコレクタ電流 $I_c$ は、次式(2)で表される。

## 【0016】

## 【数2】

$$I_c = hFE \times (I_{\text{sup}} + I_p) \quad \dots (2)$$

## 【0017】

ここで、 $hFE$ はバイポーラトランジスタ80の電流増幅率、 $I_p$ は光電変換素子10の光電流、 $I_{\text{sup}}$ は電流源110の電流値である。式(1)及び式(2)から、次式(3)を導出することができる。

## 【0018】

## 【数3】

$$hFE \times (I_{\text{sup}} + I_p) = I_s \times \exp(qV_{be}/kT) \quad \dots (3)$$

## 【0019】

式(3)から、図3の光電変換素子10の光電流 $I_p$ が半分になった場合、すなわち、図4の横軸のセンサ照度が一目盛低下した場合のベースとエミッタ間の電圧 $V_{be}$ の低下量を見積もることができる。式(3)において、光電流 $I_p$ が $I_p/2$ となる場合の電圧 $V_{be}$ の低下量 $\Delta V_{be}$ は、次式(4)になる。

## 【0020】

## 【数4】

$$\Delta V_{be} = \frac{kT}{q} \times \ln \left\{ \frac{(I_p + I_{\text{sup}})}{\left( \frac{I_p}{2} + I_{\text{sup}} \right)} \right\} \quad \dots (4)$$

## 【0021】

10

20

30

40

50

式(4)において、 $I_{sup}$ が $I_p$ に対して無視できる場合、次式(5)が成立する。

【0022】

【数5】

$$\Delta V_{be} \approx \frac{kT}{q} \times \ln(2) \quad \dots (5)$$

【0023】

図4において、例えば、横軸のセンサ照度が、目盛4から3に低下する場合、式(4)において、電流 $I_{sup}$ (横軸の目盛が-3相当)は、 $I_p / 2^7$ の大きさしかないので、電流 $I_{sup}$ が無視できる。その結果、ベースとエミッタ間の電圧 $V_{be}$ の低下量 $\Delta V_{be}$ は式(5)のようになる。これは、図1の場合と同等の結果である。しかし、更に低照度の領域で、式(4)において、電流 $I_{sup}$ が無視できない領域になってくると、ベースとエミッタ間の電圧 $V_{be}$ の低下量 $\Delta V_{be}$ は、式(5)よりも小さくなってくる。すなわち、図4において、横軸のセンサ照度が一目盛低下しても、ベースとエミッタ間の電圧 $V_{be}$ があまり変化しなくなってくる。更に、低照度の領域で、式(4)において、逆に光電流 $I_p$ が電流 $I_{sup}$ に対して無視できる程度の大きさの領域においては、 $\Delta V_{be} = 0$ となって、ベースとエミッタ間の電圧 $V_{be}$ は変化しなくなる。最終的に、ベースとエミッタ間の電圧 $V_{be}$ は、式(3)から、式(6)で一定となる。

【0024】

【数6】

$$V_{be} \approx \frac{kT}{q} \times \ln\left(\frac{hFE \times I_{sup}}{I_s}\right) \quad \dots (6)$$

【0025】

このように、電流供給手段50を追加し、電流供給手段50として電流源110を用いることによって、通常、光量を検出する範囲より暗い状態から、図4の横軸の例えば目盛0にセンサ照度が変化する場合のベース電位の変化量が低減していることがわかる。これにより、ベース電位を持ち上げるために、ベースに付随する容量を充電する時間を短縮することが可能となる。よって、光応答性を向上させることが可能となる。

【0026】

以上のように、光電変換素子10の端子20に電流供給手段50として第2の電流源110を設けることにより、光量変動による端子20の電位変動を抑えることが可能となり、光応答特性の良い光電変換装置を提供することができる。

【0027】

なお、上記の説明では電流源110の電流値が、図4の横軸の目盛が-3相当の場合を例にとって説明を行った。センサで検出する最低照度が、図4の横軸の目盛0とすると、最低照度時には、電流源110から光電流の1/8の誤差電流が発生することを意味する。よって、ベース電位の低下量を減らす観点では、電流源110の電流を増加することが望ましいが、S/Nの観点では増加させすぎないことが望ましい。両者のトレードオフから、最適な電流値が決定される。

【0028】

(第2の実施形態)

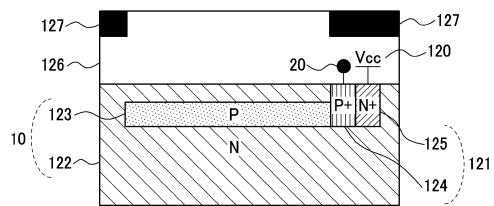

図5及び図6を用いて、本発明の第2の実施形態に係る光電変換装置について説明する。以下、本実施形態が第1の実施形態と異なる点についてのみ説明する。電流供給手段50は、ダイオード121を有する。ダイオード121は、リーケ電流により端子20に電流を供給する。また、図6に光電変換素子10とダイオード121の断面構造の例を示す。図6において、N型領域122中に、P型領域123、コンタクト部124、N型コン

10

20

30

40

50

タクト部 125 が設けられている。また、126 は層間絶縁膜、127 は遮光膜である。図 6において、N型領域 122 と P型領域 123 で光電変換素子 10 が構成されている。また、コンタクト部 124 と N型コンタクト部 125 でダイオード 121 が構成されている。コンタクト部 124 は端子 20 に接続されており、N型コンタクト部 125 は電源電圧端子 120 に接続されている。図 6 のように、コンタクト部 124 と N型コンタクト部 125 でダイオード 121 を構成することにより、電流供給手段 50 を簡便に追加することができ、省スペース化の効果が得られる。

#### 【0029】

図 6において、コンタクト部 124 と N型コンタクト部 125 は、それぞれ高濃度領域であるため、ダイオード 121 中の空乏層幅は狭くなり、高電界が印加される。電界次第では、雪崩現象によりダイオード 121 の両端子間に大きなリーク電流が発生する。よって、ダイオード 121 は、リーク電流により端子 20 に電流を供給する。10

#### 【0030】

以上のように、電流供給手段 50 としてリーク電流を供給するダイオード 121 を用いることにより、省スペース化の効果が得られる。

#### 【0031】

##### (第3の実施形態)

図 7 を用いて、本発明の第 3 の実施形態に係る光電変換装置について説明する。以下、本実施形態が第 1 の実施形態と異なる点についてのみ説明する。図 7 においては、電流供給手段 50 として、MOSFET 130 を用いている。電流出力端子 60 からの出力電流を用いて、センサ照度の検出を行う場合は、MOSFET 130 をオフにする、もしくは流れる電流値を小さくすることで、MOSFET 130 により光電変換素子 10 の光電流に重畠される誤差電流の影響を低減することができる。更に述べると、センサを用いるシステムにおいて、特定のタイミングでのみセンサ照度がセンサの光量検出範囲より低下する場合（例えば、遮光される場合）は、その時のみ、MOSFET 130 から所定の電流が供給されるようにゲート電位を駆動すればよい。20

#### 【0032】

電流供給手段 50 は、第 1 の期間には第 1 の電流値の電流を光電変換素子 10 の端子 20 に供給し、第 2 の期間には第 1 の電流値より小さい第 2 の電流値の電流を光電変換素子 10 の端子 20 に供給する又は電流を供給しない。第 1 の期間は画素信号を生成する期間であり、第 2 の期間は照度の検出を行う期間である。以上のように、電流供給手段 50 は、光電変換装置の動作状態や光量に応じて、光電変換素子 10 の端子 20 への電流供給をオフする、もしくは供給電流を小さくすることにより、誤差電流による S/N の悪化を低減することができる。30

#### 【0033】

##### (第4の実施形態)

図 7 を用いて、本発明の第 4 の実施形態に係る光電変換装置について説明する。以下、本実施形態が第 1 の実施形態と異なる点についてのみ説明する。本実施形態は、電源投入時の駆動方法に関する。図 7 において、電源を投入した際、すなわち電源電圧端子 120 の電圧を 0V から電源電圧 Vcc に設定した際に、バイポーラトランジスタ 80 のベース電位が 0V から定常電位に達するまでに長い時間を要してしまう。これは、光電流によるベースに付随する寄生容量の充電に時間がかかるためであり、低輝度時ほど光電流が小さいため、時間を要する。よって、電源投入後の一定期間にベース電位を所定の電位に持ち上げる手段を設けることが望ましい。図 7 において、電源投入後の一定期間に、MOSFET 130 のゲート電位を下げて、より大きな電流を供給することで、その役割を果たすことができる。よって、素子を追加することなく、ベース電位を持ち上げる手段を設けることができるので、省スペース化の効果が得られる。40

#### 【0034】

電流供給手段 50 は、第 1 の期間には第 1 の電流値の電流を光電変換素子 10 の端子 20 に供給し、第 2 の期間には第 1 の電流値より小さい第 2 の電流値の電流を光電変換素子50

10 の端子 20 に供給する又は電流を供給しない。第 1 の期間は電源投入後の一定期間であり、第 2 の期間は第 1 の期間の後の期間である。以上のように、電流供給手段 50 は、電源投入時に、光電変換素子 10 の端子 20 への供給電流を大きくすることにより、素子を追加することなく、ベース電位を持ち上げる手段を設けることができるので、省スペース化の効果が得られる。

#### 【0035】

##### (第 5 の実施形態)

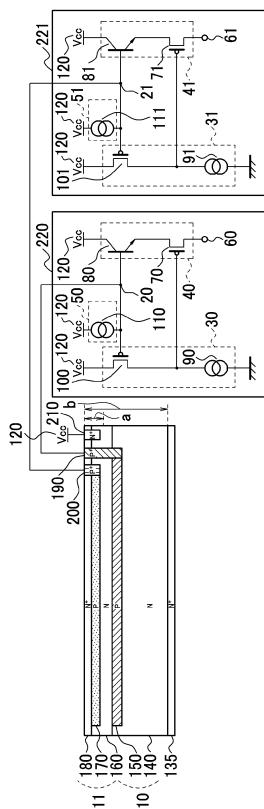

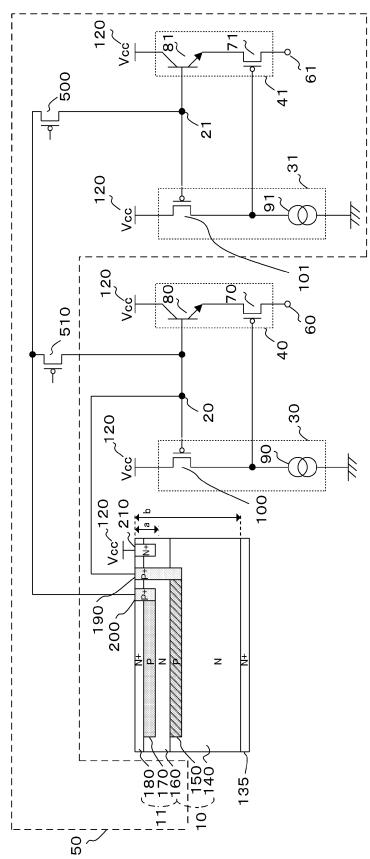

図 8 を用いて、本発明の第 5 の実施形態に係る光電変換装置について説明する。以下、本実施形態が第 1 の実施形態と異なる点についてのみ説明する。本実施形態は、深さ方向に複数の光電変換素子 10 及び 11 を積層した構成に関する。図 8 において、N<sup>+</sup>領域 135 上に、N 型領域 140、P 型領域 150、N 型領域 160、P 型領域 170、表面 N<sup>+</sup>領域 180 と、N 型領域と P 型領域が交互に積層されており、P 型領域 150 及び 170 はそれぞれ異なる深さに形成されている。シリコンに入射した光は波長の長いものほど深く侵入するので、P 型領域 150 及び 170 からは異なる波長帯域の光に対する光信号を得ることができる。このように図 8 においては、N 型領域 140、P 型領域 150、N 型領域 160 から光電変換素子 10 が、N 型領域 160、P 型領域 170、表面 N<sup>+</sup>領域 180 から光電変換素子 11 が形成されており、深さ方向に複数の光電変換素子 10 及び 11 が積層されている。P 型領域 150 及び 170 のそれぞれにコンタクト部 190 及び 200 を設けて、それぞれの光電変換素子 10 及び 11 から光電流を読み出す構成となつてあり、それぞれの光電変換素子 10 及び 11 に対して、それぞれの読み出し回路 220 及び 221 を設けている。読み出し回路 220 及び 221 は、それぞれ、図 3 の光電変換装置において光電変換素子 10 を除く構成と同じ構成を有する。それぞれの読み出し回路 220 及び 221 は、それぞれの検出手段 30 及び 31 を有しており、それぞれの定電流源 90 及び 91、及びそれぞれの MOSFET 100 及び 101 を有する。また、それぞれのフィードバック手段 40 及び 41 を有しており、それぞれの MOSFET 70 及び 71、及びそれぞれのバイポーラトランジスタ 80 及び 81 を有する。また、それぞれの電流供給手段 50 及び 51 として、それぞれの定電流源 110 及び 111 を有する。また、それぞれの電流出力端子 60 及び 61 を有する。また、図 8 においては、N 型領域 140 及び 160、表面 N<sup>+</sup>型領域 180 中に N 型コンタクト部 210 を設けて、電源端子 120 に接続している。このように、図 8 においては、光電変換素子 10 及び 11 のそれぞれに対して読み出し回路 220 及び 221 を設けて、それぞれ電流源 110 及び 111 を設けている。これにより、それぞれの光電変換素子 10 及び 11 の光応答性と S/N について最適化を行うことが可能となる。

#### 【0036】

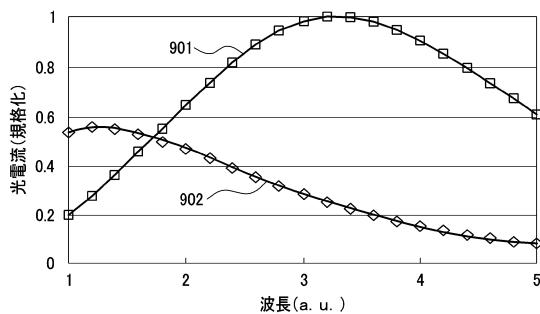

図 8 において、a は N 型領域 160 の深さ方向の不純物プロファイルのピーク位置、b は N<sup>+</sup>領域 135 上に形成された半導体層のトータルの厚さを示している。図 8 において、光電変換素子 10 及び 11 の分光特性は、主に、この 2 つのファクタ a 及び b により決まる。a と b が、ある値の場合の分光特性シミュレーション結果を図 9 に示す。図 9 において、横軸が照射光の波長、縦軸がそれぞれの光電変換素子 10 及び 11 から得られる光電流である。光電流特性 902 は波長 1 強にピークを持っている光電変換素子 11 の特性であり、光電流特性 901 は波長 3 強にピークを持っている光電変換素子 10 の特性である。図 9 のような分光特性の場合、ほとんどの分光特性の光源に対して、光電変換素子 10 は 11 よりも大きな光電流を得ることができる。よって、電流源 111 よりも電流源 110 の方がより大きな電流を設定しても、同等の S/N を得ることができる。ゆえに、電流源 110 及び 111 の電流値を個別に設定し、それぞれの光電変換素子 10 及び 11 の光応答性と S/N について最適化を行うことが可能となる。複数の電流供給手段 50, 51 のうちの一の電流供給手段 50 は、少なくとも他の一の電流供給手段 51 とは異なる電流値の電流を供給する。

#### 【0037】

光電変換素子 10, 11、検出手段 30, 31、フィードバック手段 40, 41 及び電

流供給手段 50, 51 の組みが複数設けられる。複数の光電変換素子 10, 11 は、第 1 の導電型（例えば P 型）の光電変換領域 150, 170 と、第 1 の導電型と逆の導電型である第 2 の導電型（例えば N 型）の領域 180, 160, 140 を交互に複数積層することにより、深さ方向に積層される。以上のように、深さ方向に積層したそれぞれの光電変換素子 10 及び 11 のそれぞれの端子 20 及び 21 に電流供給手段 50 及び 51 をそれぞれ設けることにより、それぞれの光電変換素子 10 及び 11 の光応答性と S/N について最適化を行うことが可能となる。

#### 【 0038 】

##### ( 第 6 の実施形態 )

図 10 を用いて、本発明の第 6 の実施形態に係る光電変換装置について説明する。以下 10

、本実施形態が第 3 の実施形態と異なる点についてのみ説明する。図 10 において、電流低下検出手段（電流検出手段）230 を設けている。電流低下検出手段 230 は、バイポーラトランジスタ 240, 250、電流源 260、コンパレータ 270、MOSFET 280, 290、及び電流源 300 を有する。また、バイポーラトランジスタ 301 及び電流出力端子 305 を有する。電流低下検出手段 230 により MOSFET 130 のゲート電位を制御することにより、光電変換装置の駆動を簡便化することが可能となる。

#### 【 0039 】

バイポーラトランジスタ 240 及び 250 のベースとエミッタ間電圧とコレクタ電流の間には第 1 の実施形態で示した式（1）の関係がある。よって、MOSFET 70 のドレイン電流より電流源 260 の電流の方が大きい場合は、コンパレータ 270 の正転端子電圧が反転端子電圧より高いため、コンパレータ 270 の出力は電源電圧レベルとなる。ゆえに、MOSFET 280 がオフ状態となるので、MOSFET 130 のゲート電位は、電流源 300 の電流値と MOSFET 290 のサイズで決まるバイアス電位に設定される。逆に、MOSFET 70 のドレイン電流より電流源 260 の電流の方が小さい場合は、コンパレータ 270 の反転端子電圧が正転端子電圧より高いため、コンパレータ 270 の出力はグランドレベルとなる。ゆえに、MOSFET 280 がオン状態となるので、MOSFET 130 のゲート電位は高くなり、MOSFET 130 のドレイン電流は低下する。MOSFET 70 のドレイン電流は、光電変換素子 10 の光電流（センサ照度）で決まるので、上記の説明より、センサ照度が一定以上の場合は、MOSFET 130 のドレイン電流が低下する。これにより、外部からの制御信号により MOSFET 130 を制御しなくても、例えばセンサが遮光された場合には、自動的に MOSFET 130 のドレイン電流を増加させる。それ以外の場合には MOSFET 130 のドレイン電流を低減し、誤差電流を低減することが可能となる。よって、光電変換装置の駆動を簡便化することが可能となる。なお、バイポーラトランジスタ 301 は、バイポーラトランジスタ 240 とカレントミラー回路を構成しており、MOSFET 70 のドレインから出力された電流をコピーし、電流出力端子 305 から出力している。

#### 【 0040 】

電流低下検出手段（電流検出手段）230 は、電流出力端子 60, 305 の電流を検出する。電流供給手段 50 は、電流低下検出手段 230 により検出される電流に応じて供給する電流値が変わる。以上のように、電流低下検出手段 230 により MOSFET 130 を制御することにより、光電変換装置の駆動を簡便化することが可能となる。

#### 【 0041 】

##### ( 第 7 の実施形態 )

図 11 を用いて、本発明の第 7 の実施形態に係る光電変換装置について説明する。以下 40

、本実施形態が第 6 の実施形態と異なる点についてのみ説明する。図 11 においては、複数の画素 310 及び 311 を有している。画素 310 及び 311 は、それぞれ、図 7 の光電変換装置と同じ構成を有する。それぞれの画素 310 及び 311 は、それぞれの光電変換素子 10 及び 11 を有している。また、それぞれの検出手段 30 及び 31 を有しており、それぞれの定電流源 90 及び 91、及びそれぞれの MOSFET 100 及び 101 を有する。また、それぞれのフィードバック手段 40 及び 41 を有しており、それぞれの MO 50

S F E T 7 0 及び 7 1、及び、それぞれのバイポーラトランジスタ 8 0 及び 8 1 を有する。また、それぞれの電流供給手段 5 0 及び 5 1 として、それぞれの M O S F E T 1 3 0 及び 1 3 1 を有する。また、それぞれの電流出力端子 6 0 及び 6 1 を有する。また、図 1 1において、最小電流検出手段 3 1 5 が設けられている。最小電流検出手段 3 1 5 は、図 1 0 の電流低下検出手段 2 3 0 と同様の構成を有し、バイポーラトランジスタ 2 4 0 及び 2 4 1 を有している。また、バイポーラトランジスタ 3 0 1 及び 3 0 2 を有している。また、電流出力端子 3 0 5 及び 3 0 6 を有している。また、M O S F E T 3 2 0 及び 3 2 1 を有している。また、電流源 3 3 0 を有している。また、M O S F E T 3 4 0 及び電流源 3 5 0 を有している。図 1 1においては、複数の電流供給手段 5 0 及び 5 1 を同一の最小電流検出手段 3 1 5 によって制御することにより、省スペース化の効果が得られる。

10

## 【0042】

図 1 1において、式(1)から、電流出力端子 6 0 及び 6 1 からの出力電流でバイポーラトランジスタ 2 4 0 及び 2 4 1 のベースとエミッタ間電圧がそれぞれ決まり、M O S F E T 3 2 0 及び 3 2 1 のゲート電位が決まる。電流源 3 3 0 の電流は、M O S F E T 3 2 0 及び 3 2 1 に流しこまれるが、M O S F E T 3 2 0 及び 3 2 1 のゲート電位差が大きい場合は、ゲート電位が大きい方のM O S F E T はゲートとソース間電圧が小さいことにより、オフ状態となる。今、仮に、M O S F E T 3 2 1 がオフ状態とし、M O S F E T 3 2 0 のゲート電位を  $V_p$  とした場合のコンパレータ 2 7 0 の反転端子電位を以下で求める。

## 【0043】

電流源 3 3 0 の電流値を  $I_a$  とし、これがM O S F E T 3 2 0 を流れる電流に等しいとすると、一般的なM O S F E T のドレイン電流の式から、次式(7)が成立する。

20

## 【0044】

## 【数7】

$$I_a \approx \frac{\beta}{2} (V_{gs} - V_{th})^2 \quad \dots (7)$$

## 【0045】

ここで、 $V_{gs}$  はM O S F E T 3 2 0 のゲート及びソース間電圧、 $V_{th}$  は閾値電圧であり、また、 $\beta$  は次式(8)の通りである。

30

## 【0046】

## 【数8】

$$\beta = \mu_0 C_{ox} \frac{W}{L} \quad \dots (8)$$

## 【0047】

ここで、 $\mu_0$  はキャリアの移動度、 $C_{ox}$  はM O S F E T の単位面積当たりのゲート容量、 $W$  はM O S F E T のゲート幅、 $L$  はM O S F E T のゲート長である。式(7)から、電圧  $V_{gs}$  は次式(9)のようになる。

40

## 【0048】

## 【数9】

$$V_{gs} \approx V_{th} + \sqrt{\frac{2I_a}{\beta}} \quad \dots (9)$$

## 【0049】

よって、コンパレータ 2 7 0 の反転端子電圧  $V_n$  は、次式(10)となる。

## 【0050】

## 【数10】

$$V_n \approx V_p + V_{th} + \sqrt{\frac{2I_a}{\beta}} \quad \cdots (10)$$

## 【0051】

図11において、この反転端子電圧  $V_n$  がコンパレータ270の正転端子電圧を下回った時に、コンパレータ270の出力は電源電圧となり、MOSFET280がオフすることにより、MOSFET130及び131のゲートにバイアス電位が与えられる。式(9)より、反転端子電圧  $V_n$  は、ゲート電位  $V_p$  により決まるので、画素310及び311の出力電流の最小値がある値を下回った時にMOSFET130及び131からバイアス電流が供給される。

10

## 【0052】

光電変換素子10, 11、検出手段30, 31、フィードバック手段40, 41及び電流供給手段50, 51の組みが複数設けられる。最小電流検出手段315は、複数の電流出力端子60, 61の電流のうちの最小値の電流を検出する。複数の電流供給手段50, 51は、最小電流検出手段315により検出される最小値の電流に応じて供給する電流値が変わる。以上のように、複数の電流供給手段50及び51を同一の最小電流検出手段315によって制御することにより、画素毎に電流検出手段を設ける必要がなくなり、省スペース化の効果が得られる。

20

## 【0053】

なお、バイポーラトランジスタ301及び302は、バイポーラトランジスタ240及び241とそれぞれカレントミラー回路を構成している。これにより、MOSFET70及び71のドレインからそれぞれ出力された電流をコピーし、電流出力端子305及び306からそれぞれ出力している。

## 【0054】

## (第8の実施形態)

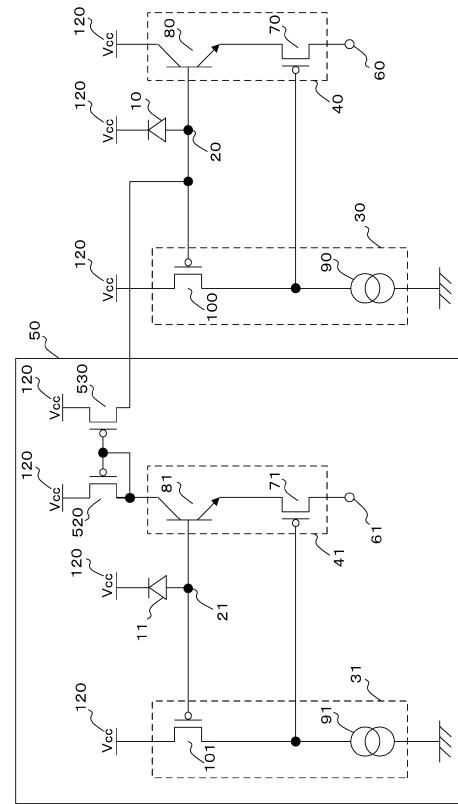

図12を用いて、本発明の第8の実施形態に係る光電変換装置について説明する。以下、本実施形態が第1の実施形態及び図8と異なる点についてのみ説明する。図12においては、電流供給手段50は、図8と同様に、第2の光電変換素子11と、第2の端子21と、第2の検出手段31と、第2のフィードバック手段41と、MOSFET500, 510とを有する。第2の光電変換素子11は、例えば第2のダイオードであり、光電変換により電流を第2の端子21に出力可能である。第2の検出手段31は、第3の電界効果トランジスタ(MOSFET)101及び第3の電流源(定電流源)91を有し、第2の端子21の電位を検出する。第2のフィードバック手段41は、第2のバイポーラトランジスタ81及び第4の電界効果トランジスタ(MOSFET)71を有する。また、第2のフィードバック手段41は、第2の検出手段31より検出された電位に基づく信号を第2の端子21にフィードバックし、第2の端子21の電位に基づく電流を第2の電流出力端子61に出力する。第2の端子21は、MOSFET101のゲート及び第2のバイポーラトランジスタ81のベースに接続される。MOSFET101は、ドレインが第3の電流源91に接続される。MOSFET71は、ソースが第2のバイポーラトランジスタ81のエミッタに接続され、ゲートがMOSFET101のドレインに接続され、ドレインが第2の電流出力端子61に接続される。第5の電界効果トランジスタ(MOSFET)500は、ドレインが第2の端子21に接続され、ソースが第2の光電変換素子(第2のフォトダイオード)のアノードに接続される。第6の電界効果トランジスタ(MOSFET)510は、ドレインが第1の光電変換素子(第1のフォトダイオード)10のアノードに接続され、ソースが第2の光電変換素子(第2のフォトダイオード)11のアノードに接続される。MOSFET500及び510は、電流加算手段であり、第2の光電変換素子11で発生する電流を用いて第1の光電変換素子10の第1の端子20へ電流を出力する。

40

50

**【0055】**

MOSFET 500をオン状態、MOSFET 510をオフ状態で動作させた場合には、光電変換素子10及び11で発生した光電流はそれぞれ、バイポーラトランジスタ80及び81で増幅され、電流出力端子60及び61から出力される。この場合に、光電変換素子10に照射されている光が、図1の横軸の目盛が-10の照度の状態から、0の照度の状態に変化した場合、光電流で端子20に付随する容量を充電する。これにより、図1のベース電位151を、目盛-10のベース電位151から、目盛0のベース電位151まで持ち上げる必要がある。これに要する時間は、端子20に付随する容量をC、ベース電位151の変化分をV、光電変換素子10の光電流をIとすると、 $C \cdot V / I$ となる。

10

**【0056】**

これに対して、MOSFET 500をオフ状態、MOSFET 510をオン状態で動作させた場合には、光電変換素子10及び11で発生したそれぞれの光電流の加算電流がバイポーラトランジスタ80で増幅され、電流出力端子60から出力される。この場合、上記と同様に、光電変換素子10及び11に照射されている光が、図1の横軸の目盛が-10の照度の状態から、0の照度の状態に変化した場合、光電変換素子10及び11の光電流で端子20に付随する容量を充電する。これにより、図1のベース電位151を、目盛-10のベース電位151から、目盛0のベース電位151まで持ち上げる。これに要する時間は、端子20に付随する容量をC、ベース電位151の変化分をV、光電変換素子10及び11の光電流とともにIとすると、 $C \cdot V / 2I$ となる。よって、充電に要する時間を、上記の場合の1/2に短縮できることができる。なお、バイポーラトランジスタ80に流れ込む光電流が2倍になるので、図1のベース電位151とエミッタ電位152は、横軸の1目盛分だけ、センサ照度の高い方へシフトするが、センサ照度の変化に対するベース電位151の変化分Vは変化しない。

20

**【0057】**

このように、電流供給手段50中の光電変換素子11から端子20へ光電流を供給することによって、光応答性を向上させることができる。

**【0058】**

また、図13は、第1のフィードバック手段40をMOSFET 70のみで構成し、第2のフィードバック手段41をMOSFET 71のみで構成した例を示す。第2の端子21は、MOSFET 101のゲート及びMOSFET 71のソースに接続される。MOSFET 101は、ドレインが第3の電流源91に接続される。MOSFET 71は、ゲートがMOSFET 101のドレインに接続され、ドレインが第2の電流出力端子61に接続される。この例においても、定電流源90とそれによって駆動されるMOSFET 100でソース接地回路を構成しており、そのMOSFET 100のゲートとソース間の電圧で、フォトダイオード10のアノード電位を定めている。光量が変化した際、MOSFET 70の電流が変化するので、そのソース及びゲート間の電圧が変化するが、光電変換素子10のアノード電位ではなく、ゲート電位が主に変動する構成となっている。光電流でバイアスされたアノードではなく、電流源90でバイアスされたMOSFET 70のゲート電位が動くようにすることで、光応答性を向上させている。この例においても、MOSFET 500をオフ状態、MOSFET 510をオン状態で動作させて、光電変換素子11から光電流を端子20に供給することで、光応答性を向上させることができる。

30

**【0059】****(第9の実施形態)**

図14を用いて、本発明の第9の実施形態に係る光電変換装置について説明する。本実施形態は、第5及び第8の実施形態を組み合わせたものである。以下、本実施形態が第5及び第8の実施形態と異なる点についてのみ説明する。図14においては、図8と同様に、光電変換素子10及び11が深さ方向に積層されている。

40

**【0060】**

MOSFET 500をオン状態、MOSFET 510をオフ状態で動作させた場合には

50

、光電変換素子10及び11で発生した光電流はそれぞれ、バイポーラトランジスタ80及び81で増幅され、電流出力端子60及び61から出力される。これにより、異なる色成分の光信号を個別に得ることができる。これに対して、MOSFET500をオフ状態、MOSFET510をオン状態で動作させた場合には、光電変換素子10及び11で発生したそれぞれの光電流の加算電流がバイポーラトランジスタ80で増幅され、電流出力端子60から出力される。このとき、得られる光信号の色成分は1つとなってしまうが、光応答性を向上させることができるとなる。

#### 【0061】

なお、図14の光電変換装置においては、異なる色成分の光電流を得る光電変換素子10及び11の光電流を加算する例を示したが、これに限られるものではない。例えば、図14の光電変換素子10及び11を複数組み有する場合には、同色の色成分の光電流を得る光電変換素子同士で光電流を加算することで、光応答性を向上させることも可能である。その場合、第1の光電変換素子10及び第2の光電変換素子11は、同色成分の光を光電変換する。

#### 【0062】

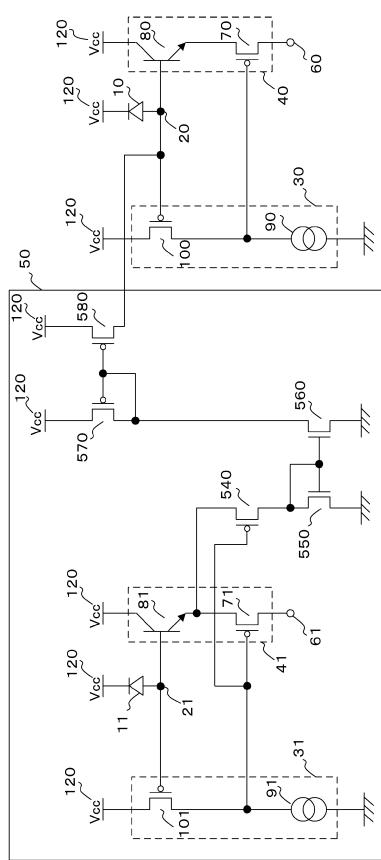

(第10の実施形態)

図15を用いて、本発明の第10の実施形態に係る光電変換装置について説明する。以下、本実施形態が第8の実施形態と異なる点についてのみ説明する。図15においては、電流供給手段50は、さらに、MOSFET520及び530を有する。MOSFET520は、ソースが電源端子120に接続され、ゲート及びドレインがバイポーラトランジスタ81のコレクタに接続される。MOSFET530は、ソースが電源端子120に接続され、ゲートがMOSFET520のゲートに接続され、ドレインが端子20に接続される。MOSFET520及び530は、カレントミラー回路を構成する。

#### 【0063】

図15において、光電変換装置は、光電変換素子11の光電流をバイポーラトランジスタ81で増幅して電流出力端子61から出力する。それとともに、光電変換装置は、MOSFET520を用いてその出力電流を検出し、MOSFET530を用いて、その出力電流に基づいた電流を生成して第1の端子20に供給する。MOSFET520及び530は、電流加算手段であり、第2の光電変換素子11で発生する電流を増幅して、第1の光電変換素子10の第1の端子20へ電流を出力する電流を生成する電流増幅手段である。このように第1の端子20に供給する電流を生成することにより、電流出力端子61からも信号電流を得ることが可能となる。つまり、端子20に付随する容量を充電する電流を増加し、光応答性を向上させることができとなる。

#### 【0064】

光電変換素子11の光電流を $I_p$ 、バイポーラトランジスタ81の電流増幅率を $hFE$ とすると、MOSFET520のドレイン電流はおよそ $I_p \cdot hFE$ となる。このとき、MOSFET530のドレイン電流 $I_d$ は、式(7)及び式(8)より、次式(11)となる。

#### 【0065】

【数11】

$$I_d \approx \frac{\beta_{530} \cdot hFE \cdot I_p}{\beta_{520}} \quad \dots (11)$$

#### 【0066】

ここで、 $\beta_{520}$ はMOSFET520の $\beta$ であり、 $\beta_{530}$ はMOSFET530の $\beta$ である。端子20に付随する容量を、光電変換素子10の光電流に加えて、MOSFET530のドレイン電流を用いて充電することにより、光応答性を向上させることができとなる。ただし、第2の光電変換素子11の感度が第1の光電変換素子10の感度よりも低く、

10

20

30

40

50

発生する光電流が小さい場合、もしくは第2の端子21に付随する容量が第1の端子20に付随する容量よりも大きい場合がある。その場合、MOSFET530の電流の立ち上がりが遅くなってしまい、光応答性向上の効果が得られない。第1の光電変換素子10の光電流による第1の端子20の充電に対して、第2の光電変換素子11の光電流による第2の端子21の充電完了が遅くなることにより、第1の端子20の充電が終わってしまってから、MOSFET530の電流が立ち上がるためである。そのため、第2の光電変換素子11の感度は、第1の光電変換素子10の感度よりも高いことが好ましい。感度は、白色光照射時に得られるトータルの光キャリア数に比例する。また、第2の端子21に付随する容量は、第1の端子20に付随する容量より小さいことが好ましい。

## 【0067】

10

なお、式(11)において、 $h_{FE}$ は、一般的には、例えば100程度の値をとるので、 $\frac{I_{530}}{I_{520}}$ を1以下の値にして、MOSFET530のドレイン電流が大きくなりすぎないように調整することが望ましい。すなわち、MOSFET520及び530の電流増幅手段は、電流ゲインが1以下であることが望ましい。これは、バイポーラトランジスタ80のエミッタ電流が大きくなりすぎることにより、バイポーラトランジスタ80のベース及びエミッタ間電圧並びにMOSFET70のゲート及びソース間電圧が大きくなりすぎて、回路の動作電圧範囲を小さくするためである。

## 【0068】

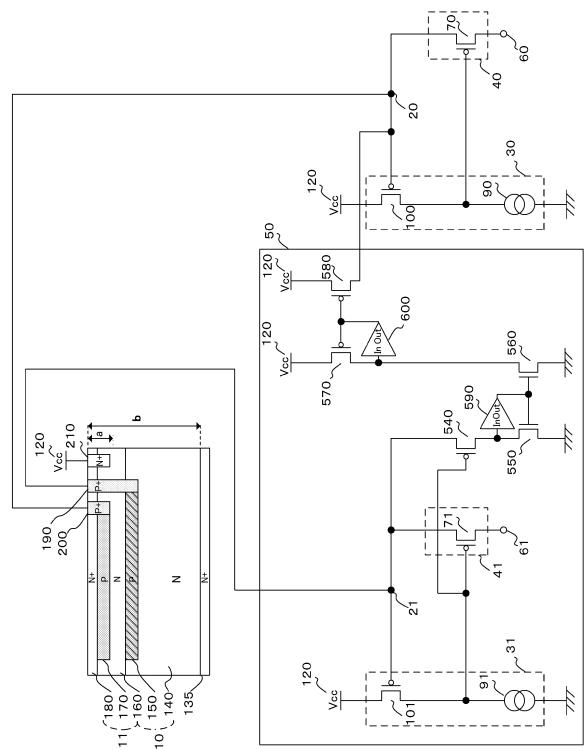

## (第11の実施形態)

20

図16を用いて、本発明の第11の実施形態に係る光電変換装置について説明する。以下、本実施形態が第10の実施形態と異なる点についてのみ説明する。図16においては、電流供給手段50は、図15のMOSFET520及び530の代わりに、MOSFET540、550、560、570、580を有する。MOSFET540は、ソースがバイポーラトランジスタ81のエミッタに接続され、ゲートがMOSFET71のゲートに接続される。MOSFET550は、ドレイン及びゲートがMOSFET540のドレインに接続され、ソースがグランド端子に接続される。MOSFET570は、ソースが電源端子120に接続され、ゲート及びドレインがMOSFET560のドレインに接続される。MOSFET580は、ソースが電源端子120に接続され、ゲートがMOSFET570のゲートに接続され、ドレインが端子20に接続される。MOSFET560は、ゲートがMOSFET550のゲートに接続され、ソースがグランド端子に接続される。MOSFET550及び560はカレントミラー回路を構成し、MOSFET570及び580もカレントミラー回路を構成する。

## 【0069】

30

図16においては、光電変換装置は、光電変換素子11の光電流をバイポーラトランジスタ81で増幅し、その一部を電流出力端子61から出力し、他の一部を用いて端子20へ出力する電流を生成している。このように端子20に供給する電流を生成することにより、バイポーラトランジスタ81の回路の動作電圧範囲を改善することが可能となる。

## 【0070】

光電変換素子11の光電流を $I_p$ 、バイポーラトランジスタ81の電流増幅率を $h_{FE}$ とすると、MOSFET71及び540のドレイン電流の合計はおよそ $I_p \cdot h_{FE}$ となる。このとき、MOSFET71及び540のゲート及びソース間電圧は等しいので、式(7)及び式(8)より、それぞれのMOSFET71及び540のが互い等しければ、MOSFET71及び540のドレイン電流は等しくなる。つまり、ドレイン電流は、それぞれ $I_p \cdot h_{FE} / 2$ となる。よって、MOSFET71により、電流出力端子61からは $I_p \cdot h_{FE} / 2$ の電流が出力される。また、MOSFET540の $I_p \cdot h_{FE} / 2$ の電流を用いて、MOSFET550、560、570、580は、端子20に出力する電流を生成する。式(7)及び式(8)より、MOSFET580の出力するドレイン電流 $I_d$ は、次式(12)となる。

## 【0071】

40

## 【数12】

$$I_d \approx \frac{\beta_{560} \cdot \beta_{580} \cdot I_p}{2\beta_{550} \cdot \beta_{570}} \quad \dots \quad (12)$$

## 【0072】

ここで、<sub>550</sub>、<sub>560</sub>、<sub>570</sub>、<sub>580</sub>は、それぞれMOSFET550、560、570、580のである。端子20に付随する容量を、フォトダイオード10の光電流に加えて、MOSFET580のドレイン電流を用いて充電することにより、光応答性向上させることが可能となる。また、図15と比較すると、図16のバイポーラトランジスタ81のコレクタ電位が図15のMOSFET520のゲートとソース間電圧分だけ高いことがわかる。バイポーラトランジスタ81を活性領域で動作させるためには、コレクタとベースが逆バイアスされている必要があり、ベース電位の上限はコレクタ電位により制限される。よって、バイポーラトランジスタ81のコレクタ電位が高い分、ベース電位をより高く設定することが可能となり、回路の動作電圧範囲を改善することが可能となる。

## 【0073】

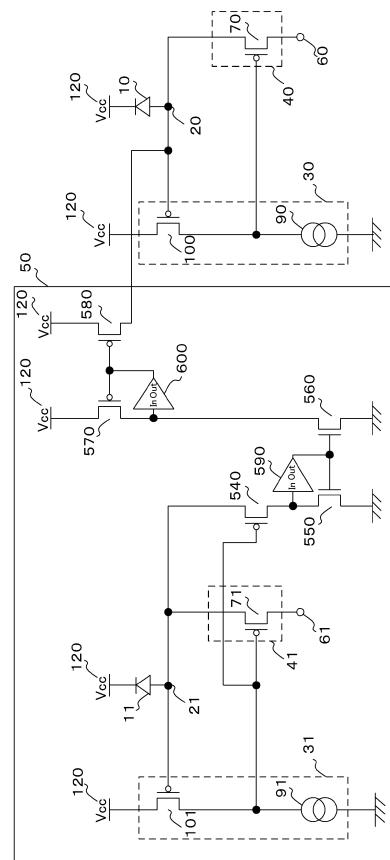

## (第12の実施形態)

図17を用いて、本発明の第12の実施形態に係る光電変換装置について説明する。以下、本実施形態が第11の実施形態と異なる点についてのみ説明する。図17においては、フィードバック手段40及び41は、それぞれ、バイポーラトランジスタ80及び81を有していない。また、電流供給手段50は、さらに電圧バッファ590及び600を有する。電圧バッファ590は、入力端子がMOSFET550のドレインに接続され、出力端子がMOSFET550のゲートに接続される。電圧バッファ600は、入力端子がMOSFET570のドレインに接続され、出力端子がMOSFET570のゲートに接続される。これらの電圧バッファ590及び600により、MOSFET550、560、570、580のゲートに付随する容量の充電にかかる時間を短縮し、光応答性を改善することが可能となる。

## 【0074】

図17においては、光電変換装置は、光電変換素子11の光電流の一部を電流出力端子61から出力し、他の一部を用いて端子20へ出力する電流を生成している。光電変換素子11の光電流をI<sub>p</sub>とすると、MOSFET71及び540のドレイン電流の合計はI<sub>p</sub>となる。このとき、それぞれのMOSFET71及び540のが互い等しければ、MOSFET71及び540のドレイン電流は等しく、I<sub>p</sub>/2となる。電圧バッファ590がない場合には、この電流でMOSFET550及び560のゲートに付随する容量を充電することになる。光電流I<sub>p</sub>が微小な場合には、その充電に時間がかかることにより、MOSFET560のドレイン電流の立ち上がりが遅れることで、MOSFET580のドレイン電流の立ち上がりが遅れてしまい、光応答性向上の妨げとなってしまう。そこで、電圧バッファ590を設けて、MOSFET550及び560のゲートに付随する容量を駆動することにより、MOSFET540のドレイン電流で充電する容量値を低減することにより、光応答性を改善することが可能となる。

## 【0075】

なお、式(12)のMOSFET580のドレイン電流は、大きいほど光応答性向上の効果を得るので、<sub>560</sub>・<sub>560</sub>/<sub>550</sub>・<sub>570</sub>を1以上として、電流を増幅して出力するのが望ましい。MOSFET540、550、560、570、580及び電圧バッファ590、600は、電流加算手段であり、第2の光電変換素子11で発生する電流を増幅して、第1の光電変換素子10の第1の端子20へ電流を出力する電流を生成する電流増幅手段である。MOSFET550、560、570、580の電流増幅手段は、上記のように、電流ゲインが1以上であることが望ましい。

## 【0076】

10

20

30

40

50

(第13の実施形態)

図18を用いて、本発明の第13の実施形態に係る光電変換装置について説明する。以下、本実施形態が第9及び第12の実施形態と異なる点についてのみ説明する。図18においては、図17と比較して、図8と同様に、光電変換素子10、11が深さ方向に積層されている点が異なる。

【0077】

図18の光電変換装置は、光電変換素子10の光電流の一部を電流出力端子61から出力し、他の一部を用いて端子20へ出力する電流を生成し、これにより光応答性を向上させている。電流出力端子60からは、光電変換素子10の光電流に基づくMOSFET580のドレン電流と光電変換素子11の光電流の加算電流が出力される。これにより、電流出力端子61からは、図9の光電流特性901を有する出力電流を得ることができ、電流出力端子60からは、図9の光電流特性901に比例する成分と光電流特性902を加算した光電流特性を有する出力電流を得ることができる。よって、図18の光電変換装置は、図14の光電変換装置と比較し、電流出力端子60及び61から異なる2つの色成分を有する出力電流を同時に得ることが可能としつつ、端子20を充電する電流を増加し、光応答性を向上させることができるとなる。

【0078】

なお、第1の電流出力端子60からの出力電流に対して、第2の電流出力端子61からの出力電流を用いて適切な差分処理を行うことにより、光電流特性901の信号成分を除去し、光電流特性902を有する信号を得ることが可能である。すなわち、第1の電流出力端子60から得られる電流に基づいた信号と第2の電流出力端子61から得られる電流に基づいた信号を用いて、差分処理を行う。

【0079】

上記の第1～第13の実施形態では、光電変換素子10及び11としてホールを集めるタイプのものを用いた場合を例にとって説明したが、これに限られるものではない。光電変換素子10及び11として電子を集めるタイプのものを用いた場合でも、同様な構成をとることにより同様な効果が得られる。

【0080】

また、上記の第1～第13の実施形態では検出手段30として、ソース接地回路を用いた場合を例にとって説明したが、これに限られるものではない。

【0081】

また、上記の第1～第13の実施形態ではフィードバック手段40として、バイポーラトランジスタ80とMOSFET70を用いた場合を例にとって説明したが、これに限られるものではない。

【0082】

また、上記の第1～第7の実施形態では電流供給手段50として、電流源110もしくはダイオード121もしくはMOSFET130を用いた場合を例にとって説明したが、これに限られるものではない。

【0083】

また、上記の第5、第9及び第13の実施形態では、深さ方向に積層した光電変換素子10及び11の数を2の場合を例にとって説明したが、これに限られるものではない。

【0084】

また、上記の第6の実施形態では、電流低下検出手段230は、図10に記載のものに限られるものではない。

【0085】

また、上記の第7の実施形態では、最小電流検出手段315は、図11に記載のものに限られるものではない。

【0086】

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものであ

10

20

30

40

50

る。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

【符号の説明】

【0087】

10、11 光電変換素子、20 端子、30 検出手段、40 フィードバック手段、

50 電流供給手段、60、61 電流出力端子

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(56)参考文献 特開2011-238856(JP,A)

特開2011-187647(JP,A)

特開2010-045294(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 31/00 - 31/02, 31/08 - 31/10, 31/18