(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4923043号

(P4923043)

(45) 発行日 平成24年4月25日(2012.4.25)

(24) 登録日 平成24年2月10日(2012.2.10)

(51) Int.Cl.

HO4N 5/232 (2006.01)

HO4N 101/00 (2006.01)

F 1

HO4N 5/232

HO4N 101:00

Z

請求項の数 16 (全 18 頁)

(21) 出願番号 特願2008-513467 (P2008-513467)

(86) (22) 出願日 平成18年3月24日 (2006.3.24)

(65) 公表番号 特表2008-543171 (P2008-543171A)

(43) 公表日 平成20年11月27日 (2008.11.27)

(86) 國際出願番号 PCT/US2006/010966

(87) 國際公開番号 WO2006/127111

(87) 國際公開日 平成18年11月30日 (2006.11.30)

審査請求日 平成21年2月3日 (2009.2.3)

(31) 優先権主張番号 11/137,303

(32) 優先日 平成17年5月24日 (2005.5.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 505001650

ゾラン・コーポレーション

Zoran Corporation

アメリカ合衆国カリフォルニア州94086

6・サニーベイル・カイファーロード 1

390

1390 Kifer Road, Sunnyvale, California

94086, U. S. A.

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100093861

弁理士 大賀 真司

(74) 代理人 100109346

弁理士 大貫 敏史

最終頁に続く

(54) 【発明の名称】引き続く画像取得の間の遅延を減らすデジタルスチルカメラ・アキテクチャ

## (57) 【特許請求の範囲】

## 【請求項 1】

デジタルカメラ内で一連の画像を処理する方法であって、

前記一連の画像内の第1画像を処理するステップであって、前記第1画像を前記デジタルカメラの統合メモリ空間に第1の順番でロードして、第2の順番で処理するステップと、

前記第1画像の処理が完了する前に、前記統合メモリ空間内の前記第1画像の少なくとも一部を、前記一連の画像内の第2画像の画像データで上書きするステップとを含み、

前記第1および第2画像は前記デジタルカメラにより連続的に取得され、

前記第1画像の画像ラインが、所定のメモリ割当てアルゴリズムに従い前記第2画像の画像ラインとは異なる仕方で前記統合メモリ空間に分散される、方法。

## 【請求項 2】

前記第1および第2画像の各々が複数の画像ラインを含み、前記画像が時間的にインターレースされた順番で前記統合メモリ空間にロードされて、論理的にプログレッシブな順番で処理される、請求項1に記載の方法。

## 【請求項 3】

前記第1画像の所定の数の画像ラインを論理的にプログレッシブな順番で処理するステップと、

前記第2画像の画像ラインを時間的にインターレースされた順番で前記統合メモリ空間にロードして、前記第1画像の処理済み画像ラインを上書きするステップと、

前記処理ステップおよびロードするステップを、前記第2画像の処理が完了するまで繰り返すステップとを更に含む、請求項1に記載の方法。

**【請求項4】**

デジタルカメラ内で一連の画像を処理する方法であって、前記デジタルカメラが画像センサを有し、前記方法が、

前記画像センサにより第1画像および第2画像を取得するステップであって、前記第1および第2画像は前記画像センサにより連続的に取得されるステップと、

前記第1画像の画像データおよび前記第2画像の画像データを前記デジタルカメラ内の統合メモリ空間に保存するステップであって、前記第1画像の処理を完了する前に前記統合メモリ空間への前記第2画像の画像データの保存を開始して、前記統合メモリ空間内の前記第1画像の画像データを前記第2画像の画像データにより少なくとも部分的に上書きすることを含むステップと、

前記画像の画像データに対し少なくとも所定の動作を実行することにより各々の画像を処理するステップであって、前記第2画像により上書きされる前に、前記第1画像の画像データに対し前記所定の動作を実行することを含むステップとを含み、

各々の画像の画像データが、前記統合メモリ空間の利用スキームに関連付けられた非連続的な順番で前記統合メモリ空間に保存され、各々の画像の画像データが、前記所定の動作を実行する際に前記統合メモリ空間から異なる順番で取り出される、方法。

**【請求項5】**

前記利用スキームが、

画像の画像ラインを時間的にインターレースされた順番で前記統合メモリ空間に保存するステップと、

前記画像の画像ラインを論理的にプログレッシブな順番で処理するステップとを含み、

前記統合メモリ空間内の画像ラインが所定のメモリ割当てアルゴリズムに従い配置されている、請求項4に記載の方法。

**【請求項6】**

前記第1画像の画像ラインが、前記所定のメモリ割当てアルゴリズムに従い、前記第2画像の画像ラインとは異なる仕方で前記統合メモリ空間内に分散されている、請求項5に記載の方法。

**【請求項7】**

デジタルカメラ内で一連の画像を処理する方法であって、前記デジタルカメラが画像センサを有し、前記方法が、

前記画像センサにより第1画像を取得するステップと、

前記第1画像の画像データを前記デジタルカメラ内の統合メモリ空間に書き出すステップと、

前記第1画像の画像データに対し第1の処理動作を実行して、前記統合メモリ空間に保存された処理済み画像データを生成するステップと、

前記画像センサにより第2画像を取得するステップと、

前記統合メモリ空間に保存された前記第1画像の処理済み画像データに対し第2の処理動作を実行するステップとを含み、

前記第1および第2画像を取得する間の取得時間間隔が、前記画像の画像データを前記画像センサから前記統合メモリ空間に書き出すための時間と、前記画像の画像データに対し前記第1および第2の処理動作を実行するための第1および第2の処理時間との合計より短く、前記統合メモリ空間に保存されている前記画像センサからの画像データの最大量が、前記第1および第2画像に関連付けられている前記画像センサからの画像データの合計量より少なく、

前記第1画像の画像ラインが、所定のメモリ割当てアルゴリズムに従い前記第2画像の画像ラインとは異なる仕方で前記統合メモリ空間に分散される、方法。

**【請求項8】**

前記第1および第2画像が、前記画像センサにより取得された一連の画像の連続的な画

10

20

30

40

50

像である、請求項 7に記載の方法。

**【請求項 9】**

前記第1および第2の画像を取得する間の取得時間間隔が、前記読み出し時間と、前記第1画像の画像データに対し前記第1の処理動作を実行するための部分的な処理時間との合計より短い、請求項 7に記載の方法。

**【請求項 10】**

前記第1画像の処理済み画像データに対する前記第2の処理動作が完了する前に、前記統合メモリ空間内の前記第1画像の画像データの一部を前記第2画像の画像データにより上書きするステップを更に含む、請求項 7に記載の方法。

**【請求項 11】**

一連の画像を処理する方法であって、

第1画像の画像データをデジタルカメラ内のメモリに保存するステップであって、前記第1画像のラインが第1の画像ライン対メモリ位置マッピングに従い前記メモリに保存されるステップと、

前記メモリからの前記第1画像の画像データを処理して処理済み画像データを生成するステップと、

前記第1画像の画像データの処理ステップに重なる時間中に、第2画像の画像データにより前記メモリ内の前記第1画像の画像データを上書きすることにより、前記第2画像の画像データを前記メモリに保存するステップであって、前記第1の画像ライン対メモリ位置マッピングとは異なる、第2の画像ライン対メモリ位置マッピングに従い前記第2画像のラインが前記メモリに保存されるステップとを含み、

前記時間中に、前記第1および第2画像の画像ラインは前記メモリ内に混在するように分散される、方法。

**【請求項 12】**

前記メモリに保存されている画像データの最大量が、前記第1および第2画像に関連付けられている画像データの合計量より少ない、請求項 11に記載の方法。

**【請求項 13】**

統合メモリ空間を収容する1個以上のメモリ素子と、

前記統合メモリ空間に第1画像の画像データを第1の順番でロードする画像前処理ユニットと、

前記統合メモリ空間内の前記第1画像の画像データを第2の順番で処理する画像処理ユニットとを含み、

前記画像処理ユニットが前記第1画像の画像データの処理を完了する前に、前記画像前処理ユニットが、前記統合メモリ空間に第2画像の画像データをロードして、前記第2画像の画像データにより前記統合メモリ空間内の前記第1画像の少なくとも一部を上書きすべく構成されており、

前記画像前処理ユニットが、第1の画像ライン対メモリ位置マッピングに従い、前記第1画像のラインを前記統合メモリ空間にロードし、前記第1の画像ライン対メモリ位置マッピングとは異なる第2の画像ライン対メモリ位置マッピングに従い、前記第2画像のラインを前記統合メモリ空間にロードすべく構成されている、デジタル画像プロセッサ。

**【請求項 14】**

前記第1画像の画像データを処理する間、前記統合メモリ空間に保存された画像データの最大量が、前記第1および第2画像に関連付けられた画像データの合計量より少ない、請求項 13に記載のデジタル画像プロセッサ。

**【請求項 15】**

ロー画像を取得する画像センサと、

処理済み画像をデジタルカメラ出力形式で保存する不揮発性記憶装置と、

前記ロー画像を処理して前記デジタルカメラ出力形式の処理済み画像に変換するデジタル画像プロセッサとを含み、

前記画像プロセッサが更に、

10

20

30

40

50

統合メモリ空間を収容する1個以上のメモリ素子と、

第1のロー画像の画像データを第1の順番で前記統合メモリ空間にロードする画像前処理ユニットと、

前記統合メモリ空間内で前記第1画像の画像データを第2の順番で処理する画像処理ユニットとを含み、

前記画像処理ユニットが前記第1画像の画像データの処理を完了する前に、前記画像前処理ユニットが、前記統合メモリ空間に第2画像の画像データをロードし、前記第2画像の画像データにより前記統合メモリ空間内の前記第1画像の少なくとも一部を上書きすべく構成されており、

前記画像前処理ユニットが、第1の画像ライン対メモリ位置マッピングに従い、前記第1画像のラインを前記統合メモリ空間にロードし、前記第1の画像ライン対メモリ位置マッピングとは異なる第2の画像ライン対メモリ位置マッピングに従い、前記第2画像のラインを前記統合メモリ空間にロードすべく構成されている、デジタルカメラ。10

#### 【請求項16】

前記デジタル画像プロセッサの動作中のあらゆる時点において、前記統合メモリ空間に保存された画像データの最大量が、前記第1および第2画像に関連付けられた画像データの合計量より少ないと、請求項15に記載のデジタルカメラ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

20

##### 発明の分野

本発明は一般にデジタルカメラに関し、特に性能が向上したデジタルカメラのアーキテクチャに関する。

##### 【背景技術】

##### 【0002】

##### 発明の背景

デジタルカメラは、人気の高い消費者向け電子装置である。従来のカメラとは異なり、デジタルカメラは「画像センサ」と呼ばれる電子素子を用いて画像を取得する。画像センサにより取得された画像は、次いでデジタル化されてメモリ素子にロードされる。デジタルカメラは、メモリ素子内のデジタル画像に対し、例えばノイズ抑制、色補正等の各種の画像処理技術を適用する。最後に、処理済み画像は特定の形式を有するファイルに圧縮されて、パソコン（P C）、携帯情報端末（P D A）、またはプリンタ等の他の電子装置により後で利用すべく、不揮発性記憶装置に保存される。30

##### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0003】

デジタルカメラの性能評価に用いるパラメータとしてクリック間隔（c l i c k - t o - c l i c k time）があり、これはデジタルカメラのシャッターボタンを2回連続的に押下する間に要する最短の時間の長さを測定することである。クリック間隔が短いほど、一定時間内により多くの画像をデジタルカメラが撮影することができる。クリック間隔が短いデジタルカメラは、ハイエンドのモーター付フィルム・カメラの動作と同様に、一連の画像を素早く連続的に撮影することができる。デジタルカメラのクリック間隔に影響を及ぼす要因には、自身のメモリのサイズおよびカメラの画像センサにより取得された画像に対し実行される各種の画像データ処理手順の速度が含まれる。本発明の目的の一つは、クリック間隔が短縮され、従って性能が向上したデジタルカメラを提供することである。40

##### 【課題を解決するための手段】

##### 【0004】

##### 概要

一連の画像の第1の画像を、当該第1画像の部分をデジタルカメラの統一メモリ空間内

50

へ第1の順番で(*in a first order*)ロードして、これらの部分を第2の順番で(*in a second order*)処理することにより、取得するデジタルカメラを提供する。第1画像の処理が完了する前に、デジタルカメラは第2画像の取得を開始して、統合メモリ空間内の第1の画像の少なくとも処理済み部分を第2画像の画像データで上書きする。

#### 【0005】

いくつかの実施形態において、デジタルカメラは第1画像および第2画像を画像センサで取得する。第1および第2画像の画像データは、デジタルカメラ内の統合メモリ空間に保存される。詳細には、デジタルカメラは、第1画像の処理を完了する前に第2画像の画像データを統合メモリ空間内に保存する。従って、第2画像の画像データは、統合メモリ空間内の第1画像の画像データを少なくとも部分的に上書きする。

10

#### 【0006】

いくつかの実施形態において、デジタルカメラは画像センサにより第1画像を取得し、画像センサから第1画像の画像データをデジタルカメラ内のメモリへ読み込んで、第1画像の画像データをデジタルカメラ出力形式に変換する。デジタルカメラは、第1画像を処理しながら同時に画像センサにより第2画像を取得し始める。その結果、クリック間隔は、画像センサから画像の画像データを読み出すための読み出し時間(*readout time interval*)と、画像の画像データをデジタルカメラ出力形式に変換するための変換時間との合計より短い。デジタルカメラが動作中のあらゆる時点において、メモリに保存されている画像データの最大量は、第1および第2画像に関連付けられた画像データの合計量より少ない。

20

#### 【0007】

図面の複数の図にわたって同一番号は対応部材を指す。

#### 【発明を実施するための最良の形態】

#### 【0008】

##### 実施形態の説明

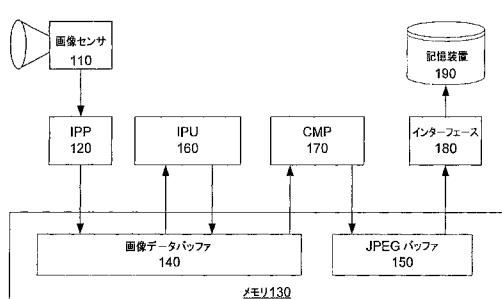

図1Aは、先行技術のデジタルカメラの動作を示すデータフロー図である。ユーザーがシャッターボタンを押したならば、光がカメラのレンズを通って入射され、画像センサ110に到達する。露光時間が終了した後で、画像センサ110においてロー画像(*raw image*)が形成される。画像センサ110において形成されたロー画像は通常、RGBカラー領域にある。RGBカラー領域からYUVカラー領域へ画像を変換するために後続の画像処理手順を必要とする。YUV画像データに対して通常は画像処理および圧縮動作が実行されるため、画像センサからのRGB画像データをYUV画像データに変換する必要がある。

30

#### 【0009】

画像前処理ユニットIPP120が、画像センサ110からロー画像データを読み出して、当該データを画像データバッファ140に保存する。いくつかの実施形態において、統合メモリ空間(画像データバッファ140およびJPEGバッファ150を含む)を収容する(host)メモリ130は、単一の電子デバイス(例:32MBのDRAM)である。他のいくつかの実施形態において、メモリ130は複数のデバイスを含んでいる。いずれの場合も、メモリ130を統合メモリ空間として扱うことができる。下記でより詳述するように、統合メモリ空間はまた、もう1つのYUVバッファおよびJPEGバッファのように、デジタルカメラ内の他のバッファを実装するためにも用いる。

40

#### 【0010】

画像データバッファ140へのロー画像データの保存が完了した後で、画像処理ユニットIPU160はロー画像データを、保存および表示に適したデジタルカメラ出力形式に変換すべく一連の処理手順を適用し始める。処理手順は、デジタルカメラ設計に熟練した技術者には公知である。説明の便宜上、以下の説明はRGBカラー領域からYUVカラー領域に画像データを変換する手順に限定する。しかし、当業者には本発明がデジタルカメラに実装される特定の画像処理手順に依存していないことが理解されよう。デジタルカメラ出力形式は、デジタルカメラに関連付けられた不揮発性記憶装置に保存される処理済み

50

デジタル画像のデータ形式である。デジタルカメラ出力形式の例として J P E G 画像標準がある。しかし、権利保護されたものを含む他の画像形式を用いてもよい。不揮発性記憶装置は、フラッシュメモリカード、光、磁気または他の任意の種類のデジタル記憶媒体の形式であってよい。不揮発性記憶装置は、メモリカードやスティック等、着脱可能なメモリ素子であっても、あるいはデジタルカメラと一体化された部分であってもよい。

#### 【 0 0 1 1 】

理想的には、巨大な画像データバッファの方がデジタルカメラの性能を向上させることができる。しかし、画像データバッファ 1 4 0 のサイズには実際的な限度がある。例えば、画像センサにより生成された画像が 8 M ピクセルを有して各ピクセルが 2 バイトに対応している場合、画像データバッファのサイズは少なくとも 1 6 M B である。他の目的で予約されているメモリ空間を除外した後で、3 2 M B D R A M に残った空きスペースは 1 個の画像しか収容することができない。より大きい容量、例えば 6 4 M B D R A M のメモリ素子を用いて、このスペース制約を解決することは技術的には可能であるにもかかわらず、そのようなメモリ素子のコストが高いことは経済的に魅力を欠いている。従って、Y U V カラー領域内の処理済み画像は、R G B カラー領域のロー画像を上書きして画像データバッファに保存する必要がある。図 1 B との関連で以下に明らかになるように、この要件はクリック間隔の短縮にとって重大な障壁となる。

#### 【 0 0 1 2 】

画像を処理した後で、デジタルカメラは通常、画像圧縮ユニット C M P ( 圧縮プロセッサとも呼ばれる ) 1 7 0 を用いて処理済み画像を圧縮して、不揮発性記憶装置 1 9 0 、例えばフラッシュメモリカード上での自身のサイズを縮める。関連技術領域には多くのよく知られた画像圧縮技術がある。これらは、画質をほとんど損なうことなくデジタル画像のサイズを大幅に縮めることができる。以下の記述では説明の便宜上 J P E G スキームを用いる。しかし、本発明があらゆる特定のデータ圧縮技術に依存しないことは当業者に理解されよう。

#### 【 0 0 1 3 】

画像を圧縮するには、C M P 1 7 0 は画像データバッファ 1 4 0 から処理済み画像を取り出して、J P E G 形式のファイルに変換し、当該ファイルを J P E G バッファ 1 5 0 に保存する。ある種のデジタルカメラは固定画像圧縮比 ( 例えば 4 : 1 ) を有し、J P E G バッファのサイズは従って固定値である。しかし、他のデジタルカメラでは、異なる画像に対して異なる圧縮比をユーザーが選択できるようにする。この場合、J P E G バッファのサイズはユーザーが選択した圧縮比に応じて動的な値である。

#### 【 0 0 1 4 】

最後に、J P E G 形式ファイルの形式で圧縮された画像は、インターフェース 1 8 0 を介して記憶装置 1 9 0 に保存される。後で、当該デジタルカメラを P C 等、他の装置に接続することができ、J P E G 形式ファイルは次いで、デジタルカメラから当該装置へ転送することができる。

#### 【 0 0 1 5 】

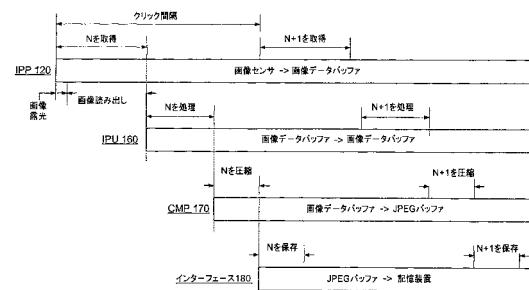

図 1 B は、先行技術のデジタルカメラの動作を異なる視点から示す時系列図である。I P P 1 2 0 は、画像センサ 1 1 0 から一連のロー画像を取得し、1 個ずつ画像データバッファにロードする。2 個の画像 N および N + 1 が必ずしも画像センサにより取得された連続する 2 個の画像とは限らない点に注意されたい。むしろ画像 N および N + 1 は、I P U 1 6 0 により連続的に処理される 2 個の画像を表わす。画像 N および N + 1 を取得するための画像取得間隔 ( the image acquisition interval ) の開始時刻間の時間間隔をデジタルカメラのクリック間隔として定義する。画像取得の時間間隔は更に、画像露光時間と、それに続く画像センサから画像データバッファへの画像読み出し時間に分割することができる。

#### 【 0 0 1 6 】

図 1 B に示すように、I P U 1 6 0 は、画像データバッファへのロードが完了した後で画像 N の処理を始める。当該処理は、ロー画像を R G B カラー領域から Y U V カラー領域

10

20

30

40

50

に変換するものである。画像データバッファがロー画像および処理済み画像の両方を同時に収容するのに十分なスペースを有していないため、処理済み画像はロー画像が占有していたのと同じスペース（または同じスペースの少なくとも一部）を占有する。

#### 【0017】

次に、CMP170は1セクションずつ新規の画像Nを圧縮して、各々の圧縮されたセクションをJPEGバッファに移動することを始める。画像圧縮の終了時点で、デジタルカメラ内に共存する画像Nの2個の複製、画像データバッファ内の圧縮されていない複製、およびJPEGバッファ内の圧縮された複製が存在している。画像圧縮が完了された後でのみ、ユーザーはデジタルカメラのシャッターボタンを押下して画像N+1を再び取得することができる。換言すれば、先行技術のデジタルカメラのクリック間隔は概ね、画像Nを取得するための時間間隔、画像Nを処理するための時間間隔、および画像Nを圧縮するための時間間隔の合計である。10

#### 【0018】

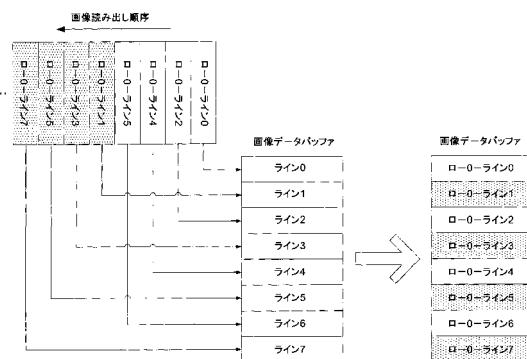

画像センサにより取得された画像は、数百または数千もの画像ラインを含み得る。説明の便宜上、図1Cに示すロー画像は、8本の画像ライン、すなわちライン0～ライン7のみを含んでいる。8本の画像ラインは通常、2個のフィールドに分類され、例えば4本の偶数ラインが1個のフィールドに対応し、4本の奇数ラインが他のフィールドに対応している。プログレッシブな順番で(in a progressive order)ロー画像ラインを読み出すべく設計された画像センサもあるが、現在利用可能な多くの画像センサは、インターレースされた順番で(in a interlaced order)ロー画像ラインを読み出すべく設計されている。20。換言すれば、最初に偶数画像ライン0、2、4、6が読み出されて画像データバッファ内のライン0、2、4、6にロードされ、次いで奇数画像ライン1、3、5、7が読み出されて各々画像データバッファ内のライン1、3、5、7にロードされる。その結果、ロー画像の8本の画像ラインは、物理的にプログレッシブな順番で画像データバッファに保存される。本構成の利点は、後続の画像処理および画像圧縮手順の多くがプログレッシブな順番で進む必要があるため、これらが容易に行なえる点である。

#### 【0019】

画像センサは、理想的な記憶装置ではない。ロー画像が画像センサにより取得されたならば、情報の喪失を避けるべく所定時間内に画像データバッファにロードされなければならない。デジタルカメラが同時に2個以上のロー画像を収容できるマルチ画像データバッファを有する場合、ロー画像を処理してデジタルカメラ出力形式に変換する動作を、画像センサからロー画像を取得して読み出す動作から分離することができる。その際に、以前に取得された画像がまだ処理中である状態で、後で取得したロー画像を同じ画像データバッファ内に保存することができる。上述のように、このマルチ画像データバッファは、デジタルカメラのコストを大幅に上昇させる恐れがある。このため、多くのデジタルカメラは、1個のロー画像しか収容できない画像データバッファを含み、従ってクリック間隔は長いものとなる。30

#### 【0020】

再び図1Cを参照すると、先行技術のデジタルカメラの限界の原因を、ロー画像の画像ラインが物理的にプログレッシブな順番で画像データバッファに保存されるのが最適であるとする不必要的仮定に帰することができる。実際には、画像ラインは時間的にインターレースされた順番で(in a temporally interlaced order)画像データバッファにロードされる一方、画像データバッファ内の画像ラインは物理的にプログレッシブな順番で処理される（すなわち、画像ラインはそれらが処理されるのと同じ順番で画像バッファ内において物理的に順番付けられている）。従って、画像N+1の第1の奇数ライン（ライン1）を配置する前に、画像N+1の全ての偶数ライン（0、2、4、6）は、画像データバッファ内でそれらの対応する位置に配置されていなければならない。しかし、画像バッファの画像Nの最後の偶数ラインが処理されてデジタルカメラ出力形式に変換され、従って上書き可能になるまで、画像バッファには画像N+1の最後の偶数ラインのためのスペースが無い。その結果、ユーザーは、画像データバッファ内の画像Nの全ての画像ラインの4050

処理および圧縮が完了するまで、次の画像の撮影することができない。後述するように、画像処理ユニットが、画像データバッファ内のロー画像の画像ラインが物理的にプログレッシブな順番で保存されていなくても、それらをプログレッシブな順番で見つけられる位置を認識していれば、対応するデジタルカメラのクリック間隔を短縮することができる。

#### 【0021】

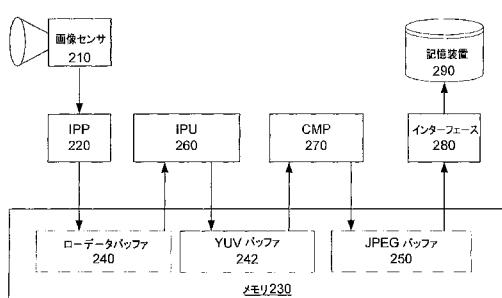

図2A～2Dに、本発明の第1実施形態によるデジタルカメラの動作を示す。特に、図2Aはデジタルカメラのデータフロー図を表す。図1Aのデータフローと比べて大きく異なるのは、画像データバッファ140が2個の構成要素、すなわちデータバッファ240およびYUVバッファ242に分けられる点である。IPP220は、画像センサ210からロー画像を読み込んで、1フィールドずつ、且つ1ラインずつインターレースされた順番でローデータバッファ240にロードする。図1Aとは異なり、ロー画像ラインは物理的にプログレッシブな順番でローデータバッファに保存する必要がない。むしろ、各々のロー画像ラインは、所定のメモリ割当てアルゴリズムに従ってローデータバッファの特定の位置に保存される。同じアルゴリズムがIPU260にも実装されていて、ローデータバッファ240内でロー画像のラインを見つけられる位置を認識しており、それらを論理的にプログレッシブな順番で（すなわち、ローデータバッファ240内におけるこれらの画像ラインの物理的な保存位置とは無関係に、画像の第1画像ラインから最終ラインへ）処理する。

#### 【0022】

更に、処理済み画像がロー画像を上書きする先行技術のデジタルカメラとは異なり、第1実施形態によるデジタルカメラは、処理済み画像をYUVバッファ242に保存する。CMP270は、YUVバッファ242から処理済み画像を取り出してJPEG形式ファイルに圧縮し、当該ファイルをJPEGバッファ250に保存する。YUVバッファがメモリ230内の動的オブジェクトである点に注意されたい。その位置およびサイズは、メモリ230の総容量、ローデータバッファ240のサイズ（画像センサの画像サイズの関数である）、およびJPEGバッファのサイズ（画像圧縮比の関数である）に依存する。説明の便宜上、以下の議論ではメモリ230が32MBDRAM、画像センサの画像サイズは7Mピクセルであって、各ピクセルは2バイトに対応するものと仮定する。従ってロー画像のサイズは約14MBである。

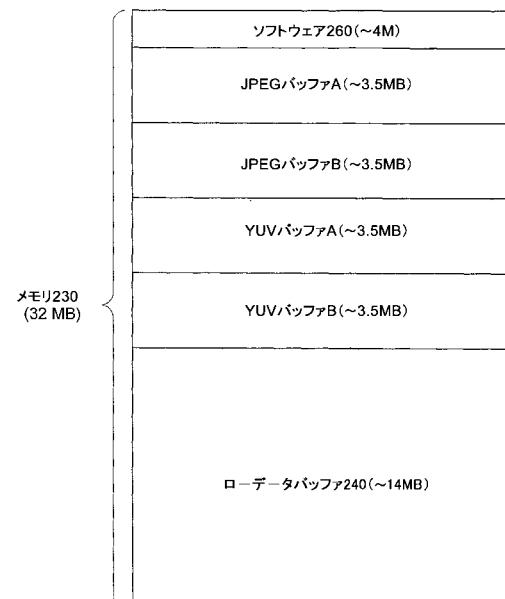

#### 【0023】

図2Bは、画像圧縮比が2対1の場合での利用に適した32MBDRAMのメモリ空間割当て図の例である。特に、約4MBのメモリ空間は、各種のソフトウェア260（画像処理手順を含むがこれに限定されない）を収容すべく予約されている。ローデータバッファ240は、1個のロー画像を収容するために、約14MBである。画像圧縮比が2：1であるため、JPEGバッファは約7MBである。いくつかの実施形態において、7MBのメモリ空間は、性能を向上させるべく2個の部分AおよびBに区切られていて、各部分が約3.5MBのメモリ空間を有する。DRAM内の残りの空きスペースは約7MBであり、これが2個のYUVバッファAおよびBに区切られていて、各々が約3.5MBのメモリ空間を有する。

#### 【0024】

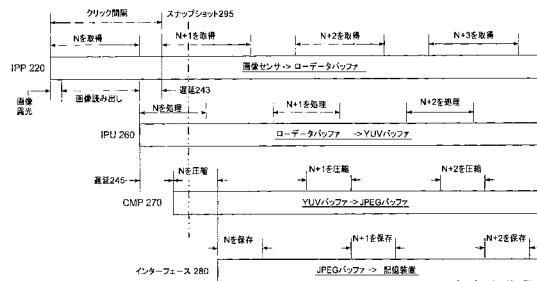

図2Cは、本発明の第1実施形態に従い、デジタルカメラの異なる構成要素が並列に動作する様子を示す時系列図である。IPU260は、ローデータバッファへのロードが完了した直後に画像Nの処理を開始する。同様に、圧縮画像は、JPEGバッファへのロードが完了した直後にインターフェース280を介して記憶装置へ送られる。しかし、図2Cに示すデジタルカメラと、図1Bに示す先行技術のデジタルカメラとの間にはいくつかの顕著な違いがある。

#### 【0025】

画像センサが、CMP270が画像Nの圧縮を完了するまで、画像N+1を取得する前に待たなくてよい点を図2Cが示すことに注意すべきである。これに関して、画像センサはIPU260が画像Nの処理を完了するまで待つ必要すらない。二つの時間遅延243

10

20

30

40

50

、245は、IPU260が処理画像Nを開始した直後、更にはCMP270が画像Nの圧縮を開始する前に、画像センサが画像N+1の取得を開始することを示す。時間遅延243は、画像センサからの画像読み出しの終了と次の画像取得動作の開始までの期間を表わす。時間遅延245は、画像センサからの画像読み出しの終了と画像圧縮の開始までの、画像処理時間の部分を表わす。その結果、図2Cに示すクリック間隔は、画像Nを取得するための時間間隔、画像Nを処理するための時間間隔、および画像Nを圧縮するための時間間隔の合計より大幅に短い。いくつかの実施形態において、時間遅延243は非常に短く、クリック間隔は画像Nを取得するための時間間隔の105%を超えない。他の実施形態において、クリック間隔は画像Nを取得するための時間間隔の110%を超えず、また別の実施形態においてクリック間隔は画像Nを取得するための時間間隔の120%を超えない。従って、図2Cに示すデジタルカメラは、図1Bに示すデジタルカメラよりも優れたクリック間隔性能を有する。10

#### 【0026】

画像センサが画像N+1を取得するのに、画像Nの処理の完了を待たなくてもよい理由が、少なくとも二つ存在する。第1に、本発明の第1実施形態によるデジタルカメラは、ロー画像の画像ラインがローデータバッファ内で物理的にプログレッシブな順番で保存されることを必要としない。図4Aとの関連において以下に示すように、異なるロー画像の同一画像ラインが、ローデータバッファ内の異なるライン（すなわち記憶場所）に保存することができる。第2に、処理済み画像ラインはローデータバッファではなく、別個のYUVバッファに保存される。ローデータバッファ内のRGB形式の画像ラインをYUVバッファ内のYUV形式の画像ラインに変換した後で、IPU260は直ちに、RGB形式の画像ラインがIPP220のために占有していたスペースを、画像N+1に関連付けられた次に入来する画像ラインをロードすべく開放する。その間、IPU260はローデータバッファ内のロー画像ラインの空間的な順番（the spatial order）を認識し、従って、論理的にプログレッシブな順番で取りだして処理する仕方を認識する。図2Cはまた、IPU260が画像Nの処理を終える前に、CMP270が画像Nの圧縮を開始できることを示唆する。より具体的には、YUVバッファ内に十分な数の処理済み画像ラインがある場合はいつでも、CMP270が画像の圧縮を開始する。20

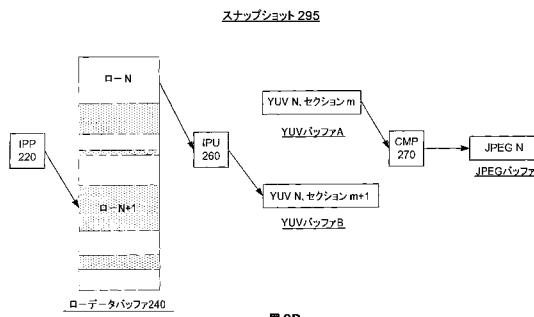

#### 【0027】

図2Dは、本発明の第1実施形態によるデジタルカメラのメモリ使用の概念図またはスナップショット295である。ロー画像Nの画像ラインがローデータバッファ240内にある程度のメモリ空間を占有し、ロー画像N+1の画像ラインがローデータバッファ240内の別のメモリ空間を占有する点に注意されたい。ロー画像Nおよびロー画像N+1のいずれもローデータバッファ240の連続する領域を占有しない。ローデータバッファ240の容量が2個の完全な画像を収容するのに十分大きくないため、ローデータバッファ240内の画像ラインは、ロー画像NおよびN+1の各々の部分を構成するに過ぎない。ロー画像Nと共に存するために、ロー画像N+1の画像ラインは、ロー画像Nの処理済み画像ラインのいくつかを上書きする必要がある。従って、デジタルカメラが動作中であるときはいつでも、ローデータバッファ240に保存されている画像データの最大量は、（A）ロー画像Nに関連付けられた画像センサからの画像データの量、および（B）ロー画像N+1に関連付けられた画像センサからの画像データの量、のうち大きい方の量を超えない。3040

#### 【0028】

IPP220は、画像N+1のインターレースされた画像ラインを、所定のメモリ割当てアルゴリズムに従いローデータバッファの特定の領域にロードする。同時に、IPU260は、同じアルゴリズムに従い、画像Nの画像ラインをローデータバッファから論理的にプログレッシブな順番で取り出し、次いで画像Nの処理済み画像ラインをYUVバッファBへ転送し、CMP270はYUVバッファA内の画像Nの処理済み画像ラインを圧縮し、圧縮されたバージョンをJPEGバッファに保存する。

#### 【0029】

50

上述のように、メモリ内のYUVバッファの存在およびその正確なサイズに影響を及ぼす複数の要因がある。画像センサの画像サイズが大き過ぎるか、または画像圧縮比が小さ過ぎる場合、デジタルカメラ内のメモリはYUVバッファ用の空きスペースを全く有していない場合がある。上述のように、別個のYUVバッファは、第1実施形態によるデジタルカメラの性能を向上させる理由の一つに過ぎない。メモリ内に別個のYUVバッファが存在しない場合でも、デジタルカメラのクリック間隔を短縮させることは依然として可能である。図3A～3Cに、本発明の第2の実施形態によるそのようなデジタルカメラの動作を示す。

### 【0030】

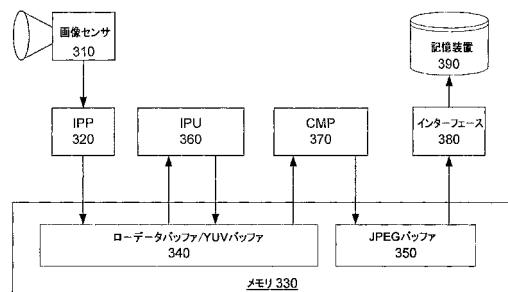

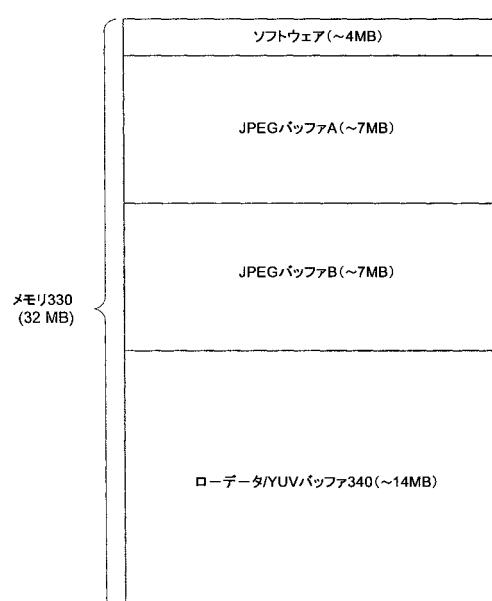

メモリ330が依然として32MBDRAMであり、画像センサの画像サイズは依然として7Mピクセルであって、従って各ピクセルが2バイトに対応する場合は14MBである、と仮定する。しかし、画像圧縮比は、今回は1:1である。換言すれば、処理済み画像は最適な解像度を実現するために本実施形態に従って圧縮されていない。従って、メモリ330内には別個のYUVバッファ用の空きスペースが存在しない。YUVバッファおよびローデータバッファは、メモリ330内の1個のバッファ340に統合される(3A図および3B)。その結果、本実施形態におけるIPU360は、IPU360によりYUVデータが生成されるにつれてロー画像データをYUVデータで上書きすべく構成されている。

### 【0031】

本構成は、一点において図1Aに示す先行技術のデジタルカメラに類似している。すなわち、画像センサが次の画像を取得する前に、処理済み画像の少なくとも一部がJPEGバッファに移動されるのを待つ必要がある。この理由は、処理済み画像ラインが、対応するロー画像ラインが以前に占有していたバッファ340の同じ位置に保存されるためである。しかし、図3C、Dとの関連で以下に示すように、画像センサは次の画像を取得する前に、JPEGバッファへの画像Nの移動が完了するのを待つ必要はない。その結果、本発明の第2の実施形態によるデジタルカメラのクリック間隔もまた、画像Nを取得するための時間間隔、画像Nを処理するための時間間隔、および画像Nを圧縮するための時間間隔の合計より短い。

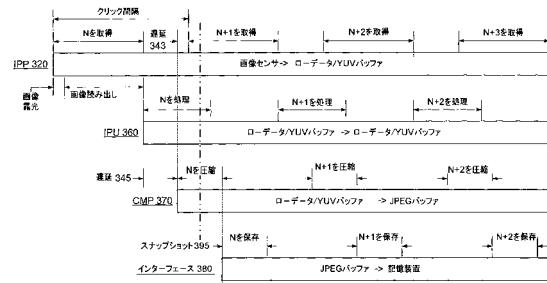

### 【0032】

図3Cに示すように、画像Nの処理開始時点および画像Nの圧縮開始時点からの時間遅延345が存在する。この時間遅延は、IPU360が、CMP370の動作を可能にすべく十分な数の処理済み画像ラインをバッファ340に蓄積するために必要である。同様に、画像Nの圧縮開始時点と画像N+1の取得開始時点との間に時間遅延343が存在する。この時間遅延は、CMP370が十分な数の画像ラインを圧縮してJPEGバッファに移動させて、その後に、画像センサが次の画像N+1のロードを開始するのに十分な空間がバッファ340にあるようにするために必要である。次の画像のロードを開始する前に圧縮する必要がある画像ラインの数は、利用する圧縮方法により決定することができ(例えば、圧縮ユニットCMP370は一度に8、16または32ラインの画像データのストリップを圧縮することができる)、画像ラインのこの組は画像ラインのストリップまたはブロックと呼ばれる場合がある。いくつかの実施形態において、時間遅延343、345は極めて短く、クリック間隔は画像Nを取得するための時間間隔の115%を超えない。

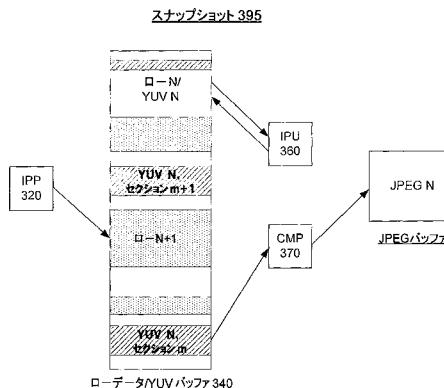

### 【0033】

図3Dに示すスナップショット395は、本発明の第2の実施形態によるデジタルカメラの動作をより直観的に示す。バッファ340内に3種類の画像データ、すなわちロー画像N+1、ロー画像N、および処理済み画像N(図3Dに「YUV N」で表わす)が存在する点に注意されたい。IPU360がロー画像Nの画像ラインを連続的に処理してそれらをRGBカラー領域からYUVカラー領域に変換する間、CMP370は画像Nの以前に処理されたYUV形式画像ラインをバッファ340からJPEGバッファへ転送する。同時に、IPP320は、ロー画像N+1の画像ラインをバッファ340ヘロードして

10

20

30

40

50

、バッファ340から既に取り出された画像Nの以前に処理された画像ラインのいくつかを上書きする。3個の構成要素、IPP320、IPU360、およびCMP370が互いに並列に動作可能である理由は、それらが全て所定のメモリ割当てアルゴリズムに従っているため、バッファ340内で次の画像ラインを取り出すおよび／または上書きする位置を認識しているためである。デジタルカメラのこれらの異なる構成要素は、バッファ340の利用を最適化すべく所定の仕方で速度調整されている(paced)。

#### 【0034】

上述のように、IPP320は画像センサからのロー画像を読み出してインターレースされた順番でローデータバッファにロードし、IPU360はロー画像を処理して論理的にプログレッシブな順番でRGBカラー領域からYUVカラー領域に変換する。デジタルカメラのクリック間隔を短縮するために、IPP320およびIPU360の両方とも同じ所定のメモリ割当てアルゴリズムに従っている必要があり、それによって、IPP320がローデータバッファ内で次の空きバッファラインが存在する位置を認識し、IPU360が処理すべき次のロー画像ラインを取りだす位置を認識する。10

#### 【0035】

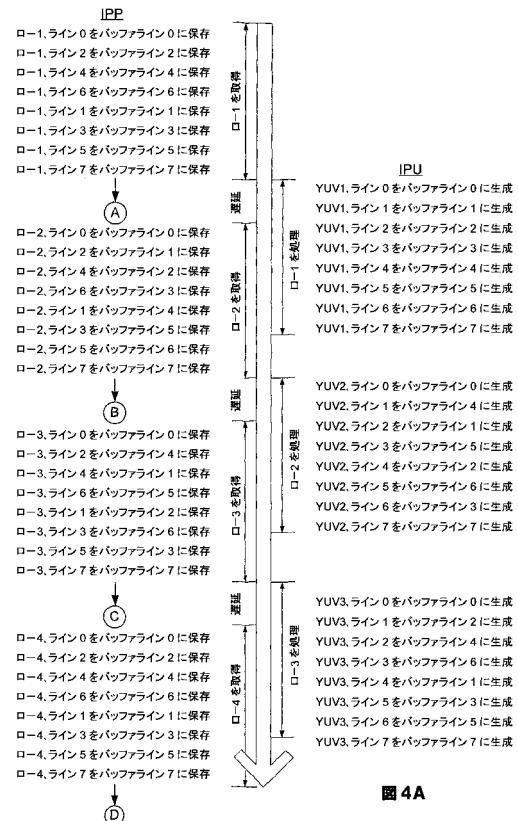

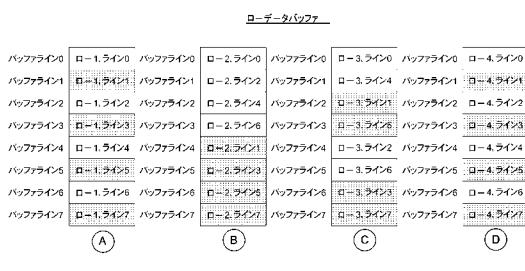

図4Aおよび4Bに、本発明のいくつかの実施形態による画像前処理ユニットおよび画像処理ユニットの並列動作を可能にするメモリ割当てアルゴリズムの例を合わせて示す。この特定のケースにおいて、デジタルカメラ内にYUVバッファとローデータバッファが別々にあると仮定する。更に、画像センサにより取得された各々のロー画像には説明の便宜上8本の画像ラインしか存在せず、当該8本の画像ラインは2つのフィールドすなわち偶数フィールド(ライン0、2、4、6を含む)と奇数フィールド(ライン1、3、5、7を含む)に分けられていると仮定する。20

#### 【0036】

本アルゴリズムによれば、ローデータバッファ内の1個の特定のバッファラインが現在ロー画像Nの画像ライン $L_N$ を収容している前提で、ローデータバッファ内の同じバッファラインにより既に収容されているロー画像N-1の画像ライン $L_{N-1}$ は次式で定義される。

$$L_{N-1} = (L_N \% \text{Field\_Num}) * \text{Field\_Size} + L_N / \text{Field\_Num}$$

ここに、30

- ・Field\_Numはロー画像が有するフィールドの数に対応し、

- ・Field\_Sizeは各フィールドが有するラインの数に対応し、

- ・%はモジュロ関数を表わし、

- ・除算は、商の分数部分を切り捨てる整数除算動作、例えば $7 / 2 = 3$ である。

#### 【0037】

図4A、4Bに示す例において、パラメータField\_Numは2に等しく、パラメータField\_Sizeは4に等しい。従って、上式は次式に簡約される。

$$L_{N-1} = (L_N \% 2) * 4 + L_N / 2$$

#### 【0038】

当式に基づいて、ローデータバッファに正に到着しようとする新規のロー画像を時間的にインターレースされた順番でどこに保存すべきかをIPPが決定し、ローデータバッファ内の既存のロー画像を論理的にプログレッシブな順番でどのように処理するかをIPUが決定することが、直接的に行なえる。便宜上、下記の表1は、上式に基づくローデータバッファ内における4個の連続的に取得されたロー画像の物理的順番のリストを示す。ロー画像N+3の物理的順番がロー画像Nの順番と同様である点に留意されたい。これは、ロー画像の物理的順番が周期的に変化することを意味し、本特定の例における周期は3である。また、画像ライン2が、先行画像内のライン1と同じバッファラインスロットを占有し、画像ライン4が、先行画像内のライン2と同じバッファラインスロットを占有し、以下同様である点に留意されたい。このパターンは、先行画像の画像ラインの論理的順番に従ってバッファラインに保存される現行画像の画像ラインの時系列として記述すること4050

ができる。別の観点から、3個の連続的な画像のシーケンス内の各画像は、当該シーケンス内の他の画像とは異なる画像ライン対メモリ位置マッピング (image line to memory location mapping) を有する。更に、画像センサからローデータバッファへ別々に読み出される3個以上フィールドを有する画像センサを用いるデジタルカメラにおいて、Fがフィールドの数を表わすとして、一連の連続的な画像に対する異なる画像ライン対メモリ位置のマッピングの数は  $F + 1$  である。

【0039】

【表1】

表1 4個の連続的に取得されたロー画像の物理的順序

10

|          | ロー画像N  | ロー画像N+1 | ロー画像N+2 | ロー画像N+3 |

|----------|--------|---------|---------|---------|

| バッファライン0 | 画像ライン0 | 画像ライン0  | 画像ライン0  | 画像ライン0  |

| バッファライン1 | 画像ライン1 | 画像ライン2  | 画像ライン4  | 画像ライン1  |

| バッファライン2 | 画像ライン2 | 画像ライン4  | 画像ライン1  | 画像ライン2  |

| バッファライン3 | 画像ライン3 | 画像ライン6  | 画像ライン5  | 画像ライン3  |

| バッファライン4 | 画像ライン4 | 画像ライン1  | 画像ライン2  | 画像ライン4  |

| バッファライン5 | 画像ライン5 | 画像ライン3  | 画像ライン6  | 画像ライン5  |

| バッファライン6 | 画像ライン6 | 画像ライン5  | 画像ライン3  | 画像ライン6  |

| バッファライン7 | 画像ライン7 | 画像ライン7  | 画像ライン7  | 画像ライン7  |

【0040】

図4Aに、IPP220およびIPU260(図2A)が同時にローデータバッファと相互作用する様子を更に示す。例えば、IPP220は最初にロー画像1の8個のインターレースされた画像ラインをローデータバッファにロードする。ローデータバッファ内の8本のラインの物理的順番を図4Bのブロック図Aにより示す。次に、IPU260はローデータバッファ内8本の画像ラインをプログレッシブな順番で処理を開始する。IPU260が特定の数(例えば2本)の画像ラインを処理して、それらを別個のYUVバッファへ転送した後で、IPP220はロー画像2のローデータバッファへのロードを開始する。この時点で、ローデータバッファ内のバッファライン0および1だけが新規の画像ラインを受け入れる準備ができている。その結果、最初の2本の画像ライン0、2は各々ローデータバッファのバッファライン0、1に保存される。

30

【0041】

IPU260がロー画像1の最後の画像ライン7を処理し終わった後で、IPP260は引き続きロー画像2の8本の画像ラインの残りをローデータバッファにロードする。ローデータバッファ内のロー画像2の8本のラインの完全な物理的順番を図4BのブロックBに示す。2個の連続的に取得された画像が、たとえそれらが時間的にインターレースされた順番でローデータバッファに到着して、論理的にプログレッシブな順番でバッファから出る場合でも、ローデータバッファ内で異なる物理的順番を有する点に留意されたい。

40

【0042】

上述のメモリ割当てアルゴリズムが説明の便宜上単純化されていることは当業者には明らかであろう。画像センサにより取得された現実の画像は数百あるいは数千本もの画像ラインを有する場合があり、各画像は3個以上のフィールドを含んでいる場合がある。しか

50

し、本発明の原理、すなわち図4A、4Bとの関連で上述したメモリ空間の利用の最適化は、本質的に変更することなく依然として適用可能である。

#### 【0043】

上述の実施形態に共通の特徴は、デジタルカメラのメモリが、各々特定の目的のために予約されている複数の領域に区分されている点である。第1実施形態において、第1の領域はロー画像データの保存のみを行なうローデータバッファであり、第2の領域は処理済み画像データの収容のみを行なうYUVバッファであり、第3の領域は圧縮画像データのキャッシュのみを行なうJPEGバッファである。この区分化スキームに付随する短所は、1個の領域内のメモリ空間は、たとえ現在本来の目的に使用されていなくても、異なる目的に使用することができない点である。この問題は、先行技術のデジタルカメラに付随する問題にある程度類似している。従って、この問題を解決すればデジタルカメラの性能を更に向上させることができる。10

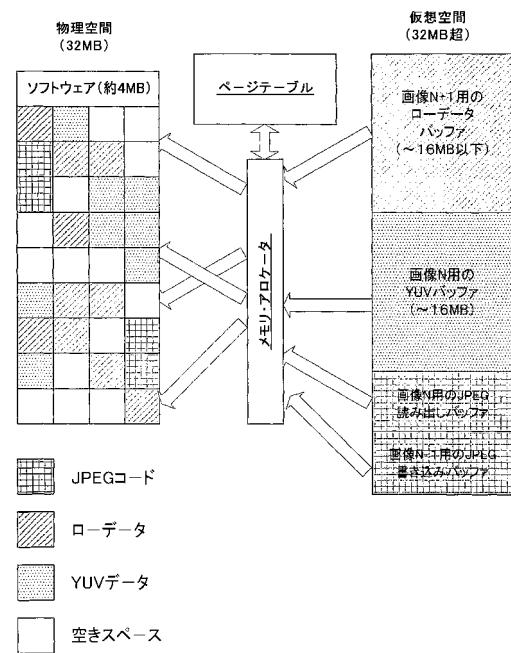

#### 【0044】

図5に、本発明のそのような代替的な実施形態を示す。本実施形態によれば、デジタルカメラのメモリ（例えば32MBDRAM）は物理メモリ空間として扱われる。物理メモリ空間内の固定領域（約4MB）は、ソフトウェアを保存するために予約されている。物理メモリ空間の残りは、多くの小さいメモリ・ページに分割されている。ページ・サイズの選択は基本的に、二つの競合する目的の間のトレードオフである。一方では、ページ・サイズが小さいほど、メモリ利用の効率が高い。他方、ページ・サイズが小さいほど管理が必要なメモリ・ページが多く、システム管理のオーバーヘッドが大きい。いくつかの実施形態において、ページ・サイズは8KBである。各メモリ・ページには固定された目的はない。ある時点にはロー画像の一部を保存するために用いられ、別の時点には圧縮されたJPEGファイルの一部を保存するために用いることができる。20

#### 【0045】

静的な物理メモリ空間に加え、巨大な動的仮想メモリ空間がある。仮想メモリ空間は通常、物理空間より大きい。例えば、仮想空間はローデータバッファ（約16MB）、YUVバッファ（約16MB）、JPEG読み出しバッファおよびJPEG書き込みバッファ等を含んでいる。仮想空間内の各々の位置を物理メモリ空間内の特定のメモリ・ページにリンクまたはマッピングするページテーブルまたはビットマップ等がある。二つの空間同士のリンクが動的である点に注意されたい。デジタルカメラの動作中に、仮想空間内の異なる位置が、異なる時点における物理空間の同一メモリ・ページを占有することができる。デジタルカメラの1個以上プロセッサが仮想メモリ・アドレスを用いて自身の動作を実行し、これらのアドレスは次いでページテーブルにより物理アドレスに変換されて、プロセッサが使用するデータへのアクセスを可能にする。プロセッサが、現在物理メモリ位置にマッピングされていない仮想メモリ・アドレスを利用しようと試みたために、メモリエラーが生じた場合、メモリ・アロケータがメモリの利用可能な物理ページを識別し、これをメモリエラーを引き起こした仮想メモリ・アドレスに関連付けられた仮想記憶ページに割当てて、適宜ページテーブルを更新する。次いでプロセッサの動作が再開される。30

#### 【0046】

本実施形態によれば、IPP202、IPU206、およびCMP270等のデジタルカメラの構成要素は、物理メモリ空間ではなく、仮想メモリ空間内のバッファと相互作用する。各バッファは次いで、物理メモリ空間内のメモリ・ページのユニークな組にマッピングされる。より具体的には、現在使用中であるページテーブルのエントリは、デジタルカメラのプロセッサ内の、トランスレーション・ルックアサイド・バッファ（the translation look-aside buffer）（TLB）とも呼ばれるページテーブル・キャッシュに保存することができる。TLB内のページテーブル・エントリは、仮想記憶ページを物理メモリ空間の物理ページ（物理ページフレームとも呼ばれる）にマッピングする。仮想記憶ページを物理メモリ・ページに動的に割当てた結果、2個の画像バッファが各々仮想メモリ空間の全く別々の領域を占有するにもかかわらず、これら2個の画像バッファに関連付けられたメモリ・ページを物理メモリ空間内に混在した状態で分散させることができる。4050

**【0047】**

個々の構成要素、例えばIPP220またはIPU260が、ローデータバッファ内における画像の物理的順番を認識している必要がある上述の実施形態とは異なり、メモリ・アロケータだけが物理的順番を認識していればよい。例えば、構成要素が動作を終えて、仮想空間内の特定のバッファの一部を解放する都度、メモリ・アロケータが適宜ページテーブルを更新して、他の構成要素が物理メモリ空間内で新たに解放されたメモリ・ページを要求できるようにする。同様に、構成要素がある量の空きスペースを必要とする都度、メモリ・アロケータはページテーブルを走査して、物理空間内で所定の数の空きメモリ・ページを確保する。メモリ・アロケータが特定の動作のために十分な空きスペースを見つけられなかった場合、必要な量のメモリ空間が利用可能になるまで当該動作は待たれる。本実施形態によれば、デジタルカメラ内の各構成要素が最適なモードで動作する。全体として、デジタルカメラは先行技術のデジタルカメラより優れた性能を実現することができる。10

**【0048】**

先の記述は、特定の実施形態に関して説明目的で述べてきた。しかし、上記の説明は、網羅的でなく、また本発明を開示された態様そのものに限定することを目的としない。上の教示から多くの修正や変更を行なうことが可能である。

**【図面の簡単な説明】****【0049】**

【図1A】先行技術のデジタルカメラの動作を示すデータフロー図である。20

【図1B】先行技術のデジタルカメラの動作を示す時系列図である。

【図1C】先行技術のデジタルカメラによる画像の取得に関連付けられた二つの異なる順番を示すプロック図である。

【図2A】本発明の第1実施形態によるデジタルカメラのデータフロー図である。

【図2B】本発明の第1実施形態によるデジタルカメラ内のメモリの空間割当て図である。

。

【図2C】本発明の第1実施形態によるデジタルカメラの時系列図である。

【図2D】本発明の第1実施形態によるデジタルカメラのメモリ使用のスナップショット図である。

【図3A】本発明の第2実施形態によるデジタルカメラのデータフロー図である。30

【図3B】本発明の第2実施形態によるデジタルカメラ内のメモリの空間割当て図である。

。

【図3C】本発明の第2実施形態によるデジタルカメラの時系列図である。

【図3D】本発明の第2実施形態によるデジタルカメラのメモリ使用のスナップショット図である。

【図4A】本発明のいくつかの実施形態によるデジタルカメラの異なる構成要素の並列動作を可能にする所定のメモリ割当てアルゴリズムの例を示す。

【図4B】本発明のいくつかの実施形態によるデジタルカメラの異なる構成要素の並列動作を可能にする所定のメモリ割当てアルゴリズムの例を示す。

【図5】本発明の別の実施形態を示すプロック図である。40

【 1 A 】

圖 1A

(先行技術)

( 义 1 B )

圖 1B

(先行技術)

【习 1 C】

圖1C

(先行技術)

【図2A】

図2A

【 図 2 B 】

2B

【図2C】

図2C

【図3A】

図3A

【図2D】

図2D

【図3B】

図3B

【図3C】

図3C

【図3D】

图 3D

圖 4A

【 4 B 】

84

( 5 )

圖 5

---

フロントページの続き

(72)発明者 フィッシュマン , アレックス

アメリカ合衆国 , カリフォルニア州 95130 , サンノゼ ボンゲート コート 1452

(72)発明者 パートセル , シモン

アメリカ合衆国 , カリフォルニア州 94087 , サニーベール , ケナード ウェイ 1672

(72)発明者 ピント , ピクター

イスラエル国 , ジクロン - ヤコフ , ハショマー ストリート 56

(72)発明者 シャレフ , マイケル

イスラエル国 , ジクロン ヤコフ , ウィングエイト ストリート , 16 ピー

審査官 宮下 誠

(56)参考文献 特開2002-320187(JP,A)

特開2003-304491(JP,A)

(58)調査した分野(Int.Cl. , DB名)

H04N 5/222