**【特許請求の範囲】**

**【請求項 1】**

アナログ入力電圧と比較電圧とを逐次比較して比較結果を生成する比較手段を備えた逐次比較型A/D変換器において、前記比較手段は、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの入出力端に並列に接続された第1の帰還スイッチと、前記第2のインバータの入出力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの入出力端に互いに並列に接続した第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジスタよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの入出力端に互いに並列に接続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトランジスタよりもドライブ能力が大きく形成され、

前記第1および第3のトランジスタのゲートは共に接続されて第1の制御信号が入力される第1の制御入力端子に接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第2の制御信号が入力される第2の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、前記アナログ入力電圧と前記基準電圧との比較を行うことを特徴とする逐次比較型A/D変換器。

**【請求項 2】**

請求項1に記載の逐次比較型A/D変換器において、前記比較手段は、前記第1および第3のトランジスタをオン状態からオフに切り替えた後に、前記第2および第4のトランジスタをオン状態からオフに切り替えることを特徴とする逐次比較型A/D変換器。

**【請求項 3】**

請求項1に記載の逐次比較型A/D変換器において、前記第1および第3のトランジスタのゲート幅とゲート長との比(W/L比)が、前記第2および第4のトランジスタのゲート幅とゲート長との比(W/L比)よりも大きく形成されていることにより、前記ドライブ能力が異なることを特徴とする逐次比較型A/D変換器。

**【請求項 4】**

請求項1に記載の逐次比較型A/D変換器において、該変換器は、CMOS回路にて形成されていることを特徴とする逐次比較型A/D変換器。

**【請求項 5】**

請求項1に記載の逐次比較型A/D変換器において、該変換器は、前記比較電圧を生成する比較電圧生成手段を備え、該比較電圧生成手段は、

前記アナログ入力電圧と基準電圧とを前記比較電圧に応じてサンプルする複数のスイッチと、

前記複数のスイッチの出力にそれぞれ対応して一方の電極が接続され、前記基準電圧および前記比較電圧を順次ホールドする複数のキャパシタであって、MSBからLSBにかけてそれぞれ容量が小さくなるように重み付けされて接続している複数のキャパシタとを含み、

前記複数のキャパシタの他方の電極が共通に接続されて該接続を該比較電圧生成手段の出力として前記比較電圧を出力し、

前記複数のスイッチは、前記MSBからLSBにかけて、前記複数のキャパシタの容量に比例して、それぞれスイッチサイズが小さくなるように形成されていることを特徴とする逐次比較型A/D変換器。

**【請求項 6】**

アナログ入力電圧と比較電圧とを逐次比較して比較結果を生成する比較手段を備えた逐

10

20

30

40

50

次比較型A/D変換器において、前記比較手段は、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、

該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、

該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの出入力端に並列に接続された第1の帰還スイッチと、

前記第2のインバータの出入力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの出入力端に互いに並列に接続した第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジスタよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの出入力端に互いに並列に接続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトランジスタよりもドライブ能力が大きく形成され、

前記第1のトランジスタのゲートは第1の制御信号が入力される第1の制御入力端子に接続され、

前記第3のトランジスタのゲートは第2の制御信号が入力される第2の制御入力端子に接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第3の制御信号が入力される第3の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、さらに、第1のトランジスタと第2のトランジスタとのオン/オフ切替タイミングを異ならせて、前記アナログ入力電圧と前記基準電圧との比較を行うことを特徴とする逐次比較型A/D変換器。

#### 【請求項7】

請求項6に記載の逐次比較型A/D変換器において、前記比較手段は、前記第1のトランジスタをオン状態からオフに切り替えた後、第3のトランジスタをオン状態からオフに切り替え、その後に、前記第2および第4のトランジスタをオン状態からオフに切り替えることを特徴とする逐次比較型A/D変換器。

#### 【請求項8】

請求項6に記載の逐次比較型A/D変換器において、前記第1および第3のトランジスタのゲート幅とゲート長との比(W/L比)が、前記第2および第4のトランジスタのゲート幅とゲート長との比(W/L比)よりも大きく形成されていることにより、前記ドライブ能力が異なることを特徴とする逐次比較型A/D変換器。

#### 【請求項9】

請求項6に記載の逐次比較型A/D変換器において、該変換器は、CMOS回路にて形成されていることを特徴とする逐次比較型A/D変換器。

#### 【請求項10】

請求項6に記載の逐次比較型A/D変換器において、該変換器は、前記比較電圧を生成する比較電圧生成手段を備え、該比較電圧生成手段は、

前記アナログ入力電圧と基準電圧とを前記比較電圧に応じてサンプルする複数のスイッチと、

前記複数のスイッチの出力にそれぞれ対応して一方の電極が接続され、前記基準電圧および前記比較電圧を順次ホールドする複数のキャパシタであって、MSBからLSBにかけてそれぞれ容量が小さくなるように重み付けされて接続している複数のキャパシタとを含み、

前記複数のキャパシタの他方の電極が共通に接続されて該接続を該比較電圧生成手段の出力として前記比較電圧を出力し、

前記複数のスイッチは、前記MSBからLSBにかけて、前記複数のキャパシタの容量に比例して、それぞれスイッチサイズが小さくなるように形成されていることを特徴とする逐次比較型A/D変換器。

#### 【請求項11】

10

20

30

40

50

アナログ入力電圧と比較電圧とを逐次比較するコンパレータにおいて、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、

該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、

該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの出入力端に並列に接続された第1の帰還スイッチと、

前記第2のインバータの出入力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの出入力端に互いに並列に接続した

第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジス

タよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの出入力端に互いに並列に接

続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトラン

ジスタよりもドライブ能力が大きく形成され、

前記第1および第3のトランジスタのゲートは共に接続されて第1の制御信号が入力さ

れる第1の制御入力端子に接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第2の制御信号が入力さ

れる第2の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタの

オン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタ

のオン/オフ切替タイミングとを異ならせて、前記アナログ入力電圧と前記基準電圧との

比較を行うことを特徴とするコンパレータ。

10

### 【請求項 1 2】

アナログ入力電圧と比較電圧とを逐次比較するコンパレータにおいて、

前記アナログ入力電圧と前記比較電圧とが順次入力される第1のインバータと、

該第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、

該キャパシタの他方の電極に接続された第2のインバータと、

前記第1のインバータの出入力端に並列に接続された第1の帰還スイッチと、

前記第2のインバータの出入力端に並列に接続された第2の帰還スイッチとを含み、

前記第1の帰還スイッチは、前記第1のインバータの出入力端に互いに並列に接続した

第1および第2のトランジスタを含み、前記第1のトランジスタは前記第2のトランジス

タよりもドライブ能力が大きく形成され、

前記第2の帰還スイッチはさらに、前記第2のインバータの出入力端に互いに並列に接

続した第3および第4のトランジスタを含み、前記第3のトランジスタは前記第4のトラン

ジスタよりもドライブ能力が大きく形成され、

前記第1のトランジスタのゲートは第1の制御信号が入力される第1の制御入力端子に

接続され、

前記第3のトランジスタのゲートは第2の制御信号が入力される第2の制御入力端子に

接続され、

前記第2および第4のトランジスタのゲートは共に接続されて第3の制御信号が入力さ

れる第3の制御入力端子に接続され、

逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタの

オン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタ

のオン/オフ切替タイミングとを異ならせて、さらに、第1のトランジスタと第2のトラン

ジスタとのオン/オフ切替タイミングを異ならせて、前記アナログ入力電圧と前記基準

電圧との比較を行うことを特徴とするコンパレータ。

20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0 0 0 1】

本発明は、逐次比較型A/D変換器およびコンパレータに係り、たとえばMOS型半導体集積

回路にて形成した逐次比較型A/D変換器およびコンパレータに関するものである。

#### 【背景技術】

10

20

30

40

50

**【 0 0 0 2 】**

アナログ信号をデジタル信号に変換するアナログ・デジタル変換回路（A/D変換回路）は、積分方式や比較方式があり、比較方式ではたとえば並列比較型や逐次比較型等の変換方式が知られている。逐次比較型A/D変換回路は、たとえば、変換対象の入力アナログ電圧と、複数の基準電圧とをMSBから順次比較することによりMSBから LSBの各ビットを比較決定する方式が採用されている。

**【 0 0 0 3 】**

逐次比較型A/D変換回路は、たとえば、入力電圧を比較電圧と比較する比較回路と、比較回路における比較結果に応じて比較電圧値を生成するとともに比較決定を行う比較レジスタと、比較電圧値をアナログ値に変換するD/A変換回路とを含むように構成される。

10

**【 0 0 0 4 】**

このような電圧比較を行う比較回路はたとえば特許文献1に示され、チョッパー型電圧比較器におけるノイズ混入による誤動作防止が図られている。

**【 0 0 0 5 】**

【特許文献1】特開平8-195655号公報

**【発明の開示】****【発明が解決しようとする課題】****【 0 0 0 6 】**

逐次比較型A/D変換器を構成する場合、D/A変換回路や、電圧比較器に備えられるスイッチをオン/オフすることにより、各ビットの電圧比較が行われる。スイッチはCMOS回路においてNMOS、PMOS、N型、P型半導体にてアナログスイッチを構成する。アナログスイッチは、トランジスタに与えるゲート電圧に応じてオン/オフするが、ゲート電圧が変化すると寄生容量が変動し、この変動によりスイッチングノイズが発生する。このスイッチングノイズによりD/A変換およびA/D変換の精度が悪化するという問題があった。

20

**【 0 0 0 7 】**

また、電圧比較器において、アナログ入力電圧をサンプル・ホールドする際に、内部キャパシタに電荷を蓄積させるが、サンプル・ホールド動作の速度を上げるために、スイッチを構成するMOSトランジスタのサイズを大きくするなどの必要がある。しかし、MOSトランジスタのサイズを大きくすると、サイズに正比例してスイッチングノイズが大きくなり、A/D変換精度が悪くなるという問題があった。

30

**【 0 0 0 8 】**

さらに、一連のA/D変換動作を行う際、変換精度を上げるためにアナログ入力電圧をホールドするキャパシタの比精度を上げる必要があるが、その場合、キャパシタサイズを小さくするには限界があり、また、動作スピードを確保しながら高精度分解能となる微小電圧レベルまで電荷を蓄積する場合、スイッチとして使用するMOSトランジスタのサイズを小さくすることに限界があった。

40

**【 0 0 0 9 】**

本発明はこのような従来技術の欠点を解消し、スイッチングノイズの影響を抑えて、高精度な逐次比較型A/D変換器およびその逐次比較型A/D変換器内等に配置されるコンパレータを提供することを目的とする。

40

**【課題を解決するための手段】****【 0 0 1 0 】**

アナログ入力電圧と比較電圧とを逐次比較して比較結果を生成する比較手段を備えた逐次比較型A/D変換器において、比較手段は、アナログ入力電圧を入力する入力手段と、比較電圧を生成する比較電圧生成手段と、アナログ入力電圧と比較電圧とを逐次比較し、比較結果を生成する比較手段と、比較結果に基づいて、比較電圧を設定する制御信号を生成する処理手段と、比較結果を蓄積して、全ビットの比較処理後にディジタル信号として出力する出力手段とを含み、比較手段は、アナログ入力電圧と比較電圧とが順次入力される第1のインバータと、第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、キャパシタの他方の電極に接続された第2のインバータと、第1のインバー

50

タの入出力端に並列に接続された第1の帰還スイッチと、第2のインバータの入出力端に並列に接続された第2の帰還スイッチとを含み、第1の帰還スイッチは、第1のインバータの入出力端に互いに並列に接続した第1および第2のトランジスタを含み、第1のトランジスタは第2のトランジスタよりもドライブ能力が大きく形成され、第2の帰還スイッチはさらに、第2のインバータの入出力端に互いに並列に接続した第3および第4のトランジスタを含み、第3のトランジスタは第4のトランジスタよりもドライブ能力が大きく形成され、第1および第3のトランジスタのゲートは共に接続されて第1の制御信号が入力される第1の制御入力端子に接続され、第2および第4のトランジスタのゲートは共に接続されて第2の制御信号が入力される第2の制御入力端子に接続され、逐次比較動作を行う際に、ドライブ能力が大きい第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、アナログ入力電圧と基準電圧との比較を行うことを特徴とする。

10

## 【0011】

この場合、比較手段は、第1および第3のトランジスタをオン状態からオフに切り替えた後に、第2および第4のトランジスタをオン状態からオフに切り替えるとよく、また、第1および第3のトランジスタのゲート幅とゲート長との比(W/L比)が、第2および第4のトランジスタのゲート幅とゲート長との比(W/L比)よりも大きく形成されていることにより、ドライブ能力が異なるとよい。

20

## 【0012】

さらにこの変換器は、比較電圧を生成する比較電圧生成手段を備え、比較電圧生成手段は、アナログ入力電圧と基準電圧とを比較電圧に応じてサンプルする複数のスイッチと、複数のスイッチの出力にそれぞれ対応して一方の電極が接続され、基準電圧および比較電圧を順次ホールドする複数のキャパシタであって、MSBからLSBにかけてそれぞれ容量が小さくなるように重み付けされて接続している複数のキャパシタとを含み、複数のキャパシタの他方の電極が共通に接続されてこの接続を比較電圧生成手段の出力として比較電圧を出力し、複数のスイッチは、MSBからLSBにかけて、複数のキャパシタの容量に比例して、それぞれスイッチサイズが小さくなるように形成されているとよい。

20

## 【0013】

また、本発明は上述の課題を解決するために、アナログ入力電圧と比較電圧とを逐次比較して比較結果を生成する比較手段を備えた逐次比較型A/D変換器において、比較手段は、アナログ入力電圧と比較電圧とが順次入力される第1のインバータと、第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、キャパシタの他方の電極に接続された第2のインバータと、第1のインバータの入出力端に並列に接続された第1の帰還スイッチと、第2のインバータの入出力端に並列に接続された第2の帰還スイッチとを含み、第1の帰還スイッチは、第1のインバータの入出力端に互いに並列に接続した第1および第2のトランジスタを含み、第1のトランジスタは第2のトランジスタよりもドライブ能力が大きく形成され、第2の帰還スイッチはさらに、第2のインバータの入出力端に互いに並列に接続した第3および第4のトランジスタを含み、第3のトランジスタは第4のトランジスタよりもドライブ能力が大きく形成され、第1のトランジスタのゲートは第1の制御信号が入力される第1の制御入力端子に接続され、第3のトランジスタのゲートは第2の制御信号が入力される第2の制御入力端子に接続され、第2および第4のトランジスタのゲートは共に接続されて第3の制御信号が入力される第3の制御入力端子に接続され、逐次比較動作を行う際に、ドライブ能力が大きい第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、さらに、第1のトランジスタと第2のトランジスタとのオン/オフ切替タイミングを異ならせて、アナログ入力電圧と基準電圧との比較を行うことを特徴とする。

30

## 【0014】

この場合、比較手段は、第1のトランジスタをオン状態からオフに切り替えた後、第3のトランジスタをオン状態からオフに切り替え、その後に、第2および第4のトランジ

40

50

タをオン状態からオフに切り替えるとよく、また、第1および第3のトランジスタのゲート幅とゲート長との比(W/L比)が、第2および第4のトランジスタのゲート幅とゲート長との比(W/L比)よりも大きく形成されることにより、ドライブ能力が異なるといい。

#### 【0015】

さらに、この変換器は、比較電圧を生成する比較電圧生成手段を備え、比較電圧生成手段は、アナログ入力電圧と基準電圧とを比較電圧に応じてサンプルする複数のスイッチと、複数のスイッチの出力にそれぞれ対応して一方の電極が接続され、基準電圧および比較電圧を順次ホールドする複数のキャパシタであって、MSBからLSBにかけてそれぞれ容量が小さくなるように重み付けされて接続している複数のキャパシタとを含み、複数のキャパシタの他方の電極が共通に接続されて該接続を比較電圧生成手段の出力として比較電圧を出力し、複数のスイッチは、MSBからLSBにかけて、複数のキャパシタの容量に比例して、それぞれスイッチサイズが小さくなるように形成されているといい。10

#### 【0016】

また、本発明は上述の課題を解決するために、アナログ入力電圧と比較電圧とを逐次比較するコンパレータにおいて、アナログ入力電圧と比較電圧とが順次入力される第1のインバータと、第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、キャパシタの他方の電極に接続された第2のインバータと、第1のインバータの出入力端に並列に接続された第1の帰還スイッチと、第2のインバータの出入力端に並列に接続された第2の帰還スイッチとを含み、第1の帰還スイッチは、第1のインバータの出入力端に互いに並列に接続した第1および第2のトランジスタを含み、第1のトランジスタは第2のトランジスタよりもドライブ能力が大きく形成され、第2の帰還スイッチはさらに、第2のインバータの出入力端に互いに並列に接続した第3および第4のトランジスタを含み、第3のトランジスタは第4のトランジスタよりもドライブ能力が大きく形成され、第1および第3のトランジスタのゲートは共に接続されて第1の制御信号が入力される第1の制御入力端子に接続され、第2および第4のトランジスタのゲートは共に接続されて第2の制御信号が入力される第2の制御入力端子に接続され、逐次比較動作を行う際に、ドライブ能力が大きい第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、アナログ入力電圧と基準電圧との比較を行うことを特徴とする。20

#### 【0017】

また、本発明は上述の課題を解決するために、アナログ入力電圧と比較電圧とを逐次比較するコンパレータにおいて、アナログ入力電圧と比較電圧とが順次入力される第1のインバータと、第1のインバータの出力に一方の電極が接続され電荷を蓄電するキャパシタと、キャパシタの他方の電極に接続された第2のインバータと、第1のインバータの出入力端に並列に接続された第1の帰還スイッチと、第2のインバータの出入力端に並列に接続された第2の帰還スイッチとを含み、第1の帰還スイッチは、第1のインバータの出入力端に互いに並列に接続した第1および第2のトランジスタを含み、第1のトランジスタは第2のトランジスタよりもドライブ能力が大きく形成され、第2の帰還スイッチはさらに、第2のインバータの出入力端に互いに並列に接続した第3および第4のトランジスタを含み、第3のトランジスタは第4のトランジスタよりもドライブ能力が大きく形成され、第1のトランジスタのゲートは第1の制御信号が入力される第1の制御入力端子に接続され、記第3のトランジスタのゲートは第2の制御信号が入力される第2の制御入力端子に接続され、第2および第4のトランジスタのゲートは共に接続されて第3の制御信号が入力される第3の制御入力端子に接続され、逐次比較動作を行う際に、ドライブ能力が大きい前記第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい前記第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせて、さらに、第1のトランジスタと第2のトランジスタとのオン/オフ切替タイミングを異ならせて、アナログ入力電圧と基準電圧との比較を行うことを特徴とする。40

#### 【発明の効果】

## 【0018】

本発明によれば、逐次比較動作を行う際に、ドライブ能力が大きい第1および第3のトランジスタのオン/オフ切替タイミングと、ドライブ能力が小さい第2および第4のトランジスタのオン/オフ切替タイミングとを異ならせるように制御タイミングを変えているので、第1および第3のトランジスタのオフ後に第2および第4のトランジスタオフすることにより、オフセット誤差を無くし、スイッチングノイズによる影響を抑えて、より高精度のアナログ電圧の比較を行うことできる。また、ドライブ能力が大きい第1および第3のトランジスタにより、サンプルホールド用のキャパシタに入力電圧の電荷をより高速に蓄積することができる。

## 【0019】

また、コンパレータの第1のインバータに並列接続したトランジスタを前にオフ状態に制御し、第2のインバータに並列接続したトランジスタをその後にオフ状態に制御することにより、同時スイッチングによって一時的にオフセットが大きくなることを低減することができる。

## 【0020】

また、比較電圧生成手段における複数のキャパシタの総和容量に較べて、比較手段のキャパシタの容量を小さく設定することができるので、たとえば、第2の帰還スイッチのサイズをより小さくすることができ、スイッチングノイズをさらに抑えるとともに、チップ面積を小さくすることが可能となる。

## 【0021】

さらに、比較手段における複数のキャパシタの容量に比例して、複数のスイッチのサイズを小さく設定することができるため、チップサイズをより小さくでき、さらにスイッチングノイズの影響が低減される。

## 【発明を実施するための最良の形態】

## 【0022】

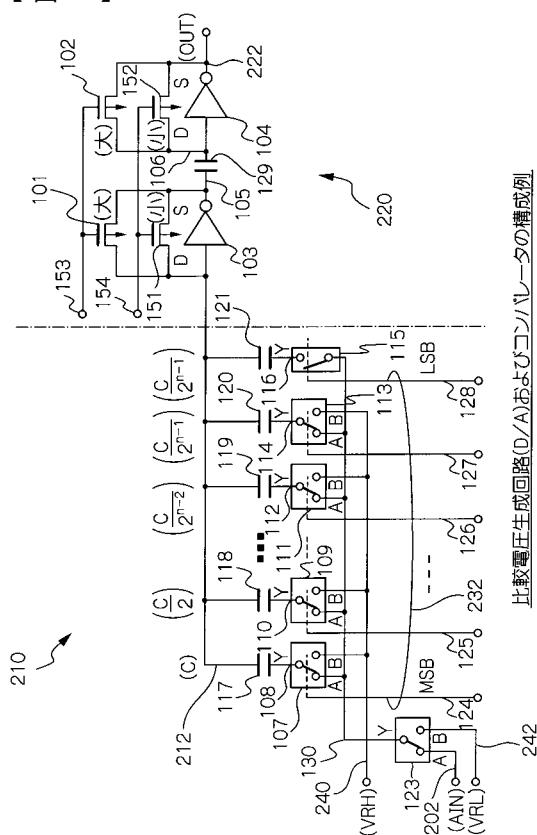

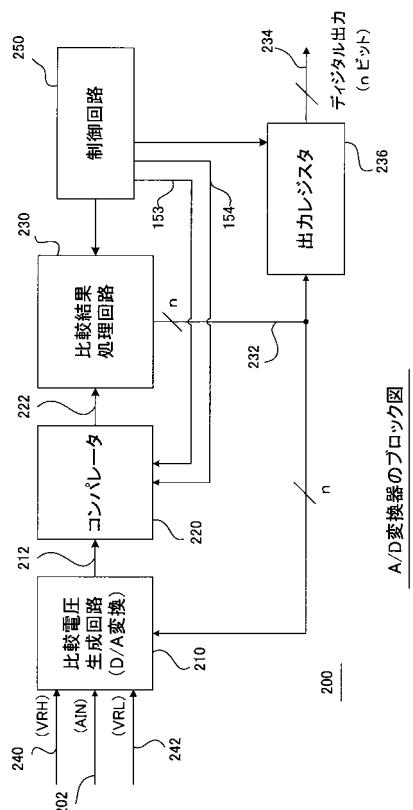

次に添付図面を参照して本発明が適用された逐次比較型A/D変換器に内蔵される比較電圧生成回路およびコンパレータの実施例を詳細に説明する。まず、図2を参照すると、CMOS LSIにて形成される逐次比較型A/D変換器200の概略構成図が示されている。本実施例における逐次比較型A/D変換器200は、アナログ入力(AIN) 202に入力するアナログ信号の電圧を比較するための比較電圧を生成する比較電圧生成回路210と、比較電圧生成回路210の出力212に接続され、出力212から出力される比較電圧と入力アナログ信号電圧とを逐次比較して、その比較結果を出力するコンパレータ220とを備えている。

## 【0023】

コンパレータ220の出力222には比較結果処理回路230が接続され、比較結果処理回路230は、コンパレータ220から出力される比較結果をnビットのバス232に出力して出力レジスタ236に供給する。さらに比較結果処理回路230は、比較電圧生成回路210内に備えられている後述のスイッチを切り替える制御信号を生成する。この制御信号は、比較結果に対応して決定した比較電圧を表すディジタル値であり、比較処理対象のビットの1つ上位ビットの比較結果の大小に応じて比較処理対象の値が決定された制御信号である。比較結果処理回路230は生成した制御信号を一旦保持する比較レジスタ(不図示)を備え、保持した制御信号をバス232を介して比較電圧生成回路210に供給する。出力レジスタ236は、バス232に接続され、入力される各ビットの値を順次保持する記憶回路であり、MSBからLSBまでの全ビット値が記憶保持されるとその保持値をnビットのディジタル信号として出力234にする。なお、以下の説明において本発明に直接関係のない部分は、図示およびその説明を省略し、また、信号の参照符号はその現われる接続線の参照番号で表わす。

## 【0024】

比較電圧生成回路210は、フルスケール基準電圧(VRH)が与えられる入力端子(VRH) 240と、ゼロスケール基準電圧(VRL)が与えられる入力端子(VRL) 242とを有している。また、制御回路250の出力153,154はコンパレータ220に接続され、制御回路250は、コンパレータ220の動作を制御信号153,154を供給して制御する。

## 【 0 0 2 5 】

比較電圧生成回路210およびコンパレータ220の内部構成例を図1に示す。図の左方に比較電圧生成回路210が示され、コンパレータ220が図の右方に示されている。本実施例における比較電圧生成回路210は、入力アナログ信号(AIN)をサンプル・ホールドする複数のスイッチと、複数のスイッチにそれぞれ接続された複数のキャパシタとを有する容量重み付けの容量ラダー型(Cラダー型)D/A変換器を形成している。

## 【 0 0 2 6 】

比較電圧生成回路210のアナログ入力(AIN)202はスイッチ123の一方の入力端子Aに接続され、ゼロスケール基準電圧(VRL)が印加される入力端子(VRL)242はスイッチ123の他の方の入力端子Bに接続されている。スイッチ123の出力端子Yはノード130により複数のスイッチ群107,109,...,111,113の一方の入力端子Aにそれぞれ接続され、フルスケール基準電圧(VRH)が印加される入力端子(VRH)240は、ノード240により複数のスイッチ群107,109,...,111,113の他方の入力端子Bにそれぞれ接続されている。また、ノード130は、スイッチ115の一方の入力端子に接続されている。複数のスイッチ群107,109,...,111,113の出力端子Yとスイッチ115の出力端子Yとは、それぞれ各スイッチ107~115と同数が配置されたキャパシタ117,118,...,119,120,121の一方の電極にそれぞれ接続されている。キャパシタ117の容量を容量Cとし、キャパシタ118の容量を容量C/2とし、さらにキャパシタ119,120,121はそれぞれ容量C/2<sup>(n-2)</sup>,容量C/2<sup>(n-1)</sup>,容量C/2<sup>(n-1)</sup>とすると、キャパシタ118とキャパシタ119との間には、それぞれ不図示のスイッチに接続された容量C/2<sup>2</sup>,...,容量C/2<sup>(n-3)</sup>の不図示のキャパシタが配置されている。ここで”n”は、不図示のキャパシタを含むキャパシタ117~121の接続段数を示す数である。

10

20

20

## 【 0 0 2 7 】

スイッチ107,109,...,111,113,115は、各キャパシタを選択する切替スイッチであり、スイッチ107,109,...,111,113は制御信号124~127に応動して端子Aまたは端子Bがオンして端子Yに接続する。また、スイッチ115は制御信号128に応動してオンして端子Yに接続する。スイッチ107,109,...,111,113,115には、それぞれ切り替え制御を行うための制御信号を入力する端子124~128がそれぞれ接続されている。キャパシタ117,118,...,119,120,121の他方の電極はノード212に接続されている。

30

## 【 0 0 2 8 】

ノード212は比較電圧生成回路210の出力を形成してコンパレータ220に接続されている。コンパレータ220は、入力212に現れる信号を順次比較して、その大小レベルに応じた比較結果を出力端子(OUT)222に出力するチョッパー・コンパレータ回路を形成している。

30

## 【 0 0 2 9 】

詳しくは、コンパレータ220は、比較電圧生成回路210の出力ノード212に第1段目のインバータ103の入力と各Pチャネル型トランジスタ(以下、PchTrと称する)101,151のドレインとが接続され、インバータ103の出力は、各PchTr101,151のソースとキャパシタ129の一方の電極とが接続されている。キャパシタ129の他方の電極は第2段目のインバータ104の入力に接続されている。インバータ103,104は、それぞれ入力を閾値電圧(Vinvt)を基準にして反転出力する反転回路であり、インバータ104の入力はさらに各PchTr102,152のドレインが接続され、インバータ104の出力は各PchTr102,152のソースが接続されている。このような容量カップリング接続により、キャパシタ129はインバータ103,104の閾値電圧の差(オフセット電圧差)をキャンセルする。このようにインバータ103の入出力端にPchTr101,151がそれぞれ並列接続されてインバータ帰還スイッチを形成し、インバータ104の入出力端にPchTr102,152がそれぞれ並列接続されてインバータ帰還スイッチを形成している。インバータ104の出力はコンパレータ220の出力(OUT)222を形成している。

40

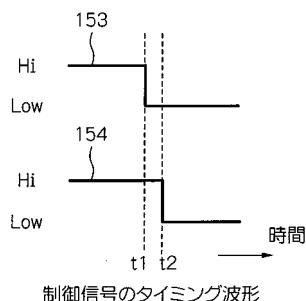

## 【 0 0 3 0 】

PchTr101,102の各ゲートは制御入力端子153に接続され、PchTr151,152の各ゲートは制御入力端子154に接続されている。制御入力端子153,154に入力される制御信号のタイミング波形例を図5に示す。図示するように制御信号153が時間t1にてハイ(Hi)レベルからロウ(Low)レベルになり、これに遅れて制御信号154が時間t2にてハイ(Hi)レベルからロ

50

ウ(Low) レベルに変化する。PchTr 101,102,151,152は、これら制御信号153,154に応じてオン状態とオフ状態とが切り替え駆動されるスイッチとして作動する。

#### 【0031】

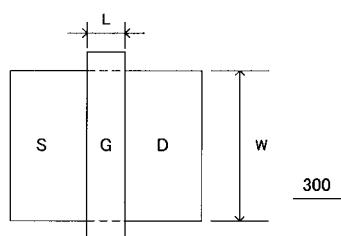

PchTrの大小関係は、PchTr 101>PchTr 151, PchTr 102>PchTr 152に設定されている。これらトランジスタの大小関係は、ゲート電極のゲート幅(W)とゲート長(L)との比(W/L比)を各トランジスタについて大小比較した関係であり、大小関係はトランジスタのドライブ能力に対応する関係を有している。したがってW/L比に応じたトランジスタの能力をドライブ能力と称する。このドライブ能力の大小に応じて、たとえばオン/オフ時の立ち上がり、立ち下がりの速度が異なる。なお、これら特性が異なるトランジスタのドライブ能力の大小は、たとえば「4:1」ないし「16:1」などの大小比が適用される。つまり、PchTr 101は、PchTr 151のたとえば4倍ないし16倍ドライブ能力が大きく形成される。また、PchTr 102は、PchTr 152のたとえば4倍ないし16倍ドライブ能力が大きく形成される。

10

20

40

50

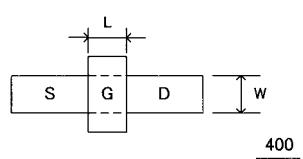

#### 【0032】

PchTrの概略構造を図3および図4に示す。図3にゲート電極(G)の幅(W)が相対的に大きいPchTr 300を示し、ゲート電極(G)の幅が相対的に小さいPchTr 400を図4に示している。これらPchTr 300,400はそれぞれゲート電極(G)の長さ(L)が同一サイズであるとすると、ドライブ能力(W/L比)がPchTr 300の方が大きく、PchTr 400はPchTr 300よりもドライブ能力が小さいトランジスタである。

#### 【0033】

図2に戻って、比較結果処理回路230は、コンパレータ220から出力される比較結果をnビットのバス232に出力して出力レジスタ236に供給する。出力レジスタ236は、バス232に接続され、所定タイミングにて入力される各ビットの値を順次保持するCMOSロジック回路で構成される記憶回路であり、MSBから LSBまでの全ビット値が記憶保持されるとその保持値をnビットのデジタル信号として出力234にする。なお、出力レジスタ236は、比較結果処理回路230から制御信号が出力されるタイミングではビット値を取り込む記憶動作を行わず、各ビットの決定値のみを順次取り込んで保持してゆく。このタイミング制御は、たとえば制御回路250や処理回路230からの制御によって行われるとよい。

#### 【0034】

さらに比較結果処理回路230は、比較電圧生成回路210内のスイッチ107,109,...,111,113,115を選択して切り替える制御信号を生成し、制御信号をバス232を介して所定タイミングごとに比較電圧生成回路210に供給する。具体的には比較結果処理回路230は、入力アナログ信号(AIN)の電圧が、比較電圧よりもハイ(Hi)レベルであった場合には、次の下位ビットに対する比較処理時にさらに1/nスケールプラス方向に設定する比較電圧を与える制御信号を生成する。この場合、具体的には現在のビットに対応するスイッチをオン状態に維持させるとともに、次の下位ビットに対応するスイッチをオンに制御して比較処理を行うように制御する。逆に入力アナログ信号の電圧が、比較電圧よりもロウ(Low)レベルであった場合には、次の下位ビットに対する比較処理時にさらに1/nスケールマイナス方向に設定する比較電圧を与える制御信号を生成する。この場合、具体的には現在のビットに対応するスイッチをオフ状態に復帰させるとともに、次の下位ビットに対応するスイッチをオンに制御して比較処理を行うように制御する。このように比較結果処理回路230は、比較結果に応じて、スイッチ107~115の接続を制御してMSB~LSBを決定するための比較電圧を制御する。

#### 【0035】

制御回路250は、各部における処理タイミングを制御するタイミング制御機能を有し、たとえばコンパレータ220の動作を制御する制御信号153,154を生成して供給する。本実施例では、図1に示すPchTr 101,102とPchTr 151,152とをそれぞれ同時にオンして、電荷を急速にキャパシタ129に蓄積させ、その後、図5に示したようにPchTr 101,102を先にオフする制御信号153を生成し、さらにその後PchTr 151,152をオフする制御信号154を生成する。このように、性質の異なる複数のトランジスタの動作タイミングを変える制御により

、最初のPchTr 101,102のオフ状態にてPchTr 151,152のオン状態が継続されて、スイッチングノイズによる電荷のずれを補正することができる。さらに次にPchTr 151,152をオフする際には、これらトランジスタはそれぞれ並列接続された他方のトランジスタよりもドライブ能力が小さく構成されているため、スイッチングノイズを最小限に抑えた状態にてトランジスタスイッチをオフにすることができる。これにより、インバータ103,104およびキャパシタ129は、ノード212の電位に変化が生じた場合、出力(OUT) 222にハイ(Hi)またはロウ(Low)を出力するコンパレータとしての動作が行われる。

#### 【0036】

以上の構成で本実施例における逐次比較型A/D変換器200に内蔵される比較電圧生成回路210およびコンパレータ220の動作を説明する。

10

#### 【0037】

アナログ入力(AIN)にアナログ入力電圧(Vain)が印加され、このとき切替スイッチ123と切替スイッチ107,109,...,111,113は、それぞれ端子Aがオン状態となり、スイッチ115もオン状態となっている。さらに制御入力端子153に与えられる制御信号153によりPchTr 101,102がオン状態になり、同時に制御入力端子154に与えられる制御信号154によりPchTr 151,152がオン状態となる。PchTr 101,102は、それぞれ並列に接続された他方のトランジスタよりもドライブ能力が大きいため、PchTr 101,102は、キャパシタ129に容量2Cの電荷をより高速にセトリングレベルまで蓄積する。

#### 【0038】

キャパシタ117,118,...,119,120,121の全容量の総和2Cに、アナログ電圧(Vain)とインバータ103の閾値電圧(Vinvt)との電位差をもつ電荷2C(Vain-Vinvt)が蓄積される。次に、制御信号153によりPchTr 101,102がオフし、PchTr 151,152のオンが維持されている状態にてスイッチングノイズによる電荷ズレが補正される。

20

#### 【0039】

次に、PchTr 151,152が制御信号154によりオフされる。PchTr 151,152は、それぞれ並列に接続された他方のトランジスタよりもドライブ能力(W/L比)が小さく構成しているのでスイッチングノイズを最小限に抑えてスイッチをオフすることができる。これにより、インバータ103,104は、ノード212に電位変化が生じた場合、出力(OUT) 222に"H"または"L"を出力する。このとき各インバータ103,104の閾値電圧の差(オフセット電圧差)はキャパシタ129にてキャンセルされる。

30

#### 【0040】

さらに次の状態としてスイッチ107の端子Bがオン状態に切り替え、同時にスイッチ123の端子Bをオン状態にすると、スイッチ107の出力端子Yのノード108はフルスケール基準電圧(VRH)になり、他のスイッチ109,111,...,113,115の出力端子Yのノード110,112,...,114,116は全てゼロスケール基準電圧(VRL)となる。総和容量2Cに蓄積された電荷2C(Vain-Vinvt)は一定であり、電荷分配によりノード212の電位は $1/2(VRH-VRL)-(Vain-Vinvt)$ となる。インバータ103は、閾値電圧(Vinvt)との電位差を反転して出力し、最終的に出力端子(OUT) 222に入力電圧(Vain)と $1/2(VRH-VRL)$ との大小を比較して"H"または"L"を出力する。この逐次比較動作によりMSBが確定し、その比較結果が比較結果処理回路230を介して出力レジスタ236(図2)に取り込まれる。

40

#### 【0041】

その後、比較結果処理回路230は、MSBの大小比較結果に応じて、スイッチ107は端子Aがオン状態となり、同時にスイッチ109は端子Bがオン状態となり、他のスイッチはそのままの状態とする制御信号を生成して比較電圧生成回路210に供給する。

#### 【0042】

上記と同様に各キャパシタの容量の重み付けに応じてノード212は、 $1/4(VRH-VRL)-(Vain-Vinvt)$ となり、逐次比較動作を行って、MSBから1つ下位1ビットにおける比較結果が出力端子(OUT) 222に出力される。この比較結果が出力レジスタ236に取り込まれるとともに、比較結果に応じた制御信号が比較結果処理回路230にて生成されて比較電圧生成回路210のスイッチが制御される。

50

## 【 0 0 4 3 】

以降、MSBから下位nビット目まで $1/2^{(n+1)}$ (VRH-VRL)-(Vain-Vinv)と、閾値電圧(Vinvt)との電位差を比較し、比較結果を出力(OUT)222に出力することにより、MSBから LSBまでのnビットの出力コードが順次確定されて出力レジスタ236にそれぞれが順次取り込まれる。出力コードがLSBまで確定すると出力レジスタ236は、nビットのA/D変換結果として保持値を出力する。

## 【 0 0 4 4 】

以上説明したように、図1に示した第1の実施例によれば、制御信号入力端子153に接続したドライブ能力が大のPchTr 101,102によって、内部サンプルホールドキャパシタ129に入力電圧の電荷をより高速に蓄積することができ、PchTr 101,102をオフ状態にした後に、制御タイミングを変えてドライブ能力が小のPchTr 151,152をオフ状態に駆動することで、オフセット誤差を無くし、スイッチングノイズによる影響を抑えて、より高精度のアナログ電圧の比較を行うことできる容量ラダー型D/A変換器(比較電圧生成回路)とチヨツパコンパレータとを有する逐次比較型A/D変換器が提供される。10

## 【 0 0 4 5 】

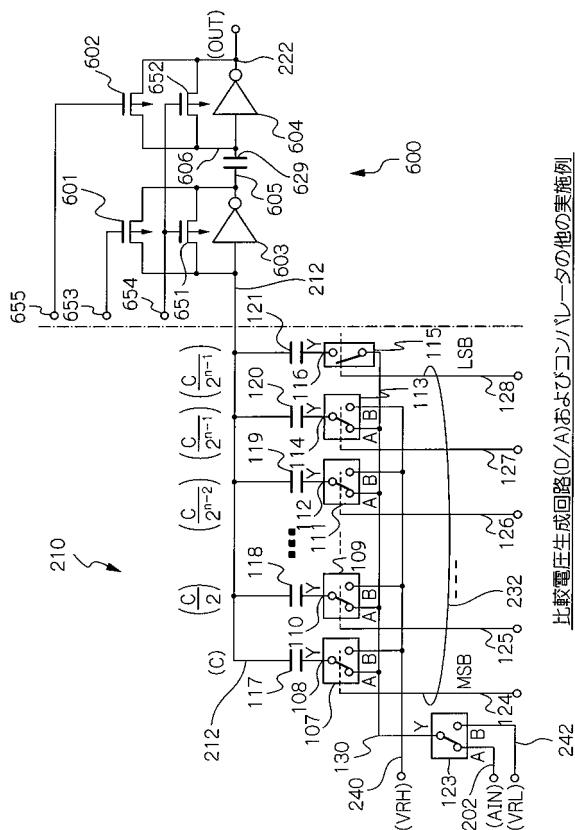

次に図6を参照して、逐次比較型A/D変換器に内蔵される比較電圧生成回路およびコンパレータの他の実施例を説明する。本実施例における全体ブロックは、図2に示した構成と同様の構成でよく、また、比較電圧生成回路についても図1に示した第1の実施例における比較電圧生成回路210と同様の構成でよい。本実施例では、比較電圧生成回路のノード212に接続されるコンパレータ600が、そのPchTr 601,602の各ゲートに個別に制御信号を所定タイミングにて供給する点で第1の実施例と異なり、基本構成は、コンパレータ220と同様である。20

## 【 0 0 4 6 】

詳しくはコンパレータ600は、比較電圧生成回路210の出力ノード212にインバータ603の入力と各PchTr 601,651のドレインとが接続され、インバータ603の出力は、各PchTr 601,651のソースとキャパシタ629の一方の電極とが接続され、キャパシタ629の他方の電極はインバータ604の入力に接続されている。インバータ603,604は、それぞれ入力を閾値電圧(Vinvt)を基準にして反転出力する反転回路であり、インバータ604の入力はさらに各PchTr 602,652のドレインが接続され、インバータ604の出力は各PchTr 602,652のソースが接続されている。このような容量カップリング接続により、キャパシタ629はインバータ603,604の閾値電圧の差(オフセット電圧差)をキャンセルする。このようにインバータ603の出入力端にはPchTr 601,651がそれぞれ並列接続されてインバータ帰還スイッチを形成し、インバータ604の出入力端にPchTr 602,652がそれぞれ並列接続されてインバータ帰還スイッチを形成している。インバータ604の出力はコンパレータ600の出力(OUT)222を形成している。30

## 【 0 0 4 7 】

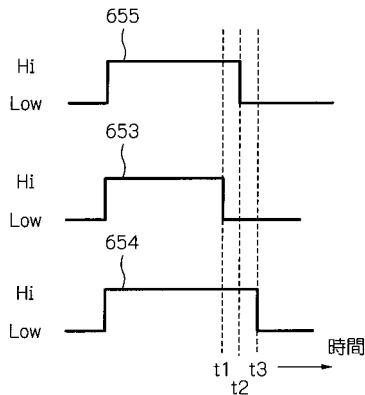

さらに、PchTr 601のゲートは制御入力端子653に接続され、PchTr 602のゲートは制御入力端子655に接続され、PchTr 651,652の各ゲートは共通に制御入力端子654に接続されている。制御入力端子655,653,654に入力される制御信号のタイミング波形例を図7に示す。図示するようにハイ(Hi)レベル状態の制御信号653が時間t1にて最初にロウ(Low)レベルになり、これに遅れて次に制御信号655が時間t2にてロウ(Low)レベルに変化し、これに遅れてさらに次に制御信号654が時間t3にてロウ(Low)レベルに変化する。PchTr 601,602,651,652は、これら制御信号653,655,654に応動してオフ状態とオン状態とが切り替え駆動される。これら制御信号655,653,654は、たとえば図2に示した制御回路250から与えられる。40

## 【 0 0 4 8 】

本実施例における各PchTrのドライブ能力(W/L比)の大小関係は、PchTr 601>PchTr 602>PchTr 651>PchTr 652に設定されている。これら異なるトランジスタのドライブ能力の大小は、図1に示した第1の実施例と同様に、たとえば「4:1」ないし「16:1」などの大小比が適用される。50

## 【0049】

以上の構成で本実施例における逐次比較型A/D変換器200に内蔵される比較電圧生成回路210およびコンパレータ220の動作を説明する。

## 【0050】

まず、比較電圧生成回路210のアナログ入力(AIN) 202にアナログ入力電圧(Vain)が印加されるとき、切替スイッチ123と切替スイッチ107, 109, ..., 111, 113は、それぞれ端子Aがオン状態となり、スイッチ115もオン状態となっている。さらに、制御入力端子653, 655に入力される制御信号653, 655によりPchTr 601, 602がそれぞれオン状態となり、同時に制御入力端子654に入力される制御信号654によりPchTr 651, 652がそれぞれオン状態となる。PchTr 601, 602は、それぞれ並列に接続された他方のトランジスタよりもドライブ能力が大きいため、PchTr 601, 602は、キャパシタ629に総量2Cの電荷をより高速にセトリングレベルまで蓄積する。10

## 【0051】

キャパシタ117, 118, ..., 119, 120, 121の総和2Cの全容量に、アナログ電圧(Vain)とインバータ603の閾値電圧(Vinvt)との電位差をもつ電荷2C(Vain-Vinvt)が蓄積される。次に、制御信号653によりPchTr 601がオフし、次にタイミングを遅らせた制御信号655によりPchTr 602がオフする。このときPchTr 651, 652はまだオン状態が維持されている状態にあり、スイッチングノイズによる電荷ズレが補正される。

## 【0052】

次に制御信号654によりPchTr 651, 652をオフする。PchTr 651, 652はそれぞれ並列に接続された他方のトランジスタよりもドライブ能力(W/Lが小さい)が小さいため、スイッチングノイズを最小限に抑えた状態でスイッチをオフすることができる。これにより、インバータ603, 204はノード212に電位変化が生じた場合、出力(OUT) 222に"H"または"L"を出力する。このとき各インバータ603, 604の閾値電圧の差(オフセット電圧差)はキャパシタ629にてキャンセルされる。20

## 【0053】

さらに次の状態としてスイッチ107の端子Bをオン状態に切り替えて、同時にスイッチ123の端子Bをオン状態にすると、スイッチ107の出力端子Yのノード108はフルスケール基準電圧(VRH)となり、スイッチ109, 111, 113, 115の出力端子Yのノード110, 112, 114, 116は全てゼロスケール基準電圧(VRL)となる。このとき総和容量2Cに蓄積された電荷2C(Vain-Vinvt)は一定であり、電荷分配によりノード212の電位は $1/2(VRH-VRL)-(Vain-Vinvt)$ となる。するとインバータ103は閾値電圧(Vinvt)との電位差を反転して出力し、最終的に出力端子(OUT) 222に入力電圧(Vain)と $1/2(VRH-VRL)$ との大小を比較し"H"または"L"を出力する。この逐次比較動作によりMSBが確定し、その比較結果が比較結果処理回路230を介して出力レジスタ236(図2)に取り込まれる。30

## 【0054】

その後、比較結果処理回路230は、MSBの大小比較結果に応じて、スイッチ107は端子Aがオン状態となり、同時にスイッチ109は端子Bがオン状態となり、他のスイッチ111から116はそのままの状態とする制御信号を比較電圧生成回路210に与える。

## 【0055】

次いで上記と同様に、各キャパシタの容量の重み付けによってノード212は、 $1/4(VRH-VRL)-(Vain-Vinvt)$ となり、逐次比較動作を行って、MSBから下位1ビットにおける比較結果が出力端子(OUT) 222に出力される。この比較結果が出力レジスタ236に取り込まれるとともに、大小比較結果に応じた制御信号が比較結果処理回路230にて生成されて比較電圧生成回路210のスイッチが制御される。40

## 【0056】

以降さらに、MSBから下位nビット目まで $1/2^{(n+1)}(VRH-VRL)-(Vain-Vinvt)$ と閾値電圧(Vinvt)との電位差を比較し、比較結果を出力(OUT) 222に出力することにより、MSBからLSBまでのnビットの出力コードが確定されて出力レジスタ236にそれが順次取り込まれる。出力コードがLSBまで確定すると出力レジスタ236はnビットのA/D変換結果として

保持値を出力する。

#### 【0057】

以上説明したように、図6に示した第2の実施例によれば、制御信号入力端子653に接続したドライブ能力(W/L比)の大きいPchTr601と制御信号655に接続したPchTr 202によって、より高速に内部サンプルホールドキャパシタ629に入力電圧の電荷を蓄積することができる。さらに制御タイミングを、第一段目のPchTr 601を先にオフし、第二段目のPchTr 602をその後にオフに制御することによって、同時スイッチングによって一時的にオフセットが大きくなる問題を抑えることができる。

#### 【0058】

また、第1の実施例と同様に制御タイミングを変えて、PchTr 601,602をオフ状態にした後に、ドライブ能力の小さいPchTr 651,652をオフ状態にすることにより、ゲインが低くなる原因の一つであるオフセット誤差を無くして、スイッチングノイズの影響をより少なくすることができる。この結果、より高精度のアナログ電圧の比較を行うことできる容量ラダー型D/A変換器(比較電圧生成回路)とチョッパコンパレータとを有するA/D変換器が提供される。

#### 【0059】

また、コンパレータ600のキャパシタ629の容量は、比較電圧生成回路210内のサンプルホールド用キャパシタ117～121の総和容量に比較して、小さく設定することができるので、第二段目のPchTr 602,652のサイズをより小さくすることができ、スイッチングノイズをさらに抑えることができ、また、チップ面積を小さくすることができる。

#### 【0060】

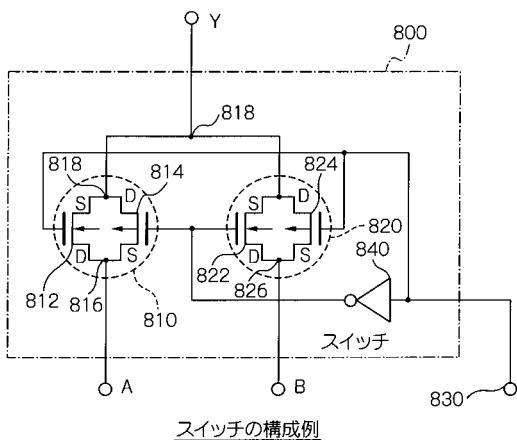

なお、図1および図6に示した各実施例における比較電圧生成回路210に備えられているスイッチ107,109,...,111,113,115のスイッチを、それぞれ、たとえば図8に示すスイッチ回路構成とし、また、スイッチ115をたとえば図9に示すスイッチ回路構成とすることができる。

#### 【0061】

図8に示すスイッチ回路800は、制御入力端子AにCMOSアナログスイッチ810が接続され、制御入力端子BにCMOSアナログスイッチ820が接続されている。CMOSアナログスイッチ810は、NchTr 812とPchTr 814とを含み、制御入力端子AはNchTr 812のドレインとPchTr 814のソースにノード816にて接続され、NchTr 812のソースとPchTr 814とのドレインはノード818にて接続されるとともに、スイッチ回路800の出力端子Yに接続されている。

#### 【0062】

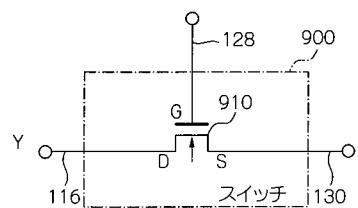

また、CMOSアナログスイッチ820は、NchTr 822とPchTr 824とを含み、制御入力端子BはNchTr 822のドレインとPchTr 824のソースにノード826にて接続され、NchTr 822のソースとPchTr 824とのドレインはノード818を介して出力端子Yに接続されている。NchTr 812とPchTr 824との各ゲートがともに接続され、さらに制御入力端子830が接続される。制御入力端子830はさらにインバータ840を介して、PchTr 814とNchTr 822との各ゲートに接続されている。また、図1および図6に示した各実施例におけるスイッチ115は、図9に示すように、たとえば、NchTr 910によるNMOSスイッチ回路900を構成することができる。

#### 【0063】

図1および図6に示した切替スイッチ107～120の内部回路構成を、図8に示した回路800のように構成した場合に、CMOSアナログスイッチ820のサイズ、つまり内蔵しているトランジスタ822,824のサイズを以下の関係で小さくするとよい。すなわち、キャパシタ117～120の容量C, C/2, C/2<sup>2</sup>, ..., C/2<sup>(n-2)</sup>, C/2<sup>(n-1)</sup>, C/2<sup>(n-2)</sup>に比例して切替スイッチ107～113内のCMOSアナログスイッチサイズを小さく設定し、スイッチ107>スイッチ110>,...>スイッチ111>スイッチ113の大小関係とする。なお、スイッチ113とスイッチ115とは同じスイッチサイズでよい。

#### 【0064】

以上のような構成により、キャパシタのサイズC, C/2, C/2<sup>2</sup>, ..., C/2<sup>(n-2)</sup>, C/2<sup>(n-1)</sup>, C/2<sup>(n-2)</sup>に比例して切替スイッチ内のCMOSアナログスイッチサイズを小さく設定するこ

10

20

20

30

40

50

とができるため、チップサイズをより小さくでき、さらにスイッチングノイズを影響を抑えることができる。

#### 【0065】

以上、各実施例では、コンパレータ回路220,600のスイッチをPchTrで構成したが、インバータの閾値電圧の設定によってNチャネル型トランジスタ(NchTr)で構成することもでき、また、CMOSアナログスイッチにて構成することもできる。また、コンパレータ回路210,600をCカップリングオフセットキャンセル2段構成として説明したが、これに限らず、3段、4段構成としてゲインをあげることもできる。また、実施例では、容量重み付けのCラダー型D/A変換器(比較電圧生成回路)およびコンパレータとして構成したが、チヨツパー・コンパレータの制御方式に有利に適用することができる。

10

#### 【図面の簡単な説明】

#### 【0066】

【図1】逐次比較型A/D変換器に内蔵される比較電圧生成回路(D/A)およびコンパレータの構成例を示すブロック図である。

【図2】逐次比較型A/D変換器の実施例を示すブロック図である。

【図3】ドライブ能力が大であるトランジスタの概略を示す平面図である。

【図4】ドライブ能力が小であるトランジスタの概略を示す平面図である。

【図5】コンパレータに供給される制御信号のタイミング波形図である。

【図6】逐次比較型A/D変換器に内蔵される比較電圧生成回路(D/A)およびコンパレータの他の実施例を示すブロック図である。

20

【図7】コンパレータに供給される制御信号のタイミング波形図である。

【図8】比較電圧生成回路に配置されるスイッチの構成例を示す図である。

【図9】比較電圧生成回路に配置されるスイッチの構成例を示す図である。

#### 【符号の説明】

#### 【0067】

101,102,151,152 Pチャネル型トランジスタ(PchTr)

103,104 インバータ

107,109,111,113,115,123 スイッチ

117,118,119,120,121,129 キャパシタ

210 比較電圧生成回路(D/A)

30

220 コンパレータ

【図1】

【図2】

【図3】

【図5】

【図4】

【 四 6 】

【 図 7 】

#### 制御信号のタイミング波形

【図8】

## スイッチの構成例

【 図 9 】

## スイッチの構成例