#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO~2014/018791~Al

- (51) International Patent Classification: *G01R 19/00* (2006.01)

- (21) International Application Number:

PCT/US20 13/052 122

(22) International Filing Date:

25 July 2013 (25.07.2013)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

13/558,1 17

25 July 2012 (25.07.2012)

US

- (71) Applicant: QUALCOMM INCORPORATED [US/US]; Attn: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121 (US).

- (72) Inventors: YU, Baiying; 5775 Morehouse Drive, San Diego, California 92121 (US). BAJAJ, Nihit; 5775 Morehouse Drive, San Diego, California 92121 (US). STOCK-STAD, Troy; 5775 Morehouse Drive, San Diego, California 92121 (US). MIKUTEIT, Eric I.; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (74) Agent: HOOKS, William M.; Attn: International IP Administration, 5775 Morehouse Drive, San Diego, Califonia 9212 1 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, FT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to applyfor and be granted a patent (Rule 4.17(H))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(in))

[Continued on nextpage]

(54) Title: METHOD AND APPARATUS FOR TEMPERATURE ADJUSTED CONTROL OF BATFET CURRENT SENSING

(57) Abstract: A method and apparatus for providing a temperature sensing loop used in connection with a current sensing component, such as a BATFET, in order to compensate for variations in the BATFET's resistance due to temperature variations. The temperature sensing loop detects a temperature of the BATFET and regulates the gate voltage of the BATFET based on the detected temperature in order to compensate for changes in the BATFET's resistance. The temperature sensing feedback loop maintains the BATFET at a constant resistance for current sensing through negative feedback control. The BATFET and temperature sensing loop can be provided as components of an on-chip fuel gauging application for a UE.

# **Published:**

— with international search report (Art. 21(3))

1

# METHOD AND APPARATUS FOR TEMPERATURE ADJUSTED CONTROL OF BATFET CURRENT SENSING

### **BACKGROUND**

#### **Field**

[0001]

The present disclosure relates generally to a method and apparatus for temperature adjusted control of BATFET current sensing, and more particularly to such control of BATFET current sensing in fuel gauging applications.

# **Background**

[0002]

Wireless communication systems are widely deployed to provide various telecommunication services such as telephony, video, data, messaging, and broadcasts. Typical wireless communication systems may employ multiple-access technologies capable of supporting communication with multiple users by sharing available system resources (e.g., bandwidth, transmit power). Examples of such multiple-access technologies include code division multiple access (CDMA) systems, time division multiple access (TDMA) systems, frequency division multiple access (OFDMA) systems, single-carrier frequency division multiple access (SC-FDMA) systems, and time division synchronous code division multiple access (TD-SCDMA) systems.

[0003]

These multiple access technologies have been adopted in various telecommunication standards to provide a common protocol that enables different wireless devices to communicate on a municipal, national, regional, and even global level. An example of an emerging telecommunication standard is Long Term Evolution (LTE). LTE is a set of enhancements to the Universal Mobile Telecommunications System (UMTS) mobile standard promulgated by Third Generation Partnership Project (3GPP). It is designed to better support mobile broadband Internet access by improving spectral efficiency, lower costs, improve services, make use of new spectrum, and better integrate with other open standards using OFDMA on the downlink (DL), SC-FDMA on the uplink (UL), and multiple-input multiple-output (MIMO) antenna technology. However, as the demand for mobile broadband access continues to increase, there exists a need for further

2

improvements in LTE technology. Preferably, these improvements should be applicable to other multi-access technologies and the telecommunication standards that employ these technologies.

[0004]

The demand for precise fuel gauges for smart phone batteries continues to increase. Such a fuel gauge in user equipment (UE) can be accomplished via current sensing. Typical current sensing relies on an external precision sensing resistor which has a low Temperature Coefficient (TC). Such precision sensing resistors achieve current sensing by inserting a series resistor in the high current path. The voltage drop on the sense resistor is measured and converted to current information in order to track the battery's capacity. A disadvantage of this method of precision sensing is a non-zero insertion loss, e.g., inserting the sense resistor in the high current path degrades the battery efficiency, which reduces the amount of talk time that can be supported by the battery. The industry strives for zero insertion in order to improve battery efficiency.

[0005]

Thus, a need exists for a precise fuel gauge that avoids degradation of the battery efficiency.

## **SUMMARY**

[0006]

In order to accurately monitor the fuel level of a battery in a more effective manner, current sensing can be performed through an on-chip Battery Field-Effect Transistor (BATFET). On-chip BATFET is a switch component that is part of charging circuitry to allow the phone to either stop charging or discharging the battery when needed. The on-chip BATFET provides a more effective current sensing method due to the fact that no extra insertion resistance is placed in the high current path from the battery. Such on-chip BATFET measurements increase the efficiency of the battery measurement, which results in a longer potential talk time.

[0007]

In order to maintain accurate measurements across temperature variations, a temperature sensing loop can be used in connection with the BATFET in order to compensate for variations in the BATFET's resistance due to temperature variations. For example, the temperature sensing loop can be applied to detect the temperature of the BATFET and to regulate the gate voltage of the BATFET based on the detected temperature in order to compensate for changes in the resistance. This provides an elegant temperature sensing and control loop which tracks the temperature variation of an on-chip BATFET and maintains it at a constant

resistance for current sensing through negative feedback control. This can be applied to enable accurate fuel gauging using an on-chip BATFET.

[0008]

By tracking the temperature variation of the on-chip BATFET and modulating the gate voltage of the BATFET to achieve a constant resistance, the BATFET and temperature control loop can perform precise current sensing.

[0009]

The BATFET and feedback loop enable zero insertion current sensing that maximizes battery efficiency while still achieving the required accuracy in the fuel level measurement because it can be accomplished without inserting an additional resistor into the voltage line. The BATFET and control loop, may be provided on a power management integrated circuit (PMIC).

[0010]

Aspects may include an apparatus for temperature sensing control for a current sensing component. The apparatus may include a current sensing component inserted in a voltage line in order to measure current in the voltage line. The apparatus may further include a feedback loop component that tracks a temperature of the current sensing component and modulates the resistance of the current sensing component based on the tracked temperature in order to maintain the current sensing component at a substantially constant resistance.

[0011]

Additional aspects may include a method of adjusting the resistance of a current sensing component to adjust for temperature and process variations. A first voltage is received at a current sensing component inserted in a voltage line. The temperature of the current sensing component is detected via a feedback loop component. Then, the resistance of the current sensing component is adjusted via the feedback loop component based on the detected temperature.

### **BRIEF DESCRIPTION OF THE DRAWINGS**

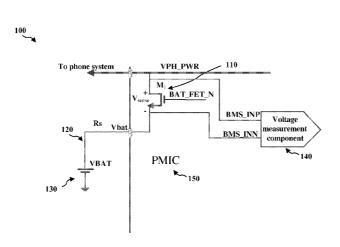

- [0012] FIG. 1 is a diagram illustrating an example system for performing current sensing via a BATFET.

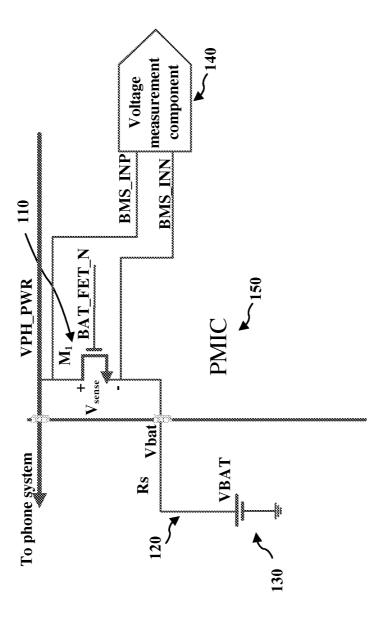

- [0013] FIG. 2 is a diagram illustrating an example system for adjusting the resistance of a current sensing component for temperature changes.

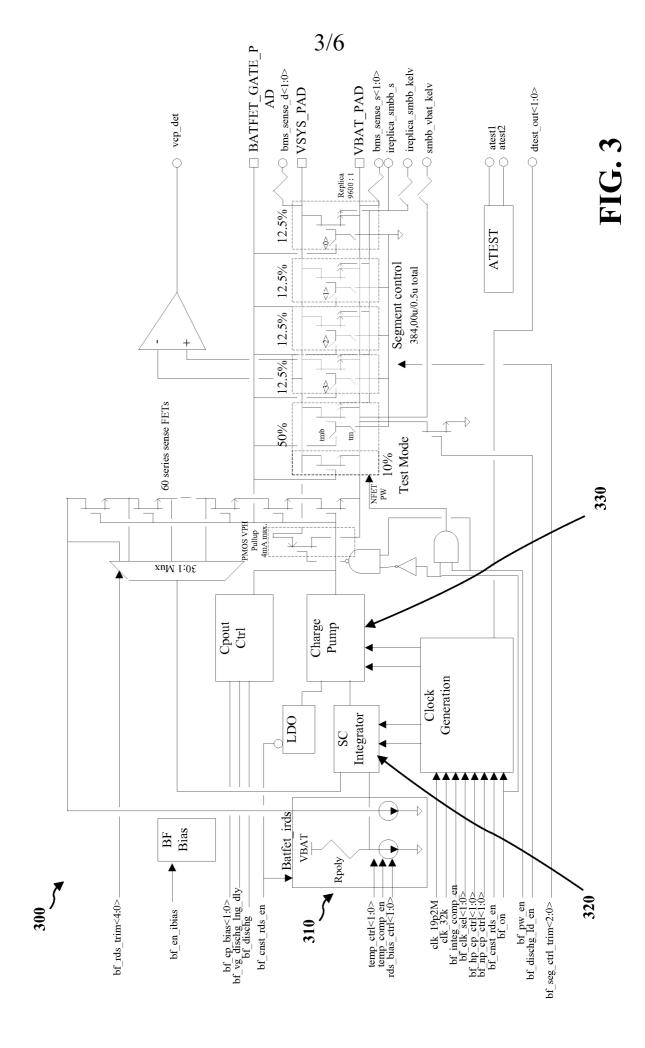

- [0014] FIG. 3 is a diagram illustrating an example of a system using BATFET and a feedback loop.

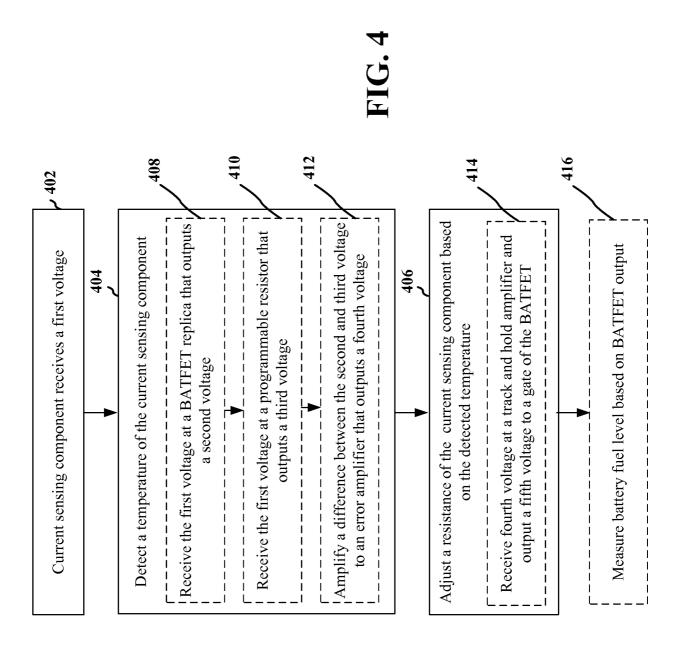

- [0015] FIG. 4 is a flow chart of a method of temperature sensing control for a current sensing component.

4

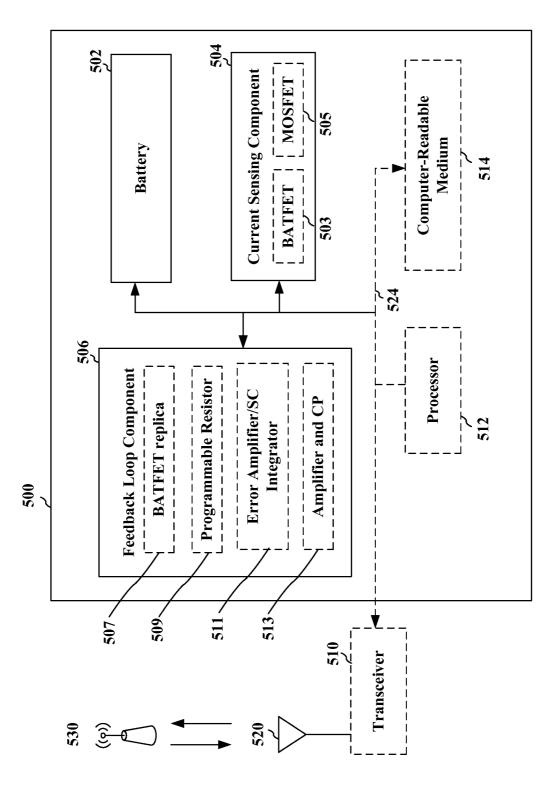

[0016] FIG. 5 is a diagram illustrating an example of a hardware implementation for an apparatus employing a temperature sensing control for a current sensing component.

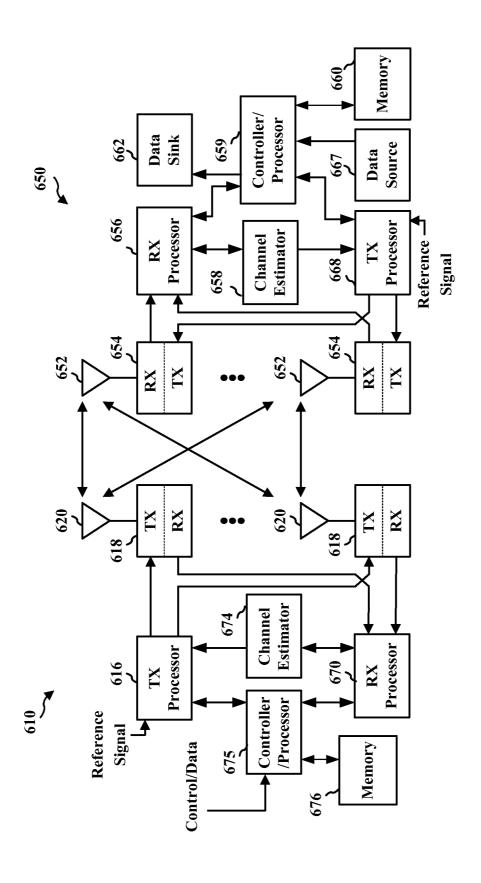

[0017] FIG. 6 is a diagram illustrating an example of an evolved Node B and user equipment in an access network.

#### **DETAILED DESCRIPTION**

[0018] The detailed description set forth below in connection with the appended drawings is intended as a description of various configurations and is not intended to represent the only configurations in which the concepts described herein may be practiced. The detailed description includes specific details for the purpose of providing a thorough understanding of various concepts. However, it will be apparent to those skilled in the art that these concepts may be practiced without these specific details. In some instances, well known structures and components are shown in block diagram form in order to avoid obscuring such concepts.

In order to accurately monitor the fuel level of a battery in a more effective manner, current sensing can be performed through an on-chip Battery Field-Effect Transistor (BATFET). On-chip BATFET is a switch component that is part of charging circuitry to allow the phone to either stop charging or discharging the battery when needed. The on-chip BATFET provides a more effective current sensing method due to the fact that no extra insertion resistance is placed in the high current path from the battery. Such on-chip BATFET measurements increase the efficiency of the battery measurement, which results in a longer potential talk time. Additionally, the BATFET can perform current sensing without any external sensing resistors, because the sensing can implemented using an on-chip BATFET. FIG. 1 illustrates an example diagram for performing BATFET sensing of the fuel level in a battery according to aspects presented herein.

On-chip current sensing with a BATFET makes high side current sensing very attractive because it enables a minimum routing resistance in the high current path by avoiding any additional sensing resistors in the high current path and because it minimizes the number of pins needed for both on-chip BATFET and on-chip fuel gauge sensing. However, a BATFET has a very low impedance (-10 mOhm) and a high temperature coefficient  $\mathbf{R}_{ds}$  (TC=4000 ppm/° C). This results in a  $\pm 24\%$  variation when the temperature varies from -30° C to 90° C. Thus, a BATFET on its own is not feasible for the accuracy required in precision current sensing. The

[0020]

5

technique that uses BATFET for current sensing through current mirror usually has a 5% error at high current and 10% or higher error for low current.

[0021] Requirements for on-chip sensing include, e.g., a minimal resistance added in a high current path of the battery, low temperature sensitivity, and limited process variation. For an accurate measurement, a TC<100ppm/° C is typically required.

[0022] Any use of a BATFET on its own for such current sensing would require a microprocessor to constantly adjust the measured BATFET voltage in order to compensate for the resistance drift based on temperature.

[0023] In order to address the problems associated with inaccuracy across temperature variations, a temperature sensing loop can be used in connection with the BATFET in order to compensate for variations in the BATFET's resistance due to temperature variations. For example, the temperature sensing loop can be applied to detect a temperature of the BATFET and to regulate the gate voltage of the BATFET based on the detected temperature in order to compensate for changes in the resistance.

By tracking the temperature variation of the on-chip BATFET and modulating the gate voltage of the BATFET to achieve a constant resistance, the BATFET and temperature control loop can perform precise current sensing. This enables a BATFET resistance  $R_{ds}$  having an extremely low TC (e.g., TC<100 ppm/ $^{\circ}$  C) to be used for precise fuel gauge applications. Such a BATFET enables highly accurate current sensing, e.g., for monitoring the fuel level of a battery in a UE, because the current information from the BATFET can be precisely derived.

FIG. 1 illustrates an example circuit diagram 100 for performing BATFET sensing of the fuel level in a battery 130. As illustrated in FIG. 1, a BATFET 110 can be provided in the high current path 120 from the battery 130. BATFET may be connected to a voltage measurement component 140 as a part of the fuel gauge. BATFET 110 may be provided on a power management integrated circuit (PMIC) 150. FIG. 1 illustrates that current sensing may be performed in the high current path without providing an additional resistor in the high current path. This leads to higher efficiency and provides a longer talk time for a UE. No external sensing resistor is required, because sensing is implemented using a pre-existing on-chip BATFET.

[0026] FIG. 2 illustrates such a BATFET 210 having negative feedback control. The illustrated BATFET receives the high side voltage Vbat 220 from the battery 230 at its source and outputs voltage VPH\_PWR from its drain. The gate of the BATFET

210 is connected to a negative feedback loop comprising BATFET replica 240, programmable resistor 250, and error amplifier 260. BATFET 210 has a resistance R2. BATFET 210 may be resized in order to achieve a nominal 10 mOhm.

[0027]

BATFET replica 240 receives Vbat at its source and outputs a voltage Vmos from its drain. BATFET replica 240 has a resistance Rl. BATFET replica 240 outputs Vmos to an input of error amplifier 260. The gate of replica 240 connected to the gate of BATFET 210. BATFET replica 240 is on a much smaller scale than BATFET 210, e.g., on the order of 500,000 to 1. For example, the BATFET may be approximately 10 mohm and the BATFET replica may be approximately 5kohm. A typical reference voltage may be 25mV.

[0028]

The programmable resistor 250 receives Vbat and outputs Vr to an input of error amplifier 260. The programmable resistor 250 has a resistance Rr and a very low temperature coefficient. Rr is programmable in order to compensate for the process variation between R1 and Rr. Rr is programmed to substantially match R1 at a certain temperature. For example, Rr may be set to substantially match R1 at room temperature with less than 10% variation. This variation can be calibrated through a one-time calibration. The programmable resistor 250 may comprise an on-chip P+ poly having TC = -100 ppm/C.

[0029]

Alternately, instead of the programmable resistor 250, the sense point of the BATFET replica may be adjusted. For example, the BATFET replica may comprise a plurality of field effect transistors (FET) in series such that the BATFET replica is programmable by selecting an amount of the plurality of FETs used in the BATFET replica.

[0030]

The BATFET replica may comprise a series of sense FETs biased by the sense current, in order to achieve a high ratio. Additionally, a multiplexer (MUX) may be used to trim the sense point of the BATFET replica to center the loop bias point, e.g. RDS(on), as illustrated in FIG. 3.

[0031]

Error amplifier 260 receives Vr at a first input and Vmos at a second input and outputs an amplified difference between the two received voltages. In this example, error amplifier 260 outputs Av\*(Vmos-Vr). The gain provided by the feedback amplifier biases the BATFET to the appropriate level to equalize the reference and sense inputs.

[0032]

The output of error amplifier 260 is input to amplifier and charge pump (CP) 270 which output VB+Vbat to the gate of BATFET 210 and BATFET replica 240 in

order to adjust for changes in the resistance due to a temperature variation. Thus, the resistance of both BATFET 210 and BATFET replica 240 track each other. Error amplifier 260 may be implemented as a switch cap integrator (SC Integrator). Such an SC integrator may comprise an auto-zeroed integrator that compensates for input offset, common mode rejection errors from the amplifier, gain error, and power supply changes. For example, with a 75 kHz clock, the loop bandwidth (BW) may be approximately 12.5 kHz. Amplifier 270, e.g., a track and hold amplifier, decouples settling requirements and the charge pump capacitive load.

[0033] When the temperature varies, the output impedance of BATFET 210 and its

210, R2 can be maintained at a constant resistance.

replica 240 will vary also. However, due to the low TC, Rr of programmable resistor 250 will remain the same. Although Rr was programmed to match Rlto compensate process mismatch between R1 and Rr within 10% difference, R1 varies with the change in temperature in the same manner as R2 of BATFET 210, while Rr does not vary. The voltage difference between Vmos from replica 240 and VR from programmable resistor 250 will be sensed and amplified by error amplifier 260. Thereafter, the amplified difference undergoes control via a track and hold amplifier and a charge pump 270 before being output to the gate of BATFET 210. Through this negative feedback, the gate voltage of BATFET 210 will be regulated to keep Vmos at the same voltage level of VR. By modulating the gate voltage of BATFET

[0034]

Although the resistance R<sub>ds</sub> of a BATFET may have a ±40% process variation, a one-time calibration can be performed on an Automatic Testing Equipment (ATE) so its resistance can be stored in non-volatile memory. Or R<sub>ds</sub> can be made with segments and its resistance can be coarsely adjusted where low resistance variation is demanded. For example, with two programmable bits, the process variation can be reduced to  $\pm 10\%$ .

[0035]

A BATFET and feedback loop enables zero insertion current sensing, e.g., that maximizes battery efficiency while still achieving the required high accuracy.

[0036]

The BATFET and control loop, may be provided on a PMIC, e.g., PMIC 150 as illustrated in FIG. 1. A PMIC may comprise integrated circuits or a system block in a system-on-a-chip device for managing power consumption. A PMIC may provide battery management, voltage regulation, or charging functions, etc.

8

[0037]

FIG. 3 illustrates a detailed block diagram 300 of a BATFET 310 and feedback loop. Feedback loop may comprise an integrator 320 having a clock rate between 75kHz to 10kHz and a charge pump 330 having a charge pump clock rate between 19.2MHz to 32kHz. A track and hold buffer may be provided between integrator 320 and charge pump 330 to allow separate clock control. The BATFET contains five segments so its total resistance can be programmable to reduce process variation.

[0038]

Although examples have been described in connection with a fuel gauge and with a fuel gauge on a UE, the aspects described herein can be applied to other situations requiring stable on chip MOSFET or BATFET performance across a variable temperature range.

[0039]

FIG. 4 illustrates a flow chart 400 of a method of adjusting a resistance of a current sensing component to adjust for temperature and process variations. The method may be performed by a UE, and more specifically by a current sensing component and feedback loop provided on a PMIC of the UE. The current sensing component may be inserted in the voltage line on the top side of the battery. At step 402, the current sensing component receives a first voltage. As the current sensing component may be inserted on the top side of the battery, the first voltage may comprise a high side voltage from the battery. At step 404, a temperature of the current sensing component is detected via a feedback loop component. At 406, a resistance of the current sensing component is adjusted via the feedback loop component based on the detected temperature. The resistance of the current sensing component is adjusted based on the tracked temperature in order to regulate the resistance of the current sensing component to a substantially constant value. By tracking the temperature of the current sensing component and adjusting its resistance accordingly, the resistance of the current sensing component is adjusted in real time in order to maintain it at a substantially constant value. By maintaining a constant resistance, an accurate measurement of the current can be provided regardless of the temperature.

[0040]

The current sensing component may comprise any of a Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) and a BATFET, as illustrated e.g., in FIGs. 1-2. For example, as illustrated in FIG. 2, the current sensing component may comprise a BATFET. The gate voltage of the BATFET may be

9

modulated based on the detected temperature in order to adjust the resistance of the BATFET.

[0041]

Additional, optional steps are illustrated with a dotted line. At step 408, the first voltage is received at a BATFET replica. The BATFET replica then outputs a second voltage. In the example, in FIG. 2, BATFET replica 240 receives Vbat and outputs Vmos. At step 410, the first voltage is also received at a programmable resistor that outputs a third voltage. In the example in FIG. 2, programmable resistor 250 receives Vbat and outputs VR. At 412, a difference between the second voltage and the third voltage is amplified at an error amplifier that outputs a fourth voltage. The error amplifier may comprise a switch cap integrator. In FIG. 2, error amplifier 260 amplifies the difference between Vmos and VR and outputs Av\*(Vmos-VR). At 414, the fourth voltage is received at a track and hold amplifier, and a fifth voltage is output from the track and hold amplifier to a gate of the BATFET. FIG. 2 illustrates CP 270 receiving the output from the error amplifier 260 and outputting VB+Vbat to the gate of BATFET 210 in order to regulate the resistance of BATFET 210 to adjust for any changes in resistance due to a change in temperature.

[0042]

Although aspects may be used for other applications, at step 416, the fuel level of the battery may be measured based on an output from the current sensing component, e.g., BATFET. The BATFET and feedback loop may be comprised within a UE, e.g., as a component of the UE's PMIC. The resistance of the current sensing component may be programmed in segments through digital control in order to reduce process variation. In this case, a single calibration may be performed to eliminate process variation in the resistance of the current sensing component.

[0043]

FIG. 5 is a diagram 500 illustrating an example of a hardware implementation for an apparatus 500 employing temperature sensing control for a current sensing component. The apparatus comprises a current sensing component 504. The current sensing component 504 is inserted in a voltage line from a battery 502 of the apparatus and measures current in the voltage line. The current sensing component may comprise any of a BATFET 503 and a MOSFET 505. The apparatus comprises a feedback loop component 506 that tracks a temperature of the current sensing component and modulates a resistance of the current sensing component based on the tracked temperature. The feedback loop modulates the resistance of the current

10

sensing component in order to regulate the resistance of the current sensing component to a substantially constant resistance.

[0044]

The feedback loop component may detect the temperature of the BATFET and modulate the gate voltage of the BATFET based on the detected temperature. The BATFET may receive a first voltage in the voltage line. The feedback loop component may comprise a BATFET replica 513 that receives the first voltage and outputs a second voltage, a programmable resistor 509 that receives the first voltage and outputs a third voltage, an error amplifier 511 that receives the second voltage and the third voltage and outputs a fourth voltage, and a second amplifier 513 that receives the fourth voltage and outputs a fifth voltage to the gate of the BATFET 503. The error amplifier 511 may comprise a switch cap integrator. The BATFET 503 may be configured to receive a high side voltage from the battery 502 at a source of the BATFET.

[0045]

The BATFET may measure a fuel level of the battery. The apparatus may comprise a UE, and the BATFET may measure a fuel level of the UE's battery. The current sensing component and feedback loop component may be comprised in a PMIC of the UE.

[0046]

In this example, the UE may further comprise a transceiver 510 having an antenna 520 for communicating with node 530. Such a UE may further include a processor 512 and computer readable medium 514. The transceiver 510 provides a means for communicating with various other apparatus over a transmission medium. The processor 512 is responsible for general processing, including the execution of software stored on the computer-readable medium 514. The software, when executed by the processor 512, may cause the system to perform the various functions described *supra* for any particular apparatus. The computer-readable medium 514 may also be used for storing data that is manipulated by the processor 512 when executing software.

[0047]

FIG. 6 is a block diagram of an evolved Node B (eNB) 610 in communication with a UE 650 in an access network. In the downlink (DL), upper layer packets from the core network are provided to a controller/processor 675. The controller/processor 675 implements the functionality of the L2 layer. In the DL, the controller/processor 675 provides header compression, ciphering, packet segmentation and reordering, multiplexing between logical and transport channels, and radio resource allocations to the UE 650 based on various priority metrics. The

11

controller/processor 675 is also responsible for hybrid automatic repeat request (HARQ) operations, retransmission of lost packets, and signaling to the UE 650.

[0048]

The transmit (TX) processor 616 implements various signal processing functions for the LI layer (i.e., physical layer). The signal processing functions includes coding and interleaving to facilitate forward error correction (FEC) at the UE 650 and mapping to signal constellations based on various modulation schemes (e.g., binary phase-shift keying (BPSK), quadrature phase-shift keying (QPSK), M-phaseshift keying (M-PSK), M-quadrature amplitude modulation (M-QAM)). The coded and modulated symbols are then split into parallel streams. Each stream is then mapped to an orthogonal frequency division multiple access (OFDM) subcarrier, multiplexed with a reference signal (e.g., pilot) in the time and/or frequency domain, and then combined together using an Inverse Fast Fourier Transform (IFFT) to produce a physical channel carrying a time domain OFDM symbol stream. The OFDM stream is spatially precoded to produce multiple spatial streams. Channel estimates from a channel estimator 674 may be used to determine the coding and modulation scheme, as well as for spatial processing. The channel estimate may be derived from a reference signal and/or channel condition feedback transmitted by the UE 650. Each spatial stream is then provided to a different antenna 620 via a separate transmitter 618TX. Each transmitter 618TX modulates an RF carrier with a respective spatial stream for transmission.

[0049]

At the UE 650, each receiver 654RX receives a signal through its respective antenna 652. Each receiver 654RX recovers information modulated onto an RF carrier and provides the information to the receive (RX) processor 656. The RX processor 656 implements various signal processing functions of the LI layer. The RX processor 656 performs spatial processing on the information to recover any spatial streams destined for the UE 650. If multiple spatial streams are destined for the UE 650, they may be combined by the RX processor 656 into a single OFDM symbol stream. The RX processor 656 then converts the OFDM symbol stream from the time-domain to the frequency domain using a Fast Fourier Transform (FFT). The frequency domain signal comprises a separate OFDM symbol stream for each subcarrier of the OFDM signal. The symbols on each subcarrier, and the reference signal, is recovered and demodulated by determining the most likely signal constellation points transmitted by the eNB 610. These soft decisions may be based on channel estimates computed by the channel estimator 658. The soft

decisions are then decoded and deinterleaved to recover the data and control signals that were originally transmitted by the eNB 610 on the physical channel. The data and control signals are then provided to the controller/processor 659.

[0050]

The controller/processor 659 implements the L2 layer. The controller/processor can be associated with a memory 660 that stores program codes and data. The memory 660 may be referred to as a computer-readable medium. In the UL, the controller/processor 659 provides demultiplexing between transport and logical channels, packet reassembly, deciphering, header decompression, control signal processing to recover upper layer packets from the core network. The upper layer packets are then provided to a data sink 662, which represents all the protocol layers above the L2 layer. Various control signals may also be provided to the data sink 662 for L3 processing. The controller/processor 659 is also responsible for error detection using an acknowledgement (ACK) and/or negative acknowledgement (NACK) protocol to support HARQ operations.

[0051]

In the UL, a data source 667 is used to provide upper layer packets to the controller/processor 659. The data source 667 represents all protocol layers above the L2 layer. Similar to the functionality described in connection with the DL transmission by the eNB 610, the controller/processor 659 implements the L2 layer for the user plane and the control plane by providing header compression, ciphering, packet segmentation and reordering, and multiplexing between logical and transport channels based on radio resource allocations by the eNB 610. The controller/processor 659 is also responsible for HARQ operations, retransmission of lost packets, and signaling to the eNB 610.

[0052]

Channel estimates derived by a channel estimator 658 from a reference signal or feedback transmitted by the eNB 610 may be used by the TX processor 668 to select the appropriate coding and modulation schemes, and to facilitate spatial processing. The spatial streams generated by the TX processor 668 are provided to different antenna 652 via separate transmitters 654TX. Each transmitter 654TX modulates an RF carrier with a respective spatial stream for transmission.

[0053]

The UL transmission is processed at the eNB 610 in a manner similar to that described in connection with the receiver function at the UE 650. Each receiver 618RX receives a signal through its respective antenna 620. Each receiver 618RX recovers information modulated onto an RF carrier and provides the information to a RX processor 670. The RX processor 870 may implement the LI layer.

[0054]

The controller/processor 675 implements the L2 layer. The controller/processor 675 can be associated with a memory 676 that stores program codes and data. The memory 876 may be referred to as a computer-readable medium. In the UL, the control/processor 675 provides demultiplexing between transport and logical channels, packet reassembly, deciphering, header decompression, control signal processing to recover upper layer packets from the UE 650. Upper layer packets from the controller/processor 675 may be provided to the core network. The controller/processor 675 is also responsible for error detection using an ACK and/or NACK protocol to support HARQ operations.

[0055]

Several aspects have been presented with reference to various apparatus and methods. These apparatus and methods will be described in the following detailed description and illustrated in the accompanying drawings by various blocks, modules, components, circuits, steps, processes, algorithms, etc. (collectively referred to as "elements"). These elements may be implemented using electronic hardware, computer software, or any combination thereof. Whether such elements are implemented as hardware or software depends upon the particular application and design constraints imposed on the overall system.

[0056]

By way of example, an element, or any portion of an element, or any combination of elements may be implemented with a "processing system" that includes one or more processors. Examples of processors include microprocessors, microcontrollers, digital signal processors (DSPs), field programmable gate arrays (FPGAs), programmable logic devices (PLDs), state machines, gated logic, discrete hardware circuits, and other suitable hardware configured to perform the various functionality described throughout this disclosure. One or more processors in the processing system may execute software. Software shall be construed broadly to mean instructions, instruction sets, code, code segments, program code, programs, subprograms, software modules, applications, software applications, software packages, routines, subroutines, objects, executables, threads of execution, procedures, functions, etc., whether referred to as software, firmware, middleware, microcode, hardware description language, or otherwise.

[0057]

Accordingly, in one or more exemplary embodiments, the functions described may be implemented in hardware, software, firmware, or any combination thereof. If implemented in software, the functions may be stored on or encoded as one or more instructions or code on a computer-readable medium. Computer-

WO 2014/018791

14

PCT/US2013/052122

readable media includes computer storage media. Storage media may be any available media that can be accessed by a computer. By way of example, and not limitation, such computer-readable media can comprise RAM, ROM, EEPROM, CD-ROM or other optical disk storage, magnetic disk storage or other magnetic storage devices, or any other medium that can be used to carry or store desired program code in the form of instructions or data structures and that can be accessed by a computer. Disk and disc, as used herein, includes compact disc (CD), laser disc, optical disc, digital versatile disc (DVD), floppy disk and Blu-ray disc where disks usually reproduce data magnetically, while discs reproduce data optically with lasers. Combinations of the above should also be included within the scope of computer-readable media.

[0058]

Furthermore, various aspects are described herein in connection with a terminal, which can be a wired terminal or a wireless terminal. A terminal can also be called a system, device, subscriber unit, subscriber station, mobile station, mobile, mobile device, remote station, remote terminal, access terminal, user terminal, communication device, user agent, user device, or user equipment (UE). A wireless terminal may be a cellular telephone, a satellite phone, a cordless telephone, a Session Initiation Protocol (SIP) phone, a wireless local loop (WLL) station, a personal digital assistant (PDA), a handheld device having wireless connection capability, a computing device, or other processing devices connected to a wireless modem. Moreover, various aspects are described herein in connection with a base station. A base station may be utilized for communicating with wireless terminal(s) and may also be referred to as an access point, a Node B, or some other terminology.

[0059]

Moreover, the term "or" is intended to man an inclusive "or" rather than an exclusive "or." That is, unless specified otherwise, or clear from the context, the phrase "X employs A or B" is intended to mean any of the natural inclusive permutations. That is, the phrase "X employs A or B" is satisfied by any of the following instances: X employs A; X employs B; or X employs both A and B. In addition, the articles "a" and "an" as used in this application and the appended claims should generally be construed to mean "one or more" unless specified otherwise or clear from the context to be directed to a singular form.

[0060]

It is understood that the specific order or hierarchy of steps in the processes disclosed is an illustration of exemplary approaches. Based upon design preferences, it is understood that the specific order or hierarchy of steps in the

15

processes may be rearranged. Further, some steps may be combined or omitted. The accompanying method claims present elements of the various steps in a sample order, and are not meant to be limited to the specific order or hierarchy presented.

[0061]

The previous description is provided to enable any person skilled in the art to practice the various aspects described herein. Various modifications to these aspects will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other aspects. Thus, the claims are not intended to be limited to the aspects shown herein, but is to be accorded the full scope consistent with the language claims, wherein reference to an element in the singular is not intended to mean "one and only one" unless specifically so stated, but rather "one or more." Unless specifically stated otherwise, the term "some" refers to one or more. All structural and functional equivalents to the elements of the various aspects described throughout this disclosure that are known or later come to be known to those of ordinary skill in the art are expressly incorporated herein by reference and are intended to be encompassed by the claims. Moreover, nothing disclosed herein is intended to be dedicated to the public regardless of whether such disclosure is explicitly recited in the claims. No claim element is to be construed as a means plus function unless the element is expressly recited using the phrase "means for."

## WHAT IS CLAIMED IS:

16

## **CLAIMS**

1. An apparatus for temperature adjusted control for a current sensing component, comprising:

a current sensing component inserted in a voltage line, wherein the current sensing component measures current in the voltage line; and

a feedback loop component that tracks a temperature of the current sensing component and modulates a resistance of the current sensing component based on the tracked temperature.

- 2. The apparatus of claim 1, wherein the current sensing component comprises one of a Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) and a Battery Field-Effect Transistor (BATFET).

- 3. The apparatus of claim 2, wherein the current sensing component comprises a BATFET, and wherein the feedback loop component detects a temperature of the BATFET and modulates a gate voltage of the BATFET based on the detected temperature.

- 4. The apparatus of claim 3, wherein the BATFET receives a first voltage in the voltage line, and wherein the feedback loop component comprises:

- a BATFET replica that receives the first voltage and outputs a second voltage; a programmable resistor that receives the first voltage and outputs a third voltage;

an error amplifier that receives the second voltage and the third voltage and outputs a fourth voltage;

and a second amplifier that receives the fourth voltage and outputs a fifth voltage to a gate of the BATFET.

- 5. The apparatus of claim 3, wherein the BATFET receives a first voltage in the voltage line, and wherein the feedback loop component comprises:

- a BATFET replica that receives the first voltage and outputs a second voltage, wherein the BATFET replica comprises a plurality of field effect transistors (FET) in

series such that a sense point of the BATFET replica is programmable by selecting an amount of the FETs used in the BATFET replica;

an error amplifier that receives the second voltage and the third voltage and outputs a fourth voltage;

and a second amplifier that receives the fourth voltage and outputs a fifth voltage to a gate of the BATFET.

- 6. The apparatus of claim 5, wherein the error amplifier comprises a switch cap integrator.

- 7. The apparatus of claim 5, wherein the BATFET is configured to receive a high side voltage from a battery at a source of the BATFET.

- 8. The apparatus of claim 7, wherein the BATFET measures the fuel level of the battery.

- 9. The apparatus of claim 8, wherein the apparatus is comprised in a UE.

- 10. The apparatus of claim 9, wherein the apparatus is comprised in a power management integrated circuit (PMIC) of the UE.

- 11. The apparatus of claim 1, wherein the feedback loop component modulates the resistance of the current sensing component based on the tracked temperature in order to regulate the resistance of the current sensing component to a substantially constant resistance.

- 12. A method of adjusting a resistance of a current sensing component to adjust for temperature and process variations, the method comprising:

receiving a first voltage at a current sensing component inserted in a voltage line;

detecting a temperature of the current sensing component via a feedback loop component; and

18

adjusting a resistance of the current sensing component via the feedback loop component based on the detected temperature.

- 13. The method of claim 12, wherein the current sensing component comprises one of a Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) and a Battery Field-Effect Transistor (BATFET).

- 14. The method of claim 13, wherein the current sensing component comprises a BATFET, the method further comprising:

modulating a gate voltage of the BATFET based on the detected temperature in order to adjust the resistance of the BATFET.

15. The method of claim 13, further comprising receiving the first voltage at a BATFET replica that outputs a second voltage; receiving the first voltage at a programmable resistor that outputs a third voltage; amplifying a difference between the second voltage and the third voltage at an error amplifier that outputs a fourth voltage;

receiving the fourth voltage at a track and hold amplifier; and outputting a fifth voltage from the track and hold amplifier to a gate of the BATFET.

16. The method of claim 14, further comprising

receiving the first voltage at a BATFET replica that outputs a second voltage, wherein the BATFET replica comprises a plurality of field effect transistors (FET) in series;

adjusting a sense point of the BATFET replica by selecting an amount of the FETs used in the BATFET replica;

amplifying a difference between the second voltage and the third voltage at an error amplifier that outputs a fourth voltage;

receiving the fourth voltage at a track and hold amplifier; and outputting a fifth voltage from the track and hold amplifier to a gate of the BATFET.

19

- 17. The method of claim 16, wherein the error amplifier comprises a switch cap integrator.

- 18. The method of claim 16, wherein the first voltage is a high side voltage from a battery.

- The method of claim 18, further comprising:measuring a fuel level of the battery based on an output from the BATFET.

- 20. The method of claim 19, wherein the BATFET and feedback loop are comprised in a UE.

- 21. The method of claim 20, wherein the BATFET and feedback loop are comprised in a power management integrated circuit (PMIC) of the UE.

- 22. The method of claim 12, wherein the resistance of the current sensing component is programmed in segments through digital control to reduce process variation, the method further comprising:

performing a single calibration to eliminate process variation in the resistance of the current sensing component.

23. The method of claim 12, wherein the resistance of the current sensing component is adjusted based on the tracked temperature in order to regulate the resistance of the current sensing component to a substantially constant resistance.

FIG. 1

FIG. 5

**FIG.** 6

#### INTERNATIONAL SEARCH REPORT

International application No PCT/US2013/052122

a. classification of subject matter INV. G01R19/00

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G01R

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal , WPI Data

| ENTS CONSIDERED TO BE RELEVANT                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Citation of document, with indication, where appropriate, of the relevant passages                                                                                             | Relevant to claim No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| US 7 154 291 B2 (TURNER STEVEN R [US] TURNER STEVEN RICHARD [US]) 26 December 2006 (2006-12-26) col umn 1, lines 50-58; figure 1 col umn 2, lines 34-51 col umn 4, lines 11-36 | 1-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| us 2011/095818 AI (SULLIVAN PATRICK [US]) 28 Apri I 2011 (2011-04-28) paragraphs [0012] - [0029] , [0037] , [0045] , [0050] - [0052] ; figures 5,6                             | 1-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EP 2 042 879 AI (MAGNETI MARELLI SISTEMI<br>ELETTR [IT] MAGNETI MARELLI SPA [IT] )<br>1 April 2009 (2009-04-01)                                                                | 1,12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| paragraphs [0010] - [0013] , [0016] , [0020] - [0027] ; claim 1; figure 1                                                                                                      | 2-11 ,<br>13-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                | US 7 154 291 B2 (TURNER STEVEN R [US] TURNER STEVEN RICHARD [US]) 26 December 2006 (2006-12-26) col umn 1, lines 50-58; figure 1 col umn 2, lines 34-51 col umn 4, lines 11-36  US 2011/095818 Al (SULLIVAN PATRICK [US]) 28 April 2011 (2011-04-28) paragraphs [0012] - [0029], [0037], [0045], [0050] - [0052]; figures 5,6  EP 2 042 879 Al (MAGNETI MARELLI SISTEMI ELETTR [IT] MAGNETI MARELLI SPA [IT]) 1 April 2009 (2009-04-01) paragraphs [0010] - [0013], [0016], [0020] - [0027]; claim 1; figure 1 |

| <u> </u> | Further | documents | are | listed | in the | continuation | of Box | С. |

|----------|---------|-----------|-----|--------|--------|--------------|--------|----|

|          |         |           |     |        |        |              |        |    |

See patent family annex.

- \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" documentwhich may throw doubts on priority claim(s) orwhich is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

- "&" document member of the same patent family

Date of the actual completion of the international search Date of mailing of the international search report

#### 16 October 2013

28/10/2013 Authorized officer

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016

O'Callaghan, D

Form PCT/ISA/210 (second sheet) (April 2005)

1

# **INTERNATIONAL SEARCH REPORT**

International application No

PCT/US2013/052122

| A US 6 016 047 A (NOTTEN PETRUS H L [NL] ET AL) 18 January 2000 (2000-01-18) col umn 7, line 50 - col umn 8, line 35 col umn 26, lines 5-35 |

|---------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                             |

1

# INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No PCT/US2013/052122

| Patent document cited in search report | Public<br>da |                                            | Patent family member(s)           | Publication date |                                                                    |

|----------------------------------------|--------------|--------------------------------------------|-----------------------------------|------------------|--------------------------------------------------------------------|

| US 7154291                             | 32 26 –      | 12-2006 DE<br>EP                           | 602005003518<br>1630564           | T2               | 23-10-2008<br>01-03-2006                                           |

|                                        |              | US                                         |                                   |                  | 02-03-2006                                                         |

| <b>us</b> 2011095818                   | Al 28'-      | 04-2011 CN                                 |                                   | A                | 04-05-2011                                                         |

|                                        |              | kr<br>T <b>W</b>                           |                                   | A<br>A           | 28-04-2011<br>01-07-2011                                           |

|                                        |              | US                                         | 2011095818                        | Al               | 28-04-2011                                                         |

| EP 2042879 .                           | A1 01'-      | 04-2009 AT<br>EP                           |                                   |                  | 15-01-2012<br>01-04-2009                                           |

| us 6016047 .                           | A 18 -       | 01-2000 DE<br>DE<br>EP<br><b>J</b> P<br>US | 69730413<br>0880710<br>2000504477 | A                | 30-09-2004<br>08-09-2005<br>02-12-1998<br>11-04-2000<br>18-01-2000 |

|                                        |              | Wo                                         |                                   |                  | 28-05-1998                                                         |