(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4623963号

(P4623963)

(45) 発行日 平成23年2月2日(2011.2.2)

(24) 登録日 平成22年11月12日(2010.11.12)

(51) Int.Cl.

G06F 7/24 (2006.01)

G06F 17/10 (2006.01)

F 1

G06F 7/24

G06F 17/10M

A

請求項の数 3 (全 46 頁)

(21) 出願番号 特願2003-540797 (P2003-540797)

(86) (22) 出願日 平成14年10月28日 (2002.10.28)

(65) 公表番号 特表2005-508043 (P2005-508043A)

(43) 公表日 平成17年3月24日 (2005.3.24)

(86) 國際出願番号 PCT/US2002/034404

(87) 國際公開番号 WO2003/038601

(87) 國際公開日 平成15年5月8日 (2003.5.8)

審査請求日 平成17年10月28日 (2005.10.28)

(31) 優先権主張番号 09/952,891

(32) 優先日 平成13年10月29日 (2001.10.29)

(33) 優先権主張國 米国(US)

(31) 優先権主張番号 10/280,612

(32) 優先日 平成14年10月25日 (2002.10.25)

(33) 優先権主張國 米国(US)

(73) 特許権者 593096712

インテル コーポレイション

アメリカ合衆国 95052 カリフォルニア州 サンタクララ ミッション カレッジ ブールバード 2200

(74) 代理人 100070150

弁理士 伊東 忠彦

(74) 代理人 100091214

弁理士 大貫 進介

(74) 代理人 100107766

弁理士 伊東 忠重

前置審査

最終頁に続く

(54) 【発明の名称】コンテンツデータを効率的にフィルタリング及び畳み込む方法及び装置

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサにより実行されるコンテンツデータを効率的にフィルタリング及び畳み込む方法であって、

前記プロセッサがデータシャッフル命令を実行することに応答して、マスクの値に従つてソースデータの選択された部分を、目的データ記憶装置内のデータが係数データ記憶装置内の係数と乗算されるように配置されるよう、整理するステップと、

前記プロセッサが乗算命令を実行することに応答して、前記目的データ記憶装置内のバイトデータと前記係数データ記憶装置内のバイト係数との複数の積和ペアを生成するステップと、

前記プロセッサが隣接加算命令を実行することに応答して、1以上のデータ処理演算結果を構成するため、前記複数の積和ペアの隣接する積和ペアを加算するステップと、

前記1以上のデータ処理演算結果をデータ記憶装置に格納するステップと、

から構成され、

前記データシャッフル命令は、バイトシャッフル命令を含み、前記整理するステップは、前記ソースデータの選択された部分の個々のバイトを整理するバイトシャッフル処理を実行し、

前記バイトシャッフル命令はさらに、4バイトを有する各ダブルワードを、前記各ダブルワード内の4バイトの相対位置を維持することによって、整理できることを特徴とする方法。

## 【請求項 2】

プロセッサにより実行されると、

データシャッフル命令の実行に応答して、マスクの値に従ってソースデータの選択された部分を、目的データ記憶装置内のデータが係数データ記憶装置内の係数と乗算されるように配置されるよう、整理するステップと、

乗加算命令の実行に応答して、前記目的データ記憶装置内のバイトデータと前記係数データ記憶装置内のバイト係数との複数の積和ペアを生成するステップと、

隣接加算命令の実行に応答して、1以上のデータ処理演算結果を構成するため、前記複数の積和ペアの隣接する積和ペアを加算するステップと、

前記1以上のデータ処理演算結果を格納するステップと、

から構成される方法を実行するプログラム命令を有するコンピュータ可読記憶媒体であつて、

前記データシャッフル命令は、バイトシャッフル命令を含み、前記整理するステップは、前記ソースデータの選択された部分の個々のバイトを整理するバイトシャッフル処理を実行し、

前記バイトシャッフル命令はさらに、4バイトを有する各ダブルワードを、前記各ダブルワード内の4バイトの相対位置を維持することによって、整理できることを特徴とする記憶媒体。

## 【請求項 3】

命令を実行する回路を有するプロセッサと、

前記プロセッサに接続され、命令シーケンスが格納される記憶装置と、

から構成される装置であつて、

前記命令シーケンスは、前記プロセッサによる実行時に、

データ処理演算に従って、記憶装置内に構成されるように、係数を係数データ記憶装置にロードするステップと、

データシャッフル命令の実行に応答して、マスクの値に従ってソースデータの選択された部分を、目的データ記憶装置内のデータが前記係数データ記憶装置内の係数と乗算されるように配置されるよう、整理するステップと、

乗加算命令の実行に応答して、前記目的データ記憶装置内のバイトデータと前記係数データ記憶装置内のバイト係数との複数の積和ペアを生成するステップと、

隣接加算命令の実行に応答して、1以上のデータ処理演算結果を構成するため、前記複数の積和ペアの隣接する積和ペアを加算するステップと、

1以上のデータ処理演算結果を格納するステップと、

を前記プロセッサに実行させ、

前記データシャッフル命令は、バイトシャッフル命令を含み、前記整理するステップは、前記ソースデータの選択された部分の個々のバイトを整理するバイトシャッフル処理を実行し、

前記バイトシャッフル命令はさらに、4バイトを有する各ダブルワードを、前記各ダブルワード内の4バイトの相対位置を維持することによって、整理できることを特徴とする装置。

## 【発明の詳細な説明】

## 【発明の詳細な説明】

## 【0001】

本特許出願は、2001年10月29日に出願された米国特許出願第09/952,891号「コンテンツデータの効率的フィルタリング及び畳み込み装置及び方法(An Apparatus And Method For Efficient Filtering And Convolution Of Content Data)」の一部継続出願である。

## 【0002】

本特許出願は、2002年10月25日に出願された同時係属中の米国特許出願第10

10

20

30

40

50

/ 2 8 0 , 6 1 2 号「 SIMD マージ命令による高速全探索動き ( F a s t F u l l S e a r c h M o t i o n W i t h S I M D M e r g e I n s t r u c t i o n ) 」に関する。

【発明の技術分野】

本発明は、一般に、マイクロプロセッサ及びコンピュータシステムの分野に関する。より詳細には、本発明は、データの右方向平行シフトマージ ( p a r a l l e l s h i f t r i g h t m e r g e ) 方法及び装置に関する。

【発明の背景】

プロセッサ技術の進歩により、このようなプロセッサを備えたマシーン上で実行される新しいソフトウェアコードが生成されている。一般に、ユーザは、使用しているソフトウェアのタイプに関わらず、コンピュータからより高いパフォーマンスを期待及び要求する。このような問題は、プロセッサ内部において実行されている命令及び処理のタイプから生じる可能性がある。あるタイプの処理には、必要とされる回路の処理及び / あるいはタイプの複雑さに基づき、その完了に多くの時間を要するものもある。このようなことから、複雑な処理のプロセッサ内部での実行方法を最適化するという動機付けが生じる。

【 0 0 0 3 】

メディアアプリケーションは、数十年もの間、マイクロプロセッサの発達を促進してきた。実際、近年における大部分の計算機の性能向上はメディアアプリケーションにより促進されてきたものである。娛樂性を高めた教育及び通信目的のため、重大な進歩は企業部門において見出されてきたが、上記のような性能の向上は主として消費者部門において起こってきたものである。にもかかわらず、これからのメディアアプリケーションには、さらに高い計算要件が要求されるであろう。この結果、将来のパーソナルコンピュータ ( P C ) では、使い安さだけでなくより充実したオーディオビジュアル機能が実現されるであろう。さらに、より重要なものとしては、計算機が通信と融合されるであろう。

【 0 0 0 4 】

従って、現在の計算機においては、コンテンツとして総称される音声及び映像データの再生だけでなく画像の表示も、ますます一般的なアプリケーションとなりつつある。フィルタリング及び畳み込み処理は、画像、音声及び映像データのようなコンテンツデータに対し最もよく実行される処理である。当業者には周知のように、フィルタリング及び相關計算では、データや係数の積を加える乗加算演算により計算される。2つのベクトル A と B の相関は、和 S の計算からなる。

【 0 0 0 5 】

【数 1】

$$S[k] = \frac{1}{N} \sum_{i=0}^{N-1} a[i] \cdot b[i+k] \quad \text{等式 (1)}$$

これはしばしば  $k = 0$  により使われる。

【 0 0 0 6 】

【数 2】

$$S[0] = \frac{1}{N} \sum_{i=0}^{N-1} a[i] \cdot b[i] \quad \text{等式 (2)}$$

ベクトル V に適用される N タップフィルタ f の場合、計算される和 S は以下のようになる。

【 0 0 0 7 】

10

20

30

40

## 【数3】

$$S = \sum_{i=0}^{N-1} f[i] \cdot V[i] \quad \text{等式 (3)}$$

このような演算には大きな計算量を要する一方、例えば、单一命令多重データ（S I M D）レジスタのような様々なデータ格納装置を利用した効率的実現法を通じ利用可能なハイレベルのデータ並列処理を提供する。

## 【0008】

10 フィルタリング処理の応用は、より広い範囲の画像及び映像処理タスク及び通信において見出すことができる。フィルタの利用例としては、M P E G (M o t i o n P i c t u r e E x p e r t G r o u p) 映像におけるブロックアーチファクトの低減、ノイズや音声の低減、透かし検出を向上させるための画素値からの透かしの抽出、スムージング、シャープニング、ノイズ低減、エッジ検出、画像または映像フレームサイズのスケーリングのための相関、サブピクセル動き予測のための映像フレームのアップサンプリング、音声信号の音質向上、及び通信における信号のパルス整形及び等化処理などが挙げられる。従って、疊み込み処理だけでなくフィルタリング処理もまた、画像、音声及び映像データを含むコンテンツの再生を提供する計算機にとって重要なものである。

## 【0009】

20 しかしながら、既存の方法及び指示はフィルタリングの通常必要とされるものを満足することを目的としたものであり、より広い範囲をカバーするものではない。実際、多くのアーキテクチャが様々なフィルタ長及びデータタイプに対する効率的なフィルタ計算手段をサポートしていない。さらに、レジスタ内及びレジスタ間における部分的なデータ転送に対する隣接する値の加算と共に、S I M D レジスタのようなデータ記憶装置におけるデータオーダリングは、一般にサポートされていない。その結果、既存のアーキテクチャは不必要的データタイプの変更を必要とし、それによって、命令あたりの処理数が最小化され、算術演算のためのデータ順序付けに要するクロックサイクル数を著しく増加させてしまう。

## 【0010】

30 本発明が実施例を利用することにより示される。本発明は添付される図面に制限されるものではない。図面中、同一の参照記号は同一の要素を示している。

## [詳細な説明]

データに対し右方向平行シフトマージを実行する方法及び装置が開示される。また、コンテンツデータの効率的なフィルタリング及び疊み込みを実行する方法及び装置が開示される。さらにまた、S I M D マージ処理による高速全探索動き検出のための方法及び装置が開示される。ここで説明される実施例はマイクロプロセッサに関するものであるが、必ずしもそれに限定されるものではない。以下の実施例はプロセッサに関し説明されるが、他の実施例では、他のタイプの集積回路及び論理装置に適用することもできる。本発明の同様なテクニック及び教示は、より高いパイプラインスループット及び性能を享受しうる他のタイプの回路あるいは半導体デバイスに容易に適用することができる。本発明の教示は、データ操作を実行する任意のプロセッサあるいはマシンに適用可能である。しかしながら、本発明は、256ビット、128ビット、64ビット、32ビットあるいは16ビットデータ処理を実行するプロセッサあるいはマシンに限定されるものでなく、データの右方向シフトマージを必要とする任意のプロセッサ及びマシンに適用することができる。

## 【0011】

以下の記述では、説明のため、本発明の完全な理解を提供するため様々な具体的な詳細が与えられる。本発明の実践に対し、これら具体的な詳細が必ずしも必要でないということは当業者には認識されるであろう。また、周知の電気構造及び回路は、本発明を必要に不

10

20

30

40

50

明瞭にしないよう詳細には与えられていない。さらに、以下の説明は実施例を与えるものであり、添付される図面は例示のため様々な実施例を示している。しかしながら、これらの実施例は限定のためのものと解釈されるべきでない。これらの実施例は、本発明のすべての可能な実現を包括的に列挙するものでなく、単に本発明の例を提供することを目的としている。

#### 【0012】

一実施例において、本発明による方法は、マシーン実行可能な命令により実現される。これらの命令により、プログラム可能な汎用あるいは特定用途向けプロセッサは本発明の各ステップを実行する。あるいは、本発明の各ステップは、これらのステップを実行する配線論理を含む特定のハードウェア要素により実行されてもよいし、あるいはプログラムされたコンピュータ構成要素及びカスタムハードウェア構成要素による任意の組み合わせにより実行されてもよい。

10

#### 【0013】

本発明は、これに従う処理を実行するようコンピュータ（あるいは他の電子装置）をプログラムするのに利用される命令を有するマシーンまたはコンピュータ読み出し可能な媒体を備えたコンピュータプログラムプロダクトまたはソフトウェアとして与えることができる。そのようなソフトウェアはシステム内部のメモリに格納することができる。同様に、そのコードはネットワークまたは他のコンピュータ読み出し可能な媒体を介し配信される。コンピュータ読み出し可能な媒体には、以下に限定されるものではないが、フロッピーディスク（登録商標）、光ディスク、CD（Compact Disc）、CD-R 20

OM（CD Read-Only Memory）、光磁気ディスク、ROM（Read-Only Memory）、RAM（Random Access Memory）、EPROM（Erasable Programmable Read-Only Memory）、EEPROM（Electrically Erasable Programmable Read-Only Memory）、磁気あるいは光カード、フラッシュメモリ、インターネット上の送信などが含まれる。

20

#### 【0014】

従って、コンピュータ読み出し可能な媒体には、マシーン（例えば、コンピュータ）による読み出し可能な形態により電子的命令あるいは情報の格納または送信に適した任意のタイプのメディア／マシーン読み出し可能な媒体が含まれる。さらに、本発明はまた、コンピュータプログラムプロダクトとしてダウンロード可能であってもよい。その場合、プログラムはリモートコンピュータ（例えば、サーバ）からリクエストコンピュータ（例えば、クライアント）に転送される。プログラムの転送は、電子、光、音響あるいは搬送波で実現される他の形態のデータ信号、あるいは通信リンク（例えば、モ뎀、ネットワーク接続など）を介した他の伝搬媒体により実行されてもよい。

30

#### 【0015】

今日のプロセッサでは、様々なコード及び命令の処理及び実行に多くの実行ユニットが利用されている。命令の中には即座に完了するものがある一方、膨大なクロックサイクルを要する命令もあるので、必ずしもすべての命令が等しく生成されることは限らない。命令のスループットが速くなるほど、プロセッサの全体的なパフォーマンスはより向上する。従って、できる限り多くの命令が実行されることが望ましい。しかしながら、大きな複雑さを有し、多くの実行時間及びプロセッサリソースを要する命令もある。例えば、浮動小数点命令、ロード／ストア処理、データ転送などが挙げられる。

40

#### 【0016】

ますます多くのコンピュータシステムがインターネットやマルチメディアアプリケーションにおいて利用されるに従い、追加的なプロセッササポートがこれまで導入されてきた。例えば、单一命令多重データ（SIMD）整数／浮動小数点命令やストリーミング SIMD エクステンション（SSE）は、特定のプログラムタスクの実行に要する全体の命令数を減少させる命令である。これらの命令は、複数のデータ要素に対し並列処理を行うことにより、ソフトウェアパフォーマンスの高速化を可能にする。これにより、映像、音声

50

、及び画像／フォト処理を含む広範なアプリケーションにおいてパフォーマンスの向上を達成することが可能となる。通常、マイクロプロセッサや類似の論理回路における SIMD 命令の実現には多くの発行が伴う。さらに、SIMD 処理の複雑さはしばしば、正確なデータ処理及び操作のための追加的回路の必要性を生じさせる。

#### 【0017】

本発明の実施例は、SIMD に関するハードウェアを利用するアルゴリズムとして、右方向平行シフトの実現方法を提供する。一例として、当該アルゴリズムは、所望の数のデータセグメントがあるオペランドから第 2 のオペランドの最上位サイドに右方向シフトし、同数のデータセグメントが第 2 のオペランドの最下位サイドにシフトするというコンセプトに基づいている。概念的には、この右方向シフトマージ処理では、データの 2 つのブロックを 1 つのブロックとしてマージし、新たなデータパターンを形成するために、データセグメントを所望の位置で揃えるようマージされたブロックのシフトが実行される。従って、本発明による右方向シフトマージアルゴリズムの実施例は、全体のパフォーマンスを大きく損なうことなく効率的に SIMD 処理をサポートするプロセッサにおいて実現可能である。

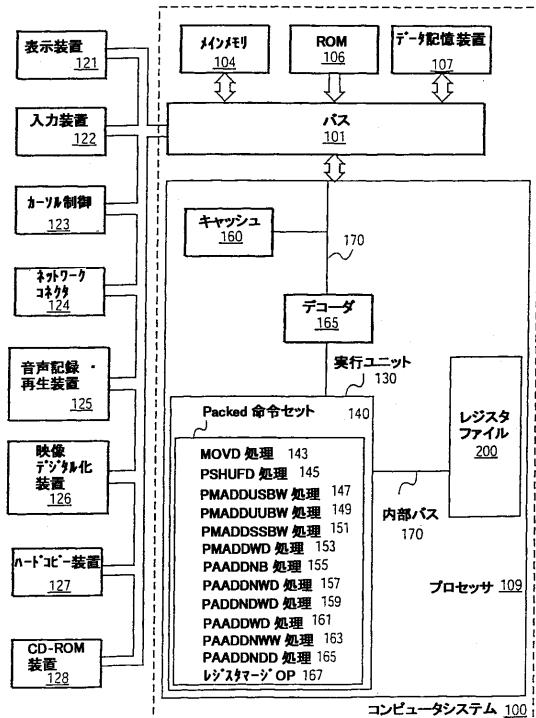

#### コンピュータアーキテクチャ

図 1 は、本発明の一実施例が実現されうるコンピュータシステム 100 を示す。コンピュータシステム 100 は、情報を通信するためのバス 101 と、バス 101 に接続され、情報を処理するプロセッサ 109 から構成される。コンピュータシステム 100 はまた、バス 101 に接続され、プロセッサ 109 のための情報や命令を格納するメモリサブシステム 104 ~ 107 を備える。

#### 【0018】

プロセッサ 109 は、実行ユニット 130、レジスタファイル 200、キャッシュメモリ 160、デコーダ 165 及び内部バス 170 から構成される。k ドッ主メモリ 160 は、実行ユニット 130 に接続され、プロセッサ 109 のために頻繁に及び／または最近使用された情報を格納する。レジスタファイル 200 は、プロセッサ 109 における情報を格納し、内部バス 170 を介し実行ユニット 130 に接続される。本発明の一実施例では、レジスタファイル 200 は、マルチメディア情報を格納する SIMD レジスタのような複数のマルチメディアレジスタを備える。一実施例では、各マルチメディアレジスタは、128 ビットまでのパケットデータを格納する。マルチメディアレジスタは、専用マルチメディアレジスタであってもよいし、あるいはマルチメディア情報や他の情報の格納に利用されるレジスタであってもよい。一実施例では、マルチメディアレジスタは、マルチメディア処理の実行時にはマルチメディア情報を格納し、浮動小数点演算の実行時には浮動小数点データを格納する。

#### 【0019】

実行ユニット 130 は、Packed 命令セット 140 に含まれるプロセッサ 109 により受信された命令セットに従い Packed データを処理する。実行ユニット 130 はまた、汎用プロセッサにおいて実現される命令に従って、スカラーデータを処理する。プロセッサ 109 は、Pentium (登録商標) マイクロプロセッサ命令セットと Packed 命令セット 140 をサポートすることができる。Pentium (登録商標) マイクロプロセッサ命令セットのような標準的なマイクロプロセッサ命令セットに Packed 命令セット 140 を含めることにより、Packed データ命令を（標準的なマクロプロセッサ命令セットのために以前に書かれた）既存のソフトウェアに容易に内蔵することができる。PowerPC (商標) や Alpha (商標) プロセッサの命令セットのような他の標準的な命令セットが、説明される本発明に従い使用されてもよい。（Pentium (登録商標) は、インテルコーポレーションの登録商標である。PowerPC (商標) は、IBM、アップルコンピュータ及びモトローラの商標である。Alpha (商標) は、デジタルイクイップメントコーポレーションの商標である。）

一実施例では、Packed 命令セット 140 は、（以下でさらなる詳細が示されるように）転送データ (MOV D) 処理 143 と、データ記憶装置内のデータを構成するデー

10

20

30

40

50

タシャッフル ( P S H U F D ) 処理 145 のための命令を含む。符号なし第 1 ソースレジスタと符号付き第 2 ソースレジスタに対する P a c k e d 乗算及び加算 ( P M A D D U S B W 処理 147 )。符号なし第 1 ソースレジスタと符号なし第 2 ソースレジスタに対する乗加算を実行する P a c k e d 乗加算処理 ( P M A D D U U B W 処理 149 )。符号付き第 1 ソースレジスタと符号付き第 2 ソースレジスタに対する P a c k e d 乗加算処理 ( P M A D D S S B W 処理 151 ) と、16 ビットデータを含む符号付き第 1 及び第 2 ソースレジスタに対する P a c k e d 乗加算処理 ( P M A D D W D 処理 153 )。最終的に、P a c k e d 命令セットには、隣接バイトを加える隣接加算命令 ( P A A D D N B 処理 155 )、隣接ワードを加える隣接加算命令 ( P A A D D N W D 処理 157 )、隣接ダブルワードを加える隣接加算命令 ( P A A D D N D W D 処理 159 )、2 つのワード値を加える隣接加算命令 ( P A A D D W D 処理 161 )、16 ビットの結果を生成するための 2 つのワードを加える隣接加算命令 ( P A A D D N W W 処理 163 )、クアドワード結果を生成するため 2 つのクアドワードを加える隣接加算命令 ( P A A D D N D D 処理 165 )、及びレジスタマージ処理 167 が含まれる。

#### 【 0020 】

P a c k e d 命令セット 140 を汎用プロセッサ 109 の命令セットに、命令を実行する関連する回路と共に含めることによって、多くの既存のマルチメディアアプリケーションにより使われる処理が汎用プロセッサの P a c k e d データを利用することにより実行されてもよい。従って、P a c k e d データを処理するプロセッサのデータバスの最大幅を利用することにより、多くのマルチメディアアプリケーションは高速化され、より効率的に実行される。これにより、データのより小さなユニットをプロセッサのデータバスに転送し、一度にデータあたり複数の処理を実行させる必要がなくなる。

#### 【 0021 】

図 1 を参照するに、本発明のコンピュータシステム 100 は、モニタのような表示装置 121 を含んでいてもよい。表示装置 121 は、フレームバッファのような中間装置を含んでいてもよい。コンピュータシステム 100 はまた、キーボードのような入力装置 122 と、マウス、トラックボールまたはトラックパッドのようなカーソル制御 123 を含んでいてもよい。表示装置 121 、入力装置 122 及びカーソル制御 123 は、バス 101 に接続される。コンピュータシステム 100 はまた、コンピュータシステム 100 がローカルエリアネットワーク ( L A N ) やワイドエリアネットワーク ( W A N ) の一部となるようネットワークコネクタ 124 を含んでもよい。

#### 【 0022 】

さらに、コンピュータシステム 100 は、音声認識のための音声入力を記録するためのマイクロフォンに接続されるオーディオデジタイザのような音声記録及び / あるいは再生装置 125 に接続することができる。コンピュータシステム 100 はまた、映像のキャプチャに利用可能な映像デジタル化装置 126 、プリンタのようなハードコピー装置 127 、及び C D - R O M 装置 128 を備えてもよい。これらの装置 124 ~ 128 はまた、バス 101 に接続される。

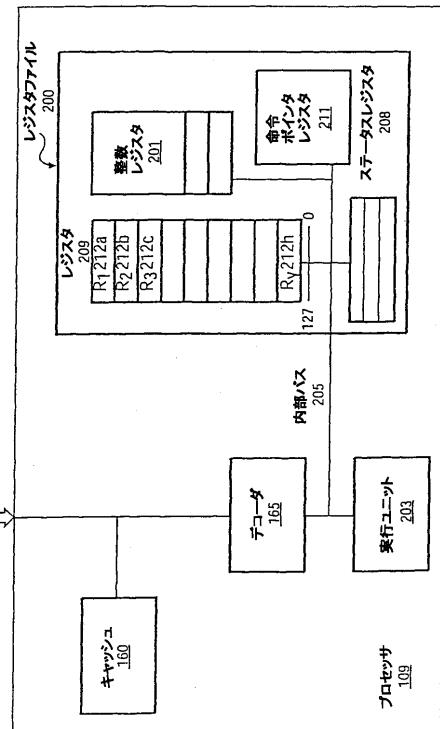

#### プロセッサ

図 2 は、プロセッサ 109 の詳細な図を示す。プロセッサ 109 は、B i C M O S 、C M O S 及び N M O S のような多くのプロセス技術の何れかを利用した複数の基板において実現することができる。プロセッサ 109 は、プロセッサ 109 により使われる制御信号及びデータの復号化を行うデコーダ 202 を備える。その後、データは内部バス 205 を介しレジスタファイル 200 に格納される。問題を明瞭にするため、一例となるレジスタは特定のタイプの回路に限定されるべきでない。一例となるレジスタは、データの格納及び供給、並びにここで説明される機能の実行が可能であることが必要である。

#### 【 0023 】

データタイプに応じて、データは、整数レジスタ 201 、レジスタ 209 、ステータスレジスタ ( s t a t u s r e g i s t e r ) 208 、または命令ポインタレジスタ 211 に格納することができる。例えば、浮動小数点レジスタのような他のレジスタは、レジ

10

20

30

40

50

スタファイル 204 に含めることができる。一実施例では、整数レジスタ 201 は 32 ビット整数データを格納する。一実施例では、レジスタ 209 は、例えば、Packed データを含む SIMD レジスタのような 8 つのマルチメディアレジスタ  $R_0, R_1, R_2, R_3, R_4, R_5, R_6, R_7$  を有する。レジスタ 209 の各レジスタは、128 ビット長である。 $R_1, R_2, R_3, R_4$  及び  $R_5, R_6, R_7$  は、レジスタ 209 の各レジスタの一例である。レジスタ 209 のあるレジスタの 32 ビットを整数レジスタ 201 の整数レジスタに転送することができる。同様に、整数レジスタの値をレジスタ 209 のあるレジスタの 32 ビットに転送することができる。

#### 【0024】

ステータスレジスタ 208 は、プロセッサ 109 の状態を示す。命令ポインタレジスタ 211 は、実行されるべき次の命令のアドレスを格納している。整数レジスタ 201、レジスタ 209、ステータスレジスタ 208 及び命令ポインタレジスタ 211 はすべて内部バス 205 に接続される。任意の追加的レジスタがまた内部バス 205 に接続されるであろう。

#### 【0025】

他の実施例では、これらのレジスタのいくつかは、2 つのデータタイプに利用することができます。例えば、レジスタ 209 と整数レジスタ 201 は、各レジスタが整数データあるいは Packed データのどちらかを格納できるよう一体化されてもよい。他の実施例では、レジスタ 209 は浮動小数点レジスタとして利用することができる。この実施例では、Packed データはレジスタ 209 あるいは浮動小数点データに格納することができる。一実施例では、一体化されたレジスタは 128 ビット長を有し、整数は 128 ビットとして表現される。この実施例では、Packed データ及び整数データの格納において、レジスタはこれら 2 つのデータタイプを区別する必要はない。

#### 【0026】

機能ユニット 203 は、プロセッサ 109 により実行される処理を行う。そのような処理には、シフト、加算、減算及び乗算などが含まれる。機能ユニット 203 は内部バス 205 に接続される。キャッシュ 160 は、プロセッサ 109 の選択的ユニットであり、例えば、メインメモリ 104 からのデータ及び/あるいは制御信号をキャッシュするのに利用される。キャッシュ 160 は、デコーダ 202 に接続され、制御信号 207 を受信するよう接続される。

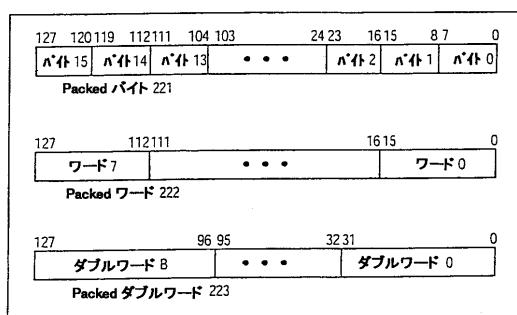

#### データ及び記録フォーマット

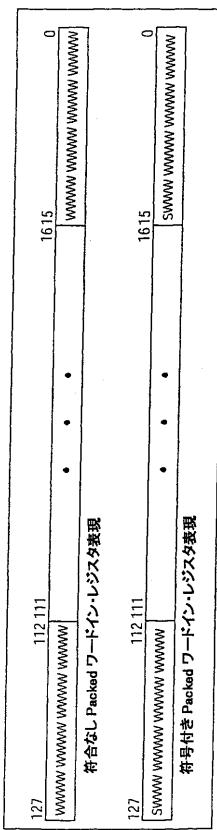

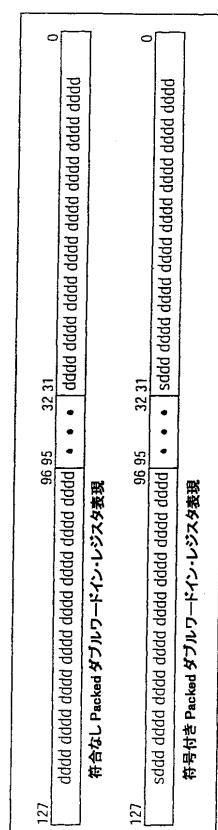

図 3 は、Packed バイト 221、Packed ワード 222 及び Packed ダブルワード (double word) 223 の 3 つの Packed データタイプを示す。Packed バイト 221 は、16 の Packed バイトデータ要素を含む 128 ビット長である。一般に、データ要素とは、同じデータ長を有する他のデータ要素と共に 1 つのレジスタ (あるいはメモリ位置) に格納される個々のデータである。Packed データ系列では、レジスタに格納されるデータ要素数は、データ要素のビット長により分割される 128 ビットである。

#### 【0027】

Packed ワード 222 は、128 ビット長であり、8 つの Packed ワードデータ要素を含む。各 Packed ワードは 16 ビットの情報を含んでいる。Packed ダブルワード 223 は、128 ビット長であり、4 つ以上の Packed ダブルワードデータ要素を含んでいる。各 Packed ダブルワードデータ要素は、32 ビットの情報を含んでいる。Packed クアドワードは、128 ビット長で、2 つの Packed クアドワードデータ要素を含んでいる。

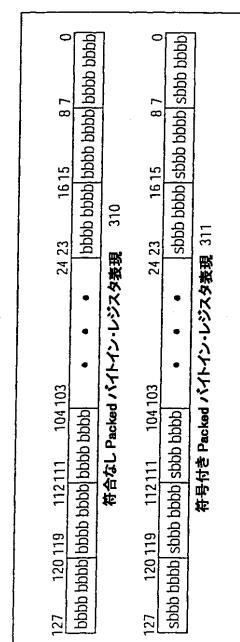

#### 【0028】

図 4A ~ 4C は、本発明の一実施例によるイン・レジスタ (in-register) Packed データ記録表現を示す。図 4A に示されるように、符号なし Packed バイトイン・レジスタ表現 310 により、符号なし Packed バイト 201 のマルチメディアレジスタ 209 の 1 つへの記録が示される。各バイトデータ要素の情報は、第 0 バイ

10

20

30

40

50

トには第7ビットから第0ビットに、第1バイトには第15ビットから第8ビットに、第2バイトには第23ビットから第16ビットに、最後に、第15バイトには第128ビットから第127ビットから第120ビットにそれぞれ格納される。

【0029】

これにより、利用可能なすべてのビットがレジスタにおいて使用される。この記録配置は、プロセッサの記憶効率を高めるものである。さらに、16のデータ要素がアクセスされることにより、1つの処理がこれら16のデータ要素に同時に実行することができる。符号付き Packed バイトイン・レジスタ表現 311 により、符号付き Packed バイト 211 の記録が示される。ここで、すべてのバイトデータ要素の第8ビットは符号表示に使われる。

10

【0030】

図4B に示されるように、符号なし Packed ワードイン・レジスタ表現 312 により、第7ワードから第0ワードまでがどのようにマルチメディアレジスタ 209 のレジスタに格納されるか示されている。符号付き Packed ワードイン・レジスタ表現 313 は、符号なし Packed ワードイン・レジスタ表現 312 と同様である。ここで、各ワードデータ要素の第16ビットは符号表示に使われる。図4C に示されるように、符号なし Packed ダブルワードイン・レジスタ表現 314 により、マルチメディアレジスタ 209 がどのように2つのダブルワードデータ要素を格納するか示されている。符号付き Packed ダブルワードイン・レジスタ表現 315 は、符号なし Packed ダブルワードイン・レジスタ表現 314 と同様である。ここで、必要な符号ビットは、ダブルワードデータ要素の第32ビットである。

20

【0031】

本発明のより教示されるように、コンテンツデータの効率的フィルタリング及び畳み込みは、データ及びフィルタ/畳み込み係数によるデータソース装置のロードにより開始される。多くの場合、例えば、単一命令多重データ ( SIMD ) レジスタのようなデータ記憶装置内のデータあるいは係数の順序は、算術計算が実行される前に変更を要する。従って、効率的なフィルタ計算及び畳み込みには、適切な算術命令だけでなく、計算の実行に要する効率的なデータ構造化方法が必要とされる。

【0032】

例えば、バックグラウンド部において記号を利用して、例えば、S[I] により与えられる画素 I の値を置換することにより画像がフィルタリングされる。画素 I の何れかのサイドにおける画素値が S[I] のフィルタリング計算において使用される。同様に、画素 I + 1 の何れかのサイドにおける画素が、SD[I + 1] の計算に必要とされる。これにより、SIMD レジスタにおける 1 より多い画素のフィルタリング結果を計算するために、データが複製され、SIMD レジスタに置かれる。

30

【0033】

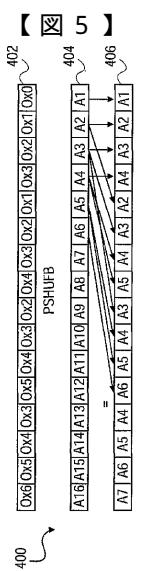

しかしながら、既存のコンピューターアーキテクチャでは、アーキテクチャ内の適切なすべてのデータサイズに対する効率的なデータ配置方法が欠落している。従って、図5 に示されるように、本発明は、任意のサイズのデータを効率的に順序付けするバイトシャッフル命令 ( PSHUFB ) 145 を備える。このバイトシャッフル処理 145 では、シャッフル処理中にバイトの相対位置をより大きなデータ内に維持することにより、バイトより大きなデータサイズの順序付けが行われる。さらに、バイトシャッフル処理 145 では、SIMD レジスタ内のデータの相対位置の変更、及びデータの複製もまた可能である。

40

【0034】

図5を再度参照するに、図5は、3つの係数を有するフィルタに対するバイトシャッフル処理 145 の一例が示されている。従来技術を利用すると、フィルタ係数 ( 図示せず ) が3つの画素に適用され、その後このフィルタ係数が他の画素に移動され、再び適用される。しかしながら、これらの処理を並列に実行するために、本発明は、データの配置に新たな命令を導入する。従って、図5に示されるように、データ 404 は目的データ記憶装置 ( destination data storage device ) 406 内で構

50

成される。一実施例では、目的データ記憶装置 406 は、各データ要素を格納するアドレスを特定するのにマスク 402 を利用したソースデータ記憶装置 (source data storage device) 404 である。一実施例では、マスクの配置は、例えば、フィルタリング処理、畳み込み処理などを含む所望のデータ処理に基づく。

【0035】

従って、マスク 402 を利用することにより、係数と共にデータ 406 は並列に処理することが可能になる。上述の実施例では、ソースデータ記憶装置 404 は、初期的に 16 の 8 ビット画素を格納する 128 ビット SIMD レジスタである。さらに、3 つの係数による画素フィルタが利用されるとき、第 4 の係数は 0 に設定される。一実施例では、ソースデータ記憶装置 404 内のデータ要素数に応じて、ソースレジスタ 404 は目的データ記憶装置あるいはレジスタとして利用され、それにより、一般に必要とされるよりレジスタ数を減少させることができる。さらに、ソースデータ記憶装置 404 内の上書きされたデータは、メモリから他のレジスタに再ロードされる。さらに、所望のように各データを目的データ記憶装置 406 内で構成することにより、複数のレジスタがソースデータ記憶装置 404 として利用されてもよい。

【0036】

データ要素と係数の順序付けが完了したら、データと対応する係数がデータ処理に従い処理される必要がある。様々なフィルタ係数及びデータサイズを利用することにより、フィルタ計算と畳み込み計算には様々な精度による処理が必要とされる。最も基本的なフィルタ処理は、2 つの数のペアの乗算と、それらの加算である。この処理は、乗加算命令と呼ばれる。

【0037】

しかしながら、既知のコンピュータアーキテクチャでは、符号付きまたは符号なし係数を利用した複数の配列あるいはフィルタ長及びデータサイズに対する効率的な乗加算をサポートしていない。さらに、バイト演算もサポートされていない。その結果、従来技術によるコンピュータアーキテクチャは、Unpack 命令を利用することにより 16 ビットデータを変換しなければならない。一般に、これらのコンピュータアーキテクチャは、異なるレジスタにある 16 ビットデータの積を計算し、隣接する積を加え合わせ、32 ビットの結果を与える乗加算処理をサポートしている。この解決策は 16 ビットの精度を要するデータのフィルタ係数には受け入れられるが、(画像や映像において一般的な) 8 ビットデータの 8 ビットフィルタ係数に対しては、命令及びデータレベルの並列化は無駄である。

【0038】

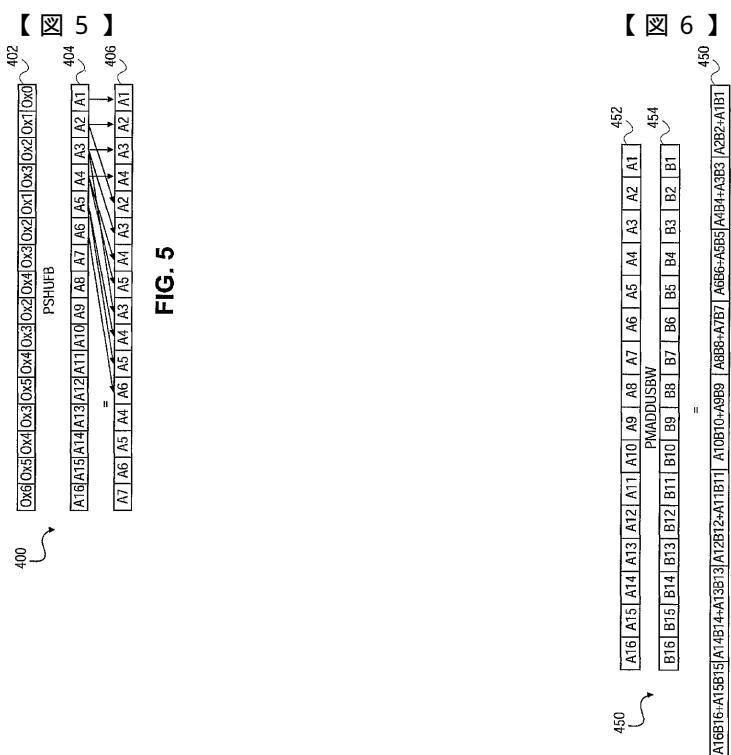

図 6 を参照するに、図 6 は、第 1 ソースレジスタ 452 と第 2 ソースレジスタ 454 を示す。一実施例では、第 1 及び第 2 ソースレジスタは、例えば、128 ビット Intel (登録商標) SSE2 XMM レジスタのような N ビット長 SIMD レジスタである。このようなレジスタで実現される乗加算命令は、2 つの画素ベクトル 452 と 454 に対して以下の結果を与え、目的レジスタ 456 内に格納される。従って、実施例は P M A D D U S B W 处理 147 (図 1) と呼ばれる 8 ビットバイト - 16 ワード乗加算命令 (8-bit byte to 16 word multiply - accumulate instruction) を示す。ここで、命令中の「U」と「S」はそれぞれ符号なしと符号付きバイトを表している。ソースレジスタの一方におけるバイトは符号付きであり、もう一方におけるバイトは符号なしである。

【0039】

本発明の一実施例では、符号なしデータを有するレジスタは、目的及び 16 乗加算結果である。この選択は、大部分の実行において、データは符号なし、係数は符号付きであるという理由による。データは以降の計算において必要とされる確率は低いので、データを上書きすることが好ましい。図 1 に示されるような追加的バイト乗加算命令は、両方のレジスタにおける符号なしバイトに対する P M A D D U U B W 处理 149 と、両方のソースレジスタにおける符号付きバイトに対する P M A D D S S B W 处理 151 である。この乗

10

20

30

40

50

加算命令は、32ビット符号付き積の生成のために、16ビット符号付きワードのペアに適用されるPMAADDWD命令153により完了される。

#### 【0040】

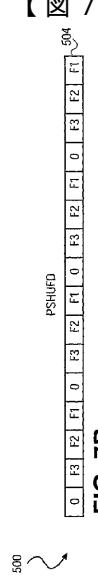

一般的に、フィルタリング処理では、第2ベクトルはフィルタ係数を含んでいる。従って、XMMレジスタを用意するため、係数がレジスタの一部にロードされ、シャッフル命令145を使ってレジスタの残りの部分にコピーするようにしてもよい。例えば、図7Aに示されるように、例えば、XMM128ビットレジスタのような係数データ記憶装置502は、データロード命令の実行に応答して、3つの係数により初期ロードされる。しかしながら、フィルタ係数はデータ処理以前にメモリにおいて構成されるようにしてもよいということは当業者には理解されるであろう。さらに、フィルタリング処理以前に、係数はメモリ内の係数の構成に基づき図7Bに示されるように初期ロードされてもよい。

10

#### 【0041】

さらに、係数レジスタ502には、符号付きあるいは符号なしとして符号化が可能なフィルタ係数F3、F2及びF1が含まれる。係数レジスタ502がロードされると、既存の命令PSHUFDを使って、図7Bに示されるような結果を得るために、係数レジスタの残り部分内のフィルタ係数をコピーする。図7Bに示されるように、係数レジスタ504には、データ処理の並列実行に要するシャッフルされた係数が含まれる。当業者に知られるように、3つの係数を含むフィルタは画像処理アルゴリズムではよく知られている。しかしながら、JPEG2000のようなフィルタリング処理では、9つの16ビット係数と7つの16ビット係数が利用される。従って、このような係数の処理は係数レジスタの能力を超えるものであり、部分的にフィルタリングされた結果が生じることとなる。各係数を使って最終的な結果が得られるまで、処理が続けられる。

20

#### 【0042】

図7Cを参照するに、図7Cは、図5に示されるようなソースレジスタ404に初期的に含まれ、目的レジスタ406においてシャッフルされたソースレジスタ506の画素値の配置を示す。データ処理の実行に応答して、PMAADDUSBW命令を使って、目的レジスタ510に格納されるにより2つの乗算の和が計算される。しかしながら、計算を完了させ、選ばれたデータ処理に対するデータ処理結果を生成するため、目的レジスタ510の隣接する積和ペアを加算する必要がある。

30

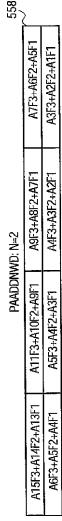

#### 【0043】

従って、乗加算命令の和が一般的である2画素より長い場合、個々の和が加算される必要がある。しかしながら、既存のコンピューターアーキテクチャでは、隣接する和が同じ目的レジスタにあるということから、隣接する和を加える効率的な方法は提供されていない。従って、本発明は、隣接加算命令を利用している。その結果が図8A～図8Dに示されている。

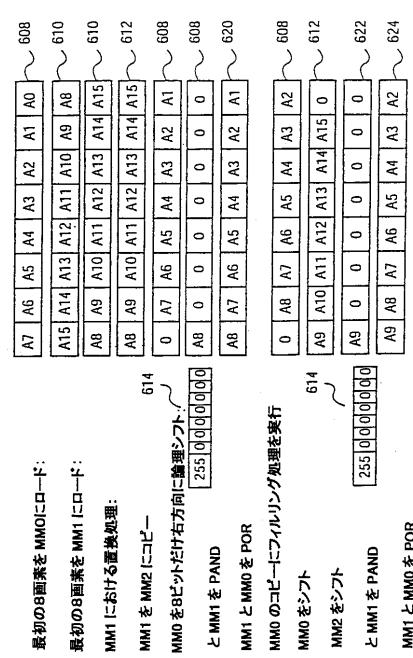

#### 【0044】

図8Aを参照するに、図8Aは、32ビット和を与えるために、2つの隣接する16ビット値の加算(PADDWD処理157)に従う目的レジスタ552を示す。さらに、図8Aは、4バイトの積の32ビット和を与えるために加算される乗加算命令の2つの隣接する16ビットの結果を示す。図8Bは、32ビット和を与えるために4つの隣接する16ビット値を加算する隣接加算命令(PAADDWD処理157)を示す。さらに、バイト乗加算命令の4つの隣接する16ビットの結果が、8バイトの積の32ビット和を与えるために加算される。図8Cは、32ビット和を与えるために8つの隣接16ビット値を加算する隣接加算命令(PAADD8WD処理157)を示す。さらに、この例は、16倍との積の32ビット和を与えるために加算されるバイト乗加算処理の8つの隣接する16ビットの結果を示す。

40

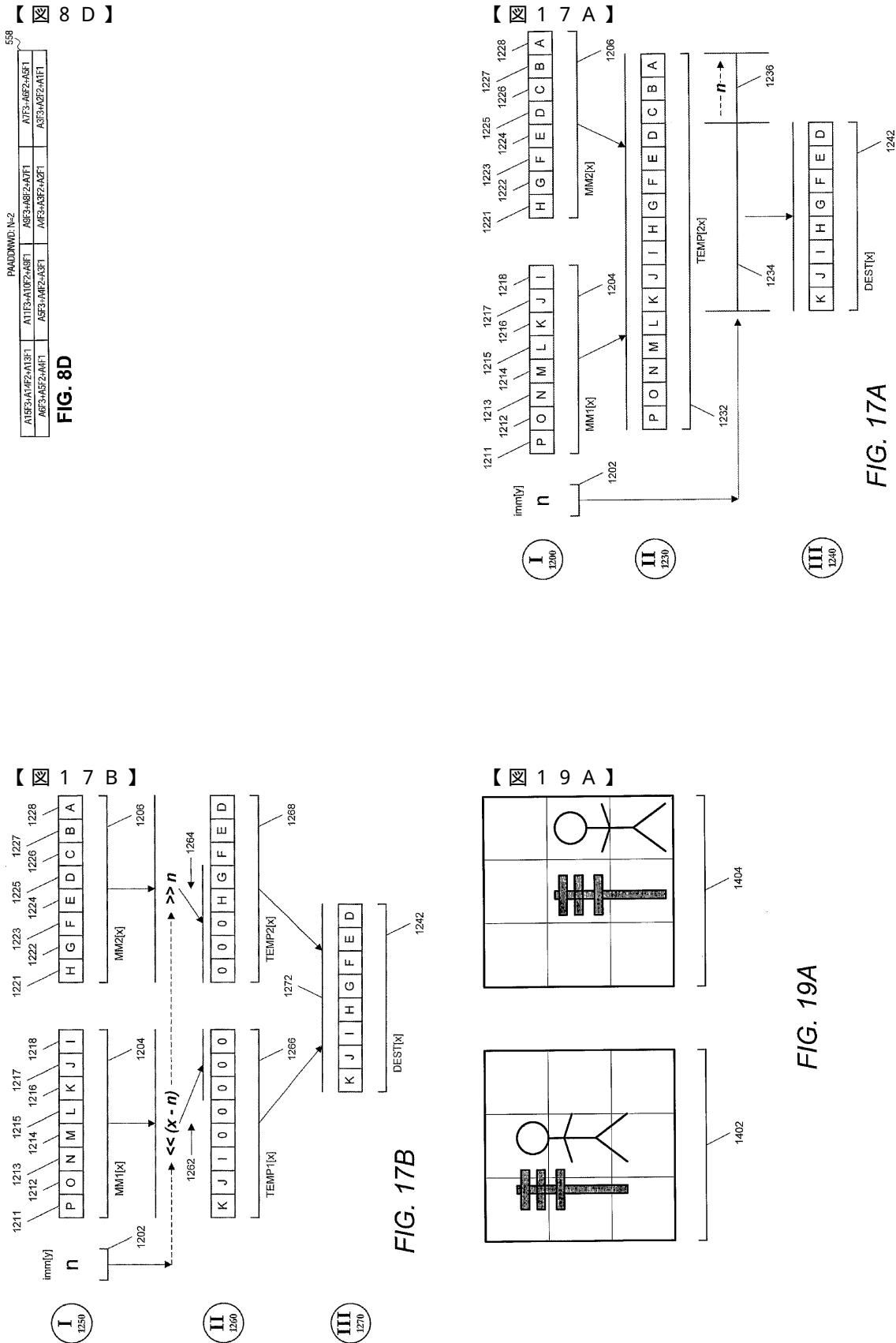

#### 【0045】

隣接加算処理を実行するための命令の選択は、和(N)におけるターン(turn)数に基づく。例えば、図7Aから図7Cに示されるような3タップフィルタを利用することにより、第1命令(PAADD2WD処理157)は図8Dに示されるような以下の結果

50

を取得する。しかしながら、2つの16ビット画素ベクトル（例えば、マクロブロックの第1ライン）間の相関に対して、図8Cに示されるような最終命令（PADD8WD処理157）が利用される。このような処理は、 SIMDレジスタのサイズが大きくなるに従い、効率的な実行のためにますます重要となってきている。このような処理がなければ、多くの追加的な命令が必要となる。

#### 【0046】

さらに、本発明により示されるように、隣接加算命令セットは、加算可能な隣接値の数と共通のデータタイプを広範にサポートする。一実施例において、隣接する16ビット値の加算は、2つの隣接する値を加算すること（N=2）から開始され、加算対象の数を4（N=4）、それから8（N=8）、そしてレジスタの合計まで倍加する範囲を有する命令セットを含む。16ビットの隣接加算の和のデータサイズは32ビットである。他の実施例では、隣接する16ビットの値が32ビットの和となるよう加算される（PADDWD処理161）。

10

#### 【0047】

この実施例では、16ビットのデータサイズによる他の命令は含まれない。なぜなら、32ビットの入力による隣接加算命令を使って、16ビットの入力による命令によって生成される和が加算される。どちらの実施例においても、2つの隣接する値を加算すること（N=2）から開始され、加算対象の数を4（N=4）、それから8（N=8）、そしてレジスタの合計まで倍加する範囲を有する32ビット隣接加算命令セット（PADDNDW処理159）が含まれる。32ビット隣接加算の和のデータサイズは32ビットである。いくつかのケースでは、その結果はレジスタを満たさない。例えば、図8Aから図8Cに示されるような命令である3つの相異なる隣接加算により、4、2及び132ビットの結果がもたらされる。一実施例では、これらの結果は目的データ記憶装置の下位及び最下位部分に格納される。

20

#### 【0048】

従って、図8Bに示されるように、2つの32ビットの結果がある場合、この結果は下位の64ビットに格納される。図8Cに示されるように、32ビットの結果が1つである場合、この結果は下位の32ビットに格納される。当業者により認識されるように、アプリケーションの中には隣接バイトの和を利用するものもある。本発明は、16ビットワードを与える2つの隣接する符号付きバイトを加算する命令（PADDNB処理155）と、16ビットワード結果を与える2つの隣接する符号なしバイトを加算する命令によりバイトの隣接加算をサポートしている。2より多くの隣接バイトの加算を要するアプリケーションでは、適当な16ビット隣接加算処理により2バイトの16ビットの和が加算される。

30

#### 【0049】

データ処理結果が計算されると、次の処理はこの結果をメモリ装置に送ることからなる。上述の実施例によって示されるように、この結果は32ビットの精度による符号化が可能である。従って、例えば、レジスタ全体に実行される右方向シフト論理処理（PSRLDQ）や右方向シフトダブルクアドワード論理（shift double quad-word right logical quad）と共に、上述のMOV D処理143のようなダブルワードに関し実行されるシンプルな転送処理を利用することにより、結果がメモリに書き込まれる。さらに、すべての結果をメモリに書き込むには、第1のケース（図8A）では4つのMOV Dと3つのPSRLDQを必要とし、第2のケース（図8B）では2つのMOV Dと1つのPSRLDQを必要とし、最後のケースでは図8Cに示されるように1つのMOV Dが必要とされる。

40

#### 【0050】

しかしながら、図7Cに示されるように、隣接加算処理は並列に実行することが可能ではあるが、一般にフィルタリング計算では画像における次の画素が必要とされる。さらに、複数の画素がソースデータ記憶装置またはレジスタにロードされる必要がある。各時点で8つの画素をレジスタにロードすることを回避するために、この処理に2つの解決法が

50

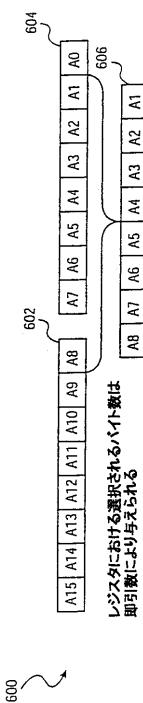

提案される。一実施例では、本発明は、図 9 A に示されるように、レジスタマージ処理 163 を説明する。さらに、目的レジスタ 606 における画素 A1 から A8 を処理するために、画素 A7 から A1 が画素 A8 により連結され、目的レジスタ 606 に画素 A8 から A1 が形成される。これにより、レジスタマージ処理は入力引数により与えられるバイト数を利用して、レジスタの選択を行う。

#### 【0051】

図 9 B を参照するに、図 9 B は、レジスタマージ処理の実行のための他の実施例を示す。初期的に、8つの画素が第 1 ソースレジスタ 608 (MM0) にロードされる。次に、後続の 8 つの画素が第 2 ソースレジスタ 610 (MM1) にロードされる。次に、置換処理が第 2 ソースレジスタ 610 に対し実行される。実行されると、レジスタ 610 が第 3 ソースレジスタ (MM2) 612 にコピーされる。次に、第 1 ソースレジスタ 608 が 8 ビット分右方向にシフトされる。さらに、第 2 ソースレジスタ 610 とマスクレジスタ 614 が、Packed 論理 AND 命令に従って合成され、第 1 ソースレジスタ 608 に格納される。

10

#### 【0052】

次に、論理 OR 演算が第 2 ソースレジスタ 610 と第 1 ソースレジスタ 608 に対し実行され、目的レジスタ 620 に結果が生成され、レジスタマージ処理が実行された。この処理は、第 1 ソースレジスタ 608 をシフトすることにより、図示されるように続けられる。次に、第 2 ソースレジスタ 610 がシフトされ、レジスタ 612 が生成される。次に、論理 AND 演算がマスクレジスタ 614 と第 2 ソースレジスタ 612 に対し実行され、結果が目的レジスタ 622 に格納される。最後に、Packed OR 演算が第 2 ソースレジスタ 612 と第 1 ソースレジスタ 608 に対し実行され、目的レジスタ 624 に後続のレジスタマージ処理が生成される。本発明の教示を実現する手続き方法が説明される。

20

#### 動作

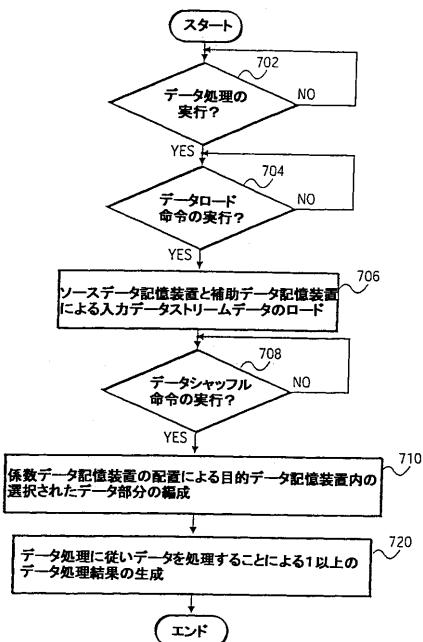

図 10 を参照するに、図 10 は、例えば、図 1 及び図 2 に示されるようなコンピュータシステム 100 におけるコンテンツデータの効率的フィルタリング及び畳み込みのための方法 700 を示すブロック図を示す。ここで説明されるように、コンテンツデータとは、画像、音声及び映像データを意味する。さらに、本発明は、当業者に理解されるように、例えば、128 ビット Intel (登録商標) アーキテクチャ SSE2 MMX レジスタのようなデータレジスタを含むデジタルデータの格納が可能な様々な装置を有するデータ記憶装置に關し言及している。

30

#### 【0053】

図 10 を再び参照するに、本発明による方法は処理ブロック 702 から開始され、データ処理が実行されているか判断される。ここで説明されるように、このデータ処理には、以下に限定されないが、画素データに關し実行される畳み込み及びフィルタリング処理が含まれる。これが実行されると、処理ブロック 704 が実行される。処理ブロック 704 では、データロード命令が実行される。このデータロード命令の実行に応答して、処理ブロック 706 において、入力データストリームデータが、例えば図 2 に示されるように、ソースデータ記憶装置 212A と補助データ記憶装置 212B にロードされる。

40

#### 【0054】

処理ブロック 708 において、このデータ処理によりデータシャッフル命令が実行されたか判断される。データシャッフル命令の実行に応答して、処理ブロック 710 において、例えば、ソースデータ記憶装置 212B からのデータの選択部分が、目的データ記憶装置内で、あるいは係数データ記憶装置 (図 5 を参照) 内の係数配置に従って構成される。係数データ記憶装置内の係数が、所望のデータ処理計算に従って (例えば、図 7A 及び図 7B に示されるように) 構成される。一実施例では、フィルタリング処理以前に、係数はメモリ内で構成される。従って、シャッフルする必要なく、係数は係数データ記憶装置にロードすることができる (図 7B 参照)。

#### 【0055】

上述のように、図 7A から図 7C に示されるように、データ処理に求められる並列計算

50

の実現にはデータ及び係数の順序付けが必要とされる。しかしながら、これらの係数はデータ処理前に既知となっているので、データ処理中係数をシャッフルする必要なくメモリにおいて構成されるように係数レジスタへのロードを可能にするために、係数はメモリ内で構成されるようにしてもよい。最後に、処理ブロック 720において、ロードされたデータはデータ処理に従って処理され、1つ以上のデータ処理結果が生成される。生成されると、データ処理結果はメモリに書き込まれる。

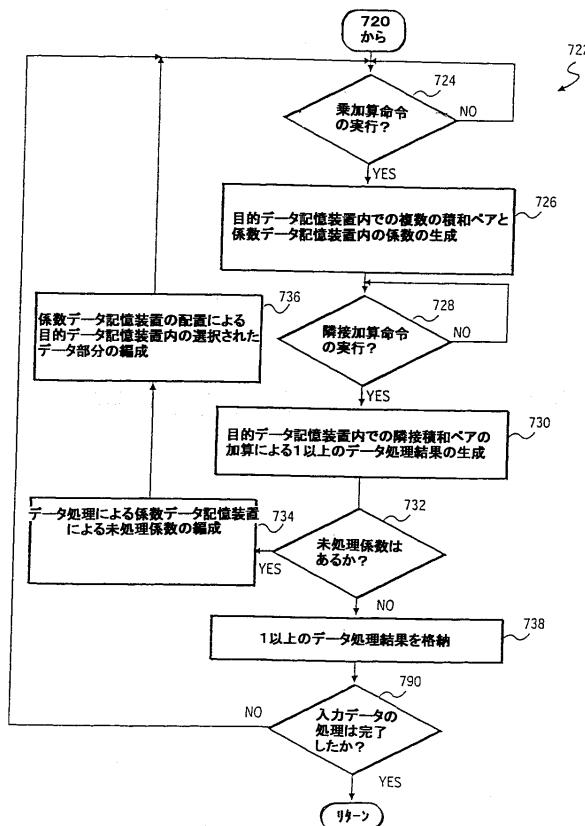

#### 【0056】

図11を参照するに、図11は、データ処理に従ってデータを処理するための方法722を示すブロック図を示す。処理ブロック724において、データ処理が乗加算命令を実行したか判断される。乗加算命令の実行に応答して、処理ブロック726において、図7Cに示されるように、目的記憶装置におけるデータと係数データ記憶装置における係数の複数の積和ペアが生成される。次に、処理ブロック728において、データ処理が隣接加算命令を実行したか判断される。

10

#### 【0057】

隣接加算命令の実行に応答して、処理ブロック730において、目的データ記憶装置510(図7C)における隣接積和ペアが加算され、1つ以上のデータ処理結果が生成される(図8D参照)。しかしながら、ある実施例では、係数の個数が係数レジスタの容量を超える場合(処理ブロック732参照)、部分的なデータ処理結果が取得される。従って、係数(処理ブロック734)とデータ(処理ブロック736)の処理及び構成は、選択的な処理ブロック732から736に示されるように、最終的なデータ処理結果が得られるまで続けられる。そうでない場合、処理ブロック738において、1つ以上のデータ処理結果は格納される。最後に、処理ブロック790において、入力データストリームデータの処理が完了したか判断される。処理が完了すると、制御フローは処理ブロック720に戻り、方法700は終了される。

20

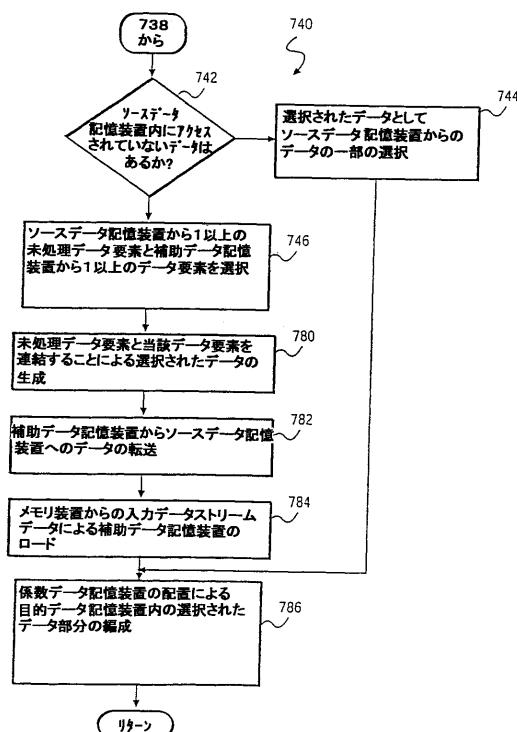

#### 【0058】

図12を参照するに、図12は、追加的な入力データを処理するための追加的方法740を示すブロック図を示す。処理ブロック742において、ソースデータ記憶装置212A内にアクセスされていないデータが存在するか判断される。ここで説明されるように、アクセスされていないデータとは、乗加算命令を実行するためデータ記憶装置においてシャッフルされていないソースデータ記憶装置212A内のデータを意味する。データ記憶装置がアクセスされていないデータを含む場合、処理ブロック744において、データの一部が選択データとしてソースデータ記憶装置から選択される。選択されると、処理ブロック786が実行される。

30

#### 【0059】

そうでない場合、処理ブロック746において、ソースデータ記憶装置から1つ以上の未処理データ要素が選ばれると共に、補助データ記憶装置から1つ以上のデータ要素が選ばれる。ここで説明されるように、未処理データ要素とは、データ処理結果がまだ計算されていないデータ要素を意味している。次に、処理ブロック780において、レジスタマージ命令(図9A及び図9B参照)が実行され、ソースデータ記憶装置の未処理データ要素と補助データ記憶装置から選ばれたデータ要素が連結され、選択されたデータが生成される。次に、処理ブロック782において、補助データ記憶装置からのデータがソースデータ記憶装置に転送される。

40

#### 【0060】

さらに、ソースデータ記憶装置は、すべて処理済であるため、もはや必要とされない。従って、未処理データを含むデータの補助記憶が利用され、ソースデータ記憶装置におけるデータが上書きされる。処理ブロック784において、補助データ記憶装置は、フィルタリング処理や畳み込み処理のような追加的なデータ処理に必要なメモリ装置からの入力データストリームデータによりロードされる。最後に、処理ブロック786において、選択されたデータが係数データ記憶装置(図5参照)における係数配置に従って、目的データ記憶装置内で構成される。これが実行されると、制御フローは選択されたデータの継続

50

処理のため、図 11 に示されるように処理ブロック 790 に戻る。

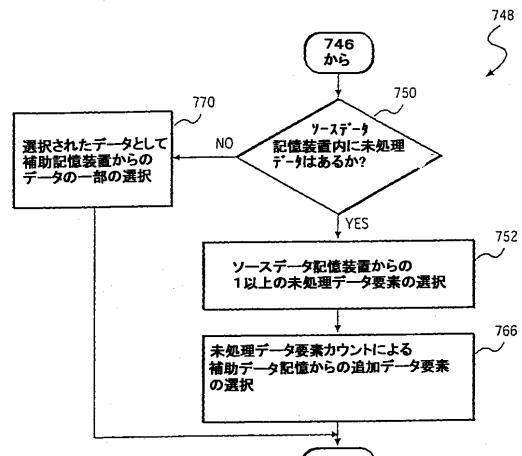

【0061】

図 13 を参照するに、図 13 は、未処理データ要素を選択するための追加的方法 748 を示す。処理ブロック 750 において、ソースデータ記憶装置に未処理データが含まれているか判断される。ソースデータ記憶装置におけるデータの各部分が処理済である場合、処理ブロック 770 が実行される。処理ブロック 770 において、選択されたデータとして機能するデータの一部が補助データ記憶装置から選ばれ、データ処理に従い処理される。

【0062】

そうでない場合、処理ブロック 752 において、1 つ以上の未処理データ要素がソースデータ記憶装置から選ばれる。最後に、処理ブロック 766 において、未処理データ要素の合計に従い補助データ記憶装置から追加的なデータ要素が選択され、選択されたデータが生成される。さらに、データ処理の実行前に、目的データ記憶装置におけるシャッフル処理のため選択されたデータは、フィルタ係数の個数に基づきデータ要素数に制限される。従って、このデータ要素の合計を利用して、レジスタマージ処理実行のため、補助データ記憶装置から選ばれるデータ要素数を決定するために、未処理データ要素数がデータ要素の合計から差し引かれる。

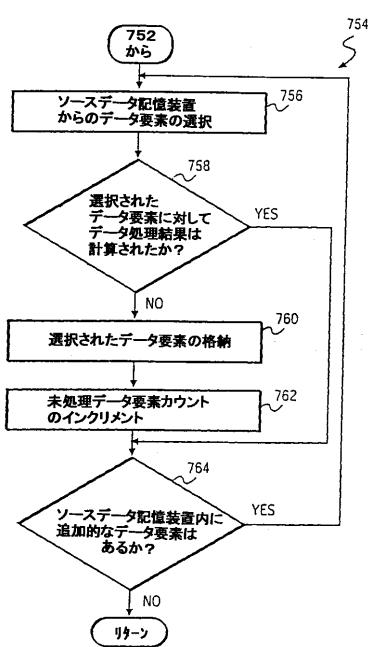

【0063】

最後に、図 14 を参照するに、図 13 に示されるように、処理ブロック 752 の未処理データ要素を選択するための追加的方法 754 を示す。処理ブロック 756 において、ソースデータ記憶装置からデータ要素が選ばれる。次に、処理ブロック 758 において、当該データ要素のデータ処理結果が計算されているかどうか判断される。この結果が計算されている場合、選択されたデータ要素は破棄される。そうでない場合、処理ブロック 760 において、この選択されたデータ要素は未処理データ要素であり、格納される。次に、処理ブロック 762 において、未処理データ要素の合計がインクリメントされる。最後に、処理ブロック 764 において、ソースデータ記憶装置内の各データ要素が処理されるまで、処理ブロック 756 から 762 が繰り返される。

【0064】

さらに、本発明の教示を使って、不要なデータタイプ変更が回避される。これにより、命令あたりの SIMD 处理数を最大化することができる。さらに、算術演算のためのデータ順序付けに要するクロックサイクル数を大幅に減らすことができる。従って、表 1 は、本発明のより説明された教示及び指示を利用したいくつかのフィルタリングアプリケーションのための高速化された推定値を与える。

【0065】

【表 1】

| 処理              | スピードアップ |

|-----------------|---------|

| 9-7ウェーブレット      | 1.7     |

| バイト係数による3×3フィルタ | 4.3     |

| 透かし補正           | 6.8     |

他の実施例

SIMD レジスタを利用したコンテンツデータの効率的なフィルタリング及び畳み込み処理を提供するコンピューターアーキテクチャの一実施例のいくつかの特徴が説明してきた。しかしながら、コンピューターアーキテクチャの様々な実施形態により、上述の特徴の補完、補助及び / あるいは置換を含む多くの特徴が提供される。これらの特徴は、コンピューターアーキテクチャの一部、あるいは異なる実施形態でのソフトウェアまたはハードウ

10

20

30

40

50

エア要素の一部として実現される。また、上記記述では説明のため、本発明の完全な理解を与えるため特定の用語が利用された。しかしながら、本発明の実践のために特定の詳細が必ずしも必要でないということは当業者には明らかであろう。

#### 【 0 0 6 6 】

さらに、ここで説明された実施例は、S I M D レジスタを使ったコンテンツデータの効率的なフィルタリング及び畳み込み処理のためのシステムを対象としているが、本発明の教示は他のシステムに適用可能であるということは当業者には理解されるであろう。実際、画像、音声及び映像データの処理システムは、本発明の範囲及び趣旨から逸脱することなく本発明の教示の範囲内に入る。上述の実施例は、本発明の原理及びその実践的適用を最も良く説明するため選ばれ、記述された。これらの実施例は、当業者が特定の利用形態に適するよう様々な修正を行うことにより、発明及び様々な実施例を最も良く利用できるよう選ばれた。

#### 【 0 0 6 7 】

本発明の実施例は、従来技術に対する多くの効果を提供する。本発明は、複数の配列長、データサイズ及び係数符号に対するフィルタリング／畳み込み処理を効率的に実行することができる。これらの処理は、小さな単一命令多重データ（S I M D）命令群の一部であるいくつかの命令を利用することにより実行される。従って、本発明は不要なデータタイプ変更を回避する。この結果、不要なデータタイプ変更を回避することによって、本発明は命令あたりのS I M D処理数を最大化する一方、乗加算演算のような算術処理のためデータを順序付ける必要があるクロックサイクル数を大きく減少させることができる。

#### 【 0 0 6 8 】

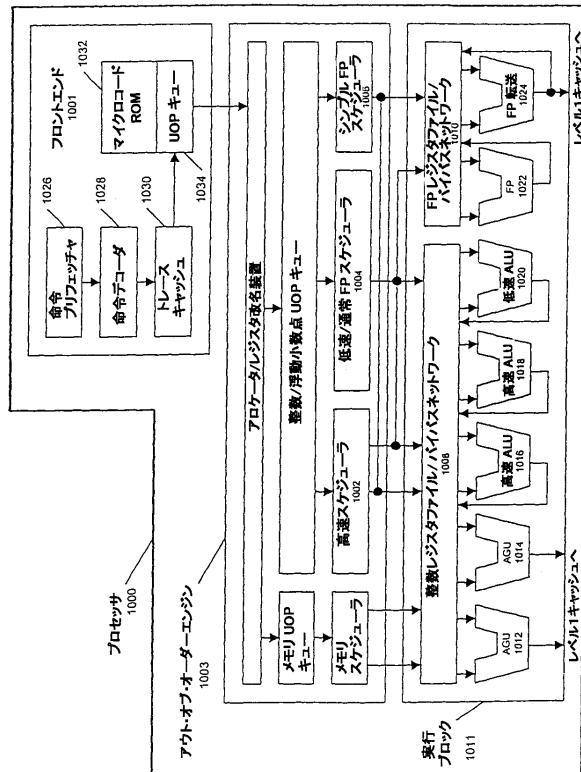

図15は、本発明による右方向平行シフトマージ処理を実行する論理回路を含む一例となるプロセッサのマイクロアーキテクチャのブロック図である。右方向シフトマージ処理はまた、上記説明と同様に、レジスタマージ処理及びレジスタマージ命令として呼ばれる。右方向シフトマージ命令（P S R M R G）の一実施例のため、当該命令は図1、9A及び9Bのレジスタマージ処理167と同じ結果をもたらす。イン・オーダーフロントエンド（in-order front end）1001は、実行対象のマクロ命令を取り込み、プロセッサパイプラインでの後の利用のためそれらを用意するプロセッサ1000の一部である。本実施例のフロントエンドは複数のユニットを含んでいる。命令プレフェッチャ（instruction prefetcher）1026は、メモリからマクロ命令を取り込み、それらを命令デコーダ1026に供給する。そして命令デコーダ1028は、このマクロ命令をマシーンが実行可能なマイクロ命令あるいはマイクロ処理（またはマイクロo pまたはu o pと呼ばれる）と呼ばれる要素に復号する。トレースキャッシュ1030は、復号化されたu o pを受け取り、実行のためu o pキューリストラクチャ1034においてそれらを順序付けされたプログラムシーケンスあるいはトレースに分解する。トレースキャッシュ1030が複雑なマクロ命令に直面すると、マイクロコードROM1032が当該処理の完了に必要なu o pを提供する。

#### 【 0 0 6 9 】

多くのマクロ命令が1つのマイクロo pに変換される一方、他のマクロ命令は完全な処理の完了のため複数のマイクロo pを必要とするかもしれない。本実施例では、マクロ命令の完了のため4より多くのマイクロo pが必要な場合、デコーダ1028はマイクロコードROM1032にアクセスし、マクロ命令を実行する。一実施例では、右方向平行シフトマージアルゴリズムのための命令は、多数のマイクロo pが処理の実行に必要である場合、マイクロコードROM1032に格納することができる。トレースキャッシュ1030は、入力ポイントPLA（Programmable Logic Array）を参照し、マイクロコードROM1032における分割アルゴリズムのためのマイクロコードシーケンスを読み込むための正しいマイクロ命令ポインタを決定する。マイクロコードROM1032が現在のマクロ命令に対するマイクロo pの順序付けを完了すると、マシーンのフロントエンド1001はトレースキャッシュ1030からマイクロo pの取り込みを再開する。

10

20

30

40

50

## 【0070】

いくつかの SIMD 及び他のマルチメディアタイプの命令は複雑な命令とみなされる。浮動小数点に関する大部分の命令もまた複雑な命令である。さらに、命令デコーダ 1028 が複雑なマクロ命令に直面すると、マイクロコード ROM 1032 は当該マクロ命令のためのマイクロコードシーケンスを抽出するために、適当な位置でアクセスされる。このマクロ命令の実行に要する様々なマイクロ op が、適当な整数及び浮動小数点実行ユニットにおける実行のため、アウト・オブ・オーダー実行エンジン 1003 に通信される。

## 【0071】

アウト・オブ・オーダー実行エンジン 1003 では、実行のためにマイクロ命令が用意されている。アウト・オブ・オーダー実行論理は、マイクロ命令がバイオペランドに入り、実行のためスケジューリングされるとき、パフォーマンスを最適化するためマイクロ命令のフローを平滑化及び順序調整をするための複数のバッファを有する。割り当て論理は、各 op が実行に必要とするマシンバッファやリソースを割り当てる。レジスタリネーム論理は、論理レジスタをレジスタファイルの入力に改名する。割り当て論理はまた、メモリスケジューラ、高速スケジューラ 1002、低速 / 通常浮動小数点スケジューラ 1004、及びシンプル浮動小数点スケジューラ 1006 の命令スケジューラの前に、メモリ処理及び非メモリ処理のための 2 つの op キューの 1 つにおける各 op に対する入力を割り当てる。op スケジューラ 1002、1004 及び 1006 は、スケジューラの従属入力レジスタオペランドソースの準備状況と、op が処理の遂行に必要とする実行リソースの利用可能状況に基づき、op の実行準備がいつ整うかを判断する。本実施例の高速スケジューラ 1002 がメインクロックサイクルの半サイクルごとにスケジューリングを行う一方、その他のスケジューラはメインプロセッサクロックサイクルあたり 1 回だけスケジューリングを行うことができる。スケジューラはディスパッチポートを調停して、実行のための op をスケジューリングする。

## 【0072】

レジスタファイル 1008 と 1010 は、スケジューラ 1002、1004 及び 1006 と、実行ブロック 1011 の実行ユニット 1012、1014、1016、1018、1020、1022 及び 1024 との間に配置される。整数及び浮動小数点演算のためにそれぞれレジスタファイル 1008 と 1010 がある。本実施例の各レジスタファイル 1008 と 1010 はまた、まだレジスタファイルに書き込まれていない完了結果を新しい従属 op にバイパスあるいは転送するバイパスネットワークを含む。整数レジスタファイル 1008 と 浮動小数点レジスタファイル 1010 はまた、互いにデータの通信を行うことができる。一実施例において、整数レジスタファイル 1008 は 2 つのレジスタファイルに分割され、その一方は下位 32 ビットデータ用のレジスタファイルであり、もう一方は上位 32 ビットデータ用のレジスタファイルである。一実施例の浮動小数点レジスタファイルは 1010 は、128 ビット幅の入力を有する。これは浮動小数点命令は典型的に、64 から 128 ビット幅のオペランドを有するからである。

## 【0073】

実行ブロック 1011 は、命令を実際に実行する実行ユニット 1012、1014、1016、1018、1020、1022 及び 1024 を含む。この部分は、マイクロ命令が実行に必要とする整数及び浮動小数点データオペランド値を格納するレジスタファイル 1008 と 1010 を含む。本実施例のプロセッサ 1000 は、アドレス生成ユニット (AGU) 1012、AGU 1014、高速 ALU 1016、高速 ALU 1018、低速 ALU 1020、浮動小数点 ALU 1022 及び浮動小数点移動ユニット 1024 からなる複数の実行ユニットから構成される。本実施例において、浮動小数点実行ブロック 1022 と 1024 は、浮動小数点 MMX、SIMD 及び SSE 处理を実行する。本実施例の浮動小数点 ALU 322 は、割算、平方根及び剰余に関するマイクロ op を実行するための 64 ビット単位浮動小数点割算器を有する。本発明の実施例では、浮動小数に関する任意の処理は浮動小数点ハードウェアにより引き起こされる。例えば、整数形式と浮動小数形式間の変換には、浮動小数点レジスタファイルが関係する。同じように、浮動小数割算処理

10

20

30

40

50

理は浮動小数点割算器において引き起こされる。他方、非浮動小数点数及び整数タイプは整数ハードウェアリソースにより処理される。単純かつ頻繁に使用される A L U 演算は、高速 A L U 実行ユニット 1 0 1 6 と 1 0 1 8 において処理される。本実施例の高速 A L U 1 0 1 6 と 1 0 1 8 は、半分のクロックサイクルの効果的な待ち時間により高速処理を実行することができる。一実施例では、大部分の複雑な整数演算は低速 A L U 1 0 2 0 に渡される。低速 A L U 1 0 2 0 は、乗算、シフト、フラグ論理及び分岐処理のような長い待ち時間を要するタイプの処理用の整数実行ハードウェアを含む。メモリロード／ストア処理は、A G U 1 0 1 2 と 1 0 1 4 により実行される。本実施例では、整数 A L U 1 0 1 6 、 1 0 1 8 及び 1 0 2 0 は、64ビットデータオペランドに対する整数処理の実行について説明される。他の実施例では、A L U 1 0 1 6 、 1 0 1 8 及び 1 0 2 0 は、16、32、128、256などの様々なデータビットをサポートするよう実現することができる。同じように、浮動小数点ユニット 1 0 2 2 と 1 0 2 4 は、様々なビット幅を有するオペランドをサポートするよう実現することができる。一実施例では、浮動小数点ユニット 1 0 2 2 と 1 0 2 4 は、S I M D 及びマルチメディア命令について、128ビット幅の P a c k e d データオペランドにおいて実行される。

#### 【 0 0 7 4 】

本実施例では、u o p スケジューラ 1 0 0 2 、 1 0 0 4 及び 1 0 0 6 は、親ロードが実行を完了する前に、従属処理をディスパッチする。u o p がプロセッサ 1 0 0 0 において投機的にスケジューリング及び実行されるとき、プロセッサ 1 0 0 0 はまたメモリミスを処理するための論理を含む。データキャッシュにおいてデータロードがミスする場合、一時的に誤ったデータをスケジューラに残したパイプラインにおけるフライト ( f l i g h t ) での従属処理が存在しうる。リプレイ機構が、誤ったデータを利用する命令を追跡及び再実行する。従属処理のみがリプレイされる必要があり、独立した処理は完了させることができる。プロセッサの一実施例のスケジューラ及びリプレイ機構はまた、拡張された精度整数割算処理の命令シーケンスを獲得するよう構成されている。

#### 【 0 0 7 5 】

「レジスタ」という単語は、オペランドを特定するマクロ命令の一部として利用されるオン・ボードプロセッサ記憶領域を参照するのにここでは使われる。言い換えると、ここで呼ばれるレジスタとは、プロセッサ外部から（プログラマーの視点から）見ることができるものである。しかしながら、ここで述べられるレジスタは、例えば、専用物理レジスタ、レジスタリネーミングを利用した動的に割り当てられた物理レジスタ、専用物理レジスタと動的に割り当てられる物理レジスタとを組み合わせたものなどの様々なテクニックを利用したプロセッサ内部の回路により実現することができる。

#### 【 0 0 7 6 】

以下の説明のため、レジスタは、カリフォルニア州サンタクララのインテルコーポレーションからのM M X 技術が可能なマイクロプロセッサにおける 64ビット幅 M M X (商標) レジスタ (mmレジスタ) のような P a c k e d データの保持が可能なデータレジスタであると解釈される。このような M M X レジスタは、整数及び浮動小数点の両方の形式で利用可能であり、S I M D と S S E 命令を伴う P a c k e d データ要素により動作可能である。同様に、S S E 2 技術に関する 128ビット幅 X M M レジスタもまた、そのような P a c k e d データオペランドの保持に利用可能である。

#### 【 0 0 7 7 】

以下の図面による例では、多数のデータオペランドが説明される。簡単化のため、データセグメントは A からアルファベット順にラベル付けされ、A は最下位アドレスに、Z は最上位アドレスに位置する。従って、A はアドレス 0 に、B はアドレス 1 に、C はアドレス 3 に、以下同様にしてラベル付けされる。いくつかの例では、データシーケンスは逆アルファベット順に配置された文字により表されるが、アドレッシングは依然として 0 にある A から、1 にある B という順で開始される。概念的には、一実施例のための右方向シフトマージと同様に、右方向シフト処理は、シーケンスが D 、 C 、 B 、 A である場合、最下位アドレスのデータセグメントを右方向にシフトすることに関する。右方向のシフトは、

1つのデータブロック分のデータ要素を固定線に沿って単に右方向にシフトする。さらには、概念的には右方向シフトマージ処理は、最右データセグメントを1つのオペランドから他のデータオペランドの左側に、あたかもこれら2つのオペランドが連続するように、右方向にシフトする。

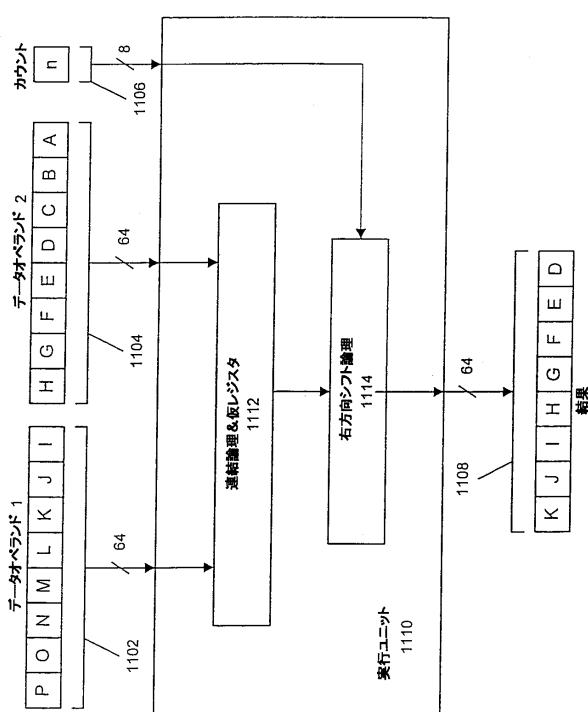

【0078】

図16Aは、本発明によるデータオペランドに対する右方向平行シフトマージ処理を実行する論理の一実施例のブロック図である。本実施例の右方向シフトマージ（またはレジスタシフト）処理のための命令（PSRMRG）は、第1データオペランド1102、第2データオペランド1104及びシフトカウント1106からなる3つの情報から開始される。一実施例では、シフトPSRMRG命令が1つのマイクロ処理に復号される。他の実施例では、当該命令はデータオペランドに対するシフトマージ処理を実行する様々なマイクロopに復号されてもよい。本実施例では、データオペランド1102と1104はレジスタ/メモリに格納された64ビット幅のデータ片であり、シフトカウント1106は8ビット幅の即値である。特定の実現に応じて、データオペランドとシフトカウントは、それぞれ128/256ビットと16ビットのような他の幅であってもよい。本実施例での第1オペランド1102は、P、O、N、M、L、K、J及びIの8つのデータセグメントから構成される。第2オペランドもまた、H、G、F、E、D、C、B及びAの8つのデータセグメントから構成される。これらデータセグメントは等しい長さを有し、それぞれ1バイト（8ビット）データから構成される。しかしながら、本発明の他の実施例はより長い128ビットのオペランドにより動作する。この場合、各データセグメントは1バイト（8ビット）からなり、128ビット幅のオペランドは16バイト幅のデータセグメントを有する。同様に、各データセグメントがダブルワード（32ビット）またはクアドワード（64ビット）である場合、128ビットオペランドはそれぞれ4ダブルワード幅あるいは2クアドワード幅のデータセグメントを有する。従って、本発明の実施例は特定の長さのデータオペランド、データセグメントあるいはシフトカウントに限定されるものではなく、各実現形態に対し適当なサイズとすることができます。

【0079】

オペランド1102と1104は、レジスタ、メモリ領域、レジスタファイルあるいはそれらを組み合わせたものに格納することができる。データオペランド1102と1104とカウント1106が、右方向シフトマージ命令と共にプロセッサ内の実行ユニット1110に送信される。右方向シフトマージ命令が実行ユニット1110に届くまでに、当該命令はプロセッサパイプラインにおいて復号されるべきであった。従って、右方向シフトマージ命令は、マイクロ処理（uop）による形式あるいは他の復号形式でありうる。本実施例では、2つのデータオペランド1102と1104が連結論理と仮のレジスタにおいて受信される。連結論理は、これら2つのオペランドに対しデータセグメントをマージ/ジョインし、新しいデータブロックを仮のレジスタに配置する。ここで、この新しいデータブロックは、P、O、N、M、L、K、J、I、H、G、F、E、D、C、B及びAの16のデータセグメントから構成される。本実施例は64ビット幅のオペランドにより動作するので、合成されたデータを保持する必要のある仮のレジスタは128ビット幅である。128ビット幅のデータオペランドに対しては、256ビット幅の仮レジスタが必要とされる。

【0080】

実行ユニット1110における右方向シフト論理1114は、仮レジスタのコンテンツを取得し、カウント1106により要求に従い、nデータセグメントだけデータブロックを右方向に論理シフトする。本実施例では、カウント1106は右方向にシフトするバイト数を示す。特定の実現形態に応じて、カウント1106を使ってデータセグメントの粒度に応じたシフトされるべきビット数、ニブル（nibble）数、ワード数、ダブルワード数、クアドワード数などを示すことができる。本実施例では、仮レジスタのコンテンツが3バイトだけシフトされるようnは3に等しくされる。各データセグメントがワードあるいはダブルワード幅であるとき、カウントはそれぞれシフトされるべきワード数ある

10

20

30

40

50

いはダブルワード数を表す。本実施例では、レジスタのデータが右方向にシフトされるとき、空のスペースを埋めるために、仮レジスタの左側から0がシフト入力される。従って、シフトカウント1106がデータオペランドのデータセグメント数（この場合、8）より大きい場合、1つ以上の0が結果となる1108に現れる。さらに、シフトカウント1106が両方のオペランドに対しデータセグメントの総数以上であれば、すべてのデータセグメントがシフトにより破棄されるので、結果はすべて0となる。右方向シフト論理1114は、仮レジスタから適当な個数のデータセグメントを結果1108として出力する。他の実施例では、出力マルチブレクサあるいはラッチを、結果を出力する右方向シフト論理の後に備えることができる。本実施例では、当該結果は64ビット幅であり、8バイトを有する。2つのデータオペランド1102と1104に対する右方向シフトマージ処理により、結果はK、J、I、H、G、F、E及びDの8つのデータセグメントから構成される。10

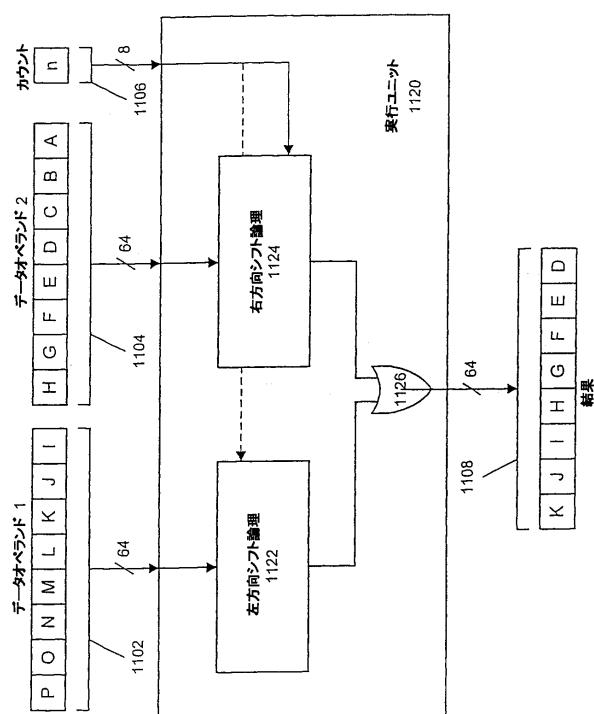

#### 【0081】

図16Bは、右方向シフトマージ処理を実行する論理の他の実施例のブロック図である。図16Aの前記実施例と同様に、本実施例の右方向シフトマージ処理は、64ビット幅の第1データオペランド1102、64ビット幅の第2データオペランド1104及び8ビット幅のシフトカウント1106の3つの情報から開始される。シフトカウント1106は、データセグメントのシフト数を示す。本実施例では、カウント1106はバイト数に関し記述される。他の実施例では、カウントはデータのシフトされるべきビット数、二進数、ワード数、ダブルワード数、あるいはクアドワード数を示してもよい。本実施例における第1及び第2オペランドはそれぞれ、8に等しい長さのバイトサイズデータセグメントからなり、第1オペランド1102は8つのデータセグメント（H、G、F、E、D、C、B、A）、第2オペランド1104は8つのデータセグメント（P、O、N、M、L、K、J、I）から構成される。カウントnは3に等しい。本発明の他の実施例は、例えば、128/256/512ビット幅のオペランド、ビット/バイト/ワード/ダブルワード/クアドワードのサイズのデータセグメント、8/16/32ビット幅のシフトカウントのような他の長さのオペランド及びデータセグメントにより動作することも可能である。従って、本発明の実施例は、特定の長さのデータオペランド、データセグメントあるいはシフトカウントに限定されず、各実施形態に適したサイズとすることができる。20

#### 【0082】

データオペランド1102と1104、及びカウント1106は、右方向シフトマージ命令と共にプロセッサ内の実行ユニット1120に送信される。本実施例では、第1データオペランド1102と第2データオペランド1104が、それぞれ左方向シフト論理1122と右方向シフト論理1124において受信される。カウント1106もまた、シフト論理1122と1124に送られる。左方向シフト論理1122は、第1オペランド1102のデータセグメントを「第1オペランドのデータセグメント数-n」個のセグメントだけ左方向にシフトする。データセグメントが左にシフトされると、空いたスペースを埋めるように左側から0がシフト入力される。この場合、8つのデータセグメントがあるので、第1オペランド1102は8-3=5だけ左にシフトされる。第1オペランド1102は、論理ORゲート1126においてマージのため正しくデータを配置するために、この異なる値だけシフトされる。ここでの左方向へのシフト後、第1データオペランドは、K、J、I、0、0、0、0となる。カウント1106がオペランドのデータセグメント数より大きい場合、左方向へのシフト計算は負の値となり、これは左方向への負のシフトを表す。負のカウントによる左方向シフト論理は、負の方向へのシフトとして解釈され、実質的に右方向へのシフト論理となる。左方向への負のシフトにより、第1オペランド1102の左側から0となる。40

#### 【0083】

同じように、右方向シフト論理1124は、第2オペランドのデータセグメントをnセグメントだけ右方向にシフトする。データセグメントが右にシフトされると、殻のスペースを埋めるために左側から0がシフト入力される。第2データオペランドは、0、0、050

、H、G、F、E、Dとなる。シフトされたオペランドは左シフト論理1122または右シフト論理1124から出力され、論理ORゲート1126においてマージされる。ORゲートは、データセグメントの論理OR処理を実行し、本実施例の64ビット幅の結果1108を与える。「K、J、I、0、0、0、0、0」と「0、0、0、H、G、F、E、D」のOR処理により、8バイトのK、J、I、H、G、F、E、Dから構成される結果1108が生成される。この結果は、図16Aにおける本発明の第1実施例のものと同じである。ここで、オペランドのデータセグメント数より大きなカウントn1106に対しては、適当な数の0が結果の左側から現れる。さらに、カウント1106が両方のオペランドのデータ要素数の合計以上である場合、当該結果はすべて0より構成される。

## 【0084】

10

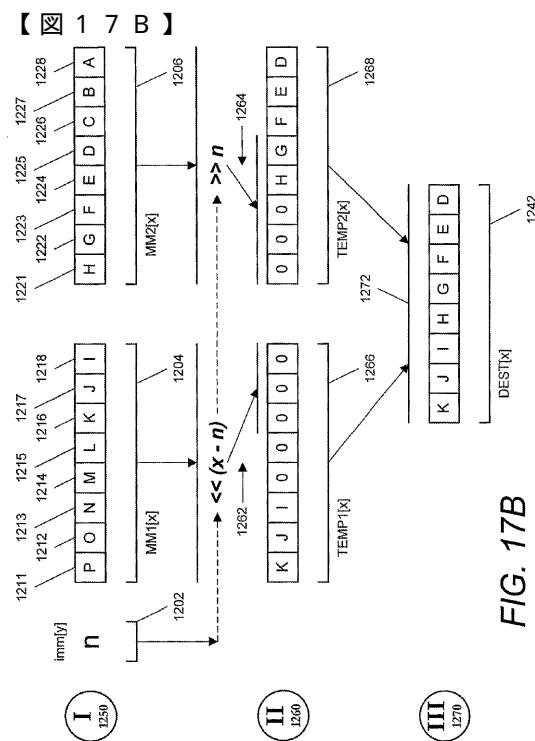

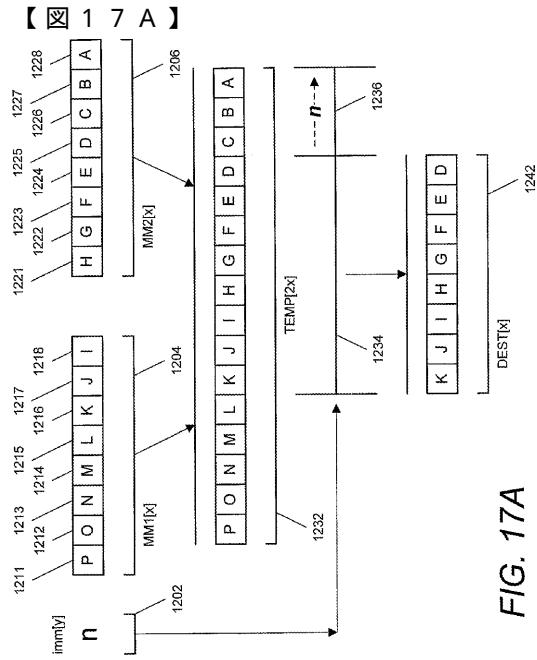

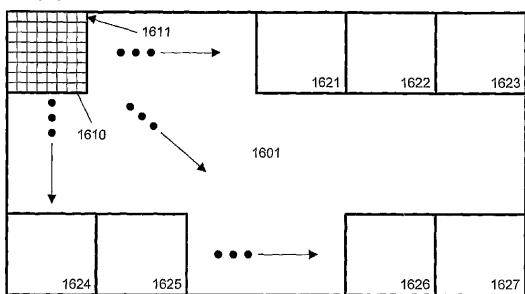

図17Aは、本発明の第1実施例による右方向平行シフトマージ命令の動作を示す。この説明において、MM11204、MM21206、TEMP1232及びDEST1242は一般に、オペランドまたはデータブロックと呼ばれるが、それに限定されるものではなく、レジスタ、レジスタファイル及びメモリ領域を含む。一実施例では、MM11204とMM21206は、64ビット幅のMMXレジスタ（あるいはいくつかの例では「mm」と呼ばれる）である。状態I1200において、シフトカウントimm[y]1202、第1オペランドMM1[x]1204及び第2オペランドMM2[x]1206が、右方向平行シフトマージ命令と共に送られる。カウント1202は、yビット幅の即値である。第1オペランド1204と第2オペランド1206はそれぞれ、各データセグメントが1バイト（8ビット）の場合、xデータセグメントを含み、8×ビットの合計幅を有するデータブロックである。第1オペランドと第2オペランドはそれぞれ、多数のより小さいデータセグメントによりパックされる。本実施例では、第1データオペランドMM11204は、P1211、O

1212、N1213、M1214、L1215、K1216、J1217、I1218の8に等しい長さのデータセグメントから構成される。同じように、第2データオペランドMM21206は、H1221、G1222、F1223、E1224、D1225、C1226、B1227、A1228の8に等しい長さのデータセグメントから構成される。従って、これらのデータセグメントのそれぞれは「x・8」ビット幅となる。これより、xが8のとき、各オペランドは8バイトあるいは64ビット幅となる。他の実施例では、データ要素は、ニブル（4ビット）、ワード（16ビット）、ダブルワード（32ビット）、クアドワード（64ビット）などであってもよい。他の実施例では、xは16、32、64のデータ要素幅であってもよい。本実施例では、カウントyは8に等しく、即値はバイトで表される。他の実施例では、yは4、16、32などのビット幅であってもよい。さらに、カウント1202は、即値に限定されず、レジスタまたはメモリ領域に格納される。

## 【0085】

20

30

オペランドMM11204とMM21206は、状態II1203においてマージされ、2×データ要素幅（あるいはこの場合にはバイト）の仮のデータブロックTEMP[2x]1232が生成される。本実施例のマージされたデータ1232は、P、O、N、M、L、K、J、I、H、G、F、E、D、C、B及びAとして配置される16のデータセグメントから構成される。8バイト幅の窓1234は、最右端から始まる仮のデータブロック1232の8つのデータセグメントから構成される。従って、窓1234の右端は、窓1234がH、G、F、E、D、C、B及びAのデータセグメントから構成されるようデータブロック1232の右端から並べられる。シフトカウントn1202は、マージされたデータを右方向にシフトする所望のシフト数を示す。このカウント値は、ビット、ニブル、バイト、ワード、ダブルワード、クアドワードなど、あるいは特定のデータセグメント数に関するシフト数を示すよう実現されてもよい。カウント値1202に基づき、データブロック1232はnデータセグメントだけ右方向へシフトされる（1236）。本実施例では、nは3に等しく、データブロックは3だけ右にシフトされる。これのもう1つの見方は、窓1234を反対方向へシフトするというものである。言い換えると、窓1

40

50

234は概念的には、仮のデータブロック1232の右端から左に3つシフトしたとみなすことができる。一実施例において、シフトカウントnが合成されたデータブロックにおいて与えられるデータセグメントの総数2xより大きい場合、結果はすべて0から構成されるであろう。同じように、シフトカウントnが第1オペランド1204におけるデータセグメント数x以上である場合、結果はその右端から1つ以上の0を含むことになる。状態III1240において、窓1234により構成されるデータセグメント「K、J、I、H、G、F、E、D」が、結果としてxデータ要素幅目的DEST[x]1242に出力される。

#### 【0086】

図17Bは、第2実施例による右方向シフトマージ命令の動作を示す。状態I1250において、右方向シフトマージ命令は、yビットのカウントimm[y]、xデータセグメントの第1データオペランドMM1[x]、及びxデータセグメントの第2データオペランドMM2[x]により伴われる。図17Aの実施例に関し、yは8に等しく、xも8に等しい。ここでMM1とMM2はそれぞれ64ビットまたは8バイト幅である。本実施例の第1及び第2オペランドはそれぞれ同じサイズのデータセグメント数によりパックされる。この場合、各オペランドは1バイト幅であり、第1オペランド1204は「P1211、O1212、N1213、M1214、L1215、K1216、J1217、I1218」、第2オペランド1206は「H1221、G1222、F1223、E1224、D1225、C1226、B1227、A1228」から構成される。

#### 【0087】

状態III1260において、第1オペランド1204と第2オペランド1206をシフトするのにシフトカウントn1202が利用される。本実施例のカウントは、マージされたデータを右にシフトするデータセグメント数を示す。本実施例では、第1オペランド1204と第2オペランド1206とのマージ処理前に、シフト処理は行われる。この結果、第1オペランド1204は異なってシフトされる。本実施例では、第1オペランド1204は(x-n)データセグメント数だけ左にシフトされる。この「x-n」の計算により、後のデータマージ処理での適切なデータ配置が可能になる。従って、カウントnが3のとき、第1オペランド1204は5データセグメントあるいは5バイトだけ左方向にシフトされる。空のスペースを埋めるために、左端から0がシフト入力される。しかしながら、シフトカウントn1202が第1オペランド1204において利用可能なデータセグメント数xより大きい場合、「x-n」の左方向シフト計算は、実質的に負の左方向へのシフトを示す負の値を生じる。一実施例では、負のカウントによる左方向への論理シフトは負の方向への左シフトとして解釈され、実質的に右方向への論理シフトとなる。負の左方向へのシフトにより、第1オペランド1204の左側から0が配置される。同じように、第2オペランド1206は、3のシフトカウントだけ右にシフトされ、空白を埋めるため左方向から0がシフト入力される。第1オペランド1204と第2オペランド1206に行われたシフト結果はそれぞれ、xデータセグメント幅のレジスタTEMP11266とTEMP21268に格納される。TEMP11266とTEMP21268からのシフト結果がマージされ(1272)、状態III1270においてレジスタDEST1242で所望のシフトマージデータが生成される。シフトカウントn1202がxより大きい場合、結果の中に左端から1つ以上の0を含む。さらに、シフトカウントn1202が2x以上である場合、DEST1242における結果はすべて0から構成されている。

#### 【0088】

上記実施例において、図17A及び図17Bに示されるように、MM1とMM2の一方または両方がMMX/SSE技術により可能なプロセッサの64ビットデータレジスタ、あるいはSSE2技術による128ビットデータレジスタであってもよい。実施形態に応じて、これらのレジスタは64/128/256ビット幅であってもよい。同じように、MM1とMM2の一方または両方がレジスタ以外のメモリ領域であってもよい。一実施例のプロセッサアーキテクチャでは、MM1とMM2は上述のような右方向シフトマージ命令(PSRMRG)に対するソースオペランドである。シフトカウントIMMはまた、こ

10

20

30

40

50

のような P S R M R G 命令の即値である。一実施例では、結果のための目的 D E S T はまた、M M X または X M M データレジスタである。さらに、D E S T はソースオペランドの 1 つと同じレジスタであってもよい。例えば、あるアーキテクチャでは、P S R M R G 命令は、第 1 ソースオペランド M M 1 と第 2 ソースオペランド M M 2 を有する。結果に対する所定の目的は、この場合 M M 1 である第 1 ソースオペランドのレジスタでありうる。

#### 【0089】

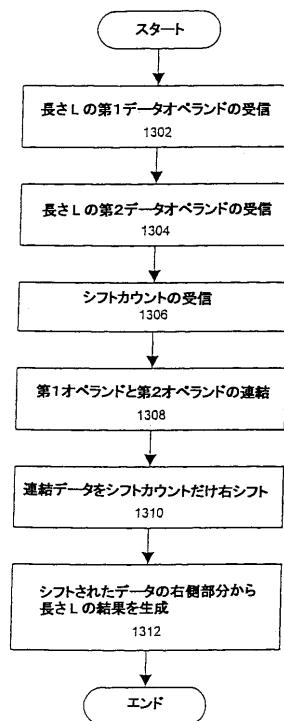

図 18 A は、データオペランドを並列に右方向シフト及びマージする方法の一実施例を示すフローチャートを示す。L の長さが一般に、オペランドとデータブロックの幅を表すのに使われる。特定の実施例に応じて、L はデータセグメント数、ビット数、倍と数、ワード数などに関して幅を表すのに使われてもよい。ブロック 1302 において、長さ L の第 1 データオペランドが、シフトマージ処理の実行において利用するため受信される。このシフトマージ処理のための長さ L の第 2 データオペランドがまたブロック 1304 において受信される。ブロック 1306 において、ビット / ニブル / バイト / ワード / ダブルワード / クアドワードでのデータセグメント数あるいは距離を示すシフトカウントが受信される。ブロック 1308 における実行論理は、第 1 オペランドと第 2 オペランドを連結する。一実施例において、長さ 2 L の仮のレジスタにおいて、連結されたデータブロックが保持される。他の実施例では、マージされたデータはメモリ領域に保持される。ブロック 1310 において、連結されたデータブロックはシフトカウントだけ右にシフトされる。このカウントがデータセグメントカウントとして表されている場合、データブロックはそのデータブロックだけ右にシフトされ、空白を埋めるためデータブロックの最上位エンド (most significant end) に沿って左から 0 がシフト入力される。例えば、このカウントがビットあるいはバイトで表されていれば、データブロックはその距離だけ同じように右方向にシフトされる。ブロック 1312 において、長さ L の結果がシフトされたデータブロックの左側あるいは最下位エンド (least significant end) から生成される。一実施例において、長さ L のデータセグメントが、シフトされたデータブロックから目的レジスタあるいはメモリ領域にマックス (max) される。

#### 【0090】

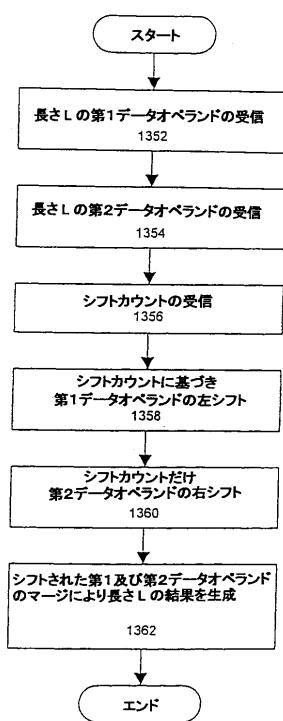

図 18 B は、データの右方向へのシフト及びマージ方法の他の実施例を示すフロー図である。ブロック 1352 において、長さ L の第 1 データオペランドが右方向シフト及びマージ処理のため受信される。長さ L の第 2 データセグメントがブロック 1354 において受信される。ブロック 1356 において、所望の右方向シフト距離を示すシフトカウントが受信される。ブロック 1358 において、シフトカウントによる計算に基づき、第 1 データオペランドが左方向にシフトされる。一実施例の計算は、シフトカウントを L から差し引くことからなる。例えば、オペランドの長さ L とシフトカウントがデータセグメントに関するものである場合、第 1 オペランドは「L - シフトカウント」セグメントだけ左にシフトされ、当該オペランドの最下位エンドから 0 がシフト入力される。同じように、L がビットにより、カウントがバイトにより表される場合、第 1 オペランドは「L - シフトカウント・8」ビットだけ左にシフトされる。ブロック 1360 において、第 2 データオペランドはシフトカウント分右にシフトされ、空白を埋めるため第 2 オペランドの最上位エンドから 0 がシフト入力される。ブロック 1362 において、シフトされた第 1 オペランドとシフトされた第 2 オペランドはマージされ、長さ L の結果が生成される。一実施例では、このマージ処理により、第 1 及び第 2 オペランドの両方からの所望のデータセグメントからなる結果が生成される。

#### 【0091】

コンピュータにおいてますますよく使われる利用方法は、サイズの大きな映像及び音声ファイルの操作に関するものである。これらの映像及び音声は典型的には広帯域幅のネットワークあるいは大容量記憶媒体を介し転送されるとしても、トラフィック処理のため依然としてデータ圧縮は必要である。この結果、様々な圧縮アルゴリズムが、多くの一般的な音声、画像及び映像フォーマットのための表現または符号化スキームの重要な部分になり

つつある。M P E G ( M o t i o n P i c t u r e E x p e r t G r o u p ) 規格の1つに従う映像は、圧縮を利用した1つの適用例である。M P E G映像は、レイヤ階層に分解され、エラー処理、ランダム探索と編集、及び同期に利用される。

#### 【 0 0 9 2 】

例示のため、1つのM P E G映像を構成するこれらのレイヤが簡潔に説明される。最上位レベルには、自己完結した ( s e l f - c o n t a i n e d ) ビットストリームを含む映像シーケンスレイヤがある。第2レイヤには、1つ以上のイントラ及び／または非イントラフレーム群からなる画像群がある。第3レイヤには画像レイヤがあり、その次のレイヤはスライスレイヤ ( s l i c e l a y e r ) である。各スライスは、以下に限定されるものではないが、最もよく利用されている典型的な映像アプリケーションでの行ベースに基づくラスター順序のマクロブロックの連続したシーケンスである。各スライスは、

10 16 × 16 の輝度画素 ( l u m i n a n c e p i x e l ) 配列と、それに対応する2つの8 × 8 の色光度画素 ( c h r o m i n a n c e p i x e l ) 配列とを有するマクロブロックまたは画像データ要素から構成される。マクロブロックは、変換符号化のようなさらなる処理のため相異なる複数の8 × 8 ブロックに分割される。マクロブロックは、動き補償及び動き予測のための基本ユニットであり、それに関連付けされた動きベクトルを有する。実施例に応じて、マクロブロックは16行16列であってもよいし、あるいは様々なサイズであってもよい。

#### 【 0 0 9 3 】

M P E G映像で使われる時間予測テクニックは動き予測に基づいている。動き予測は、連続する映像フレームは一般に、これらフレーム内で動いているオブジェクトに起因する変化以外は、同じであるという前提に基づくものである。フレーム間の動きがゼロである場合、エンコーダは現在フレームを過去あるいは予測フレームの複製として容易かつ効率的に予測することができる。前フレーム ( p r e v i o u s ) はまた、参照フレームと呼ばれる。他の実施例では、参照フレームは、当該シーケンスにおける次のフレームあるいは他のフレームであるかもしれない。動き予測の実施例は、前フレームと現在フレームを比較する必要はない。他の任意のフレームがこの比較において利用できる。エンコーダに送信される必要のある情報は、もとの参照フレームから画像を復元するのに必要な構文オーバヘッド ( s y n t a c t i c o v e r h e a d ) となる。しかしながら、画像間に動きが存在する場合、状況はより複雑である。最もよく一致するマクロブロックと現在マクロブロックとの差は、理想的には多くが0となることである。マクロブロックを符号化するとき、最もよく一致するマクロブロックと現在マクロブロックとの差が変換及び量子化される。一実施例では、量子化された値が、圧縮のため可変長符号化処理に通信される。0は良好に圧縮することができるので、差が0である値を多く有する最もよく一致するマクロブロックが望ましい。動きベクトルはまた、これらの差の値から導出することもできる。

20 30

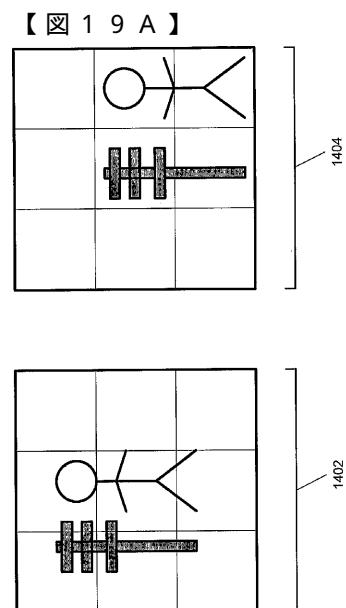

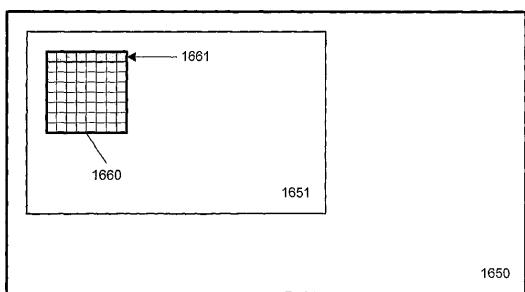

#### 【 0 0 9 4 】

図19Aは、動き予測の第1実施例を示す。左のフレーム1402は、棒線画と案内標識を含む前映像フレームのサンプルである。右のフレーム1404は、同様の棒線画と案内標識を含む現在映像フレームのサンプルである。現在フレーム1404では、パン撮りにより、案内標識が前フレーム1402のもとの位置から右下方に移動している。棒線画は現在フレームでは腕を上げ、さらに前フレーム1402の中央から右下方にシフトしている。動き予測アルゴリズムを利用することにより、これら2つの映像フレーム1402と1404との間の変化を適切に表すことができる。

40

#### 【 0 0 9 5 】

一実施例では、動き予測アルゴリズムは、各輝度マクロブロックに対して総合的な2次元 ( 2 D ) 空間探索を実行する。実施形態に応じて、動き予測はM P E G映像の色光度に直接適用されてはならない。なぜなら、色の動きは輝度と同じ動き情報により適切に表すことができるからである。多くの様々な方法が動き予測の実現に利用可能であるので、動き予測を行う方式はアプリケーションの複雑さと質の問題に依存する。一般に、広い2D

50

領域での完全かつ網羅的な探索により、最もよく一致する結果を生成することができる。しかしながら、動き予測はしばしば映像符号化において最も計算量のかかる部分であるので、このパフォーマンスは膨大な計算コストを要する。画素探索の範囲や探索タイプを制限することによるコストを減らす試みは、映像クオリティをある程度犠牲にするというものである。

#### 【0096】

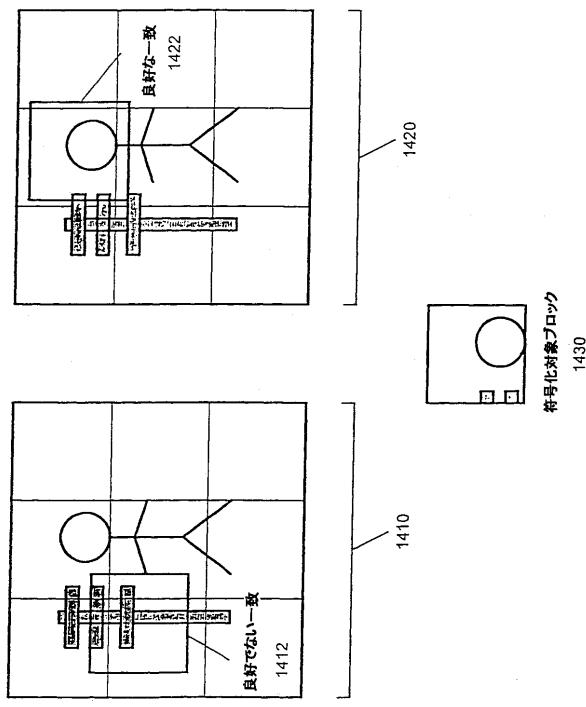

図19Bは、マクロブロック探索の一例を示す。フレーム1410と1420は、それぞれ様々なマクロブロックを備えている。現在フレームのターゲットマクロブロック1430は、前フレーム1410と1420からの前マクロブロックと一致した現在マクロブロックである。第1フレーム1410では、良好に一致しないマクロブロック1412は、案内標識部分を含み、現在マクロブロックと良好に一致していない。第2フレーム1420では、符号化対象の現在マクロブロック1430と同様に、良好に一致したマクロブロック1420は案内標識と傍線画の頭部のビットを含んでいる。これら2つのマクロブロック1422と1430は、ある程度の共通点を有しており、わずかな違いしか見出すことはできない。相対的に良好な一致が検出されているので、エンコーダは当該マクロブロックに動きベクトルを割り当てる。これらのベクトルは、一致が達成されるように、マクロブロックの水平及び垂直方向への移動量を表す。

#### 【0097】

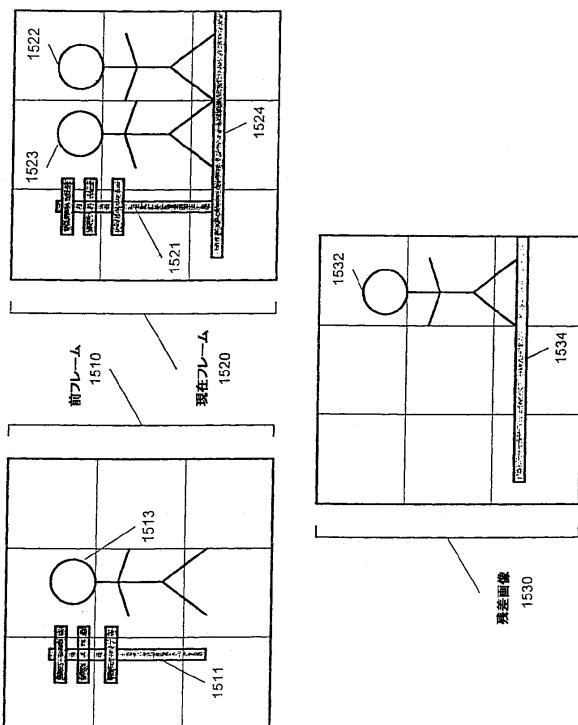

図20は、第2フレームの生成における動き予測の適用例と予測結果を示す。前フレーム1510は、時間に関し現在フレーム1520の前にくる。本実施例では、符号化及び送信対象のより複雑さを有しない残差エラー画像1530を得るために、現在フレーム1520が前フレーム1510から差し引かれる。本実施例の前フレーム1510は、案内標識1511と棒線画1513から構成される。現在フレーム1520は、ボード1524上の案内標識1511と2つの棒線画1522と1523から構成される。動きがより正確に予測及び一致すると、残差エラーはより高い確率でゼロに近づき、それにより高い符号化効率が達成される。マクロブロック予測は、探索窓サイズの減少に貢献する。

#### 【0098】

符号化効率の向上は、動きベクトルがマクロブロック間で大きな相関を有する傾向があるという事実を利用することにより達成することができる。従って、水平要素が、以前に有効な水平方向の動きベクトルと比較され、その差が符号化されてもよい。同じように、符号化前に、垂直要素の差を計算することができる。本実施例では、前フレーム1510からの現在フレーム1520を差し引くことにより、腕を上げた第2の棒線画1532とボード1534を含む残差画像1530が生成される。この残差画像1530は、圧縮そして送信される。この残差画像1530は、現在フレーム1520全体の圧縮及び送信より、符号化及びより少ないメモリの使用を可能にする複雑さが低減されたものであることが理想的である。しかしながら、必ずしもすべてのマクロブロック探索が許容できる一致を生じさせるとは限らない。エンコーダが許容可能な一致がないと判断すると、特定のマクロブロックが符号化される。

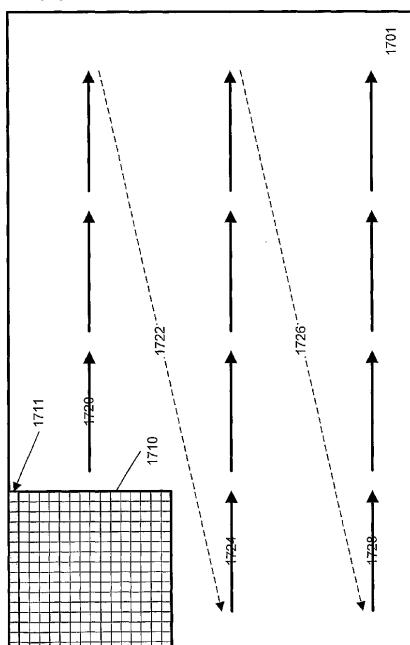

#### 【0099】

図21A及び21Bは、動き予測において処理される一例となる現在フレーム1601と前フレーム1650を示す。前フレーム1650は、映像フレーム系列に対し時間順で現在フレーム1601を移行していく。各フレームは、フレームにおいて水平及び垂直方向に延びる多数の画素から構成される。現在フレーム1601は、水平及び垂直方向に配置されている多数のマクロブロック1610、1621から1627から構成される。本実施例では、現在フレーム1601は、同じサイズの重複のないマクロブロック1610、1621から1627に分割される。これら正方形のマクロブロックのそれぞれは、さらに同数の行と列に分割される。同一のマクロブロック1610に対し、8行8列のマトリックスを見ることができる。マクロブロック1610の各正方形が1つの画素に対応している。従って、このサンプルマクロブロック1610は64画素を含んでいる。他の実施例では、マクロブロックは16行16列(16×16)のサイズであってもよい。一実

10

20

30

40

50

施例では、各画素のデータは、8データビットまたは1ワードから構成されている。他の実施例では、データ画素は、ニブル、ワード、ダブルワード、クアドワードなどを含む他のサイズから構成することができる。現在フレームのこれらの現在マクロブロックは、動き予測のため前フレーム1650のマクロブロックと一致させられる。

【0100】

本実施例では、前フレーム1650は、フレームの一部が囲まれた探索窓1651を含む。探索窓1651は、現在フレーム1601からの現在マクロブロックが一致させられる領域を有する。現在フレームと同様に、探索窓は複数のサイズの等しいマクロブロックに分割される。8行8列を有する一例となるマクロブロック1660がここでは示されているが、マクロブロックは16行16列を有する他の様々なサイズから構成することができる。一実施例の動き予測アルゴリズムにおいて、探索窓1651からの各マクロブロックは、許容できる一致を検出するため系列において、現在フレームからの現在マクロブロックと比較される。一実施例では、探索窓1651の第1前マクロブロックの左上方のコーナーが探索窓1651の左上方コーナーと並べられる。動き予測アルゴリズムにおいて、マクロブロック処理の方向は、画素単位で探索窓の左側から右端に進行する。従って、第2マクロブロックの左端は、探索窓の左端からの1画素である。第1画素行の終わりで、アルゴリズムは探索窓の左端に戻り、次の行の第1画素から進んでいく。探索窓1651の各画素のマクロブロックと現在マクロブロックとの比較が完了するまで、この処理は繰り返される。

【0101】

図22Aから22Dは、本発明の一実施例によるフレームの動き予測の動作を示す。ここで説明される本発明の実施例は、完全な探索動き予測アルゴリズムに関する。完全な探索では、前フレーム（参照フレーム）の探索窓のすべての画素位置に対するマクロブロックが、現在フレームのマクロブロックと一致するよう試みられる。一実施例では、高速完全探索動き予測アルゴリズムは、 SIMD右方向シフトマージ処理を利用して、フレームからのPackedデータの高速処理を行う。一実施例の SIMD右方向シフトマージ処理はまた、データロード数、特に並べられていないメモリロード数及び他のデータ操作命令数を減らすことによって、プロセッサのパフォーマンスを向上させることができる。一般に、一実施例の動き予測処理は以下の擬似コードで記述することができる。

【0102】

【表2】

x方向及びy方向の各現在ブロックに対し {

探索窓のy軸のすべての mod 1 位置に対し {

探索窓のx軸のすべての mod 4 位置に対し {

メモリからレジスタに画素データをロード；

隣接する4つの前マクロブロックに対しブロック一致処理を実行；

当該前マクロブロックの最小値及びインデックス位置を追跡；

} } }

ここで、ブロック一致処理では以下が行われる。

【0103】

10

20

30

40

## 【表3】

```

1 から m の各ラインに対し {

第1列から第4列で始まる各マクロブロックに対し {

レジスタに保持されるデータから当該前[ライン]の正しいデータを生成;

評価データ[ライン]+=絶対差 (現在[ライン], 前[ライン]) の合計;

}

}

```

10

従って、本実施例では、探索窓の各画素位置に対する前マクロブロックが現在マクロブロックに対し評価される。上述のように、本実施例ではループあたり4つの隣接する前マクロブロックが評価される。画素データはメモリ配置ロードにより、メモリからレジスタにロードされる。右方向シフトマージ処理の利用を通じて、この画素データは操作され、隣接するマクロブロックに適したシフトデータセグメントの様々な組み合わせが生成される。例えば、第1前マクロブロックの第1ラインにおける第1、第2、第3及び第4画素がそれぞれメモリアドレス0、1、2及び3においてスタートすることができる。第2前マクロブロックの第1ラインの第1画素に対して、当該画素はメモリアドレス1において開始される。従って、レジスタデータの右方向シフトマージ処理は、第1前マクロブロックのメモリからすでにロードされたデータを再利用することによって、第2前マクロブロックの必要な画素ラインデータを生成することができ、それによって、時間とリソースの節約が可能になる。同様のシフトマージ処理により、第3、第4、…のような他の隣接する前マクロブロックのラインデータを生成することができる。

## 【0104】

一実施例の動き予測アルゴリズムのブロック一致処理は以下の擬似コードで記述することができる。

## 【0105】

## 【表4】

```

隣接する4つの前マクロブロックのブロック一致処理 {

1 から m の各ラインに対し {

現在マクロブロックの1つのラインの画素データをロード;

探索窓の1ラインの連続する2つの画素データ群のメモリからレジスタへの並べられた

メモリロード;

右方向シフトマージ処理によるロードされたデータから隣接する4つの前マクロ

ブロックの各々に対し適切な画素データラインを生成;

隣接する4つの前マクロブロックの各々に対し前マクロブロックの1ラインと現在マクロ

ブロックの対応するライン間の絶対差の合計の計算;

隣接する4つの前マクロブロックの各々に対し4つの絶対差の合計を累積;

}

}

```

30

この処理が以下でさらに説明される。これらの実施例は探索窓の隣接する4つのマクロブロックにおける処理に関し説明されているが、本発明の他の実施例はそれに制限されるものではない。しかしながら、本発明の実施例は隣接するマクロブロックでの処理に制限されるものではない。処理に要する複数の参照マクロブロックは1画素ずつ変わる必要はない。一実施例では、特定の画素位置の周囲の $16 \times 16$ の窓の中の画素を有する任意の参照マクロブロックと一緒に処理してもよい。利用可能なデータレジスタ及び実行ユニットのようなハードウェアリソースの大きさに応じて、他の実施例はブロック一致処理やマクロ

40

50

ブロック数に関する絶対差の和の計算を実行することもできる。例えば、8データセグメント幅の2つのデータ群に対する右方向シフトマージ処理から生成される画素データの4つの異なる組み合わせを保持する少なくとも8つのPackedデータレジスタを有する他の実施例では、4つの隣接する前マクロブロックへの2つの並べられた8データセグメント幅のメモリロードによる処理を行うことが可能である。8つのPackedデータレジスタのうちの4つが、前フレームからの最初の8データセグメント、前フレームの次の8データセグメント、現在フレームのための8データセグメント、及び右方向シフトマージよりからの8データセグメントを保持する計算オーバヘッドに利用される。その他の4つのPackedデータレジスタは、4つのマクロブロックのそれぞれに対し、絶対差の和(SAD)の合計を累積するのに利用される。より多くのPackedデータレジスタが、共に処理される参照マクロブロックの数を増やすために、SAD計算と累積計算のために加えられてもよい。従って、4つの追加的Packedデータレジスタが利用可能である場合、4つの追加的な前マクロブロックもまた処理可能となる。一実施例の累積された絶対差の和を保持するのに利用可能なPackedデータレジスタ数は、一度に処理可能なマクロブロック数を制限するかもしれない。

#### 【0106】

さらに、いくつかのプロセッサーキテクチャでは、メモリアクセスは特定の粒度を有し、ある境界で並べられる。例えば、あるプロセッサは16または32バイトブロックに基づきメモリにアクセスすることができる。この場合、16または32バイトの境界で揃えられていないデータへのアクセスには、揃えられていないメモリアクセスを必要とし、実行時間とリソースにおいてコストがかかってしまう。さらに悪いことに、所望のデータ部分が境界をまたぎ、複数のメモリブロックを重複させてしまうかもしれない。異なる2つのキャッシュラインにあるデータにアクセスするために、揃えられていないロードをするキャッシュライン分割はコストがかかってしまう。メモリページの境界をまたぐデータラインはさらに悪い。例えば、8バイトメモリブロック及び画素あたり1バイトのデータを有する8画素にわたるマクロブロックにより動作するプロセッサでは、1つの揃えられたメモリロードで当該マクロブロックラインにとて十分であろう。次の隣接マクロブロックがなければ、その画素ラインに必要なデータの1画素列は、第1マクロブロックからの、しかしながら、次のメモリブロックの1データバイトのメモリ境界を越してメモリブロックの7データバイトにわたるであろう。本発明の実施例は、右方向シフトマージ処理を使って、効率的にデータを処理する。一実施例では、2つの連続したメモリブロックが揃えられたメモリ境界に置かれ、いくつかの利用のためにレジスタに保持される。右方向シフトマージ処理は、これらのメモリブロックを取得し、そのなかのデータセグメントを正しいデータラインを得るのに必要な距離だけシフトする。本実施例によると、右方向シフトマージよりは、ロード済みの2つのメモリブロックを取得し、第2ブロックから1データバイトをシフトし、第1ブロックから第2ブロックへ1データバイトをシフトし、並べられていないロードを実行する必要なく第2マクロブロックの第1ラインのデータを生成する。動き予測の実施例はまた、アルゴリズムの実現方法に基づき従属関係の連鎖を断ち切ることもできる。例えば、計算順序を変えることによって、データ/命令の依存関係が、図15のプロセッサ1000と同じように、ある計算及び命令を順序に従わずに削除あるいはシフトすることが可能である。実行待ち時間と利用可能な計算リソースの増加によって、より新しい世代のプロセッサーキテクチャによるパフォーマンスの向上がより大きくなる。右方向シフトマージ処理の一実施例を使うことによって、ブロック一致シーケンスにおけるある依存関係が回避することができる。例えば、複数の絶対差の和の演算及び/あるいは累積演算は並列に実行することができる。

#### 【0107】

図22Aは、現在フレーム1701における現在マクロブロックの経過を示す。本実施例では、各現在マクロブロック1710は16行16列に分割され、それによって、256の画素から構成されるようになる。本実施例では、各マクロブロック1710の画素は一度に各列1711処理される。現在ブロックの16行すべてが探索窓の所望のマクロブ

10

20

30

40

50

ロックに対し処理されると、次の現在マクロブロックが処理される。本実施例のマクロブロックは、マクロブロックサイズ毎に現在フレーム 1701 の左側から右側に水平方向 1720 で処理される。言い換えると、本実施例において現在マクロブロックは重複することなく、現在マクロブロックは各マクロブロックが次のマクロブロックと隣接するよう配置される。例えば、第 1 マクロブロックは第 1 画素列から第 16 画素列に拡張可能である。第 2 マクロブロックは第 17 列から第 32 列に、以下同様にして、拡張することができる。マクロブロック行の終わりで、処理は左端に戻り (1722)、本実施例では 16 行である 1 マクロブロックの高さだけ下に降りる。フレーム 17011 の全体に対し一致処理が完了されるまで、マクロブロックサイズ毎にマクロブロックは水平方向に左から右へ処理されていく (1724)。

10

#### 【0108】

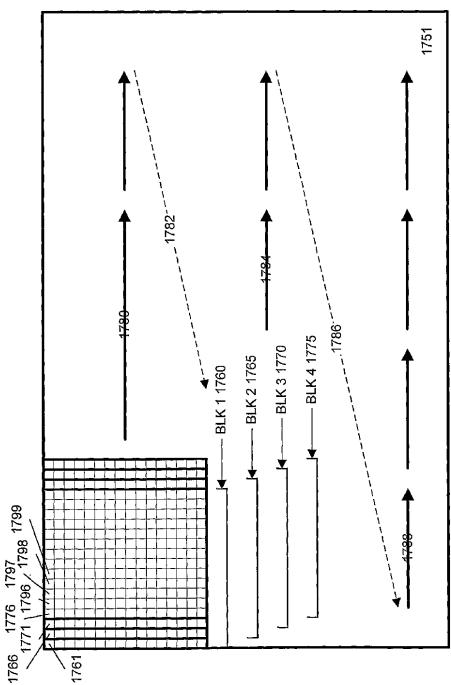

図 22B は、前 (参照) フレームの探索窓 1751 におけるマクロブロックの経過を示す。特定の実施形態に応じて、探索窓 1751 はある領域に焦点が当てられ、前フレーム全体よりも小さくされる。他の実施例では、探索窓は前フレームに完全に重複してもよい。現在フレームと同じように、各前マクロブロック 1760、1765、1770 及び 1775 は、それぞれが合計で 256 画素の 16 行 16 列に分割される。本実施例では、探索窓 1751 の 4 つの前マクロブロック 1760、1765、1770 及び 1775 が、一致探索での 1 つの現在ブロックに対して並列に処理される。現在フレームの現在マクロブロックと異なり、探索窓 1751 の前マクロブロック 1760、1765、1770 及び 1775 は本実施例と同じように重複しうる。ここで、各前マクロブロックは 1 画素列だけシフトされる。従って、BLK1 の第 1 行の最左画素は画素 1761 であり、BLK2 では画素 1766、BLK3 では画素 1771、BLK4 では画素 1776 である。動き予測アルゴリズムでは、前マクロブロック 1760、1765、1770 及び 1775 の各行は現在ブロックの対応する行に対して比較される。例えば、BLK1 1760、BLK2 1765、BLK3 1770 及び BLK4 1775 の第 1 行はそれぞれ現在ブロックの第 1 行と共に処理される。

20

#### 【0109】

マクロブロックの 16 行すべてに対し実行されるまで、4 つの重複した隣接するマクロブロックに対する行単位での比較が続けられる。本実施例のアルゴリズムは、次の 4 つのマクロブロックでの処理のため、4 画素列だけシフトする。従って、例えば、次の 4 つのマクロブロックの最左第 1 画素列は、それぞれ画素 1796、1797、1798 及び 1799 となる。本実施例では、探索窓が完了するまで、前マクロブロック処理は探索窓 1751 において右方向 1780 へ続けられ、探索窓 1751 の最左画素において 1 画素列下に降りて再開される。本実施例の現在フレームの現在マクロブロックは重複せず、次のマクロブロックはマクロブロックの高さあるいは幅であるが、前フレームまたは参照フレームの前マクロブロックは重複し、次のマクロブロックは 1 画素行あるいは 1 画素列だけインクリメントされる。本実施例の 4 つの基準マクロブロック 1760、1765、1770 及び 1775 は隣接し、1 画素列だけ異なっているが、選択された画素位置の周囲の特定領域を重複している探索窓 1751 の任意のマクロブロックを当該画素位置のマクロブロックとともに処理することができる。例えば、画素 1796 のマクロブロック 1760 が処理される。画素 1796 の周囲の  $16 \times 16$  の窓の中の任意のマクロブロックを、マクロブロック 1760 と共に扱うことができる。本実施例の  $16 \times 16$  の窓は、マクロブロックのサイズと行のライン長による。この場合、1 つの行またはデータラインは、16 のデータ要素を有する。動き予測アルゴリズムの本実施例のこのブロック一致機能により、16 のデータ要素の 2 つのデータラインがロードされ、右方向シフトマージ処理の実行により 2 つのデータラインのシフト / マージされたものを有する様々なデータラインが生成されるので、このマクロブロックに対しデータがロードされる  $16 \times 16$  の窓を重複する他のマクロブロックがこのロードされたデータを少なくとも部分的に再利用することができる。従って、マクロブロック 1765、1770 及び 1775 のような、マクロブロック 1760 を重複する任意のマクロブロック、あるいはマクロブロック 1760 の右

30

40

50

下端画素位置で始まるマクロブロックを、マクロブロック 1760 と共に処理することができる。重複の大きさの差は、前のデータロードから再利用することができるデータ量に影響を与える。

【0110】

本発明による動き予測の実施例によると、マクロブロック解析は、2つのマクロブロック間の絶対差の和を得るために、行単位により前(参照)マクロブロックと現在マクロブロックとの比較からなる。この絶対差の和は、これらのマクロブロックがどれくらい異なっているか、そしてどれくらい近い一致が存在するかについて示している。一実施例の各前マクロブロックは、当該マクロブロックの16行すべての絶対差の和を累積することにより得られる値により表すことができる。解析中の現在マクロブロックに対し、最も近く一致するマクロブロックの記号が維持される。例えば、絶対差の最小累積和と、対応する前マクロブロックの位置インデックスが追跡される。動き予測が探索窓において進むとき、各前マクロブロックの累積和とこの最小値が比較される。より新しい前マクロブロックが追跡されている最小値のものより小さい累積差を有し、すなわち、これまでに最も近い一致よりもさらに近い一致を示すものがある場合、この新しい前マクロブロックの累積差とインデックス上方が、新しい最小差とインデックスになる。探索窓のすべての画素に対する利用可能なマクロブロックが一実施例において処理されるとき、最小差を有するこのインデックスのマクロブロックが、当該現在フレームの圧縮のため残差画像を取得するのに利用される。

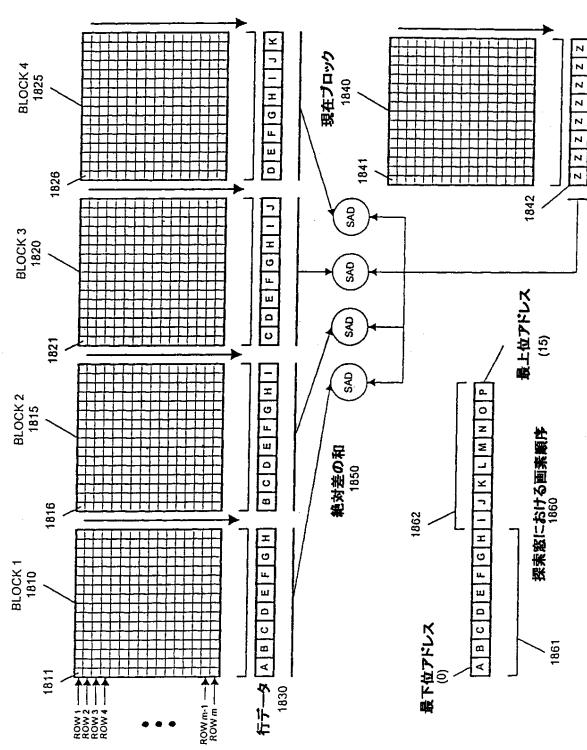

【0111】

図22Cは、本発明の一実施例による現在ブロック1840による所与の探索窓の4つの参照マクロブロック1810、1815、1820及び1825の並列処理を示す。本実施例では、探索窓の画素データが「A、B、C、D、E、F、G、H、I、J、K、L、M、N、O、P」1860として順序付けされている。ここで、「A」はデータセットにおける最下位アドレス位置(0)であり、「P」は最上位アドレス(15)である。この画素セット1860は、各自が8(m)データセグメントを有する2つのせく著ン1681と1682から構成される。右方向シフトマージ処理により、上述のように、本発明の実施例はこれら2つのデータセクション1618と1682によりオペランドを操作し、異なる前マクロブロック1810、1815、1820及び1825に対し適切に並べられた行データ1830を生成することができる。前マクロブロック1810、1815、1820及び1825と現在マクロブロック1840の各マクロブロックは、m行m列のサイズを有する。説明及び簡単化のため、本実施例においてmは8に等しい。他の実施例は、異なるサイズのマクロブロックを有することができ、例えば、mは4、16、32、64、128、256などであってもよい。

【0112】

本実施例では、動き予測アルゴリズムが、これら4つの前ブロック1810、1815、1820及び1825の第1行に、現在ブロックの第1行と共に適用される。一実施例では、2つのマクロブロック幅(2m)に対し2つのデータセクション1861と1862を含む画素データが、2つの配置メモリロード命令によりメモリからロードされ、仮レジスタに保持される。この2つのデータセクション1861と1862への右方向シフトマージ処理により、メモリアクセスを多用することなく、行データ1830の可能な9つの組み合わせを生成することができる。さらに、実行時間とリソースを多用する非配置メモリロードを回避することができる。本実施例では、2つのデータセクション1861と1862がバイト境界で並べられる。例えば、データセグメントBまたはDのようなバイト境界でのアドレスから始まらないメモリロードは、典型的には、非配置メモリロード処理を要するであろう。各ブロックの行データ1830は以下のようになる。ここで最左データセグメントが最下位アドレスである。BLOCK11810において、ROW11811は、「A、B、C、D、E、F、G、H」から構成される。ROW11811のデータが第1データセクション1861と同じであるとき、シフト処理は必要ない。しかし、BLOCK21815のROW11816は、「B、C、D、E、F、G、H、I」

10

20

30

40

50

から構成されている。前 B L O C K 1

1 8 1 0 と B L O C K 2 1 8 1 5 が水平方向に 1 画素だけずれているので、 B L O C K 2 1 8 1 5 は画素データ B から始まるが、 B L O C K 1 1 8 1 0 は画素データ A から始まり、第 2 画素データは B である。従って、1 のシフトカウントにより、2 つのデータセクション 1 8 6 1 と 1 8 6 2 の右方向シフトマージ処理により、 B L O C K 2 R O W 1 データが生成される。

【 0 1 1 3 】

同様にして、 B L O C K 3 1 8 2 0 は、右方向へさらに 1 画素シフトしており、 B L O C K 3 1 8 2 0 の R O W 1 1 8 2 1 は、画素データ C から始まり、「 C 、 D 、 E 、 F 、 G 、 H 、 I 、 J 」から構成される。2 のシフトカウントによる 2 つのデータセクション 1 8 6 1 と 1 8 6 2 のオペランドに対する右方向シフトマージ処理により、 B L O C K 3 R O W 1 データが生成される。 B L O C K 4 1 8 2 5 の R O W 1 1 8 2 6 は、「 D 、 E 、 F 、 G 、 H 、 I 、 J 、 K 」から構成される。このデータは、同じデータオペランドに対する 4 のシフトカウントによる右方向シフトマージ処理により生成される。一時的にセーブされ、前にロードされたデータセクション 1 8 6 1 と 1 8 6 2 に対する右方向シフトマージ処理により、他の隣接するマクロブロックの行データの生成におけるデータの再利用と、メモリロード数、特に非配置メモリロード数を減らすことによる時間 / リソースの節約が可能になる。ここで、現在ブロックの画素データは、前フレームの参照マクロブロックに対する絶対差の和のすべての比較において同じである。1 つの配置メモリロードは、現在ブロック 1 8 4 0 がメモリ境界で並んでいるとき、現在ブロック 1 8 4 0 の行データ 1 8 4 2 に対し可能であるかもしれない。

【 0 1 1 4 】

動き予測の一実施例のこの例に関して、絶対差の和を得るために、前マクロブロック 1 8 1 0 、 1 8 1 5 、 1 8 2 0 及び 1 8 2 5 の各行が現在ブロック 1 8 4 0 の対応する行と比較される。従って、 B L O C K 1 1 8 1 0 の R O W 1 1 8 1 1 が、絶対差の和 ( S A D ) を求める処理 1 8 5 0 において、現在ブロック 1 8 4 0 の R O W 1 1 8 4 1 と比較される。ここで処理されている他の 3 つのブロックに関しても同様の処理が行われる。これら 4 つのマクロブロック 1 8 1 0 、 1 8 1 5 、 1 8 2 0 及び 1 8 2 5 は同時あるいは並列に処理されているようであるが、本発明の他の実施例はこれに限定されない。従って、この 4 つのマクロブロックの処理は逐次的に 4 つのシーケンスとして実行することができる。例えば、各参照ブロックの第 1 行は、 B L O C K 1 1 8 1 0 、 B L O C K 2 1 8 1 5 、 B L O C K 3 1 8 2 0 及び B L O C K 4 1 8 2 5 の順で、現在ブロック 1 8 4 0 と共に S A D 処理 1 8 5 0 が実行される。その後、各参照ブロックの第 2 行に対し、そして以下同様に、 S A D 処理 1 8 5 0 が実行される。各 S A D 処理 1 8 5 0 の実行後、絶対差の和の現在トータルが仮レジスタに蓄積される。従って、本実施例では、4 つのレジスタが、当該マクロブロックのすべての m 行が処理されるまで、絶対差の和を蓄積していく。マクロブロックの最良一致探索の一部として、各ブロックに対して蓄積された値がこれまでの最小差と比較される。本実施例は 4 つの隣接しかつ重複した前マクロブロックの処理を説明しているが、探索窓の第 1 ブロック B L K 1 8 1 0 に重複している他のマクロブロックもまた、データラインに関連がある場合、 B L K 1 8 1 0 のデータラインと共に処理することができる。従って、処理中のマクロブロックの周囲の 1 6 × 1 6 の窓の中のマクロブロックもまた処理することができる。

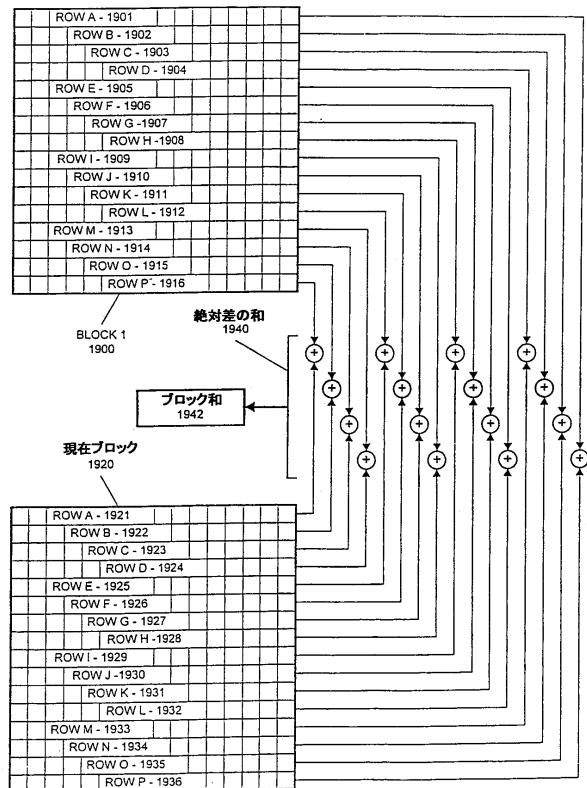

【 0 1 1 5 】

図 2 2 D は、絶対差の和 ( S A D ) の計算処理 1 9 4 0 とこれら S A D 値の合計処理を示す。ここで、参照マクロブロック B L O C K 1 1 9 0 0 の R O W A から R O W P の各行と、現在マクロブロック 1 9 2 0 におけるそれに対応するものとが、 S A D 処理 1 9 4 0 を実行される。 S A D 処理 1 9 4 0 では、各行の画素を表すデータが比較され、前マクロブロック 1 9 0 0 と現在マクロブロック 1 9 2 0 からの 2 つの行の間の絶対差を表す値が計算される。 A から P のすべての行に対して、 S A D 処理 1 9 4 0 による値がブロック和 1 9 4 2 として合計される。このブロック和 1 9 4 2 は、前マクロブロック 1 9 0 0 50

と現在マクロブロック 1920 全体に対する絶対差の和の蓄積された値を提供する。このブロック和 1942 に基づき、動き予測アルゴリズムは、前マクロブロック 1900 が現在マクロブロック 1920 に関してどのくらい近い一致であるか決定することができる。

#### 【0116】

本実施例は一度に 4 つの参照マクロブロックに対して動作するが、他の実施例はロードされる画素データ量及び利用可能なレジスタ数に応じて、異なる数のマクロブロックに対して動作することができる。さらに、動き予測処理では、様々なレジスタを利用することができる。例えば、MMX 技術による mm レジスタや SSE2 技術による XMM レジスタのような拡張レジスタを利用して、画素データのような Packed データを保持することができる。一実施例では、64 ビット幅の MMX レジスタは 8 バイトを保持することができ、またもし各画素が 8 ビットデータを有していれば、8 画素を保持することができる。他の実施例では、128 ビット幅の XMM レジスタは、16 バイト、もし各画素が 8 ビットデータであれば、16 画素を保持することができる。同じように、Packed データを保持する 32 / 128 / 256 / 512 ビット幅のような他のサイズのレジスタもまた、本発明の実施例と共に利用可能である。他方、通常の整数演算のような Packed データレジスタを必要としない計算は、整数レジスタや整数ハードウェアを利用することができます。

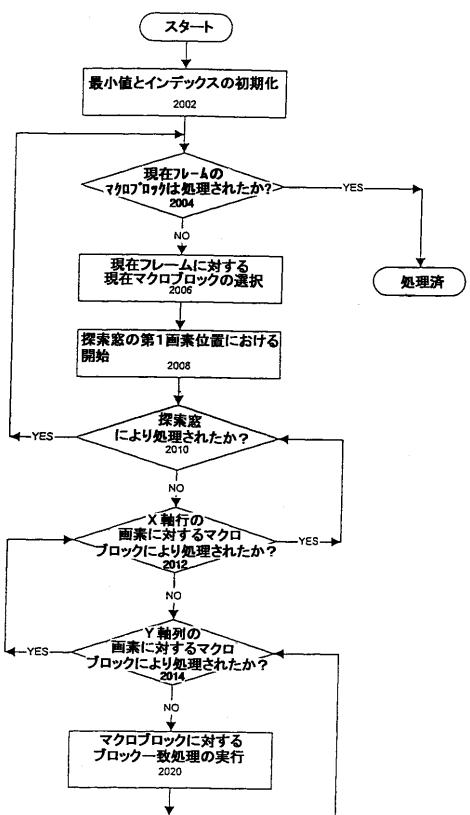

#### 【0117】

図 23A は、動きを予測する方法の一実施例を示すフローチャートである。ブロック 2002 において、追跡される最小値 (min) と、この最小値に対するインデックス位置が初期化される。本実施例では、この追跡されている min 値とインデックスは、探索窓からの処理された前 (参照) マクロブロックのどれが現在マクロブロックに最も近く一致しているか示す。ブロック 2004 において、現在フレームのすべての所望のマクロブロックが完了されたかチェックされる。もし完了されていれば、動き予測アルゴリズムのこの部分が実行される。もしすべての所望の現在マクロブロックが処理されていなければ、ブロック 2006 において未処理の現在マクロブロックが現在フレームに対し選択される。ブロック 2008 において、ブロック一致処理が前 (参照) フレームの探索窓における第 1 画素位置から進む。ブロック 2010 において、探索窓が完了されたかチェックされる。第 1 のパスでは、探索窓の何れもが処理されていない。しかしこのパスで、探索窓の全体が処理されていれば、フローはブロック 2004 に戻り、他の現在マクロブロックが利用可能であるか判断される。

#### 【0118】

探索窓の全体が解析されていなければ、ブロック 2012 において、この X 軸行に沿ったすべての画素が処理されているかチェックされる。当該行が処理されていれば、行カウントは次の行にインクリメントされ、フローはブロック 2010 に戻り、この新たな行においてより多くのマクロブロックが探索窓において利用可能であるかチェックされる。しかしこの行の画素のすべての利用可能なマクロブロックが処理されていなければ、ブロック 2014 において、この画素列と行におけるマクロブロックが処理されているかチェックされる。もし当該マクロブロックが処理されていれば、列カウントがインクリメントされ、フローはブロック 2012 に戻り、この新しい列における画素のマクロブロックが処理されているかどうかチェックされる。一方、もしこの列及び行の画素のマクロブロックが処理されていなければ、ブロック一致処理がこの参照マクロブロックと現在マクロブロックとの間で実行される。

#### 【0119】

本実施例におけるフローは、簡単化のため一度に 1 画素だけ X と Y 軸に沿って画素の行及び列位置をインクリメントする処理を述べている。しかしながら、本発明の一実施例では、パスあたり 4 つの前マクロブロックが処理される。従って、Y 軸に沿った列カウントはパスあたり 4 列分インクリメントされる。他の実施例はまた、一度に 8、16、32 などのマクロブロックを処理してもよく、これにより列カウントは、アルゴリズムの後続のパスに対し正しい画素位置を指すよう 8、16、32 などの列だけ対応してインクリメン

10

20

30

40

50

トされる。本実施例のブロック一致処理は順序付けされた形式で X 及び Y 軸に沿って探索が実行されるが、他の実施例のブロック一致処理は、異なるパターンを使うダイアモンド探索やログ探索のような他のアルゴリズムを利用することもできる。

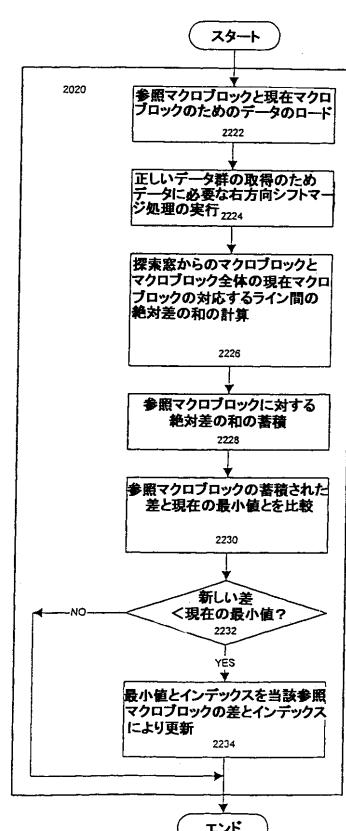

#### 【 0 1 2 0 】

図 23B は、図 23A のブロック一致処理をさらに説明するフローチャートである。ブロック 2222 において、参照マクロブロックと現在マクロブロックのデータがロードされる。一実施例では、2 つの Pack ed データ群が多数の連続する画素のデータを含むとき、参照マクロブロックデータがロードされる。一実施例では、各 Pack ed データ群は 8 つのデータセグメントから構成される。ブロック 2224 において、正確なデータ群を取得するために、右方向シフトマージ処理はデータ群に対し必要なものとして実行される。4 つの前マクロブロックが一緒に処理された前述の実施例では、右方向シフトマージ処理は各マクロブロックにあるラインに対応するデータ群を生成することができる。各隣接マクロブロックに対するデータ群が 1 画素だけシフトされ、マクロブロックは探索窓の各画素行に対し同時に 1 画素だけスライドしているように見える。ブロック 2226、2228、2230 及び 2232 における処理が一緒に処理される 4 つの前マクロブロックのそれぞれに対し適用される。一実施例において、次の処理が実行される前に、4 つのすべてのマクロブロックに対し同様の処理が行われる。他の実施例では、1 つの前マクロブロックは、適切にシフトされたデータセグメントを含むデータ群を有する次の前マクロブロックが処理される前に、すべての処理を完了させるようにしてよい。

#### 【 0 1 2 1 】

ブロック 2226 において、前マクロブロックと現在マクロブロックの対応するライン間の絶対差の和が、これらマクロブロックの各行に対し計算される。ブロック 2228 において、前マクロブロックのすべてのラインに対する絶対差の和が蓄積される。ブロック 2230 において、当該前マクロブロックに対し蓄積された差は現在の最小値と比較される。ブロック 2232 においてこの前マクロブロックの差が現在最小値より小さい場合、最小値はこの新しい差により更新される。インデックスもまた、このマクロブロックがこれまでで最も近い一致であるということを示すために、当該マクロブロックの位置を反映するよう更新される。しかし、ブロック 2232 においてこの新しい差が現在の最小値より大きい場合、当が前マクロブロックはこれまで一致してきたものより近い一致ではない。

#### 【 0 1 2 2 】

本発明による動き予測アルゴリズムの実施例はまた、現在のハードウェアリソースによるプロセッサ及びシステムのパフォーマンスの向上を可能にする。しかしながら、技術の進歩に従って、より多くのハードウェアリソースやより高速でより効率的な論理回路と組み合わされるとき、本発明の実施例はパフォーマンスの向上にさらなる著しい影響を与える。従って、動き予測の効率的な一実施例はプロセッサの生成に異なるより大きな影響をもたらしうる。最新のプロセッサーアーキテクチャにより多くのリソースを単に付加するだけでは、よりよいパフォーマンスの向上は保証されない。動き予測と右方向シフトマージ命令 (PSRMRG) の一実施例と同様にアプリケーションの効率を維持することにより、より大きなパフォーマンスの向上が可能になる。

#### 【 0 1 2 3 】

議論の簡単化のため、上記実施例は一般的に 64 ビット幅ハードウェア / レジスタ / オペランドに関し説明されているが、他の実施例では 128 ビット幅ハードウェア / レジスタ / オペランドを利用して、レジスタマージ処理、右方向シフトマージ処理、及び動き予測計算が実行される。さらに、本発明の実施例は MMX / SSE / SSE2 技術のような特定のハードウェアあるいは技術タイプに制限されるものではなく、他の SIMD 実施形態及び他のグラフィカルなデータ操作技術と共に利用することもできる。図 20 から 23B に関し説明された動き予測及びブロック一致の実施例は、8 画素幅または 8 データ要素幅のライン / 行、及び 8 行 8 列のマクロブロックに関して説明されているが、他の実施例は他のサイズを含んでいる。例えば、ライン / 行は 16 画素幅または 16 データ要素幅で

10

20

30

40

50

ありうるし、マクロブロックは 16 行 16 列でありうる。

【0124】

上記明細書では、本発明は特定の実施例を参照することにより説明されてきた。しかしながら、添付されたクレームに与えられるように、発明のより広範な趣旨及び範囲から逸脱することなく様々な修正及び変更が可能であるということは明らかであろう。従って、明細書及び図面は限定的な意味よりも例示的な意味でみなされるべきである。

【図面の簡単な説明】

【0125】

【図 1】図 1 は、本発明の一実施例を実現することができるコンピュータシステムを示すブロック図を示す。

10

【図 2】図 2 は、本発明のさらなる一実施例による図 1 に示されるようなプロセッサの一実施例を示すブロック図を示す。

【図 3】図 3 は、本発明のさらなる一実施例による Packed データタイプを示すブロック図を示す。

【図 4 A】図 4 A は、本発明の一実施例によるイン・レジスタ Packed バイト表現を示す。

【図 4 B】図 4 B は、本発明の一実施例によるイン・レジスタ Packed ワード表現を示す。

【図 4 C】図 4 C は、本発明の一実施例によるイン・レジスタ Packed ダブルワード表現を示す。

20

【図 5】図 5 は、本発明の一実施例によるバイトシャッフル命令の動作を示すブロック図を示す。

【図 6】図 6 は、本発明の一実施例によるバイト乗加算命令を示すブロック図を示す。

【図 7 A】図 7 A は、本発明のさらなる一実施例による複数の積和ペアを生成する図 6 に示されるようなバイト乗加算命令と合成された図 5 のバイトシャッフル命令を示すブロック図を示す。

【図 7 B】図 7 B は、本発明のさらなる一実施例による複数の積和ペアを生成する図 6 に示されるようなバイト乗加算命令と合成された図 5 のバイトシャッフル命令を示すブロック図を示す。

【図 7 C】図 7 C は、本発明のさらなる一実施例による複数の積和ペアを生成する図 6 に示されるようなバイト乗加算命令と合成された図 5 のバイトシャッフル命令を示すブロック図を示す。

30

【図 8 A】図 8 A は、本発明のさらなる一実施例による隣接加算命令を示すブロック図を示す。

【図 8 B】図 8 B は、本発明のさらなる一実施例による隣接加算命令を示すブロック図を示す。

【図 8 C】図 8 C は、本発明のさらなる一実施例による隣接加算命令を示すブロック図を示す。

【図 8 D】図 8 D は、本発明のさらなる一実施例による隣接加算命令を示すブロック図を示す。

40

【図 9 A】図 9 A は、本発明のさらなる一実施例によるレジスタマージ命令を示す。

【図 9 B】図 9 B は、本発明のさらなる一実施例によるレジスタマージ命令を示す。

【図 10】図 10 は、本発明の一実施例によるコンテンツデータの効率的なデータ処理のためのフローチャートを示すブロック図を示す。

【図 11】図 11 は、本発明のさらなる一実施例によるデータ処理によるコンテンツデータを処理するための追加的方法を示すブロック図を示す。

【図 12】図 12 は、本発明のさらなる一実施例によるコンテンツデータの継続処理のためのフローチャートを示すブロック図を示す。

【図 13】図 13 は、本発明のさらなる一実施例によるレジスタマージ処理を示すフローチャートを示すブロック図を示す。

50

【図14】図14は、本発明の一実施例によるソースデータ記憶装置からの未処理データ要素を選択するための追加的方法を示すフローチャートを示す。

【図15】図15は、本発明による右方向シフトマージ処理を実行する論理回路を含む一実施例のプロセッサのためのマイクロアーキテクチャのブロック図である。

【図16A】図16Aは、本発明によるデータオペランドに対する右方向平行シフトマージ処理を実行する論理の一実施例のブロック図である。

【図16B】図16Bは、右方向シフトマージ処理を実行する論理の他の実施例のブロック図である。

【図17A】図17Aは、本発明の第1実施例による右方向平行シフトマージ命令の動作を示す。

10

【図17B】図17Bは、第2実施例による右方向シフトマージ命令の動作を示す。

【図18A】図18Aは、データオペランドを並列に右方向にシフトしマージする方法の一実施例を示すフローチャートである。

【図18B】図18Bは、データを右方向にシフトしマージする方法の他の実施例を示すフローチャートである。

【図19A】図19Aは、動き予測の一例を示す。

【図19B】図19Bは、動き予測の一例を示す。

【図20】図20は、動き予測の適用例と予測結果を示す。

【図21A】図21Aは、動き予測において処理される一例となる現在及び前フレームを示す。

20

【図21B】図21Bは、動き予測において処理される一例となる現在及び前フレームを示す。

【図22A】図22Aは、本発明の一実施例によるフレームに対する動き予測の動作を示す。

【図22B】図22Bは、本発明の一実施例によるフレームに対する動き予測の動作を示す。

【図22C】図22Cは、本発明の一実施例によるフレームに対する動き予測の動作を示す。

【図22D】図22Dは、本発明の一実施例によるフレームに対する動き予測の動作を示す。

30

【図23A】図23Aは、動き予測方法の一実施例を示すフローチャートである。

【図23B】図23Bは、動き予測方法の一実施例を示すフローチャートである。

【図1】

【図2】

【図3】

【図4 A】

【図 4 B】

【図 4 C】

【図 9 A】

【図 9 B】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16A】

【図16B】

【図 18 A】

【図 18 B】

【図 19 B】

【図 20】

【図22C】

【図22D】

【図23A】

【図23B】

FIG. 5

FIG. 1A

6

EIG 7B

FIG. 7C

554

PAUDNNWD: N-4

A1B1+A2B2+A3B3+A4B4+A5B5+A6B6+A7B7+A8B8 [A9B9+A10B10+A11B11+A12B12+A13B13+A14B14+A15B15+A16B16]

FIG 8B

FIG 8A

FIG. 8C

552

PANDONNET, N.-Z

[A1B1-A1B2-A1B3-A1B4-A1B5-A1B6-A1B7-A1B8-A1B9-A1B10-A1B11-A1B12 A1B13-A1B14-A1B15-A1B16]

FIG. 8D

FIG. 17B

FIG. 17A

FIG. 19A

【図 2 1 A】

FIG. 21A

【図 2 1 B】

FIG. 21B

【図 2 2 A】

FIG. 22A

【図 2 2 B】

FIG. 22B

---

フロントページの続き

(72)発明者 セボット, ジュリエン

アメリカ合衆国 97124 オレゴン州 ヒルズボロ ノースウェスト 188ス ストリート

2323 アパートメント 1322

(72)発明者 メイシー, ウィリアム, ジュニア

アメリカ合衆国 94301 カリフォルニア州 パロアルト メルヴィル アヴェニュー 15

1

(72)発明者 デベス, エリック

アメリカ合衆国 95054 カリフォルニア州 サンタクララ レキシントン ストリート 1

365

(72)発明者 ギュエン, ヒュイ

アメリカ合衆国 78660 テキサス州 フルジャーヴィル アイル オブ マン ロード 1

6909

審査官 緑川 隆

(56)参考文献 Peleg, A. Weiser, U., MMX technology extension to the Intel architecture, IEEE Micro

米国, IEEE, 1996年 8月, Volume: 16, Issue: 4, p.42-50

松原 敦, Pentium IIIの新命令を検証, 第3部 新命令セット, プログラミング・テクニック

で性能は大きく変わる, 日経バイト, 日本, 日経BP社 Nikkei Business Publications, Inc.

, 1999年 3月12日, 第189号, p.136-143

SUGATECH, Pentium IIIプログラミング, C MAGAZINE, 日本, ソフトバンクパブリッシング株式

会社, 1999年 4月23日, 第11巻 第5号, p.42-49

(58)調査した分野(Int.Cl., DB名)

G06F 7/24

G06F 17/10