(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7561560号

(P7561560)

(45)発行日 令和6年10月4日(2024.10.4)

(24)登録日 令和6年9月26日(2024.9.26)

(51)国際特許分類

|        |                  |     |        |        |   |

|--------|------------------|-----|--------|--------|---|

| H 01 L | 21/822 (2006.01) | F I | H 01 L | 27/04  | V |

| H 01 L | 27/04 (2006.01)  |     | H 01 L | 27/092 |   |

| H 01 L | 21/8238(2006.01) |     | H 01 L | 27/092 | C |

| H 01 L | 27/092 (2006.01) |     |        |        |   |

請求項の数 7 (全11頁)

(21)出願番号 特願2020-163985(P2020-163985)

(22)出願日 令和2年9月29日(2020.9.29)

(65)公開番号 特開2022-56141(P2022-56141A)

(43)公開日 令和4年4月8日(2022.4.8)

審査請求日 令和5年6月22日(2023.6.22)

(73)特許権者 308033711

ラピスセミコンダクタ株式会社

神奈川県横浜市港北区新横浜二丁目4番

地8

(74)代理人 110001519

弁理士法人太陽国際特許事務所

森 徹

(72)発明者 宮城県黒川郡大衡村沖の平1番 ラピス

セミコンダクタ宮城株式会社内

市川 武宜

審査官

最終頁に続く

(54)【発明の名称】 半導体装置、および半導体装置の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板に形成されたP型の第1のウェルと、

前記第1のウェル内に予め定められた間隔を隔てて形成されたN型のソース領域および

ドレイン領域と、

前記ソース領域および前記ドレイン領域を囲んで形成されたP型の不純物領域と、

前記ソース領域と前記ドレイン領域との間の前記半導体基板上に形成された第1のゲート酸化膜と、

前記第1のゲート酸化膜上に形成された第2のゲート酸化膜と、

前記第2のゲート酸化膜上に形成されたゲート電極と、

前記第1のゲート酸化膜の下部に形成され、ヒューズとして機能するP型の不純物層と、

を含む半導体装置。

## 【請求項2】

前記不純物層の不純物濃度が、前記第1のウェルの不純物濃度および前記不純物領域の

不純物濃度より高い 請求項1に記載の半導体装置。

## 【請求項3】

前記不純物領域と、前記ソース領域、前記ドレイン領域、および前記ゲート電極と、の

間に逆バイアスを印加することによって前記第1のウェル内にキャリアを発生させ、発生

したキャリアを前記第1のゲート酸化膜と前記第2のゲート酸化膜との界面に蓄積させる

請求項1または請求項2に記載の半導体装置。

**【請求項 4】**

前記第1のゲート酸化膜と前記第2のゲート酸化膜との間に蓄積されたキャリアによって変化する前記半導体装置の特性を用いて、前記不純物層をヒューズとして機能させる請求項3に記載の半導体装置。

**【請求項 5】**

前記ソース領域および前記ドレイン領域の各々の周囲の前記第1のウェル内に形成された2つの第2の導電型の第2のウェルをさらに含み、

前記不純物層は、前記第2のウェルの間で、前記第1のゲート酸化膜の下部の前記半導体基板に形成された活性領域と一部重なるように2個配置された

請求項1から請求項4のいずれか1項に記載の半導体装置。

10

**【請求項 6】**

前記ゲート電極下の領域において、前記第1のゲート酸化膜および前記第2のゲート酸化膜が前記不純物層の上部にのみ形成され、残余の領域には第1のゲート酸化膜のみが形成されている

請求項1から請求項5のいずれか1項に記載の半導体装置。

**【請求項 7】**

同一の半導体基板上にヒューズとして機能する第1の素子およびトランジスタとして機能する第2の素子を形成する半導体装置の製造方法であって、

前記半導体基板にP型のウェルを形成し、

前記ウェル内に予め定められた間隔を隔ててN型のソース領域およびドレイン領域を形成し、

前記ソース領域と前記ドレイン領域との間の前記半導体基板上に第1のゲート酸化膜を形成し、

前記第1のゲート酸化膜上に第2のゲート酸化膜を形成することにより前記第2の素子を形成し、

さらに、前記第1のゲート酸化膜の下部にヒューズとして機能するP型の不純物層を形成することにより前記第1の素子を形成する

半導体装置の製造方法。

20

**【発明の詳細な説明】****【技術分野】**

30

**【0001】**

本発明は、半導体装置、および半導体装置の製造方法に関する。

**【背景技術】****【0002】**

半導体装置において用いられる技術のひとつに、ヒューズ素子に関する技術がある。半導体装置におけるヒューズ素子とは、半導体装置内に設けられた所定の方法で切断が可能な素子であり、切断することによって回路の調整（トリミング）を行うことができる素子である。本発明は、半導体装置におけるヒューズ素子、とりわけ高耐圧ヒューズ素子に関する。

**【0003】**

40

図8に一般的なヒューズの例を示す。図8(a)はレーザヒューズを示しており、図8(a)<1>はレーザヒューズの平面図、図8(a)<2>は断面図を各々表している。図8(a)に示すレーザヒューズは、両端が回路素子等に接続されたA1(アルミニウム)配線100を含み、切断領域CAにおいて、A1配線100をレーザで切断することにより目的とするトリミングを行う。

**【0004】**

また、図8(b)は別の例であるZAPヒューズを示している。ZAPヒューズは、図8(b)に示すように、N+不純物領域101、P+不純物領域102、および重畠領域103を備えている。N+不純物領域101はN型不純物が相対的に高濃度に添加された領域であり、P+不純物領域はP型不純物が相対的に高濃度に添加された領域であり、重

50

疊領域 103 は N+ 不純物領域 101 と P+ 不純物領域とが重なった領域である。ZAP ヒューズは、N+ 不純物領域 101 と P+ 不純物領域 102 との間に順方向に電圧を印加し、過電流を流すことによって接合を破壊しトリミングを行う。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

ここで、ヒューズによるトリミングは製造工程の一環として行われる場合のみならず、製造工程終了後パッケージ等に実装された状態（組立後の状態）で行われる場合もある。従って、両方の状態でトリミングができると至便である。この点上記のレーザヒューズは、製造工程終了後にレーザで A1 配線 100 を切断するため組立後にトリミングをすることはできない。一方、ZAP ヒューズは、パッケージの端子を介して重疊領域 103 に過電流を流して切断を行うことにより、組立後にトリミングが可能である。しかしながら、N+ 不純物領域 101、P+ 不純物領域 102 による高濃度の接合を使用しているため、高電圧が印加される箇所のトリミングができないという欠点がある。

10

#### 【0006】

また、半導体装置の製造方法においては、ヒューズ素子は付加的な素子であることから極力専用の工程を減らし、さらに半導体装置の主要な回路素子の製造プロセスと兼用化が図られていると製造プロセスが簡略化され、コスト面からも好ましい。

#### 【0007】

本発明は、上記の事情を踏まえ、組立後にトリミング可能で製造が簡易な高耐圧のヒューズ素子を含む半導体装置、および半導体装置の製造方法を提供することを目的とする。

20

#### 【課題を解決するための手段】

#### 【0008】

上記課題を解決するため、本発明に係る半導体装置は、半導体基板に形成された第1の極性の第1のウェルと、前記第1のウェル内に予め定められた間隔を隔てて形成された第2の極性のソース領域およびドレイン領域と、前記ソース領域および前記ドレイン領域を囲んで形成された第1の極性の不純物領域と、前記ソース領域と前記ドレイン領域との間の前記半導体基板上に形成された第1のゲート酸化膜と、前記第1のゲート酸化膜上に形成された第2のゲート酸化膜と、前記第2のゲート酸化膜上に形成されたゲート電極と、前記第1のゲート酸化膜の下部に形成された第1の極性の不純物層と、を含む。

30

#### 【0009】

上記課題を解決するため、本発明に係る半導体装置の製造方法は、同一の半導体基板上にヒューズとして機能する第1の素子およびトランジスタとして機能する第2の素子を形成する半導体装置の製造方法であって、前記半導体基板に第1の極性のウェルを形成し、前記ウェル内に予め定められた間隔を隔てて第2の極性のソース領域およびドレイン領域を形成し、前記ソース領域と前記ドレイン領域との間の前記半導体基板上に第1のゲート酸化膜を形成し、前記第1のゲート酸化膜上に第2のゲート酸化膜を形成することにより前記第2の素子を形成し、さらに、前記第1のゲート酸化膜の下部に第1の極性の不純物層を形成することにより前記第1の素子を形成する。

#### 【発明の効果】

40

#### 【0010】

本発明によれば、組立後にトリミング可能で製造が簡易な高耐圧のヒューズ素子を含む半導体装置、および半導体装置の製造方法を提供することが可能となる、という効果を奏する。

#### 【図面の簡単な説明】

#### 【0011】

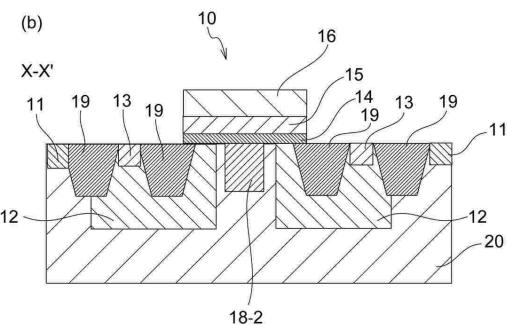

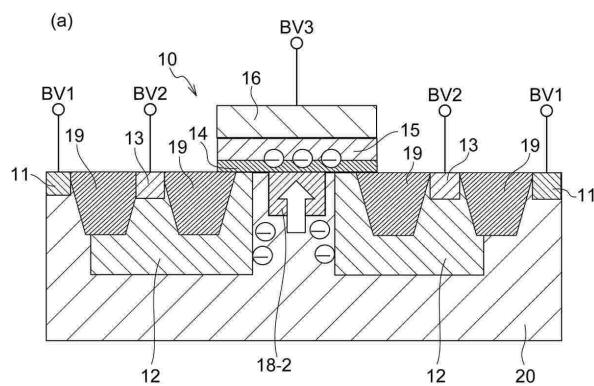

【図1】第1の実施の形態に係る半導体装置の構成の一例を示す、(a)は平面図、(b)は断面図である。

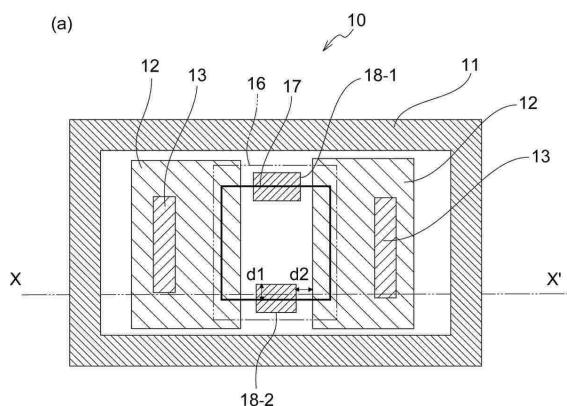

【図2】第1の実施の形態に係る高電圧MOSトランジスタの構成の一例を示す断面図である。

50

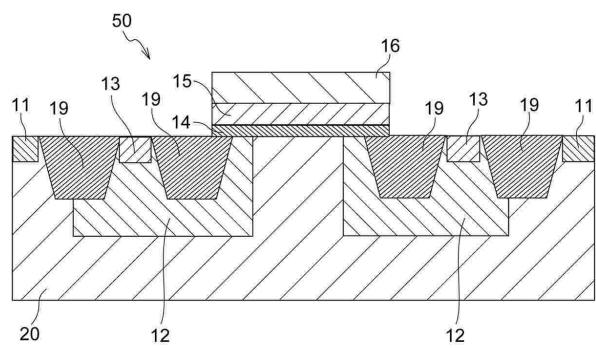

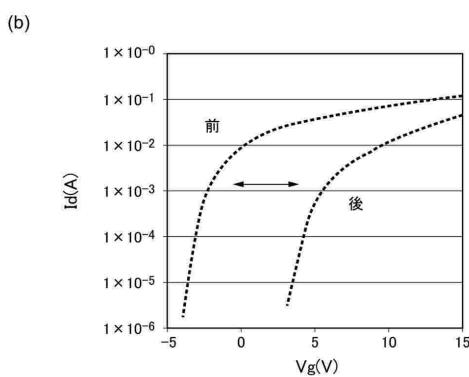

【図3】第1の実施の形態に係る半導体装置の、(a)は書き込み動作を説明する断面図、(b)は書き込み前後のドレイン電流特性を示すグラフである。

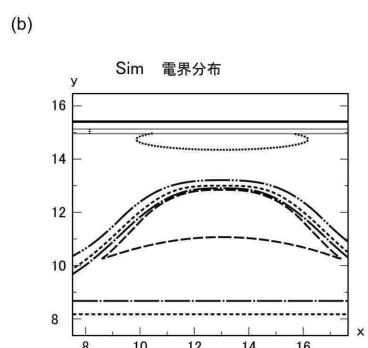

【図4】第1の実施の形態に係る半導体装置の書き込み時の電界分布を示す、(a)は断面図、(b)はシミュレーション結果である。

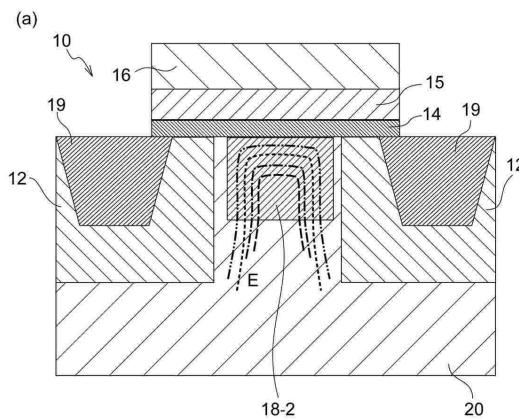

【図5】(a)から(c)は、第1の実施の形態に係る半導体装置の製造方法の一例を示す断面図である。

【図6】第2の実施の形態に係る高電圧MOSトランジスタの構成の一例を示す断面図である。

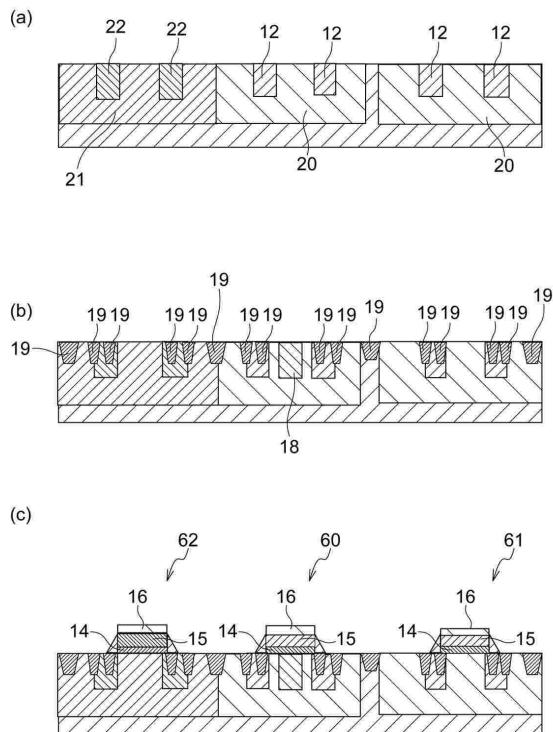

【図7】第3の実施の形態に係る半導体装置の構成の一例を示す、(a)は平面図、(b)はY-Y'断面図、(c)はZ-Z'断面図である。

【図8】(a)はレーザヒューズを示す平面図および断面図、(b)はZAPヒューズを示す平面図である。

#### 【発明を実施するための形態】

##### 【0012】

以下、図面を参照し、本発明の実施の形態について詳細に説明する。以下の説明では、本発明に係る半導体装置を、高電圧MOS(Metal Oxide Semiconductor)トランジスタ(以下、「HV(High Voltage)トランジスタ」)と共に構成を備え、HVトランジスタの製造プロセスと大部分が共通する製造プロセスで製造することができるヒューズに適用した形態を例示して説明する。

##### 【0013】

#### 【第1の実施の形態】

図1から図5を参照して、本実施の形態に係る半導体装置10について説明する。図1(a)は半導体装置10の平面図を、図1(b)は、図1(a)におけるX-X'線に沿った断面図を各々示している。図1(b)に示すように、半導体装置10は、図示を省略する半導体基板内に形成されたPウェル(P型不純物が添加されたウェル領域)20、P+不純物領域11、N-不純物領域12、N+不純物領域13、第1ゲート酸化膜14、第2ゲート酸化膜15、ゲート電極16、電子引上層18-2、およびトレンチ19を含んでいる。電子引上層18-2以外の構成はHVトランジスタ(図2参照)と共にあり、換言すれば、半導体装置10は、HVトランジスタに電子引上層18-2を附加した構成となっている。従って、本実施の形態では、製造プロセスの簡単な変更によって、ヒューズとHVトランジスタを作り分けることができる。

##### 【0014】

N-不純物領域12は、Pウェル20内に形成されたNウェルである。N+不純物領域13はN-不純物領域12内に形成され、トレンチ19に挟まれている。N+不純物領域13は、ソース領域、およびドレイン領域の機能を有する。半導体装置10ではゲート酸化膜が第1ゲート酸化膜14および第2ゲート酸化膜15の2層構造となっている。第1ゲート酸化膜14は一例として厚さ10nmから50nmの熱酸化膜とされ、第2酸化膜15は一例として厚さ150nmから250nmのLPTEOSによる膜(以下、「TEOS膜」とされている)とされている。ここで、LPTEOSとは、TEOSを用いたLow Pressure CVD(Chemical Vapor Deposition)によって形成された酸化膜をいう。電子引上層18-2はヒューズとしての半導体装置10に固有の層であり、P型不純物が比較的高濃度で添加された領域である。電子引上層18-2の不純物濃度は、例えば、Pウェル20の不純物濃度、およびP+不純物領域11の不純物濃度より高くする。本実施の形態に係る半導体装置10では、トレンチ19をSTI(Shallow Trench Isolation)としているが、これに限られない。

##### 【0015】

図1(a)を参照して、P+不純物領域11は、半導体装置10の外周を取り囲んで形成されている。ゲート電極16の下部に位置して、活性領域17(アクティブ領域)が形成されている。電子引上層18-1、18-2が各々活性領域17と一部重なるように配置されている。なお、図1(a)ではトレンチ19の図示を省略している。

10

20

30

40

50

## 【0016】

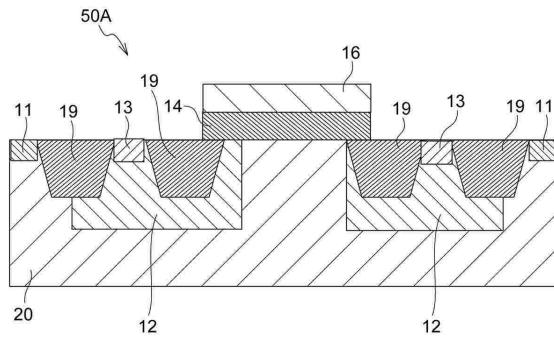

図2は、本実施の形態に係るH Vトランジスタとしての半導体装置50を示している。上述したように、半導体装置50は、半導体装置10から電子引上層18-1、18-2(以下、総称する場合は「電子引上層18」)を除いた構成となっている。なお、「電子引上層18」は、本発明に係る「不純物層」の一例である。

## 【0017】

次に図3および図4を参照して、本実施の形態に係る電子引上層18-1、18-2の作用について説明する。半導体装置10ではトリミング(切断、以下「書き込み」という場合がある)を行う場合に、図3(a)に示すようにバイアス電圧を印加する。すなわち、P+不純物領域11にバイアス電圧BV1、N+不純物領域13にバイアス電圧BV2、ゲート電極16にバイアス電圧BV3を印加する。バイアス電圧BV1、BV2、BV3(以下、総称する場合は「バイアス電圧BV」)の組み合わせ(BV1、BV2、BV3)は、例えば以下のように設定する。すなわち、

(BV1, BV2, BV3) = (-70V~-100V, 0V, 0V)

または、

$$(BV1, BV2, BV3) = (0V, 70V~80V, 70V~80V)$$

のように設定する。ただし、バイアス電圧BVの組み合わせはこれに限られず、要は、P+不純物領域11と、N+不純物領域13およびゲート電極16との間に所定の電位差が印加されるように設定すればよい。

## 【0018】

半導体装置10に対して上記のようにバイアス電圧BVを印加すると、Pウェル20内で電子が発生し、電子引上層18(図3(a)では電子引上層18-2が見えている)による高電界に引き寄せられ、ゲート酸化膜(第1ゲート酸化膜14、第2ゲート酸化膜15)、特に、第1ゲート酸化膜14と第2ゲート酸化膜15の界面に蓄積される。すなわち、半導体装置10では、書き込み処理を行うことによって、主として第1ゲート酸化膜14と第2ゲート酸化膜15の界面に電子が蓄積される。さらにこの電子はバイアス電圧BVを切っても保持される。

## 【0019】

図3(b)は、書き込み前後のゲート電圧(Vg) - ドレイン電流(Id)特性を示している。図3(b)に示すように、H Vトランジスタとしての半導体装置10の特性は、書き込み前はVg = 0Vでオンとなり、書き込み後はVg = 0Vでオフになる特性を示す。半導体装置10は、Vg = 0Vを境界とする(以下、「境界電圧」という場合がある)この特性、すなわち、書き込みを行う前には導通していた(ショートしていた)H Vトランジスタが書き込みを行うことによって遮断される(オープンとされる)という特性を利用し、書き込み処理をおこなうことによりトリミングを行う。むろん、ここで例示したバイアス電圧BV、境界電圧は一例であり、H Vトランジスタの特性等に応じて適切な値を設定してよい。

## 【0020】

図4を参照して、電子引上層18の作用についてより詳細に説明する。半導体装置10では、上記バイアス処理によって、ゲート酸化膜(第1ゲート酸化膜14、第2ゲート酸化膜15)の方向に食い込むように電界が発生する。電子引上層18はこの領域の電界をさらに強くする作用を有する。図4(b)は、半導体装置10における電界分布のシミュレーション結果を示しており、2つのN-不純物領域12の間の等電位線を示している。図4(b)に示すように、2つのN-不純物領域12の間の等電位線は凸状の形状を示し、紙面上にいくほど電位が高くなっている。図4(a)は、図4(b)に示すシミュレーション結果を概念的に示した図であり、2つのN-不純物領域12の間の電界Eがゲート酸化膜(第1ゲート酸化膜14、第2ゲート酸化膜15)に向かって食い込むように発生し、ゲート酸化膜(第1ゲート酸化膜14、第2ゲート酸化膜15)に近づくほど電位が高くなっている。すなわち、電界Eは紙面上から下に向かう方向に発生し、この電界Eが電子引上層18でさらに強化され、強化された電界Eによって電子がゲート酸化膜(第1

10

20

30

40

50

ゲート酸化膜 14、第2ゲート酸化膜 15)に引き上げられる。

【0021】

ここで、図1(a)を参照し、電子引上層 18の位置について説明する。電子引上層 18が上述した作用を発揮するためには、電子引上層 18と、活性領域 17およびN-不純物領域 12との相対的な位置関係を適切に設定する必要がある。このことは、電子引上層 18-1についても、18-2についても同様であるので、以下電子引上層 18-2を例示して説明する。まず、電子引上層 18-2と活性領域 17との重なり長 d1 は、0.2 μm から 1 μm とするのが好ましい。電子引上層 18-2と活性領域 17との重なる面積の割合が大きいと耐圧に影響し、重なる面積の割合が小さいとトリミング後の電気特性に影響がでるためである。また、電子引上層 18-2とN-不純物領域との距離 d2 は 2 μm から 4 μm とするのが好ましい。さらに、第1ゲート酸化膜 14が厚くなるほど書き込み(トリミング)特性が悪くなる傾向がある。

【0022】

以上のように、本実施の形態に係る半導体装置 10は、基本的に高電圧MOSトランジスタの構造となっているため、ドレインに高電圧をかけることが可能である。すなわち半導体装置 10によれば、高電圧の半導体装置にヒューズ機能を組み込むことが可能である。二重のゲート酸化膜(第1ゲート酸化膜 14、第2ゲート酸化膜 15)と、活性領域 17の端部に一部重なるように配置された電子引上層 18と、によって書き込みを行うため、電気的にトリミングが可能である。このため組立後のトリミングが可能となっている。また、高電圧MOSトランジスタに電子引上層 18を付加するだけで製造が可能なので、ヒューズを含む半導体装置の製造が簡略化される。

【0023】

次に図5を参照して、半導体装置 10の製造方法について説明する。上述したように、本実施の形態に係る半導体装置 10は、HVトランジスタ(半導体装置 50)と同一基板上に混載して形成することにより様々な回路機能を実現することができる。以下、このようなHVトランジスタと高耐圧ヒューズを混載した半導体装置の製造方法を例示して説明する。図5では、ヒューズ 60(半導体装置 10)、N型MOSトランジスタ 61(HVトランジスタ、半導体装置 50)、P型MOSトランジスタ 62(HVトランジスタ)の製造を例示して説明する。

【0024】

図5(a)に示すように、フォトリソグラフィ、イオン注入等を用いて半導体基板(図示省略)にP型不純物を導入してPウェル 20を形成し、N型不純物を導入してNウェル 21を形成する。その後、フォトリソグラフィを用いて、N-不純物領域 12、P-不純物領域 22を形成する。その後熱処理を行って不純物の拡散を行うとともに、熱処理で形成された酸化膜を除去する。

【0025】

その後図5(b)に示すように、フォトリソグラフィ、エッチングを用いてトレンチ 19を形成する。その後、例えばHDP(High Density Plasma)-CVD(Chemical Vapor Deposition)によってトレンチ 19を絶縁物で充填し、その後CMP(Chemical Mechanical Polishing)によって絶縁物を研削し平坦化する。その後、P型不純物を高濃度に導入して電子引上層 18を形成する。

【0026】

その後図5(c)に示すように、フォトリソグラフィ、エッチングを用いて第1ゲート酸化膜 14、第2ゲート酸化膜 15を形成する。その後、例えばCVDによりポリシリコンを成膜し、フォトリソグラフィ、エッチングによりゲート電極 16を形成する。その後フォトグラフィ、およびイオン注入等を用いて、ソース、ドレインとなるN+不純物領域(N型MOSトランジスタ 61の場合、図示省略)、P+不純物領域(P型MOSトランジスタ 62の場合、図示省略)を形成する。

【0027】

10

20

30

40

50

## [ 第 2 の実施の形態 ]

図 6 を参照して、本実施の形態に係る半導体装置について説明する。本実施の形態はヒューズと H V トランジスタとを混載した半導体装置において、H V トランジスタとしての半導体装置 5 0 を H V トランジスタとしての半導体装置 5 0 A に置き換えた形態である。従って、組み合わせるヒューズは半導体装置 1 0 と同じなので図示を省略する。

## 【 0 0 2 8 】

図 6 に示すように、半導体装置 5 0 A は、図 2 に示す半導体装置 5 0 における第 2 ゲート酸化膜 1 5 を削除し、ゲート酸化膜を第 1 ゲート酸化膜 1 4 の単層にした形態である。半導体装置 1 0 では電子蓄積のために T E O S 膜である第 2 ゲート酸化膜 1 5 を設けていた。製造プロセスの共用化の観点からは半導体装置 5 0 A においても第 2 ゲート酸化膜 1 5 を備えていた方が好都合であるが、H V トランジスタにおいては電子の蓄積は不要であり、電子が蓄積されることによってむしろ H V トランジスタとしての信頼性が低下する場合がある。そこで、本実施の形態では電子を蓄積させるための構成である第 2 ゲート酸化膜 1 5 を削除することとした。

10

## 【 0 0 2 9 】

半導体装置 5 0 A を含む半導体装置の製造プロセスにおいては、半導体装置 1 0 の形成完了後、半導体装置 5 0 A に形成されたゲート酸化膜（第 1 ゲート酸化膜 1 4、第 2 ゲート酸化膜 1 5）を一旦削除し、新たに第 1 ゲート酸化膜 1 4 を形成する。従って製造プロセス的には工程数が増えるが、H V トランジスタとしての半導体装置 5 0 A の信頼性をより向上させることができる。

20

## 【 0 0 3 0 】

## [ 第 3 の実施の形態 ]

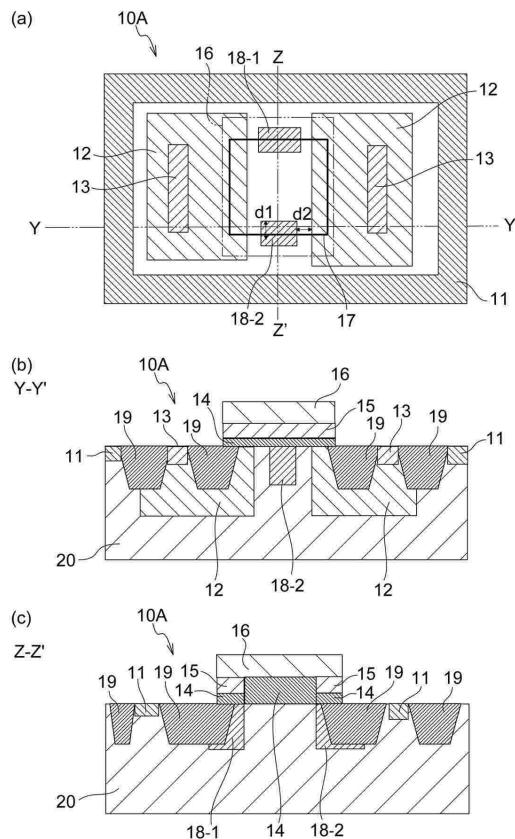

図 7 を参照して。本実施の形態に係る半導体装置 1 0 A について説明する。半導体装置 1 0 A は、半導体装置 1 0 に対して二重のゲート酸化膜（第 1 ゲート酸化膜 1 4、第 2 ゲート酸化膜 1 5）の配置位置を限定した形態である。図 7 ( a ) は半導体装置 1 0 A の平面図、図 7 ( b ) は図 7 ( a ) に示す Y - Y' 線に沿って切断した断面図、図 7 ( c ) は図 7 ( a ) に示す Z - Z' 線に沿って切断した断面図である。

## 【 0 0 3 1 】

図 7 ( b ) に示すように、半導体装置 1 0 A の Y - Y' で切断した断面は、図 1 ( b ) に示す半導体装置 1 0 の断面と変わらない。しかしながら、図 7 ( c ) に示すように、Z - Z' 線で切断した断面は半導体装置 1 0 の断面と異なっている。すなわち、図 7 ( c ) に示すように。半導体装置 1 0 A では、ゲート酸化膜が、ゲート電極 1 6 の下部の両端に配置された第 1 ゲート酸化膜 1 4 と第 2 ゲート酸化膜 1 5 の二重構造のゲート酸化膜と、中央に配置された第 1 ゲート酸化膜 1 4 の単層のゲート酸化膜とを備えている。そして、二重構造のゲート酸化膜は電子引上層 1 8 - 1、1 8 - 2 の上部に配置されている。

30

## 【 0 0 3 2 】

本実施の形態に係る半導体装置 1 0 A は、電子引上層 1 8 の直上部のみに二重ゲート酸化膜を配置した。このことにより、半導体装置 1 0 と比較してより効率的に書き込みを行うことができるので、トリミング速度をより向上させる（速くする）ことができる。製造プロセス的には、上記半導体装置 5 0 A と同様にゲート酸化膜の再形成という製造プロセスの追加がある。しかしながら、電子蓄積のための二重ゲート酸化膜を配置する領域が半導体装置 1 0 よりも限定されているため、H V トランジスタをヒューズとしての半導体装置 1 0 A と同様の構成で製造しても、信頼性の低下は抑制される。

40

## 【 0 0 3 3 】

なお、上記各実施の形態では、ヒューズとしての半導体装置を N 型 M O S トランジスタを用いて形成する形態を例示して説明したが、P 型 M O S トランジスタを用いた形態としてもよい。この場合、二重のゲート酸化膜にホールを蓄積するので、電子引上層はホールを引き上げるホール引上層になる。この意味で電子引上層は一般的にはキャリア引上層と考えることができる。

## 【 符号の説明 】

50

## 【0034】

1 0、10A 半導体装置

1 1 P + 不純物領域

1 2 N - 不純物領域

1 3 N + 不純物領域

1 4 第1ゲート酸化膜

1 5 第2ゲート酸化膜

1 6 ゲート電極

1 7 活性領域

1 8、18-1、18-2 電子引上層

1 9 トレンチ

2 0 P ウェル

2 1 N ウェル

2 2 P - 不純物領域

5 0、50A 半導体装置

6 0 ヒューズ

6 1 N型MOSトランジスタ

6 2 P型MOSトランジスタ

1 0 0 A1配線

1 0 1 N + 不純物領域

1 0 2 P + 不純物領域

1 0 3 重畠領域

B V 1、B V 2、B V 3 バイアス電圧

C A 切断領域

d 1 重なり長

d 2 距離、E 電界

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

【図 3】

【図 4】

30

40

50

【図5】

【 四 6 】

10

20

【図7】

【 四 8 】

30

40

---

フロントページの続き

(56)参考文献 特開2011-035412(JP,A)

特開2015-079950(JP,A)

特開2008-243329(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/822

H01L 21/8238

H01L 27/04

H01L 27/092