(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6725147号

(P6725147)

(45) 発行日 令和2年7月15日(2020.7.15)

(24) 登録日 令和2年6月29日(2020.6.29)

|                      |                 |

|----------------------|-----------------|

| (51) Int.Cl.         | F 1             |

| HO2M 3/155 (2006.01) | HO2M 3/155 G    |

| HO2J 7/10 (2006.01)  | HO2J 7/10 H     |

| HO2J 9/06 (2006.01)  | HO2J 9/06 110   |

| B60R 16/02 (2006.01) | B60R 16/02 660L |

請求項の数 4 (全 26 頁)

(21) 出願番号 特願2017-108216 (P2017-108216)

(22) 出願日 平成29年5月31日 (2017.5.31)

(65) 公開番号 特開2018-207598 (P2018-207598A)

(43) 公開日 平成30年12月27日 (2018.12.27)

審査請求日 令和1年10月24日 (2019.10.24)

早期審査対象出願

(73) 特許権者 000237592

株式会社デンソーテン

兵庫県神戸市兵庫区御所通1丁目2番28

号

(74) 代理人 100113608

弁理士 平川 明

(74) 代理人 100123098

弁理士 今堀 克彦

(74) 代理人 100146330

弁理士 本間 博行

(72) 発明者 小山 輝芳

兵庫県神戸市兵庫区御所通1丁目2番28

号 富士通テン株式会社内

審査官 遠藤 尊志

最終頁に続く

(54) 【発明の名称】充電制御装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電源から供給された電力をキャパシタに充電するスイッチングレギュレータと、第一抵抗素子及び第二抵抗素子を含む第1の分圧抵抗とを備える充電制御装置において、

前記スイッチングレギュレータは、

帰還入力される制御量と基準電圧との差電圧に基づく誤差信号を出力する誤差アンプと

、

前記誤差信号に基づき前記キャパシタに供給する充電電流を制御する制御部とを備え、

前記第一抵抗素子及び前記第二抵抗素子が、前記制御部に入力される前の前記誤差信号

を出力する端子とグランドとの間に直列に設けられ、

前記誤差アンプが出力する前記誤差信号を前記第一抵抗素子と前記第二抵抗素子とで分

圧した電圧を前記制御量として前記誤差アンプに帰還入力することを特徴とする充電制御

装置。

## 【請求項 2】

電源から供給された電力をキャパシタに充電するスイッチングレギュレータを備える充

電制御装置において、

前記スイッチングレギュレータは、

帰還入力される制御量と基準電圧との差電圧に基づく誤差信号を出力する誤差アンプと

、

前記誤差信号に基づき前記キャパシタに供給する充電電流を制御する制御部とを備え、

10

20

前記誤差アンプの出力端子と前記電源の出力ラインとの間に接続される第2の分圧抵抗を有し、前記誤差信号を前記第2の分圧抵抗で分圧した電圧を前記制御量として前記誤差アンプに帰還入力することを特徴とする充電制御装置。

【請求項3】

直列に接続された前記第一抵抗素子と前記第二抵抗素子との接続点に一端が接続され、他端が前記キャパシタの正極に接続された第三抵抗素子を更に備え、

前記誤差信号を前記第一抵抗素子と前記第二抵抗素子とで分圧することに加え、前記キャパシタに充電された充電電圧を前記第三抵抗素子を介して前記誤差アンプに帰還入力することを特徴とする請求項1に記載の充電制御装置。

【請求項4】

前記キャパシタに充電された充電電圧を前記第2の分圧抵抗を介して前記誤差アンプに帰還入力することを特徴とする請求項2に記載の充電制御装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、充電制御装置に関する。

【背景技術】

【0002】

従来、車両に搭載したカメラ等の撮像装置で車両周辺や車内の状況を撮影し、撮影した映像を記録するドライブレコーダが知られている。ドライブレコーダを介し、例えば、衝撃等の所定の事象が発生した際の車両周辺や車内の状況を映像として記録することができる。ドライブレコーダでは、例えば、発生した衝撃によって、電力を供給するバッテリとの間で断線が生じた場合であっても、所定動作が可能なようにバックアップ用の電源を備える場合がある。

【0003】

ドライブレコーダの備えるバックアップ用の電源として、例えば、ウルトラ・キャパシタ(Ultracapacitor)やスーパー・キャパシタ(Supercapacitor)とも称される電気二重層キャパシタ(Electric double-layer capacitor、以下、「EDLC」とも称す)が例示される。EDLCでは、電力エネルギーの蓄電量を相対的に高めることができため、記録映像の可搬メモリ(例えば、SDカード)への退避保存や、衝撃発生後の映像撮影および記録保存が可能になる。

【0004】

近年の、ドライブレコーダの高機能化、高性能化に伴い、バックアップ用の電源として、EDLCを備えるドライブレコーダが普及してきている。なお、本明細書で説明する技術に関連する技術が記載されている先行技術文献としては、以下の特許文献が存在している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2016-46993号公報

【特許文献2】特開2016-54628号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

EDLCをバックアップ用の電源として備えるドライブレコーダ等の電子機器では、EDLCの劣化を抑制するために、非運用状態に移行する際には、運用時に充電された電力(電荷)を放電し、空き状態にすることが求められる。このため、運用開始時には、EDLCに対して、バッテリから供給された電力を用いて、空き状態から上記電子機器の動作をバックアップ可能な電力量まで急速に充電することが求められる。

【0007】

10

20

30

40

50

リニアレギュレーション方式による充電回路では、発熱量が高く回路損失が大きいため、E D L Cへの急速な充電期間に対応することは困難である。スイッチング方式による充電回路では、E D L Cを充電するための定電流を供給する機能が求められる。しかしながら、スイッチング方式においては、バッテリ等から供給された電力をスイッチングのオン／オフで時分割する際の低調波発振を抑制するための専用の定電流制御機能を設けた上で、バッテリ等からの供給電力を一定値以下に抑えつつ急速にE D L Cを充電することが求められる。このようなスイッチング方式の充電回路を備えたI Cは汎用的には提供されていないため、専用のI C開発を必要としていた。

## 【0008】

本発明の目的は、キャパシタへの急速充電が可能な定電流制御の技術の提供にある。

10

## 【課題を解決するための手段】

## 【0009】

開示の技術の一側面は、充電制御装置によって例示される。すなわち、充電制御装置は、電源から供給された電力をキャパシタに充電するスイッチングレギュレータを備える。充電制御装置は、所定の制御量をスイッチングレギュレータに帰還入力させるフィードバック手段と、スイッチングレギュレータは、フィードバック手段から帰還入力された制御量に応じてキャパシタに供給する充電電流を制御する制御手段と、を備えることを特徴とする。

## 【発明の効果】

## 【0010】

20

開示の技術の一側面によれば、キャパシタへの急速充電が可能な定電流制御の技術が提供される。

## 【図面の簡単な説明】

## 【0011】

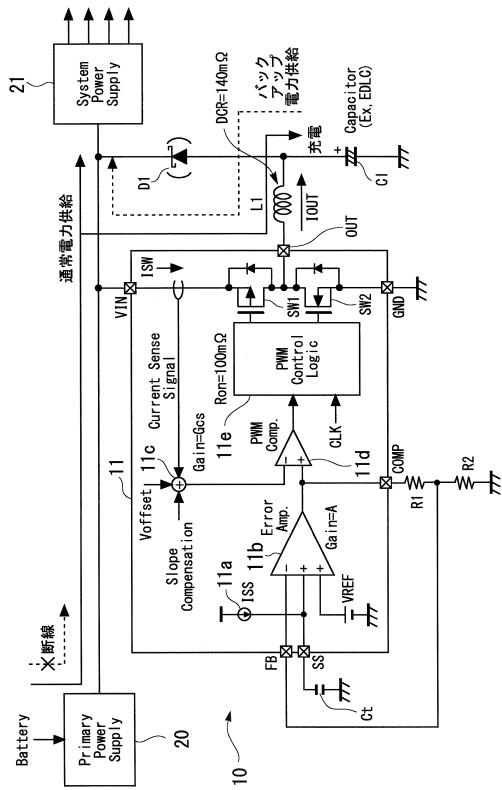

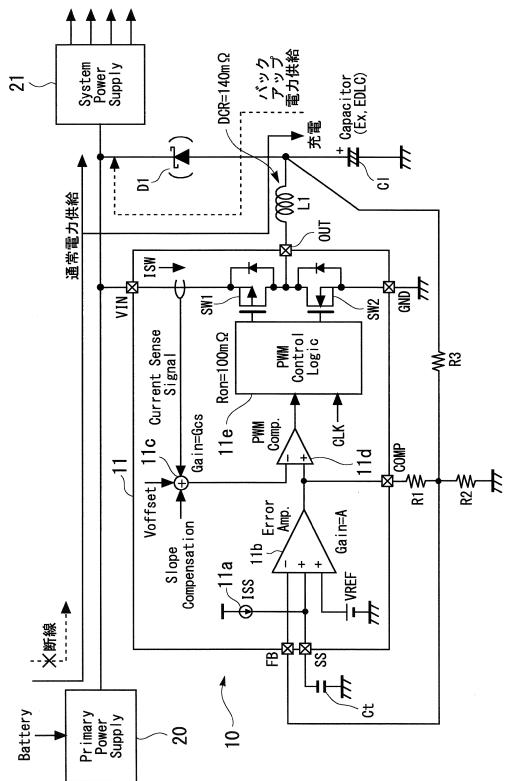

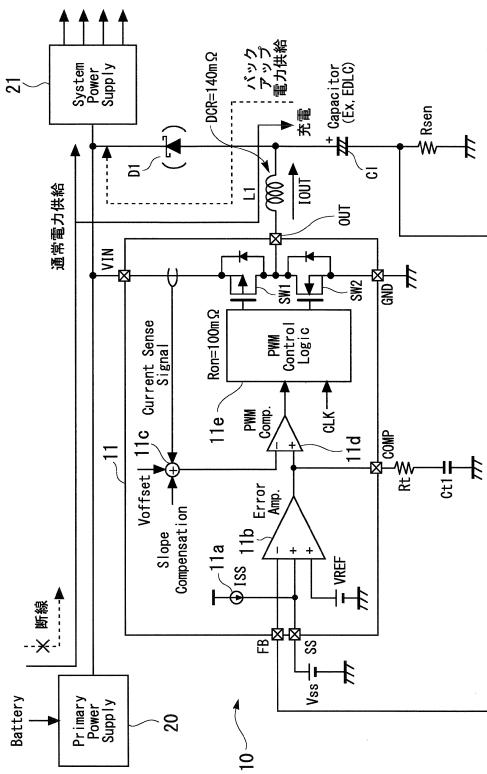

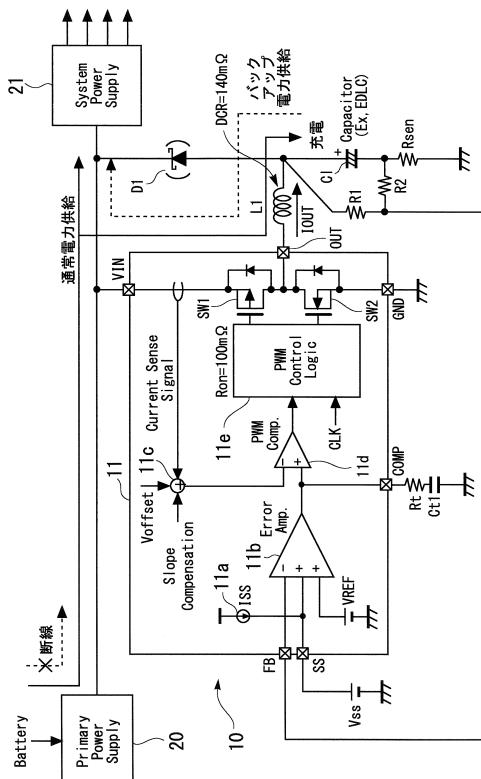

【図1】実施例1の充電制御装置のブロック構成の一例を示す図である。

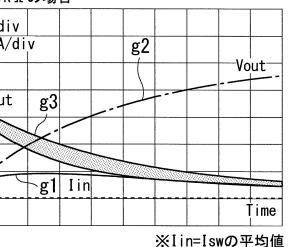

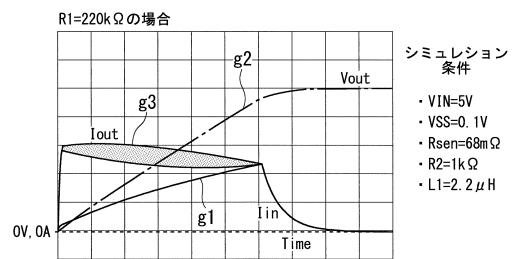

【図2】実施例1の充電電流特性の一例を示す図である。

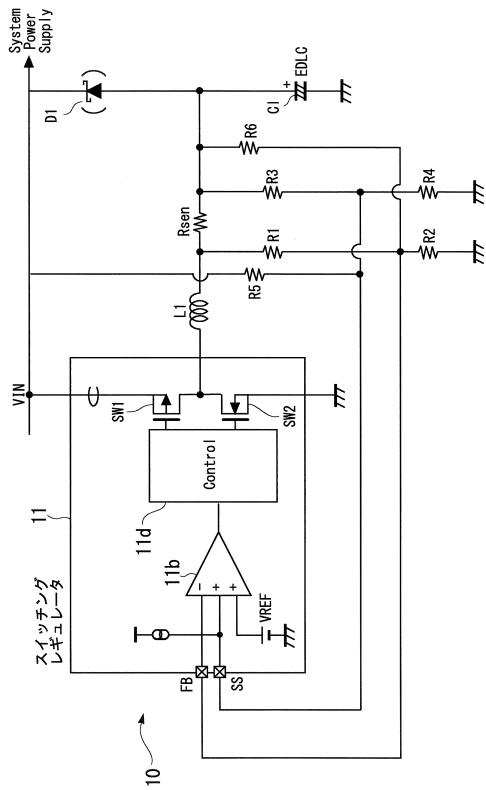

【図3】実施例2の充電制御装置のブロック構成の一例を示す図である。

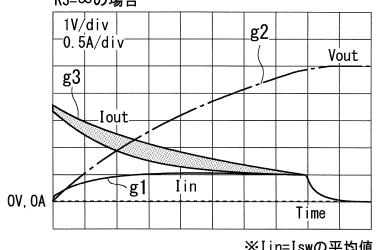

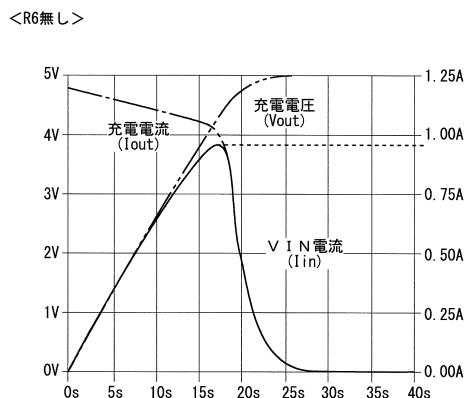

【図4】実施例2の充電電流特性の一例を示す図である。

【図5】実施例3の充電制御装置のブロック構成の一例を示す図である。

【図6】実施例3の充電電流特性の一例を示す図である。

30

【図7】実施例4の充電制御装置のブロック構成の一例を示す図である。

【図8】実施例4の充電電流特性の一例を示す図である。

【図9】実施例5の充電制御装置のブロック構成の一例を示す図である。

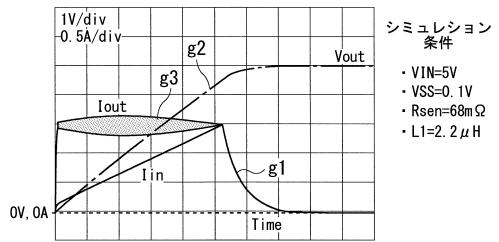

【図10】実施例5の充電電流特性の一例を示す図である。

【図11】実施例6の充電制御装置のブロック構成の一例を示す図である。

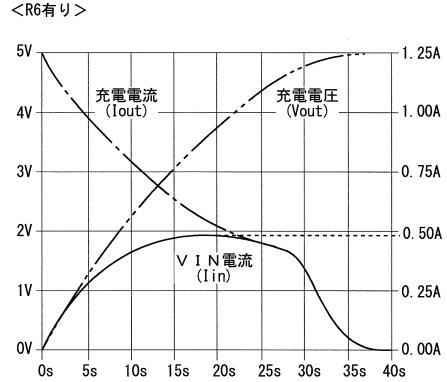

【図12】実施例6の充電電流特性の一例を示す図である。

【図13】実施例6の充電電流特性の一例を示す図である。

【図14】変形例の充電制御装置のブロック構成の一例を示す図である。

【図15】変形例の充電電流特性を説明する図である。

【図16】変形例の充電電流特性を説明する図である。

40

## 【発明を実施するための形態】

## 【0012】

以下、図面を参照して、一実施形態に係る充電制御装置について説明する。以下の実施形態の構成は例示であり、本充電制御装置は実施形態の構成には限定されない。

## 【0013】

<実施の形態>

## 〔実施例1〕(ブロック構成)

図1は、本実施形態に係る充電制御装置10のブロック構成の一例を示す図である。図1に例示の充電制御装置10は、例えば、ドライブレコーダといった車両に搭載可能な車載装置の受電部に含まれる充電制御装置である。車載装置は、受電部を介して車両に搭載

50

されたバッテリに接続する。受電部は、接続するバッテリから供給された電力を所定の直流電圧に変換し、車載装置が有するメモリやプロセッサ等のデバイスに供給する。また、受電部は、バックアップ用電源を備える。車載装置内のプロセッサ等は、受電部を介して供給された電力を使用し、メモリ等に格納された各種プログラムを実行する。各種プログラムの実行により、車両に搭載したカメラ等の撮像装置で車両周辺や車内の状況を撮影し、撮影した映像を記録する。

【0014】

なお、ドライブレコーダ以外の車載装置として、例えば、ナビゲーション機能、オーディオ機能、画像再生機能、通信機能といった各種機能を搭乗員に提供するオーディオ・ビジュアル・ナビゲーション一体機（AVN機）が例示される。以下の説明では、充電制御装置10を受電部に含む車載装置例は、ドライブレコーダとする。

10

【0015】

図1において、キャパシタC1と、ダイオード素子D1は、車載装置の受電部に設けられたバックアップ用電源を構成する。なお、図1に示す受電部の電力供給形態は、バッテリから供給された供給電力（Battery）を所定の直流電圧に変換する「Primary Power Supply20」と、「Primary Power Supply20」で変換された直流電圧を車載装置の有する各デバイス用に変換する「System Power Supply21」とを備える形態の一例である。以下では、「Primary Power Supply20」を「一次電源20」とも称し、「System Power Supply21」を「二次電源21」とも称する。

【0016】

20

バックアップ用電源を構成するキャパシタC1は、例えば、EDLC等のキャパシタであり、ダイオード素子D1は、ショットキーバリアダイオード等である。キャパシタC1は極性を有し、負極側は搭載される車両のGNDに接地され、正極側はダイオード素子D1のアノードに接続される。ダイオード素子D1のカソードは、二次電源21の入力端に接続される。二次電源21の入力端には、一次電源で変換された所定の直流電圧が印加される。図1に示すバックアップ用電源では、例えば、バッテリと一次電源20との間で断線が生じた場合や、一次電源20と二次電源21との間で断線が生じた場合には、キャパシタC1に充電された電力がダイオード素子D1を介し、定電圧の電力として二次電源21に供給される。

【0017】

30

（充電制御動作）

本実施形態に係る充電制御装置10には、少なくとも、スイッチングレギュレータ11と、インダクタ素子L1と、抵抗R1、R2とが含まれる。スイッチングレギュレータ11は、汎用的な電流モード型のスイッチングレギュレータである。スイッチングレギュレータ11は、「VIN」、「GND」、「OUT」、「FB」、「SS」、「COMP」の各端子を有する。

【0018】

スイッチングレギュレータ11のVIN端子は、一次電源20の出力端に接続され、GND端子は車両のGNDに接地される。また、スイッチングレギュレータ11のOUT端子は、一端がバックアップ用電源を構成するキャパシタC1のアノードに接続するインダクタ素子L1の他端に接続される。

40

【0019】

スイッチングレギュレータ11では、VIN端子に入力された一次電源20の供給電力がPWM（Pulse Width Modulation）方式で時分割され、該時分割された電力がOUT端子に出力される。OUT端子に出力された電力は、インダクタ素子L1を介してキャパシタC1に充電される。

【0020】

電流モード型のスイッチングレギュレータ11には、内部構成として、内部電流源11a、誤差アンプ（Error Amp）11b、スロープ補償ユニット11c、コンパレータ（PWM Comp）11d、PWM制御ユニット（PWM Control Logic）11e、スイッチング素子S

50

W1、SW2が含まれる。

【0021】

スイッチング素子SW1、SW2は、例えば、MOSFET (Metal-Oxide-Semiconductor Field-Effect-Transistor) 等の半導体デバイスである。図1においては、スイッチング素子SW1はP型のMOSFET、スイッチング素子SW2はN型のMOSFETで構成される。スイッチング素子SW1のソースはVIN端子に接続され、ドレインはスイッチング素子SW2のドレインに接続される。スイッチング素子SW2のソースはGND端子と接続する。スイッチング素子SW1、SW2のそれぞれのゲートは、PWM制御ユニット11eと接続する。

【0022】

PWM制御ユニット11eは、自身に接続するコンパレータ11dの出力値と、入力された所定周期のクロック信号(CLK)とに基づいて、スイッチング素子SW1、SW2のゲートのオン状態およびオフ状態を決定するゲート制御信号を生成する。ここで、オン状態とは、例えば、各スイッチング素子のゲート閾値電圧を超える電圧値である論理値H(例えば、5V)を示す状態であり、オフ状態とは、各スイッチング素子のゲート閾値電圧より小さい電圧値である論理値L(例えば、0V)を示す状態である。スイッチング素子SW1、SW2は、ゲート制御信号が、オン状態のときにソース-ドレイン間を導通し、オフ状態のときにソース-ドレイン間を解放する。

【0023】

スイッチングレギュレータ11は、PWM制御ユニット11eを介し、ゲート制御信号のオン状態の期間(以下、「オン期間」とも称す)、オフ状態の期間(以下、「オフ期間」とも称す)を制御することで、スイッチング素子SW1、SW2のスイッチング動作を制御する。

【0024】

電流モード型のスイッチングレギュレータ11では、誤差アンプ11b、スロープ補償ユニット11c、コンパレータ11dを介して、ゲート制御信号のオン・オフ状態、オン期間、オフ期間が決定される。

【0025】

スロープ補償ユニット11cは、スイッチング素子SW1、SW2のスイッチング動作時に、VIN端子とスイッチング素子SW1のソースとの間に流れる電流ISWのピーク値を検出する。そして、スロープ補償ユニット11cは、予め設定されたコンダクタンス(ゲイン値(Gcs))を用いて検出した電流ISWを電圧信号に変換する。

【0026】

スロープ補償ユニット11cは、電流ISWから変換された電圧信号と、オフセット電圧(Voffset)に基づいて、電流モード時のPWM制御の基準になるスロープ波形を生成する。なお、生成されたスロープ波形には、スロープ補償信号(Slope Compensation)が反映される。スロープ補償ユニット11cは、電流ISWから変換された電圧信号と、オフセット電圧(Voffset)に基づいて生成されたスロープ波形にスロープ補償信号(例えば、ランプ波)を反映することで、スイッチング動作時の電圧変化と電流変化の位相差による低調波発振を抑制する。

【0027】

スロープ補償ユニット11cは、スロープ補償信号が反映されたスロープ波形をコンパレータ11dの反転端子に出力する。なお、コンパレータ11dの非反転入力端子には、誤差アンプ11bの出力端子から出力された誤差信号が入力される。

【0028】

コンパレータ11dは、反転端子に入力されたスロープ波形の電圧値と、非反転端子に入力された誤差信号の電圧値との比較を行い、比較結果を出力端子に出力する。例えば、非反転入力端子に入力されたスロープ波形の電圧値が、反転端子に入力された誤差信号の電圧値よりも高い場合には、論理値Hのステータス信号が出力される。一方、非反転入力端子に入力されたスロープ波形の電圧値が、反転端子に入力された誤差信号の電圧値より

10

20

30

40

50

も低い場合には、論理値 L のステータス信号が出力される。

【0029】

コンパレータ 11d の出力端子に接続される PWM 制御ユニット 11e では、ステータス信号の論理値の状態、および、それぞれの論理値が継続する期間に基づいて、スイッチング素子 SW1、SW2 のスイッチング動作を制御するゲート制御信号が生成される。

【0030】

誤差アンプ 11b は、反転入力端子と、2つの非反転入力端子を備える誤差アンプである。誤差アンプ 11b の反転入力端子は、スイッチングレギュレータ 11 内では、負帰還入力端子である FB 端子に接続される。スイッチングレギュレータ 11 内において、誤差アンプ 11b の一方の非反転入力端子には基準電圧 VREF が接続し、他方の非反転入力端子には SS 端子が接続する。

【0031】

なお、SS 端子（ソフトスタート端子）に接続する内部電流源 11a は、スイッチングレギュレータ 11 の有するソフトスタート機能を機能させるための電源である。SS 端子にスイッチングレギュレータ 11 外で接続されるキャパシタ Ct の容量と内部電流源 11a から供給される電流量に応じて、ソフトスタート期間が決定される。誤差アンプ 11b の出力端子は、コンパレータ 11d の非反転入力端子および COMP 端子に接続される。

【0032】

本実施形態に係るスイッチングレギュレータ 11 においては、誤差アンプ 11b の出力電圧を、スイッチングレギュレータ 11 外で COMP 端子に接続された抵抗 R1、R2 を介して分圧し、該分圧された出力電圧をバイアス電圧として FB 端子にフィードバック入力させる。抵抗 R1、R2 は、分圧抵抗を構成する。分圧抵抗 R1 の一端は COMP 端子に接続され、他端は FB 端子に接続される。また、分圧抵抗 R1 の FB 端子に接続される他端は、一端が車両の GND に接地された分圧抵抗 R2 の他端に接続される。

【0033】

本実施形態に係るスイッチングレギュレータ 11 では、誤差アンプ 11b の反転入力端子には、FB 端子を介して、分圧抵抗 (R1、R2) で分圧された誤差アンプ 11b の出力電圧 (Vcomp) がフィードバック電圧として入力される。

【0034】

誤差アンプ 11b は、FB 端子に入力されたフィードバック電圧と、基準電圧 VREF との差電圧（誤差）を所定ゲイン (A) で増幅し、該増幅された差電圧を誤差信号として出力端子に出力する。スイッチングレギュレータ 11 の COMP 端子には、誤差アンプ 11b の出力電圧 (Vcomp) が出力される。

【0035】

ここで、COMP 端子に出力された出力電圧 (Vcomp) と、基準電圧 VREF との電圧関係は、次に示す式 (1) で表される。

【数1】

$$V_{comp} = \frac{R1+R2}{R2} \times V_{REF} \quad \dots \text{ (式1)}$$

(但し、A=\infty として計算)

【0036】

式 (1) に示すように、例えば、COMP 端子に接続される分圧抵抗 (R1、R2) の値を誤差アンプ 11b の所定ゲイン (A) と、基準電圧 VREF に応じて予め設定することで、分圧抵抗 (R1、R2) 値に応じた任意の電圧を誤差アンプ 11b の出力端子に出力することが可能になる。

【0037】

既述したように、スイッチングレギュレータ 11 においては、コンパレータ 11d の反

10

20

30

40

50

転端子に入力されたスロープ波形の電圧値と、非反転端子に入力された誤差アンプ 11 b の出力電圧値との比較結果により、ゲート制御信号が生成される。このため、本実施形態に係る充電制御装置 10 では、スイッチングレギュレータ 11 の誤差アンプ 11 b の出力電圧 (V<sub>comp</sub>) を制御することで、例えば、スイッチング素子 SW 1 のオン期間に導通されるソース - ドレイン間に流れる電流 I<sub>SW</sub> を制御できる。

【0038】

ここで、電流 I<sub>SW</sub> と、誤差アンプ 11 b の出力電圧 (V<sub>comp</sub>) との関係は、次に示す式 (2) で表される。

【数2】

$$I_{SW}(\text{peak}) = G_{CS} \times (V_{comp} - V_{offset}) \quad \dots \text{(式2)}$$

10

※ I<sub>SW</sub>(peak) = I<sub>SW</sub> のリップル電流のピーカー値

【0039】

式 (2) に示すように、本実施形態に係る充電制御装置 10 は、スイッチングレギュレータ 11 のスイッチング素子 SW 1 のオン期間にソース - ドレイン間に流れ込む電流 I<sub>SW</sub> の値を、基準電圧 V<sub>REF</sub> と分圧抵抗 (R<sub>1</sub>、R<sub>2</sub>) 値とに応じた定電流値に制御できる。充電制御装置 10 のスイッチングレギュレータ 11 は、基準電圧 V<sub>REF</sub> の精度に応じた電流 I<sub>SW</sub> をキャパシタ C<sub>1</sub> に供給できる。本実施形態に係る充電制御装置 10 によれば、流通量が多い汎用のスイッチングレギュレータを用いて、キャパシタに供給される充電電流を一定値に制御しながら充電することができる。

20

【0040】

また、スイッチングレギュレータ 11 に付加される付加回路は、COMP 端子から出力される誤差アンプ 11 b の出力電圧 (V<sub>comp</sub>) を分圧する分圧抵抗 (R<sub>1</sub>、R<sub>2</sub>) で構成される。このため、本実施形態に係る充電制御装置 10 を備えるドライブレコーダ等の車載装置においては、小型化、低コスト化が可能になる。

【0041】

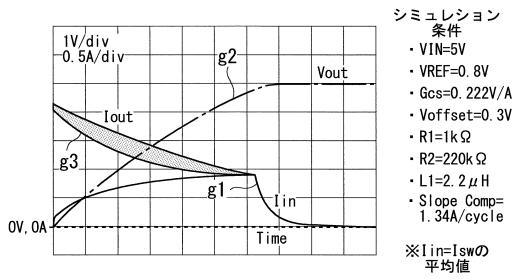

(充電電流特性)

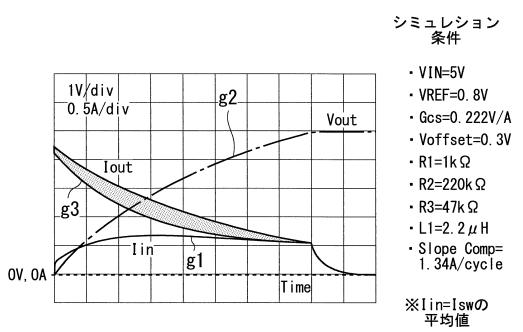

図 2 に、スイッチングレギュレータ 11 の充電電流特性を例示する。図 2 の充電電流特性は、VIN 端子の入力電圧を「5 V」、基準電圧 V<sub>REF</sub> を「0.8 V」、ゲイン値 (G<sub>CS</sub>) を「0.222 V/A」、オフセット電圧 (V<sub>offset</sub>) を「0.3 V」、スロープ補償信号を「1.34 A/cycle」、分圧抵抗 R<sub>1</sub> を「1 k」、分圧抵抗 R<sub>2</sub> を「220 k」、インダクタ素子 L<sub>1</sub> を「2.2 μH」として、図 1 に示す充電制御装置 10 のシミュレーション解析を行った結果である。ゲイン値 (G<sub>CS</sub>) は、スイッチングレギュレータ 11 における、スイッチング素子 SW 1 のオン時のインピーダンス R<sub>on</sub> を「100 m」、インダクタ素子 L<sub>1</sub> のインピーダンス DCR を「140 m」とした場合のゲイン値である。

30

【0042】

図 2において、グラフ g<sub>1</sub> は、スイッチング素子 SW 1、SW 2 のスイッチング動作時に、VIN 端子とスイッチング素子 SW 1 のソースとの間に流れる電流 I<sub>SW</sub> の平均値 (I<sub>in</sub>) の時間変化を表す。同様にして、グラフ g<sub>2</sub> は、キャパシタ C<sub>1</sub> の充電電圧値 (V<sub>out</sub>) の時間変化を表し、グラフ g<sub>3</sub> は、インダクタ素子 L<sub>1</sub> を介してキャパシタ C<sub>1</sub> に供給される電流値 (I<sub>out</sub>) の時間変化を表す。なお、図 2 の縦軸は電流値 (0.5 A/div)、電圧値 (1 V/div) を表し、横軸は正規化された時間経過を表す。横軸に平行する破線は、図 2 における 0 V 基準、0 A 基準を表す。

40

【0043】

グラフ g<sub>2</sub> に示すように、キャパシタ C<sub>1</sub> の充電電圧値 (V<sub>out</sub>) は、スイッチング動作の開始時から時間経過に伴って緩やかに上昇するように変化し、キャパシタ C<sub>1</sub> の充電容量で定められる一定電圧値に到達する。また、グラフ g<sub>1</sub> に示すように、スイッチ

50

グ動作時にスイッチングレギュレータ 11 に流れ込む電流値 (  $I_{in}$  ) は、スイッチング動作の開始時から時間経過に伴って緩やかに上昇し、0.9 A から 1.0 A の範囲内で一定状態に到達する。グラフ g 1 とグラフ g 2 の相対的な時間変化から、キャパシタ C 1 の満充電容量近傍で、スイッチングレギュレータ 11 に流れ込む電流値 (  $I_{in}$  ) は、0.9 A から 1.0 A の範囲内の一定状態に到達することが判る。図 1 に示す充電制御装置 10 は、スイッチングレギュレータ 11 に流れ込む電流値 (  $I_{in}$  ) をキャパシタ C 1 の充電容量に応じた一定状態に抑制しつつ、充電動作を行うことが判る。

#### 【 0 0 4 4 】

また、グラフ g 3 に示すように、スイッチングレギュレータ 11 のスイッチング動作に伴ってキャパシタ C 1 に供給される電流値 (  $I_{out}$  ) は、スイッチング動作の開始時から時間経過に伴って緩やかに減少し、0.9 A から 1.0 A の範囲内で一定状態に到達する。なお、グラフ g 3 のハッチングされた領域は、スイッチング素子 SW 1、SW 2 のスイッチング動作に伴って脈動する電流値 (  $I_{out}$  ) の変化幅を表す。

#### 【 0 0 4 5 】

スイッチングレギュレータ 11 のスイッチング動作に伴う電流値 (  $I_{out}$  ) は、キャパシタ C 1 の充電容量に応じて一定状態に到達した電流値 (  $I_{in}$  ) と同値になるよう時間変化することが判る。図 1 に示す充電制御装置 10 は、スイッチング動作の開始時には 2 A を超える電流値 (  $I_{out}$  ) をキャパシタ C 1 に供給しつつ、充電量 ( 充電電圧値 (  $V_{out}$  ) ) の増加に従って電流値 (  $I_{out}$  ) を減少させながら充電動作することが判る。

#### 【 0 0 4 6 】

##### 〔 実施例 2 〕 ( ブロック構成 )

実施例 1 で説明した充電制御装置 10 の形態は、車両の GND に接地された分圧抵抗 ( R 1、R 2 ) を介して、COMP 端子に出力される出力電圧 (  $V_{comp}$  ) をバイアス電圧として FB 端子に入力する形態である。充電制御装置 10 においては、COMP 端子に出力される出力電圧 (  $V_{comp}$  ) を、電源側にプルアップされた分圧抵抗 ( R 1、R 2 ) を介して分圧し、該分圧された電圧をバイアス電圧として FB 端子に入力するとしてもよい。

#### 【 0 0 4 7 】

分圧抵抗 ( R 1、R 2 ) が電源側にプルアップされた形態では、COMP 端子から出力される出力電圧値を、基準電圧 VREF より低い電圧値に設定することが可能になる。充電制御装置 10 は、基準電圧 VREF より低い電圧値に設定された出力電圧値に基づきスイッチング動作を行うことで、図 1 に示す充電制御装置 10 の形態と比較して、スイッチング動作時にスイッチングレギュレータ 11 に流れ込む電流値 (  $I_{in}$  ) の大きさを相対的に抑制できる。実施例 2 の形態では、車載装置側の電力供給能力への負荷を軽減する充電制御装置 10 が提供可能になる。

#### 【 0 0 4 8 】

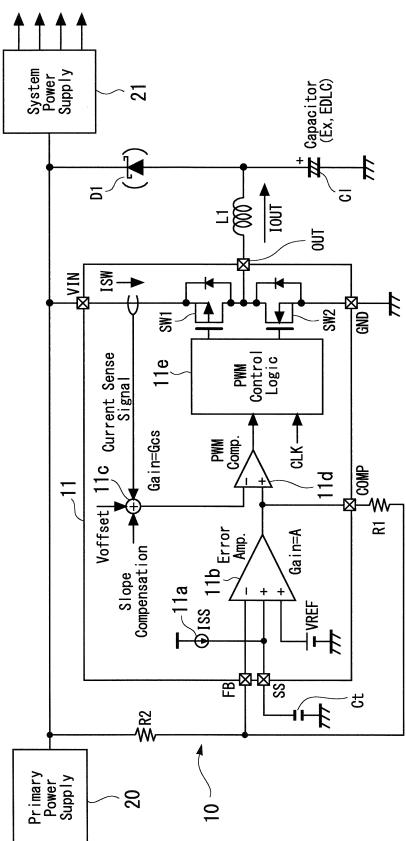

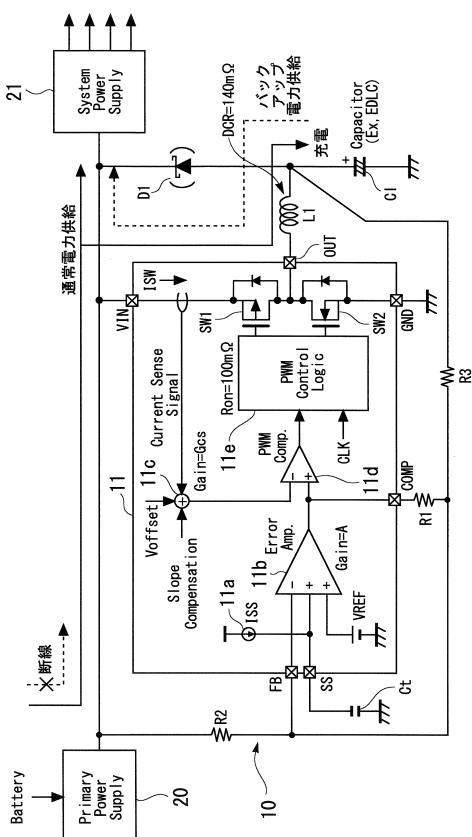

図 3 は、実施例 2 ( 以下、「本実施形態」とも称する ) に係る充電制御装置 10 のブロック構成の一例を示す図である。図 3 に示す充電制御装置 10 の形態は、COMP 端子に出力される出力電圧 (  $V_{comp}$  ) を、一次電源 20 側にプルアップされた分圧抵抗 ( R 1、R 2 ) を介して、FB 端子にフィードバック入力させる形態である。

#### 【 0 0 4 9 】

分圧抵抗 R 1 の一端は COMP 端子に接続され、他端は FB 端子に接続される。また、分圧抵抗 R 1 の FB 端子に接続される他端は、一端が一次電源 20 側にプルアップ接続された分圧抵抗 R 2 の他端に接続される。なお、図 3 に示すブロック構成においては、分圧抵抗 ( R 1、R 2 ) 以外の構成は、図 1 と同様の構成である。以下、図 1 と相違する構成を主として本実施形態の充電制御装置 10 の充電制御動作を説明する。

#### 【 0 0 5 0 】

##### ( 充電制御動作 )

図 3 に示す形態の、スイッチングレギュレータ 11 においては、誤差アンプ 11b の反

10

20

30

40

50

転入力端子には、一次電源 20 側にプルアップ接続された分圧抵抗 (R1、R2) を介して分圧された誤差アンプ 11b の出力電圧 (Vcomp) がフィードバック電圧として入力される。

【0051】

誤差アンプ 11b は、FB 端子に入力されたフィードバック電圧と、基準電圧 VREF との差電圧 (誤差) を所定ゲイン (A) で増幅し、該増幅された差電圧を誤差信号として出力端子に出力する。スイッチングレギュレータ 11 の COMP 端子には、誤差アンプ 11b の出力電圧 (Vcomp) が出力される。

【0052】

実施例 2 の形態では、COMP 端子に出力された出力電圧 (Vcomp) と、基準電圧 VREF との電圧関係は、次に示す式 (3) で表される。 10

【数 3】

$$V_{comp} = V_{REF} - \frac{R1}{R2} \times (V_{IN} - V_{REF}) \quad \dots \text{式3}$$

(但し、A=∞として計算)

【0053】

実施例 2 の形態においても、COMP 端子に接続される分圧抵抗 (R1、R2) の値を誤差アンプ 11b の所定ゲイン (A)、基準電圧 VREF、一次電源 20 側の電圧に応じて予め設定することで、分圧抵抗 (R1、R2) 値に応じた任意の電圧を誤差アンプ 11b の出力端子に出力することが可能になる。充電制御装置 10 は、スイッチングレギュレータ 11 の誤差アンプ 11b の出力電圧 (Vcomp) を制御することで、スイッチング素子 SW1 のオン期間に導通されるソース - ドレイン間に流れる電流 ISW を制御することができる。 20

【0054】

実施例 1 と同様に、電流 ISW と、誤差アンプ 11b の出力電圧 (Vcomp) との関係は、次に示す式 (4) で表される。

【数 4】

$$ISW(\text{peak}) = G_{CS} \times (V_{comp} - V_{offset}) \quad \dots \text{式4}$$

※ISW(peak)=ISWのリップル電流のピーカー値

【0055】

式 (4) に示すように、実施例 2 の形態においても充電制御装置 10 は、スイッチングレギュレータ 11 のスイッチング素子 SW1 のオン期間にソース - ドレイン間に流れ込む電流 ISW の値を、基準電圧 VREF と、電源側にプルアップされた分圧抵抗 (R1、R2) 値に応じた定電流値に制御できる。充電制御装置 10 のスイッチングレギュレータ 11 は、基準電圧 VREF の精度に応じた電流 ISW をキャパシタ C1 に供給できる。実施例 2 の充電制御装置 10 においても、流通量が多い汎用のスイッチングレギュレータを用いて、キャパシタに充電される電流を制御しながら急速充電可能な充電回路が提供可能になる。 40

【0056】

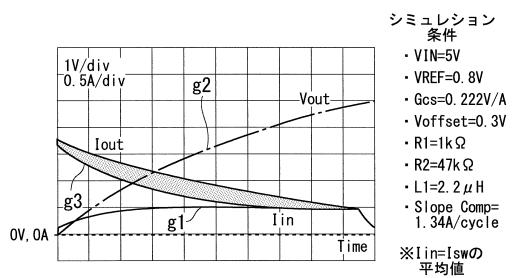

(充電電流特性)

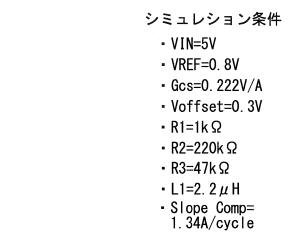

図 4 に、スイッチングレギュレータ 11 の充電電流特性を例示する。図 4 の充電電流特性は、VIN 端子の入力電圧を「5V」、基準電圧 VREF を「0.8V」、ゲイン値 (GCS) を「0.222V/A」、オフセット電圧 (Voffset) を「0.3V」、スロープ補償信号を「1.34A/cycle」、分圧抵抗 R1 を「1k」、分圧抵抗 R2 を 50

「47k」、インダクタ素子L1を「2.2μH」として、図3に示す充電制御装置10のシミュレーション解析を行った結果である。ゲイン値(Gcs)は、図2と同様である。

【0057】

図4の、グラフg1は、スイッチング素子SW1、SW2のスイッチング動作時に、VIN端子とスイッチング素子SW1のソースとの間に流れる電流ISWの平均値(Iin)の時間変化を表す。グラフg2は、キャパシタC1の充電電圧値(Vout)の時間変化を表し、グラフg3は、インダクタ素子L1を介してキャパシタC1に供給される電流値(Iout)の時間変化を表す。図4の縦軸は電流値(0.5A/div)、電圧値(1V/div)を表し、横軸は正規化された時間経過を表し、横軸に平行な破線は、0V基準、0A基準を表す。 10

【0058】

図4に示すグラフg1、g2、g3の時間変化傾向は、実施例1と同様の変化傾向を示す。但し、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(Iin)は、0.5A近傍で一定状態に到達する。また、スイッチング動作の開始時のキャパシタC1に供給される電流値(Iout)は、1.75A近傍に低下する。

【0059】

図2に示すグラフg1からg3の時間変化傾向と、図4に示すグラフg1からg3の時間変化傾向とを比較した場合、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(Iin)、キャパシタC1に供給される電流値(Iout)の相対的な大きさが抑制されることが判る。但し、キャパシタC1に供給される電流値(Iout)が相対的に減少した分、キャパシタC1の充電に係る期間が相対的に長くなる傾向になる。 20

【0060】

〔実施例3〕(ブロック構成)

図5は、実施例3(以下、「本実施形態」とも称する)に係る充電制御装置10のブロック構成の一例を示す図である。図5に示す充電制御装置10は、実施例1で説明した充電制御装置10の形態に対して、さらに、キャパシタC1に充電された充電電圧(Vout)をフィードバック量として反映させる形態である。

【0061】

本実施形態の充電制御装置10においては、少なくとも、スイッチングレギュレータ11と、インダクタ素子L1と、抵抗R1、R2、R3とが含まれる。抵抗R1、R2、R3は、分圧抵抗を構成する。図5に示すブロック構成においては、分圧抵抗(R1、R2、R3)以外の構成は、図1と同様の構成である。 30

【0062】

分圧抵抗R1の一端はCOMP端子に接続され、他端はFB端子に接続される。分圧抵抗R1のFB端子に接続される他端は、一端が車両のGNDに接地された分圧抵抗R2の他端に接続される。分圧抵抗R3の一端は、キャパシタC1の正極側端子に接続され、他端は分圧抵抗R1のFB端子に接続する他端に接続される。

【0063】

実施例3の充電制御装置10においては、キャパシタC1の充電電圧(Vout)を、分圧抵抗R3を介して誤差アンプ11bの反転端子に負帰還入力させることで、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(Iin)をキャパシタC1の充電状態に応じて制御することが可能になる。例えば、本実施形態の充電制御装置10を備えるドライブレコーダ等の車載装置においては、一次電源20の電流容量やバッテリの供給可能な電流量に制約がある場合に、該制約された電流量に従って、スイッチング動作時のスイッチングレギュレータ11に流れ込む電流値(Iin)の調整が可能になる。以下、図1と相違する構成を主として本実施形態の充電制御装置10の充電制御動作を説明する。 40

【0064】

(充電制御動作)

図5に示す形態の、スイッチングレギュレータ11においては、誤差アンプ11bの反転入力端子には、分圧抵抗R3を介して分圧されたキャパシタC1の充電電圧(Vout)と分圧抵抗(R1、R2)で分圧された誤差アンプ11bの出力電圧(Vcomp)がフィードバック電圧として入力される。

【0065】

誤差アンプ11bは、FB端子に入力されたフィードバック電圧と、基準電圧VREFとの差電圧(誤差)を所定ゲイン(A)で増幅し、該増幅された差電圧を誤差信号として出力端子に出力する。スイッチングレギュレータ11のCOMP端子には、誤差アンプ11bの出力電圧(Vcomp)が出力される。

【0066】

実施例3の形態では、COMP端子に出力された出力電圧(Vcomp)と、基準電圧VREFとの電圧関係は、次に示す式(5)で表される。

【数5】

$$V_{comp} = V_{REF} + R1 \times \left( \frac{V_{REF}}{R2} - \frac{V_{out} - V_{REF}}{R3} \right) \quad \cdots \text{(式5)}$$

(但し、A=∞として計算)

【0067】

式(5)に示すように、分圧抵抗(R1、R2、R3)の各値を誤差アンプ11bの所定ゲイン(A)に応じて予め設定することで、キャパシタC1の充電電圧(Vout)に応じた電圧を誤差アンプ11bの出力端子に出力することが可能になる。充電制御装置10は、スイッチングレギュレータ11の誤差アンプ11bの出力電圧(Vcomp)を制御することで、スイッチング素子SW1のオン期間に導通されるソース-ドレイン間に流れる電流ISWの制御にキャパシタC1の充電電圧(Vout)を反映することが可能になる。

【0068】

実施例1と同様に、電流ISWと、COMP端子に出力された出力電圧(Vcomp)との関係は、次に示す式(6)で表される。

【数6】

$$ISW(\text{peak}) = G_{cs} \times (V_{comp} - V_{offset}) \quad \cdots \text{(式6)}$$

※ISW(peak)=ISWのリップル電流のピーカー値

【0069】

式(6)に示すように、本実施形態の充電制御装置10は、スイッチングレギュレータ11のスイッチング素子SW1のオン期間にソース-ドレイン間に流れ込む電流ISWの値を、基準電圧VREFと分圧抵抗(R1、R2、R3)値に応じた定電流値に制御できる。

【0070】

(充電電流特性)

図6は、本実施形態の充電制御装置10による充電電流特性の一例を示す図である。図6の充電電流特性は、VIN端子の入力電圧を「5V」、基準電圧VREFを「0.8V」、ゲイン値(Gcs)を「0.222V/A」、オフセット電圧(Voffset)を「0.3V」、スロープ補償信号を「1.34A/cycle」、分圧抵抗R1を「1k」、分圧抵抗R2を「220k」、分圧抵抗R3を「47k」、インダクタ素子L1を「2.2μH」として、図5に示す充電制御装置10のシミュレーション解析を行った結果である。ゲイン値(Gcs)は、図2と同様である。

10

20

30

40

50

## 【0071】

図6の、グラフg1は、スイッチング素子SW1、SW2のスイッチング動作時に、VIN端子とスイッチング素子SW1のソースとの間に流れる電流ISWの平均値(Iin)の時間変化を表す。グラフg2は、キャパシタC1の充電電圧値(Vout)の時間変化を表し、グラフg3は、インダクタ素子L1を介してキャパシタC1に供給される電流値(Iout)の時間変化を表す。図6の縦軸は電流値(0.5A/div)、電圧値(1V/div)を表し、横軸は正規化された時間経過を表し、横軸に平行な破線は、0V基準、0A基準を表す。

## 【0072】

グラフg1に示すように、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(Iin)は、スイッチング動作の開始時から時間経過に伴って緩やかに上昇変化して0.7A程度の最大値に到達する。上記最大値に到達後の電流値(Iin)は、0.7Aから0.5Aの範囲において一定状態、あるいは、時間経過に伴って微小に減少変化するように推移する。

10

## 【0073】

グラフg1とグラフg2の相対的な時間変化から、キャパシタC1の充電状態が満充電容量の粗半分付近で、電流値(Iin)が最大値に到達することが判る。また、図2に示すグラフg1の時間変化傾向と、図4に示すグラフg1の時間変化傾向とを比較した場合、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(Iin)の相対的な大きさが抑制されていることが判る。また、キャパシタC1に供給される電流値(Iout)が相対的に減少した分、キャパシタC1の充電に係る期間が相対的に長くなる傾向にあることが判る。なお、図6に示すグラフg2、g3の時間変化傾向は、実施例1と同様の変化傾向を示す。

20

## 【0074】

本実施形態の充電制御装置10においては、一次電源20の電流容量やバッテリの供給可能な電流量に制約がある場合に、充電時のスイッチングレギュレータ11に流れ込む電流値(Iin)の最大値を充電状態に応じて抑制しつつ、キャパシタC1を充電することが可能になる。

## 【0075】

## 〔実施例4〕(ブロック構成)

30

図7は、実施例4(以下、「本実施形態」とも称する)に係る充電制御装置10のブロック構成の一例を示す図である。図7に示す充電制御装置10は、実施例2で説明した充電制御装置10の形態に対して、さらに、キャパシタC1に充電された充電電圧(Vout)をフィードバック量として反映させる形態である。

## 【0076】

図7に示す充電制御装置10は、少なくとも、スイッチングレギュレータ11と、インダクタ素子L1と、分圧抵抗を構成する抵抗R1、R2、R3とを含む。分圧抵抗R1の一端はCOMP端子に接続され、他端はFB端子に接続される。分圧抵抗R1のFB端子に接続される他端は、一端が一次電源20側にプルアップ接続された分圧抵抗R2の他端に接続される。分圧抵抗R3の一端は、キャパシタC1の正極側端子に接続され、他端は分圧抵抗R1のFB端子に接続する他端に接続される。図7に示すブロック構成においては、分圧抵抗(R1、R2、R3)以外の構成は、図3と同様の構成である。以下、図3と相違する構成を主として本実施形態の充電制御装置10の充電制御動作を説明する。

40

## 【0077】

## (充電制御動作)

実施例4の充電制御装置10においては、キャパシタC1の充電電圧(Vout)を、分圧抵抗R3を介して誤差アンプ11bの反転端子に負帰還入力することで、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(Iin)をキャパシタC1の充電状態に応じて制御することが可能になる。

## 【0078】

50

図7に示す形態の、スイッチングレギュレータ11においては、誤差アンプ11bの反転入力端子には、分圧抵抗R3を介して分圧されたキャパシタC1の充電電圧(Vout)と、一次電源20側にプルアップ接続された分圧抵抗(R1、R2)で分圧された誤差アンプ11bの出力電圧(Vcomp)がフィードバック電圧として入力される。

## 【0079】

誤差アンプ11bは、FB端子に入力されたフィードバック電圧と、基準電圧VREFとの差電圧(誤差)を所定ゲイン(A)で増幅し、該増幅された差電圧を誤差信号として出力端子に出力する。スイッチングレギュレータ11のCOMP端子には、誤差アンプ11bの出力電圧(Vcomp)が出力される。

## 【0080】

実施例4の形態では、COMP端子に出力された出力電圧(Vcomp)と基準電圧VREFとの電圧関係、および、電流ISWと、誤差アンプ11bの出力電圧(Vcomp)との関係は、次に示す式(7)で表される。また、

## 【数7】

$$V_{comp} = V_{REF} - R1 \times \left( \frac{V_{IN} - V_{REF}}{R2} - \frac{V_{out} - V_{REF}}{R3} \right)$$

(但し、 $A=\infty$ として計算)

…(式7)

$$ISW(\text{peak}) = G_{cs} \times (V_{comp} - V_{offset})$$

※ISW(peak)=ISWのリプル電流のピーカー値

## 【0081】

実施例4の形態においても、分圧抵抗(R1、R2、R3)の各値を誤差アンプ11bの所定ゲイン(A)、基準電圧VREF、一次電源20側の電圧に応じて予め設定することで、キャパシタC1の充電電圧(Vout)に応じた電圧を誤差アンプ11bの出力端子に出力することが可能になる。

## 【0082】

充電制御装置10は、スイッチングレギュレータ11の誤差アンプ11bの出力電圧(Vcomp)を制御することで、スイッチング素子SW1のオン期間に導通されるソース-ドレイン間に流れる電流ISWの制御にキャパシタC1の充電電圧(Vout)を反映することができる。充電制御装置10は、スイッチングレギュレータ11のスイッチング素子SW1のオン期間にソース-ドレイン間に流れ込む電流ISWの値を、基準電圧VREFと分圧抵抗(R1、R2、R3)値に応じた定電流値に制御できる。

## 【0083】

(充電電流特性)

図8は、本実施形態の充電制御装置10による充電電流特性の一例を示す図である。図8(1)の充電電流特性は、VIN端子の入力電圧を「5V」、基準電圧VREFを「0.8V」、ゲイン値(Gcs)を「0.222V/A」、オフセット電圧(Voffset)を「0.3V」、スロープ補償信号を「1.34A/cycle」、分圧抵抗R1を「1k」、分圧抵抗R2を「220k」、分圧抵抗R3を「47k」、インダクタ素子L1を「2.2μH」として、図7に示す充電制御装置10のシミュレーション解析を行った結果である。また、図8(2)の充電電流特性は、上記の各種条件において分圧抵抗R3を無限大とした場合の、シミュレーション解析結果である。ゲイン値(Gcs)は、図2と同様である。

## 【0084】

図8(1)、(2)の、グラフg1は、スイッチング素子SW1、SW2のスイッチ

10

20

30

40

50

グ動作時に、V IN 端子とスイッチング素子 SW 1 のソースとの間に流れる電流 I SW の平均値 (I in) の時間変化を表す。グラフ g 2 は、キャパシタ C 1 の充電電圧値 (V out) の時間変化を表し、グラフ g 3 は、インダクタ素子 L 1 を介してキャパシタ C 1 に供給される電流値 (I out) の時間変化を表す。図 8 (1)、(2) の縦軸は電流値 (0.5 A / div)、電圧値 (1 V / div) を表し、横軸は正規化された時間経過を表し、横軸に平行な破線は、0 V 基準、0 A 基準を表す。

#### 【0085】

図 8 (1) に示すように、分圧抵抗 R 3 を「47 k」とした場合には、電流値 (I in) の最大値が 0.4 A 程度になるため、充電期間がスケールアウトする。実施例 4 における各グラフの時間変化傾向を特定するため、分圧抵抗 R 3 を無限大としてシミュレーション解析を行った。この結果、図 8 (2) に示すように、グラフ g 1、g 2、g 3 の時間変化傾向は、実施例 3 と同様の変化傾向を示すことが確認された。

10

#### 【0086】

図 8 (2) においては、スイッチング動作時にスイッチングレギュレータ 11 に流れ込む電流値 (I in) は、スイッチング動作の開始時から時間経過に伴って緩やかに上昇変化して 0.6 A 程度の最大値に到達する。上記最大値に到達後の電流値 (I in) は、実施例 3 と同様に、0.6 A から 0.5 A の範囲において一定状態、あるいは、時間経過に伴って微小に減少変化するように推移することが確認された。グラフ g 1 とグラフ g 2 の相対的な時間変化から、キャパシタ C 1 の充電状態が満充電容量の粗半分付近で、電流値 (I in) が最大値に到達することが確認された。また、図 8 (1) に示すグラフ g 1 と、図 8 (2) に示すグラフ g 1 との時間変化傾向の比較から、電流値 (I in) は分圧抵抗 R 3 の大小関係に応じて増減することが判る。

20

#### 【0087】

本実施形態の充電制御装置 10 は、実施例 3 と同様に、一次電源 20 の電流容量やバッテリの供給可能な電流量に制約がある場合に、充電時のスイッチングレギュレータ 11 に流れ込む電流値 (I in) の最大値を充電状態に応じて抑制しつつ、キャパシタ C 1 を充電することが可能になる。

#### 【0088】

##### 〔実施例 5〕(ブロック構成)

図 9 は、実施例 5 (以下、「本実施形態」とも称する) に係る充電制御装置 10 のブロック構成の一例を示す図である。本実施形態においては、充電制御装置 10 は、SS 端子に、スイッチングレギュレータ 11 外からバイアス電圧 V ss を印加する。そして、本実施形態に係る充電制御装置 10 は、バイアス電圧 V ss と FB 端子に入力されるフィードバック電圧とに基づいて、キャパシタ C 1 に定電流を供給する電流制御を行う。本実施形態に係る充電制御装置 10 においては、キャパシタ C 1 の充電電圧 (V out) に依存しないスイッチングレギュレータ 11 の定電流制御が提供される。

30

#### 【0089】

図 9 に示す充電制御装置 10 は、少なくとも、スイッチングレギュレータ 11 と、インダクタ素子 L 1 と、バイアス電圧 V ss を印加するユニット (以下、単に「バイアス電圧 V ss」とも称す) と、抵抗 R sen とを含む。

40

#### 【0090】

バイアス電圧 V ss は、例えば、スイッチングレギュレータ 11 の SS 端子に接続し、所定のバイアス電圧 V ss を印加するユニットである。抵抗 R sen は、一端を FB 端子と接続する抵抗デバイスである。本実施形態では、抵抗 R sen は、バックアップ用電源を構成するキャパシタ C 1 の負極側端子と GND との間に設けられる。FB 端子と接続する抵抗 R sen の他端は、車両の GND に接地される。本実施形態では、抵抗 R sen を介して、キャパシタ C 1 の負極側端子と GND との間の電位差がフィードバック電圧として検出される。

#### 【0091】

既に説明したように、キャパシタ C 1 は、車載装置の受電部に設けられたバックアップ

用電源の一部を構成する。抵抗  $R_{sen}$  を用いて、キャパシタ  $C_1$  の負極側端子と GND との間の電位差を FB 端子に負帰還入力させる場合には、抵抗  $R_{sen}$ 、ダイオード素子  $D_1$  を含めて、キャパシタ  $C_1$  に充電された電力がバックアップ供給されることになる。このため、キャパシタ  $C_1$  の負極側端子と GND との間の電位差をフィードバック電圧として検出する抵抗  $R_{sen}$  の抵抗値は、できる限り小さいことが好ましい。抵抗  $R_{sen}$  の抵抗値を小さくすることで、バックアップ動作時における電力の負荷損失を減らすことができる。

#### 【0092】

なお、スイッチングレギュレータ 11 の COMP 端子は、抵抗  $R_t$  とキャパシタ  $C_t$  1 を介して車両の GND に接地される。スイッチングレギュレータ 11 においては、COMP 端子に接続する抵抗  $R_t$  の値とキャパシタ  $C_t$  1 の値から決定される時定数に基づいて、スイッチング動作時のスイッチング帯域が制限される。スイッチング帯域が制限されることにより、例えば、スイッチング動作時の電圧変化と電流変化の位相差による低調波発振が抑制される。

#### 【0093】

図 9 に示すブロック構成においては、バイアス電圧  $V_{ss}$  と抵抗  $R_{sen}$  以外の構成は、図 1 と同様の構成である。以下、図 1 と相違する構成を主として本実施形態の充電制御装置 10 の充電制御動作を説明する。

#### 【0094】

##### (充電制御動作)

20

スイッチングレギュレータ 11 外で SS 端子に接続されたバイアス電圧  $V_{ss}$  は、誤差アンプ 11b の非反転入力端子に入力される。また、抵抗  $R_{sen}$  を介して検出された、キャパシタ  $C_1$  の負極側端子と GND との間の電位差は、FB 端子を介して誤差アンプ 11b の反転入力端子に入力される。なお、既に説明したように、誤差アンプ 11b の 2 つの非反転入力端子の内、バイアス電圧  $V_{ss}$  が入力される非反転入力端子以外の非反転入力端子には、基準電圧  $V_{REF}$  が入力される。

#### 【0095】

誤差アンプ 11b の動作では、2 つの非反転入力端子に入力された電圧値の内、相対的に低い電圧値の非反転入力端子が優先される。ここで、基準電圧  $V_{REF}$  の電圧値は、0.6V から 1.0V 程度に設定される。従って、スイッチングレギュレータ 11 外で SS 端子に接続されたバイアス電圧  $V_{ss}$  の電圧値を上記基準電圧  $V_{REF}$  未満に設定することで、FB 端子に入力されたフィードバック電圧と SS 端子に入力されたバイアス電圧  $V_{ss}$  との間の差電圧（誤差）に基づく誤差アンプ 11b の動作が可能になる。

30

#### 【0096】

誤差アンプ 11b は、FB 端子に入力されたフィードバック電圧と、バイアス電圧  $V_{ss}$  との差電圧（誤差）を所定ゲイン（A）で増幅し、該増幅された差電圧を誤差信号として出力端子に出力する。

#### 【0097】

本実施形態においても、スイッチングレギュレータ 11 は、コンパレータ 11d の反転端子に入力されたスロープ波形の電圧値と、非反転端子に入力された誤差アンプ 11b の出力電圧値との比較結果に基づいて、ゲート制御信号を生成する。本実施形態においても、充電制御装置 10 は、スイッチングレギュレータ 11 の誤差アンプ 11b の出力電圧を制御することで、例えば、スイッチング動作時にインダクタ素子  $L_1$  を介してキャパシタ  $C_1$  に供給される電流を制御できる。

40

#### 【0098】

ここで、インダクタ素子  $L_1$  を介してキャパシタ  $C_1$  に供給される電流（ $I_{out}$ ）の電流平均値（ $I_{avg}$ ）と、バイアス電圧  $V_{ss}$ 、抵抗  $R_{sen}$  との関係は、次に示す式（8）で表される。

【数8】

$$I_{chg} = V_{ss} \div R_{sen} \quad \dots \text{式8}$$

※  $I_{chg} = I_{OUT}$  のリップルを除いた平均値。

【0099】

式(8)に示すように、本実施形態に係る充電制御装置10は、スイッチング動作時にインダクタ素子L1を介してキャパシタC1に供給される電流平均値( $I_{chg}$ )を、バイアス電圧 $V_{ss}$ と抵抗 $R_{sen}$ とに応じた定電流値に制御できる。

10

【0100】

なお、キャパシタC1の負極側端子とGNDとの間に設けられる抵抗 $R_{sen}$ の抵抗値は、上述したように、バックアップ動作時における電力の負荷損失を抑制するために、できる限り小さいことが好ましい。例えば、抵抗 $R_{sen}$ とバイアス電圧 $V_{ss}$ の設定例として、抵抗 $R_{sen}$ の抵抗値を「68m」、バイアス電圧 $V_{ss}$ の電圧値を「0.1V」とすることが提示できる。

【0101】

(充電電流特性)

図10は、本実施形態の充電制御装置10による充電電流特性の一例を示す図である。図10の充電電流特性は、VIN端子の入力電圧を「5V」、バイアス電圧 $V_{ss}$ を「0.1V」、抵抗 $R_{sen}$ を「68m」、インダクタ素子L1を「2.2μH」として、図9に示す充電制御装置10のシミュレーション解析を行った結果である。

20

【0102】

図10の、グラフg1は、スイッチング素子SW1、SW2のスイッチング動作時に、VIN端子とスイッチング素子SW1のソースとの間に流れる電流 $I_{SW}$ の平均値( $I_{in}$ )の時間変化を表す。グラフg2は、キャパシタC1の充電電圧値( $V_{out}$ )の時間変化を表し、グラフg3は、インダクタ素子L1を介してキャパシタC1に供給される電流値( $I_{out}$ )の時間変化を表す。図10の縦軸は電流値(0.5A/div)、電圧値(1V/div)を表し、横軸は正規化された時間経過を表し、横軸に平行な破線は、0V基準、0A基準を表す。

30

【0103】

グラフg2に示すように、キャパシタC1の充電電圧値( $V_{out}$ )は、スイッチング動作の開始時から時間経過に伴って緩やかに上昇するように変化し、キャパシタC1の充電容量で定められる一定電圧値に到達する。また、グラフg3に示すように、キャパシタC1に供給される電流値( $I_{out}$ )の時間変化は、一定状態で推移する。電流値( $I_{out}$ )は、式(8)で表される関係式で求められる電流平均値( $I_{chg}$ )が、1.5A近傍を中心として推移することが判る。

【0104】

グラフg2とグラフg3の相対的な時間変化から、キャパシタC1に供給される電流値( $I_{out}$ )は、キャパシタC1の充電電圧値( $V_{out}$ )に依存せずに一定状態で推移することが判る。なお、グラフg1に示すように、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値( $I_{in}$ )は、スイッチング動作の開始時から時間経過に伴って一定傾斜で上昇し、最大値として、式(8)で表される関係式で求められる電流平均値( $I_{chg}$ )に到達することが判る。

40

【0105】

なお、本実施形態の充電制御装置10においては、キャパシタC1に供給される平均電流値( $I_{chg}$ )は、SS端子に入力されるバイアス電圧 $V_{ss}$ と抵抗 $R_{sen}$ とで決定される。本実施形態においては、実施例1から実施例4で説明したスロープ波形の生成に係る電流帰還ループを備えなくとも、キャパシタC1に供給される平均電流値( $I_{chg}$ )が制御できる。このため、実施例5に示す充電制御装置10の形態は、電流モード型の

50

スイッチングレギュレータ以外に、電圧モード型、ヒステリシス型、C O T ( Constant on Time ) 型のスイッチングレギュレータにおいても適用可能になる。

【 0 1 0 6 】

〔実施例 6 〕 ( ブロック構成 )

図 1 1 は、実施例 6 ( 以下、「本実施形態」とも称する ) に係る充電制御装置 1 0 のブロック構成の一例を示す図である。図 1 0 に示す充電制御装置 1 0 は、実施例 5 で説明した充電制御装置 1 0 の形態に対して、さらに、キャパシタ C 1 に充電された充電電圧 ( V out ) をフィードバック量として反映させる形態である。

【 0 1 0 7 】

本実施形態の充電制御装置 1 0 においては、例えば、実施例 3 で説明したように、キャパシタ C 1 に充電された充電電圧 ( V out ) をフィードバック量として反映させることで、スイッチング動作時にスイッチングレギュレータ 1 1 に流れ込む電流値 ( I in ) をキャパシタ C 1 の充電状態に応じて制御する。

本実施形態の充電制御装置 1 0 においては、電流モード型のスイッチングレギュレータ以外であっても、一次電源 2 0 の電流容量やバッテリの供給可能な電流量に制約がある場合に、スイッチングレギュレータ 1 1 に流れ込む電流値 ( I in ) の最大値を抑制しつつ、キャパシタ C 1 を充電することが可能になる。

【 0 1 0 8 】

図 1 1 に示す充電制御装置 1 0 は、少なくとも、スイッチングレギュレータ 1 1 と、インダクタ素子 L 1 と、バイアス電圧 V ss を印加するユニット ( 以下、単に「バイアス電圧 V ss 」とも称す ) と、抵抗 R sen と、抵抗 R 1 、 R 2 を含む。抵抗 R 1 、 R 2 は、キャパシタ C 1 に充電された充電電圧を検出する。図 1 1 に示すブロック構成においては、抵抗 R 1 、 R 2 以外の構成は、図 9 と同様の構成である。

【 0 1 0 9 】

抵抗 R 1 の一端はキャパシタ C 1 の正極側端子と接続し、他端は F B 端子と接続する。抵抗 R 2 の一端はキャパシタ C 1 の負極側端子と接続し、他端は F B 端子と接続する。以下、図 9 と相違する構成を主として本実施形態の充電制御装置 1 0 の充電制御動作を説明する。

【 0 1 1 0 】

( 充電制御動作 )

図 1 1 の、スイッチングレギュレータ 1 1 においては、誤差アンプ 1 1 b の反転入力端子には、抵抗 ( R 1 、 R 2 ) を介して検出されたキャパシタ C 1 の充電電圧 ( V out ) と、抵抗 R sen を介して検出されたキャパシタ C 1 の負極側端子と G N D との間の電位差がフィードバック電圧として入力される。

【 0 1 1 1 】

なお、スイッチングレギュレータ 1 1 外で S S 端子と接続するバイアス電圧 V ss の電圧値は、基準電圧 V R E F 未満の電圧値に設定される。 S S 端子に印加されたバイアス電圧 V ss は、誤差アンプ 1 1 b の非反転入力端子に入力される。

【 0 1 1 2 】

誤差アンプ 1 1 b は、 F B 端子に入力されたフィードバック電圧と、バイアス電圧 V ss との差電圧 ( 誤差 ) を所定ゲイン ( A ) で増幅し、該増幅された差電圧を誤差信号として出力端子に出力する。

【 0 1 1 3 】

本実施形態の、インダクタ素子 L 1 を介してキャパシタ C 1 に供給される電流 ( I out ) の電流平均値 ( I chg ) と、キャパシタ C 1 の充電電圧 ( V out ) と、バイアス電圧 V ss 、抵抗 R sen 、抵抗 ( R 1 、 R 2 ) との関係は、次に示す式 ( 9 ) で表される。

10

20

30

40

【数9】

$$I_{chg} = \frac{V_{ss} - \frac{R_2}{R_1} \times (V_{out} - V_{ss})}{R_{sen}} \quad \dots \text{式9}$$

※ $I_{chg}=I_{OUT}$ のリップルを除いた平均値。

10

【0114】

式(9)に示すように、本実施形態に係る充電制御装置10は、スイッチング動作時にインダクタ素子L1を介してキャパシタC1に供給される電流平均値( $I_{chg}$ )を、バイアス電圧 $V_{ss}$ と抵抗 $R_{sen}$ と、抵抗 $R_1$ 、 $R_2$ を介して検出されたキャパシタC1の充電電圧( $V_{out}$ )とに応じた定電流値に制御できる。

【0115】

(充電電流特性)

図12は、本実施形態の充電制御装置10による充電電流特性の一例を示す図である。図12の充電電流特性は、VIN端子の入力電圧を「5V」、バイアス電圧 $V_{ss}$ を「0.1V」、抵抗 $R_{sen}$ を「68m」、抵抗 $R_1$ を「82k」、抵抗 $R_2$ を「1k」、インダクタ素子L1を「2.2μH」として、図11に示す充電制御装置10のシミュレーション解析を行った結果である。

20

【0116】

図12の、グラフg1は、スイッチング素子SW1、SW2のスイッチング動作時に、VIN端子とスイッチング素子SW1のソースとの間に流れる電流 $I_{SW}$ の平均値( $I_{in}$ )の時間変化を表す。グラフg2は、キャパシタC1の充電電圧値( $V_{out}$ )の時間変化を表し、グラフg3は、インダクタ素子L1を介してキャパシタC1に供給される電流値( $I_{out}$ )の時間変化を表す。図12の縦軸は電流値(0.5A/div)、電圧値(1V/div)を表し、横軸は正規化された時間経過を表し、横軸に平行な破線は、0V基準、0A基準を表す。

30

【0117】

グラフg1に示すように、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値( $I_{in}$ )は、スイッチング動作の開始時から時間経過に伴って緩やかに上昇変化して0.7A程度の最大値に到達する。上記最大値に到達後の電流値( $I_{in}$ )は、0.7Aから0.5Aの範囲において一定状態、あるいは、時間経過に伴って微小に減少変化するように推移する。

【0118】

グラフg2に示すように、キャパシタC1の充電電圧値( $V_{out}$ )は、スイッチング動作の開始時から時間経過に伴って緩やかに上昇するように変化し、キャパシタC1の充電容量で定められる一定電圧値に到達する。グラフg1とグラフg2の相対的な時間変化から、キャパシタC1の充電状態が満充電容量の粗半分付近で、電流値( $I_{in}$ )が最大値に到達することが判る。また、図10に示すグラフg1の時間変化傾向と、図12に示すグラフg1の時間変化傾向とを比較した場合、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値( $I_{in}$ )の相対的な大きさが抑制されていることが判る。

40

【0119】

グラフg3に示すように、キャパシタC1に供給される電流値( $I_{out}$ )の時間変化は、スイッチング動作の開始時から時間経過に伴って一定傾斜で下降し、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値( $I_{in}$ )に到達するよう変化する。グラフg3とグラフg2の相対的な時間変化から、キャパシタC1の充電電圧値( $V$

50

$I_{out}$ ) が増加するに従い、スイッチングレギュレータ 11 に流れ込む電流値 ( $I_{in}$ ) が減少することが判る。

【0120】

図 13 は、本実施形態の充電制御装置 10 による充電電流特性の他の一例を示す図である。図 13 は、充電電流特性に対する抵抗  $R_1$  の寄与の度合いを確認するため、抵抗  $R_1$  を「220k」、他の条件は図 12 と同様として、図 11 に示す充電制御装置 10 のシミュレーション解析を行った結果である。なお、図 13 に示す、グラフ g1、g2、g3、縦軸、横軸、0V 基準、0A 基準は、図 12 と同様である。

【0121】

グラフ g1 に示すように、スイッチング動作時にスイッチングレギュレータ 11 に流れ込む電流値 ( $I_{in}$ ) は、スイッチング動作の開始時から時間経過に伴って上昇変化し、1.1A 程度の最大値に到達する。グラフ g3 に示すように、キャパシタ C1 に供給される電流値 ( $I_{out}$ ) の時間変化は、スイッチング動作の開始時から時間経過に伴って一定傾斜で下降し、スイッチング動作時にスイッチングレギュレータ 11 に流れ込む電流値 ( $I_{in}$ ) に到達するよう変化する。

【0122】

図 12 に示すグラフ g1、g2 と、図 13 に示すグラフ g1、g2 との時間変化傾向の比較から、抵抗  $R_1$  の抵抗値の増加に伴い、電流値 ( $I_{in}$ ) のスイッチング動作の開始時からの上昇変化は、直線的な一定傾斜に近づくことが確認判る。抵抗  $R_1$  の抵抗値の増加に伴い、電流値 ( $I_{in}$ ) の到達する最大値は増加することが判る。また、抵抗  $R_1$  の抵抗値の増加に伴い、キャパシタ C1 に供給される電流値 ( $I_{out}$ ) の時間変化の一定傾斜が減少することが判る。

【0123】

(変形例) (ブロック構成)

図 14 は、変形例に係る充電制御装置 10 のブロック構成の一例を示す図である。実施例 5 に示す形態、実施例 6 に示す形態では、充電制御装置 10 は、バイアス電圧  $V_{ss}$  とフィードバック電圧とに基づいて、バックアップ用電源を構成するキャパシタ C1 に供給する充電電流の制御が可能なことを説明した。変形例の充電制御装置 10 では、インダクタ素子 L1 とキャパシタ C1 の正極端子との間に抵抗  $R_{sen}$  を設け、該抵抗  $R_{sen}$  に生ずる電位差を用いて定電流制御を行う。

【0124】

変形例の充電制御装置 10 においては、少なくとも、スイッチングレギュレータ 11 と、インダクタ素子 L1 と、抵抗  $R_{sen}$  と、抵抗  $R_1$ 、 $R_2$ 、 $R_3$ 、 $R_4$ 、 $R_5$ 、 $R_6$  とが含まれる。図 14 に示すブロック構成においては、抵抗  $R_{sen}$ 、抵抗 ( $R_1 - R_6$ ) 以外の構成は、図 9 と同様の構成である。なお、図 14 のスイッチングレギュレータ 11 は簡略化されている。

【0125】

(充電制御動作)

図 14において、抵抗  $R_{sen}$  の一端はインダクタ素子 L1 の出力端に接続され、他端はキャパシタ C1 の正極側端子に接続される。抵抗  $R_1$  の一端とインダクタ素子 L1 の出力端とは接続し、抵抗  $R_1$  の他端とスイッチングレギュレータ 11 の FB 端子とは接続する。また、一端が車両の GND に接地された抵抗  $R_2$  の他端とスイッチングレギュレータ 11 の FB 端子とは接続する。一端が、キャパシタ C1 の正極側端子に接続される抵抗  $R_6$  の他端とスイッチングレギュレータ 11 の FB 端子とは接続する。

【0126】

抵抗  $R_1$ 、 $R_2$  を介し、インダクタ素子 L1 とキャパシタ C1 の正極端子との間に設けられた抵抗  $R_{sen}$  の、インダクタ素子 L1 の出力端側の電圧がフィードバック電圧としてスイッチングレギュレータ 11 の FB 端子に入力される。なお、抵抗  $R_6$  により、キャパシタ C1 に充電された充電電圧 ( $V_{out}$ ) がフィードバック量に反映される。

【0127】

10

20

30

40

50

また、図14において、抵抗R3の一端とキャパシタC1の正極側端子とは接続し、抵抗R3の他端とスイッチングレギュレータ11のSS端子とは接続する。一端が車両のGNDに接地された抵抗R4の他端とスイッチングレギュレータ11のSS端子とは接続する。一端が、図示しない一次電源20の供給する電圧(VIN)に接続される抵抗R5の他端とスイッチングレギュレータ11のSS端子とは接続する。

【0128】

抵抗R3、R4を介し、インダクタ素子L1とキャパシタC1の正極端子との間に設けられた抵抗Rsenの、キャパシタC1の正極端子側の電圧がバイアス電圧Vssとしてスイッチングレギュレータ11のSS端子に入力される。なお、抵抗R5により、バイアス電圧Vssをオフセットするオフセット電圧が供給される。

10

【0129】

変形例の充電制御装置10においては、抵抗(R1-R4)により、スイッチングレギュレータ11のSS端子とFB端子との間には、インダクタ素子L1とキャパシタC1の正極端子との間に設けられた抵抗Rsenを介して検出された電位差が印加される。また、変形例の充電制御装置10においては、抵抗R5により、バイアス電圧Vssがオフセットされる。抵抗R6により、キャパシタC1に充電された充電電圧(Vout)がフィードバック量に反映される。以下、図9と相違する構成を主として変形例の充電制御装置10の充電制御動作を説明する。

【0130】

(充電制御動作)

20

変形例の形態では、スイッチングレギュレータ11の誤差アンプ11bの反転入力端子には、上述したフィードバック電圧が入力される。また、誤差アンプ11bの非反転入力端子には、上述したオフセットされたバイアス電圧Vssが入力される。なお、オフセットされたバイアス電圧Vssの電圧値は、基準電圧VREF未満となるように、抵抗R3、R4、R5を介して設定される。

【0131】

誤差アンプ11bは、反転入力端子に入力されたフィードバック電圧と、オフセットされたバイアス電圧Vssとの差電圧(誤差)を所定ゲイン(A)で増幅し、該増幅された差電圧を誤差信号として出力端子に出力する。

【0132】

30

図14において、抵抗R1と抵抗R3の抵抗値を同値に設定し、抵抗R2と抵抗R4の抵抗値を同値に設定する。変形例の形態では、スイッチングレギュレータ11は、上記設定条件において、オフセット電圧値のR1/R2倍の電圧がインダクタ素子L1とキャパシタC1の正極端子との間に設けられた抵抗Rsenに発生するように制御動作を行う。この結果、変形例の充電制御装置10においても、実施例5に示す形態と同様にして定電流制御が可能になる。

【0133】

また、抵抗R6により、キャパシタC1に充電された充電電圧(Vout)をフィードバック量に反映することで、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(ain)をキャパシタC1の充電状態に応じて制御することが可能になる。変形例の充電制御装置10においても、実施例6に示す形態と同様にしてスイッチングレギュレータ11に流れ込む電流値(ain)の最大値を抑制しつつ、キャパシタC1を充電することが可能になる。

40

【0134】

(充電電流特性)

図15、図16は、変形例の充電電流特性を説明する図である。図15は、抵抗R6を含まない形態の変形例の充電電流特性であり、図16は、抵抗R6を含む形態の変形例の充電電流特性である。図15、図16において、実線で示されるグラフは、スイッチング素子SW1、SW2のスイッチング動作時に、VIN端子とスイッチング素子SW1のソースとの間に流れる電流ISWの平均値(ain)の時間変化を表す。二点鎖線で示され

50

るグラフは、キャパシタC1の充電電圧値(  $V_{out}$  )の時間変化を表す。一点鎖線で示されるグラフは、インダクタ素子L1を介してキャパシタC1に供給される電流値(  $I_{out}$  )の時間変化を表す。なお、図15、図16の縦軸は電流値( 0.25 A / div )、電圧値( 1 V / div )を表し、横軸は時間経過( 単位時間 : 5 sec )を表す。

【0135】

図15の一点鎖線のグラフに示すように、インダクタ素子L1を介してキャパシタC1に供給される電流値(  $I_{out}$  )は、二点鎖線のグラフで示されるキャパシタC1の充電電圧値(  $V_{out}$  )の増加に伴って減少する変化傾向を示す。また、実線のグラフに示すように、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(  $I_{in}$  )は、スイッチング動作の開始時から時間経過に伴って上昇変化し、0.9 A近傍の最大値に到達する変化傾向を示す。

【0136】

また、抵抗R6を含む形態では、図16の実線のグラフに示すように、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(  $I_{in}$  )は、スイッチング動作の開始時から時間経過に伴って上昇変化し、最大値に到達する変化傾向を示す。また、最大値に到達後の電流値(  $I_{in}$  )は、最大値近傍で一定状態、あるいは、時間経過に伴って減少変化する傾向を示す。抵抗R6を含む形態では、スイッチング動作時にスイッチングレギュレータ11に流れ込む電流値(  $I_{in}$  )の最大値は、0.5 A未満に抑制される傾向を示す。

【符号の説明】

【0137】

10 充電制御装置

11 スイッチングレギュレータ

11a 内部電流源

11b 誤差アンプ( Error Amp )

11c スロープ補償ユニット

11d コンパレータ( PWM Comp )

11e PWM制御ユニット( PWM Control Logic )

20 一次電源

21 二次電源

C1 キャパシタ( バックアップ用電源 )

Ct、Ct1 キャパシタ

COMP、FB、GND、OUT、VIN、SS 端子

D1 ダイオード素子

L1 インダクタ素子

R1、R2、R3、R4、R5、R6、Rsen、Rt 抵抗

SW1、SW2 スイッチング素子

VREF 基準電圧

Vss バイアス電圧

10

20

30

## 【 义 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

シミュレーション条件

- $V_{IN}=5V$

- $V_{REF}=0.8V$

- $G_{CS}=0.222V/A$

- $V_{offset}=0.3V$

- $R_1=1k\Omega$

- $R_2=220k\Omega$

- $R_3=47k\Omega$

- $L_1=2.2\mu H$

- $Slope Comp=1.34A/cycle$

※ $I_{in}=I_{sw}$ の平均値

【図7】

【図8】

(1)

$R_3=47k\Omega$ の場合

(2)

$R_3=\infty$ の場合

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特開2009-303281(JP,A)

特開2010-051155(JP,A)

特開2010-142111(JP,A)

特開2010-220454(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |                 |

|--------|-----------------|

| H 02 M | 3 / 00 - 3 / 44 |

| G 05 F | 1 / 00 - 1 / 10 |

| B 60 R | 16 / 02         |

| H 02 J | 7 / 10          |

| H 02 J | 9 / 06          |