(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7269397号

(P7269397)

(45)発行日 令和5年5月8日(2023.5.8)

(24)登録日 令和5年4月25日(2023.4.25)

|                         |                      |

|-------------------------|----------------------|

| (51)国際特許分類              | F I                  |

| H 01 L 21/336 (2006.01) | H 01 L 29/78 6 1 9 A |

| H 01 L 29/786 (2006.01) | G 02 F 1/1368        |

| G 02 F 1/1368 (2006.01) | G 09 F 9/30 3 3 8    |

| G 09 F 9/30 (2006.01)   | H 01 L 27/146 C      |

| H 01 L 27/146 (2006.01) | H 01 L 29/78 6 1 8 B |

請求項の数 1 (全95頁) 最終頁に続く

|                   |                              |          |                                 |

|-------------------|------------------------------|----------|---------------------------------|

| (21)出願番号          | 特願2022-22090(P2022-22090)    | (73)特許権者 | 000153878                       |

| (22)出願日           | 令和4年2月16日(2022.2.16)         |          | 株式会社半導体エネルギー研究所                 |

| (62)分割の表示         | 特願2021-23047(P2021-23047)の分割 |          | 神奈川県厚木市長谷398番地                  |

| 原出願日              | 平成27年11月26日(2015.11.26)      | (72)発明者  | 山崎 舜平                           |

| (65)公開番号          | 特開2022-81496(P2022-81496A)   |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

| (43)公開日           | 令和4年5月31日(2022.5.31)         | (72)発明者  | 肥塚 純一                           |

| 審査請求日             | 令和4年2月25日(2022.2.25)         |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

| (31)優先権主張番号       | 特願2014-241466(P2014-241466)  | (72)発明者  | 岡崎 健一                           |

| (32)優先日           | 平成26年11月28日(2014.11.28)      |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                      | (72)発明者  | 神長 正美                           |

| (31)優先権主張番号       | 特願2014-264766(P2014-264766)  |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

| (32)優先日           | 平成26年12月26日(2014.12.26)      |          | 最終頁に続く                          |

| (33)優先権主張国・地域又は機関 |                              |          | 最終頁に続く                          |

(54)【発明の名称】 表示装置の作製方法

## (57)【特許請求の範囲】

## 【請求項1】

酸化物半導体膜を用いてチャネル形成領域が形成されるトランジスタを有する表示装置の作製方法であって、

前記酸化物半導体膜を形成する工程と、

前記酸化物半導体膜上に絶縁膜を形成する工程と、

前記絶縁膜上にインジウムを含む膜を形成し、前記絶縁膜に酸素を添加する工程と、

前記インジウムを含む膜を除去する工程と、を有する、表示装置の作製方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明の一態様は、酸化物半導体膜を有する半導体装置、該半導体装置の作製方法、及び該半導体装置を有する表示装置に関する。

## 【0002】

なお、本発明の一態様は、上記の技術分野に限定されない。本明細書等で開示する発明の一態様の技術分野は、物、方法、または、製造方法に関する。または、本発明の一態様は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明の一態様は、半導体装置、表示装置、液晶表示装置、発光装置、蓄電装置、記憶装置、撮像装置、それらの駆動方法、またはそれらの製造方法に関する。

## 【0003】

なお、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は、半導体装置を有している場合がある。

## 【背景技術】

## 【0004】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ（電界効果トランジスタ（FET）、または薄膜トランジスタ（TFT）ともいう）を構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコンを代表とする半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている（例えば、特許文献1）。

10

## 【0005】

また、酸化物半導体層上に酸化物絶縁層を形成し、酸化物絶縁層を通過して酸素を導入（添加）し、加熱処理を行い、該酸素導入及び該加熱処理によって、水素、水分、水酸基または水素化物などの不純物を酸化物半導体層より排除し、酸化物半導体層を高純度化する半導体装置の作製方法が開示されている（例えば、特許文献2）

20

## 【先行技術文献】

## 【特許文献】

## 【0006】

【文献】特開2006-165529号公報

特開2011-199272号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】

酸化物半導体膜をチャネル領域に有するトランジスタを作製する場合、酸化物半導体膜のチャネル領域中に混入する水素または水分などの不純物は、トランジスタ特性に影響を与えるため問題となる。また、酸化物半導体膜のチャネル領域中に形成される酸素欠損は、トランジスタ特性に影響を与えるため問題となる。例えば、酸化物半導体膜のチャネル領域中に酸素欠損が形成されると、該酸素欠損に水素が結合し、キャリア供給源となる。酸化物半導体膜のチャネル領域中にキャリア供給源が生成されると、酸化物半導体膜を有するトランジスタの電気特性の変動、代表的にはしきい値電圧のシフトが生じる。また、トランジスタごとに電気特性がばらつくという問題がある。したがって、酸化物半導体膜のチャネル領域においては、酸素欠損が少ないほど好ましい。また、酸化物半導体膜のチャネル領域においては、酸素欠損とともに、水素または水分などの不純物が少ないほど好ましい。

30

## 【0008】

また、電極または配線が接触する酸化物半導体膜の領域においては、良好な接触抵抗を得るために抵抗が低い方が好ましい。

40

## 【0009】

上記問題に鑑み、本発明の一態様は、酸化物半導体膜を有する半導体装置において、電気特性の変動を抑制すると共に、信頼性を向上させることを課題の1つとする。または、本発明の一態様は、新規な半導体装置及び新規な半導体装置の作製方法を提供することを課題の1つとする。または、本発明の一態様は、新規な表示装置を提供することを課題の1つとする。

## 【0010】

なお、上記の課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの課題の全てを解決する必要はない。上記以外の課題は、明細

50

書等の記載から自ずと明らかになるものであり、明細書等の記載から上記以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0011】

本発明の一態様は、酸化物半導体膜を有する半導体装置であって、半導体装置は、ゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート絶縁膜上の酸化物半導体膜と、酸化物半導体膜上の二対の電極と、を有し、酸化物半導体膜は、チャネル領域と、二対の電極と接するn型領域と、を有し、チャネル領域の酸素欠損は、n型領域の酸素欠損よりも少ない半導体装置である。

【0012】

また、本発明の他の一態様は、酸化物半導体膜を有する半導体装置であって、半導体装置は、ゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート絶縁膜上の酸化物半導体膜と、酸化物半導体膜上の二対の電極と、酸化物半導体膜及び二対の電極上の酸化物絶縁膜と、を有し、酸化物半導体膜は、チャネル領域と、二対の電極と接するn型領域と、を有し、チャネル領域の酸素欠損は、n型領域の酸素欠損よりも少ない半導体装置である。

【0013】

また、本発明の他の一態様は、酸化物半導体膜を有する半導体装置であって、半導体装置は、第1のゲート電極と、第1のゲート電極上のゲート絶縁膜と、ゲート絶縁膜上の酸化物半導体膜と、酸化物半導体膜上の二対の電極と、酸化物半導体膜及び二対の電極上の酸化物絶縁膜と、酸化物絶縁膜上の窒化物絶縁膜と、窒化物絶縁膜上の第2のゲート電極と、を有し、酸化物半導体膜は、チャネル領域と、二対の電極と接するn型領域と、を有し、チャネル領域の酸素欠損は、n型領域の酸素欠損よりも少ない半導体装置である。

【0014】

また、上記態様において、チャネル領域は、二対の電極の下に形成される酸化物半導体膜よりも薄い領域を有すると好ましい。

【0015】

また、上記態様において、酸化物半導体膜は、Inと、Znと、M(Mは、Ti、Ga、Y、Zr、La、Ce、Nd、SnまたはHfを表す)と、を有すると好ましい。また、上記態様において、酸化物半導体膜は、結晶部を有し、結晶部は、c軸配向性を有し、c軸が酸化物半導体膜の被形成面の法線ベクトルに平行である部分を有すると好ましい。

【0016】

また、上記態様において、酸化物絶縁膜は、昇温脱離ガス分析法によって、 $8.0 \times 10^{14} \text{ atoms/cm}^2$ 以上の酸素原子が検出されると好ましい。

【0017】

また、本発明の他の一態様は、上記態様にいずれか一つに記載の半導体装置と表示素子とを有する表示装置である。また、本発明の他の一態様は、該表示装置とタッチセンサとを有する表示モジュールである。また、本発明の他の一態様は、上記態様にいずれか一つに記載の半導体装置、上記態様の表示装置、または上記態様の表示モジュールと、操作キーまたはバッテリとを有する電子機器である。

【0018】

また、本発明の他の一態様は、酸化物半導体膜を有する半導体装置の作製方法であって、基板上にゲート電極を形成する工程と、ゲート電極上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上に酸化物半導体膜を形成する工程と、酸化物半導体膜上に導電膜を形成することで、酸化物半導体膜中に酸素欠損を有する領域を形成する工程と、導電膜を加工し、二対の電極を形成する工程と、酸化物半導体膜、及び二対の電極上から薬液またはガスにより、二対の電極間の酸化物半導体膜の酸素欠損を有する領域を除去する工程とを、有する半導体装置の作製方法である。

【0019】

また、本発明の他の一態様は、酸化物半導体膜を有する半導体装置の作製方法であって、基板上にゲート電極を形成する工程と、ゲート電極上にゲート絶縁膜を形成する工程と

10

20

30

40

50

、ゲート絶縁膜上に酸化物半導体膜を形成する工程と、酸化物半導体膜上に導電膜を形成することで、酸化物半導体膜中に酸素欠損を有する領域を形成する工程と、導電膜を加工し、一対の電極を形成する工程と、酸化物半導体膜、及び一対の電極上から薬液またはガスにより、一対の電極間の酸化物半導体膜の酸素欠損を有する領域を除去する工程と、酸化物半導体膜、及び一対の電極上に酸化物絶縁膜を形成する工程と、酸化物絶縁膜中に酸素を添加する工程と、有する半導体装置の作製方法である。

【0020】

上記態様において、導電膜は、スパッタリング装置により形成されると好ましい。また、上記態様において、電力密度が  $1 \text{ W} / \text{cm}^2$  以上  $4 \text{ W} / \text{cm}^2$  以下で形成されると好ましい。

10

【発明の効果】

【0021】

本発明の一態様により、酸化物半導体膜を有する半導体装置において、電気特性の変動を抑制すると共に、信頼性を向上させることができる。または、本発明の一態様により、消費電力が低減された半導体装置を提供することができる。または、本発明の一態様により、新規な半導体装置または新規な半導体装置の作製方法を提供することができる。または、本発明の一態様により、新規な表示装置を提供することができる。

【0022】

なお、これらの効果の記載は、他の効果の存在を妨げるものではない。なお、本発明の一態様は、必ずしも、これらの効果の全てを有する必要はない。なお、これら以外の効果は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の効果を抽出することが可能である。

20

【図面の簡単な説明】

【0023】

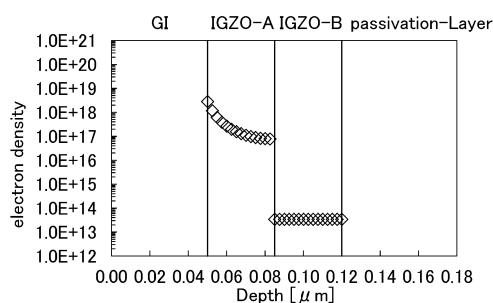

【図1】半導体装置の一態様を示す上面図及び断面図。

【図2】半導体装置の一態様を示す断面図。

【図3】半導体装置の一態様を示す上面図及び断面図。

【図4】半導体装置の一態様を示す断面図。

【図5】半導体装置の一態様を示す断面図。

【図6】半導体装置の一態様を示す断面図。

30

【図7】バンド構造を説明する図。

【図8】酸化物半導体膜中の電流が流れる際の概念を説明する模式図。

【図9】バンド構造の模式図及びバンドダイアグラムを説明する図。

【図10】トランジスタの信頼性試験結果を説明する図。

【図11】トランジスタ中の電子密度分布を計算した結果を説明する図。

【図12】半導体装置の作製工程の一例を示す断面図。

【図13】半導体装置の作製工程の一例を示す断面図。

【図14】半導体装置の作製工程の一例を示す断面図。

【図15】半導体装置の作製工程の一例を示す断面図。

【図16】ガスベーク炉の加熱処理時の熱プロファイルを説明する図。

40

【図17】ガスベーク炉の加熱処理時の熱プロファイルを説明する図。

【図18】半導体装置の作製工程の一例を示す断面図。

【図19】半導体装置の作製工程の一例を示す断面図。

【図20】C A A C - O S の断面における C s 補正高分解能 TEM 像、および C A A C - O S の断面模式図。

【図21】C A A C - O S の平面における C s 補正高分解能 TEM 像。

【図22】C A A C - O S および単結晶酸化物半導体の X R D による構造解析を説明する図。

【図23】C A A C - O S の電子回折パターンを示す図。

【図24】I n - G a - Z n 酸化物の電子照射による結晶部の変化を示す図。

50

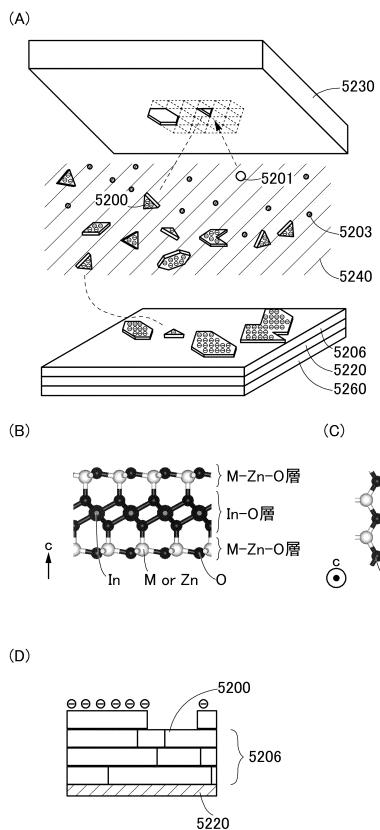

【図 2 5】 C A A C - O S の成膜方法を説明する図。

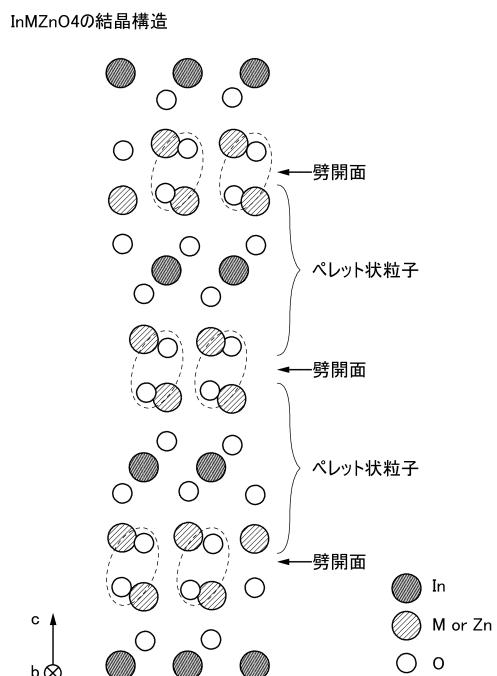

【図 2 6】 I n M Z n O 4 の結晶を説明する図。

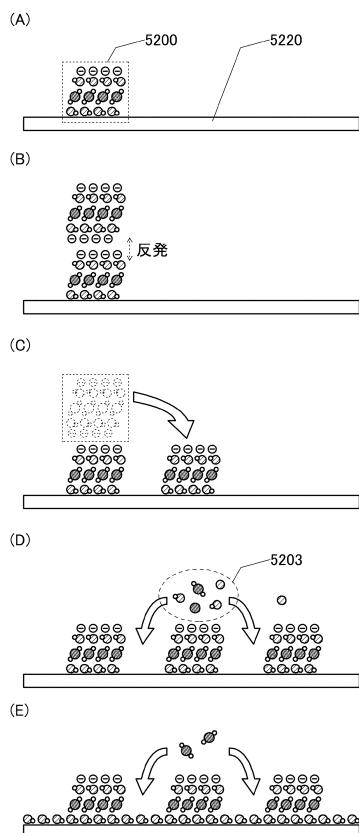

【図 2 7】 C A A C - O S の成膜方法を説明する図。

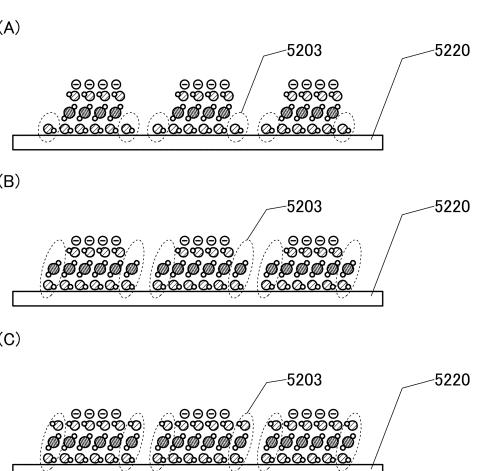

【図 2 8】 C A A C - O S の成膜方法を説明する図。

【図 2 9】 n c - O S の成膜方法を説明する図。

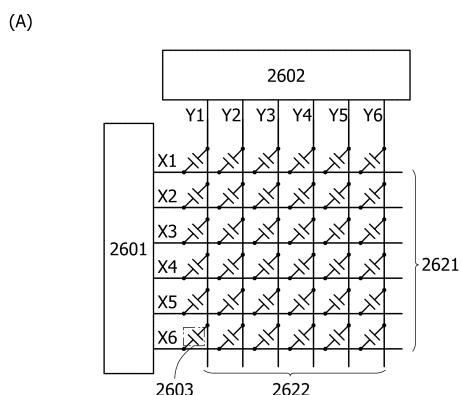

【図 3 0】 表示装置を説明するブロック図及び回路図。

【図 3 1】 タッチパネルの一例を示す斜視図。

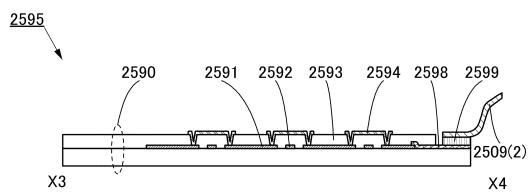

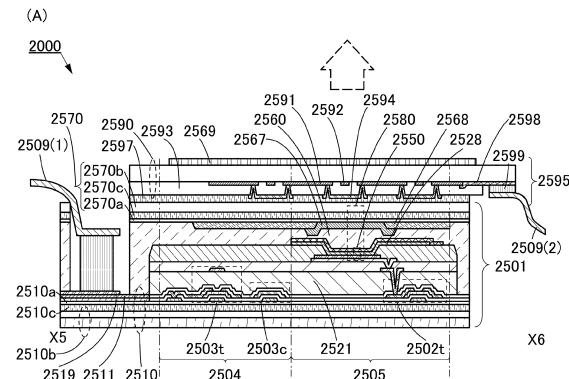

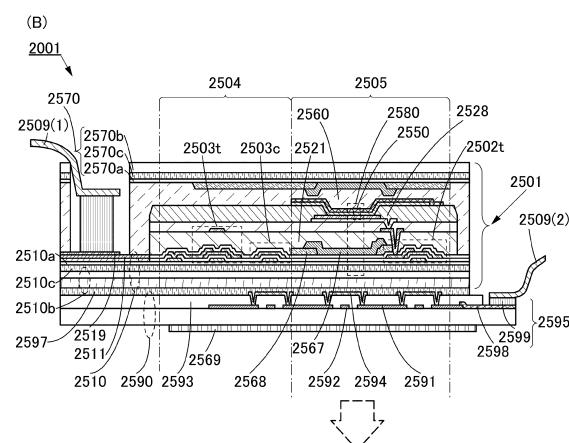

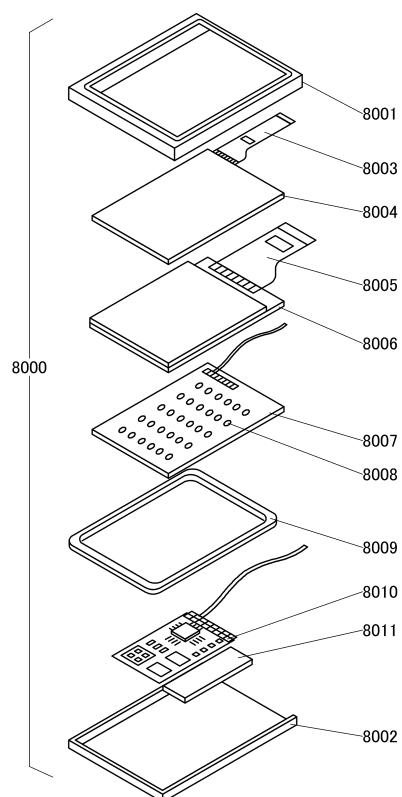

【図 3 2】 表示装置の一例を示す断面図。

【図 3 3】 タッチセンサの一例を示す断面図。

【図 3 4】 タッチパネルの一例を示す断面図。

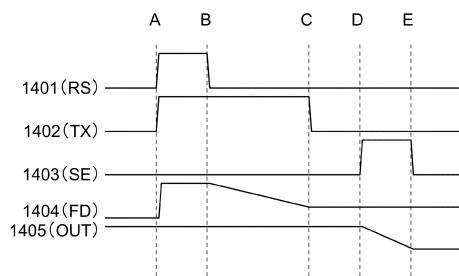

【図 3 5】 タッチセンサのブロック図及びタイミングチャート図。

【図 3 6】 タッチセンサの回路図。

【図 3 7】 半導体装置の回路構成を説明する図。

【図 3 8】 画素回路の構成を説明する図、及び画素回路の動作を説明するタイミングチャート。

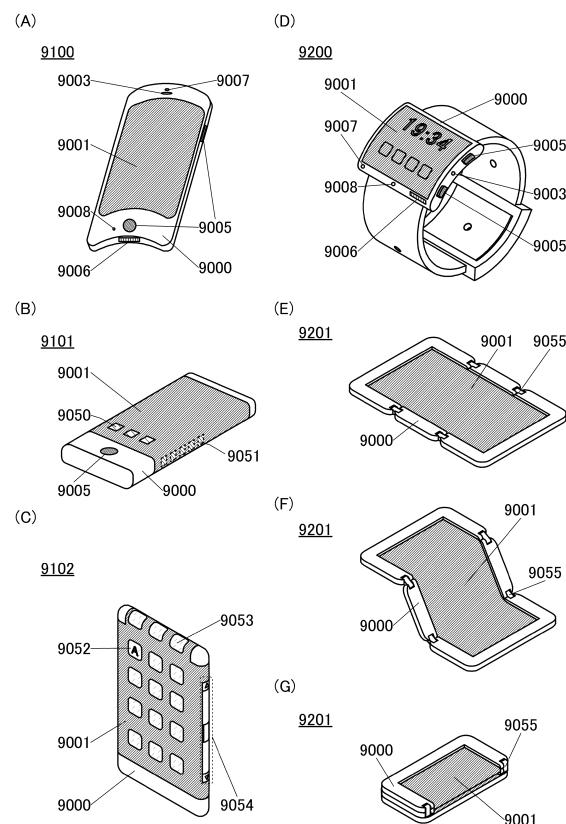

【図 3 9】 表示モジュールを説明する図。

【図 4 0】 電子機器を説明する図。

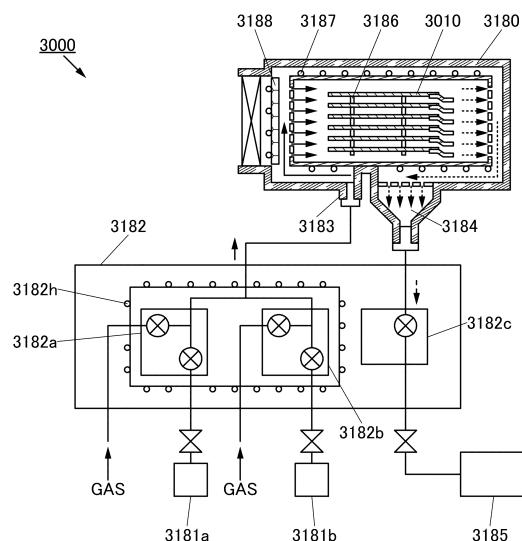

【図 4 1】 成膜装置の構成を説明する図。

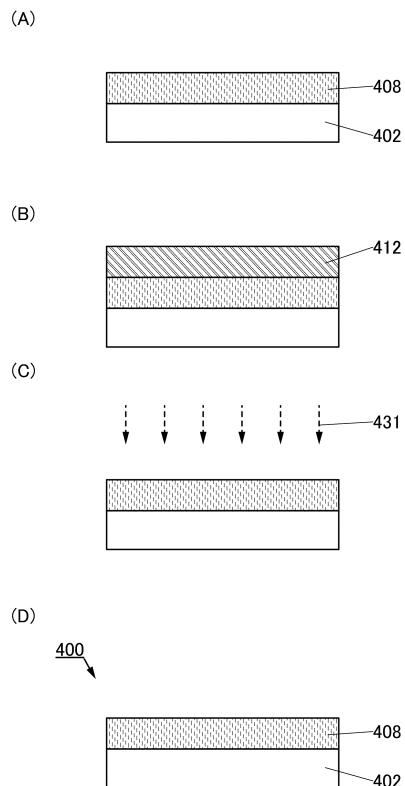

【図 4 2】 実施例における試料を説明する断面図、及び実施例における試料の作製工程を説明する断面図。

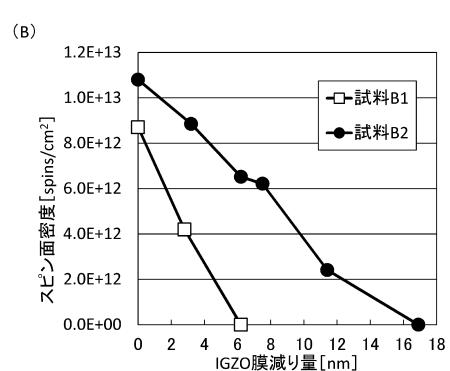

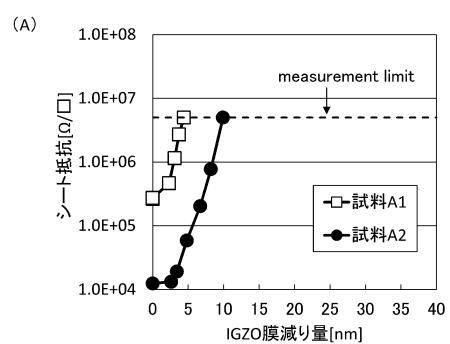

【図 4 3】 シート抵抗測定結果、及び E S R 測定結果を説明する図。

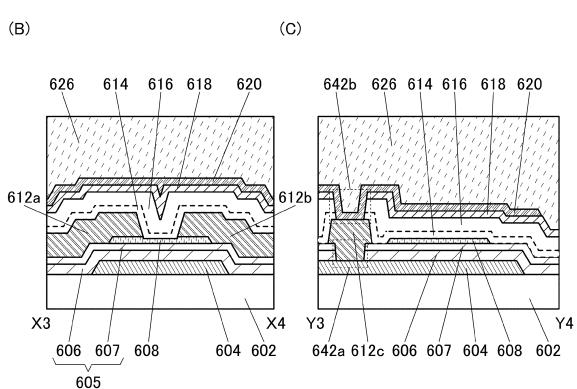

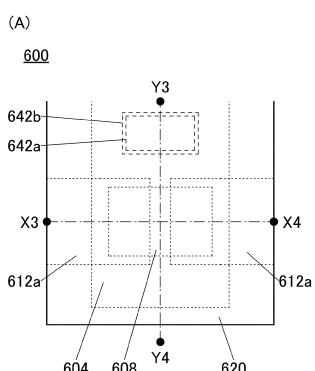

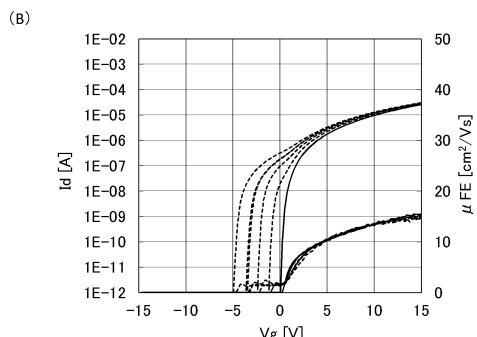

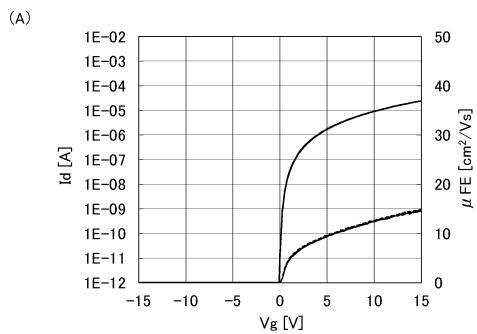

【図 4 4】 実施例における、トランジスタを説明する上面図及び断面図。

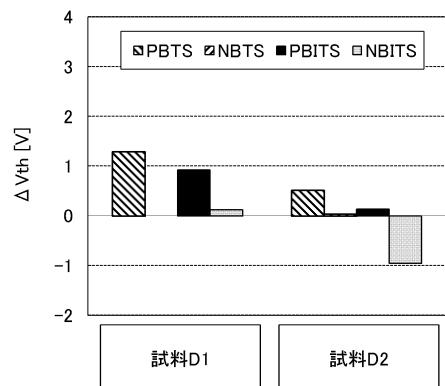

【図 4 5】 実施例における、トランジスタの信頼性試験結果を説明する図。

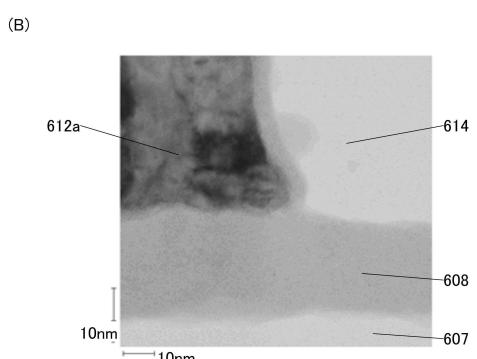

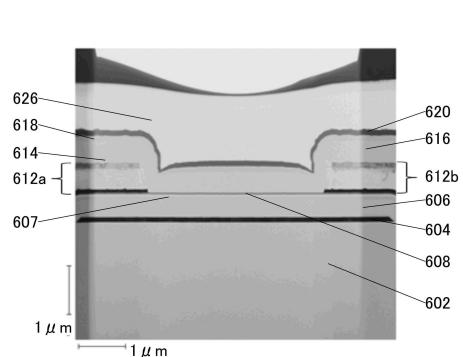

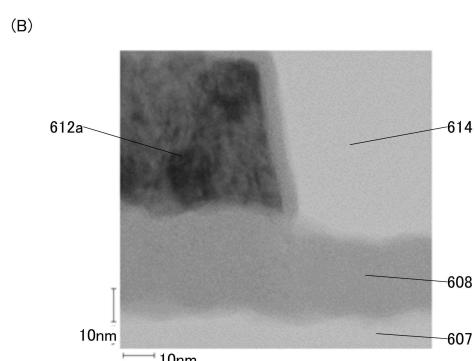

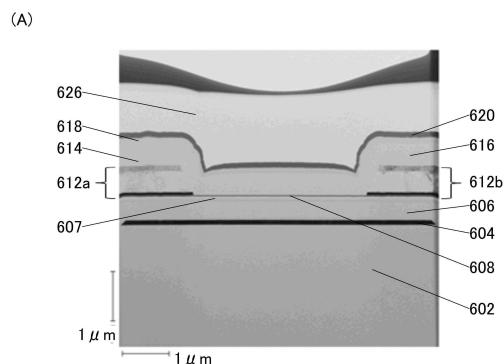

【図 4 6】 実施例における、トランジスタの断面 T E M 像。

【図 4 7】 実施例における、トランジスタの断面 T E M 像。

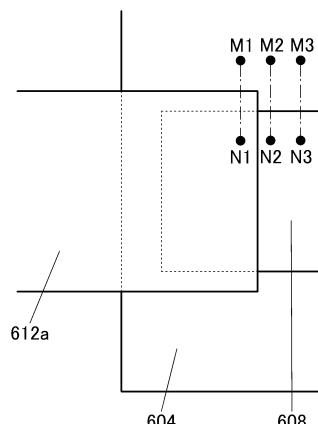

【図 4 8】 実施例における、断面観察箇所を表す上面図。

【図 4 9】 実施例における、トランジスタの断面 T E M 像。

【図 5 0】 実施例における、トランジスタの断面 T E M 像。

【図 5 1】 実施例における、トランジスタのオン電流及びしきい値電圧の確率分布を説明する図。

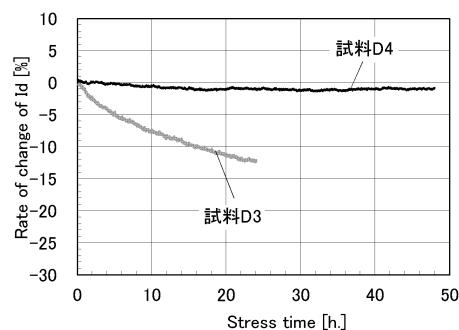

【図 5 2】 実施例における、トランジスタの信頼性試験結果を説明する図。

【図 5 3】 実施例における、トランジスタのストレス時間に対するオン電流の劣化率を説明する図。

【発明を実施するための形態】

【0 0 2 4】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は、以下の実施の形態の記載内容に限定して解釈されるものではない。

【0 0 2 5】

また、図面において、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。なお図面は、理想的な例を模式的に示したものであり、図面に示す形状又は値などに限定されない。

【0 0 2 6】

また、本明細書などにおいて、第 1、第 2 等として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。そのため、例えば、「第 1 の」を「第 2 の」又は「第 3 の」などと適宜置き換えて説明することができる。また、本明細書等に記載されている序数詞と、本発明の一態様を特定するために用いられる序数詞は一致しない場合がある。

【0 0 2 7】

10

20

30

40

50

また、本明細書において、「上に」、「下に」などの配置を示す語句は、構成同士の位置関係を、図面を参照して説明するために、便宜上用いている。また、構成同士の位置関係は、各構成を描写する方向に応じて適宜変化するものである。従って、明細書で説明した語句に限定されず、状況に応じて適切に言い換えることができる。

#### 【0028】

また、本明細書等において、半導体装置とは、半導体特性を利用することで機能しうる装置全般を指す。トランジスタなどの半導体素子をはじめ、半導体回路、演算装置、記憶装置は、半導体装置の一態様である。撮像装置、表示装置、液晶表示装置、発光装置、電気光学装置、発電装置（薄膜太陽電池、有機薄膜太陽電池等を含む）、及び電子機器は、半導体装置を有する場合がある。

10

#### 【0029】

また、本明細書等において、トランジスタとは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子である。そして、ドレイン（ドレイン端子、ドレン領域またはドレン電極）とソース（ソース端子、ソース領域またはソース電極）の間にチャネル領域を有しており、ドレインとチャネル領域とソースとを介して電流を流すことができるものである。なお、本明細書等において、チャネル領域とは、電流が主として流れる領域をいう。

#### 【0030】

また、ソースやドレインの機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。

20

#### 【0031】

また、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。例えば、「何らかの電気的作用を有するもの」には、電極や配線をはじめ、トランジスタなどのスイッチング素子、抵抗素子、インダクタ、キャパシタ、その他の各種機能を有する素子などが含まれる。

#### 【0032】

30

なお、本明細書等において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、好ましくは酸素が55原子%以上65原子%以下、窒素が1原子%以上20原子%以下、シリコンが25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の濃度範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、好ましくは窒素が55原子%以上65原子%以下、酸素が1原子%以上20原子%以下、シリコンが25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の濃度範囲で含まれるものという。

#### 【0033】

40

また、本明細書等において、「膜」という用語と、「層」という用語とは、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

#### 【0034】

また、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。したがって、-5°以上5°以下の場合も含まれる。また、「略平行」とは、二つの直線が-30°以上30°以下の角度で配置されている状態をいう。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。したがって、85°以上95°以下の場合も含まれる。また、「略垂直」とは、二つの直線が60°以上120°以下の角度で配置されている状態をいう。

50

## 【0035】

## (実施の形態1)

本実施の形態では、本発明の一態様の半導体装置、及び当該半導体装置の作製方法について、図1乃至図19を参照して説明する。

## 【0036】

## &lt;半導体装置の構成例1&gt;

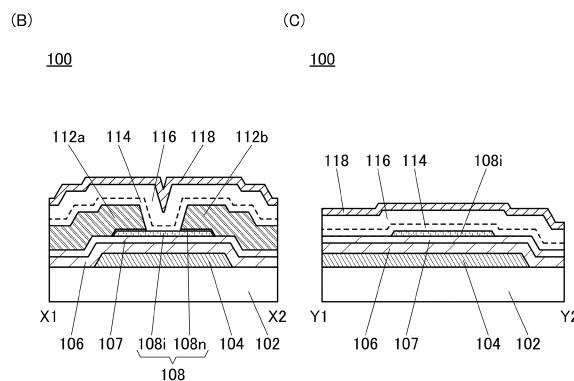

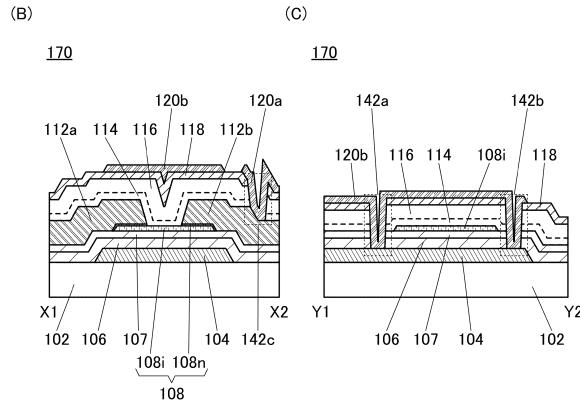

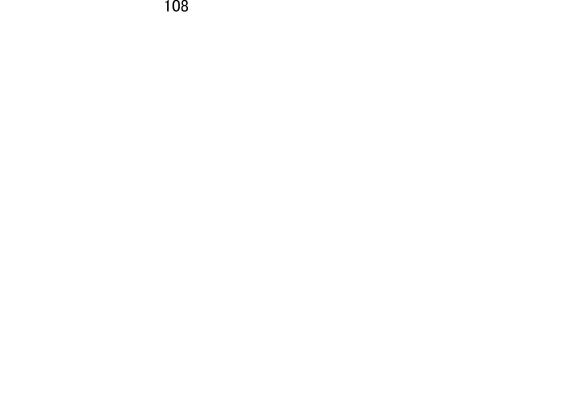

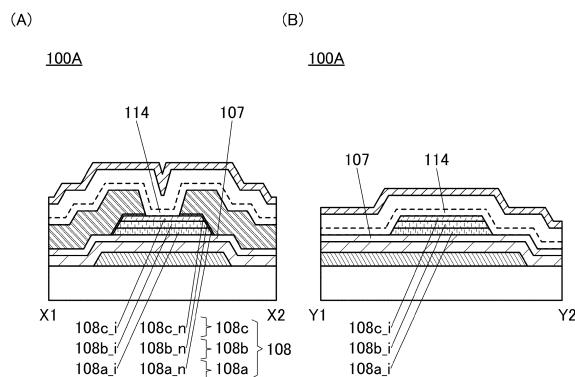

図1(A)は、本発明の一態様の半導体装置であるトランジスタ100の上面図であり、図1(B)は、図1(A)に示す一点鎖線X1-X2間ににおける切断面の断面図に相当し、図1(C)は、図1(A)に示す一点鎖線Y1-Y2間ににおける切断面の断面図に相当する。なお、図1(A)において、煩雑になることを避けるため、トランジスタ100の構成要素の一部(ゲート絶縁膜として機能する絶縁膜等)を省略して図示している。また、一点鎖線X1-X2方向をチャネル長方向、一点鎖線Y1-Y2方向をチャネル幅方向と呼称する場合がある。なお、トランジスタの上面図においては、以降の図面においても図1(A)と同様に、構成要素の一部を省略して図示する場合がある。

10

## 【0037】

トランジスタ100は、基板102上のゲート電極として機能する導電膜104と、基板102及び導電膜104上の絶縁膜106と、絶縁膜106上の絶縁膜107と、絶縁膜107上の酸化物半導体膜108と、酸化物半導体膜108に電気的に接続されるソース電極として機能する導電膜112aと、酸化物半導体膜108に電気的に接続されるドレイン電極として機能する導電膜112bと、を有する。また、トランジスタ100上、より詳しくは、導電膜112a、112b及び酸化物半導体膜108上には絶縁膜114、116、及び絶縁膜118が設けられる。絶縁膜114、116、118は、トランジスタ100の保護絶縁膜としての機能を有する。

20

## 【0038】

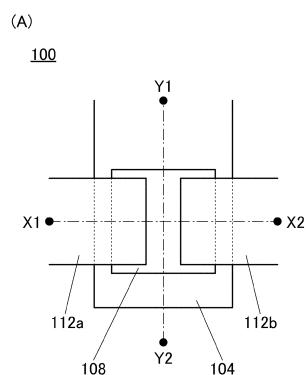

ここで、図2を用いて酸化物半導体膜108について説明を行う。図2(A)(B)は、図1(B)に示す酸化物半導体膜108近傍の拡大図である。

## 【0039】

図1(B)及び図2(A)(B)に示すように、酸化物半導体膜108は、チャネル領域108iと、n型領域108nと、を有する。チャネル領域108iは、ソース電極及びドレイン電極として機能する導電膜112a、112bの間の領域である。また、n型領域108nは、ソース電極及びドレイン電極として機能する導電膜112a、112bと接する領域に形成される。

30

## 【0040】

なお、図2(A)は、チャネル領域108iの上面がn型領域108nの下面と概ね一致した構成であり、図2(B)は、チャネル領域108iの上面がn型領域108nの下面よりも下側に位置する構成である。チャネル領域108iの形状としては、図2(A)、及び図2(B)に示すいずれの構成でもよい。

## 【0041】

酸化物半導体膜108が有するチャネル領域108iに水素、水分等の不純物が混入すると、酸化物半導体膜108中に形成される酸素欠損と結合し、キャリアである電子が生じる。上述の不純物起因のキャリアが生じると、トランジスタ100がノーマリーオン特性になりやすい。したがって、酸化物半導体膜108が有するチャネル領域108i中の水素、水分等の不純物を減らすこと、及び酸化物半導体膜108が有するチャネル領域108i中の酸素欠損を減らすことが安定したトランジスタ特性を得る上でも重要となる。一方で、酸化物半導体膜108が有するn型領域108nとしては、ソース電極及びドレイン電極として機能する導電膜112a、112bと接合するため、抵抗が低い方が好みしい。そこで、本発明の一態様のトランジスタの構成においては、酸化物半導体膜108が有するn型領域108n中に酸素欠損を形成し、該酸素欠損に水素を結合させることで、低抵抗領域を形成する。酸素欠損としては、ソース電極及びドレイン電極として機能する導電膜112a、112bとなる導電膜を形成する際に酸化物半導体膜108の上部

40

50

に形成される。また、ソース電極及びドレイン電極として機能する導電膜 112a、112bを形成後、チャネル領域 108i となる領域の上部の酸素欠損が形成された領域を取り除き、且つ絶縁膜 114 及び絶縁膜 116 からチャネル領域 108i 中に酸素を移動させることで、チャネル領域 108i 中の酸素欠損を補填する。

#### 【0042】

上記構造とすることで、チャネル領域 108i においては、不純物濃度が低く、欠陥準位密度の低い（以下では、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性という）酸化物半導体膜とすることができます、且つn型領域 108n においては、ソース電極及びドレイン電極として機能する導電膜 112a、112bとの接触抵抗が低い酸化物半導体膜とすることができます。よって、電気特性の変動が抑制された半導体装置を提供することができる。10

#### 【0043】

なお、絶縁膜 114、116 は、化学量論的組成よりも過剰に酸素を含有する領域（酸素過剰領域）を有する。別言すると、絶縁膜 114、116 は、酸素を放出することが可能な絶縁膜である。なお、絶縁膜 114、116 に酸素過剰領域を設けるには、例えば、成膜後の絶縁膜 114、116 に酸素を添加して、酸素過剰領域を形成する。酸素の添加方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。なお、該プラズマ処理としては、酸素ガスを高周波電力によってプラズマ化させる装置（プラズマエッティング装置またはプラズマアッシング装置ともいう）を用いると好適である。20

#### 【0044】

また、昇温脱離ガス分析法（TDS（Thermal Desorption Spectroscopy））を用いて絶縁膜を測定することで、酸素の放出量を測定することができます。例えば、絶縁膜 114、116 を昇温脱離ガス分析法において測定した場合、酸素原子の放出量が  $8.0 \times 10^{14}$  atoms/cm<sup>2</sup> 以上、好ましくは  $1.0 \times 10^{15}$  atoms/cm<sup>2</sup> 以上、さらに好ましくは  $1.5 \times 10^{15}$  atoms/cm<sup>2</sup> 以上である。なお、昇温脱離ガス分析法における膜の表面温度は、100 以上 700 以下、好ましくは 100 以上 500 以下である。

#### 【0045】

また、本発明の一態様においては、絶縁膜 114、116 に酸素過剰領域を形成するため、絶縁膜 116 上に酸素の放出を抑制できる機能を有する保護膜（単に保護膜という場合もある）を形成し、該保護膜を通過させて、絶縁膜 114、116 に酸素を導入する。30

#### 【0046】

酸素の放出を抑制できる機能を有する保護膜としては、例えば、インジウム（In）と、亜鉛（Zn）、錫（Sn）、タンゲステン（W）、チタン（Ti）、またはシリコン（Si）の中から選ばれた一種を含む材料を用いることができる。とくに、保護膜としては、インジウムを含む導電膜、またはインジウムを含む半導体膜が好ましい。また、上記保護膜は、酸素の導入後に除去してもよい。インジウムを含む導電膜としては、タンゲステンを含むインジウム酸化物、タンゲステンを含むインジウム亜鉛酸化物、チタンを含むインジウム酸化物、チタンを含むインジウム錫酸化物、インジウム錫酸化物（In-Sn 酸化物：ITOともいう）、インジウム亜鉛酸化物（In-Zn 酸化物）、シリコンを含むインジウム錫酸化物（In-Sn-Si 酸化物：ITSOともいう）などの透光性を有する導電性材料が挙げられる。上述した中でも、酸素の放出を抑制できる機能を有する保護膜として、特にITSOを用いると、凹凸等を有する絶縁膜上にも被覆性がよく形成できるため好適である。40

#### 【0047】

次に、図1に示すトランジスタ 100 の構成について、より詳細に説明する。

#### 【0048】

##### <基板>

基板 102 の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度

10

20

30

40

50

の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板 102 として用いてもよい。また、シリコンや炭化シリコンなどを材料とした単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI 基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板 102 として用いてもよい。なお、基板 102 として、ガラス基板を用いる場合、第 6 世代 (1500 mm × 1850 mm)、第 7 世代 (1870 mm × 2200 mm)、第 8 世代 (2200 mm × 2400 mm)、第 9 世代 (2400 mm × 2800 mm)、第 10 世代 (2950 mm × 3400 mm) 等の大面積基板を用いることで、大型の表示装置を作製することができる。

#### 【0049】

また、基板 102 として、可撓性基板を用い、可撓性基板上に直接、トランジスタ 100 を形成してもよい。または、基板 102 とトランジスタ 100 の間に剥離層を設けてもよい。剥離層は、その上に半導体装置を一部あるいは全部完成させた後、基板 102 より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ 100 は耐熱性の劣る基板や可撓性の基板にも転載できる。

#### 【0050】

##### <導電膜>

ゲート電極として機能する導電膜 104、及びソース電極及びドレイン電極として機能する導電膜 112a、112b としては、クロム (Cr)、銅 (Cu)、アルミニウム (Al)、金 (Au)、銀 (Ag)、亜鉛 (Zn)、モリブデン (Mo)、タンタル (Ta)、チタン (Ti)、タンゲステン (W)、マンガン (Mn)、ニッケル (Ni)、鉄 (Fe)、コバルト (Co) から選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いてそれぞれ形成することができる。

#### 【0051】

また、導電膜 104、112a、112b は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンゲステン膜を積層する二層構造、窒化タンタル膜または窒化タンゲステン膜上にタンゲステン膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンゲステン、モリブデン、クロム、ネオジム、スカンジウムから選ばれた一または複数を組み合わせた合金膜、もしくは窒化膜を用いてもよい。

#### 【0052】

また、導電膜 104、112a、112b には、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。

#### 【0053】

また、導電膜 104、112a、112b には、Cu-X 合金膜 (X は、Mn、Ni、Cr、Fe、Co、Mo、Ta、または Ti) を適用してもよい。Cu-X 合金膜を用いることで、ウェットエッティングプロセスで加工できるため、製造コストを抑制することが可能となる。

#### 【0054】

##### <ゲート絶縁膜>

トランジスタ 100 のゲート絶縁膜として機能する絶縁膜 106、107 としては、プラズマ化学気相堆積 (PECVD: (Plasma Enhanced Chemical Vapour Deposition)) 法、スパッタリング法等により、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜、酸化アルミニウム膜

10

20

30

40

50

、酸化ハフニウム膜、酸化イットリウム膜、酸化ジルコニウム膜、酸化ガリウム膜、酸化タンタル膜、酸化マグネシウム膜、酸化ランタン膜、酸化セリウム膜および酸化ネオジム膜を一種以上含む絶縁層を、それぞれ用いることができる。なお、絶縁膜 106、107 の積層構造とせずに、上述の材料から選択された単層の絶縁膜、または 3 層以上の絶縁膜を用いてもよい。

#### 【0055】

なお、トランジスタ 100 の酸化物半導体膜 108 と接する絶縁膜 107 は、酸化物絶縁膜であることが好ましく、化学量論的組成よりも過剰に酸素を含有する領域（酸素過剰領域）を有することがより好ましい。別言すると、絶縁膜 107 は、酸素を放出することが可能な絶縁膜である。なお、絶縁膜 107 に酸素過剰領域を設けるには、例えば、酸素雰囲気下にて絶縁膜 107 を形成すればよい。または、成膜後の絶縁膜 107 に酸素を導入して、酸素過剰領域を形成してもよい。酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオン注入法、プラズマ処理等を用いることができる。

10

#### 【0056】

また、絶縁膜 107 として、酸化ハフニウムを用いる場合、以下の効果を奏する。酸化ハフニウムは、酸化シリコンや酸化窒化シリコンと比べて比誘電率が高い。したがって、酸化シリコンを用いた場合と比べて、絶縁膜 107 の膜厚を大きくできるため、トンネル電流によるリーク電流を小さくすることができる。すなわち、オフ電流の小さいトランジスタを実現することができる。さらに、結晶構造を有する酸化ハフニウムは、非晶質構造を有する酸化ハフニウムと比べて高い比誘電率を備える。したがって、オフ電流の小さいトランジスタとするためには、結晶構造を有する酸化ハフニウムを用いることが好ましい。結晶構造の例としては、単斜晶系や立方晶系などが挙げられる。ただし、本発明の一態様は、これらに限定されない。

20

#### 【0057】

なお、本実施の形態では、絶縁膜 106 として窒化シリコン膜を形成し、絶縁膜 107 として酸化シリコン膜を形成する。窒化シリコン膜は、酸化シリコン膜と比較して比誘電率が高く、酸化シリコン膜と同等の静電容量を得るのに必要な膜厚が大きいため、トランジスタのゲート絶縁膜として、窒化シリコン膜を含むことで絶縁膜を厚膜化することができる。よって、トランジスタ 100 の絶縁耐圧の低下を抑制、さらには絶縁耐圧を向上させて、トランジスタ 100 の静電破壊を抑制することができる。

30

#### 【0058】

##### <酸化物半導体膜>

酸化物半導体膜 108 は、In と、Zn と、M（M は、Ti、Ga、Y、Zr、La、Ce、Nd、Sn または Hf を表す）と、を有する。代表的には、酸化物半導体膜 108 は、In-Ga 酸化物、In-Zn 酸化物、In-M-Zn 酸化物を用いることができる。特に酸化物半導体膜 108 としては、In-M-Zn 酸化物を用いると好ましい。

#### 【0059】

酸化物半導体膜 108 が In-M-Zn 酸化物の場合、In-M-Zn 酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In-M-Zn を満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In:M:Zn = 1:1:1、In:M:Zn = 1:1:1.2、In:M:Zn = 2:1:3、In:M:Zn = 3:1:2、In:M:Zn = 4:2:4.1 が好ましい。

40

#### 【0060】

例えば、In-M-Zn 酸化物として、In:Ga:Zn = 4:2:4.1 [原子数比] のスパッタリングターゲットを用いて、酸化物半導体膜 108 を形成する場合、トランジスタの電界効果移動度を高められるため好適である。トランジスタの電界効果移動度を高めることで、例えば、4k × 2k（水平方向画素数 = 3840 画素、垂直方向画素数 = 2160 画素）または 8k × 4k（水平方向画素数 = 7680 画素、垂直方向画素数 = 4

50

320画素)に代表される高精細な表示装置の画素回路または駆動回路のトランジスタとして好適に用いることができる。

#### 【0061】

また、成膜される酸化物半導体膜108の原子数比はそれぞれ、上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む場合がある。例えば、スパッタリングターゲットとして、原子数比が $In : Ga : Zn = 4 : 2 : 4$ 、 $In : Ga : Zn = 4 : 2 : 3$ 近傍となる場合がある。また、スパッタリングターゲットとして、原子数比が $In : Ga : Zn = 1 : 1 : 1$ 、 $In : Ga : Zn = 1 : 1 : 1$ 近傍となる場合がある。

10

#### 【0062】

なお、酸化物半導体膜108が $In - M - Zn$ 酸化物膜であるとき、 $Zn$ 及び $O$ を除いての $In$ と $M$ の原子数比率は、好ましくは $In$ が25atomic%より高く、 $M$ が75atomic%未満、さらに好ましくは $In$ が34atomic%より高く、 $M$ が66atomic%未満とする。

#### 【0063】

また、酸化物半導体膜108は、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタのオフ電流を低減することができる。

20

#### 【0064】

また、酸化物半導体膜108の厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

#### 【0065】

なお、これらに限られず、必要とするトランジスタの半導体特性及び電気特性(電界効果移動度、しきい値電圧等)に応じて適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体膜108のキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0066】

なお、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、該酸化物半導体膜にチャネル領域が形成されるトランジスタは、しきい値電圧がマイナスとなる電気特性(ノーマリーオンともいう。)になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、オフ電流が著しく小さく、チャネル幅が $1 \times 10^6 \mu m$ でチャネル長 $L$ が $10 \mu m$ の素子であっても、ソース電極とドレイン電極間の電圧(ドレイン電圧)が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13} A$ 以下という特性を得ることができる。

30

#### 【0067】

したがって、上記高純度真性、または実質的に高純度真性の酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとすることができます。なお、酸化物半導体膜のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等がある。

40

#### 【0068】

酸化物半導体膜108に含まれる水素は、金属原子と結合する酸素と反応して水になると共に、酸素が脱離した格子(または酸素が脱離した部分)に酸素欠損を形成する。該酸

50

素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。従って、水素が含まれている酸化物半導体膜を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体膜 108 は水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体膜 108 において、S I M S ( Secondary Ion Mass Spectrometry ) 分析により得られる水素濃度を、 $2 \times 10^{20}$  atoms / cm<sup>3</sup> 以下、好ましくは  $5 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $1 \times 10^{19}$  atoms / cm<sup>3</sup> 以下、 $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは  $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下、さらに好ましくは  $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以下とする。

#### 【 0069 】

酸化物半導体膜 108 において、第 14 族元素の一つであるシリコンや炭素が含まれると、酸化物半導体膜 108 において酸素欠損が増加し、n型化してしまう。このため、酸化物半導体膜 108 におけるシリコンや炭素の濃度と、酸化物半導体膜 108 と隣接する膜との界面近傍のシリコンや炭素の濃度 ( S I M S 分析により得られる濃度 ) を、 $2 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは  $2 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。

#### 【 0070 】

また、酸化物半導体膜 108 において、S I M S 分析により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは  $2 \times 10^{16}$  atoms / cm<sup>3</sup> 以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体膜 108 のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。

#### 【 0071 】

また、酸化物半導体膜 108 に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体膜を用いたトランジスタはノーマリーオン特性となりやすい。従って、該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、S I M S 分析により得られる窒素濃度は、 $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下にすることが好ましい。

#### 【 0072 】

また、酸化物半導体膜 108 に用いることのできる酸化物半導体については、実施の形態 2 にて詳細を説明する。

#### 【 0073 】

##### < 保護絶縁膜 >

絶縁膜 114、116、118 は、保護絶縁膜としての機能を有する。絶縁膜 114、116 は酸素を有し、絶縁膜 118 は窒素を有する。また、絶縁膜 114 は、酸素を透過することのできる絶縁膜である。なお、絶縁膜 114 は、後に形成する絶縁膜 116 を形成する際の、酸化物半導体膜 108 へのダメージ緩和膜としても機能する。

#### 【 0074 】

絶縁膜 114 としては、厚さが 5 nm 以上 150 nm 以下、好ましくは 5 nm 以上 50 nm 以下の酸化シリコン膜または酸化窒化シリコン膜を用いることができる。

#### 【 0075 】

また、絶縁膜 114 は、欠陥量が少ないことが好ましく、代表的には、E S R ( Electron Spin Resonance ) 測定により、シリコンのダンギリングボンドに由来する  $g = 2.001$  に現れる信号のスピン密度が  $3 \times 10^{17}$  spins / cm<sup>3</sup> 以下であることが好ましい。これは、絶縁膜 114 に含まれる欠陥密度が多いと、該欠陥に酸素が結合してしまい、絶縁膜 114 における酸素の透過量が減少してしまうためである。

#### 【 0076 】

10

20

30

40

50

なお、絶縁膜 114においては、外部から絶縁膜 114に入った酸素が全て絶縁膜 114の外部に移動せず、絶縁膜 114にとどまる酸素もある。また、絶縁膜 114に酸素が入ると共に、絶縁膜 114に含まれる酸素が絶縁膜 114の外部へ移動することで、絶縁膜 114において酸素の移動が生じる場合もある。絶縁膜 114として酸素を透過することができる酸化物絶縁膜を形成すると、絶縁膜 114上に設けられる、絶縁膜 116から脱離する酸素を、絶縁膜 114を通過させて酸化物半導体膜 108に移動させることができる。

#### 【0077】

また、絶縁膜 114は、窒素酸化物に起因する準位密度が低い酸化物絶縁膜を用いて形成することができる。なお、当該窒素酸化物に起因する準位密度は、酸化物半導体膜の価電子帯の上端のエネルギー ( $E_{V_{\text{Ox}}}$ ) と酸化物半導体膜の伝導帯の下端のエネルギー ( $E_{C_{\text{Ox}}}$ ) の間に形成され得る場合がある。上記の酸化物絶縁膜として、窒素酸化物の放出量が少ない酸化窒化シリコン膜、または窒素酸化物の放出量が少ない酸化窒化アルミニウム膜等を用いることができる。

#### 【0078】

なお、窒素酸化物の放出量の少ない酸化窒化シリコン膜は、昇温脱離ガス分析法において、窒素酸化物の放出量よりアンモニアの放出量が多い膜であり、代表的にはアンモニアの放出量が  $1 \times 10^{18}$  個 /  $\text{cm}^3$  以上  $5 \times 10^{19}$  個 /  $\text{cm}^3$  以下である。なお、アンモニアの放出量は、膜の表面温度が 50 以上 650 以下、好ましくは 50 以上 550 以下の加熱処理による放出量とする。

#### 【0079】

窒素酸化物 ( $\text{NO}_x$ 、 $x$  は 0 以上 2 以下、好ましくは 1 以上 2 以下)、代表的には  $\text{NO}_2$  または  $\text{NO}$  は、絶縁膜 114などに準位を形成する。当該準位は、酸化物半導体膜 108 のエネルギーギャップ内に位置する。そのため、窒素酸化物が、絶縁膜 114 及び酸化物半導体膜 108 の界面近傍に拡散すると、当該準位が絶縁膜 114 側において電子をトラップする場合がある。この結果、トラップされた電子が、絶縁膜 114 及び酸化物半導体膜 108 界面近傍に留まるため、トランジスタのしきい値電圧をプラス方向にシフトさせてしまう。

#### 【0080】

また、窒素酸化物は、加熱処理においてアンモニア及び酸素と反応する。絶縁膜 114 に含まれる窒素酸化物は、加熱処理において、絶縁膜 116 に含まれるアンモニアと反応するため、絶縁膜 114 に含まれる窒素酸化物が低減される。このため、絶縁膜 114 及び酸化物半導体膜 108 の界面近傍において、電子がトラップされにくい。

#### 【0081】

絶縁膜 114として、上記の酸化物絶縁膜を用いることで、トランジスタのしきい値電圧のシフトを低減することが可能であり、トランジスタの電気特性の変動を低減することができる。

#### 【0082】

なお、トランジスタの作製工程の加熱処理、代表的には 300 以上基板歪み点未満の加熱処理により、絶縁膜 114 は、100 K 以下の ESR で測定して得られたスペクトルにおいて  $g$  値が 2.037 以上 2.039 以下の第 1 のシグナル、 $g$  値が 2.001 以上 2.003 以下の第 2 のシグナル、及び  $g$  値が 1.964 以上 1.966 以下の第 3 のシグナルが観測される。なお、第 1 のシグナル及び第 2 のシグナルのスプリット幅、並びに第 2 のシグナル及び第 3 のシグナルのスプリット幅は、X バンドの ESR 測定において約 5 mT である。また、 $g$  値が 2.037 以上 2.039 以下の第 1 のシグナル、 $g$  値が 2.001 以上 2.003 以下の第 2 のシグナル及び  $g$  値が 1.964 以上 1.966 以下の第 3 のシグナルのスピンの密度の合計が  $1 \times 10^{18}$  spins /  $\text{cm}^3$  未満であり、代表的には  $1 \times 10^{17}$  spins /  $\text{cm}^3$  以上  $1 \times 10^{18}$  spins /  $\text{cm}^3$  未満である。

#### 【0083】

10

20

30

40

50

なお、100K以下のESRスペクトルにおいてg値が2.037以上2.039以下の第1シグナル、g値が2.001以上2.003以下の第2のシグナル、及びg値が1.964以上1.966以下の第3のシグナルは、窒素酸化物( $\text{NO}_x$ 、xは0以上2以下、好ましくは1以上2以下)起因のシグナルに相当する。窒素酸化物の代表例としては、一酸化窒素、二酸化窒素等がある。即ち、g値が2.037以上2.039以下の第1のシグナル、g値が2.001以上2.003以下の第2のシグナル及びg値が1.964以上1.966以下の第3のシグナルのスピンの密度の合計が少ないほど、酸化物絶縁膜に含まれる窒素酸化物の含有量が少ないとえる。

#### 【0084】

また、上記の酸化物絶縁膜は、SIMS分析で測定される窒素濃度が $6 \times 10^{20} \text{ atoms/cm}^3$ 以下である。

10

#### 【0085】

基板温度が220以上、または280以上、または350以上であり、シラン及び一酸化二窒素を用いたPECVD法を用いて、上記の酸化物絶縁膜を形成することで、緻密であり、且つ硬度の高い膜を形成することができる。

#### 【0086】

絶縁膜116は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、TDS分析にて、酸素原子に換算して、酸素の放出量が $8.0 \times 10^{14} \text{ atoms/cm}^2$ 以上、好ましくは $1.0 \times 10^{15} \text{ atoms/cm}^2$ 以上である酸化物絶縁膜である。なお、上記TDS分析時における膜の表面温度は、100以上700以下、好ましくは100以上500以下である。

20

#### 【0087】

絶縁膜116としては、厚さが30nm以上500nm以下、好ましくは50nm以上400nm以下の、酸化シリコン膜または酸化窒化シリコン膜を用いることができる。

#### 【0088】

また、絶縁膜116は、欠陥量が少ないことが好ましく、代表的には、ESR測定により、シリコンのダングリングボンドに由来する $g = 2.001$ に現れる信号のスピン密度が $1.5 \times 10^{18} \text{ spins/cm}^3$ 未満、さらには $1 \times 10^{18} \text{ spins/cm}^3$ 以下であることが好ましい。なお、絶縁膜116は、絶縁膜114と比較して酸化物半導体膜108から離れているため、絶縁膜114より、欠陥密度が多くともよい。

30

#### 【0089】

また、絶縁膜114、116は、同種の材料の絶縁膜を用いることができるため、絶縁膜114と絶縁膜116の界面が明確に確認できない場合がある。したがって、本実施の形態においては、絶縁膜114と絶縁膜116の界面は、破線で図示している。なお、本実施の形態においては、絶縁膜114と絶縁膜116の2層構造について説明したが、これに限定されず、例えば、絶縁膜114または絶縁膜116のいずれか一方の単層構造としてもよい。

#### 【0090】

絶縁膜118は、窒素を有する。また、絶縁膜118は、窒素と、シリコンとを有する。また、絶縁膜118は、酸素、水素、水、アルカリ金属、アルカリ土類金属等をプロッキングできる機能を有する。絶縁膜118を設けることで、酸化物半導体膜108からの酸素の外部への拡散と、絶縁膜114、116に含まれる酸素の外部への拡散と、外部から酸化物半導体膜108への水素、水等の入り込みを防ぐことができる。絶縁膜118としては、例えば、窒化物絶縁膜を用いることができる。該窒化物絶縁膜としては、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。なお、酸素、水素、水、アルカリ金属、アルカリ土類金属等のプロッキング効果を有する窒化物絶縁膜の代わりに、酸素、水素、水等のプロッキング効果を有する酸化物絶縁膜を設けてもよい。酸素、水素、水等のプロッキング効果を有する酸化物絶縁膜としては、酸化アル

40

50

ミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

【0091】

なお、上記記載の、導電膜、絶縁膜、酸化物半導体膜などの様々な膜の形成方法としては、スパッタリング法、化学気相堆積(CVD)法、真空蒸着法、パルスレーザ堆積(PLD)法などが挙げられる。また、上記記載の、導電膜、絶縁膜、酸化物半導体膜などの様々な膜の形成方法としては、プラズマ化学気相堆積(PECVD)法、熱CVD(Chemical Vapor Deposition)法、またはALD(Atomic Layer Deposition)法としてもよい。熱CVD法の例としてMOCVD(Metal Organic Chemical Vapor Deposition)法が挙げられる。また、上記記載の、導電膜、絶縁膜、酸化物半導体膜などの様々な膜の形成方法としては、塗布法や印刷法でもよい。

【0092】

熱CVD法は、プラズマを使わない成膜方法のため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

【0093】

熱CVD法は、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。

【0094】

また、ALD法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次にチャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。例えば、それぞれのスイッチングバルブ(高速バルブとも呼ぶ)を切り替えて2種類以上の原料ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないように第1の原料ガスと同時またはその後に不活性ガス(アルゴン、或いは窒素など)などを導入し、第2の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキャリアガスとなり、また、第2の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第1の原料ガスを排出した後、第2の原料ガスを導入してもよい。第1の原料ガスが基板の表面に吸着して第1の層を成膜し、後から導入される第2の原料ガスと反応して、第2の層が第1の層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なFETを作製する場合に適している。

【0095】

ALD法、またはMOCVD法などの熱CVD法は、上記実施形態の導電膜、絶縁膜、酸化物半導体膜、金属酸化膜などの様々な膜を形成することができ、例えば、In-Ga-Zn-O膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、及びジメチル亜鉛を用いる。なお、トリメチルインジウムの化学式は、In(CH<sub>3</sub>)<sub>3</sub>である。また、トリメチルガリウムの化学式は、Ga(CH<sub>3</sub>)<sub>3</sub>である。また、ジメチル亜鉛の化学式は、Zn(CH<sub>3</sub>)<sub>2</sub>である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム(化学式Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>)を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛(化学式Zn(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>)を用いることもできる。

【0096】

例えば、ALDを利用する成膜装置により酸化ハフニウム膜を形成する場合には、溶媒とハフニウム前駆体化合物を含む液体(ハフニウムアルコキシドや、テトラキスジメチルアミドハフニウム(TDMAH)などのハフニウムアミド)を気化させた原料ガスと、酸化剤としてオゾン(O<sub>3</sub>)の2種類のガスを用いる。なお、テトラキスジメチルアミドハフニウムの化学式はHf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>である。また、他の材料液としては、テト

10

20

30

40

50

ラキス(エチルメチルアミド)ハフニウムなどがある。

【0097】

例えば、ALDを利用する成膜装置により酸化アルミニウム膜を形成する場合には、溶媒とアルミニウム前駆体化合物を含む液体(トリメチルアルミニウム(TMA)など)を気化させた原料ガスと、酸化剤としてH<sub>2</sub>Oの2種類のガスを用いる。なお、トリメチルアルミニウムの化学式はAl(CH<sub>3</sub>)<sub>3</sub>である。また、他の材料液としては、トリス(ジメチルアミド)アルミニウム、トリイソブチルアルミニウム、アルミニウムトリス(2,2,6,6-テトラメチル-3,5-ヘプタンジオナート)などがある。

【0098】

例えば、ALDを利用する成膜装置により酸化シリコン膜を形成する場合には、ヘキサクロロジシランを被成膜面に吸着させ、吸着物に含まれる塩素を除去し、酸化性ガス(O<sub>2</sub>、一酸化二窒素)のラジカルを供給して吸着物と反応させる。

10

【0099】

例えば、ALDを利用する成膜装置によりタンゲステン膜を成膜する場合には、WF<sub>6</sub>ガスとB<sub>2</sub>H<sub>6</sub>ガスを用いて初期タンゲステン膜を形成し、その後、WF<sub>6</sub>ガスとH<sub>2</sub>ガスを用いてタンゲステン膜を形成する。なお、B<sub>2</sub>H<sub>6</sub>ガスに代えてSiH<sub>4</sub>ガスを用いてもよい。

【0100】

例えば、ALDを利用する成膜装置により酸化物半導体膜、例えばIn-Ga-Zn-O膜を成膜する場合には、In(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>3</sub>ガスを用いてIn-O層を形成し、その後、Ga(CH<sub>3</sub>)<sub>3</sub>ガスとO<sub>3</sub>ガスを用いてGaO層を形成し、更にその後Zn(CH<sub>3</sub>)<sub>2</sub>ガスとO<sub>3</sub>ガスとを用いてZnO層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜてIn-Ga-O層やIn-Zn-O層、Ga-Zn-O層などの混合化合物層を形成しても良い。なお、O<sub>3</sub>ガスに変えてAr等の不活性ガスでバーリングして得られたH<sub>2</sub>Oガスを用いても良いが、Hを含まないO<sub>3</sub>ガスを用いる方が好ましい。また、In(CH<sub>3</sub>)<sub>3</sub>ガスの代わりに、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いても良い。また、Ga(CH<sub>3</sub>)<sub>3</sub>ガスの代わりに、Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いても良い。また、Zn(CH<sub>3</sub>)<sub>2</sub>ガスを用いても良い。

20

【0101】

<半導体装置の構成例2>

30

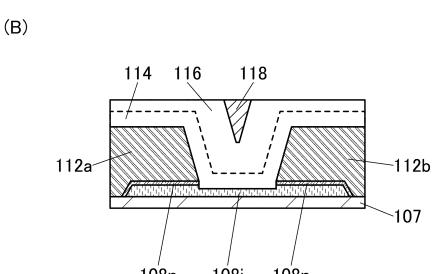

次に、図1(A)(B)(C)に示すトランジスタ100と異なる構成例について、図3(A)(B)(C)を用いて説明する。なお、先に説明した機能と同様の機能を有する場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0102】

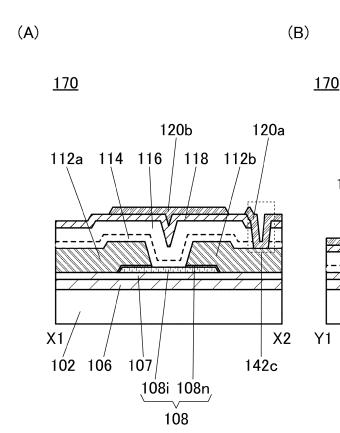

図3(A)は、本発明の一態様の半導体装置であるトランジスタ170の上面図であり、図3(B)は、図3(A)に示す一点鎖線X1-X2間における切断面の断面図に相当し、図3(C)は、図3(A)に示す一点鎖線Y1-Y2間における切断面の断面図に相当する。

【0103】

トランジスタ170は、基板102上の第1のゲート電極として機能する導電膜104と、基板102及び導電膜104上の絶縁膜106と、絶縁膜106上の絶縁膜107と、絶縁膜107上の酸化物半導体膜108と、酸化物半導体膜108に電気的に接続されるソース電極として機能する導電膜112aと、酸化物半導体膜108に電気的に接続されるドレイン電極として機能する導電膜112bと、酸化物半導体膜108及び導電膜112a、112b上の絶縁膜114と、絶縁膜114上の絶縁膜116と、絶縁膜116上の絶縁膜118と、絶縁膜118上の導電膜120a、120bと、を有する。

40

【0104】

トランジスタ170としては、先に示すトランジスタ100と同様に、酸化物半導体膜108は、チャネル領域108iと、n型領域108nと、を有する。チャネル領域108iにおいては、酸素欠損が低減され高純度真性の酸化物半導体膜とすることができる、且

50

つ<sub>n</sub>型領域108nにおいては、ソース電極及びドレイン電極として機能する導電膜112a、112bと接触抵抗が低い酸化物半導体膜とすることができる。よって、電気特性の変動が抑制された半導体装置を提供することができる。

【0105】

また、絶縁膜106、107は、トランジスタ170の第1のゲート絶縁膜としての機能を有する。また、絶縁膜114、116、118は、トランジスタ170の第2のゲート絶縁膜としての機能を有する。また、導電膜120aは、例えば、表示装置に用いる画素電極としての機能を有する。また、導電膜120aは、絶縁膜114、116、118に設けられる開口部142cを介して、導電膜112bと接続される。また、導電膜120bは、第2のゲート電極(バックゲート電極ともいう)として機能する。

10

【0106】

また、図3(C)に示すように導電膜120bは、絶縁膜106、107、114、116、118に設けられる開口部142a、142bにおいて、第1のゲート電極として機能する導電膜104に接続される。よって、導電膜120bと導電膜104とは、同じ電位が与えられる。

【0107】

なお、本実施の形態においては、開口部142a、142bを設け、導電膜120bと導電膜104を接続する構成について例示したが、これに限定されない。例えば、開口部142aまたは開口部142bのいずれか一方の開口部のみを形成し、導電膜120bと導電膜104を接続する構成、または開口部142a及び開口部142bを設けずに、導電膜120bと導電膜104を接続しない構成としてもよい。なお、導電膜120bと導電膜104を接続しない構成の場合、導電膜120bと導電膜104には、それぞれ異なる電位を与えることができる。

20

【0108】

また、図3(B)に示すように、酸化物半導体膜108は、第1のゲート電極として機能する導電膜104と、第2のゲート電極として機能する導電膜120bのそれぞれと対向するように位置し、2つのゲート電極として機能する導電膜に挟まれている。第2のゲート電極として機能する導電膜120bのチャネル長方向の長さ及びチャネル幅方向の長さは、酸化物半導体膜108のチャネル長方向の長さ及びチャネル幅方向の長さよりもそれぞれ長く、酸化物半導体膜108の全体は、絶縁膜114、116、118を介して導電膜120bに覆われている。また、第2のゲート電極として機能する導電膜120bと第1のゲート電極として機能する導電膜104とは、絶縁膜106、107、114、116、118に設けられる開口部142a、142bにおいて接続されるため、酸化物半導体膜108のチャネル幅方向の側面は、絶縁膜114、116、118を介して第2のゲート電極として機能する導電膜120bと対向している。

30

【0109】

別言すると、トランジスタ170のチャネル幅方向において、第1のゲート電極として機能する導電膜104及び第2のゲート電極として機能する導電膜120bは、第1のゲート絶縁膜として機能する絶縁膜106、107及び第2のゲート絶縁膜として機能する絶縁膜114、116、118に設けられる開口部において接続すると共に、第1のゲート絶縁膜として機能する絶縁膜106、107及び第2のゲート絶縁膜として機能する絶縁膜114、116、118を介して酸化物半導体膜108を囲む構成である。

40

【0110】

このような構成を有することで、トランジスタ170に含まれる酸化物半導体膜108を、第1のゲート電極として機能する導電膜104及び第2のゲート電極として機能する導電膜120bの電界によって電気的に囲むことができる。トランジスタ170のように、第1のゲート電極及び第2のゲート電極の電界によって、チャネル領域が形成される酸化物半導体膜を電気的に囲むトランジスタのデバイス構造をSurrounded channel( S - channel )構造と呼ぶことができる。

【0111】

50

トランジスタ 170 は、S-channel 構造を有するため、第 1 のゲート電極として機能する導電膜 104 によってチャネルを誘起させるための電界を効果的に酸化物半導体膜 108 に印加することができるため、トランジスタ 170 の電流駆動能力が向上し、高いオン電流特性を得ることが可能となる。また、オン電流を高くすることが可能であるため、トランジスタ 170 を微細化することが可能となる。また、トランジスタ 170 は、第 1 のゲート電極として機能する導電膜 104 及び第 2 のゲート電極として機能する導電膜 120b によって囲まれた構造を有するため、トランジスタ 170 の機械的強度を高めることができる。

【0112】

<半導体装置の構成例 3>

次に、図 3 (A) (B) (C) に示すトランジスタ 170 と異なる構成例について、図 4 (A) (B) を用いて説明する。なお、先に説明した機能と同様の機能を有する場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0113】

図 4 (A) は、図 3 (A) の一点鎖線 X1 - X2 間における切断面の断面図に相当し、図 4 (B) は、図 3 (A) に示す一点鎖線 Y1 - Y2 間における切断面の断面図に相当する。

【0114】

図 4 (A) (B) に示すトランジスタ 170 は、図 3 (B) (C) に示すトランジスタ 170 のゲート電極として機能する導電膜 104 を設けない構成である。すなわち、図 4 (A) (B) に示すトランジスタ 170 は、酸化物半導体膜 108 の上方にゲート電極として機能する導電膜 120b を有する。すなわち、トップゲート型のシングルゲートのトランジスタである。

【0115】

<半導体装置の構成例 4>

次に、図 1 (A) (B) (C) に示すトランジスタ 100 と異なる構成例について、図 5 (A) (B) (C) (D) を用いて説明する。なお、先に説明した機能と同様の機能を有する場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0116】

図 5 (A) (B) (C) (D) は、図 1 (B) (C) に示すトランジスタ 100 の変形例の断面図である。

【0117】

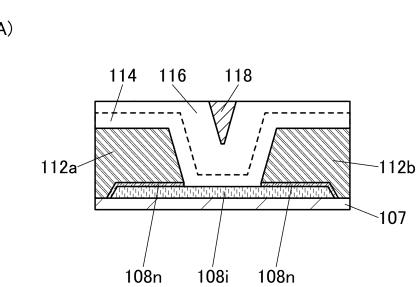

図 5 (A) (B) に示すトランジスタ 100A は、図 1 (B) (C) に示すトランジスタ 100 が有する酸化物半導体膜 108 を 3 層の積層構造としている。より具体的には、トランジスタ 100A が有する酸化物半導体膜 108 は、酸化物半導体膜 108a と、酸化物半導体膜 108b と、酸化物半導体膜 108c と、を有する。また、酸化物半導体膜 108a は、高純度領域 108a\_i と、n 型領域 108a\_n と、を有し、酸化物半導体膜 108b は、チャネル領域 108b\_i と、n 型領域 108b\_n と、を有し、酸化物半導体膜 108c は、高純度領域 108c\_i と、n 型領域 108c\_n と、を有する。

【0118】

図 5 (C) (D) に示すトランジスタ 100B は、図 1 (B) (C) に示すトランジスタ 100 が有する酸化物半導体膜 108 を 2 層の積層構造としている。より具体的には、トランジスタ 100B が有する酸化物半導体膜 108 は、酸化物半導体膜 108b と、酸化物半導体膜 108c と、を有する。また、酸化物半導体膜 108b は、チャネル領域 108b\_i と、n 型領域 108b\_n と、を有し、酸化物半導体膜 108c は、高純度領域 108c\_i と、n 型領域 108c\_n と、を有する。

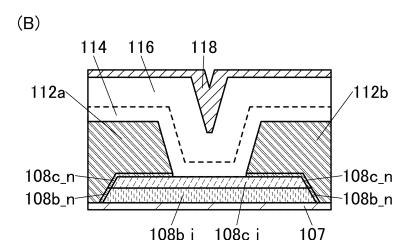

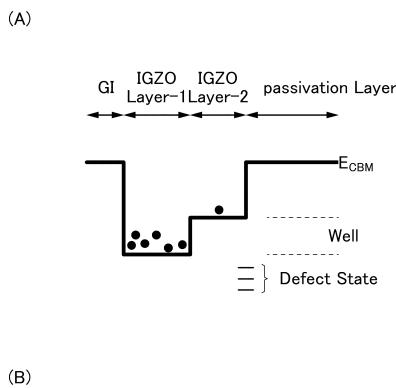

【0119】

なお、図 5 (A) に示す酸化物半導体膜 108 近傍の拡大図を図 6 (A) に、図 5 (C) に示す酸化物半導体膜 108 近傍の拡大図を図 6 (B) に、それぞれ示す。

10

20

30

40

50

## 【0120】

図6(A)(B)に示すように、酸化物半導体膜108は、高純度領域108a\_i、チャネル領域108b\_i、及び高純度領域108c\_iと、n型領域108a\_n、108b\_n、108c\_nと、を有する。チャネル領域108b\_iは、ソース電極及びドレイン電極として機能する導電膜112a、112bの間の領域である。また、n型領域108a\_n、108b\_n、108c\_nは、ソース電極及びドレイン電極として機能する導電膜112a、112bと接する領域に形成される。

## 【0121】

トランジスタ100Aとしては、先に示すトランジスタ100と同様に、高純度領域108a\_i、チャネル領域108b\_i、及び高純度領域108c\_iにおいては、酸素欠損が低減され高純度真性の酸化物半導体とすることができる、且つn型領域108a\_n、108b\_n、108c\_nにおいては、ソース電極及びドレイン電極として機能する導電膜112a、112bと接触抵抗が低い酸化物半導体膜108とすることができる。よって、電気特性の変動が抑制された半導体装置を提供することができる。

10

## 【0122】

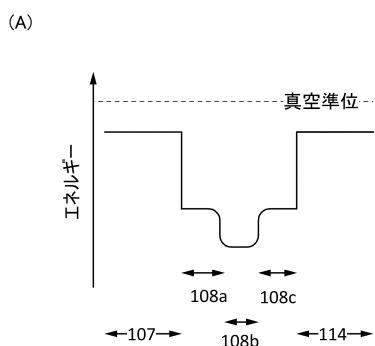

ここで、酸化物半導体膜108a、108b、108c、及び酸化物半導体膜108a、108b、108cに接する絶縁膜のバンド構造について、図7を用いて説明する。

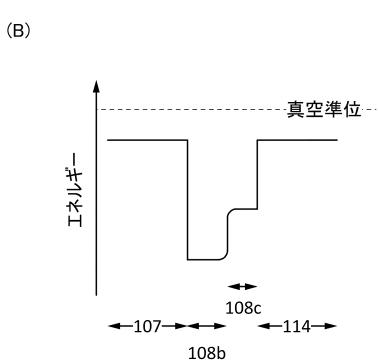

## 【0123】

図7(A)は、絶縁膜107、酸化物半導体膜108a、108b、108c、及び絶縁膜114を有する積層構造の膜厚方向のバンド構造の一例である。また、図7(B)は、絶縁膜107、酸化物半導体膜108b、108c、及び絶縁膜114を有する積層構造の膜厚方向のバンド構造の一例である。なお、バンド構造は、理解を容易にするため絶縁膜107、酸化物半導体膜108a、108b、108c、及び絶縁膜114の伝導帯下端のエネルギー準位(Ec)を示す。

20

## 【0124】

また、図7(A)は、絶縁膜107、114として酸化シリコン膜を用い、酸化物半導体膜108aとして金属元素の原子数比をIn:Ga:Zn=1:3:2の金属酸化物ターゲットを用いて形成される酸化物半導体膜を用い、酸化物半導体膜108bとして金属元素の原子数比をIn:Ga:Zn=1:1:1の金属酸化物ターゲットを用いて形成される酸化物半導体膜を用い、酸化物半導体膜108cとして金属元素の原子数比をIn:Ga:Zn=1:3:2の金属酸化物ターゲットを用いて形成される酸化物半導体膜を用いる構成のバンド図である。

30

## 【0125】

また、図7(B)は、絶縁膜107、114として酸化シリコン膜を用い、酸化物半導体膜108bとして金属元素の原子数比をIn:Ga:Zn=1:1:1の金属酸化物ターゲットを用いて形成される酸化物半導体膜を用い、酸化物半導体膜108cとして金属元素の原子数比をIn:Ga:Zn=1:3:2の金属酸化物ターゲットを用いて形成される金属酸化膜を用いる構成のバンド図である。

## 【0126】

図7(A)(B)に示すように、酸化物半導体膜108a、108b、108cにおいて、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、連続的に変化または連続接合するともいうことができる。このようなバンド構造を有するためには、酸化物半導体膜108aと酸化物半導体膜108bとの界面、または酸化物半導体膜108bと酸化物半導体膜108cとの界面において、トラップ中心や再結合中心のような欠陥準位を形成するような不純物が存在しないとする。

40

## 【0127】

酸化物半導体膜108a、108b、108cに連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置(スパッタリング装置)を用いて各膜を大気に触れさせることなく連続して積層すればよい。

## 【0128】

50

図7(A)(B)に示す構成とすることで酸化物半導体膜108bがウェル(井戸)となり、上記積層構造を用いたトランジスタにおいて、チャネル領域が酸化物半導体膜108bに形成されることがわかる。

#### 【0129】

なお、酸化物半導体膜108a、108cを形成しない場合に酸化物半導体膜108bに形成されうるトラップ準位は、上記積層構造とすることで、酸化物半導体膜108a、108cに形成される。したがって、酸化物半導体膜108bからトラップ準位を離すことができる。

#### 【0130】

また、トラップ準位がチャネル領域として機能する酸化物半導体膜108bの伝導帯下端のエネルギー準位(Ec)より真空準位に遠くなることがあり、トラップ準位に電子が蓄積しやすくなってしまう。トラップ準位に電子が蓄積されることで、マイナスの固定電荷となり、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。したがって、トラップ準位が酸化物半導体膜108bの伝導帯下端のエネルギー準位(Ec)より真空準位に近くなるような構成すると好ましい。このようにすることで、トラップ準位に電子が蓄積しにくくなり、トランジスタのオン電流を増大させることが可能であると共に、電界効果移動度を高めることができる。

10

#### 【0131】

また、図7(A)(B)において、酸化物半導体膜108a、108cは、酸化物半導体膜108bよりも伝導帯下端のエネルギー準位が真空準位に近く、代表的には、酸化物半導体膜108bの伝導帯下端のエネルギー準位と、酸化物半導体膜108a、108cの伝導帯下端のエネルギー準位との差が、0.15eV以上、または0.5eV以上、かつ2eV以下、または1eV以下である。すなわち、酸化物半導体膜108a、108cの電子親和力と、酸化物半導体膜108bの電子親和力との差が、0.15eV以上、または0.5eV以上、かつ2eV以下、または1eV以下である。

20

#### 【0132】

このような構成を有することで、酸化物半導体膜108bが電流の主な経路となり、チャネル領域として機能する。また、酸化物半導体膜108a、108cは、チャネル領域が形成される酸化物半導体膜108bを構成する金属元素の一種以上から構成される酸化物半導体膜であるため、酸化物半導体膜108aと酸化物半導体膜108bとの界面、または酸化物半導体膜108bと酸化物半導体膜108cとの界面において、界面散乱が起こりにくい。従って、該界面においてはキャリアの動きが阻害されないため、トランジスタの電界効果移動度が高くなる。

30

#### 【0133】

また、酸化物半導体膜108a、108cは、チャネル領域の一部として機能することを防止するため、導電率が十分に低い材料を用いるものとする。または、酸化物半導体膜108a、108cには、電子親和力(真空準位と伝導帯下端のエネルギー準位との差)が酸化物半導体膜108bよりも小さく、伝導帯下端のエネルギー準位が酸化物半導体膜108bの伝導帯下端エネルギー準位と差分(バンドオフセット)を有する材料を用いるものとする。また、ドレイン電圧の大きさに依存したしきい値電圧の差が生じることを抑制するためには、酸化物半導体膜108a、108cの伝導帯下端のエネルギー準位が、酸化物半導体膜108bの伝導帯下端のエネルギー準位よりも0.2eVより真空準位に近い材料、好ましくは0.5eV以上真空準位に近い材料を適用することが好ましい。

40

#### 【0134】

また、酸化物半導体膜108a、108cは、膜中にスピネル型の結晶構造が含まれないことが好ましい。酸化物半導体膜108a、108cの膜中にスピネル型の結晶構造を含む場合、該スピネル型の結晶構造と他の領域との界面において、導電膜112a、112bの構成元素が酸化物半導体膜108bへ拡散してしまう場合がある。なお、酸化物半導体膜108a、108cが後述するCAC-OSである場合、導電膜112a、112bの構成元素、例えば、銅元素のブロッキング性が高くなり好ましい。

50

## 【0135】

酸化物半導体膜108a、108cの膜厚は、導電膜112a、112bの構成元素が酸化物半導体膜108bに拡散することを抑制することができる膜厚以上であって、絶縁膜114から酸化物半導体膜108bへの酸素の供給を抑制する膜厚未満とする。例えば、酸化物半導体膜108a、108cの膜厚が10nm以上であると、導電膜112a、112bの構成元素が酸化物半導体膜108bへ拡散するのを抑制することができる。また、酸化物半導体膜108a、108cの膜厚を100nm以下とすると、絶縁膜114、116から酸化物半導体膜108bへ効果的に酸素を供給することができる。

## 【0136】

酸化物半導体膜108a、108cがIn-M-Zn酸化物であるとき、MとしてTi、Ga、Y、Zr、La、Ce、Nd、SnまたはHfをInより高い原子数比で有することで、酸化物半導体膜108a、108cのエネルギーギャップを大きく、電子親和力を小さくしうる。よって、酸化物半導体膜108bとの電子親和力の差を元素Mの組成によって制御することが可能となる場合がある。また、Ti、Ga、Y、Zr、La、Ce、Sn、NdまたはHfは、酸素との結合力が強い金属元素であるため、これらの元素をInより高い原子数比で有することで、酸素欠損が生じにくくなる。

10

## 【0137】

また、酸化物半導体膜108a、108cがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInおよびMの原子数比率は、好ましくは、Inが50atomic%未満、Mが50atomic%より高く、さらに好ましくは、Inが25atomic%未満、Mが75atomic%より高くする。また、酸化物半導体膜108a、108cとして、酸化ガリウム膜を用いてもよい。

20

## 【0138】

また、酸化物半導体膜108a、108b、108cが、In-M-Zn酸化物の場合、酸化物半導体膜108bと比較して、酸化物半導体膜108a、108cに含まれるMの原子数比が大きく、代表的には、酸化物半導体膜108bに含まれる上記原子と比較して、1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上高い原子数比である。

## 【0139】

また、酸化物半導体膜108a、108b、108cが、In-M-Zn酸化物の場合、酸化物半導体膜108bをIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub> [原子数比]、酸化物半導体膜108a、108cをIn:M:Zn=x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub> [原子数比]とすると、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも大きく、好ましくは、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも1.5倍以上である。より好ましくは、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも2倍以上大きく、さらに好ましくは、y<sub>2</sub>/x<sub>2</sub>がy<sub>1</sub>/x<sub>1</sub>よりも3倍以上または4倍以上大きい。このとき、酸化物半導体膜108bにおいて、y<sub>1</sub>がx<sub>1</sub>以上であると、酸化物半導体膜108bを用いるトランジスタに安定した電気特性を付与できるため好ましい。ただし、y<sub>1</sub>がx<sub>1</sub>の3倍以上になると、酸化物半導体膜108bを用いるトランジスタの電界効果移動度が低下してしまうため、y<sub>1</sub>はx<sub>1</sub>の3倍未満であると好ましい。

30

## 【0140】

酸化物半導体膜108bがIn-M-Zn酸化物の場合、酸化物半導体膜108bを成膜するために用いるターゲットにおいて、金属元素の原子数比をIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub>とすると、x<sub>1</sub>/y<sub>1</sub>は、1/3以上6以下、さらには1以上6以下であって、z<sub>1</sub>/y<sub>1</sub>は、1/3以上6以下、さらには1以上6以下であることが好ましい。なお、z<sub>1</sub>/y<sub>1</sub>を1以上6以下とすることで、酸化物半導体膜108bとして後述のCAA-C-OSが形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、In:M:Zn=1:1:1、In:M:Zn=1:1:1.2、In:M:Zn=3:1:2等がある。

40

## 【0141】

また、酸化物半導体膜108a、108cがIn-M-Zn酸化物の場合、酸化物半導

50

体膜 108a、108c を成膜するために用いるターゲットにおいて、金属元素の原子数比を  $In : M : Zn = x_2 : y_2 : z_2$  とすると、 $x_2 / y_2 < x_1 / y_1$  であって、 $z_2 / y_2$  は、1/3 以上 6 以下、さらには 1 以上 6 以下であることが好ましい。また、インジウムに対する M の原子数比率を大きくすることで、酸化物半導体膜 108a、108c のエネルギーギャップを大きく、電子親和力を小さくすることが可能であるため、 $y_2 / x_2$  を 3 以上、または 4 以上とすることが好ましい。ターゲットの金属元素の原子数比の代表例としては、 $In : M : Zn = 1 : 3 : 2$ 、 $In : M : Zn = 1 : 3 : 4$ 、 $In : M : Zn = 1 : 3 : 5$ 、 $In : M : Zn = 1 : 3 : 6$ 、 $In : M : Zn = 1 : 4 : 2$ 、 $In : M : Zn = 1 : 4 : 4$ 、 $In : M : Zn = 1 : 4 : 5$ 、 $In : M : Zn = 1 : 5 : 5$  等がある。

10

#### 【0142】

また、酸化物半導体膜 108a、108c が  $In - M$  酸化物の場合、M として 2 値の金属原子（例えば、亜鉛など）を含まない構成とすることで、スピネル型の結晶構造を含有しない酸化物半導体膜 108a、108c を形成することができる。また、酸化物半導体膜 108a、108c としては、例えば、 $In - Ga$  酸化物膜を用いることができる。該  $In - Ga$  酸化物としては、例えば、 $In - Ga$  金属酸化物ターゲット ( $In : Ga = 7 : 93$ ) を用いて、スパッタリング法により形成することができる。また、酸化物半導体膜 108a、108c を、DC 放電を用いたスパッタリング法で成膜するためには、 $In : M = x : y$  [原子数比] としたときに、 $y / (x + y)$  を 0.96 以下、好ましくは 0.95 以下、例えば 0.93 とするとよい。

20

#### 【0143】

なお、酸化物半導体膜 108a、108b、108c の原子数比はそれぞれ、誤差として上記の原子数比のプラスマイナス 40% の変動を含む。

#### 【0144】

##### < 酸化物半導体膜の積層構造の概念 >

次に、上記説明した酸化物半導体膜の積層構造を評価するために様々な検証を行った。まず、酸化物半導体膜の積層構造の概念について、図 8 を用いて説明を行う。

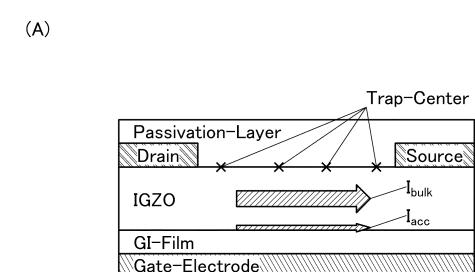

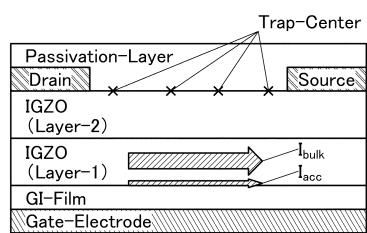

#### 【0145】

図 8 (A) (B) は、酸化物半導体膜中の電流が流れる際の概念の模式図である。図 8 (A) は、酸化物半導体膜が単層構造の場合を、図 8 (B) は、酸化物半導体膜が積層構造の場合を、それぞれ表している。

30

#### 【0146】

なお、図 8 (A) において、ゲート電極を「Gate - Electrode」、ゲート絶縁膜を「GI - Film」、酸化物半導体膜を「IGZO」、ソース電極を「Source」、ドレイン電極を「Drain」、保護絶縁膜を「Passivation - Layer」、トラップ準位を「Trap - center」、バルク電流を  $I_{bulk}$ 、蓄積電流を  $I_{acc}$ 、として、それぞれ表記している。また、図 8 (B) においては、下層の酸化物半導体膜を「IGZO (Layer - 1)」、上層の酸化物半導体膜を「IGZO (Layer - 2)」として、それぞれ表記している。

40

#### 【0147】

チャネルエッチ型の FET では、バックチャネルが露出した状態で配線工程を処理するため、配線エッチングなどプロセス時のダメージや不純物汚染に起因する特性変動を引き起こす場合がある。また、図 8 (A) に示すように、OS - FET は多数キャリアである電子を蓄積させて動作するため、GI - Film 側の蓄積電流のみでなく、次式で表されるような膜厚方向に一様なバルク電流が存在する。

#### 【0148】

#### 【数 1】

$$I_{on} = I_{bulk} + I_{acc} (V_G > V_D + V_{th}) \quad (1)$$

50

【0149】

【数2】

$$\begin{cases} I_{bulk} = \frac{W}{L} \mu_b e N_d t_s V_D \\ I_{acc} = \frac{W}{L} \mu_s C_{ox} [(V_G - V_{FB}) V_D - \frac{V_D^2}{2}] \end{cases} \quad (2)$$

10

【0150】

数式(1)(2)において、 $I_{on}$ はオン電流を、 $I_{bulk}$ はバルク電流を、 $I_{acc}$ は蓄積電流を、 $V_G$ はゲート電圧を、 $V_D$ はドレイン電流を、 $V_{th}$ はしきい値電圧を、それぞれ表す。また、数式(2)において、 $\mu_b$ はバルク移動度を、 $\mu_s$ は表面移動度を、 $C_{ox}$ はG I 容量を、 $V_{FB}$ はフラットバンド電圧を、 $N_d$ はドナー密度を、それぞれ表す。

【0151】

このように、バックチャネル側にトラップ準位が存在する場合、容易にキャリアはトラップされてしまう。

20

【0152】

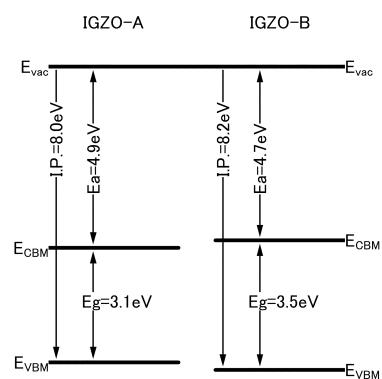

そこで、図8(B)に示すように、異なる組成のIGZO膜の積層膜を形成することで、図9(A)のバンド構造とすることができます。なお、図9(A)は、バンド構造のモデル図である。図8(B)及び図9(A)に示すように、異なる組成のIGZO膜を積層し、伝導帯下端のエネルギー準位(E<sub>CBM</sub>)にウェルを形成することでバックチャネル側に流れる電流を抑制し、保護絶縁膜と酸化物半導体膜との界面近傍に存在する電子トラップの影響を抑制することができる。

【0153】

次に、IGZO膜の積層膜を形成することで、伝導帯下端のエネルギー準位(E<sub>CBM</sub>)にウェルを形成することができるか確認するため、以下の評価を行った。

30

【0154】

まず、IGZO膜としては、下層のIGZO膜として、In:Ga:Zn = 1:1:1.2 [原子数比] のIGZO膜(以下、IGZO-Aとして表す)と、上層のIGZO膜として、In:Ga:Zn = 1:3:2 [原子数比] のIGZO膜(以下、IGZO-Bとして表す)とのイオン化ポテンシャル、及びエネルギーギャップを測定した。なお、イオン化ポテンシャルについては、紫外線光電子分光分析(UPS: Ultraviolet Photoelectron Spectroscopy)により測定し、エネルギーギャップについては分光エリプソメトリ法により測定した。

【0155】

図9(B)にIGZO膜のバンドダイアグラムを示す。なお、図9(B)において、I.P.はionized potentialを、E<sub>a</sub>はelectron affinityを、E<sub>g</sub>はenergy gapを、それぞれ示す。

40

【0156】

図9(B)に示すように、IGZO-Aは、I.P.(A) = 8.0 eV、E<sub>a</sub>(A) = 4.9 eV、E<sub>g</sub>(A) = 3.1 eVであった。また、IGZO-Bは、I.P.(B) = 8.2 eV、E<sub>a</sub>(B) = 4.7 eV、E<sub>g</sub>(B) = 3.5 eVであった。すなわち、IGZO-Bは、IGZO-Aに比べてE<sub>g</sub>が広く、概ね E<sub>CBM</sub>(E<sub>a</sub>(A) - E<sub>a</sub>(B))が0.2 eVのウェルが形成されていることが確認できた。

【0157】

次に、図1(A)(B)(C)に示すトランジスタ100に相当するトランジスタ(IGZO-A単層構造)と、図5(C)(D)に示すトランジスタ100Bに相当するトランジ

50

ンジスタ (IGZO-A と IGZO-B との積層構造) と、を作製し、当該トランジスタの信頼性の確認を行った。なお、トランジスタサイズを  $L / W = 6 / 50 \mu m$  とした。

#### 【0158】

また、信頼性の確認方法としては、PBTs 試験 (Positive Bias Temperature Stress) を用いて行った。なお、PBTs 試験条件としては、ゲート電圧 ( $V_g$ ) を  $+30V$  とし、ドレイン電圧 ( $V_d$ ) とソース電圧 ( $V_s$ ) を  $0V$  (COMMON) とし、ストレス温度を  $60^\circ C$  とし、ストレス印加時間を  $3600\text{sec}$  とし、測定環境をダーク環境で行った。すなわち、トランジスタのソース電極とドレイン電極を同電位とし、ゲート電極にはソース電極及びドレイン電極とは異なる電位を一定時間印加した。また、ゲート電極に与える電位は、ソース電極及びドレイン電極の電位よりも高い。

10

#### 【0159】

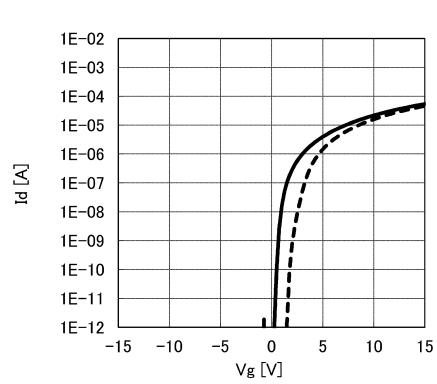

信頼性試験結果を図 10 (A) (B) に示す。

#### 【0160】

なお、図 10 (A) は IGZO-A 単層構造での結果であり、図 10 (B) は IGZO-A と IGZO-B との積層構造での結果である。また、図 10 (A) (B) において、実線が初期の電気特性であり、破線が信頼性試験後の電気特性の結果である。

#### 【0161】

図 10 (A) に示す結果より、IGZO-A 単層構造においては、しきい値電圧の変動量 ( $V_{th}$ ) が  $4.4V$  であった。また、図 10 (B) に示す結果より、IGZO-A と IGZO-B との積層構造においては、しきい値電圧の変動量 ( $V_{th}$ ) が  $1.5V$  であった。このように、IGZO 膜を積層構造とすることで、IGZO 膜の単層構造よりも PBTs ストレス試験前後における、しきい値電圧の変動量 ( $V_{th}$ ) を抑制できることが確認された。

20

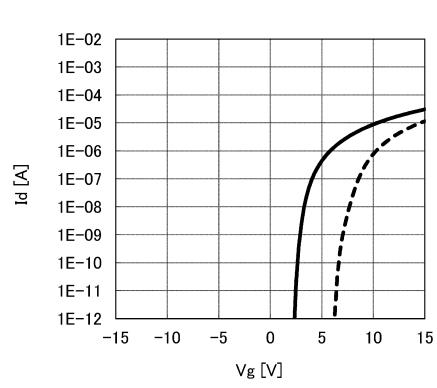

#### 【0162】

次に、IGZO-A と、IGZO-B とのそれぞれの物性値を元にして、トランジスタ中の電子密度分布を計算した。計算に用いた物性値を表 1 に、計算結果を図 11 に、それぞれ示す。

#### 【0163】

#### 【表 1】

30

|                                        | IGZO-A | IGZO-B |

|----------------------------------------|--------|--------|

| thickness[nm]                          | 35     | 35     |

| electron mobility[cm <sup>2</sup> /Vs] | 10     | 0.1    |

| hole mobility[cm <sup>2</sup> /Vs]     | 0.01   | 0.01   |

| Eg[eV]                                 | 3.2    | 3.6    |

| electorn affinity[V]                   | 4.8    | 4.6    |

| $\epsilon_r$                           | 15     | 15     |

40

#### 【0164】

図 11 に示す通り、 $E_{CBM} = 0.2\text{eV}$  のウェルが形成されていることにより、バックチャネル側 (IGZO-B) の電子密度はチャネル側 (IGZO-A) の電子密度と比較して、3 桁以上の電子密度が低減しており、バックチャネル側 (IGZO-B) に電流がほとんど流れていな計算結果が得られた。

#### 【0165】

図 10 及び図 11 に示す結果より、IGZO 膜を積層構造とすることで、バックチャネル側の電子密度が低減され、電子トラップの影響を受けにくくなるため、PBTs ストレス前後における、しきい値電圧の変動量 ( $V_{th}$ ) が抑制できることが確認された。

50

## 【0166】

また、本実施の形態に係るトランジスタは、上記の構造のそれぞれを自由に組み合わせることが可能である。

## 【0167】

## &lt;半導体装置の作製方法1&gt;

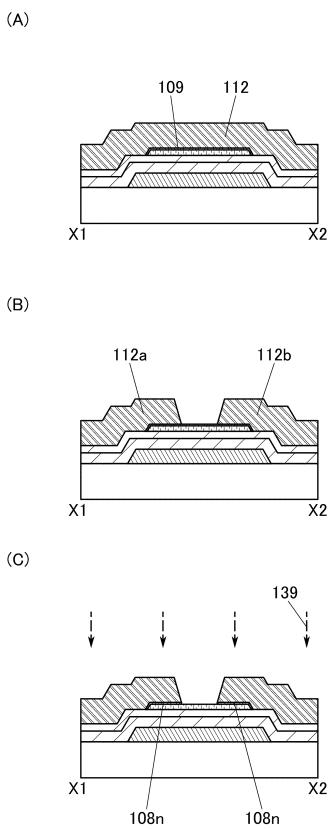

次に、本発明の一態様の半導体装置であるトランジスタ100の作製方法について、図12乃至図15を用いて説明する。なお、図12乃至図15は、半導体装置の作製方法を説明する断面図である。

## 【0168】

## &lt;ゲート電極を形成する工程&gt;

まず、基板102上に導電膜を形成し、該導電膜をリソグラフィ工程及びエッティング工程を行い加工して、ゲート電極として機能する導電膜104を形成する（図12（A）参照）。

## 【0169】

本実施の形態では、基板102としてガラス基板を用い、ゲート電極として機能する導電膜104として厚さ100nmのタンゲステン膜をスパッタリング法で形成する。

## 【0170】

## &lt;ゲート絶縁膜を形成する工程&gt;

次に、導電膜104上にゲート絶縁膜として機能する絶縁膜106、107を形成する（図12（B）参照）。

## 【0171】

本実施の形態では、PECVD法により、絶縁膜106として厚さ400nmの窒化シリコン膜を形成し、絶縁膜107として厚さ50nmの酸化窒化シリコン膜を形成する。

## 【0172】

なお、絶縁膜106は、窒化シリコン膜の積層構造とする。具体的には、絶縁膜106を、第1の窒化シリコン膜と、第2の窒化シリコン膜と、第3の窒化シリコン膜との3層積層構造とすることができます。該3層積層構造の一例としては、以下のように形成することができる。

## 【0173】

第1の窒化シリコン膜としては、例えば、流量200sccmのシラン、流量2000sccmの窒素、及び流量100sccmのアンモニアガスを原料ガスとしてPECVD装置の反応室に供給し、反応室内の圧力を100Paに制御し、27.12MHzの高周波電源を用いて2000Wの電力を供給して、厚さが50nmとなるように形成すればよい。

## 【0174】

第2の窒化シリコン膜としては、流量200sccmのシラン、流量2000sccmの窒素、及び流量2000sccmのアンモニアガスを原料ガスとしてPECVD装置の反応室に供給し、反応室内の圧力を100Paに制御し、27.12MHzの高周波電源を用いて2000Wの電力を供給して、厚さが300nmとなるように形成すればよい。

## 【0175】

第3の窒化シリコン膜としては、流量200sccmのシラン、及び流量5000scmの窒素を原料ガスとしてPECVD装置の反応室に供給し、反応室内の圧力を100Paに制御し、27.12MHzの高周波電源を用いて2000Wの電力を供給して、厚さが50nmとなるように形成すればよい。

## 【0176】

なお、上記第1の窒化シリコン膜、第2の窒化シリコン膜、及び第3の窒化シリコン膜形成時の基板温度は350とすることができます。

## 【0177】

絶縁膜106を、窒化シリコン膜の3層の積層構造とすることで、例えば、導電膜104に銅（Cu）を含む導電膜を用いる場合において、以下の効果を奏する。

10

20

30

40

50

## 【0178】

第1の窒化シリコン膜は、導電膜104からの銅(Cu)元素の拡散を抑制することができる。第2の窒化シリコン膜は、水素を放出する機能を有し、ゲート絶縁膜として機能する絶縁膜の耐圧を向上させることができる。第3の窒化シリコン膜は、第3の窒化シリコン膜からの水素放出が少なく、且つ第2の窒化シリコン膜からの放出される水素の拡散を抑制することができる。

## 【0179】

絶縁膜107としては、後に形成される酸化物半導体膜108との界面特性を向上させるため、酸素を含む絶縁膜で形成されると好ましい。

## 【0180】

<酸化物半導体膜を形成する工程>

次に、絶縁膜107上に酸化物半導体膜108を形成する(図12(C)参照)。

## 【0181】

本実施の形態では、In-Ga-Zn金属酸化物ターゲット(In:Ga:Zn=1:1:1.2(原子数比))を用いて、スパッタリング法により酸化物半導体膜を成膜し、該酸化物半導体膜上にリソグラフィ工程によりマスクを形成し、該酸化物半導体膜を所望の領域に加工することで島状の酸化物半導体膜108を形成する。

## 【0182】

酸化物半導体膜108の形成後、150以上基板の歪み点未満、好ましくは200以上450以下、さらに好ましくは300以上450以下の加熱処理を行ってもよい。ここで加熱処理は、酸化物半導体膜の高純度化処理の一つであり、酸化物半導体膜108に含まれる水素、水等を低減することができる。なお、水素、水等の低減を目的とした加熱処理は、酸化物半導体膜108を島状に加工する前に行ってもよい。

## 【0183】

酸化物半導体膜108への加熱処理は、ガスベーク炉、電気炉、RTA装置等を用いることができる。RTA装置を用いることで、短時間に限り基板の歪み点以上の温度で熱処理を行うことができる。そのため、加熱時間を短縮することが可能となる。

## 【0184】

なお、酸化物半導体膜108への加熱処理は、窒素ガス、酸素ガス、超乾燥空気(Clean Dry Air:CDAともいう。CDAとは、水の含有量が20ppm以下、好ましくは1ppm以下、より好ましくは10ppb以下の空気である。)、または希ガス(アルゴン、ヘリウム等)の雰囲気下で行えばよい。なお、上記窒素ガス、酸素ガス、CDA、または希ガスに水素、水等が含まれないことが好ましい。

## 【0185】

例えば、上記窒素ガス、酸素ガス、またはCDAの純度を高めると好ましい。具体的には、窒素ガス、酸素ガス、またはCDAの純度を、6N(99.9999%)または7N(99.99999%)とすればよい。また、窒素ガス、酸素ガス、またはCDAの露点が-60以下、好ましくは-100以下にまで高純度化したガスを用いることで酸化物半導体膜108に水分等が取り込まれることを可能な限り防ぐことができる。

## 【0186】

また、酸化物半導体膜108を窒素または希ガス雰囲気で加熱処理した後、酸素またはCDA雰囲気で加熱してもよい。この結果、酸化物半導体膜108中に含まれる水素、水等を脱離させると共に、酸化物半導体膜108中に酸素を供給することができる。この結果、酸化物半導体膜108中に含まれる酸素欠損量を低減することができる。

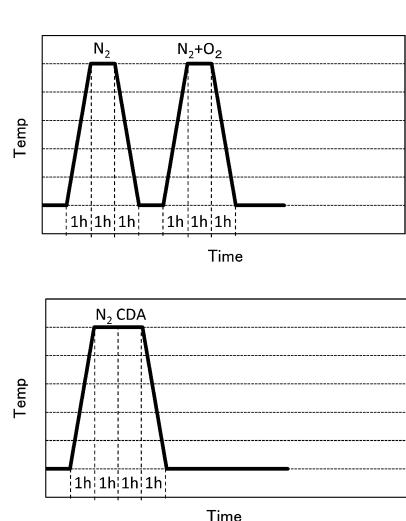

## 【0187】

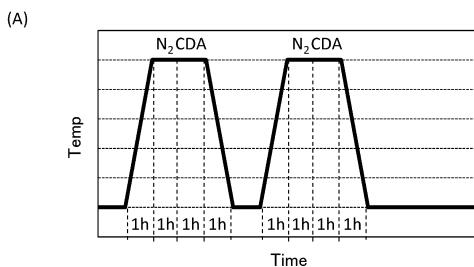

ここで、酸化物半導体膜108への加熱処理を行う際のガスベーク炉の熱プロファイルについて、図16及び図17を用いて説明を行う。図16(A)(B)及び図17(A)(B)は、ガスベーク炉の加熱処理時の熱プロファイルを説明する図である。

## 【0188】

なお、図16(A)(B)及び図17(A)(B)は、所望の温度(ここでは、450

10

20

30

40

50

、以下では、第1の温度とする)にまで昇温させて、所望の温度(ここでは、室温以上150以下、以下では第2の温度とする)にまで降温させる熱プロファイルである。

【0189】

図16(A)に示すように、酸化物半導体膜108へ加熱処理を行う際に、2つのガス種を用い、2つのステップに分けて処理することができる。例えば、1つ目のステップで、ガスベーク炉に窒素ガスを導入する。その後、第1の温度にまで昇温させる時間を1時間とし、第1の温度で1時間処理した後に、第2の温度にまで1時間かけて降温させる。2つ目のステップで、窒素ガスから窒素と酸素との混合ガスに切り替える。その後、第1の温度にまで昇温させる時間を1時間とし、第1の温度で1時間処理した後に、第2の温度にまで1時間かけて降温させる。

10

【0190】

または、図16(B)に示すように、酸化物半導体膜108へ加熱処理を行う際に、2つのガス種を用い、1つのステップで処理することができる。例えば、最初にガスベーク炉に窒素ガスを導入する。その後、第1の温度にまで昇温させる時間を1時間とし、第1の温度で1時間処理した後に、ガス種を窒素ガスからCDAに切り替える。ガス種を切り替えてから、さらに1時間処理した後に、第2の温度にまで1時間かけて降温させる。

20

【0191】

なお、図16(B)に示すようなガスベーク炉の加熱処理時の熱プロファイルとすることで、図16(A)に示すガスベーク炉の加熱処理時の熱プロファイルよりも処理時間を短縮することができる。したがって、生産性が高められた半導体装置を提供することができる。

30

【0192】

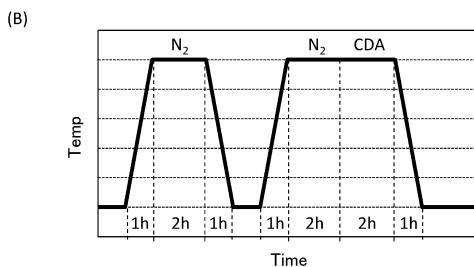

または、図17(A)に示すように、酸化物半導体膜108へ加熱処理を行う際に、2つのガス種を用い、2つのステップで処理することができる。例えば、1つ目のステップで、最初にガスベーク炉に窒素ガスを導入する。その後、第1の温度にまで昇温させる時間を1時間とし、第1の温度で1時間処理した後に、ガス種を窒素ガスからCDAに切り替える。ガス種を切り替えてから、さらに1時間処理した後に、第2の温度にまで1時間かけて降温させる。2つ目のステップで、CDAから窒素ガスに切り替える。その後、第1の温度にまで昇温させる時間を1時間とし、第1の温度で1時間処理した後に、ガス種を窒素ガスからCDAに切り替える。ガス種を切り替えてから、さらに1時間処理した後に、第2の温度にまで1時間かけて降温させる。

30

【0193】

または、図17(B)に示すように、酸化物半導体膜108へ加熱処理を行う際に、2つのガス種を用い、2つのステップで処理することができる。例えば、1つ目のステップで、最初にガスベーク炉に窒素ガスを導入する。その後、第1の温度にまで昇温させる時間を1時間とし、第1の温度で2時間処理した後に、第2の温度にまで1時間かけて降温させる。2つ目のステップで、第1の温度にまで昇温させる時間を1時間とし、第1の温度で2時間処理した後に、ガス種を窒素ガスからCDAに切り替える。ガス種を切り替えてから、さらに2時間処理した後に、第2の温度にまで1時間かけて降温させる。

40

【0194】

なお、酸化物半導体膜108への加熱処理のガスベーク炉の熱プロファイルとしては、図16(A)(B)及び図17(A)(B)のように、最初に窒素ガスにより加熱することが好ましい。

【0195】

最初に、窒素ガスにより酸化物半導体膜108を加熱することで、酸化物半導体膜108中の主成分の一つである酸素と、酸化物半導体膜108中に存在しうる水素とが反応し、OH基となる。その後、当該OH基は、酸化物半導体膜108の表面よりH<sub>2</sub>Oとして脱離する。すなわち、最初の窒素ガスにより酸化物半導体膜108中の水素を捕獲することが可能となる。

【0196】

50

ただし、窒素ガスのみで酸化物半導体膜 108 を加熱することで、酸化物半導体膜 108 から酸素が  $H_2O$  として脱離するため、酸化物半導体膜 108 中に酸素欠損が形成される場合がある。そこで、図 16 (A) (B) 及び図 17 (A) (B) に示すように、窒素ガスと酸素ガスとの混合ガス、または CDA のいずれか一方のガス種に切り替えることと、ガス中に含まれる酸素が、酸化物半導体膜 108 の酸素欠損を補填することが可能となる。

#### 【0197】

なお、図 16 (A) (B) 及び図 17 (A) (B) においては、所望の温度で安定したのち、1時間または2時間の処理としたが、これに限定されない。例えば図 17 (B) に示す1つ目のステップの窒素ガスでの処理時間を、1時間以上10時間以下としてもよい。図 17 (B) に示す1つ目のステップの処理時間を長くすることで、酸化物半導体膜 108 中から、より多くの水素を脱離させることができるとなるため、好適である。

10

#### 【0198】

また、必要に応じて、窒素ガスと酸素ガスとの混合ガス、または CDA のいずれか一方のガス種でのベーク時間を長く、例えば、1時間以上10時間以下としてもよい。酸素ガスが含まれる雰囲気での加熱時間を長くすることで、酸化物半導体膜 108 に形成された酸素欠損を好適に補填することが可能となる。

#### 【0199】

また、スパッタリング法で酸化物半導体膜を形成する場合、スパッタリングガスには、希ガス（代表的にはアルゴン）、酸素、または希ガス及び酸素の混合ガスが適宜用いられる。なお、混合ガスの場合、希ガスに対して酸素のガス比を高めることができると嬉しい。また、スパッタリングガスの高純度化も必要である。例えば、スパッタリングガスとして用いる酸素ガスやアルゴンガスは、露点が -60 以下、好ましくは -100 以下にまで高純度化したガスを用いることで酸化物半導体膜 108 に水分等が取り込まれることを可能な限り防ぐことができる。

20

#### 【0200】

また、スパッタリング法で酸化物半導体膜 108 を形成する場合、スパッタリング装置におけるチャンバーを、酸化物半導体膜 108 にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて、高真空排気 ( $5 \times 10^{-7} \text{ Pa}$  から  $1 \times 10^{-4} \text{ Pa}$  程度まで) することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体、特に炭素または水素を含む気体が逆流しないようにしておくことが好ましい。

30

#### 【0201】

<酸化物半導体膜中に酸素欠損を有する領域を形成する工程>

次に、絶縁膜 107 及び酸化物半導体膜 108 上に導電膜 112 を形成する。なお、導電膜 112 の形成時に酸化物半導体膜 108 の表面近傍に変性層 109 が形成される（図 13 (A) 参照）。

#### 【0202】

変性層 109 は、酸化物半導体膜 108 中に酸素欠損を多く有する領域である。なお、変性層 109 は、例えば、導電膜 112 をスパッタリング法で成膜した場合、スパッタリング時のプラズマダメージ、スパッタリング時の反跳アルゴンによるダメージ、またはスパッタリング時に導電膜 112 に用いる材料の原子あるいは分子の衝突により酸化物半導体膜 108 の表面近傍に形成される。したがって、導電膜 112 の形成方法としては、特にスパッタリング法または PLD 法が好ましい。また、スパッタリング装置において、用いる電源としては DC (Direct Current) 電源、RF (Radio Frequency) 電源、AC (Alternating Current) 電源などが挙げられるが、中でも DC 電源または AC 電源を用いてスパッタリングを行うと、生産性が高められるため好ましい。

40

#### 【0203】

本実施の形態においては、導電膜 112 として、厚さ 50 nm のタンゲスタン膜と、厚

50

さ 4 0 0 nm のアルミニウム膜と、厚さ 1 0 0 nm のチタン膜と、の積層膜をスパッタリング法により形成する。なお、変性層 1 0 9 の形成においては、導電膜 1 1 2 の成膜電力が重要である。例えば、スパッタリング時の電力密度を 1 W / cm<sup>2</sup> 以上 4 W / cm<sup>2</sup> 以下とすることで、厚さ 5 nm 以下の変性層 1 0 9 を形成することができる。

【 0 2 0 4 】

< ソース電極及びドレイン電極を形成する工程 >

次に、導電膜 1 1 2 上の所望の領域にレジストマスクを形成し、導電膜 1 1 2 を加工することで、ソース電極及びドレイン電極として機能する導電膜 1 1 2 a、1 1 2 b を形成する。導電膜 1 1 2 a、1 1 2 b を形成後、レジストマスクを除去する（図 1 3 ( B ) 参照）。

10

【 0 2 0 5 】

< 酸素欠損を有する領域を除去する工程 >

次に、導電膜 1 1 2 a、1 1 2 b 上から、エッチャント 1 3 9 を用いて、導電膜 1 1 2 a と導電膜 1 1 2 b との間の変性層 1 0 9 を除去する。変性層 1 0 9 の一部を除去することで、酸化物半導体膜 1 0 8 中に導電膜 1 1 2 a、1 1 2 b に接する n 型領域 1 0 8 n が形成される（図 1 3 ( C ) 参照）。

【 0 2 0 6 】

エッチャント 1 3 9 としては、変性層 1 0 9 を除去できればよく、薬液またはエッチングガスを用いて除去すればよい。特にエッチャント 1 3 9 としては、薬液を用いる方が、チャネル領域 1 0 8 i の表面へのダメージを低減できるため好適である。本実施の形態においては、エッチャント 1 3 9 として、リン酸水溶液により、変性層 1 0 9 の一部を除去する。なお、エッチングを行う工程において、チャネル領域 1 0 8 i の一部に凹部が形成される場合がある。

20

【 0 2 0 7 】

以上の工程でトランジスタ 1 0 0 が形成される。

【 0 2 0 8 】

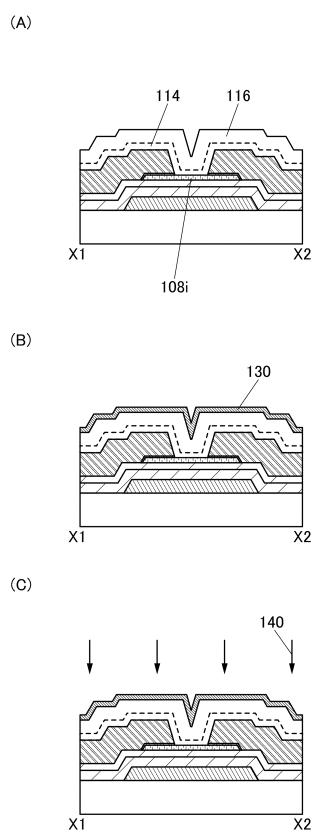

< 酸化物絶縁膜を形成する工程 >

次に、トランジスタ 1 0 0 上に、具体的には酸化物半導体膜 1 0 8 、及び導電膜 1 1 2 a、1 1 2 b 上にトランジスタ 1 0 0 の保護絶縁膜として機能する絶縁膜 1 1 4 、1 1 6 を形成する。絶縁膜 1 1 4 、1 1 6 の形成時、または絶縁膜 1 1 4 、1 1 6 の形成後の熱処理によって、酸化物半導体膜 1 0 8 中の酸素欠損が補填され、チャネル領域 1 0 8 i が形成される（図 1 4 ( A ) 参照）。

30

【 0 2 0 9 】

なお、絶縁膜 1 1 4 を形成した後、大気に曝すことなく、連続的に絶縁膜 1 1 6 を形成することが好ましい。絶縁膜 1 1 4 を形成後、大気開放せず、原料ガスの流量、圧力、高周波電力及び基板温度の一以上を調整して、絶縁膜 1 1 6 を連続的に形成することで、絶縁膜 1 1 4 と絶縁膜 1 1 6 の界面において大気成分由来の不純物濃度を低減することができるとともに、絶縁膜 1 1 4 、1 1 6 に含まれる酸素を酸化物半導体膜 1 0 8 中のチャネル領域 1 0 8 i に移動させることができとなり、チャネル領域 1 0 8 i の酸素欠損量を低減することが可能となる。

40

【 0 2 1 0 】

例えば、絶縁膜 1 1 4 として、PECVD 法を用いて、酸化窒化シリコン膜を形成することができる。この場合、原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、一酸化二窒素、二酸化窒素等がある。また、上記の堆積性気体の流量に対して酸化性気体の流量を 20 倍より大きく 100 倍未満、好ましくは 40 倍以上 80 倍以下とし、処理室内の圧力を 100 Pa 未満、好ましくは 50 Pa 以下とする PECVD 法を用いることで、絶縁膜 1 1 4 が、窒素を含み、且つ欠陥量の少ない絶縁膜となる。

【 0 2 1 1 】

50

本実施の形態においては、絶縁膜 114 として、基板 102 を保持する温度を 220 とし、流量 50 sccm のシラン及び流量 2000 sccm の一酸化二窒素を原料ガスとし、処理室内の圧力を 20 Pa とし、平行平板電極に供給する高周波電力を 13.56 MHz、100 W (電力密度としては  $1.6 \times 10^{-2} \text{ W/cm}^2$ ) とする PECVD 法を用いて、酸化窒化シリコン膜を形成する。

#### 【0212】

絶縁膜 116 としては、PECVD 装置の真空排気された処理室内に載置された基板を 180 以上 280 以下、さらに好ましくは 200 以上 240 以下に保持し、処理室内に原料ガスを導入して処理室内における圧力を 100 Pa 以上 250 Pa 以下、さらに好ましくは 100 Pa 以上 200 Pa 以下とし、処理室内に設けられる電極に 0.17 W/cm<sup>2</sup> 以上 0.5 W/cm<sup>2</sup> 以下、さらに好ましくは 0.25 W/cm<sup>2</sup> 以上 0.35 W/cm<sup>2</sup> 以下の高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成する。

#### 【0213】

絶縁膜 116 の成膜条件として、上記圧力の反応室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、絶縁膜 116 中における酸素含有量が化学量論的組成よりも多くなる。一方、基板温度が、上記温度で形成された膜では、シリコンと酸素の結合力が弱いため、後の工程の加熱処理により膜中の酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化物絶縁膜を形成することができる。

#### 【0214】

なお、絶縁膜 116 の形成工程において、絶縁膜 114 が酸化物半導体膜 108 中のチャネル領域 108i の保護膜となる。したがって、チャネル領域 108i へのダメージを低減しつつ、パワー密度の高い高周波電力を用いて絶縁膜 116 を形成することができる。

#### 【0215】

なお、絶縁膜 116 の成膜条件において、酸化性気体に対するシリコンを含む堆積性気体の流量を増加することで、絶縁膜 116 の欠陥量を低減することができる。代表的には、ESR 測定により、シリコンのダングリングボンドに由来する  $g = 2.001$  に現れる信号のスピントラップ濃度が  $6 \times 10^{17} \text{ spins/cm}^3$  未満、好ましくは  $3 \times 10^{17} \text{ spins/cm}^3$  以下、好ましくは  $1.5 \times 10^{17} \text{ spins/cm}^3$  以下である欠陥量の少ない酸化物絶縁膜を形成することができる。この結果トランジスタの信頼性を高めることができる。

#### 【0216】

絶縁膜 114、116 を形成した後、加熱処理を行ってもよい。該加熱処理により、絶縁膜 114、116 に含まれる窒素酸化物を低減することができる。また、上記加熱処理により、絶縁膜 114、116 に含まれる酸素の一部を酸化物半導体膜 108 中のチャネル領域 108i に移動させ、チャネル領域 108i に含まれる酸素欠損量を低減することができる。

#### 【0217】

絶縁膜 114、116 への加熱処理の温度は、代表的には、150 以上 400 以下、好ましくは 300 以上 400 以下、好ましくは 320 以上 370 以下とする。加熱処理は、窒素、酸素、CDA、または希ガス (アルゴン、ヘリウム等) の雰囲気下で行えばよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水等が含まれないことが好ましい。該加熱処理には、ガスベーク炉、電気炉、RTA 装置等を用いることができる。

#### 【0218】

本実施の形態では、窒素及び酸素雰囲気で、350 、1 時間の加熱処理を行う。

#### 【0219】

10

20

30

40

50

<酸化物絶縁膜中に酸素を添加する工程>

次に、絶縁膜116上に酸素の放出を抑制する保護膜130を形成する(図14(B)参照)。

【0220】

保護膜130には、インジウムを含む導電膜、またはインジウムを含む半導体膜を用いることが出来る。本実施の形態においては、保護膜130として、スパッタリング装置を用いて、膜厚5nmのITO膜を形成する。なお、保護膜130の厚さは、1nm以上20nm以下、または2nm以上10nm以下とすると好適に酸素を透過し、且つ酸素の放出を抑制できるため好ましい。

【0221】

次に、保護膜130を通過させて絶縁膜114、116に酸素140を添加する(図14(C)参照)。

【0222】

保護膜130を通過させて、絶縁膜114、116に酸素140を添加する方法としては、イオンドーピング法、イオン注入法(Ion Implantation、Plasma Based Ion Implantation、Plasma Immersion Ion Implantation、Plasma Source Ion Implantationなど)、プラズマ処理法などが挙げられる。また、プラズマ処理法として、マイクロ波を用いて、ハロゲン元素及び酸素を励起し、高密度なプラズマを発生させてもよい。

【0223】

また、酸素140を添加する際に、基板側にバイアス電圧を印加することで効果的に酸素140を絶縁膜114、116に添加することができる。上記バイアス電圧としては、例えば、アッシング装置を用い、該アッシング装置の基板側に印加するバイアス電圧の電力密度を0.5W/cm<sup>2</sup>以上5W/cm<sup>2</sup>以下とすればよい。また、酸素140を添加する際の基板温度としては、室温以上300以下、好ましくは100以上250以下とすることで、絶縁膜114、116に効率よく酸素を添加することができる。

【0224】

なお、本実施の形態では、アッシング装置を用い、酸素ガスをアッシング装置内に導入し、基板側にバイアスを印加することで、絶縁膜114、116中に酸素140を添加する。

【0225】

絶縁膜116上に保護膜130を設けて酸素を添加することで、保護膜130が絶縁膜116から酸素が放出することを抑制する保護膜として機能する。このため、絶縁膜114、116に多くの酸素を添加することができる。

【0226】

次に、エッチャント142を用いて保護膜130を除去する(図15(A)参照)。

【0227】

エッチャント142としては、保護膜130を除去できればよく、薬液、またはエッチャングガスを用いて除去すればよい。本実施の形態においては、エッチャント142として、シウ酸の濃度が5%のシウ酸水溶液を用いる。なお、エッチャント142としては、上記シウ酸の濃度が5%のシウ酸水溶液を用いた後、さらにフッ酸の濃度が0.5%のフッ化水素酸水溶液を用いてもよい。フッ酸の濃度が0.5%のフッ化水素酸水溶液を用いることで、酸素の放出を抑制する保護膜130を好適に除去することができる。

【0228】

次に、絶縁膜116上に絶縁膜118を形成することで、図1に示すトランジスタ100が形成される(図15(B)参照)。

【0229】

絶縁膜118をPECVD法で形成する場合、基板温度は300以上400以下に、好ましくは320以上370以下にすることで、緻密な膜を形成できるため好まし

10

20

30

40

50

い。

### 【0230】

例えば、絶縁膜118としてPECVD法により窒化シリコン膜を形成する場合、シリコンを含む堆積性気体、窒素、及びアンモニアを原料ガスとして用いることが好ましい。窒素と比較して少量のアンモニアを用いることで、プラズマ中でアンモニアが解離し、活性種が発生する。該活性種が、シリコンを含む堆積性気体に含まれるシリコン及び水素の結合、及び窒素の三重結合を切断する。この結果、シリコン及び窒素の結合が促進され、シリコン及び水素の結合が少なく、欠陥が少なく、緻密な窒化シリコン膜を形成することができる。一方、窒素に対するアンモニアの量が多いと、シリコンを含む堆積性気体及び窒素の分解が進まず、シリコン及び水素結合が残存してしまい、欠陥が増大した、且つ粗な窒化シリコン膜が形成されてしまう。これらのため、原料ガスにおいて、アンモニアに対する窒素の流量比を好ましくは5以上50以下、さらに好ましくは10以上50以下とすればよい。

### 【0231】

本実施の形態においては、絶縁膜118として、PECVD装置を用いて、シラン、窒素、及びアンモニアを原料ガスとして用いて、厚さ50nmの窒化シリコン膜を形成する。流量は、シランが50sccm、窒素が5000sccmであり、アンモニアが100sccmである。処理室の圧力を100Pa、基板温度を350とし、27.12MHzの高周波電源を用いて1000Wの高周波電力を平行平板電極に供給する。PECVD装置は電極面積が6000cm<sup>2</sup>である平行平板型のPECVD装置であり、供給した電力を単位面積あたりの電力(電力密度)に換算すると $1.7 \times 10^{-1} \text{ W/cm}^2$ である。

### 【0232】

また、絶縁膜118を加熱成膜する場合においては、絶縁膜118の成膜前の予備加熱を無くした方が好適である。例えば、絶縁膜118の成膜前に予備加熱をした場合、絶縁膜114、116中の過剰酸素が外部に放出される場合がある。そこで、絶縁膜118の成膜の際には、予備加熱を行わずに、具体的には、加熱されたチャンバー内に基板を搬入後、好ましくは3分以内、さらに好ましくは1分以内に絶縁膜116上に絶縁膜118が形成される手順とすることで、絶縁膜114、116中の過剰酸素が外部に放出されるのを抑制することが可能となる。

### 【0233】

なお、絶縁膜118の形成前、または絶縁膜118の形成後に加熱処理を行って、絶縁膜114、116に含まれる過剰酸素を酸化物半導体膜108中のチャネル領域108iに拡散させ、チャネル領域108iの酸素欠損を補填することができる。あるいは、絶縁膜118を加熱成膜とすることで、絶縁膜114、116に含まれる過剰酸素をチャネル領域108i中に拡散させ、チャネル領域108i中の酸素欠損を補填することができる。絶縁膜118の形成前、または絶縁膜118の形成後に行うことができる、加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、好ましくは320以上370以下とする。

### 【0234】

以上の工程により、図1に示すトランジスタ100を作製することができる。

### 【0235】

<半導体装置の作製方法2>

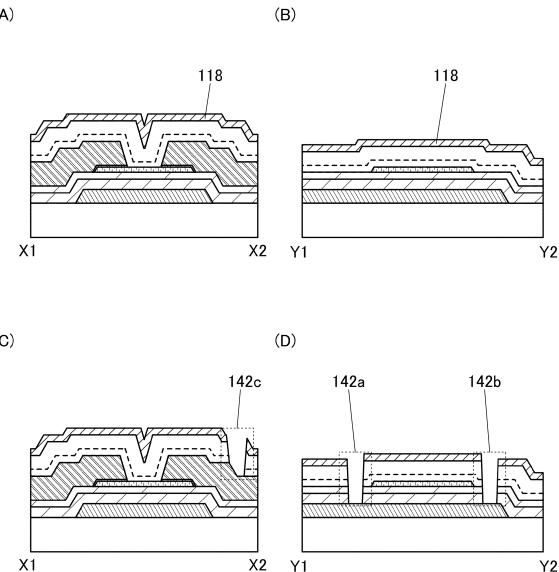

次に、図3に示すトランジスタ170の作製方法について、図18及び図19を用いて説明する。なお、図18(A)(C)及び図19(A)(C)は、作製工程における、トランジスタ170のチャネル長方向の断面図であり、図18(B)(D)及び図19(B)(D)は、作製工程における、トランジスタ170のチャネル幅方向の断面図である。

### 【0236】

まず、図15(B)に示す工程まで行う(図18(A)(B)参照)。

### 【0237】

10

20

30

40

50

次に、絶縁膜 118 上にリソグラフィ工程によりマスクを形成し、絶縁膜 114、116、118 の所望の領域に開口部 142c を形成する。また、絶縁膜 118 上にリソグラフィ工程によりマスクを形成し、絶縁膜 106、107、114、116、118 の所望の領域に開口部 142a、142b を形成する。なお、開口部 142c は、導電膜 112b に達するように形成される。また、開口部 142a、142b は、それぞれ導電膜 104 に達するように形成される（図 18（C）（D）参照）。

#### 【0238】

なお、開口部 142a、142b と開口部 142c とは、同時に形成してもよく、異なる工程で形成してもよい。開口部 142a、142b と開口部 142c を同時に形成する場合、例えば、グレートーンマスクまたはハーフトーンマスクを用いて形成することができる。

10

#### 【0239】

次に、開口部 142a、142b、142c を覆うように絶縁膜 118 上に導電膜 120 を形成する（図 19（A）（B）参照）。

#### 【0240】

導電膜 120 としては、例えば、インジウム（In）、亜鉛（Zn）、錫（Sn）の中から選ばれた一種を含む材料を用いることができる。とくに、導電膜 120 としては、酸化タンクス滕を含むインジウム酸化物、酸化タンクス滕を含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを含むインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。また、導電膜 120 を酸素の放出を抑制できる保護膜 130 と同種の材料を用いることで、製造コストを抑制できるため好適である。

20

#### 【0241】

また、導電膜 120 としては、例えば、スパッタリング法を用いて形成することができる。本実施の形態においては、膜厚 110 nm のITO膜をスパッタリング法で形成する。

#### 【0242】

次に、導電膜 120 上にリソグラフィ工程によりマスクを形成し、導電膜 120 を所望の領域に加工し、導電膜 120a、120b を形成する（図 19（C）（D）参照）。

30

#### 【0243】

以上の工程で図 3 に示すトランジスタ 170 を作製することができる。

#### 【0244】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

#### 【0245】

##### （実施の形態 2）

本実施の形態では、本発明の一態様の半導体装置に含まれる酸化物半導体の詳細について、以下説明する。

40

#### 【0246】

##### <酸化物半導体の構造>

まず、酸化物半導体の構造について説明する。

#### 【0247】

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、nc-OS (nanocrystalline Oxide Semiconductor)、擬似非晶質酸化物半導体 (a-like OS: amorphous like Oxide Semiconductor)、非晶質酸化物半導体などがある。

#### 【0248】

50

また別の観点では、酸化物半導体は、非晶質酸化物半導体と、それ以外の結晶性酸化物半導体とに分けられる。結晶性酸化物半導体としては、単結晶酸化物半導体、CAAC-OS、多結晶酸化物半導体、n c - OSなどがある。

#### 【0249】

非晶質構造の定義としては、一般に、準安定状態で固定化していないこと、等方的であつて不均質構造を持たないことなどが知られている。また、結合角度が柔軟であり、短距離秩序性は有するが、長距離秩序性を有さない構造と言い換えることもできる。

#### 【0250】

逆の見方をすると、本質的に安定な酸化物半導体の場合、完全な非晶質 (completely amorphous) 酸化物半導体と呼ぶことはできない。また、等方的でない（例えば、微小な領域において周期構造を有する）酸化物半導体を、完全な非晶質酸化物半導体と呼ぶことはできない。ただし、a - like OSは、微小な領域において周期構造を有するものの、鬆（ボイドともいう。）を有し、不安定な構造である。そのため、物性的には非晶質酸化物半導体に近いといえる。

10

#### 【0251】

<CAAC-OS>

まずは、CAAC-OSについて説明する。

#### 【0252】

CAAC-OSは、c軸配向した複数の結晶部（ペレットともいう。）を有する酸化物半導体の一つである。

20

#### 【0253】

透過型電子顕微鏡（TEM: Transmission Electron Microscope）によって、CAAC-OSの明視野像と回折パターンとの複合解析像（高分解能TEM像ともいう。）を観察すると、複数のペレットを確認することができる。一方、高分解能TEM像ではペレット同士の境界、即ち結晶粒界（グレインバウンダリーともいう。）を明確に確認することができない。そのため、CAAC-OSは、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

#### 【0254】

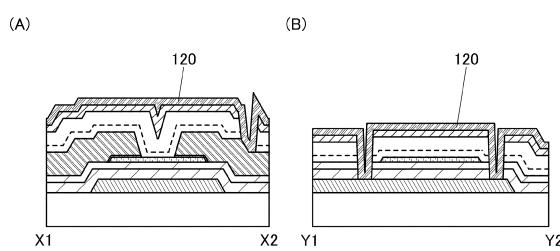

以下では、TEMによって観察したCAAC-OSについて説明する。図20(A)に、試料面と略平行な方向から観察したCAAC-OSの断面の高分解能TEM像を示す。高分解能TEM像の観察には、球面収差補正（Spherical Aberration Corrector）機能を用いた。球面収差補正機能を用いた高分解能TEM像を、特にCs補正高分解能TEM像と呼ぶ。Cs補正高分解能TEM像の取得は、例えば、日本電子株式会社製原子分解能分析電子顕微鏡JEM-ARM200Fなどによって行うことができる。

30

#### 【0255】

図20(A)の領域(1)を拡大したCs補正高分解能TEM像を図20(B)に示す。図20(B)より、ペレットにおいて、金属原子が層状に配列していることを確認できる。金属原子の各層の配列は、CAAC-OSの膜を形成する面（被形成面ともいう。）または上面の凹凸を反映しており、CAAC-OSの被形成面または上面と平行となる。

40

#### 【0256】

図20(B)に示すように、CAAC-OSは特徴的な原子配列を有する。図20(C)は、特徴的な原子配列を、補助線で示したものである。図20(B)および図20(C)より、ペレット一つの大きさは1nm以上3nm以下程度であり、ペレットとペレットとの傾きにより生じる隙間の大きさは0.8nm程度であることがわかる。したがって、ペレットを、ナノ結晶（nc: nanocrystal）と呼ぶこともできる。また、CAAC-OSを、CANC（C-Axis Aligned nanocrystals）を有する酸化物半導体と呼ぶこともできる。

#### 【0257】

ここで、Cs補正高分解能TEM像をもとに、基板5120上のCAAC-OSのペレ

50

ット 5100 の配置を模式的に示すと、レンガまたはブロックが積み重なったような構造となる（図 20 (D) 参照）。図 20 (C) で観察されたペレットとペレットとの間で傾きが生じている箇所は、図 20 (D) に示す領域 5161 に相当する。

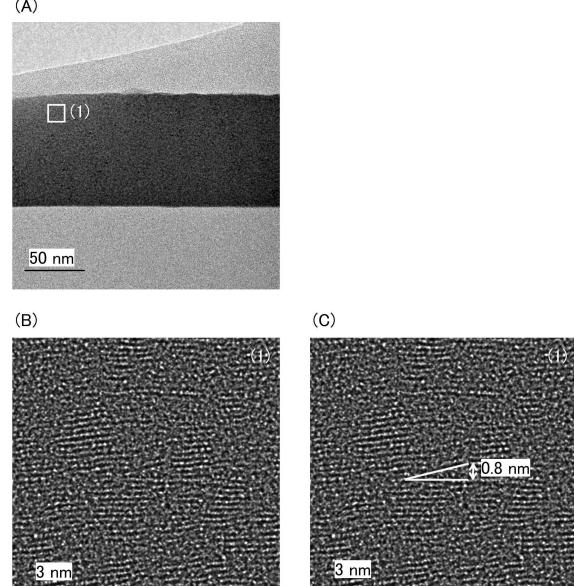

#### 【0258】

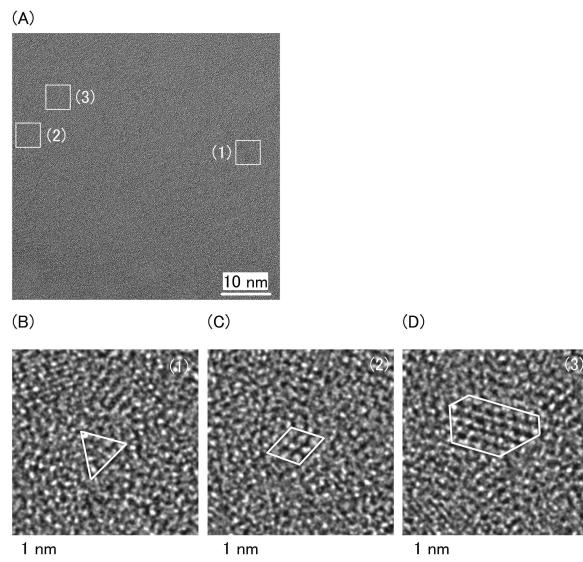

また、図 21 (A) に、試料面と略垂直な方向から観察した CAAc - OS の平面の Cs 補正高分解能 TEM 像を示す。図 21 (A) の領域 (1)、領域 (2) および領域 (3) を拡大した Cs 補正高分解能 TEM 像を、それぞれ図 21 (B)、図 21 (C) および図 21 (D) に示す。図 21 (B)、図 21 (C) および図 21 (D) より、ペレットは、金属原子が三角形状、四角形状または六角形状に配列していることを確認できる。しかしながら、異なるペレット間で、金属原子の配列に規則性は見られない。

10

#### 【0259】

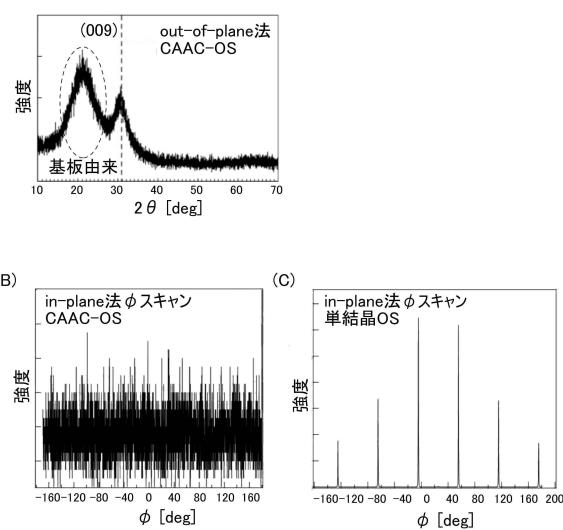

次に、X 線回折 (XRD : X - Ray Diffraction) によって解析した CAAc - OS について説明する。例えば、InGaZnO<sub>4</sub> の結晶を有する CAAc - OS に対し、out-of-plane 法による構造解析を行うと、図 22 (A) に示すように回折角 (2θ) が 31° 近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (009) 面に帰属されることから、CAAc - OS の結晶が c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることが確認できる。

#### 【0260】

なお、CAAc - OS の out-of-plane 法による構造解析では、2θ が 31° 近傍のピークの他に、2θ が 36° 近傍にもピークが現れる場合がある。2θ が 36° 近傍のピークは、CAAc - OS 中の一部に、c 軸配向性を有さない結晶が含まれることを示している。より好ましい CAAc - OS は、out-of-plane 法による構造解析では、2θ が 31° 近傍にピークを示し、2θ が 36° 近傍にピークを示さない。

20

#### 【0261】

一方、CAAc - OS に対し、c 軸に略垂直な方向から X 線を入射させる in-plane 法による構造解析を行うと、2θ が 56° 近傍にピークが現れる。このピークは、InGaZnO<sub>4</sub> の結晶の (110) 面に帰属される。CAAc - OS の場合は、2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行っても、図 22 (B) に示すように明瞭なピークは現れない。これに対し、InGaZnO<sub>4</sub> の単結晶酸化物半導体であれば、2θ を 56° 近傍に固定してスキャンした場合、図 22 (C) に示すように (110) 面と等価な結晶面に帰属されるピークが 6 本観察される。したがって、XRD を用いた構造解析から、CAAc - OS は、a 軸および b 軸の配向が不規則であることが確認できる。

30

#### 【0262】

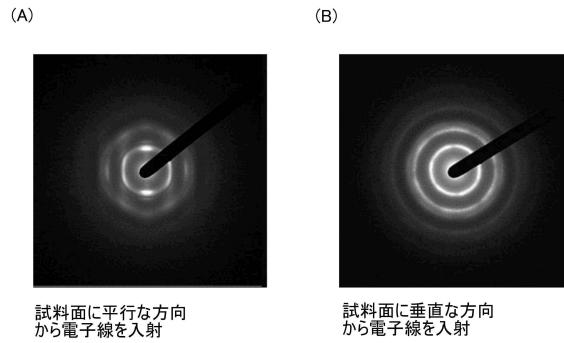

次に、電子回折によって解析した CAAc - OS について説明する。例えば、InGaZnO<sub>4</sub> の結晶を有する CAAc - OS に対し、試料面に平行にプローブ径が 300 nm の電子線を入射させると、図 23 (A) に示すような回折パターン（制限視野透過電子回折パターンともいう。）が現れる場合がある。この回折パターンには、InGaZnO<sub>4</sub> の結晶の (009) 面に起因するスポットが含まれる。したがって、電子回折によっても、CAAc - OS に含まれるペレットが c 軸配向性を有し、c 軸が被形成面または上面に略垂直な方向を向いていることがわかる。一方、同じ試料に対し、試料面に垂直にプローブ径が 300 nm の電子線を入射させたときの回折パターンを図 23 (B) に示す。図 23 (B) より、リング状の回折パターンが確認される。したがって、電子回折によっても、CAAc - OS に含まれるペレットの a 軸および b 軸は配向性を有さないことがわかる。なお、図 23 (B) における第 1 リングは、InGaZnO<sub>4</sub> の結晶の (010) 面および (100) 面などに起因すると考えられる。また、図 23 (B) における第 2 リングは (110) 面などに起因すると考えられる。

40

#### 【0263】

上述したように、CAAc - OS は結晶性の高い酸化物半導体である。酸化物半導体の結晶性は不純物の混入や欠陥の生成などによって低下する場合があるため、逆の見方をす

50

ると C A A C - O S は不純物や欠陥（酸素欠損など）の少ない酸化物半導体ともいえる。

#### 【 0 2 6 4 】

なお、不純物は、酸化物半導体の主成分以外の元素で、水素、炭素、シリコン、遷移金属元素などがある。例えば、シリコンなどの、酸化物半導体を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体から酸素を奪うことで酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体の原子配列を乱し、結晶性を低下させる要因となる。

#### 【 0 2 6 5 】

酸化物半導体が不純物や欠陥を有する場合、光や熱などによって特性が変動する場合がある。例えば、酸化物半導体に含まれる不純物は、キャリアトラップとなる場合や、キャリア発生源となる場合がある。また、酸化物半導体中の酸素欠損は、キャリアトラップとなる場合や、水素を捕獲することによってキャリア発生源となる場合がある。

10

#### 【 0 2 6 6 】

不純物および酸素欠損の少ない C A A C - O S は、キャリア密度の低い酸化物半導体である。具体的には、キャリア密度を  $8 \times 10^{11} / \text{cm}^3$  未満、好ましくは  $1 \times 10^{11} / \text{cm}^3$  未満、さらに好ましくは  $1 \times 10^{10} / \text{cm}^3$  未満であり、 $1 \times 10^{-9} / \text{cm}^3$  以上とすることができる。そのような酸化物半導体を、高純度真性または実質的に高純度真性な酸化物半導体と呼ぶ。C A A C - O S は、不純物濃度が低く、欠陥準位密度が低い。即ち、安定な特性を有する酸化物半導体であるといえる。

20

#### 【 0 2 6 7 】

< n c - O S >

次に、n c - O S について説明する。

#### 【 0 2 6 8 】

n c - O S は、高分解能 TEM 像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。n c - O S に含まれる結晶部は、1 nm 以上 10 nm 以下、または 1 nm 以上 3 nm 以下の大きさであることが多い。なお、結晶部の大きさが 10 nm より大きく 100 nm 以下である酸化物半導体を微結晶酸化物半導体と呼ぶことがある。n c - O S は、例えば、高分解能 TEM 像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、C A A C - O S におけるペレットと起源を同じくする可能性がある。そのため、以下では n c - O S の結晶部をペレットと呼ぶ場合がある。

30

#### 【 0 2 6 9 】

n c - O S は、微小な領域（例えば、1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。例えば、n c - O S に対し、ペレットよりも大きい径の X 線を用いた場合、o u t - o f - p l a n e 法による解析では、結晶面を示すピークは検出されない。また、n c - O S に対し、ペレットよりも大きいプローブ径（例えば 50 nm 以上）の電子線を用いる電子回折を行うと、ハローパターンのような回折パターンが観測される。一方、n c - O S に対し、ペレットの大きさと近いかペレットより小さいプローブ径の電子線を用いるナノビーム電子回折を行うと、スポットが観測される。また、n c - O S に対しナノビーム電子回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。さらに、リング状の領域内に複数のスポットが観測される場合がある。

40

#### 【 0 2 7 0 】

このように、ペレット（ナノ結晶）間では結晶方位が規則性を有さないことから、n c - O S を、R A N C ( R a n d o m A l i g n e d n a n o c r y s t a l s ) を有する酸化物半導体、または N A N C ( N o n - A l i g n e d n a n o c r y s t a l

50

s ) を有する酸化物半導体と呼ぶこともできる。

【0271】

n c - O S は、非晶質酸化物半導体よりも規則性の高い酸化物半導体である。そのため、n c - O S は、a - l i k e O S や非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O S は、異なるペレット間で結晶方位に規則性が見られない。そのため、n c - O S は、C A A C - O S と比べて欠陥準位密度が高くなる。

【0272】

< a - l i k e O S >

a - l i k e O S は、n c - O S と非晶質酸化物半導体との間の構造を有する酸化物半導体である。

10

【0273】

a - l i k e O S は、高分解能TEM像において鬆が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。

【0274】

鬆を有するため、a - l i k e O S は、不安定な構造である。以下では、a - l i k e O S が、C A A C - O S およびn c - O S と比べて不安定な構造であることを示すため、電子照射による構造の変化を示す。

【0275】

電子照射を行う試料として、a - l i k e O S (試料Aと表記する。)、n c - O S (試料Bと表記する。)およびC A A C - O S (試料Cと表記する。)を準備する。いずれの試料もIn - Ga - Zn酸化物である。

20

【0276】

まず、各試料の高分解能断面TEM像を取得する。高分解能断面TEM像により、各試料は、いずれも結晶部を有することがわかる。

【0277】

なお、どの部分を一つの結晶部と見なすかの判定は、以下のように行えればよい。例えば、InGaZnO<sub>4</sub>の結晶の単位格子は、In - O層を3層有し、またGa - Zn - O層を6層有する、計9層がc軸方向に層状に重なった構造を有することが知られている。これらの近接する層同士の間隔は、(009)面の格子面間隔(d値ともいう。)と同程度であり、結晶構造解析からその値は0.29nmと求められている。したがって、格子縞の間隔が0.28nm以上0.30nm以下である箇所を、InGaZnO<sub>4</sub>の結晶部と見なすことができる。なお、格子縞は、InGaZnO<sub>4</sub>の結晶のa - b面に対応する。

30

【0278】

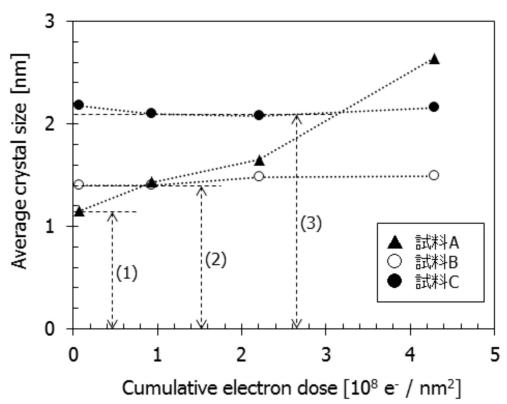

図24は、各試料の結晶部(22箇所から45箇所)の平均の大きさを調査した例である。ただし、上述した格子縞の長さを結晶部の大きさとしている。図24より、a - l i k e O S は、電子の累積照射量に応じて結晶部が大きくなっていくことがわかる。具体的には、図24中に(1)で示すように、TEMによる観察初期においては1.2nm程度の大きさだった結晶部(初期核ともいう。)が、累積照射量が4.2×10<sup>8</sup>e<sup>-</sup>/nm<sup>2</sup>においては2.6nm程度の大きさまで成長していることがわかる。一方、n c - O S およびC A A C - O S は、電子照射開始時から電子の累積照射量が4.2×10<sup>8</sup>e<sup>-</sup>/nm<sup>2</sup>までの範囲で、結晶部の大きさに変化が見られないことがわかる。具体的には、図24中の(2)および(3)で示すように、電子の累積照射量によらず、n c - O S およびC A A C - O S の結晶部の大きさは、それぞれ1.4nm程度および2.1nm程度であることがわかる。

40

【0279】

このように、a - l i k e O S は、電子照射によって結晶部の成長が見られる場合がある。一方、n c - O S およびC A A C - O S は、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a - l i k e O S は、n c - O S およびC A A C - O S と比べて、不安定な構造であることがわかる。

50

## 【0280】

また、鬆を有するため、a-like OSは、nc-OSおよびCAC-OSと比べて密度の低い構造である。具体的には、a-like OSの密度は、同じ組成の単結晶の密度の78.6%以上92.3%未満となる。また、nc-OSの密度およびCAC-OSの密度は、同じ組成の単結晶の密度の92.3%以上100%未満となる。単結晶の密度の78%未満となる酸化物半導体は、成膜すること自体が困難である。

## 【0281】

例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、菱面体晶構造を有する単結晶InGaZnO<sub>4</sub>の密度は6.357 g / cm<sup>3</sup>となる。よって、例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、a-like OSの密度は5.0 g / cm<sup>3</sup>以上5.9 g / cm<sup>3</sup>未満となる。また、例えば、In:Ga:Zn = 1:1:1 [原子数比] を満たす酸化物半導体において、nc-OSの密度およびCAC-OSの密度は5.9 g / cm<sup>3</sup>以上6.3 g / cm<sup>3</sup>未満となる。

10

## 【0282】

なお、同じ組成の単結晶が存在しない場合がある。その場合、任意の割合で組成の異なる単結晶を組み合わせることにより、所望の組成における単結晶に相当する密度を見積もることができる。所望の組成の単結晶に相当する密度は、組成の異なる単結晶を組み合わせる割合に対して、加重平均を用いて見積もればよい。ただし、密度は、可能な限り少ない種類の単結晶を組み合わせて見積もることが好ましい。

20

## 【0283】

以上のように、酸化物半導体は、様々な構造をとり、それぞれが様々な特性を有する。なお、酸化物半導体は、例えば、非晶質酸化物半導体、a-like OS、nc-OS、CAC-OSのうち、二種以上を有する積層膜であってもよい。

## 【0284】

<CAC-OS及びnc-OSの成膜方法>

次に、CAC-OSの成膜方法の一例について説明する。

## 【0285】

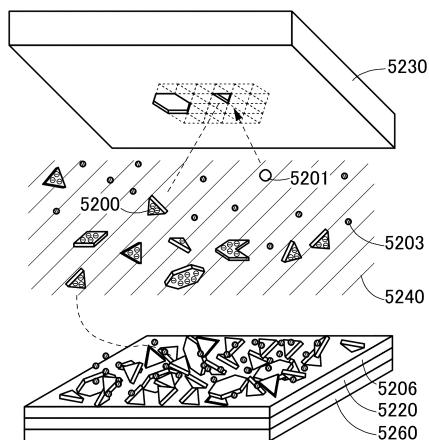

図25(A)は、成膜室内の模式図である。CAC-OSは、スパッタリング法により成膜することができる。

30

## 【0286】

図25(A)に示すように、基板5220とターゲット5230とは向かい合うように配置している。基板5220とターゲット5230との間にはプラズマ5240がある。また、基板5220の下部には加熱機構5260が設けられている。図示しないが、ターゲット5230は、バッキングプレートに接着されている。バッキングプレートを介してターゲット5230と向かい合う位置には、複数のマグネットが配置される。マグネットの磁場を利用して成膜速度を高めるスパッタリング法は、マグнетロンスパッタリング法と呼ばれる。

## 【0287】

基板5220とターゲット5230との距離d(ターゲット-基板間距離(T-S間距離)ともいう。)は0.01m以上1m以下、好ましくは0.02m以上0.5m以下とする。成膜室内は、ほとんどが成膜ガス(例えば、酸素、アルゴン、または酸素を5体積%以上の割合で含む混合ガス)で満たされ、0.01Pa以上100Pa以下、好ましくは0.1Pa以上10Pa以下に制御される。ここで、ターゲット5230に一定以上の電圧を印加することで、放電が始まり、プラズマ5240が確認される。なお、ターゲット5230の近傍には磁場によって、高密度プラズマ領域が形成される。高密度プラズマ領域では、成膜ガスがイオン化することで、イオン5201が生じる。イオン5201は、例えば、酸素の陽イオン(O<sup>+</sup>)やアルゴンの陽イオン(Ar<sup>+</sup>)などである。

40

## 【0288】

ターゲット5230は、複数の結晶粒を有する多結晶構造を有し、いずれかの結晶粒に

50

は劈開面が含まれる。一例として、図26に、ターゲット5230に含まれるInMznO<sub>4</sub>（元素Mは、例えばGaまたはSn）の結晶構造を示す。なお、図26は、b軸に平行な方向から観察した場合のInMznO<sub>4</sub>の結晶構造である。InMznO<sub>4</sub>の結晶では、酸素原子が負の電荷を有することにより、近接する二つのM-Zn-O層の間に斥力が生じている。そのため、InMznO<sub>4</sub>の結晶は、近接する二つのM-Zn-O層の間に劈開面を有する。

#### 【0289】

高密度プラズマ領域で生じたイオン5201は、電界によってターゲット5230側に加速され、やがてターゲット5230と衝突する。このとき、劈開面から平板状またはペレット状のスパッタ粒子であるペレット5200が剥離する（図25（A）参照）。 10

#### 【0290】

ペレット5200は、図26に示す二つの劈開面に挟まれた部分である。よって、ペレット5200のみ抜き出すと、その断面は図25（B）のようになり、上面は図25（C）のようになることがわかる。なお、ペレット5200は、イオン5201の衝突の衝撃によって、構造に歪みが生じる場合がある。なお、ペレット5200の剥離に伴い、ターゲット5230から粒子5203も弾き出される。粒子5203は、原子1個または原子数個の集合体を有する。そのため、粒子5203を原子状粒子（atomic particles）と呼ぶこともできる。

#### 【0291】

ペレット5200は、三角形、例えば正三角形の平面を有する平板状またはペレット状のスパッタ粒子である。または、ペレット5200は、六角形、例えば正六角形の平面を有する平板状またはペレット状のスパッタ粒子である。ただし、ペレット5200の形状は、三角形、六角形に限定されない、例えば、三角形が複数個合わさった形状となる場合がある。例えば、三角形（例えば、正三角形）が2個合わさった四角形（例えば、ひし形）となる場合もある。 20

#### 【0292】

ペレット5200は、成膜ガスの種類などに応じて厚さが決定する。例えば、ペレット5200は、厚さを0.4nm以上1nm以下、好ましくは0.6nm以上0.8nm以下とする。また、例えば、ペレット5200は、幅を1nm以上3nm以下、好ましくは1.2nm以上2.5nm以下とする。例えば、In-M-Zn酸化物を有するターゲット5230にイオン5201を衝突させる。そうすると、M-Zn-O層、In-O層およびM-Zn-O層の3層を有するペレット5200が剥離する。なお、ペレット5200の剥離に伴い、ターゲット5230から粒子5203も弾き出される。 30

#### 【0293】

ペレット5200は、プラズマ5240を通過する際に、表面が負または正に帯電する場合がある。例えば、ペレット5200がプラズマ5240中にあるO<sup>2-</sup>から負の電荷を受け取る場合がある。その結果、ペレット5200の表面の酸素原子が負に帯電する場合がある。また、ペレット5200は、プラズマ5240を通過する際に、プラズマ5240中のインジウム、元素M、亜鉛または酸素などと結合することで成長する場合がある。 40

#### 【0294】

プラズマ5240を通過したペレット5200および粒子5203は、基板5220の表面に達する。なお、粒子5203の一部は、質量が小さいため真空ポンプなどによって外部に排出される場合がある。

#### 【0295】

次に、基板5220の表面におけるペレット5200および粒子5203の堆積について図27を用いて説明する。

#### 【0296】

まず、一つ目のペレット5200が基板5220に堆積する。ペレット5200は平板状であるため、平面側を基板5220の表面に向けて堆積する（図27（A）参照）。 50

のとき、ペレット 5200 の基板 5220 側の表面の電荷が、基板 5220 を介して抜け

る。

【0297】

次に、二つ目のペレット 5200 が、基板 5220 に達する。このとき、一つ目のペレ

ット 5200 の表面、および二つ目のペレット 5200 の表面が電荷を帯びているため、

互いに反発し合う力が生じる（図 27（B）参照）。

【0298】

その結果、二つ目のペレット 5200 は、一つ目のペレット 5200 上を避け、基板 5

220 の表面の少し離れた場所に堆積する（図 27（C）参照）。これを繰り返すこと

で、基板 5220 の表面には、無数のペレット 5200 が一層分の厚みだけ堆積する。また

、ペレット 5200 と別のペレット 5200 との間には、ペレット 5200 の堆積してい

ない領域が生じる。

10

【0299】

次に、粒子 5203 が基板 5220 の表面に達する（図 27（D）参照）。

【0300】

粒子 5203 は、ペレット 5200 の表面などの活性な領域には堆積することができ

ない。そのため、ペレット 5200 の堆積していない領域を埋めるように堆積する。そして

、ペレット 5200 間で粒子 5203 が横方向に成長（ラテラル成長ともいう。）するこ

とで、ペレット 5200 間を連結させる。このように、ペレット 5200 の堆積してい

ない領域を埋めるまで粒子 5203 が堆積する。このメカニズムは、ALD 法の堆積メカニ

ズムに類似する。

20

【0301】

なお、ペレット 5200 間で粒子 5203 がラテラル成長するメカニズムは複数の可

能性がある。例えば、図 27（E）に示すように、一層目の M-Zn-O 層の側面から連結

するメカニズムがある。この場合、一層目の M-Zn-O 層が形成された後で、In-O

層、二層目の M-Zn-O 層の順に、一層ずつ連結していく（第 1 のメカニズム）。

【0302】

または、例えば、図 28（A）に示すように、まず一層目の M-Zn-O 層の一側面に

つき粒子 5203 の一つが結合する。次に、図 28（B）に示すように In-O 层の一側面に

つき一つの粒子 5203 が結合する。次に、図 28（C）に示すように二層目の M-

Zn-O 层の一側面につき一つの粒子 5203 が結合することで連結する場合もある（第

2 のメカニズム）。

30

【0303】

なお、図 28（A）、図 28（B）および図 28（C）が同時に起こることで連結する

場合もある（第 3 のメカニズム）。

【0304】

以上に示したように、ペレット 5200 間における粒子 5203 のラテラル成長のメカ

ニズムとしては、上記 3 種類が考えられる。ただし、その他のメカニズムによってペレ

ット 5200 間で粒子 5203 がラテラル成長する可能性もある。

40

【0305】

したがって、複数のペレット 5200 がそれぞれ異なる方向を向いている場合でも、複

数のペレット 5200 間を粒子 5203 がラテラル成長しながら埋めることにより、結晶

粒界の形成が抑制される。また、複数のペレット 5200 間を、粒子 5203 が滑らかに

結びつけるため、単結晶とも多結晶とも異なる結晶構造が形成される。言い換えると、微

小な結晶領域（ペレット 5200）間に歪みを有する結晶構造が形成される。このよう

に、結晶領域間を埋める領域は、歪んだ結晶領域であるため、該領域を指して非晶質構造と

呼ぶのは適切ではないと考えられる。

【0306】

粒子 5203 が、ペレット 5200 間を埋め終わると、ペレット 5200 と同程度の厚

さを有する第 1 の層が形成される。第 1 の層の上には新たな一つ目のペレット 5200 が

50

堆積する。そして、第2の層が形成される。さらに、これが繰り返されることで、積層体を有する薄膜構造が形成される。

【0307】

なお、ペレット5200の堆積の仕方は、基板5220の表面温度などによっても変化する。例えば、基板5220の表面温度が高いと、ペレット5200が基板5220の表面でマイグレーションを起こす。その結果、ペレット5200と別のペレット5200とが、粒子5203を介さずに連結する割合が増加するため、配向性の高いCAC-OSとなる。CAC-OSを成膜する際の基板5220の表面温度は、100以上500未満、好ましくは140以上450未満、さらに好ましくは170以上400未満である。したがって、基板5220として第8世代以上の大面积基板を用いた場合でも、反りなどはほとんど生じないことがわかる。

10

【0308】

一方、基板5220の表面温度が低いと、ペレット5200が基板5220の表面でマイグレーションを起こしにくくなる。その結果、ペレット5200同士が積み重なることで配向性の低いnc-OSとなる(図29参照)。nc-OSでは、ペレット5200が負に帯電していることにより、ペレット5200は一定間隔を開けて堆積する可能性がある。したがって、配向性は低いものの、僅かに規則性を有することにより、非晶質酸化物半導体と比べて緻密な構造となる。

【0309】

また、CAC-OSにおいて、ペレット同士の隙間が極めて小さくなることで、一つの大きなペレットが形成される場合がある。一つの大きなペレットの内部は単結晶構造を有する。例えば、ペレットの大きさが、上面から見て10nm以上200nm以下、15nm以上100nm以下、または20nm以上50nm以下となる場合がある。

20

【0310】

以上のようなモデルにより、ペレット5200が基板5220の表面に堆積していくと考えられる。被形成面が結晶構造を有さない場合においても、CAC-OSの成膜が可能であることから、エピタキシャル成長とは異なる成長機構であることがわかる。また、CAC-OSおよびnc-OSは、大面积のガラス基板などであっても均一な成膜が可能である。例えば、基板5220の表面(被形成面)の構造が非晶質構造(例えば非晶質酸化シリコン)であっても、CAC-OSを成膜することは可能である。

30

【0311】

また、被形成面である基板5220の表面に凹凸がある場合でも、その形状に沿ってペレット5200が配列することがわかる。

【0312】

以上、本実施の形態で示す構成、方法は、他の実施の形態で示す構成、方法と適宜組み合わせて用いることができる。

【0313】

(実施の形態3)

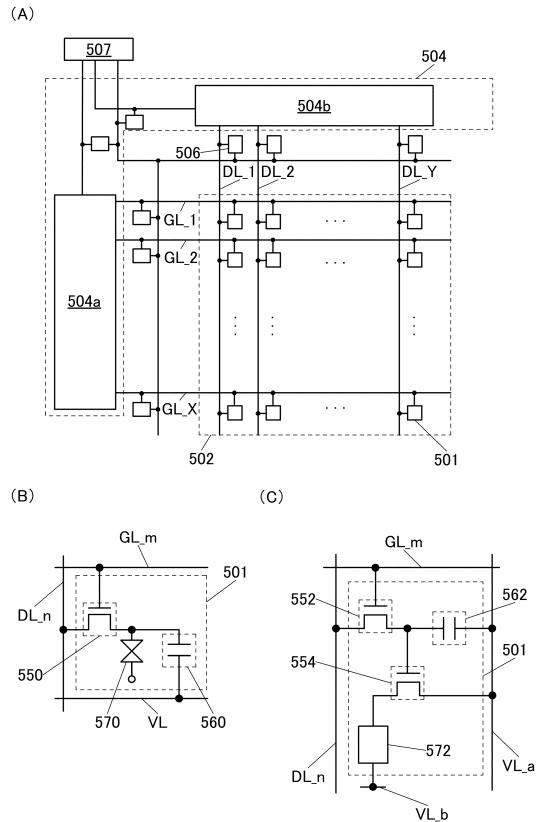

本実施の形態では、本発明の一態様の半導体装置を有する表示装置について、図30を用いて説明を行う。

40

【0314】

<表示装置に関する説明>

図30(A)に示す表示装置は、表示素子の画素を有する領域(以下、画素部502という)と、画素部502の外側に配置され、画素を駆動するための回路を有する回路部(以下、駆動回路部504という)と、素子の保護機能を有する回路(以下、保護回路506という)と、端子部507と、を有する。なお、保護回路506は、設けない構成としてもよい。

【0315】

駆動回路部504の一部、または全部は、画素部502と同一基板上に形成されていることが望ましい。これにより、部品数や端子数を減らすことが出来る。駆動回路部504

50

の一部、または全部が、画素部 502 と同一基板上に形成されていない場合には、駆動回路部 504 の一部、または全部は、COG や TAB (Tape Automated Bonding) によって、実装することができる。

#### 【0316】

画素部 502 は、X 行 (X は 2 以上の自然数) Y 列 (Y は 2 以上の自然数) に配置された複数の表示素子を駆動するための回路 (以下、画素回路 501 という) を有し、駆動回路部 504 は、画素を選択する信号 (走査信号) を出力する回路 (以下、ゲートドライバ 504a という)、画素の表示素子を駆動するための信号 (データ信号) を供給するための回路 (以下、ソースドライバ 504b) などの駆動回路を有する。

#### 【0317】

ゲートドライバ 504a は、シフトレジスタ等を有する。ゲートドライバ 504a は、端子部 507 を介して、シフトレジスタを駆動するための信号が入力され、信号を出力する。例えば、ゲートドライバ 504a は、スタートパルス信号、クロック信号等が入力され、パルス信号を出力する。ゲートドライバ 504a は、走査信号が与えられる配線 (以下、走査線 GL\_1 乃至 GL\_X という) の電位を制御する機能を有する。なお、ゲートドライバ 504a を複数設け、複数のゲートドライバ 504a により、走査線 GL\_1 乃至 GL\_X を分割して制御してもよい。または、ゲートドライバ 504a は、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ゲートドライバ 504a は、別の信号を供給することも可能である。

#### 【0318】

ソースドライバ 504b は、シフトレジスタ等を有する。ソースドライバ 504b は、端子部 507 を介して、シフトレジスタを駆動するための信号の他、データ信号の元となる信号 (画像信号) が入力される。ソースドライバ 504b は、画像信号を元に画素回路 501 に書き込むデータ信号を生成する機能を有する。また、ソースドライバ 504b は、スタートパルス、クロック信号等が入力されて得られるパルス信号に従って、データ信号の出力を制御する機能を有する。また、ソースドライバ 504b は、データ信号が与えられる配線 (以下、データ線 DL\_1 乃至 DL\_Y という) の電位を制御する機能を有する。または、ソースドライバ 504b は、初期化信号を供給することができる機能を有する。ただし、これに限定されず、ソースドライバ 504b は、別の信号を供給することも可能である。

#### 【0319】

ソースドライバ 504b は、例えば複数のアナログスイッチなどを用いて構成される。ソースドライバ 504b は、複数のアナログスイッチを順次オン状態にすることにより、画像信号を時分割した信号をデータ信号として出力できる。また、シフトレジスタなどを用いてソースドライバ 504b を構成してもよい。

#### 【0320】

複数の画素回路 501 のそれぞれは、走査信号が与えられる複数の走査線 GL の一つを介してパルス信号が入力され、データ信号が与えられる複数のデータ線 DL の一つを介してデータ信号が入力される。また、複数の画素回路 501 のそれぞれは、ゲートドライバ 504a によりデータ信号のデータの書き込み及び保持が制御される。例えば、m 行 n 列目の画素回路 501 は、走査線 GL\_m (m は X 以下の自然数) を介してゲートドライバ 504a からパルス信号が入力され、走査線 GL\_m の電位に応じてデータ線 DL\_n (n は Y 以下の自然数) を介してソースドライバ 504b からデータ信号が入力される。

#### 【0321】

図 30 (A) に示す保護回路 506 は、例えば、ゲートドライバ 504a と画素回路 501 の間の配線である走査線 GL に接続される。または、保護回路 506 は、ソースドライバ 504b と画素回路 501 の間の配線であるデータ線 DL に接続される。または、保護回路 506 は、ゲートドライバ 504a と端子部 507 との間の配線に接続することができる。または、保護回路 506 は、ソースドライバ 504b と端子部 507 との間の配線に接続することができる。なお、端子部 507 は、外部の回路から表示装置に電源及び

10

20

30

40

50

制御信号、及び画像信号を入力するための端子が設けられた部分をいう。

【0322】

保護回路506は、自身が接続する配線に一定の範囲外の電位が与えられたときに、該配線と別の配線とを導通状態にする回路である。

【0323】

図30(A)に示すように、画素部502と駆動回路部504にそれぞれ保護回路506を設けることにより、ESD(Electro Static Discharge:静電気放電)などにより発生する過電流に対する表示装置の耐性を高めることができる。ただし、保護回路506の構成はこれに限定されず、例えば、ゲートドライバ504aに保護回路506を接続した構成、またはソースドライバ504bに保護回路506を接続した構成とすることもできる。あるいは、端子部507に保護回路506を接続した構成とすることもできる。

10

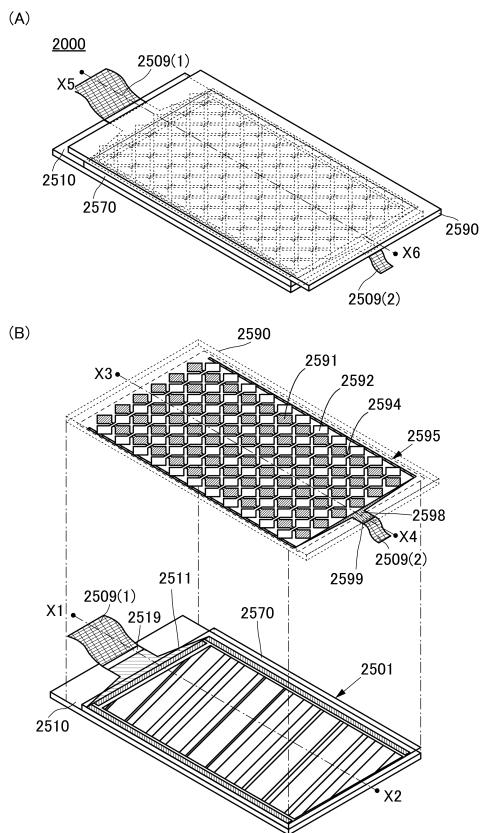

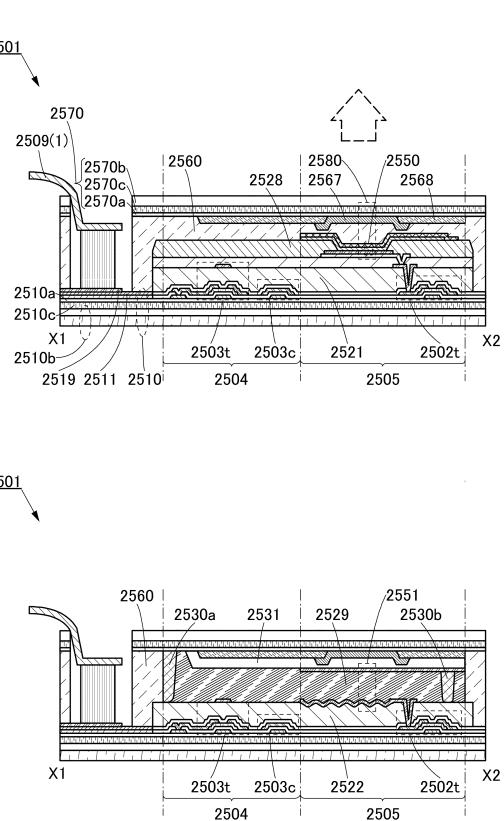

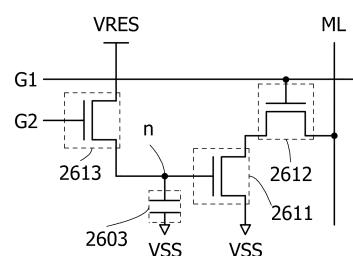

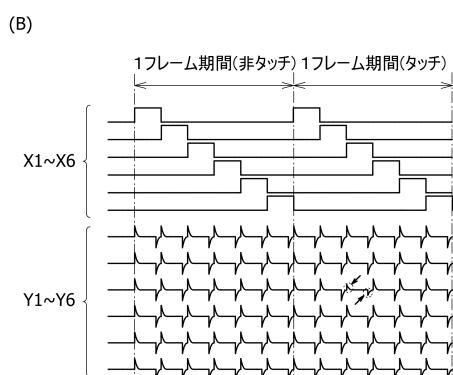

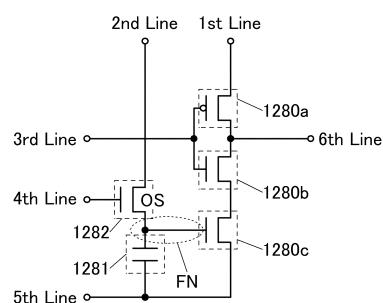

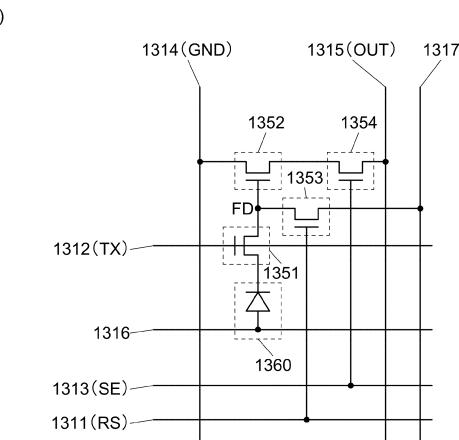

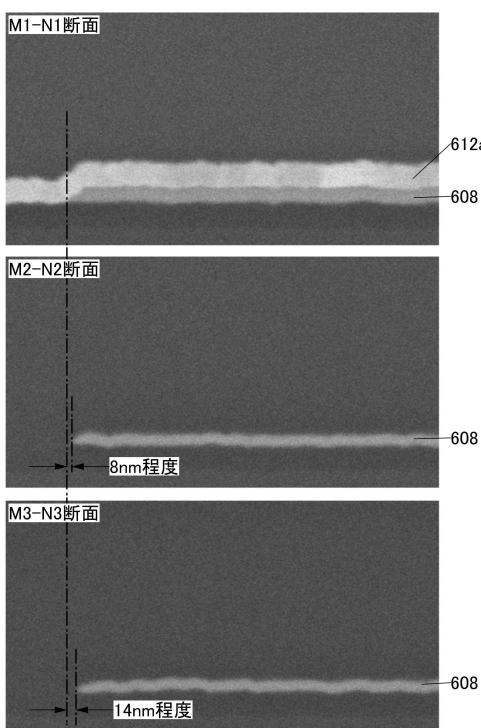

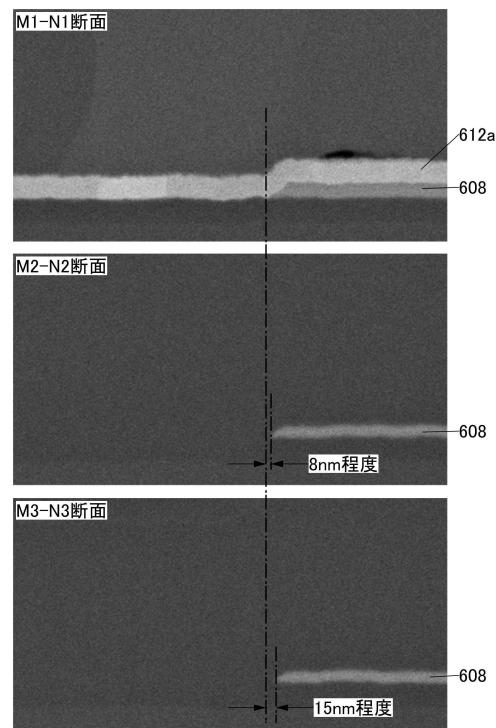

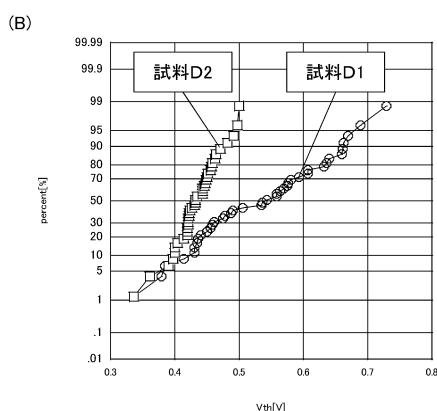

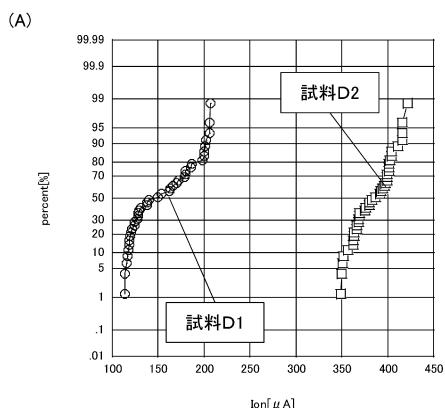

【0324】