(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-22093

(P2004-22093A)

(43) 公開日 平成16年1月22日(2004.1.22)

(51) Int.Cl.<sup>7</sup>**G 11 C 16/06**

H 01 L 21/8242

H 01 L 27/108

F 1

G 11 C 17/00

H 01 L 27/10

テーマコード(参考)

5 B 02 5

5 F 08 3

審査請求 有 請求項の数 12 O L (全 20 頁)

(21) 出願番号

(22) 出願日特願2002-176931 (P2002-176931)

平成14年6月18日 (2002. 6. 18)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100075812

弁理士 吉武 賢次

(74) 代理人 100088889

弁理士 橋谷 英俊

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100096921

弁理士 吉元 弘

(74) 代理人 100103263

弁理士 川崎 康

(74) 代理人 100107582

弁理士 関根 翔

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【要約】

【課題】同相雜音の補償を精度よく行う。

【解決手段】ビット線BLに沿って、基準ビット線RBL0、RBL1を形成し、この基準ビット線RBL0、RBL1とワード線WLとの交点位置に、基準セルRC0、RC1を配置する。データ読み出しの際には、これら基準セルRC0、RC1は、選択されたワード線WLにより、データを読み出すメモリセルMCと同様に活性化される。そして、この活性化された基準セルRC0、RC1を用いて基準電流I0 + I1を生成し、メモリセルMCのデータを読み出す際に使用する。これにより、データを読み出そうとしているメモリセルMCと基準セルRC0、RC1との間の距離を、所定範囲内に制限することができる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

第1方向に沿って互いに並列に形成された、複数のワード線と、

前記第1方向と交差する方向である第2方向に沿って互いに並列に形成された、複数のビット線と、

前記ワード線と前記ビット線の交点位置に設けられた複数のメモリセルであって、前記ビット線に接続されたドレイン領域と、ソース線に接続されたソース領域と、前記ワード線に接続されたゲート電極と、前記ドレイン領域と前記ソース領域との間に位置する電気的にフローティング状態であるフローティングボディとを有するMISFETにより構成されており、前記フローティングボディに多数キャリアを蓄積し又は前記フローティングボディから多数キャリアを放出することによりMISFETのしきい値を変化させてデータを記憶する、メモリセルと、

前記第2方向に沿って形成された、複数の基準ビット線と、

前記ワード線と前記複数の基準ビット線との交点位置に設けられた複数の基準セルであって、前記メモリセルからデータを読み出す際に、データを読み出すメモリセルの接続されたワード線により $2^N$ (Nは自然数)個が活性化され、データを読み出す際の基準となる基準電流を生成する、基準セルと、

前記基準電流と、読み出すメモリセルを流れるセル電流に基づいて、前記メモリセルのデータを読み出す、データセンス回路と、

を備えることを特徴とする半導体記憶装置。

10

20

30

**【請求項 2】**

前記基準セルの構造は、前記メモリセルの構造と同等である、ことを特徴とする請求項1に記載の半導体記憶装置。

**【請求項 3】**

1つのセンシングシステムにおいて、前記基準ビット線を基準として、前記第1方向の一方側に設けられているビット線の本数と、前記第1方向の他方側に設けられているビット線の本数とは、等しい、ことを特徴とする請求項1又は請求項2に記載の半導体記憶装置。

**【請求項 4】**

前記データセンス回路は、

活性化された $2^N$ 個の基準セルにより生成された前記基準電流に基づいて、基準電圧を発生する、基準電圧発生回路と、

前記基準電圧と前記セル電流に基づいてデータ電圧を生成し、このデータ電圧と前記基準電圧を比較することにより、メモリセルのデータを読み出す、センスアンプ回路と、を備えることを特徴とする請求項1乃至請求項3のいずれかに記載の半導体記憶装置。

**【請求項 5】**

1つの基準電圧発生回路に対して $2^N$ 本の基準ビット線が設けられている、ことを特徴とする請求項4に記載の半導体記憶装置。

**【請求項 6】**

1つの基準電圧発生回路に対して1つのセンスアンプ回路が設けられている、ことを特徴とする請求項4又は請求項5に記載の半導体記憶装置。

40

**【請求項 7】**

1つの基準電圧発生回路に対して複数のセンスアンプ回路が設けられている、ことを特徴とする請求項4又は請求項5に記載の半導体記憶装置。

**【請求項 8】**

1本のワード線により活性化される $2^N$ 個の基準セルのうち、N個の基準セルは“0”データが格納されるためのものであり、残りのN個の基準セルは“1”データが格納されるためのものである、ことを特徴とする請求項1乃至請求項7のいずれかに記載の半導体記憶装置。

**【請求項 9】**

50

前記データセンス回路は、 $2N$ 個の基準セルを流れる電流の合計である基準電流をP倍（Pは任意の正の数）し、読み出すメモリセルを流れるセル電流をQ倍（Qは任意の正の数）し、これらP倍した基準電流とQ倍したセル電流とを比較することにより、メモリセルの記憶しているデータを読み出す、ことを特徴とする請求項8に記載の半導体記憶装置。

#### 【請求項10】

P/Qは $1/2N$ であるように設計されている、ことを特徴とする請求項9に記載の半導体記憶装置。

#### 【請求項11】

第1方向に沿って互いに並列に形成された、複数のワード線と、

前記第1方向と交差する方向である第2方向に沿って互いに並列に形成された、複数のビット線と、10

前記ワード線と前記ビット線の交点位置に設けられた複数のメモリセルと、

前記第2方向に沿って形成された、複数の基準ビット線と、

前記ワード線と前記複数の基準ビット線との交点位置に設けられた複数の基準セルであつて、前記メモリセルからデータを読み出す際に、データを読み出すメモリセルの接続されたワード線により $2N$ （Nは自然数）個が活性化され、データを読み出す際の基準となる基準電流を生成する、基準セルと、

前記基準電流と、読み出すメモリセルを流れるセル電流とに基づいて、前記メモリセルのデータを読み出す、データセンス回路と、

を備えることを特徴とする半導体記憶装置。20

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は半導体記憶装置に関し、特に、基準セルを流れる基準電流を用いてメモリセルが記憶しているデータを読み出す電流読み出し型の半導体記憶装置に関する。

##### 【0002】

##### 【従来の技術】

デザインルールFが $0.1\mu m$ 未満において、セルサイズを $6F^2$ 未満の大きさにする事がダイナミック型の半導体記憶装置（DRAM）に課せられた課題であるが、これが実現できるDRAMとして、FBC（floating body transistor cell）によりメモリセルが構成されたものが提案されている（例えば、特願2001-245584号、特願2001-328204号、特願2001-220461号参照。いずれも本件出願時において未公開）。このFBCは、SOIなどの上に形成したフローティングボディを持つMISFETにより構成されており、このMISFETのフローティングボディにインパクトイオン化により多数キャリアを注入したり、ソース領域またはドレイン領域とフローティングボディの間のpn接合を順方向にバイアスして多数キャリアを引き抜いたりすることにより、フローティングボディの電位を変化させて、基板バイアス効果によりこのMISFETのしきい値電圧Vthを変化させることにより、データを記憶する。30

##### 【0003】

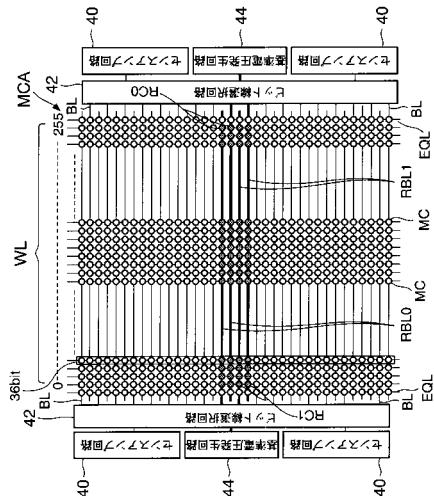

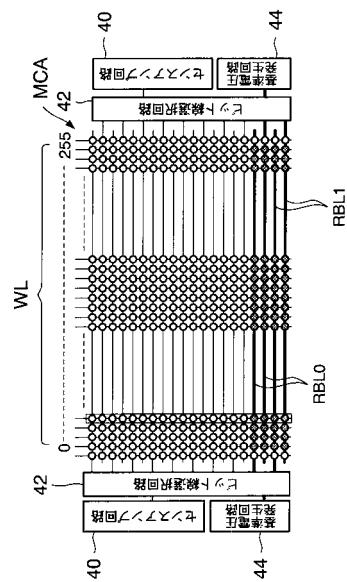

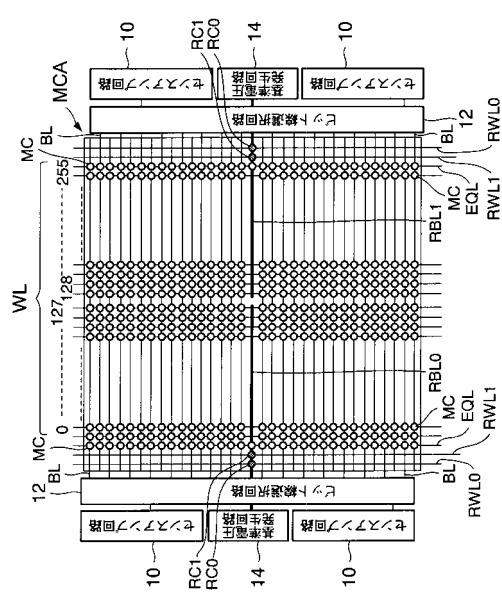

図13は、FBCのメモリセルMCにより構成された8KビットのメモリセルアレイMCAを有する半導体記憶装置の部分的な配置図を示している。この図13に示すように、FBCにより構成されたメモリセルアレイMCAを有する半導体記憶装置は、メモリセルアレイMCAの両側に、センスアンプ回路10を配置するダブルエンド型センスアンプ方式を採用している。また、このメモリセルアレイMCAにおいては、ビット線選択回路12により、8本のビット線BLから、1本のビット線BLを選択して、センスアンプ回路10に接続すると共に、基準電圧発生回路14は、2個のセンスアンプ回路10に対して1個設けられている。40

##### 【0004】

FBCは非破壊読み出しが可能なメモリセルMCであり、MISFETのドレインからソ50

ースにセル電流を流し、流れるセル電流  $I_{c e l l}$  を検出する。また、“0”データを保持している基準セル  $R C 0$  と、“1”データを保持している基準セル  $R C 1$  とを、1つのメモリセルアレイ  $MCA$  上に別途設ける。この基準セル  $R C 0$ 、 $R C 1$  は、1つの基準電圧発生回路  $14$  に対して、1対、設けられる。そして、この基準セル  $R C 0$  に流れる電流  $I_0$  と、基準セル  $R C 1$  に流れる電流  $I_1$  を合わせた基準電流  $I_0 + I_1$  と、セル電流を2倍した  $2 \times I_{c e l l}$  とを比較して、メモリセル  $MC$  のしきい値が高い状態にあるのか、それとも低い状態にあるのかを検出し、メモリセル  $MC$  が記憶しているデータを読み出す。このような  $FBC$  のメモリセル  $MC$  の電流読み出し方式は、特願2002-76374号に記述されている（本件出願時において未公開）。

## 【0005】

10

基準セル  $R C 0$  と基準セル  $R C 1$  は、メモリセルアレイ  $MCA$  の中央で2分割されている基準ビット線  $RBL_0$ 、 $RBL_1$  に、それぞれ接続されている。また、各基準セル  $R C 0$  のゲートには、基準ワード線  $RWL_0$  が接続されており、各基準セル  $R C 1$  のゲートには、基準ワード線  $RWL_1$  が接続されている。

## 【0006】

20

基準ビット線  $RBL_0$ 、 $RBL_1$  と通常のワード線  $WL$  との交点位置には、通常のメモリセル  $MC$  は配置されておらず、また、基準ワード線  $RWL_0$ 、 $RWL_1$  と通常のビット線  $BL$  との交点位置にもメモリセルは配置されていない。また、ビット線  $BL$  と基準ビット線  $RBL_0$ 、 $RBL_1$  には、それぞれ、イコライズ線  $EQL$  にゲートが接続された  $FBC$  が1個ずつ設けられており、ビット線  $BL$  と基準ビット線  $RBL_0$ 、 $RBL_1$  の電位を0V ( $GND$ ) に設定する。

## 【0007】

20

## 【発明が解決しようとする課題】

図13に示した半導体記憶装置においては、メモリセルの形成位置に依存するセル特性バラツキと温度によるセル特性バラツキを、同相雑音（common mode noise）として補償することができる。図13に示すように、8Kビットのメモリセルアレイ  $MCA$  内に位置するメモリセル  $MC$  であれば、その形成位置に依存するセル特性バラツキは無視できるし、温度変化によるセル特性バラツキも無視できる。何故ならば、読み出そうとするメモリセル  $MC$  と基準となる2個の基準セル  $R C 0$ 、 $R C 1$  は、同じ構造の  $FBC$  から構成されており、このため、例えば、メモリセル  $MC$  のしきい値  $V_{th}$ 、モビリティ、ゲート酸化膜厚、チャンネル長、チャンネル幅などのセル特性を決めるデバイスパラメータの変動が、1つのメモリセルアレイ  $MCA$  内であれば、メモリセル  $MC$  と基準セル  $R C 0$ 、 $R C 1$  と同じように生じていると考えられるからである。

30

## 【0008】

このような場合、センスアンプ回路  $10$  の特性上、それら変動がある程度以上に大きくならない限り、セル電流  $I_{c e l l}$  と基準電流  $I_0 + I_1$  との関係はほぼ変わらないとみなせる。言い換えると、セル特性の変動は、いわゆる同相雑音（common mode noise）として補償される。

## 【0009】

40

それでは、果たして上記デバイスパラメータのプロセス変動と温度変動が、読み出そうとしているメモリセル  $MC$  と基準となる2個の基準セル  $R C 0$ 、 $R C 1$  に同じ傾向で現れているという仮定が成り立つかどうかが問題であるが、これら3個の  $FBC$  がある程度物理的に近い位置に存在していて、かつ、これら  $FBC$  の周囲環境がある程度同一であれば、この仮定がある程度成り立つと考えてよい。

## 【0010】

しかしながら、上述したような電流読み出し方式においては、ビット線  $BL$  の長さが長くなったり、基準電圧発生回路  $14$  をもっと多くのセンスアンプ回路  $10$  で共有化したりすると、読み出すメモリセル  $MC$  と基準セル  $R C 0$ 、 $R C 1$  の間の相対的な距離が離れてくるので、同相雑音の補償の精度が下がってくるおそれもある。

## 【0011】

50

そこで本発明は、前記課題に鑑みてなされたものであり、読み出されるメモリセルと基準となる基準セルの配置位置を、可能な限り近づけて、より精度の良い同相雑音補償を可能にした半導体記憶装置を提供することを目的とする。

### 【0012】

#### 【課題を解決するための手段】

上記課題を解決するため、本発明に係る半導体記憶装置は、第1方向に沿って互いに並列に形成された、複数のワード線と、前記第1方向と交差する方向である第2方向に沿って互いに並列に形成された、複数のビット線と、前記ワード線と前記ビット線の交点位置に設けられた複数のメモリセルであって、前記ビット線に接続されたドレイン領域と、ソース線に接続されたソース領域と、前記ワード線に接続されたゲート電極と、前記ドレイン領域と前記ソース領域との間に位置する電気的にフローティング状態であるフローティングボディとを有するMISFETにより構成されており、前記フローティングボディに多数キャリアを蓄積し又は前記フローティングボディから多数キャリアを放出することによりMISFETのしきい値を変化させてデータを記憶する、メモリセルと、前記第2方向に沿って形成された、複数の基準ビット線と、前記ワード線と前記複数の基準ビット線との交点位置に設けられた複数の基準セルであって、前記メモリセルからデータを読み出す際に、データを読み出すメモリセルの接続されたワード線により $2^N$ (Nは自然数)個が活性化され、データを読み出す際の基準となる基準電流を生成する、基準セルと、前記基準電流と、読み出すメモリセルを流れるセル電流とに基づいて、前記メモリセルのデータを読み出す、データセンス回路と、を備えることを特徴とする。

10

20

30

### 【0013】

本発明に係る半導体記憶装置は、第1方向に沿って互いに並列に形成された、複数のワード線と、前記第1方向と交差する方向である第2方向に沿って互いに並列に形成された、複数のビット線と、前記ワード線と前記ビット線の交点位置に設けられた複数のメモリセルと、前記第2方向に沿って形成された、複数の基準ビット線と、前記ワード線と前記複数の基準ビット線との交点位置に設けられた複数の基準セルであって、前記メモリセルからデータを読み出す際に、データを読み出すメモリセルの接続されたワード線により $2^N$ (Nは自然数)個が活性化され、データを読み出す際の基準となる基準電流を生成する、基準セルと、前記基準電流と、読み出すメモリセルを流れるセル電流とに基づいて、前記メモリセルのデータを読み出す、データセンス回路と、を備えることを特徴とする。

30

### 【0014】

#### 【発明の実施の形態】

##### 〔第1実施形態〕

本発明の第1実施形態は、1つの基準電圧発生回路に対して2本の基準ビット線を設けるとともに、各ワード線と各基準ビット線との交点に基準セルを配置する。そして、基準電圧発生回路は、データを読み出すメモリセルと同じワード線に設けられている2個の基準セルを用いて、基準電流を生成することにより、データを読み出すメモリセルと、基準セルとの間の距離が一定範囲内に制限されたようにしたのである。より詳しくを、以下に説明する。

40

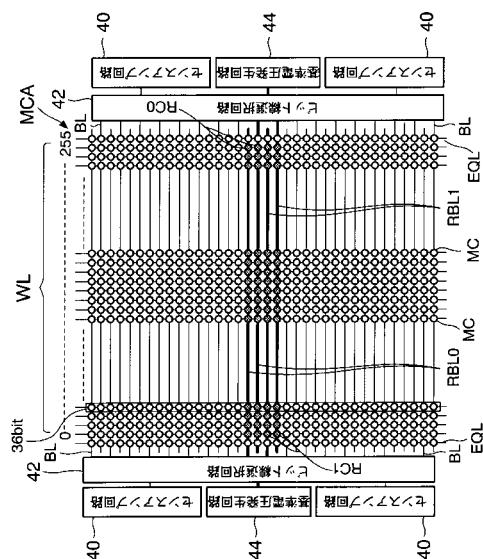

### 【0015】

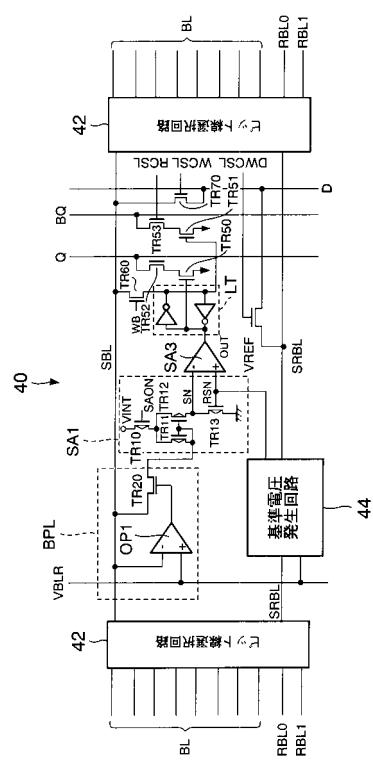

図1は、本実施形態に係る半導体記憶装置の部分的な配置図であり、図2は、本実施形態に係るメモリセルアレイを構成するメモリセルMCの構造を説明する断面図であり、図3は、各メモリセルMCの接続関係を示す回路図である。

### 【0016】

図2に示すように、本実施形態に係るメモリセルMCは、フローティングのチャネルボディを持つ一つのMISFETにより構成される。具体的には、例えば、シリコンにより形成された半導体基板20上に、絶縁膜22が形成されている。本実施形態においては、この絶縁膜22は、例えば、シリコン酸化膜により構成されている。

### 【0017】

絶縁膜22上には、p型の半導体層24が形成されている。つまり、本実施形態における

50

メモリセルMCはSOI (silicon on insulator) 基板上に形成される。半導体層24には、n型のソース領域26と、n型のドレイン領域28が形成されている。これらソース領域26とドレイン領域28とは、絶縁膜22に達する深さまで形成されている。このソース領域26とドレイン領域28との間の半導体層24は、フローティングボディ30を形成する。また、フローティングボディ30のチャネル幅方向には、他のメモリセルから絶縁するための絶縁領域(図示省略)が形成されている。このフローティングボディ30は、ソース領域26とドレイン領域28と絶縁膜22と絶縁領域により、他のメモリセルMCから電気的に絶縁されることとなり、フローティング状態になる。フローティングボディ30上には、ゲート絶縁膜32を介して、ゲート電極34が形成されている。

10

## 【0018】

図3に示すように、各メモリセルMCは、ワード線WLとビット線BLの交点位置に設けられており、そのソース領域26は共通のソース線によりグランドに接続され、ドレイン領域28はビット線BLに接続され、ゲート電極34はワード線WLに接続されている。より具体的には、ビット線BL方向に並ぶ各メモリセルMCのドレイン領域28は、1本のビット線BLに共通に接続され、ワード線WL方向に並ぶ各メモリセルMCのゲート電極34は、1本のワード線WLに共通に接続されている。

## 【0019】

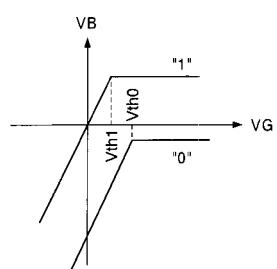

これら図2及び図3に示したメモリセルMCは、フローティングボディ30を、第1の電位に設定した第1データ状態と、第2の電位に設定した第2のデータ状態とをダイナミックに記憶する。具体的には、第1データ状態は、ワード線WL及び選択ビット線BLに高レベル電圧を与え、選択されたメモリセルMCを5極管動作させ、そのドレイン接合近傍でインパクトイオン化を起こして生成した多数キャリア(nチャネルの場合、ホール)をフローティングボディ30に保持することにより書き込まれる。これが例えば、データ“1”である。第2データ状態は、ワード線WLに高レベル電圧を与えて容量結合によりフローティングボディ30の電位を高くし、ビット線BLを低レベル電圧にして、選択されたメモリセルMCのフローティングボディ30とドレイン領域28との接合に順バイアス電流を流してフローティングボディ30の多数キャリアをドレイン領域28に放出することにより書き込まれる。これが例えばデータ“0”である。

20

## 【0020】

メモリセルMCがデータ“1”を保持しているか、それともデータ“0”を保持しているかは、MISFETのゲートしきい値の差として表れる。すなわち、データ“1”を保持しているメモリセルMCのフローティングボディ電位VBとゲート電圧VGとの関係、及び、データ“0”を保持しているメモリセルMCのフローティングボディ電位VBとゲート電圧VGとの関係は、図4に示すグラフのようになる。

30

## 【0021】

この図4に示すように、フローティングボディ電位VBによる基板バイアスの結果として、データ“1”を保持しているメモリセルMCのしきい値電圧Vth1は、データ“0”を保持しているメモリセルMCのしきい値電圧Vth0より低くなる。したがって、メモリセルMCからのデータ読み出しは、しきい値電圧の差によるセル電流の差を検出することにより、判定することができる。

40

## 【0022】

図1に示すように、本実施形態においては、このメモリセルMCにより8KビットのメモリセルアレイMCAが構成されている。具体的には、カラム方向に沿って互いに並列に256本のワード線WLが設けられており、このカラム方向と交差する方向であるロー方向に沿って、互いに並列に32本のビット線BLが設けられている。本実施形態においては、特に、ワード線WLとビット線BLとは直交している。

## 【0023】

また、本実施形態においては、ビット線方向に沿って、4本の基準ビット線RBL0、RBL1が並列に設けられている。特に本実施形態においては、このメモリセルアレイMCA

50

A の中央部分に、基準ビット線 RBL0、RBL1 が設けられている。このため、基準ビット線 RBL0、RBL1 の図中上側には、16 本のビット線 BL が設けられており、基準ビット線 RBL0、RBL1 の図中下側には、同じく 16 本のビット線 BL が設けられていることになる。つまり、基準ビット線 RBL0、RBL1 を基準として、ワード線方向の一方側に設けられているビット線 BL の本数と、ワード線方向の他方側に設けられているビット線 BL の本数とは、等しいことになる。また、本実施形態においては、図 13 に示した従来のメモリセルアレイ MCA のように、基準ビット線 RBL0、RBL1 が中央で 2 分割されることなく、通常のビット線 BL と同様に、メモリセルアレイ MCA 全体にわたって、1 本で形成されている。

## 【0024】

10

2 本の基準ビット線 RBL0 においては、各ワード線 WL とその交点位置に、“0”データが保持されるべき基準セル RC0 が設けられている。つまり、1 本の基準ビット線 RBL0 には、256 個の基準セル RC0 が接続されている。また、2 本の基準ビット線 RBL1 においては、各ワード線 WL とその交点位置に、“1”データが保持されるべき基準セル RC1 が設けられている。つまり、1 本の基準ビット線 RBL1 には、256 個の基準セル RC1 が接続されている。これら基準セル RC0、RC1 の構造は、メモリセル MC の構造と同様である。また、ゲート電極、ソース、及び、ドレインの接続関係も、図 3 に示したメモリセル MC と同様である。

## 【0025】

20

さらに、メモリセルアレイ MCA におけるビット線方向の両端位置には、ワード線 WL に沿って、イコライズ線 EQL がそれぞれ 1 本ずつ設けられている。このイコライズ線 EQL とビット線 BL との交点位置、及び、イコライズ線 EQL と基準ビット線 RBL0、RBL1 との交点位置には、メモリセル MC と同様の構造及び同様の接続関係の MISFET が設けられており、そのゲートがイコライズ線 EQL に接続されている。メモリセル MC からデータを読み出す前には、このイコライズ線 EQL を介して、ビット線 BL がグラウンド(0V)に設定される。

## 【0026】

このように構成されたメモリセルアレイ MCA におけるビット線方向の両側には、センスアンプ回路 40 が配置されている。すなわち、本実施形態に係るメモリセルアレイ MCA は、ダブルエンド型センスアンプ方式を採用している。このため、ビット線選択回路 42 も、メモリセルアレイ MCA におけるビット線方向の両側に配置されている。

30

## 【0027】

これら両側のビット線選択回路 42 には、ビット線 BL が 1 本おきに交互に接続されおり、また、基準ビット線 RBL0、RBL1 も 1 本おきに交互に接続されている。このビット線選択回路 42 により、基準ビット線 RBL0、RBL1 より図中上側にある 8 本のビット線 BL のうちの 1 本が選択され、図中上側のセンスアンプ回路 40 に接続され、基準ビット線 RBL0、RBL1 より図中下側にある 8 本のビット線 BL のうちの 1 本が選択され、図中下側のセンスアンプ回路 40 に接続される。

## 【0028】

40

片側 2 つのセンスアンプ回路 40 に対して、1 つの基準電圧発生回路 44 が設けられている。この基準電圧発生回路 44 には、メモリセル MC のデータを読み出す際には、1 本の基準ビット線 RBL0 と 1 本の基準ビット線 RBL1 との双方が接続される。これら基準電圧発生回路 44 とセンスアンプ回路 40 とにより、本実施形態に係るデータセンス回路が構成される。

## 【0029】

このように構成された半導体記憶装置において、1 つのメモリセル MC に対するデータ読み出し動作は、概略的には、次のように行われる。まず、1 本のワード線 WL が選択されて所定のハイレベル電圧 VDD に設定される。また、これと同時に、ビット線選択回路 42 により、1 本のビット線 BL が選択されて、センスアンプ回路 40 に接続される。また、ビット線選択回路 42 により、1 本の基準ビット線 RBL0 と 1 本の基準ビット線 RBL1 が接続される。

50

L 1 とが、基準電圧発生回路 4 4 に接続される。

**【 0 0 3 0 】**

次に、選択されたビット線 B L を経由して、読み出そうとしているメモリセル M C に、セル電流 I c e l l を流す。そして、このメモリセル M C を介して流れる I c e l l を、センスアンプ回路 4 0 が取得する。ここで、セル電流 I c e l l は、メモリセル M C がデータ“0”を保持しているのか、それともデータ“1”を保持しているのかで、流れる電流量が異なることとなる。

**【 0 0 3 1 】**

また、同様に、基準ビット線 R B L 0 と基準ビット線 R B L 1 にも、基準電圧発生回路 4 4 から、セル電流を流す。基準セル R C 0 、 R C 1 としては、読み出そうとしているメモリセル M C と同じワード線に接続されている基準セル R C 0 と基準セル R C 1 とが活性化されているので、この基準セル R C 0 には電流 I 0 が流れ、基準セル R C 1 には電流 I 1 が流れる。そして、これらを合わせた基準電流 I 0 + I 1 を、基準電圧発生回路 4 4 が取得する。

**【 0 0 3 2 】**

基準電圧発生回路 4 4 では、この基準電流 I 0 + I 1 に基づいて基準電圧 V R E F を生成し、センスアンプ回路 4 0 に供給する。センスアンプ回路 4 0 では、セル電流 I c e l l 1 と基準電圧 V R E F に基づいてデータ電圧 V S N を生成し、この読み出し電圧 V S N と基準電圧 V R E F とを比較して、メモリセル M C の保持しているデータを検出する。

**【 0 0 3 3 】**

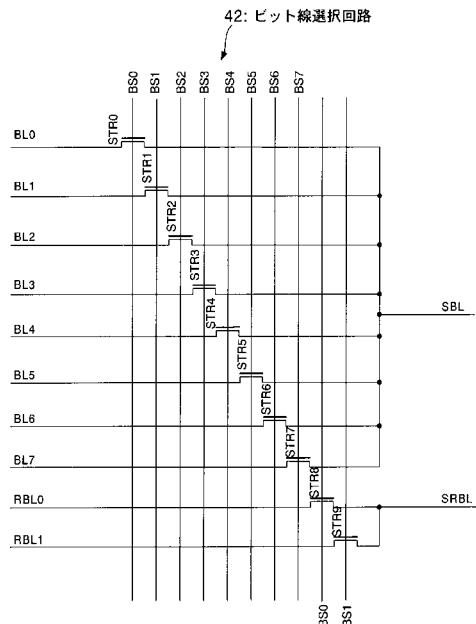

次に、センスアンプ回路 4 0 とビット線選択回路 4 2 と基準電圧発生回路 4 4 の回路構成を詳細に説明する。図 5 は、本実施形態に係るセンスアンプ回路 4 0 の回路構成を示す図であり、図 6 は、本実施形態に係るビット線選択回路 4 2 の回路構成を示す図であり、図 7 は、本実施形態に係る基準電圧発生回路 4 4 の回路構成を示す図である。

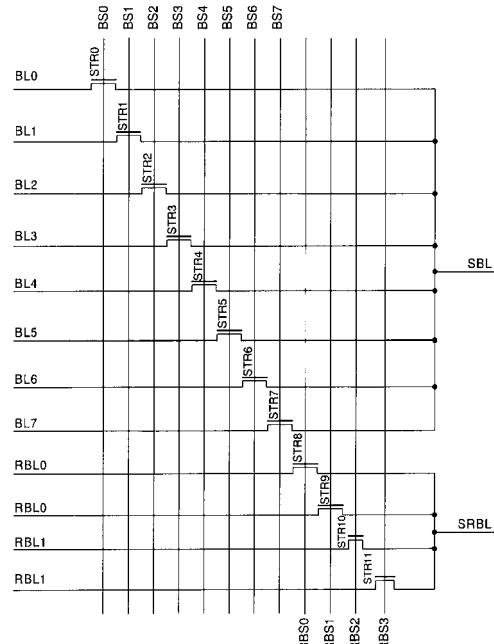

**【 0 0 3 4 】**

図 6 に示すように、ビット線選択回路 4 2 には、8 本のビット線 B L 0 ~ B L 7 と、2 本の基準ビット線 R B L 0 、 R B L 1 とが接続されている。なお、図 1 に対応させた場合には、2 本の基準ビット線 R B L 0 、 R B L 1 の図中下側に、さらに8 本のビット線 B L 8 ~ B L 15 が接続され、図中上側と同様の構成をとることになるが、この図 6 では省略している。

**【 0 0 3 5 】**

8 本のビット線 B L 0 ~ B L 7 は、それぞれ、選択トランジスタ S T L 0 ~ S T L 7 の入力端子側に接続されており、これら選択トランジスタ S T L 0 ~ S T L 7 の出力端子側は、選択ビット線 S B L に共通接続されている。また、選択トランジスタ S T L 0 ~ S T L 7 の制御端子には、それぞれ、ビット線選択信号線 B S 0 ~ B S 7 が接続されている。1 本のビット線を選択する際には、これらビット線選択信号線 B S 0 ~ B S 7 のうちのいずれか 1 つが立ち上がってハイレベルになり、1 本のビット線 B L を選択ビット線 S B L に接続する。

**【 0 0 3 6 】**

基準ビット線 R B L 0 、 R B L 1 は、それぞれ、選択トランジスタ S T L 8 、 S T L 9 の入力端子側に接続されており、これら選択トランジスタ S T L 8 、 S T L 9 の出力端子側は、選択基準ビット線 S R B L に共通接続されている。また、選択トランジスタ S T L 8 、 S T L 9 の制御端子には、それぞれ、基準ビット線選択信号線 R B S 0 、 R B S 1 が接続されている。メモリセル M C のデータを読み出す際には、基準ビット線選択信号線 R B S 0 、 R B S 1 の双方が立ち上がってハイレベルになり、選択トランジスタ S T R 8 、 S T R 9 の双方がオンになる。これにより、基準ビット線 R B L 0 と基準ビット線 R B L 1 とがショートする。但し、基準セル R C 0 、 R C 1 をリフレッシュする場合等、基準セル R C 0 、 R C 1 にデータを書き込む場合には、基準ビット線選択信号線 R B S 0 、 R B S 1 の一方が立ち上がってハイレベルになる。すなわち、基準セル R C 0 に“0”データを書き込む場合には、選択トランジスタ S T R 8 がオンになり、基準セル R C 1 に“1”デ

10

20

30

40

50

ータを書き込む場合には、選択トランジスタ S T R 9 がオンになる。

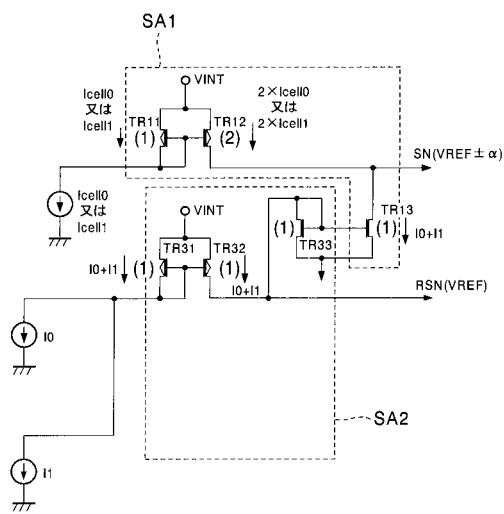

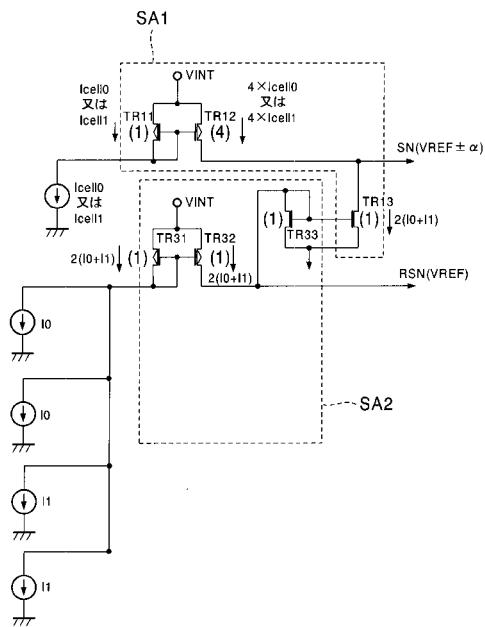

#### 【 0 0 3 7 】

図5に示すように、センスアンプ回路40は、第1センスアンプS A 1を備えている。この第1センスアンプS A 1は、p型のM I S F E T T R 1 0 ~ T R 1 2と、n型のM I S F E T T R 1 3を備えて構成されている。M I S F E T T R 1 0 の入力端子は、ハイレベル電圧端子V I N T に接続されており、出力端子はM I S F E T T R 1 1 及びM I S F E T T R 1 2 の入力端子に接続されている。これらM I S F E T T R 1 1 及びT R 1 2 の制御端子は、互いに接続されており、カレントミラー回路を構成している。このカレントミラー回路におけるM I S F E T T R 1 1 とM I S F E T T R 1 2 のミラービーは、1 : 2である。すなわち、M I S F E T T R 1 1 を流れる電流の2倍の電流が、M I S F E T T R 1 2 を流れることとなる。さらに、M I S F E T T R 1 1 の制御端子と出力端子は、ビット線電位制限回路B P L に設けられたn型のM I S F E T を介して、選択ビット線S B L に接続されている。10

#### 【 0 0 3 8 】

M I S F E T T R 1 2 の出力端子は、M I S F E T T R 1 3 の入力端子に接続されており、M I S F E T T R 1 3 の出力端子は、グランドに接続されている。これらM I S F E T T R 1 2 とM I S F E T T R 1 3との間のノードが、センスノードS N となる。。10

#### 【 0 0 3 9 】

メモリセルM C からデータを読み出すための読み出し動作の際には、信号S A O N がローレベルになり、M I S F E T T R 1 0 をオンにする。このため、ハイレベル電圧端子V I N T から電流がM I S F E T T R 1 1 とM I S F E T T R 2 0 を介して、選択ビット線S B L に流れる。これがセル電流I c e l l 1 である。選択ビット線S B L に流れるセル電流I c e l l 1 の量は、選択されたメモリセルM C が保持しているデータにより異なることとなる。ここでは、選択したメモリセルM C が“0”データを保持している場合に流れるセル電流を、I c e l l 0 とし、選択したメモリセルM C が“1”データを保持している場合に流れるセル電流を、I c e l l 1 とする。20

#### 【 0 0 4 0 】

ビット線電位制限回路B P L は、ビット線B L の電位の上昇を制限するための回路である。すなわち、ビット線電位制限回路B P L は、上述したM I S F E T T R 2 0 と、オペアンプO P 1 とにより、負帰還制御回路を構成している。オペアンプO P 1 の非反転入力端子には、電圧V B L R が入力されている。本実施形態においては、この電圧V B L R は200mVである。また、オペアンプO P 1 の反転入力端子は、選択ビット線S B L に接続されている。オペアンプO P 1 の出力端子は、M I S F E T T R 2 0 の制御端子に接続されている。このため、選択ビット線S B L の電位が電圧V B L R を越えると、つまり、ビット線B L の電位が電圧V B L R を超えると、オペアンプO P 1 の出力はローレベルとなり、n型のM I S F E T T R 2 0 をオフにする。このため、ビット線B L が、電圧V B L R 以上の電圧になってしまふのを、回避することができる。30

#### 【 0 0 4 1 】

このように、ビット線B L の電位上昇を回避するのは、次のような理由によるものである。メモリセルM C は、データ書き込みの際には、ワード線W L に高レベル電圧（例えば電源電圧V D D ）が与えられ、ビット線B L にも高レベル電圧（例えば電源電圧V D D ）が与えられて、5極管動作を行う。データ読み出しの際に、ワード線W L に同様に電源電圧V D D を与えるものとした場合、メモリセルM C を十分なセル電流が流れずに、ビット線B L の電位が電源電圧V D D まで上昇してしまうことも考えられる。もし、ビット線B L が電源電圧V D D まで上昇してしまうと、書き込みモードと同じ条件になってしまう。そこで、本実施形態においては、電圧V B L R を電源電圧V D D より低い値に設定する。例えば、電源電圧V D D を1~1.5Vとして、電圧V B L R = 200mVに設定する。このように設定すれば、データ読み出しの際に、メモリセルM C は5極管動作するおそれがなくなり、5極管動作の条件を満たさないようにすることができる。40

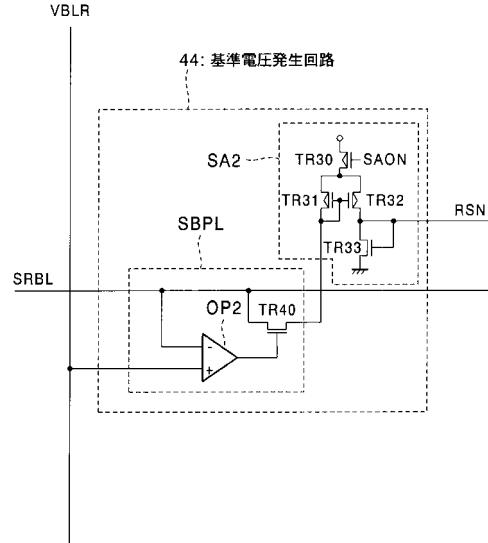

## 【0042】

図7に示すように、基準電圧発生回路44にも、選択基準ビット線S R B Lの電位を上昇するのを制限する、選択基準ビット線電位制限回路S B P Lが設けられている。この選択基準ビット線電位制限回路S B P Lを設けている理由も、上記と同様である。この選択基準ビット線電位制限回路S B P Lは、オペアンプO P 2とn型のM I S F E T T R 4 0とを備えているが、その接続関係は、上述したビット線電位制限回路B P Lと同様である。

## 【0043】

また、基準電圧発生回路44は、第2センスアンプS A 2を備えている。この第2センスアンプS A 2は、p型のM I S F E T T R 3 0～T R 3 2と、n型のM I S F E T T R 3 3とを備えて構成されているが、その接続関係は、上述した第1センスアンプS A 1と同様である。但し、M I S F E T T R 3 1とM I S F E T T R 3 2とにより構成されるカレントミラー回路のミラー比は、1：1である。すなわち、M I S F E T T R 3 1を流れる電流と同じ電流の量が、M I S F E T T R 3 2を流れる。また、M I S F E T T R 3 2とM I S F E T T R 3 3との間が、基準ノードR S Nを構成しており、M I S F E T T R 3 3の制御端子が、この基準ノードR S Nに接続されている。10

## 【0044】

さらに、この図7と図5から分かるように、基準ノードR S Nは、第1センスアンプS A 1のM I S F E T T R 1 3の制御端子に接続されている。このため、M I S F E T T R 3 3と、M I S F E T T R 1 3とにより、カレントミラー回路が構成されている。このカレントミラー回路のミラー比は、1：1である。20

## 【0045】

図7に示すように、読み出し動作の際には、信号S A O Nがローレベルになり、M I S F E T T R 3 0をオンにする。このため、ハイレベル電圧端子V I N Tから電流が、M I S F E T T R 3 1とM I S F E T T R 4 0を介して、選択基準ビット線S R B Lに流れる。これが基準電流である。この基準電流は、データ“0”を保持している基準セルR C 0を流れる電流I 0の量と、データ“1”を保持している基準セルR C 1を流れる電流I 1の量とを合わせた電流の量である。

## 【0046】

図8は、データ読み出し動作の際ににおける第1センスアンプS A 1と第2センスアンプS A 2の等価回路を示す図である。M I S F E Tの脇に書き加えられたカッコ書きの数値は、カレントミラー回路のミラー比を表している。30

## 【0047】

この図8及び図5から分かるように、読み出したメモリセルM Cを流れるセル電流I c e 1 1(I c e 1 1 0又はI c e 1 1 1)は、M I S F E T T R 1 1とM I S F E T T R 1 2とから構成されたカレントミラー回路で2倍にされ、M I S F E T T R 1 2を2×I c e 1 1の電流が流れようとする。

## 【0048】

一方、基準電流I 0+I 1は、M I S F E T T R 3 1とM I S F E T T R 3 2とから構成されたカレントミラー回路で1倍にされる。このときの基準ノードR S Nの電圧を基準電圧V R E Fとする。さらに、この基準電流I 0+I 1は、M I S F E T T R 3 3とM I S F E T T R 1 3とから構成されたカレントミラー回路で1倍にされ、M I S F E T T R 1 3を基準電流I 0+I 1が流れようとする。このM I S F E T T R 1 3を流れようとする基準電流I 0+I 1と、M I S F E T T R 1 2を流れようとする2倍のセル電流2×I c e 1 1の衝突により、センスノードS Nの電圧(データ電圧)が定まる。40

## 【0049】

具体的には、2×I c e 1 1の方が基準電流I 0+I 1より小さい場合、M I S F E T T R 1 3をオンにして電流I 0+I 1を流そうとする力の方が、M I S F E T T R 1 2をオンにして電流2×I c e 1 1を流そうとする力よりも、強いこととなる。このため、センスノードS Nのデータ電圧は、基準電圧V R E Fよりも低くなり、V R E F -とな50

る。

【0050】

一方、 $2 \times I_{c e l l}$ の方が基準電流  $I_0 + I_1$  より大きい場合、MISFET TR12をオンにして電流  $2 \times I_{c e l l}$  を流そうとする力の方が、MISFET TR13をオンにして電流  $I_0 + I_1$  を流そうとする力よりも、強いこととなる。このため、センスノードSNのデータ電圧は、基準電圧VREFよりも高くなり、VREF+となる。

【0051】

このことから分かるように、センスノードSNの電圧と基準ノードRSNの電圧との差は、データに応じて極性が異なる。この電圧の差を、図5に示すように、第3センスアンプSA3により検出する。本実施形態においては、第3センスアンプSA3はオペアンプにより構成されており、センスノードSNが基準ノードRSNよりも高電位か低電位かにより、ローレベル又はハイレベルのセンス出力OUTを出力する。このセンス出力OUTは、ラッチ回路LTによりラッチされる。10

【0052】

ラッチ回路LTによりラッチされたセンス出力OUTは、これがハイレベルであるか、それともローレベルであるかにより、n型のMISFET TR50又はn型のMISFET TR51のいずれか一方を、オンにする。n型のMISFET TR52とn型のMISFET TR53の制御端子には、読み出しカラム選択信号RCSLが入力されており、選択されたメモリセルMCを有するセンスアンプ回路40では、この読み出しカラム選択信号RCSLがハイレベルになっており、これらMISFET TR52、TR53はオンになっている。また、読み出し動作をする際には、データ読み出し線Q、BQはともにハイレベルにプリチャージされている。このため、センス出力OUTがハイレベルであるか、又は、ローレベルであるかにより、データ読み出し線Q又はデータ読み出し線BQの一方がローレベルに変化する。これにより、読み出したデータを、外部に出力することが可能になる。20

【0053】

リフレッシュ動作の際には、ライトバック信号WBがハイレベルになり、n型のMISFET TR60がオンになる。これにより、ラッチ回路LTにラッチされているセンス出力OUTが、選択基準ビット線SBLに出力され、再び選択されているメモリセルMCに書き込まれる。30

【0054】

メモリセルMCへのデータの書き込み動作の際には、書き込みカラム選択信号WCSLがハイレベルになり、n型のMISFET TR70がオンになる。そして、データ書き込み線Dが、書き込むデータに応じて、ハイレベル又はローレベルに設定され、これが選択基準ビット線SBLに出力される。例えば、本実施形態においては、データ“1”を書き込む場合には、データ書き込み線Dがハイレベルになり、ハイレベルになったワード線WLにより選択されたメモリセルMCのフローティングボディに、多数キャリアであるホールを蓄積する。一方、データ“0”を書き込む際には、データ書き込み線Dがローレベルになり、ローレベルになったワード線WLにより選択されたメモリセルMCのフローティングから、蓄積されているホールを引き抜く。これにより、選択されたメモリセルMCにデータを書き込むことができる。40

【0055】

以上のように、本実施形態に係る半導体記憶装置によれば、図1に示すように、読み出すメモリセルMCと、この読み出し動作の際に使用する基準セルRC0、RC1との間の距離を、所定範囲内に制限することができる。すなわち、図1の例では、読み出すメモリセルMCと、使用する基準セルRC0又はRC1との間の距離を、最大でもメモリセルMCの18個分に制限することができる。このため、製造プロセスに起因するセル特性のバラツキと、使用温度条件によるセル特性のバラツキを、同一傾向にあるようにすることができます。この結果、これらのバラツキを同相雑音として、精度よく補償することができるようになる。50

**【 0 0 5 6 】**

また、1つのメモリセルアレイMCAで見た場合、図13のメモリセルアレイMCAでは、読み出し動作の際に1本の通常のワード線WLに加えて、4本の基準ワード線RWL0、RWL1を活性化する必要があったが、図1のメモリセルアレイMCAでは、1本の通常ワード線だけ活性化すれば足りる。このため、読み出し動作の際の消費電力の低減を図ることができる。

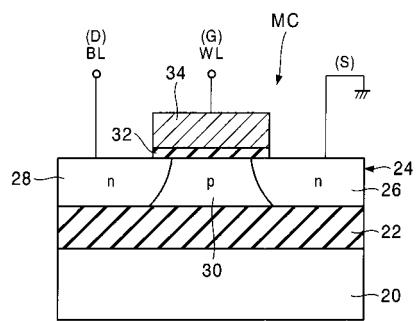

**【 0 0 5 7 】****[ 第2実施形態 ]**

上述した第1実施形態においては、1つの基準電圧発生回路44を2つのセンスアンプ回路40で共通に使用することとしたが、必ずしも共通に使用する必要はない。本発明の第2実施形態においては、1つの基準電圧発生回路44を1つのセンスアンプ回路40で使用するようにしている。

**【 0 0 5 8 】**

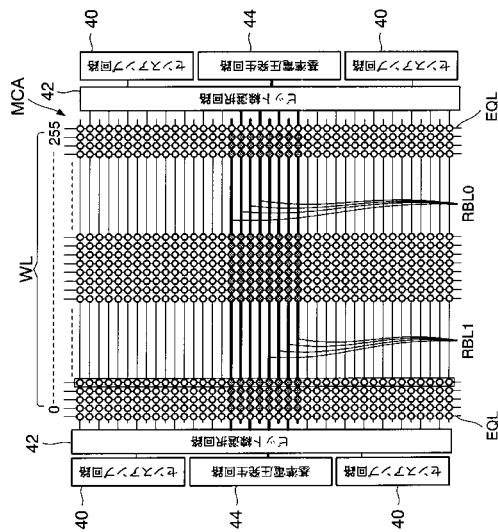

図9は、第2実施形態に係る半導体記憶装置の部分的な配置図を示している。この図9に示すように、第2実施形態においては、1つのセンスアンプ回路40に対して、1つの基準電圧発生回路44を設けている。この図9の例では、4KビットのメモリセルアレイMCAを構成している。これ以外の点は、上述した第1実施形態と同様である。

**【 0 0 5 9 】**

このことから分かるように、1つの基準電圧発生回路44は、X個(Xは、自然数)のセンスアンプ回路40で使用することが可能である。

**【 0 0 6 0 】****[ 第3実施形態 ]**

上述した実施形態においては、1本のワード線WLに、4個の基準セルRC0、RC1を設けた。すなわち、1つの基準電圧発生回路44は、1個の“0”データを保持した基準セルRC0と1個の“1”データを保持した基準セルRC1を用いて、基準電流I0+I1を取得するようにした。しかし、1つの基準電圧発生回路44に対して設ける基準セルの個数は、2個に限られるものではなく、2N個であればよい(Nは、自然数である)。この場合、基準ビット線RBL0、RBL1は、1つの基準電圧発生回路44に対して、合計で2N本設ける必要がある。

**【 0 0 6 1 】**

そこで、本発明の第3実施形態は、1つの基準電圧発生回路44に対して4個の基準セルRC0、RC1を設けるとともに、2個の基準セルRC0に“0”データを保持させ、2個の基準セルRC1に“1”データを保持させるようにしたものである。

**【 0 0 6 2 】**

図10は、そのような半導体記憶装置の部分的な配置図である。この図10に示すように、本実施形態に係るメモリセルアレイMCAは、メモリセルアレイMCAの中央部分に、ビット線BLに沿って、8本の基準ビット線RBL0、RBL1が設けられている。本実施形態においては、ワード線方向上側に、4本の基準ビット線RBL0が配置されており、ワード線方向下側に、4本の基準ビット線RBL1が配置されている。また、基準ビット線RBL0、RBL1は、交互に、図中左側のビット線選択回路42と図中左側のビット線選択回路42に接続されている。

**【 0 0 6 3 】**

ワード線WLと基準ビット線RBL0との交点位置には、それぞれ、“0”データが保持される基準セルRC0が設けられている。また、ワード線WLと基準ビット線RBL1との交点位置には、それぞれ、“1”データが保持される基準セルRC1が設けられている。

**【 0 0 6 4 】**

上述した第1実施形態の図3と同様に、本実施形態においても、基準セルRC0、RC1及びメモリセルMCにおけるゲート電極は、ワード線WLに接続されており、ソースは共通ソース線を介してグランドに接続されており、ドレインはビット線BLに接続されてい

10

20

30

40

50

る。

【0065】

図11は、本実施形態に係るビット線選択回路42の回路図を示している。この図11に示すように、ビット線選択回路42には、2本の基準ビット線RBL0と2本の基準ビット線RBL1とが接続されている。そして、これら合計4本の基準ビット線RBL0、RBL1には、選択トランジスタSTR8～STR11が設けられている。この選択トランジスタSTR8～STR11の制御端子には、それぞれ、基準ビット線選択信号線RBS0～RBS3が接続されている。

【0066】

メモリセルMCのデータを読み出す際には、基準ビット線選択信号線RBS0～RBS3のすべてが立ち上がってハイレベルになり、選択トランジスタSTR8～STR11のすべてがオンになる。これにより、2本の基準ビット線RBL0と2本の基準ビット線RBL1とがショートして、選択基準ビット線SRBLに接続される。但し、基準セルRC0、RC1をリフレッシュする場合等、基準セルRC0、RC1にデータを書き込む場合には、基準ビット線選択信号線RBS0～RBS3のいずれか2つが立ち上がってハイレベルになり、選択トランジスタSTR8～STR11のいずれか2つをオンにし、それ以外の選択トランジスタをオフにする。

【0067】

本実施形態に係る半導体記憶装置は、これらの点以外は、上述した第1実施形態の半導体記憶装置と同様の構成である。

【0068】

図12は、本実施形態における第1センスアンプSA1と第2センスアンプSA2の等価回路を示す図であり、上述した図8に対応する図である。この図12においては、図8と異なり、MISFET TR31を入力端子から出力端子へ流れる基準電流が $2 \times (I_0 + I_1)$ となる。これは、MISFET TR31の出力端子には、ワード線WLにより選択された2個の基準セルRC0と2個の基準セルRC1とが接続されているためである。

【0069】

これに対応して、MISFET TR11とMISFET TR12とで構成されるカレントミラー回路のミラー比が、1:4になっている。したがって、MISFET TR12の入力端子から出力端子へは、 $4 \times I_{ce110}$ 又は $4 \times I_{ce111}$ の電流が流れようとする。MISFET TR12を流れる電流が $4 \times I_{ce110}$ であるか、又は、 $4 \times I_{ce111}$ であるかに応じて、センスノードSNの電圧は、基準電圧VREF-又は基準電圧VREF+に変化する。

【0070】

以上に述べたことから、基準セルの個数を2N個とし、MISFET TR31とMISFET TR32で構成されるカレントミラー回路により基準電流をP倍し、MISFET TR11とMISFET TR12で構成されるカレントミラー回路により読み出したセル電流をQ倍するとした場合、 $P/Q = 1/(2N)$ の関係を満たすように設定すればよいことが分かる。ここで、P及びQは、それぞれ、任意の正の数である。

【0071】

したがって、例えば、第1実施形態における図8の例において、基準電流 $I_0 + I_1$ を、MISFET TR31とMISFET TR32とで構成されるカレントミラー回路で $1/2$ にし、読み出したセル電流を、MISFET TR11とMISFET TR12とで構成されるカレントミラー回路で1倍して、比較するようにしてもよい。

【0072】

なお、本発明は上記実施形態に限定されず種々に変形可能である。例えば、本発明は、メモリセルとしてFBCを用いて形成された半導体記憶装置に限られるものではなく、基準セルを流れる基準電流と読み出そうとしているメモリセルを流れるセル電流とに基づいて、メモリセルが記憶するデータを読み出す電流読み出し型の半導体記憶装置であれば、適

10

20

30

40

50

用することができる。

【0073】

【発明の効果】

以上説明したように、本発明によれば、データを読み出そうとするメモリセルと、このデータ読み出しの際に基準電流を得るために使用する基準セルとの間の距離を、所定範囲内に制限することができるので、セル特性の変動を精度よく補償することができる。

【図面の簡単な説明】

【図1】本発明の第1実施形態に係る半導体記憶装置におけるメモリセルアレイ周辺の部分的な配置図である。

【図2】本実施形態に係るメモリセル及び基準セルの構造を説明する模式的な断面図である。 10

【図3】本実施形態に係るメモリセル及び基準セルにおける、ゲート電極、ソース、及びドレインの接続関係を説明する回路図である。

【図4】メモリセルのしきい値の変化を、ゲート電圧とフローティングボディ電位との関係を用いて説明するためのグラフである。

【図5】本実施形態に係るセンスアンプ回路の構成を示す回路図である。

【図6】本実施形態に係るビット線選択回路の構成を示す回路図である。

【図7】本実施形態に係る基準電圧発生回路の構成を示す回路図である。

【図8】本実施形態に係るセンスアンプ回路の第1センスアンプと基準電圧発生回路の第2センスアンプとの等価回路を示す図である。 20

【図9】本発明の第2実施形態に係る半導体記憶装置におけるメモリセルアレイ周辺の配置図である。

【図10】本発明の第3実施形態に係る半導体記憶装置におけるメモリセルアレイ周辺の配置図である。

【図11】本実施形態に係るビット線選択回路の構成を示す回路図である。

【図12】本実施形態に係るセンスアンプ回路の第1センスアンプと基準電圧発生回路の第2センスアンプとの等価回路を示す図である。

【図13】従来の半導体記憶装置におけるメモリセルアレイ周辺の配置図である。

【符号の説明】

W L ワード線

B L ビット線

M C メモリセル

M C A メモリセルアレイ

R C 0、R C 1 基準セル

E Q L イコライズ線

4 0 センスアンプ回路

4 2 ビット線選択回路

4 4 基準電圧発生回路

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

**【手続補正書】**

【提出日】平成15年3月31日(2003.3.31)

**【手続補正1】**

【補正対象書類名】明細書

【補正対象項目名】特許請求の範囲

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

第1方向に沿って互いに並列に形成された、複数のワード線と、

前記第1方向と交差する方向である第2方向に沿って互いに並列に形成された、複数のビット線と、

前記ワード線と前記ビット線の交点位置に設けられた複数のメモリセルであって、前記ビット線に接続されたドレイン領域と、ソース線に接続されたソース領域と、前記ワード線に接続されたゲート電極と、前記ドレイン領域と前記ソース領域との間に位置する電気的にフローティング状態であるフローティングボディとを有するMISFETにより構成されており、前記MISFETのしきい値を変化させてデータを記憶する、メモリセルと、前記第2方向に沿って形成された、複数の基準ビット線と、

前記ワード線と前記複数の基準ビット線との交点位置に設けられた複数の基準セルであって、前記メモリセルからデータを読み出す際に、データを読み出すメモリセルの接続されたワード線により $2^N$ (Nは自然数)個が活性化され、データを読み出す際の基準となる基準電流を生成する、基準セルと、

前記基準電流と、読み出すメモリセルを流れるセル電流に基づいて、前記メモリセルのデータを読み出す、データセンス回路と、

を備えることを特徴とする半導体記憶装置。

**【請求項2】**

前記基準セルの構造は、前記メモリセルの構造と同等である、ことを特徴とする請求項1に記載の半導体記憶装置。

**【請求項3】**

1つのセンシングシステムにおいて、前記基準ビット線を基準として、前記第1方向の一方側に設けられているビット線の本数と、前記第1方向の他方側に設けられているビット線の本数とは、等しい、ことを特徴とする請求項1又は請求項2に記載の半導体記憶装置。

**【請求項4】**

前記データセンス回路は、

活性化された $2^N$ 個の基準セルにより生成された前記基準電流に基づいて、基準電圧を発生する、基準電圧発生回路と、

前記基準電圧と前記セル電流に基づいてデータ電圧を生成し、このデータ電圧と前記基準電圧を比較することにより、メモリセルのデータを読み出す、センスアンプ回路と、を備えることを特徴とする請求項1乃至請求項3のいずれかに記載の半導体記憶装置。

**【請求項5】**

1つの基準電圧発生回路に対して $2^N$ 本の基準ビット線が設けられている、ことを特徴とする請求項4に記載の半導体記憶装置。

**【請求項6】**

1つの基準電圧発生回路に対して1つのセンスアンプ回路が設けられている、ことを特徴とする請求項4又は請求項5に記載の半導体記憶装置。

**【請求項7】**

1つの基準電圧発生回路に対して複数のセンスアンプ回路が設けられている、ことを特徴とする請求項4又は請求項5に記載の半導体記憶装置。

**【請求項8】**

1本のワード線により活性化される $2N$ 個の基準セルのうち、 $N$ 個の基準セルは“0”データが格納されるためのものであり、残りの $N$ 個の基準セルは“1”データが格納されるためのものである、ことを特徴とする請求項1乃至請求項7のいずれかに記載の半導体記憶装置。

【請求項9】

前記データセンス回路は、 $2N$ 個の基準セルを流れる電流の合計である基準電流をP倍（Pは任意の正の数）し、読み出すメモリセルを流れるセル電流をQ倍（Qは任意の正の数）し、これらP倍した基準電流とQ倍したセル電流とを比較することにより、メモリセルの記憶しているデータを読み出す、ことを特徴とする請求項8に記載の半導体記憶装置。

【請求項10】

$P/Q$ は $1/2N$ あるように設計されている、ことを特徴とする請求項9に記載の半導体記憶装置。

【請求項11】

前記MISFETのしきい値は、前記フローティングボディに多数キャリアを蓄積し又は前記フローティングボディから多数キャリアを放出することにより変化することを特徴とする請求項1乃至請求項10のいずれかに記載の半導体記憶装置。

【請求項12】

第1方向に沿って互いに並列に形成された、複数のワード線と、

前記第1方向と交差する方向である第2方向に沿って互いに並列に形成された、複数のビット線と、

前記ワード線と前記ビット線の交点位置に設けられた複数のメモリセルと、

前記第2方向に沿って形成された、複数の基準ビット線と、

前記ワード線と前記複数の基準ビット線との交点位置に設けられた複数の基準セルであって、前記メモリセルからデータを読み出す際に、データを読み出すメモリセルの接続されたワード線により $2N$ （Nは自然数）個が活性化され、データを読み出す際の基準となる基準電流を生成する、基準セルと、

前記基準電流と、読み出すメモリセルを流れるセル電流とに基づいて、前記メモリセルのデータを読み出す、データセンス回路と、

を備えることを特徴とする半導体記憶装置。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0012

【補正方法】変更

【補正の内容】

【0012】

【課題を解決するための手段】

上記課題を解決するため、本発明に係る半導体記憶装置は、第1方向に沿って互いに並列に形成された、複数のワード線と、前記第1方向と交差する方向である第2方向に沿って互いに並列に形成された、複数のビット線と、前記ワード線と前記ビット線の交点位置に設けられた複数のメモリセルであって、前記ビット線に接続されたドレイン領域と、ソース線に接続されたソース領域と、前記ワード線に接続されたゲート電極と、前記ドレイン領域と前記ソース領域との間に位置する電気的にフローティング状態であるフローティングボディとを有するMISFETにより構成されており、前記MISFETのしきい値を変化させてデータを記憶する、メモリセルと、前記第2方向に沿って形成された、複数の基準ビット線と、前記ワード線と前記複数の基準ビット線との交点位置に設けられた複数の基準セルであって、前記メモリセルからデータを読み出す際に、データを読み出すメモリセルの接続されたワード線により $2N$ （Nは自然数）個が活性化され、データを読み出す際の基準となる基準電流を生成する、基準セルと、前記基準電流と、読み出すメモリセルを流れるセル電流とに基づいて、前記メモリセルのデータを読み出す、データセンス回路と、を備えることを特徴とする。

---

フロントページの続き

(72)発明者 大澤 隆

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

Fターム(参考) 5B025 AA01 AC01 AD04 AD07 AE00

5F083 AD69 GA12 LA03 LA04 LA12 LA16 ZA28