(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 698 35 238 T2 2007.05.31

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 074 049 B1

(21) Deutsches Aktenzeichen: 698 35 238.6

(86) PCT-Aktenzeichen: PCT/US98/07441

(96) Europäisches Aktenzeichen: 98 918 181.3

(87) PCT-Veröffentlichungs-Nr.: WO 1999/053548

(86) PCT-Anmeldetag: 13.04.1998

(87) Veröffentlichungstag

der PCT-Anmeldung: 21.10.1999

(97) Erstveröffentlichung durch das EPA: 07.02.2001

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 12.07.2006

(47) Veröffentlichungstag im Patentblatt: 31.05.2007

(51) Int Cl.<sup>8</sup>: H01L 27/15 (2006.01)

H01L 31/12 (2006.01)

H01L 31/153 (2006.01)

H01L 31/167 (2006.01)

H01L 33/00 (2006.01)

G06F 1/10 (2006.01)

G02B 6/43 (2006.01)

(73) Patentinhaber:

Intel Corporation, Santa Clara, Calif., US

(84) Benannte Vertragsstaaten:

DE, GB, IE

(74) Vertreter:

Hauck Patent- und Rechtsanwälte, 80339

München

(72) Erfinder:

RAO, R., Valluri, Saratoga, CA 95070, US

(54) Bezeichnung: VERFAHREN UND VORRICHTUNG ZUR OPTISCHEN TAKTVERTEILUNG IN EINER INTEGRIER-

TEN SCHALTUNG

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****STAND DER TECHNIK****Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung betrifft allgemein die Taktung integrierter Schaltungen, und im Besonderen betrifft die vorliegende Erfindung optische Taktverteilungsnetzwerke bzw. Taktverteilungsnetze in integrierten Schaltungen.

**Beschreibung des Stands der Technik**

**[0002]** Ein Aspekt, mit sich dem das Gebiet der integrierten Schaltungen heute beschäftigt, ist das Problem der Verteilung der Taktsignale durch einen Chip einer integrierten Schaltung mit geringer Taktverschiebung (englisch: Clock Skew). Bei der Taktverschiebung handelt es sich um die Differenz der Ankunftszeiten von Taktflanken an unterschiedenen Bereichen des Chips. Eine synchrone digitale Logik erfordert präzise Takte zum zwischenspeichern von Daten. Die ideale synchrone Logik basiert darauf, dass Takte gleichzeitig an allen Schaltungen ankommen. Die Taktverschiebung reduziert die maximale Betriebsfrequenz der Schaltung, da die Schaltung für einen zuverlässigen Betrieb in Bezug auf eine Verschiebung im ungünstigsten Fall gestaltet werden muss. Die Hauptursache für eine Taktverschiebung in der globalen Taktverteilung einer integrierten Schaltung ist die Abweichung der Wegführung der Impedanz der Taktverteilung in dem Chip. Somit entsteht eine Taktverschiebung auch bei einem Taktverteilungsnetz mit gleicher Länge, wie etwa H-Tree (H-Baum). Eine gute Daumenregel in der Branche ist es, dass für Taktverschiebung etwa 10% der Zykluszeit berücksichtigt werden sollten. In Bezug auf eine Taktfrequenz von 1 GHz, was einer Zykluszeit von 1 ns entspricht, beträgt die tolerierbare Taktverschiebung somit höchstens 100 ps. Da VLSI-Taktfrequenzen über 1 GHz ansteigen, werden die Anforderungen an die Taktverschiebung zunehmend anspruchsvoll.

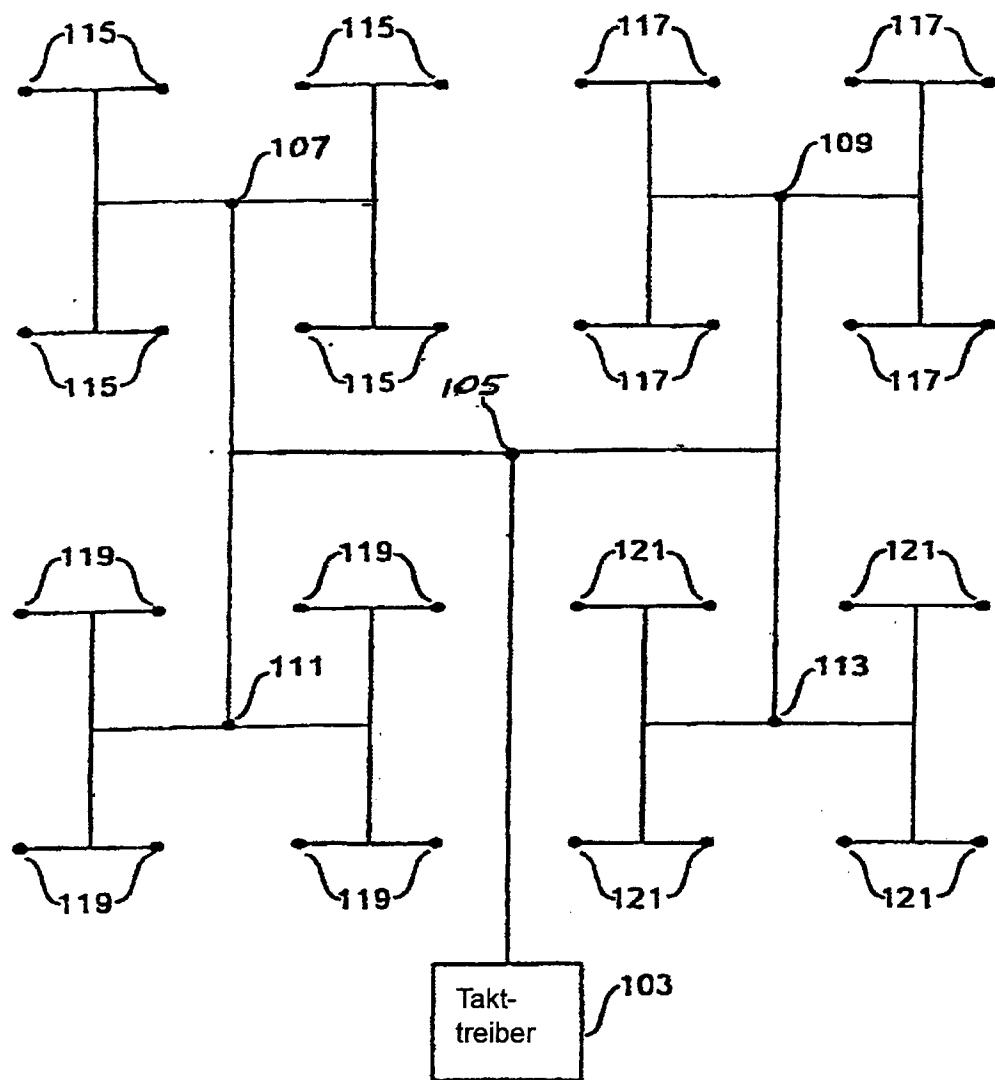

**[0003]** In dem heutigen dem Stand der Technik entsprechenden Taktverteilungsnetz wird die Taktverschiebung durch den Einsatz hierarchischer H-Bäume geregelt. Die Abbildung aus [Fig. 1A](#) zeigt ein Diagramm, das ein derartiges Taktverteilungsnetz **101** mit hierarchischem H-Baum veranschaulicht, das in integrierten Hochgeschwindigkeitsschaltungen implementiert wird, um den Effekt der Taktverschiebung zu beseitigen oder zu reduzieren. Wie dies in der Abbildung aus [Fig. 1A](#) dargestellt ist, wird ein Takttreiber **103** verwendet, um das H-Baum-Netz **101** zu steuern. Hiermit wird festgestellt, dass der Takttreiber **103** für gewöhnlich einen sehr großen Treiber darstellt, um eine ausreichende Steuerung bzw. Ansteuerung des H-Baum-Netzes **101** vorzusehen, das in

den heutigen komplexen integrierten Hochgeschwindigkeitsschaltungen eine große Kapazität aufweist. Wie dies aus [Fig. 1A](#) ersichtlich ist, weisen die Taktpfade des zwischen den Knoten **107**, **109**, **111** und **113** gebildeten „H“ gleiche Längen auf zwischen dem zentralen Knoten **105** und jedem der peripheren Punkte in dem „H“ an den Knoten **107**, **109**, **111** und **113**. Wenn somit eine einheitliche Ausbreitungsverzögerung eines Taktsignals je Längeneinheit des H-Baum-Netzes **101** angenommen wird, so sollte keine Taktverschiebung zwischen dem den Knoten **107**, **109**, **111** und **113** zugeführten Taktignal und von dem Takttreiber **103** existieren.

**[0004]** Die Abbildung aus [Fig. 1A](#) zeigt das H-Baum-Netz **101** ferner auf einer anderen hierarchischen Ebene, wobei das „H“ mit jedem entsprechenden peripheren Knoten des „H“ der ersten Ebene gekoppelt ist. Demgemäß ist jeder periphere Knoten **115** gleich weit von dem Knoten **107** entfernt. Jeder periphere Knoten **117** ist gleich weit von dem Knoten **109** entfernt. Jeder periphere Knoten **119** ist gleich weit von dem Knoten **111** entfernt. Und schließlich ist jeder periphere Knoten **121** gleich weit von dem Knoten **113** entfernt. Die Taktpfade von allen Knoten **115**, **117**, **119** und **121** sind somit alle gleich weit von dem Takttreiber **103** entfernt und sollten somit zwischen sich keine Taktverschiebung aufweisen, da die Taktverschiebung von dem Takttreiber **103** für alle peripheren Knoten des H-Baum-Netzes **101** gleich sein sollte. Somit kann jeder Knoten **115**, **117**, **119** und **121** so konfiguriert werden, dass er als eine Empfängerstation für ein Taktignal fungiert und die Taktanforderungen eines Bereichs der integrierten Schaltung nahe dem Knoten erfüllt, bei zu vernachlässigender Taktverschiebung in Bezug auf die anderen der ähnlich konfigurierten Knoten des H-Baum-Netzes **101**.

**[0005]** Integrierte Schaltungen werden immer größer, komplexer und arbeiten mit höheren Frequenzen, so dass die Taktverschiebung weiter eine Problem darstellt, und zwar auch bei einem H-Baum-Netzwerk **101**, da die Taktleitungen des H-Baum-Netzwerks **101** nicht immer einen einheitlichen charakteristischen Widerstand aufweisen. Folglich kann eine uneinheitliche Ausbreitungsverzögerung eines Taktsignals auftreten, das durch die Pfade des H-Baum-Netzes **101** verläuft, obwohl die Knoten **115**, **117**, **119** und **121** gleich weit von dem Takttreiber **103** entfernt sind. Folglich ist an den Endpunkten des H-Baum-Taktverteilungsnetzwerks **101** eine unvorhersehbare Taktverschiebung gegeben.

**[0006]** Zusätzlich zu der Taktverschiebung verbraucht die Taktverteilung auf dem Chip wertvolle Routing-Ressourcen in integrierten Schaltungen, die für Signale besser verwendet werden und somit die Wegführung der Signale verbessern könnten. Ein weiterer Aspekt, den die Entwickler von integrierten

Schaltungen berücksichtigen müssen, ist es, dass dem Stand der Technik entsprechende globale Taktverteilungsnetzwerke auch eine zunehmend große Fläche des integrierten Halbleiterchips sowie Leistung in Anspruch nehmen bzw. verbrauchen. Die globale Taktverteilung ist in den heute eingesetzten integrierten Hochgeschwindigkeits-Chips für gewöhnlich für ungefähr 10% der Chipleistung verantwortlich.

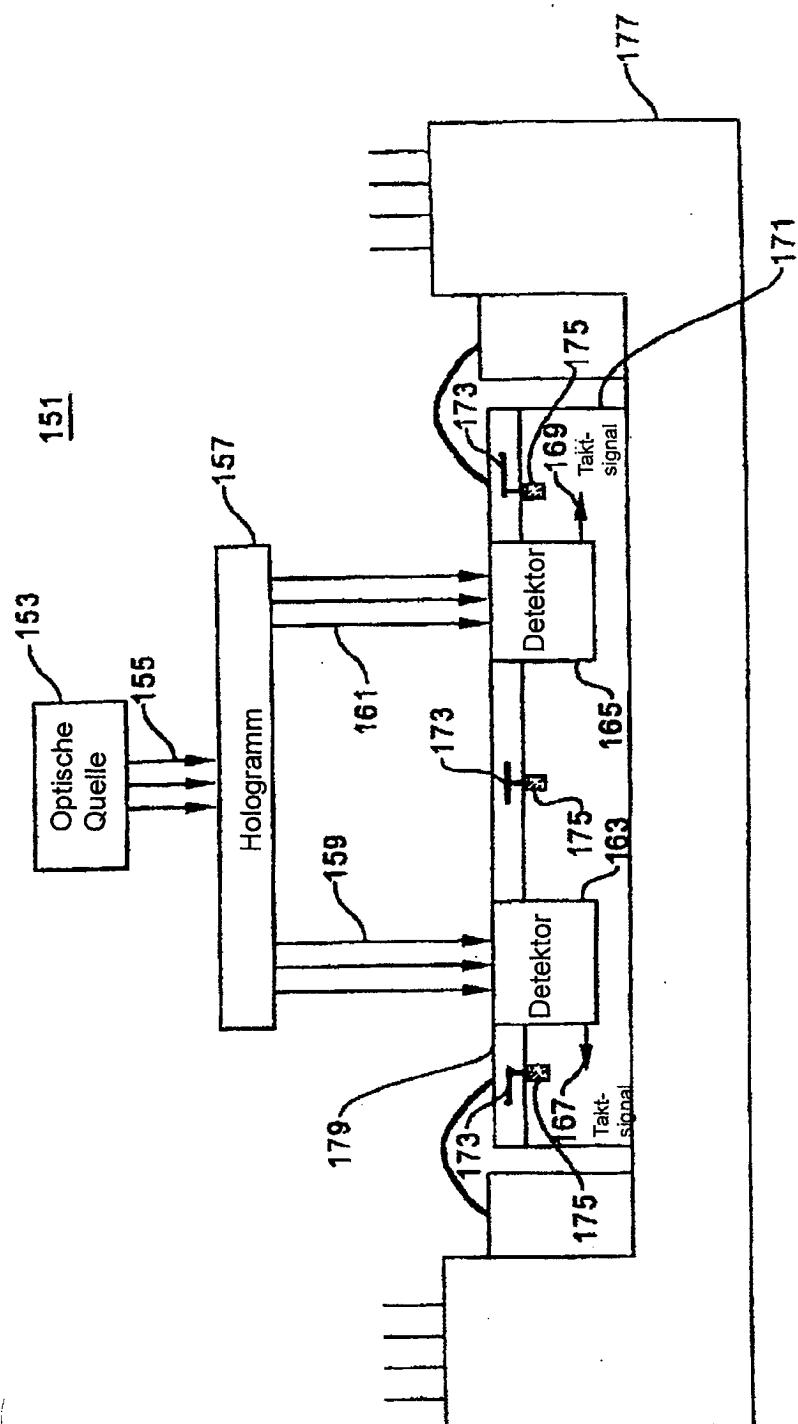

**[0007]** Untersucht wurden auch andere dem Stand der Technik entsprechende Techniken der Verteilung von Taktsignalen durch eine integrierte Schaltung. Einige dieser dem Stand der Technik entsprechenden Techniken weisen ein optisches Taktverteilungsnetzwerk **151** auf, das in der Abbildung aus [Fig. 1B](#) veranschaulicht ist. Eine außerhalb des Chips angeordnete optische Quelle **153** erzeugt ein optisches Takt signal **155**, das mittels Hologramm **157** in die geteilten Strahle **159** und **161** geteilt wird. Eine direkte Sichtlinie ist von der vorderen Seitenoberfläche **179** des integrierten Schaltungs-Halbleiterchips **171** zu den Detektoren **163** und **165** vorgesehen, um die entsprechenden geteilten Strahlen **159** und **161** zu empfangen. Das Taktsignal **167** wird von dem Detektor **163** erzeugt, und das Taktsignal **169** wird von dem Detektor **165** erzeugt. Da das Taktsignal danach von den Detektoren **163** und **165** lokal verteilt wird unter Verwendung von auf dem Chip vorgesehenen Metallzwischenverbindungen, stehen die Taktsignale **167** und **169** zur Verfügung, um ihre entsprechenden Bereiche der integrierten Schaltung zu takten.

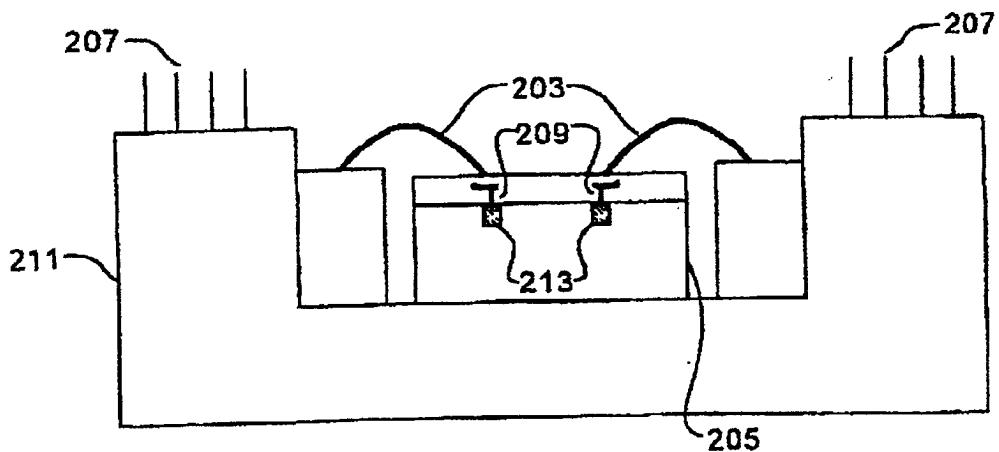

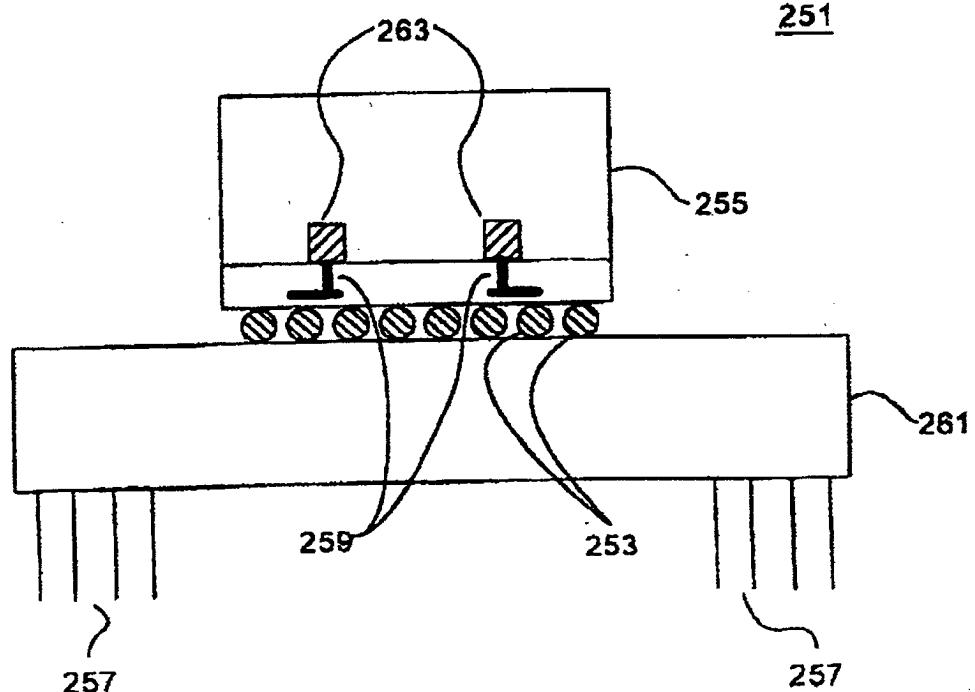

**[0008]** Eine besondere Schwierigkeit in Bezug auf die dem Stand der Technik entsprechende optische Taktverteilung ist das Problem der Implementierung dieser für moderne bzw. hoch entwickelte Packungstechnologien wie etwa verschlossene Chips vom Typ Control Collapse Chip Connection (C4) (teilweise auch als Flip-Chips bezeichnet) sowie C4/MCM (Multichip-Module). Die Abbildung aus [Fig. 2B](#) veranschaulicht einen verschlossenen C4-Chip **251**. C4 ist die Packung der Wahl für die Chips mit hohen Frequenzen der Zukunft, da C4 eine hohe Dichte induktionsarmer Anschlüsse unter Verwendung von Kugelverbindungen **253** zwischen dem Chip **255** und der Einheit **261** vorsieht, indem auf Verbindungsdrähte mit hoher Induktivität verzichtet wird, die in den heutigen Drahtverbindungs- bzw. Drahtanschlusseinheiten zum Einsatz kommen. Die Abbildung aus [Fig. 2A](#) zeigt einen Chip **201** unter Verwendung der heute erhältlichen Drahtverbindungseinheiten. Wie dies in der Abbildung aus [Fig. 2A](#) dargestellt ist, werden Drahtanschlüsse bzw. Drahtverbindungen **203** für Anschlüsse bzw. Verbindungen zwischen der Einheit **211** und dem Chip **205** verwendet. In Bezug auf eine C4-Einheit ist die Vorderseite des Chips nicht mehr zugänglich, und in Bezug auf die dem Stand der Technik entsprechende optische Wegführung bzw. das optische Routing muss die Wegführung bzw. das Routing in die Einheit selbst integriert werden. Dies

sieht in Bezug auf das Design des C4-Substrats außerordentlich komplexe Einschränkungen vor, wobei das Substrat in diesem Fall sowohl eine elektrische als auch eine optische Wegführung aufweisen muss.

**[0009]** Ein großes Problem in Bezug auf das dem Stand der Technik entsprechende optische Verteilungsnetzwerk **151** ist es, dass die Erfordernis der Positionierung der Detektoren **163** und **165** in der Sichtlinie der geteilten Strahlen **159** und **161** von der vorderen Seitenoberfläche **179** der integrierten Schaltung **171** eine herausfordernde Aufgabe in Bezug auf moderne integrierte Schaltungen darstellt, die für gewöhnlich fünf oder mehr metallische Zwischenverbindungsschichten verwenden. In Bezug auf die Stapelanordnung einer großen Anzahl von metallischen Zwischenverbindungsschichten, stellt das Erzeugen einer Sichtlinie zwischen den geteilten Strahlen **159** und **161** und den Detektoren **163** und **165**, ohne einen Wegführungsstau zu verursachen, eine besonders herausfordernde Aufgabe dar. Der Grund dafür ist es, dass die Sichtlinie impliziert, dass auf keiner Ebene der Zwischenverbindung oberhalb der pn-Übergangsdetektoren eine metallische Wegführung gegeben sein sollte. Somit werden die pn-Übergangsdetektoren zu Hindernissen in Bezug auf das Routing bzw. die Wegführung, und mit zunehmender Anzahl von Detektoren führt dies zu einem Anstieg der Größe der Halbleiterscheibe bzw. des Chips, wodurch allgemein die Fertigungsergiebigkeit und die Leistung reduziert werden.

**[0010]** EP-A-5888746 offenbart ein Verfahren zur Taktung von integrierten Schaltungs-Chips unter Verwendung eines Impulsasers, der auf das Substrat eines IS-Moduls auftrifft.

**[0011]** Das Substrat des IS-Moduls diffundiert den Laserstrahl, der danach die entgegengesetzte Oberfläche des Substrats als diffundierte Lichtimpulse verlässt. Ein auf der oberen Oberfläche des Substrats angebrachter IS-Chip weist zumindest einen optischen Empfänger auf, der die Impulsenergie von den diffundierten Lichtimpulsen empfängt und die Lichtimpulse in elektrische Impulse umwandelt, welche den Chip takten.

**[0012]** „Optical Interconnections for VLSI Systems“ von J. W. Goodman et al, Proceedings of the IEEE, IEE New York, USA, Band 72, Nummer 7, Juli 1984 (1984-07), Seiten 50–66, XP000828033 ISSN:0018-9219, offenbart die Möglichkeit der Anwendung optischer und elektrooptischer Technologien für Zwischenverbindungsprobleme in VLSI-Schaltungen. Die Referenz offenbart die Anwendung von optischen Zwischenverbindungen in Bezug auf das Problem der Taktverteilung, wobei ein einzelnes Takt signal zu vielen Abschnitten eines Chips oder einer Schaltung geleitet wird. Diesbezüglich offenbart die Referenz sowohl nicht fokussierte als auch fokussier-

te optische Verteilungsanordnungen einer Taktsignalquelle.

**[0013]** Benötigt wird somit ein Taktverteilungsnetzwerk, das die dem Stand der Technik zugeordneten Probleme behebt bzw. löst. Ein derartiges Taktverteilungsnetzwerk würde eine minimale Taktverschiebung in Bezug auf integrierte Schaltungen mit hoher Leistung und hoher Geschwindigkeit vorsehen, die in C4-Einheiten (Flip-Chip) und C4/CMC-Einheiten gepackt sind, und wobei es vollständig kompatibel ist mit der rückseitigen Kühlkörperanbringung für diese Einheiten. Zweitens sollte das Taktverteilungsnetzwerk den Leistungsverlust durch die globale Taktverteilung reduzieren, indem die hohe kapazitive Belastung des globalen Netzwerks eliminiert wird. Darüber hinaus sollte ein derartiges Taktverteilungsnetzwerk nicht die auf dem Chip vorgesehene Signalwegführung beeinträchtigen, und wobei es in der Lage wäre, mit zunehmender Größe und Komplexität der Chips sowie einem Betrieb auf zunehmenden Taktfrequenzen der integrierten Schaltung eine Taktverteilung mit geringer Taktverschiebung vorzusehen.

**[0014]** Die vorliegende Erfindung betrifft eine verbesserte Empfängerstation für ein optisches Taktverteilungsnetzwerk für eine integrierte Schaltung.

#### ZUSAMMENFASSUNG DER ERFINDUNG

**[0015]** Vorgesehen ist gemäß einem ersten Aspekt der vorliegenden Erfindung eine Empfängerstation für ein optisches Taktverteilungsnetzwerk gemäß dem gegenständlichen Anspruch 1.

**[0016]** Vorgesehen ist gemäß einem zweiten Aspekt der vorliegenden Erfindung ein Verfahren gemäß dem gegenständlichen Anspruch 4.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

**[0017]** Die vorliegende Erfindung wird in den beigefügten Abbildungen der Zeichnungen beispielhaft und ohne einzuschränken veranschaulicht. Es zeigen:

**[0018]** [Fig. 1A](#) ein hierarchisches H-Baum-Taktverteilungsnetzwerk;

**[0019]** [Fig. 1B](#) ein Diagramm eines dem Stand der Technik entsprechenden optischen Taktverteilungsnetzwerks unter Verwendung von Fotodetektoren, die auf der Oberfläche der Vorderseite eines integrierten Schaltungs-Chips angeordnet sind;

**[0020]** [Fig. 2A](#) eine heutige Drahtanschlusstechnologie;

**[0021]** [Fig. 2B](#) eine Flip-Chip- oder C4-Packungs-technologie;

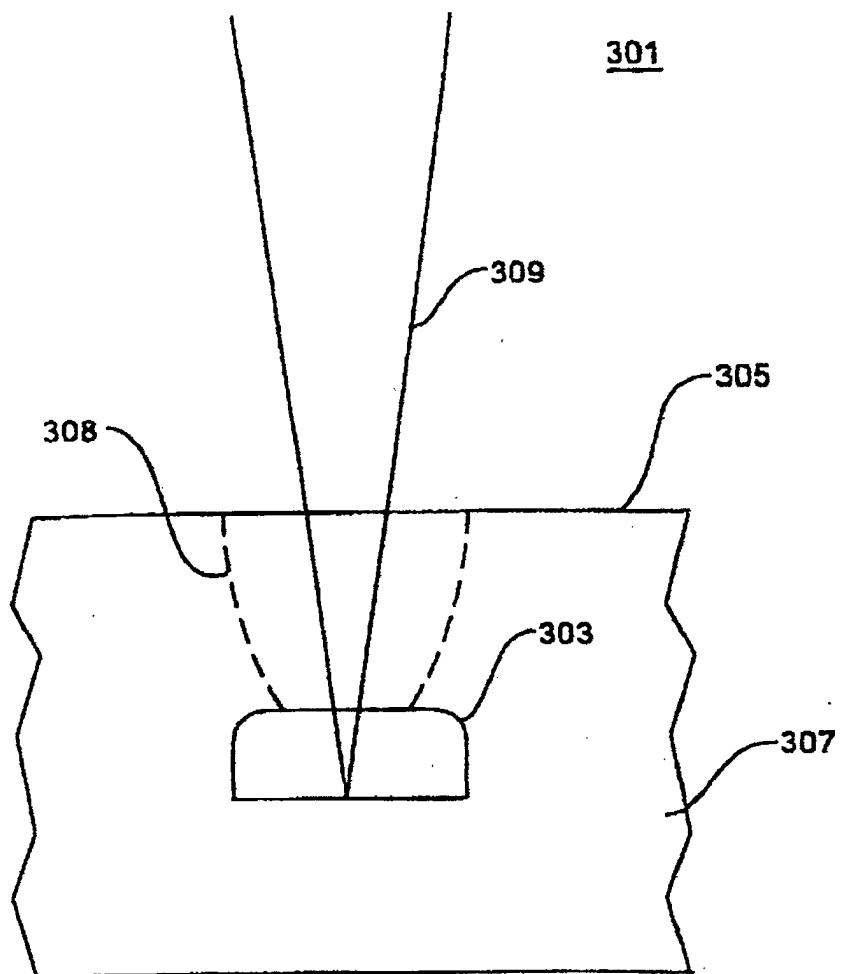

**[0022]** [Fig. 3](#) ein Diagramm eines durch eine Rückseite eines Halbleiters in einen pn-Übergang emittierten Laserimpulses;

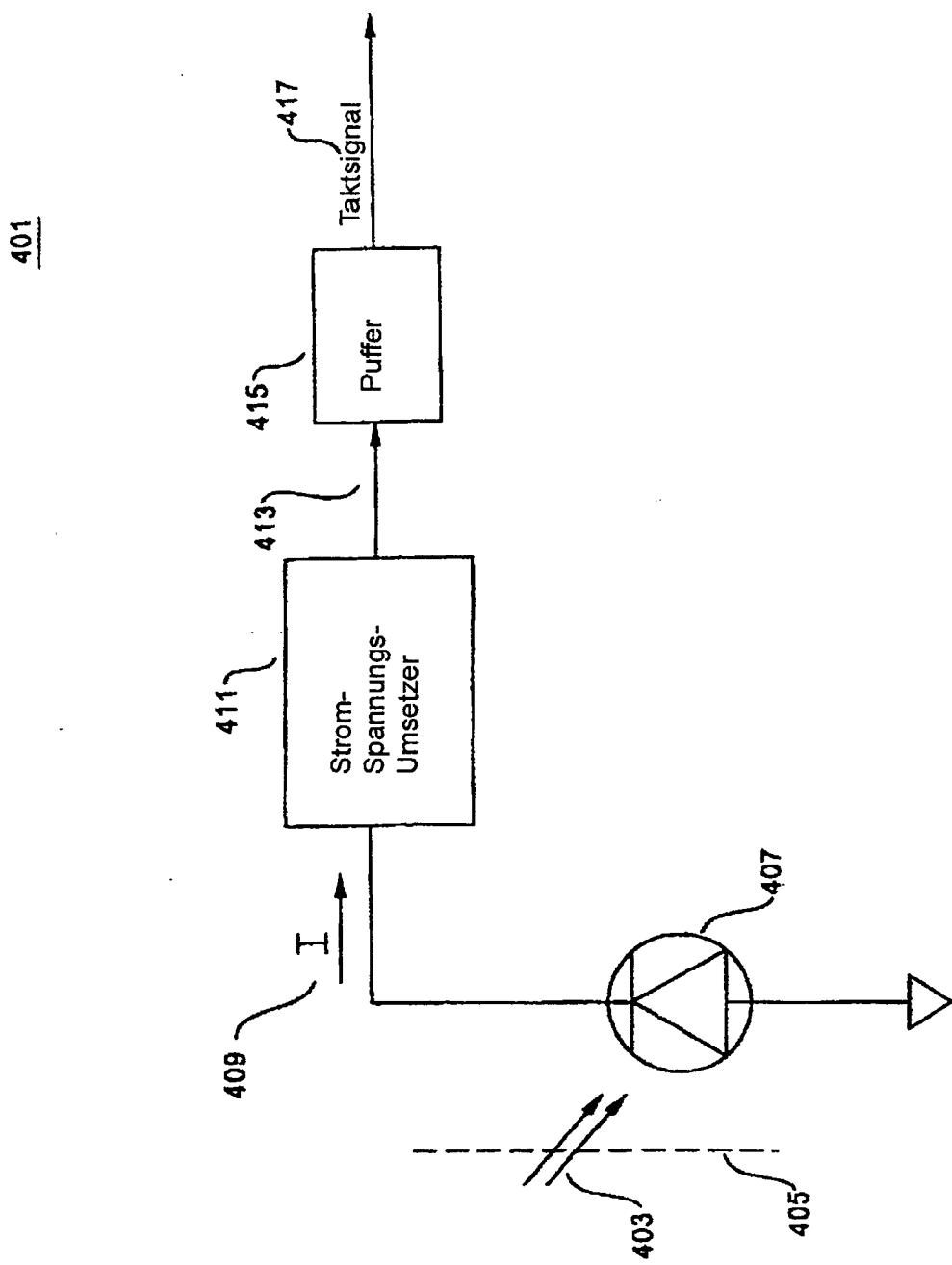

**[0023]** [Fig. 4](#) ein Blockdiagramm einer optischen Takttempfängerstation gemäß den Lehren der vorliegenden Erfindung;

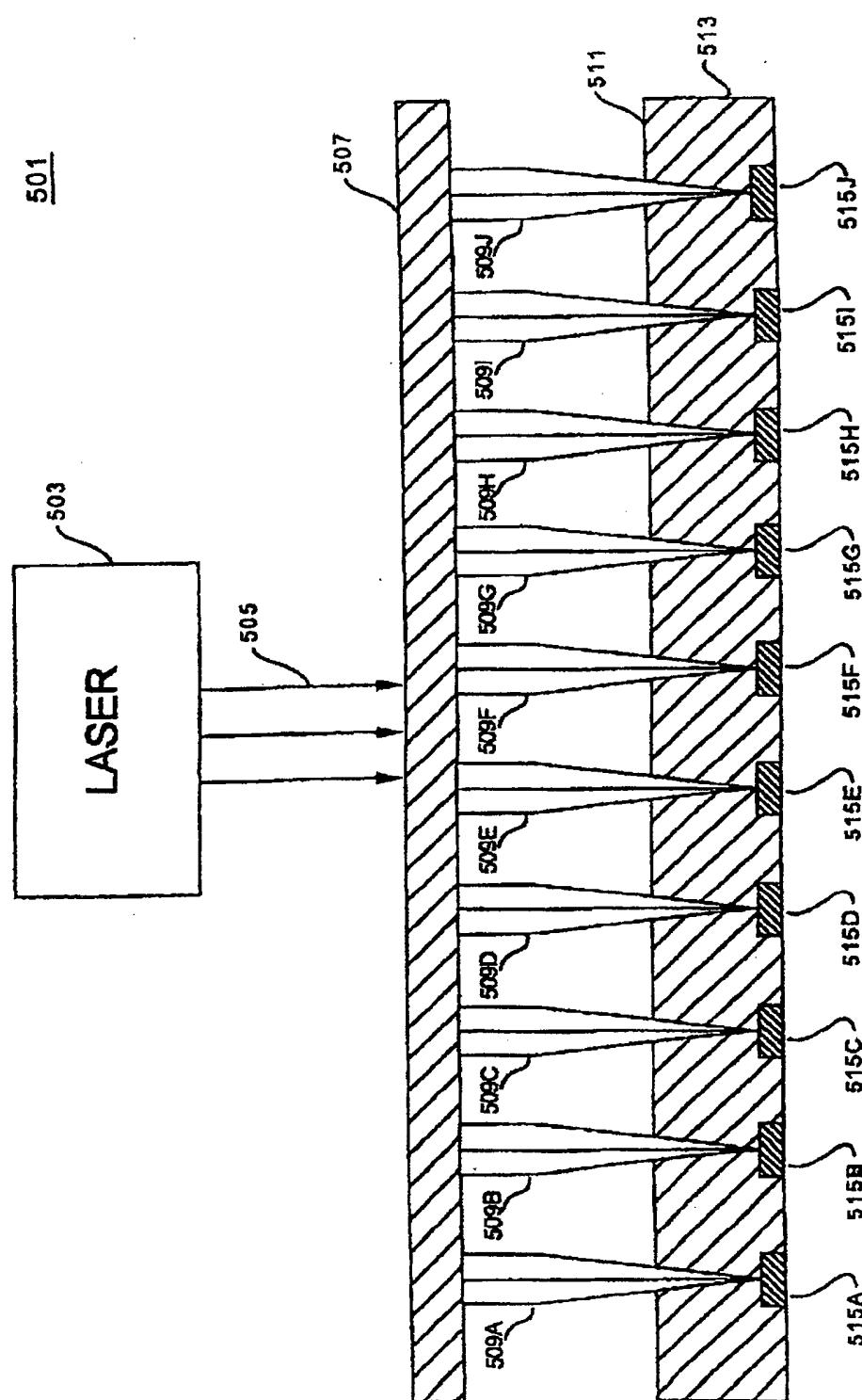

**[0024]** [Fig. 5](#) ein Diagramm eines optischen Taktverteilungsnetzwerks, das die optische Takttempfängerstation verwendet;

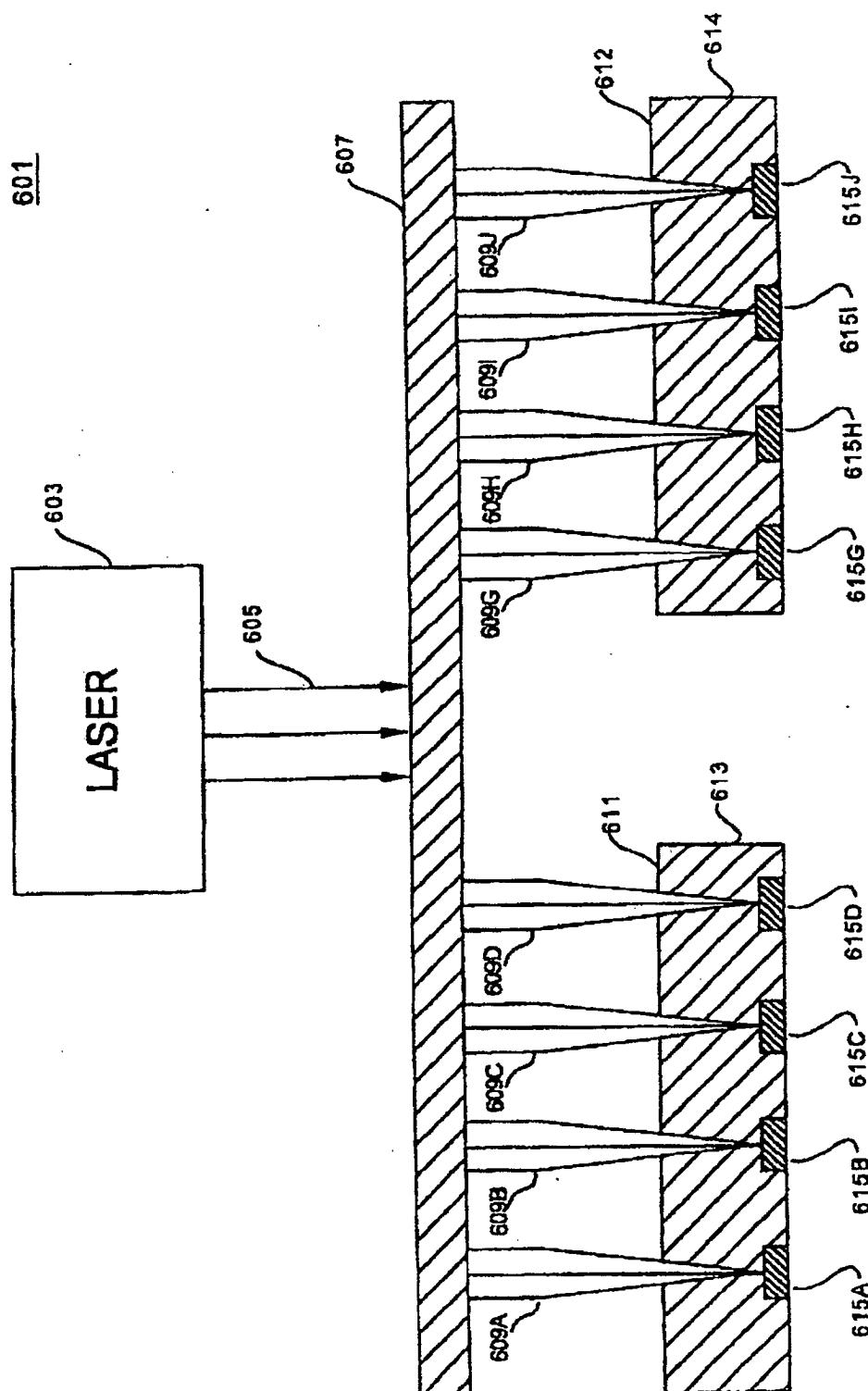

**[0025]** [Fig. 6](#) ein Diagramm eines weiteren optischen Taktverteilungsnetzwerks; und

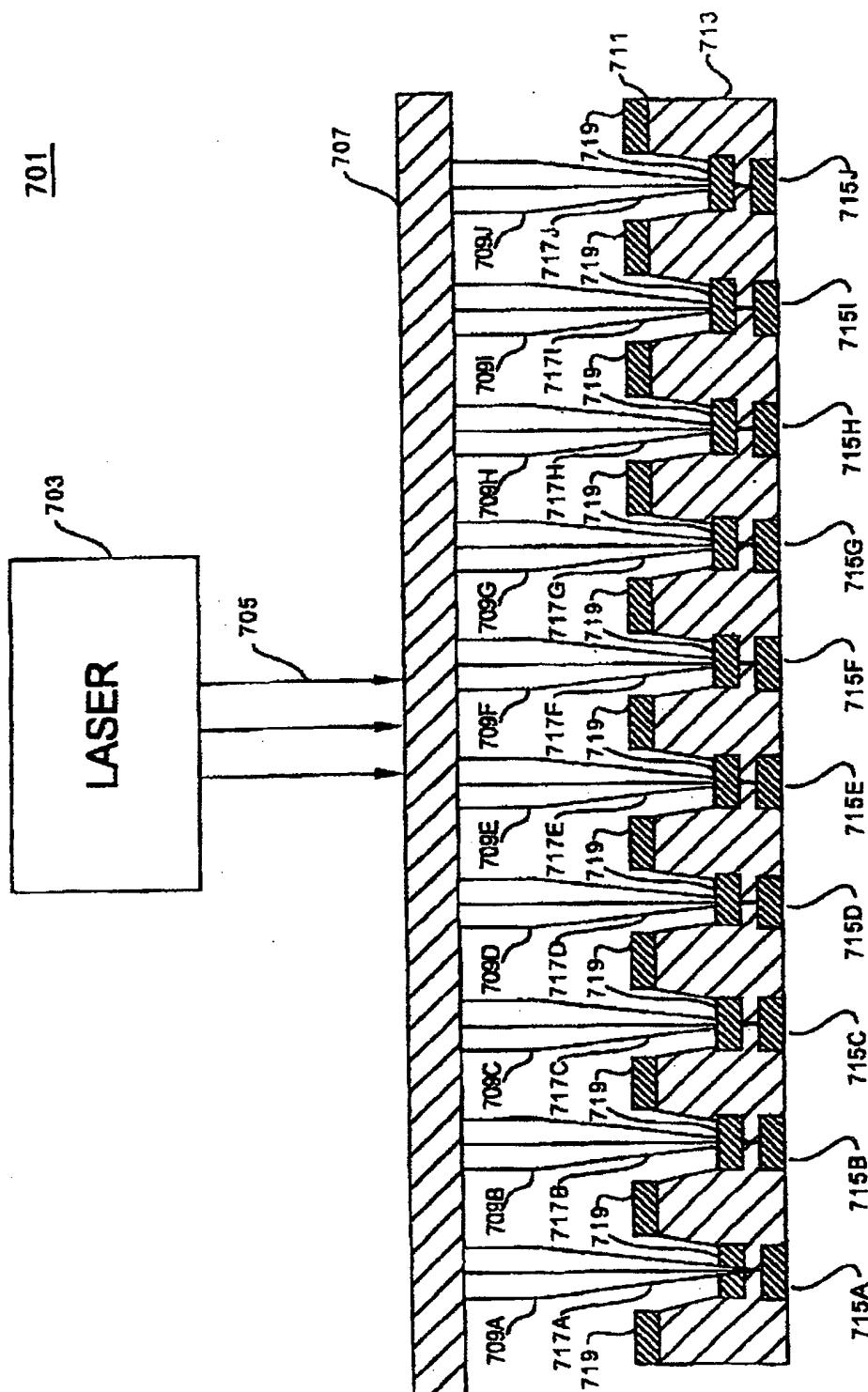

**[0026]** [Fig. 7](#) ein Diagramm eines wiederum weiteren optischen Taktverteilungsnetzwerks.

#### GENAUE BESCHREIBUNG DER ERFINDUNG

**[0027]** Offenbart werden ein Verfahren und eine Vorrichtung zur optischen Taktung einer integrierten Schaltung in einem Halbleiter. In der folgenden Beschreibung sind zahlreiche spezifische Einzelheiten ausgeführt, um ein umfassendes Verständnis der vorliegenden Erfindung zu vermitteln. Für den Durchschnittsfachmann auf dem Gebiet ist es jedoch offensichtlich, dass die spezifischen Einzelheiten nicht eingesetzt werden müssen, um die vorliegende Erfindung auszuführen. In anderen Fällen wurde auf die nähere Beschreibung allgemein bekannter Materialien oder Verfahren verzichtet, um die vorliegende Erfindung nicht unnötig zu verschleiern.

**[0028]** Vorgesehen sind gemäß der vorliegenden Erfindung ein Verfahren und eine Vorrichtung zum Taktieren einer integrierten Schaltung, indem über die Rückseite des Halbleiters optische Taktsignale eingeführt werden, und zwar unter Verwendung eines phasenverriegelten oder modulierten Infrarot- oder sichtbaren Lasers und das Fokussieren des Lichts in die pn-Übergangsempfänger, die durch das Siliziumsubstrat in die integrierte Chip-Schaltkreisanordnung integriert sind. Die vorliegende Erfindung weist den Vorteil des Einsatzes optischer Techniken auf, die eingesetzt werden können, ohne das herkömmliche CMOS-Verfahren und die C4-Packungstechnologie zu beeinträchtigen. Die Strahlenteilungs- und Fokussierungselemente können in einem Beispiel in optischen Elementen ausgebildet werden, die von dem Silizium getrennt sind, oder Lichtwellenleiter können auf die Rückseite des Siliziums abgeschieden oder mikrobearbeitet werden. Indem eine gleiche Pfadlänge von dem Master-Laser gemäß der vorliegenden Erfindung zu den pn-Übergangs-Fotodetektoren sichergestellt wird, kann der Anteil an der Taktverschiebung, die in dem globalen Taktverteilungsnetzwerk auftritt, durch die vorliegende Erfindung bei weiterem Anstieg der Taktfrequenzen minimiert werden. Durch den Ersatz des globalen Taktverteilungsnetzwerks in

dem Siliziumchip durch das hierin beschriebene optische Taktverteilungsnetzwerk lassen sich auch Chipfläche und Chipverlustleistung einsparen. Durch die Freisetzung von Siliziumchipfläche, die gemäß dem Stand der Technik vorher für die globale Taktwegführung verwendet worden ist, können ferner auch die Größen von Schaltungsschips reduziert werden. Da die Taktverteilung bei der vorliegenden Erfindung von dem Silizium und der Einheit bzw. Packung getrennt ist, wird die Taktverteilung skalierbar, so dass Entwicklungen und die optische Technologie in vorteilhafter Weise genutzt werden können.

**[0029]** In einem Beispiel für ein optisches Taktverteilungsnetzwerk ist ein außerhalb des Chips vorgesehener Infrarot-Laser als ein optischer Takt konfiguriert, um Infrarot-Laserimpulse auf einer gewünschten Taktfrequenz zu erzeugen und zu emittieren. Da Silizium in Bezug auf Infrarotlicht teilweise transparent bzw. durchlässig ist, können die Laserimpulse so konfiguriert werden, dass sie in das Silizium eindringen, und sie können in Empfängerstationen fokussiert werden, die pn-Übergänge aufweisen, die sich in dem Silizium befinden, so dass Fotoströme erzeugt werden. Hiermit wird festgestellt, dass stark dotiertes Silizium in Bezug auf Infrarotstrahlung auf einer Wellenlänge, die ungefähr im Bereich des Siliziumenergieabstands liegt, teilweise transparent ist. Im Besonderen entspricht der Bandabstand von innerem Silizium bei Zimmertemperatur 1,11 eV. Eine starke Dotierung bewirkt einen Rückgang des Bandabstands um etwa 100 meV auf 1,01 eV.

**[0030]** Die Abbildung aus [Fig. 3](#) zeigt einen Abschnitt einer Empfängerstation **301** gemäß den Lehren der vorliegenden Erfindung, der einen pn-Übergang **303** aufweist, der sich in einem Halbleiter **307** befindet. In einem Ausführungsbeispiel der vorliegenden Erfindung besteht der Halbleiter **307** aus Silizium. Hiermit wird festgestellt, dass der Halbleiter **307** Bestandteil einer integrierten Schaltung einer C4-Einheit ist, so dass die Rückseite **305** der integrierten Schaltung somit frei liegt. Folglich kann ein Infrarot-Laserimpuls **309** durch die Rückseite **305** des Halbleiters **307** in den pn-Übergang **303** fokussiert werden. Als Folge dessen kann ein Infrarot-Laserimpuls **309** durch die Rückseite **305** des Halbleiters **307** in den pn-Übergang **303** fokussiert werden. Durch die Energie des in den pn-Übergang **303** fokussierten Laserimpulses **309** wird ein Fotostrom erzeugt, der, wie dies nachstehend im Text näher beschrieben wird, gemäß den Lehren der vorliegenden Erfindung in eine Spannung und letztlich in ein Taktsignal umgewandelt wird. In einem Ausführungsbeispiel der vorliegenden Erfindung wird der Laserimpuls **309** optisch geteilt und durch die Rückseite **305** des Halbleiters **307** in eine Reihe von ähnlich konfigurierten pn-Übergängen **303** fokussiert.

**[0031]** In einem Beispiel des optischen Taktvertei-

lungsnetzwerks wird ein Neodym:Ytrium, Lithiumfluorid (Nd:YLF) Laser verwendet, der Photonen mit einer Wellenlänge von 1.054 µm erzeugt, und mit einer Energie von ungefähr 1,178 eV. Demgemäß können die Nd:YLF-Photonen von dem Infrarot-Laser von der Rückseite durch das Silizium direkt in Fotoempfängerdiode oder pn-Übergänge, die in die Schaltkreisanordnung eines C4-Chips eingebettet sind, übertragen. Die Laserstrahlung penetriert das Silizium und erzeugt Fotoströme in den pn-Übergängen. In einem Beispiel wurde für die Übertragung der Photonen eines Lasers mit einer Wellenlänge von 1,06 µm mit ungefähr 1–2% durch ein Substrat mit einer Dicke von ungefähr 720 µm gemessen.

**[0032]** Die Abbildung aus [Fig. 4](#) zeigt eine Empfängerstation **401** gemäß den Lehren der vorliegenden Erfindung, welche einen Photodetektor **407** aufweist, der sich in einem Halbleiter befindet, wobei ein Laserimpuls **403** durch die Rückseite **405** des Halbleiters auf den Photodetektor **407** fokussiert wird. Als Folge des Laserimpulses **403** wird ein Fotostrom **I 409** erzeugt, der mit einem Strom-Spannungs-Umsetzer **411** in eine Spannung **V 413** umgewandelt wird. Die Spannung **V 413** wird mit einem Puffer **415** gepuffert, so dass ein Taktsignal **417** erzeugt wird. In einem Ausführungsbeispiel der vorliegenden Erfindung handelt es sich bei dem Photodetektor **407** um einen in dem Halbleiter angeordneten pn-Übergang. Eine Mehrzahl von Empfängerstationen **401** kann durch den Chip der integrierten Schaltung verteilt sein, um ein Taktignal **417** vorzusehen, um einen bezeichneten Bereich der integrierten Schaltung zu takten. In einem Ausführungsbeispiel der vorliegenden Erfindung taktet das Taktignal **417** einen Bereich der integrierten Schaltung in der Nähe der Empfängerstation **401**. Durch eine Mehrzahl von vorgesehenen Empfängerstationen **401** zur Erzeugung der Taktsignale **417** kann der Takt mit minimaler Taktverschiebung optisch durch die integrierte Schaltung verteilt werden.

**[0033]** In einem Ausführungsbeispiel der vorliegenden Erfindung werden allgemein bekannte Schaltungstechniken eingesetzt, um den Fotostrom **I 409** in eine Spannung **V 413** umzuwandeln, und um **V 413** zu puffern, so dass das Taktsignal **417** erzeugt wird. Der Photodetektor **407**, der Strom-Spannungs-Umsetzer **411** und der Puffer **415** sind in Bezug auf Empfindlichkeit und Jitter-Verhalten optimiert, da anerkannt wird, dass der tatsächliche Chipversatz teilweise durch den Grad der Anpassung der Empfängerstationen **401** auf dem Chip bestimmt wird. Darüber hinaus wird hiermit festgestellt, dass das Ausmaß der in jeder Empfängerstation **401** eingesetzten Pufferung die tatsächliche Taktverschiebung beeinflusst, da jede zusätzliche lokale Pufferstufe entsprechend zusätzliche Taktverschiebung hinzufügt.

**[0034]** Die Abbildung aus [Fig. 5](#) zeigt das vorliegend beschriebene optische Taktverteilungsnetzwerk **501**. Ein Master-Laser **503** ist so konfiguriert, dass er Master-Laserimpulse **505** mit einer gewünschten Taktfrequenz emittiert. Ein Optikelement **507** empfängt die Master-Laserimpulse **505** und erzeugt geteilte Laserimpulse **509A–J**, wie dies in der Abbildung aus [Fig. 5](#) dargestellt ist. In einem Ausführungsbeispiel der vorliegenden Erfindung verwendet das optische Element **507** allgemein bekannte Techniken, um die geteilten Laserstrahlen **509A–J** zu teilen, parallel zu richten und durch die Rückseite **511** eines Halbleiters **513** einer integrierten Schaltung mit C4-Packung in die pn-Übergänge **515A–J** zu fokussieren. Jeder pn-Übergang **515A–J** ist einzeln in einer Empfängerstation enthalten, die der Station entspricht, wie sie vorstehend in Bezug auf die Abbildungen der [Fig. 3](#) und [Fig. 4](#) beschrieben worden ist. Folglich kann ein separates Taktsignal durch jeden pn-Übergang **515A–J** erzeugt und somit zur Taktung eines spezifizierten Bereichs der Schaltkreisanordnung in der integrierten Schaltung verwendet werden.

**[0035]** Wie dies aus der Abbildung aus [Fig. 5](#) deutlich wird, wird der Takt der integrierten Schaltung optisch durch den Chip verteilt, wodurch das Taktverteilungsnetzwerk von dem Silizium entfernt wird, und wodurch die Probleme eliminiert werden, die dem Stand der Technik entsprechenden Taktverteilungsnetzwerken zugeordnet sind, wie etwa dem H-Baum-Netzwerk **101**, das vorstehend in Bezug auf die Abbildung aus [Fig. 1](#) beschrieben worden ist.

**[0036]** Durch die optische Verteilung der Taktsignale durch die Rückseite **511** des Halbleiters **513** werden ferner die Probleme und Komplexitäten verhindert, die dem dem Stand der Technik entsprechenden optischen Taktverteilungsnetzwerk **151** aus [Fig. 1B](#) zugeordnet sind. Im Besonderen beeinträchtigt das vorliegend beschriebene optische Taktverteilungsnetzwerk **501** nicht die Wegführung des Chipsignals. Da der Zugang zu den pn-Übergängen **515A–J** nicht durch Metallzwischenverbindungen oder ein Packungs- bzw. Einheitssubstrat verdeckt ist, wie dies beim Stand der Technik der Fall ist, führt die Bereitstellung einer Sichtlinie zu den pn-Übergängen **515A–J** bei der vorliegenden Erfindung nicht zu den gleichen komplexen Wegführungsanforderungen und einer dichten Drängung von Metallzwischenverbindungen **173** des dem Stand der Technik entsprechenden optischen Taktverteilungsnetzwerks **151**.

**[0037]** In einem Ausführungsbeispiel der vorliegenden Erfindung werden die Pfadlängen des Master-Laserstrahls **505** durch geteilte Laserstrahlen **509A–J** in die pn-Übergänge **515A–J** alle mit der gleichen Länge vorgesehen, um etwaige Taktverschiebungen zwischen jedem pn-Übergang **515A–J** so ge-

ring wie möglich zu gestalten. In einem anderen Ausführungsbeispiel wird unter Verwendung der vorliegenden Erfindung eine geregelte Verschiebung leicht dadurch erreicht, dass das optische Signal verzögert wird, indem eine längere optische Pfadlänge in dem optischen Element **507** implementiert wird. In einem weiteren Ausführungsbeispiel der vorliegenden Erfindung ist das optische Element **507** über einen Lichtwellenleiter mit dem Laser **503** verbunden. In einem weiteren Ausführungsbeispiel der vorliegenden Erfindung befindet sich das optische Element **507** zwischen dem Silizium des Substrats **513** und einem Kühlkörper (nicht abgebildet). In diesem Ausführungsbeispiel befindet wird das optische Element **507** unter Verwendung allgemein bekannter Techniken in einer Sandwich-Konfiguration zwischen dem Silizium und dem Kühlkörper angeordnet, so dass die Wärme in ausreichendem Ausmaß von dem Chip der integrierten Schaltung verteilt wird.

**[0038]** Wie dies vorstehend im Text beschrieben worden ist, führt das optische Element **507** die Teilung, das Parallelrichten und die Fokussierung der Laserstrahlen **509A–J** in die pn-Übergänge **515A–J** unter Verwendung allgemein bekannter Techniken aus. In einem Beispiel weist das optische Element bzw. das Optikelement **507** ein Lichtwellenleitersystem auf, das eingesetzt wird, um die Laserleistung zu teilen, zu verteilen und in die pn-Übergänge **515A–J** zu fokussieren. Das vorliegende Ausführungsbeispiel weist an den Enden der Lichtwellenleiterelemente einzelne Mikrolinsen auf sowie jede erforderliche Angleichung des Brechungsindex von Silizium und Luft, um die Lichtkopplung in das Silizium zu maximieren.

**[0039]** In einem weiteren Beispiel kann ein per Computer erzeugtes Hologramm zur Erzeugung jedes der geteilten Laserstrahlen **509A–J** verwendet werden. Gemäß der vorliegenden Erfindung weist das Optikelement **507** Ätzphasen-Hologrammraster direkt auf der Rückseite des Siliziums auf, um das Infrarot-Laserlicht zu teilen und zu fokussieren. Das vorliegende Ausführungsbeispiel weist den Vorteil der Selbstausrichtung der Ausfächerungs- bzw. Fan-Out-Strahlen der Empfänger mit der Genauigkeit der lithografischen Deckung bzw. Übereinstimmung des eingesetzten Fertigungsverfahrens auf. In einem anderen Beispiel weist das optische Element **507** Wellenleiter auf, die aus Glas oder einem Polymer auf der Rückseite des Siliziums ausgebildet sind, um die Laserstrahlen **509A–J** zu teilen, zu biegen, parallel zu richten und in die pn-Übergänge **515A–J** zu fokussieren.

**[0040]** Die Abbildung aus [Fig. 6](#) veranschaulicht ein weiteres Beispiel des vorliegend beschriebenen optischen Taktverteilungsnetzwerks **601**, das einen Master-Laser **603** aufweist, der Laserimpulse **605** mit einer Taktfrequenz in ein optisches Element **607** emittiert. Das optische Element **607** teilt den Master-La-

serstrahl **605** in die geteilten Laserstrahlen **609A–D** und **609G–J**. Die geteilten Laserstrahlen **609A–D** werden durch die Rückseite **611** des Halbleiters **613** in die pn-Übergänge **615A–D** fokussiert. Die geteilten Laserstrahlen **609G–J** werden durch die Rückseite **612** des Halbleiters **614** in die pn-Übergänge **615G–J** fokussiert. Wie dies aus der Abbildung aus [Fig. 6](#) deutlich wird, sind die Halbleiter **613** und **614** nicht in dem gleichen Chip enthalten. Folglich sieht das vorliegende optische Taktverteilungsnetzwerk ein Taktignal an alle Empfängerstationen mit besonders geringer Taktverschiebung an mehrere Chips in einem Computersystem vor.

**[0041]** In einem Beispiel handelt es sich bei den Halbleitern **613** und **614** um Chips integrierter Schaltungen eines Mehrchip-Moduls.

**[0042]** In einem weiteren Beispiel sind die Halbleiter **613** und **614** in den Chips der integrierten Schaltung eines ganzen Computersystems integriert. Das heißt, das optische Taktverteilungsnetzwerk **601** stellt den Takt für ein ganzes Computersystem mit minimaler Taktverschiebung bereit und ist somit nicht auf die reine Bereitstellung eines Taktsignals für einen einzelnen Chip einer integrierten Schaltung beschränkt. Jeder Chip einer integrierten Schaltung gemäß der vorliegenden Erfindung weist pn-Übergänge **615** auf, um ein lokales Taktsignal zu erzeugen, um einen naheliegenden Bereich auf der integrierten Schaltung zu takten.

**[0043]** Die Abbildung aus [Fig. 7](#) zeigt ein weiteres Beispiel eines optischen Taktverteilungsnetzwerks **701** gemäß der vorliegenden Erfindung. Der Master-Laser **703** ist so konfiguriert, dass er Master-Laserimpulse **705** mit einer gewünschten Taktfrequenz in das optische Element **707** emittiert, das den Master-Laserstrahl **705** in die geteilten Laserstrahlen **709A–J** teilt. Zur Kompensation der Dämpfung, die in den geteilten Laserstrahlen **709A–J** nach der Penetration der Rückseite **711** des Halbleiters **713** auftritt, wurden die Aussparungen **717A–J** auf der Rückseite **711** dem Halbleiter **713** hinzugefügt, um den Halbleiter **713** zwischen den pn-Übergängen **715A–J** und dem Master-Laser **703** lokal dünner zu gestalten. Als Folge dessen verlaufen die geteilten Strahlen **709A–J** im Vergleich zu dem optischen Taktverteilungsnetzwerk **501** aus [Fig. 5](#) nicht durch so viel Halbleitermaterial. Somit wird das Ausmaß der Dämpfung des geteilten Laserstrahls **709A–J** vor dem Erreichen der pn-, Übergänge **715A–J** reduziert, und die Übertragung von Infrarot-Laser in jeden pn-Übergang **715A–J** wird verbessert. In einem Beispiel können die Aussparungen **717A–J** unter Verwendung allgemein bekannter Techniken mikrobearbeitet oder gefräst werden, wie zum Beispiel durch anisotropes Nassätzen oder eine beliebige andere Technik, die zum Bilden von Gräben, Durchkontakte rungen oder dergleichen heute in Verbindung mit in-

tegrierten Schaltungen eingesetzt wird.

**[0044]** Eine weitere Technik, die zur Steigerung der Effizienz der geteilten Laserstrahlen **709A–J** verwendet wird, die die pn-Übergänge **715A–J** erreichen, ist die Minimierung der von der Rückseite **711** des Halbleiters **713** reflektierten Laserleistung. Ein Beispiel wist eine Antireflexionsschicht **719** auf, die sich auf der Rückseite **711** des Halbleiters **713** befindet. Durch die Antireflexionsschicht **719** auf der Rückseite **711** des Halbleiters **713** wird die Menge der von der Rückseite **711** des Halbleiters **713** reflektierten Energie reduziert, was zu einer verbesserte Lichtkopplung in den Halbleiter **713** führt. Unter Verwendung von Techniken wie des Auftrags der Antireflexionsschicht **719** und des Fräsen des Halbleiters **713** oberhalb jedes pn-Übergangs **715A–J** wird die Menge der jeder Empfängerstation zugeführten Laserenergie erhöht, was zu einer höheren Effizienz des optischen Taktverteilungsnetzwerks **701** führt.

**[0045]** In einem Beispiel der Empfängerstation in erneutem Bezug auf die Abbildung aus [Fig. 3](#) ist der Laserimpuls **309** nicht auf einen Infrarot-Laser beschränkt. In diesem Beispiel wird ein erheblicher Abschnitt **308** des Halbleiters **307** weggefräst, so dass ein Graben oder eine Aussparung gebildet wird, so dass der Laserimpuls **309** nicht um mehr als ungefähr 0,2–1,0 µm des Halbleitermaterials penetrieren muss (abhängig von der präzise verwendeten Wellenlänge), bevor der pn-Übergang **303** erreicht wird. Wenn der größte Teil des Abschnitts **308** von dem Halbleiter **307** entfernt worden ist, kann ein Laserimpuls **309** mit Licht im sichtbaren Bereich (~0,4–0,7 µm) oder im nahen Infrarotbereich (~0,7–1,0 µm) direkt von der Rückseite **305** des Halbleiters **307** in den pn-Übergang **303** fokussiert werden und Fotoströme erzeugen. Indem ungefähr 0,2 bis 1,0 µm des Halbleitermaterials erhalten bleiben, bleibt der pn-Übergang unversehrt.

**[0046]** Der Hauptvorteil des Einsatzes einer Quelle für Licht im sichtbaren Bereich oder im nahen Infrarotbereich betrifft die Effizienz der Umsetzung von optisch in elektrisch in den Empfängern. Grund dafür ist es, dass die Fotonenenergie für Teile des Spektrums (Wellenlänge  $\leq 1,1 \mu\text{m}$ ) im sichtbaren oder nahen Infrarotbereich deutlich höher ist als in dem Infrarotschnitt des Spektrums, und dass die Lichtabsorption in den Dioden deutlich effizienter ist ( $\lambda \times E = 1,24$ , wobei  $\lambda$  die Fotonenenergie in µm bezeichnet, und wobei  $E$  der Fotonenenergie in eV entspricht). Dies bedeutet auch, dass bei einer sichtbaren Quelle weniger optische Leistung erforderlich ist. Die 0,2–1,0 µm des verbleibenden Halbleitermaterials reichen aus, um sicherzustellen, dass ein pn-Übergang vorhanden ist, während die optische Dämpfung durch das Halbleitermaterial minimiert wird.

**[0047]** Zum Beispiel werden optische Strahlen mit

einer Fotonenenergie, die höher ist als der Bandabstand von Silizium, exponential durch das Silizium gedämpft. Die kennzeichnende Dämpfung wird mit abnehmender Wellenlänge größer. Wenn die Dicke des Siliziums jedoch nur 0,2 bis 1,0 µm beträgt, so ist die Dämpfung zu vernachlässigen. Für einen Betrieb im nahen Infrarotbereich kann die Dicke des verbleibenden Siliziums bis zu 1,0 µm betragen, ohne dass eine signifikante Dämpfung gegeben ist. Für einen Betrieb im sichtbaren Bereich sollte die Dicke des verbleibenden Siliziums im Bereich von 0,2 µm liegen. In einem Beispiel wird der Graben oder die Aussparung mit Material hinterfüllt, das für Strahlung im sichtbaren Bereich oder im nahen Infrarotbereich transparent bzw. durchlässig ist, um die frei liegenden Empfänger bei dieser Anordnung zu schützen.

**[0048]** Beschrieben wurden vorstehend somit ein Verfahren und eine Vorrichtung zur optischen Taktung einer integrierten Schaltung in einem Halbleiter. In Verbindung mit dem vorliegend beschriebenen optischen Taktverteilungsnetzwerk können zahlreiche identische Takte mit praktisch keiner Verschiebung an eine integrierte Schaltung mit hoher Frequenz verteilt werden. Ferner sieht die vorliegende Erfindung eine optische Taktung ohne Taktverschiebung für Mehrchip-Module oder die Chips eines ganzen Computersystems vor. Darüber hinaus kommt das vorliegend beschriebene Taktverteilungsnetzwerk ohne große globale Takttreiber und die globale Taktverteilung von dem Siliziumchip aus, was zu Einsparungen hinsichtlich der Chip-Verlustleistung führt, zusätzliche Chipfläche für die Signalwegführung zur Verfügung stellt oder eine Reduzierung der Gesamtgröße des Chips ermöglicht, was wiederum zu höherer Produktivität in der Fertigung und einem höheren Frequenzbetrieb führt, der ein Resultat der kürzeren Zwischenverbindungsängen darstellt.

**[0049]** In der vorstehenden genauen Beschreibung wurden das Verfahren und die Vorrichtung gemäß der vorliegenden Erfindung in Bezug auf bestimmte Ausführungsbeispiele der Erfindung beschrieben. Es ist jedoch erkennbar, dass diesbezüglich verschiedene Modifikationen und Abänderungen möglich sind, ohne dabei vom Umfang der vorliegenden Erfindung abzuweichen, der ausschließlich in den anhängigen Ansprüchen definiert ist. Die vorliegende Beschreibung und die Zeichnungen dienen somit Veranschaulichungszwecken und schränken die Erfindung nicht ein.

### Patentansprüche

1. Empfängerstation (401) für ein optisches Taktverteilernetzwerk (501), wobei die genannte Empfängerstation folgendes umfasst:

ein optisches Element, das so angeordnet ist, das es empfangene Infrarot-Master-Laserimpulse (505) mit einer Master-Taktfrequenz in eine Mehrzahl geteilter

Lasertaktimpulse (509A–J) teilt; eine Mehrzahl von Fotodetektoren (407, 515A–J), die in einem Halbleiter (513) angeordnet sind, mit mindestens einer Vorderseite und einer Rückseite (405, 511), wobei jeder der Fotodetektoren so konfiguriert ist, dass er einen entsprechenden geteilten Lasertaktimpuls (509A–J) über die Rückseite des Halbleiters empfängt, so dass ein Fotostrom (409) erzeugt wird; und

eine entsprechende Mehrzahl von Strom-Spannungsumwandlern (411), die jeweils elektrisch mit einem entsprechenden der Fotodetektoren gekoppelt sind, wobei jeder Strom-Spannungsumwandler so angeordnet ist, dass er ein Taktsignal (417) aus dem Fotostrom erzeugt, um einen entsprechenden Bereich einer integrierten Schaltung zu takten, der sich in dem Halbleiter befindet;

wobei das optische Element Ätzphasen-Hologrammraster direkt auf der Rückseite des genannten Halbleiters umfasst, um Infrarot-Master-Laserimpulse zu teilen und um die geteilten Lasertaktimpulse in die Fotodetektoren zu fokussieren.

2. Empfängerstation nach Anspruch 1, wobei diese ferner einen Puffer (415) umfasst, der zwischen jeden Strom-Spannungsumwandler und jeden entsprechenden Bereich der integrierten Schaltung gekoppelt ist.

3. Empfängerstation nach Anspruch 1, wobei der Halbleiter Silizium umfasst.

4. Verfahren zur optischen Taktung einer integrierten Schaltung in einem Halbleiter (513) mit mindestens Vorder- und Rückseiten (511) und mit Ätzphasen-Hologrammrastern direkt auf der Rückseite, wobei das Verfahren die folgenden Schritte umfasst: das Teilen von Infrarot-Master-Laserimpulsen (505) mit einer Master-Taktfrequenz mit den Hologramm-Infrarotrastern in eine Mehrzahl von geteilten Lasertaktimpulsen (509A–J);

das Fokussieren der genannten geteilten Lasertaktimpulse mit den Hologrammrastern durch die Rückseite des Halbleiters, in entsprechende Fotodetektoren (407, 515A–J), die in dem Halbleiter angeordnet sind;

das Umwandeln von Fotoströmen (409) in den Fotodetektoren als Reaktion auf die geteilten erzeugten Lasertaktimpulse in eine Mehrzahl von entsprechenden Taktsignalen (417); und

das Takten entsprechender Bereiche der integrierten Schaltung, die sich in dem Halbleiter befinden, durch jedes Signal der genannten Mehrzahl von Taktsignalen.

5. Verfahren nach Anspruch 4, wobei dieses den zusätzlichen Schritt des Pufferns jedes Signals der Mehrzahl von Taktsignalen nach dem Schritt der Umwandlung des Fotostroms aufweist.

6. Verfahren nach Anspruch 5, wobei die Fotodetektoren in dem gleichen Halbleiter angeordnet sind.

Es folgen 8 Blatt Zeichnungen

## Anhängende Zeichnungen

EP98918181.3

101

FIG. 1A' (Stand der Technik)

FIG. 1B (Stand der Technik)

201

**FIG. 2A** (Stand der Technik)

251

**FIG. 2B** (Stand der Technik)

FIG. 3

FIG. 4

FIG.5

FIG.6

FIG. 7