## (12) 发明专利

(10) 授权公告号 CN 106447599 B

(45) 授权公告日 2021.10.08

(21) 申请号 201610532199.1

(51) Int.CI.

(22) 申请日 2016.07.07

G06T 1/60 (2006.01)

(65) 同一申请的已公布的文献号

申请公布号 CN 106447599 A

(56) 对比文件

(43) 申请公布日 2017.02.22

US 2010309511 A1, 2010.12.09

(30) 优先权数据

CN 204465758 U, 2015.07.08

2015-158722 2015.08.11 JP

CN 103885908 A, 2014.06.25

(73) 专利权人 瑞萨电子株式会社

齐希. 基于DM642的MPEG-4AAC编解码器的实现与优化.《中国优秀硕士学位论文全文数据库医药卫生科技辑》.2014, 第2014年卷(第5期), E080-57.

地址 日本东京

审查员 丁川

(72) 发明人 津田哲治 长谷昌 井上由纪

权利要求书2页 说明书7页 附图13页

西川直宏

(74) 专利代理机构 北京市金杜律师事务所

11256

代理人 王茂华

## (54) 发明名称

半导体装置

## (57) 摘要

本发明涉及半导体装置。所述半导体装置包括在一个半导体衬底上的中央处理单元和处理器。该处理器包括用于存储寄存器设置列表的缓冲器，并且将指示对所述寄存器设置列表的读取完成的访问完成信号通知给中央处理单元。该中央处理单元基于所述访问完成信号来改变存储器内的所述寄存器设置列表，并将更新请求信号通知给处理器。所述处理器基于更新请求信息来将由所述中央处理单元改变的所述寄存器设置列表读入到缓冲器中。

1. 一种半导体装置,包括在一个半导体衬底上的中央处理单元和处理器,

其中所述处理器包括用于分别地存储多个寄存器设置列表的多个缓冲器,并且生成对所述多个寄存器设置列表进行读取的每个开始信号和完成信号,并且所述处理器将基于所述开始信号或所述完成信号的访问完成信号通知给中央处理单元,其中所述多个缓冲器包括用于存储第一寄存器设置列表的第一缓冲器和用于存储第二寄存器设置列表的第二缓冲器,

其中所述中央处理单元基于所述访问完成信号来改变存储器内的第三寄存器设置列表,并且将改变请求信号通知给所述处理器,并且

其中所述处理器基于所述改变请求信号,读取由所述中央处理单元改变的所述第三寄存器设置列表,并且在从所述第一寄存器设置列表的所述访问完成信号到所述第二寄存器设置列表的所述访问完成信号的时段中,将所述第三寄存器设置列表存储在所述缓冲器中。

2. 根据权利要求1所述的半导体装置,

其中,所述处理器连续地按周期地执行预定时间内的处理。

3. 根据权利要求1所述的半导体装置,还包括:

存储器接口,其用于从所述存储器来读取寄存器设置列表;

处理单元,其用于基于所述寄存器设置列表来处理数据;以及

控制单元,其用于生成开始信号和完成信号。

4. 根据权利要求1所述的半导体装置,

其中,所述处理器从所述存储器读取视频数据,处理该视频数据,并且将已处理视频数据写入到所述存储器中。

5. 根据权利要求1所述的半导体装置,

其中,所述处理器从所述存储器读取声音数据,处理该声音数据,并且将已处理声音数据写入到所述存储器中。

6. 根据权利要求1所述的半导体装置,

其中,所述存储器被形成在不同于上述半导体衬底的半导体衬底上。

7. 一种半导体装置,包括在一个半导体衬底上的中央处理单元和处理器,

其中所述处理器包括用于分别地存储多个寄存器设置列表的多个缓冲器,生成对所述寄存器设置列表进行读取的每个开始信号和完成信号,并且将基于所述开始信号或所述完成信号的访问完成信号通知给所述中央处理单元,

其中所述多个缓冲器包括用于存储第一寄存器设置列表的第一缓冲器和用于存储第二寄存器设置列表的第二缓冲器,

其中所述中央处理单元基于所述访问完成信号来改变存储器内的第三寄存器设置列表,并且将改变请求信号通知给所述处理器,并且

其中所述处理器基于所述改变请求信号来读取由所述中央处理单元改变的所述寄存器设置列表,并且基于所述完成信号确定在从所述第一寄存器设置列表的所述访问完成信号到所述第二寄存器设置列表的所述访问完成信号的时段中,所述多个缓冲器中的哪个缓冲器来存储所述第三寄存器设置列表。

8. 根据权利要求7所述的半导体装置,

其中,所述处理器连续地按周期地执行预定时间内的处理。

9.根据权利要求7所述的半导体装置,还包括:

存储器接口,其用于从所述存储器来读取所述寄存器设置列表;

处理单元,其用于基于所述寄存器设置列表来处理数据;以及

控制单元,其用于生成所述开始信号和所述完成信号。

10.根据权利要求7所述的半导体装置,

其中,所述处理器从所述存储器读取视频数据,处理该视频数据,并且将已处理视频数据写入到所述存储器中。

11.根据权利要求7所述的半导体装置,

其中,所述处理器从所述存储器读取声音数据,处理该声音数据,并且将已处理声音数据写入到所述存储器中。

12.根据权利要求7所述的半导体装置,

其中,所述存储器被形成在不同于上述半导体衬底的半导体衬底上。

13.一种半导体装置,包括在一个半导体衬底上的中央处理单元和处理器,

其中所述处理器包括用于分别地存储多个寄存器设置列表的多个缓冲器,并且生成对所述寄存器设置列表进行读取的每个开始信号和完成信号,其中所述多个缓冲器包括用于存储第一寄存器设置列表的第一缓冲器和用于存储第二寄存器设置列表的第二缓冲器,

其中各个所述寄存器设置列表包括:存储有要被执行的下一列表的存储器的各个地址信息,

其中所述中央处理单元改变存储器内的第三寄存器设置列表,并且

其中所述处理器基于所述地址信息来读取由所述中央处理单元改变的所述第三寄存器设置列表,并且基于所述完成信号来确定所述缓冲器中的哪个缓冲器将存储所述第三寄存器设置列表。

14.根据权利要求13所述的半导体装置,

其中,所述处理器连续地按周期地执行预定时间内的处理。

15.根据权利要求13所述的半导体装置,还包括:

存储器接口,其用于从所述存储器来读取所述寄存器设置列表;

处理单元,其用于基于所述寄存器设置列表来处理数据,以及

控制单元,其用于生成所述开始信号和所述完成信号。

16.根据权利要求13所述的半导体装置,

其中,所述处理器从所述存储器读取视频数据,处理该视频数据,并且将已处理视频数据写入到所述存储器中。

17.根据权利要求13所述的半导体装置,

其中,所述处理器从所述存储器读取声音数据,处理该声音数据,并且将已处理声音数据写入到所述存储器中。

18.根据权利要求13所述的半导体装置,

其中,所述存储器被形成在不同于上述半导体衬底的半导体衬底上。

## 半导体装置

[0001] 相关申请的交叉引用

[0002] 2015年8月11日提交的日本专利申请号2015-158722的公开(包括说明书、附图以及摘要)被整体地通过引用结合到本文中。

### 技术领域

[0003] 本公开涉及一种半导体装置,并且其可以应用于例如提供有基于寄存器设置列表来操作的硬件知识产权(IP)的半导体装置。

### 背景技术

[0004] 形成中央处理单元(CPU)和存储器以及诸如信号处理电路之类的大规模集成化(LSI)的功能块在半导体领域中称为“IP”(知识产权)。IP包括每个功能块的硬件(逻辑电路图、LSI布局等)和软件(驱动软件、固件、中间件等)。此外,芯片上系统(SoC)是一种将某个设备或系统的操作所需的所有功能安装在一个半导体芯片上的方法,包括各种控制器和存储器的硬件IP(在下文中称为H/W\_IP),CPU被固定为核心。与本公开有关的在先技术包括例如美国专利申请公开号2010/0309511。

[0005] 根据安装在SoC上的H/W\_IP的数目的增加和来自每个H/W\_IP的中断的频率的增加,CPU的中断处理时间具有增加趋势。此外,由CPU对H/W\_IP的控制时序的限制随着更快的速率而变得严重。

[0006] 根据本描述和本发明及附图,其它目的和新型特性将是显而易见的。

### 发明内容

[0007] 将如下简要地描述本公开的典型的一个的概述。也就是说,CPU和H/W\_IP在时间共享时共享寄存器设置列表,并且在H/W\_IP未参考寄存器设置列表的同时,CPU可以重写寄存器设置列表。

[0008] 根据上述内容,可以减少由CPU对H/W\_IP的控制时序的限制。

### 附图说明

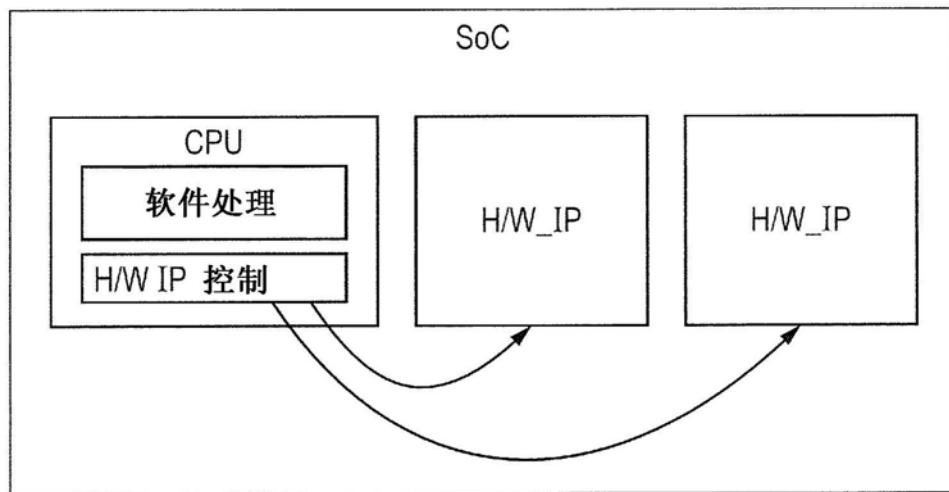

[0009] 图1是供在描述SoC时使用的框图。

[0010] 图2是根据比较例1的供在描述SoC的结构时使用的框图。

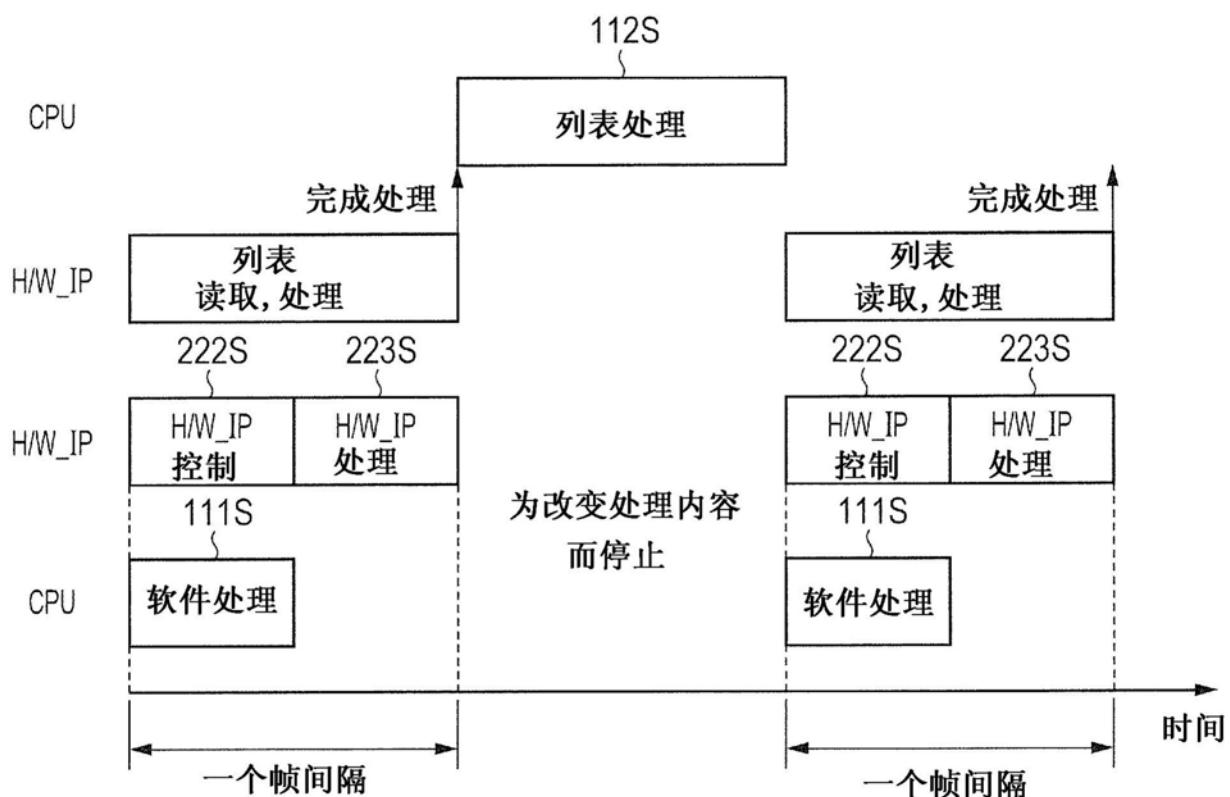

[0011] 图3是供在描述图2中的SoC中的控制时序时使用的视图。

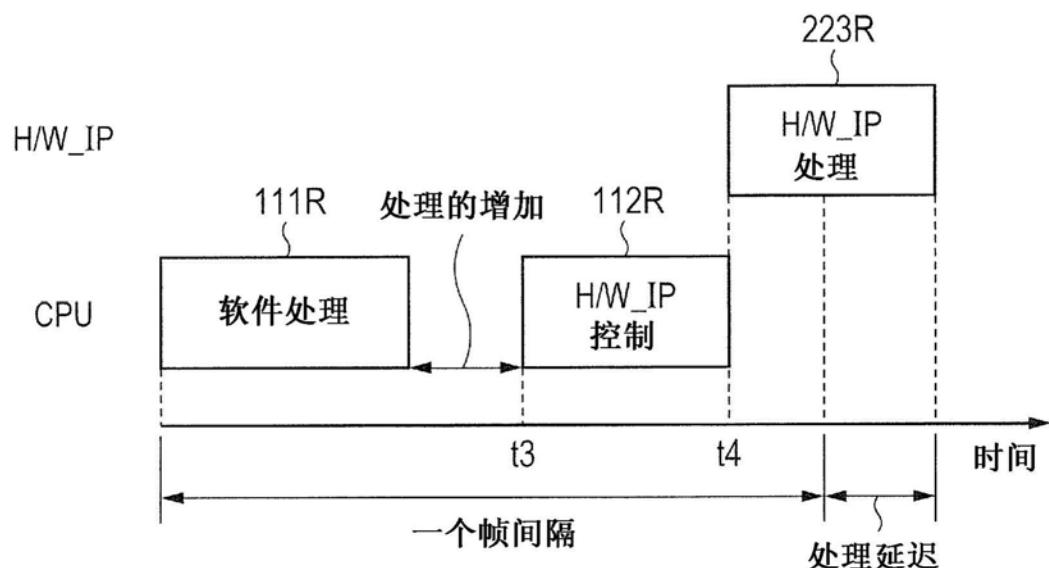

[0012] 图4是供在描述由图2的SoC中的控制时序的延迟引起的问题时使用的视图。

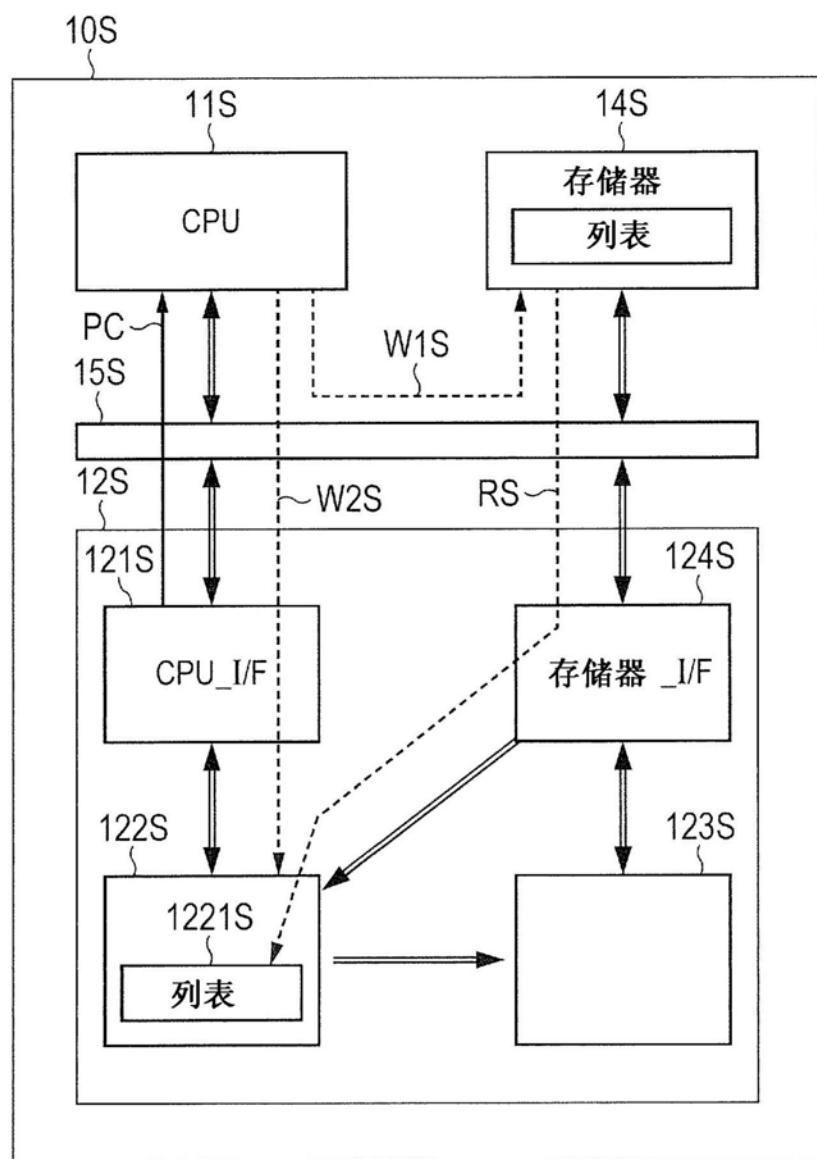

[0013] 图5是根据比较例2的供在描述SoC的结构时使用的框图。

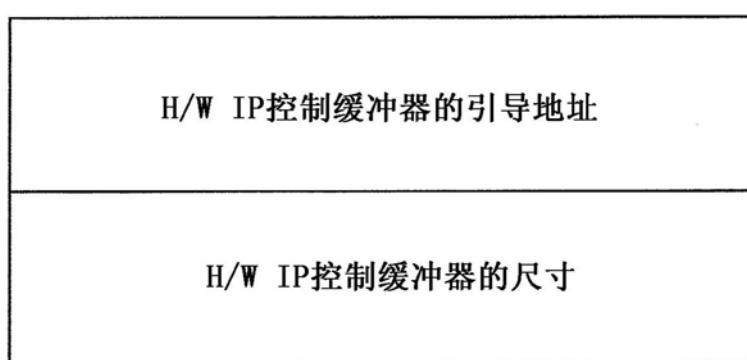

[0014] 图6是供在描述图5的SoC中的寄存器设置列表的访问信息时使用的视图。

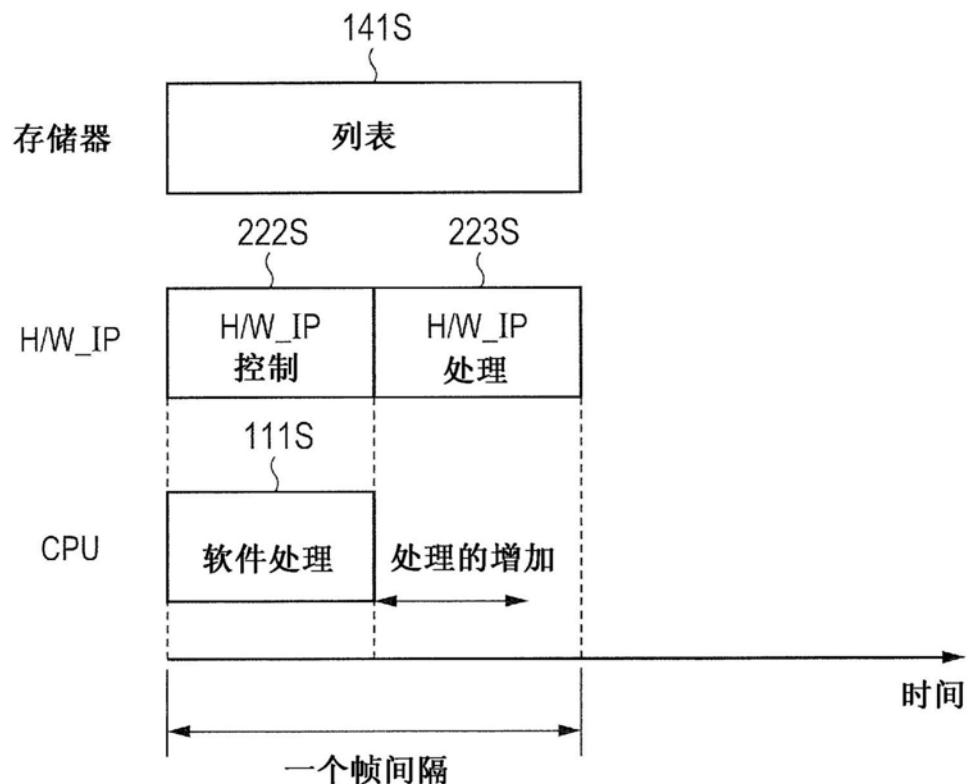

[0015] 图7是供在描述图5中的SoC中的控制时序时使用的视图。

[0016] 图8是供在描述用于改变图5的SoC中的寄存器设置列表的控制时序时使用的视图。

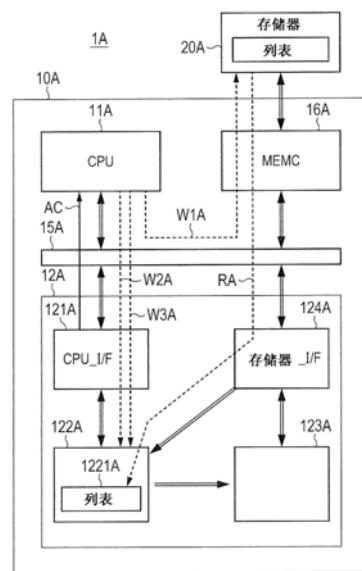

- [0017] 图9是供在描述根据第一实施例的系统的结构时使用的框图。

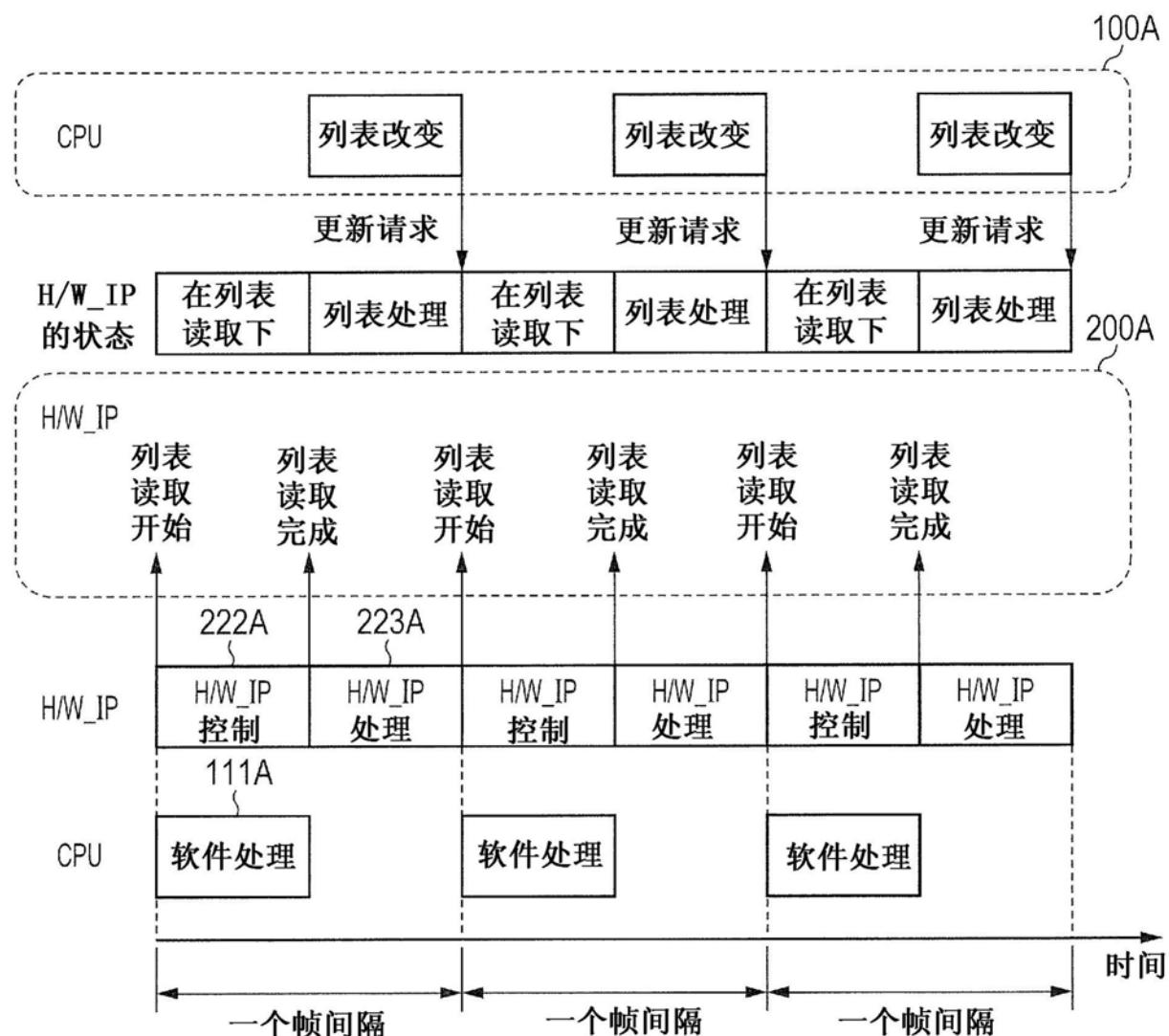

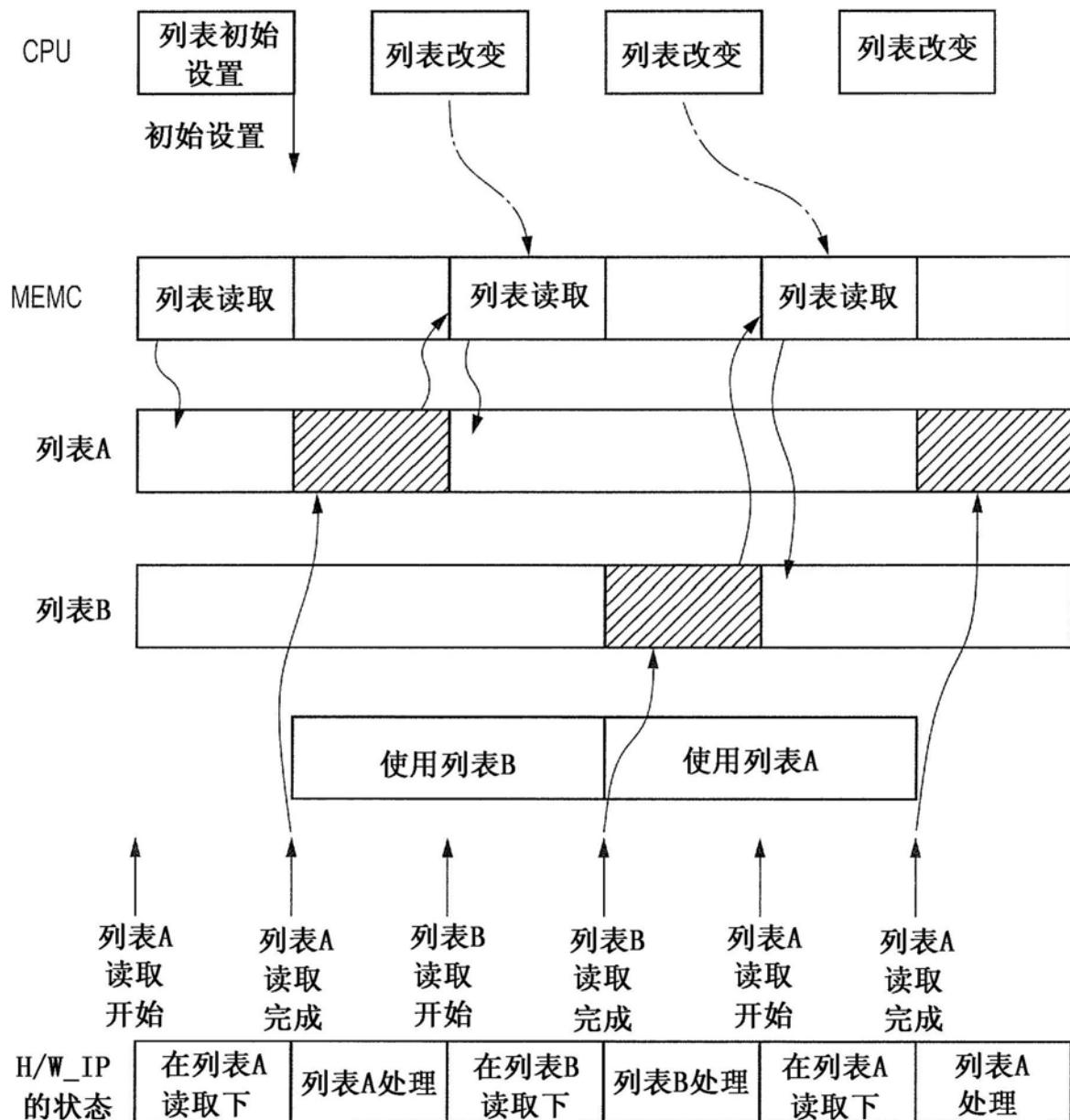

- [0018] 图10是供在描述图9中的SoC中的控制时序时使用的视图。

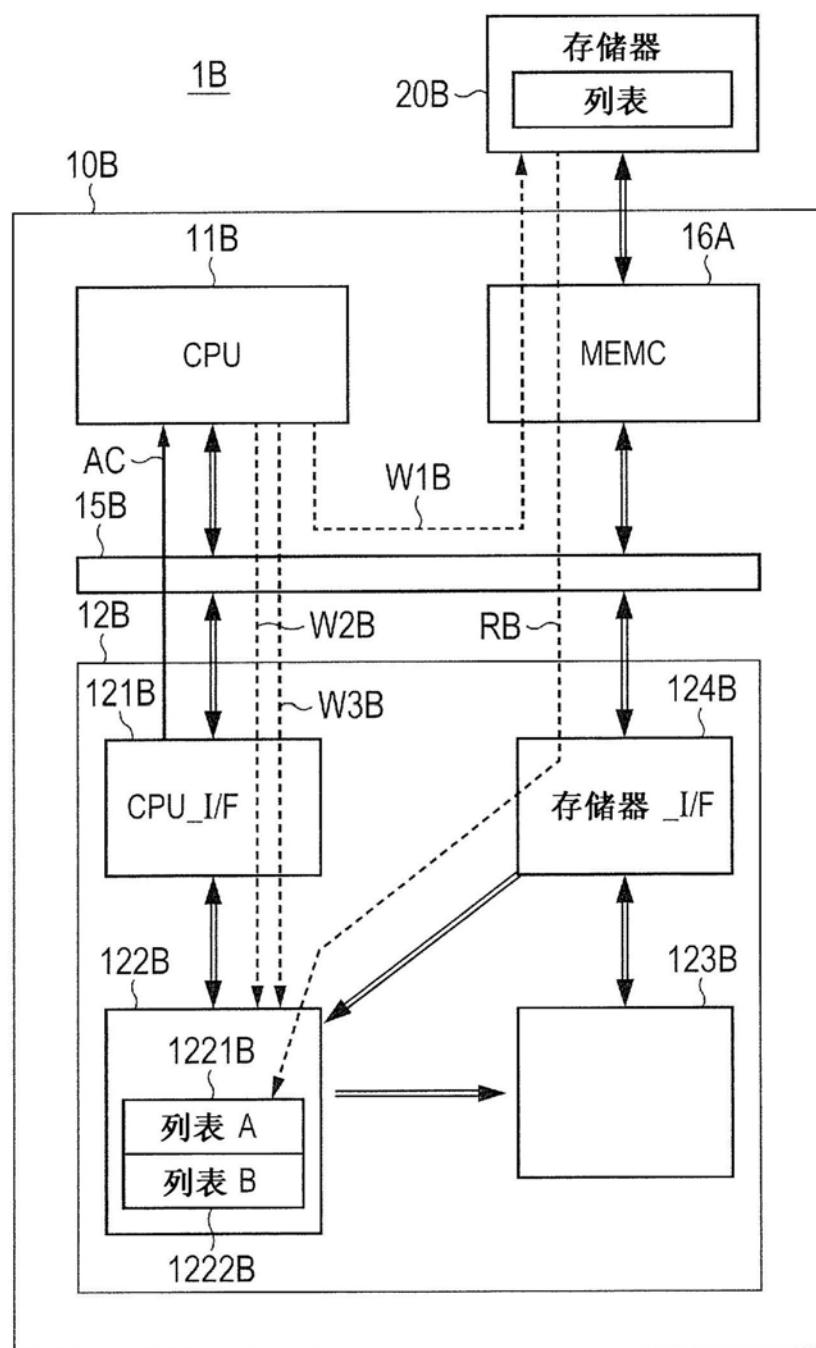

- [0019] 图11是供在描述根据第二实施例的系统的结构时使用的框图。

- [0020] 图12是供在描述图11中的SoC中的控制时序时使用的视图。

- [0021] 图13是供在描述图11的SoC中的缓冲器控制功能时使用的视图。

- [0022] 图14是供在描述根据第三实施例的系统的结构时使用的框图。

- [0023] 图15是供在描述图14中的SoC中的控制时序时使用的视图。

- [0024] 图16是供在描述图16的SoC中的缓冲器控制功能时使用的视图。

## 具体实施方式

[0025] 在下文中,将通过使用附图来描述实施例。在以下描述中,对相同的部件附着相同代码,并且可省略其重复描述。

[0026] 首先,将描述由本发明人等人研究的在本公开之前的技术(在下文中,称为比较例)。

[0027] 图1是供在描述SoC时使用的框图。SoC除中央处理单元(CPU)之外还包括H/W\_IP;因此,CPU需要不仅控制软件处理,而且控制H/W\_IP。软件处理包括普通处理和优先处理。普通处理对应于操作系统(OS)和线程处理中的过程。而优先处理是中断处理。例如,在用于处理视频和声音的SoC中,普通处理时间连同较高质量的图像和声音一起具有增加趋势。该优先处理时间根据安装在SoC上的H/W\_IP的数目的增加和来自每个H/W\_IP的中断的频率的增加而具有增加趋势。此外,H/W\_IP的控制时序的限制随着更快的速率而变得严重。例如,在60fps(每秒帧)的视频的情况下,一个帧是16.6ms(=1秒/60帧)。

[0028] <比较例1>

[0029] 如短划线箭头RS所示,H/W\_IP 12A通过存储器接口124A、总线15A和存储器控制器16A,从控制电路122A内的缓冲器1221A中的存储器20A读出寄存器设置列表。这是H/W\_IP控制122A。

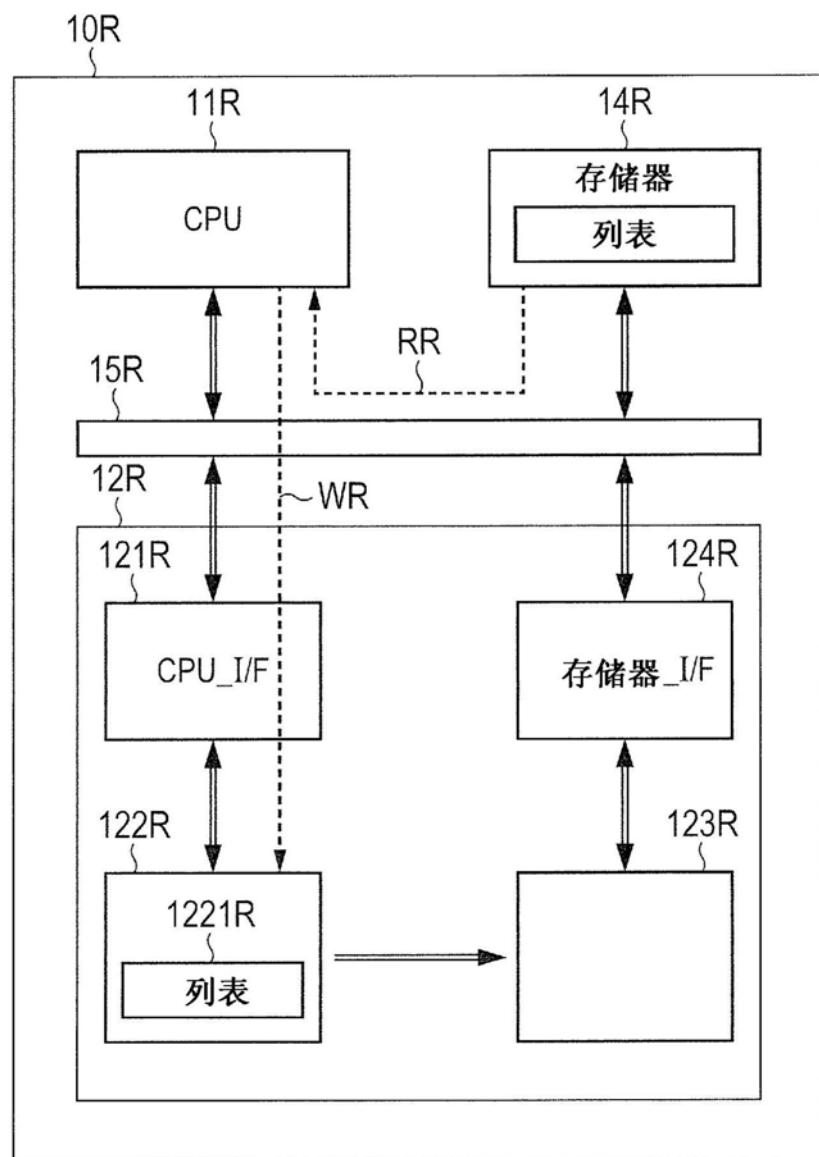

[0030] 图2是示出了根据比较例1的SoC的结构的框图。根据比较例1的SoC 10R包括CPU 11R、H/W\_IP 12R、存储器(MEMORY) 14R以及总线15R。H/W\_IP 12R包括CPU接口(CPU\_I/F) 121R、控制电路122R、处理电路123R以及存储器接口(MEMORY\_I/F) 124R。如短划线箭头RR和WR所示,CPU 11R通过总线15R从存储器14R读出寄存器设置列表,并且将寄存器设置列表写入H/W\_IP 12R的控制电路122R内的缓冲器1221R中。这是H/W\_IP控制122R。处理电路123R根据缓冲器1221R内的寄存器设置列表来处理数据,并通过存储器接口124R和总线15R在存储器14R与其本身之间发送和接收数据。

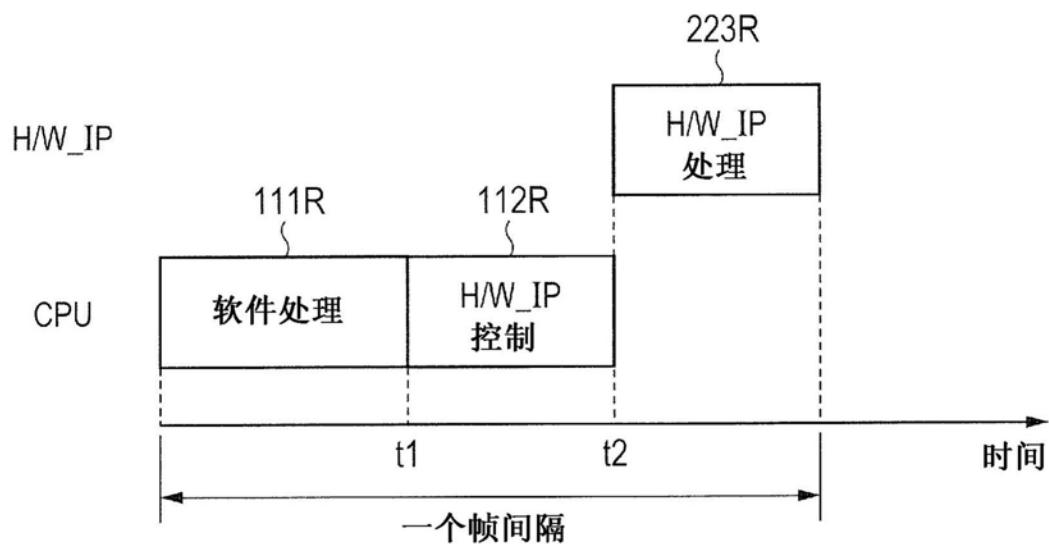

[0031] 图3是示出了比较例1中的SoC的控制时序的视图。在一个帧期间,CPU 11R执行用软件进行的从一个帧的开始至t1的处理(软件处理)111R和从t1至t2的用于控制H/W\_IP 12R的处理(H/W\_IP控制)112R,并且H/W\_IP 12R从t2至一个帧的结尾基于H/W\_IP控制来执行处理(H/W\_IP处理)223R。

[0032] 图4是示出了根据比较例1的由SoC中的控制时序的延迟引起的问题的视图。当软件处理111R的处理时间增加且H/W\_IP控制112R的开始时刻(t3)被延迟(t3>t1)时,H/W\_IP处理的开始时间(t4)被延迟(t4>t2),并且H/W\_IP处理223R在一个帧的结尾之前不结束,

从而引起问题。例如,当H/W\_IP控制112R的开始时间(t3)在用于处理视频和声音的SoC中被延迟时,视频和声音被干扰。

[0033] 作为上述问题的解决方案,可以考虑软件处理时间的减少;然而,软件尺寸被放大,并且除半导体装置制造者的开发——诸如用于OS或Soc的用户的定制开发区段——之外的软件尺寸被放大。因此,难以对增加处理时间施加限制,并且这不是切实可行的解决方法。将如下描述除软件处理时间减少之外的来自研究问题的解决方法的结果。

[0034] <比较例2>

[0035] 图5是示出了根据比较例2的SoC的结构的框图。图6是示出了根据比较例2的SoC中的寄存器设置列表的访问信息的视图。

[0036] 根据比较例2的SoC的H/W\_IP不受CPU控制,而是将控制其本身。根据比较例2的SoC 10S包括CPU 11S、H/W\_IP 12S、诸如静态随机存取存储器(SRAM)之类的存储器(MEMORY)14S以及总线15S。H/W\_IP 12S包括CPU接口(CPU\_I/F)121S、控制电路122S、处理电路123S以及存储器接口(MEMORY\_I/F)124S。如短划线箭头W1S所示,CPU 11S通过总线15S将寄存器设置列表写入到存储器14S中。如短划线箭头W2S所示,CPU 11S通过总线15S将存储器14S内的寄存器设置列表的访问信息写入到H/W\_IP 12S的缓冲器1221S中。如图6中所示,访问信息包括H/W\_IP控制缓冲器(寄存器设置列表)的引导地址和H/W\_IP控制缓冲器(寄存器设置列表)的尺寸。如短划线箭头RS所示,H/W\_IP 12S通过存储器接口124S和总线15S将寄存器设置列表从存储器14S读入到缓冲器1221S中。这是H/W\_IP控制222S。控制电路122S根据缓冲器1221S内的寄存器设置列表来控制H/W\_IP 12S。处理电路123S根据缓冲器1221S内的寄存器设置列表来处理数据,并且例如计算与存储器接口124S通过总线15S读取的存储器14S内的数据。存储器接口124S通过总线15S将所计算数据写入到存储器14S中。寄存器设置列表的内容取决于处理;例如,当在图像处理中执行图像放大时,寄存器设置列表的内容包括:输入图像的地址和尺寸;输出图像的地址和尺寸;放大因数;放大时的内插方法。

[0037] 图7是示出了根据比较例2的SoC中的控制时序的视图。在比较例2中,H/W\_IP 12S参考存储器14S中的由CPU 11S先前创建的寄存器设置列表141S以便H/W\_IP 12S控制其本身。据此,H/W\_IP控制222S可在预定时刻被开始,而不需要由CPU 11S进行的H/W\_IP控制,并不取决于软件处理111S的时刻以及由CPU 11S增加处理时间。然而,必须先前由CPU 11S创建寄存器设置列表;因此,H/W\_IP 12S是基于重复预定处理的前提。

[0038] 图8是示出了根据比较例2的用于改变SoC中的寄存器设置列表的控制时序的视图。H/W\_IP 12S在一个帧期间从存储器14S读取寄存器设置列表并执行相应处理。为了在由H/W\_IP 12S完成对寄存器设置列表的访问之前不重写寄存器设置列表,在接收到指示处理完成的处理完成信号(PC)之后,CPU 11S改变寄存器设置列表并将其写入存储器14S中。因此,在一个帧的时段内不能改变寄存器设置列表,但是不能连续地执行H/W\_IP 12S的处理。因此,当在处理的途中改变H/W\_IP 12S的寄存器设置列表时,应暂时停止H/W\_IP 12S的处理。据此,例如,当改变视频和声音的再现内容(视频尺寸和声音频率)时,视频和声音受到干扰。

[0039] <实施例>

[0040] CPU和H/W\_IP被设计成在时间共享时共享寄存器设置列表。虽然H/W\_IP不参考寄存器设置列表,但使得CPU能够重写寄存器设置列表。据此,在H/W\_IP继续处理的同时,使得

CPU能够改变H/W\_IP处理的内容,因此减少了由CPU对H/W\_IP的控制时序的限制。例如,在改变用于视频处理的H/W\_IP和用于声音处理的H/W\_IP的再现内容时,CPU可以改变H/W\_IP处理的内容而不产生视频和声音的干扰。

**[0041] 【第一实施例】**

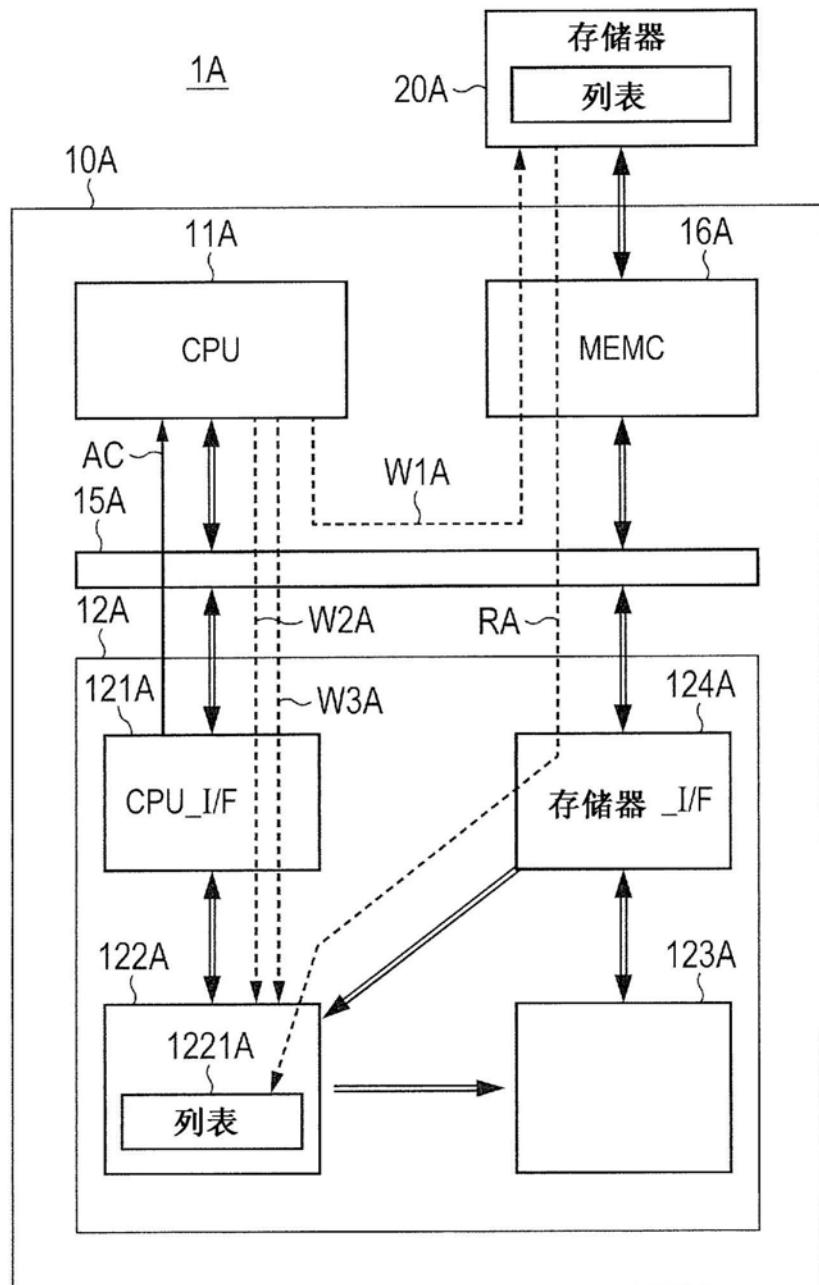

[0042] 图9是示出了根据第一实施例的系统的结构的框图。系统1A包括SoC 10A和存储器(MEMORY) 20A,诸如同步动态随机存取存储器(SDRAM)。SoC 10A是在一个半导体衬底上形成的半导体装置。存储器20A是在一个半导体衬底上形成的半导体装置。存储器20A可由多个半导体芯片形成。系统1A可以是通过将SoC 10A和存储器20A密封到一个封装中而形成的、或者通过将它们密封在独立的封装中并将它们安装在一个衬底上而形成的系统级封装(SiP)。系统1A也称为半导体装置。类似于比较例2,存储器20A可以是诸如内置在SoC 10A中的SRAM之类的存储器。

[0043] SoC 10A包括CPU 11A、H/W\_IP 12A、存储器控制器(MEMC) 16A以及总线15A。H/W\_IP 12A在预定时段(例如,在一个帧时段内16.6ms)内执行预定处理(例如,视频处理和声音处理),并且连续地按周期地执行该预定处理。H/W\_IP 12A包括CPU接口(CPU\_I/F) 121A、控制电路122A、处理电路123A以及存储器接口(MEMORY\_I/F) 124A。如短划线箭头W1A所示,CPU 11A通过总线15A和存储器控制器16A将寄存器设置列表写入到存储器20A中。如短划线箭头W2A所示,CPU 11A通过总线15A和存储器控制器16A将存储器14A内的寄存器设置列表的访问信息写入H/W\_IP 12A的控制电路122A中,类似于比较例2(图6)。H/W\_IP 12A通过存储器接口124A、总线15A以及存储器控制器16A将寄存器设置列表从存储器20A读入到控制电路122A的缓冲器1221A。这是H/W\_IP控制122A。缓冲器1221A可不在控制电路122A内,而是可例如在CPU接口121A与控制电路122A之间提供。控制电路122A根据缓冲器1221A内的寄存器设置列表来控制H/W\_IP 12A。处理电路123A根据缓冲器1221A内的寄存器设置列表来计算由存储器接口124A通过总线15A和存储器控制器16A读取的存储器14A内的数据(例如,视频数据和声音数据)。存储器接口124A通过总线15A和存储器控制器16A将所计算数据写入存储器14A中。控制电路122A生成关于存储器20A内的寄存器设置列表的通知访问开始(读取开始)和访问完成(读取完成)的信息,并且基于该信息的整体或一部分,CPU接口121A可以生成信号,例如访问完成信号(AC),并将该信号发射到CPU 11A。该信号可以是中断请求信号而不是排他性信号,诸如访问完成信号。寄存器设置列表的内容取决于处理,但是图像处理中的图像放大的情况下的寄存器设置列表与在比较例2中相同。

[0044] 图10是示出了根据第一实施例的用于改变SoC中的寄存器设置列表的控制时序的视图。H/W\_IP 12A在一个帧的前一半中将列表读取开始信息告知CPU 11A以从存储器20A读取寄存器设置列表(读取列表),并在读取完成时将列表读取完成信息告知CPU 11A,以在一个帧的后一半中执行相应处理(处理列表)。在接收到访问完成信号(AC)之后,CPU 11A改变存储器20A内的寄存器设置列表,并且如图9中的短划线箭头W3A所示,其将更新请求告知H/W\_IP 12A。短划线100A的该部分是被添加到比较例2的CPU功能(S/W\_IP功能),并且短划线200A的该部分是被添加到比较例2的H/W\_IP功能。

[0045] 根据第一实施例,在继续H/W\_IP 12A的处理的同时,使得CPU 11A能够改变H/W\_IP 12A的处理列表。据此,例如在改变视频和声音的再现内容时,可以减少视频和声音中的干扰的生成。然而,CPU 11A必须等待H/W\_IP 12A的列表未使用时段(列表读取完成)。结果,减

小了CPU被应用程序使用的时段。在列表每次更新时,CPU 11A必须向H/W\_IP 12A发布列表更新请求。因此,即使当列表被更新时,当CPU 11A在高负荷下延迟发布更新请求时,H/W\_IP 12A进行的列表更新时刻也被延迟。结果,例如,可能在高负荷下发生视频干扰和声音干扰。

**[0046] 【第二实施例】**

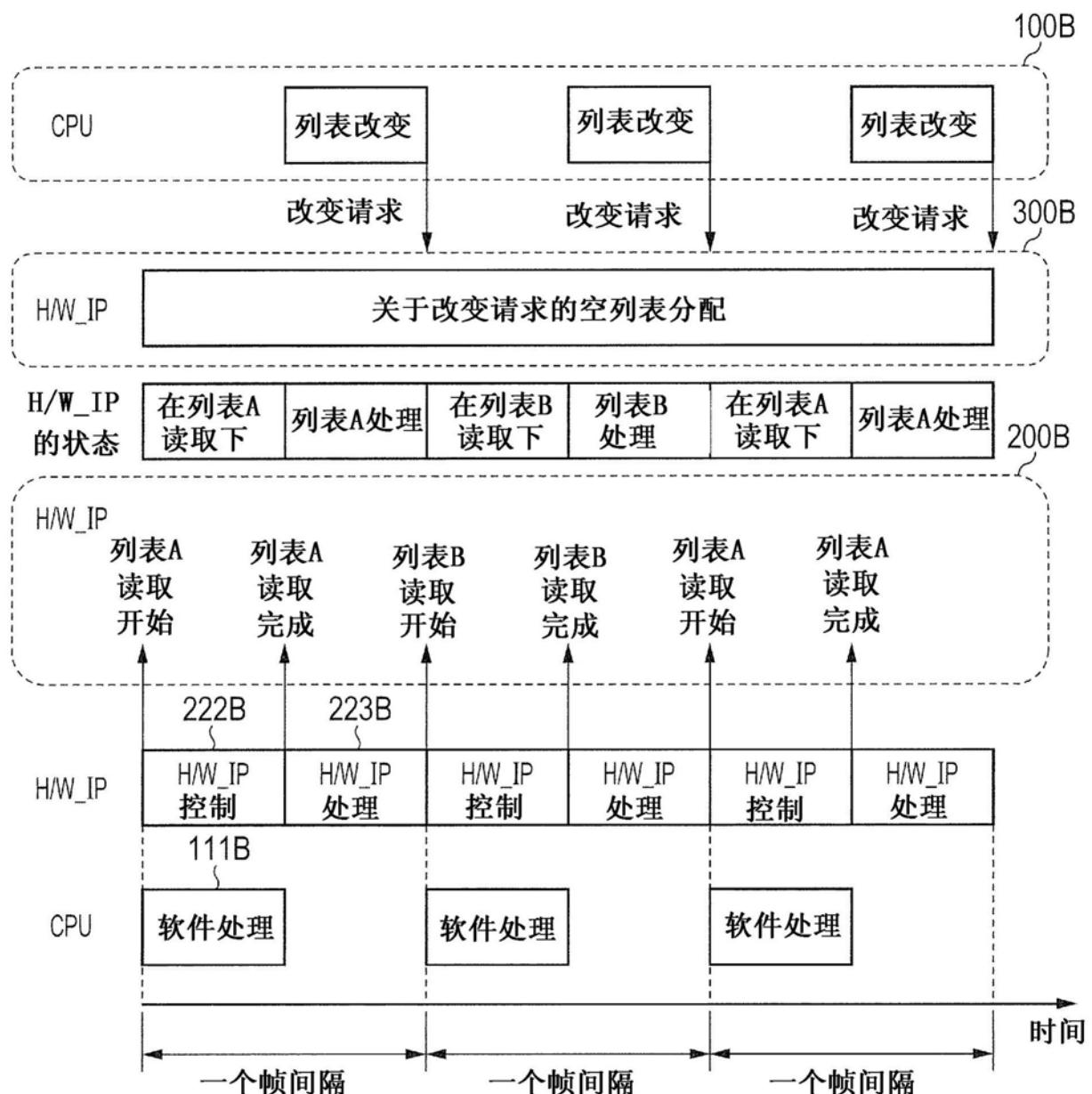

**[0047]** 图11是示出了根据第二实施例的系统的结构的框图。系统1B包括SoC 10B和存储器(MEMORY) 20B,诸如SDRAM。SoC 10B是在一个半导体衬底上形成的半导体装置。存储器20B是在一个半导体衬底上形成的半导体装置。存储器20B可由多个半导体芯片形成。系统1B可以是通过将SoC 10B和存储器20B密封到一个封装中而形成的或者可通过将它们密封到独立的封装中并将它们安装在一个衬底上而形成的SiP。系统1B也称为半导体装置。存储器20B可以是诸如内置在SoC 10B中的SRAM之类的存储器,类似于比较例2。

**[0048]** SoC 10B包括CPU 11B、H/W\_IP 12B、存储器控制器(MEMC) 16B以及总线15B。H/W\_IP 12B在预定时段(例如,16.6ms)内执行预定处理(例如,视频处理和声音处理),类似于H/W\_IP 12A,并且连续地按周期地执行该预定处理。H/W\_IP 12B包括CPU接口(CPU\_I/F) 121B、控制电路122B、处理电路123B以及存储器接口(MEMORY\_I/F) 124B。如短划线箭头W1B所示,CPU 11B通过总线15B和存储器控制器16B将寄存器设置列表写入存储器20B中。如短划线箭头W2B所示,CPU 11B通过总线15B和存储器控制器16B将存储器14B内的寄存器设置列表的访问信息写入到H/W\_IP 12B的控制电路122B中,类似于比较例2(图6)。如短划线箭头RB所示,H/W\_IP 12B通过存储器接口124B、总线15B以及存储器控制器16B将寄存器设置列表从存储器20B读入控制电路122B内的缓冲器1221B和1222B中。这是H/W\_IP控制112B。缓冲器1221B和1222B可不在控制电路122B内,而是可例如在CPU接口121B与控制电路122B之间提供。控制电路122B根据缓冲器1221B和1222B内的寄存器设置列表来控制H/W\_IP 12B。处理电路123B根据缓冲器1221B和1222B内的寄存器设置列表来计算由存储器接口124B通过总线15B和存储器控制器16B读取的存储器14B内的数据(例如,视频数据和声音数据)。存储器接口124B通过总线15B和存储器控制器16B将所计算数据写入存储器14B中。控制电路122B生成关于存储器20B内的寄存器设置列表的通知访问开始(读取开始)和访问完成(读取完成)的信息,并且基于该信息的整体或一部分,CPU接口121B可以生成信号,例如访问完成信号(AC),并将该信号发射到CPU 11B。其可以是中断请求信号而不是排他性信号,诸如访问完成信号。虽然寄存器设置列表的内容取决于处理,但是图像处理中的图像放大的情况下的寄存器设置列表与在比较例2中相同。使得H/W\_IP 12B能够使用多个类型的寄存器设置列表;因此,其包括例如容纳列表A的缓冲器1221B和容纳列表B的缓冲器1222B。

**[0049]** 图12是示出了根据第二实施例的用于改变SoC中的寄存器设置列表的控制时序的视图。H/W\_IP 12B在一个帧的前一半从存储器20B读取寄存器设置列表(读取列表A),并在一个帧的后一半执行相应处理(处理列表A)。CPU 11B在接收到访问完成信号(AC)之后改变寄存器设置列表。短划线100B的该部分是被添加到比较例2的CPU功能(S/W\_IP功能)。短划线200B的该部分是被添加到比较例2的H/W\_IP功能,类似于第一实施例的短划线200A。短划线300B的该部分是被添加到第一实施例的缓冲器控制功能。在短划线100B的该部分中,除添加到第一实施例的列表改变之外,还进一步添加到缓冲器控制功能(空列表分配功能)的改变请求发布。

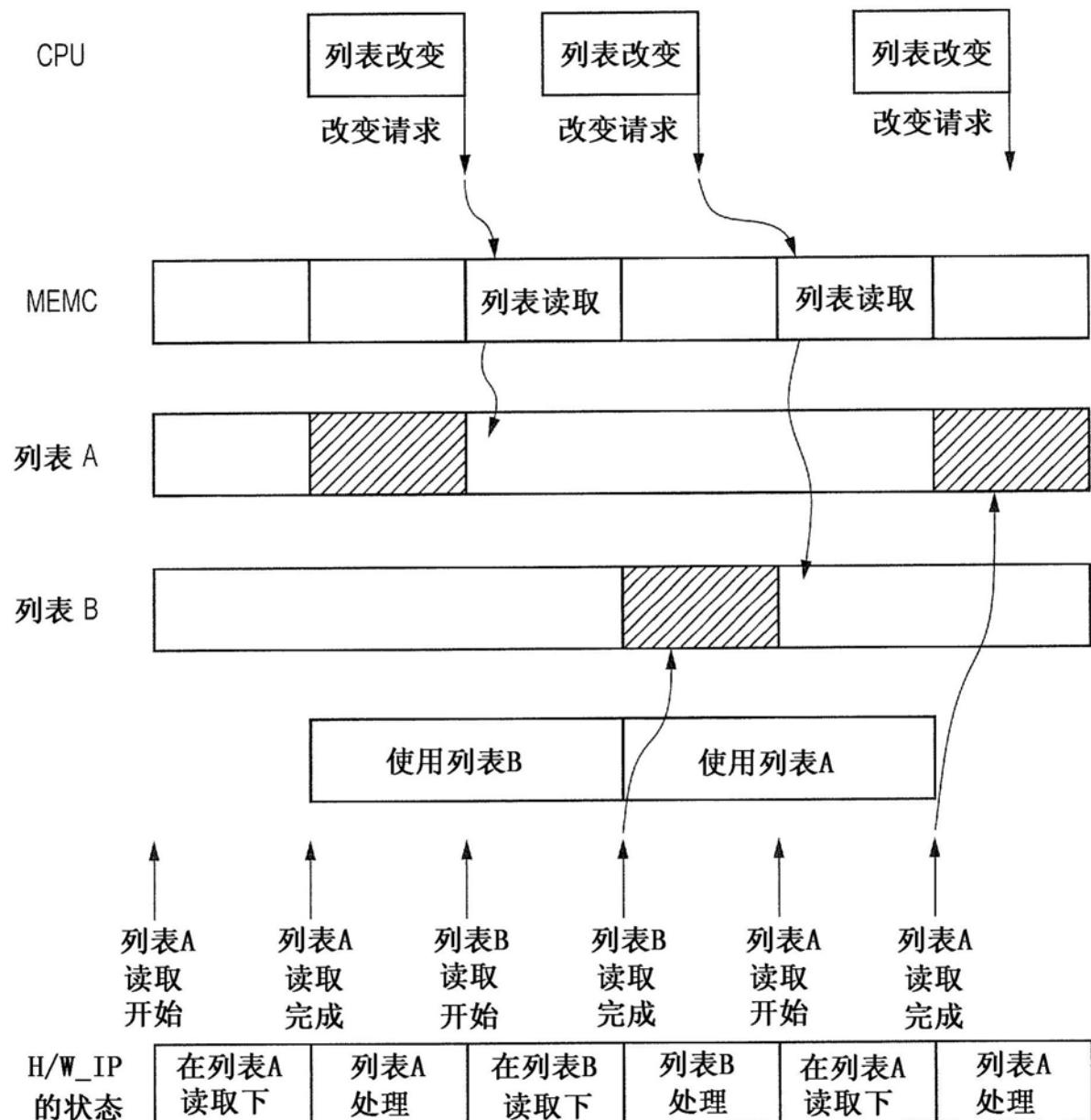

**[0050]** 图13是供在描述根据第二实施例的SoC中的缓冲控制功能时使用的视图。空列表

分配功能(缓冲器控制功能)是用于根据通知H/W\_IP 12B中的读取开始或读取完成的信息和/或来自CPU 11B的改变请求来控制列表的功能。例如,当通知了列表A的读取完成时,确定列表B正在被使用直至通知列表B的读取完成为止。当由CPU 11B提出改变请求时,如短划线箭头W3B所示,在从列表A的读取完成的通知到列表B的读取完成的通知的时段中,H/W\_IP 12B将存储器20B内的寄存器设置列表中的被CPU 11B改变的内容写入缓冲器1221B内的列表A中,并且在通知列表B的读取完成之后,其将供在控制单元122B的控制中使用的寄存器设置从列表A切换至列表B。在通知列表B的读取完成时,确定列表A正在被使用直至列表A的读取完成的通知为止。当由CPU 11B在从列表B的读取完成的通知到列表A的读取完成的通知的时段中提出改变请求时,H/W\_IP 12B将存储器20B内的寄存器设置列表中的被CPU 11B改变的内容写入到缓冲器1221B内的列表B中,并且在通知列表A的读取完成之后切换供在控制单元122B的控制中使用的寄存器设置列表。

[0051] 通过提供多个缓冲器并将列表数目从一个扩展至多个(列表A和B),CPU 11B可在H/W\_IP 12B参考列表的同时改变另一列表。据此,在继续H/W\_IP 12B的处理的同时,可以改变H/W\_IP 12B的处理内容。因此,例如,在改变视频和声音的再现内容时,可以抑制视频干扰和声音干扰的生成。此外,由于空列表分配功能,CPU 11B不必等待H/W\_IP 12B的列表未使用时段。结果,可以改善根据第一实施例的由CPU 11A使用应用程序的时段的减小。然而,不可能解决每当改变列表时必须向H/W\_IP 12B发布列表改变请求的问题。

[0052] **【第三实施例】**

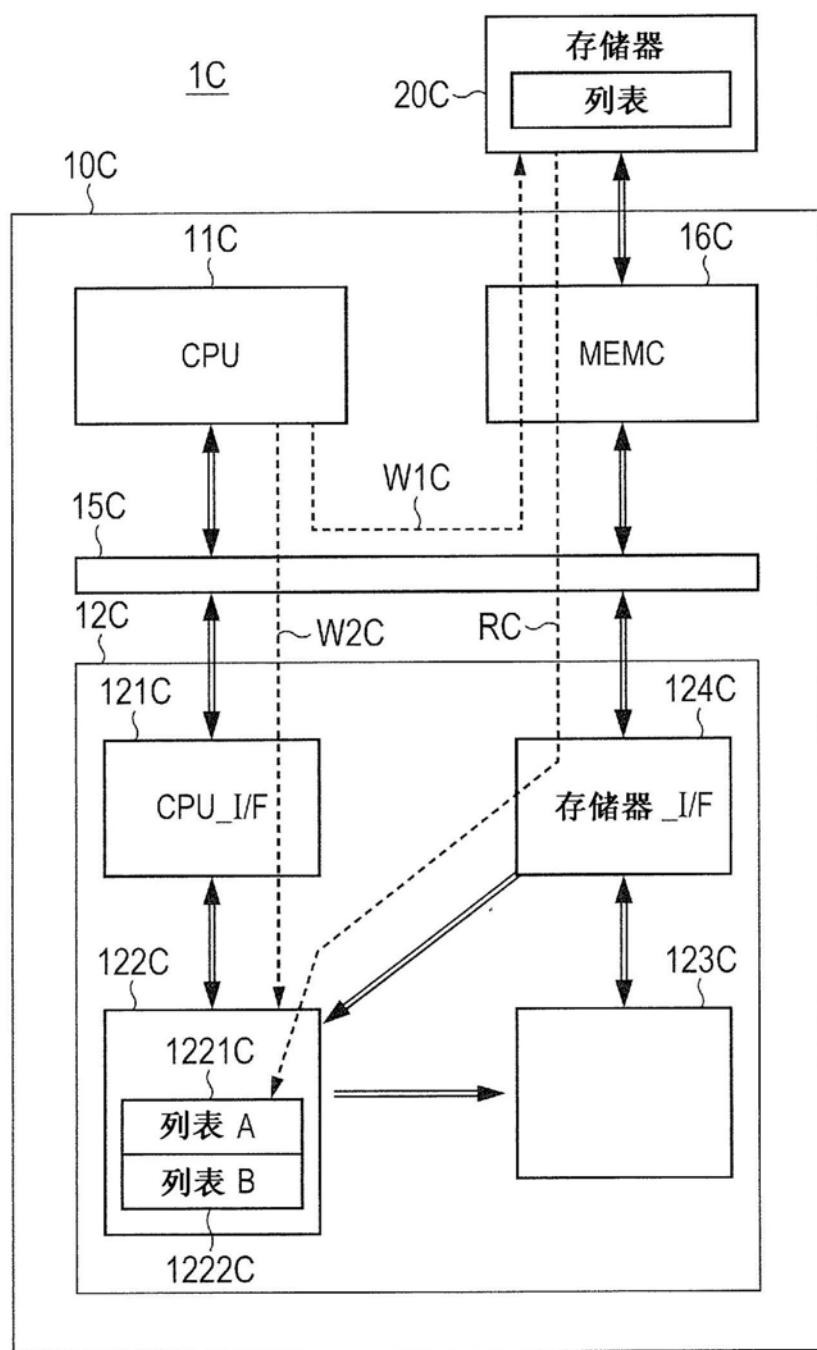

[0053] 图14是示出了根据第三实施例的系统的结构的框图。系统1C包括SoC 10C和存储器(MEMORY)20C,诸如SDRAM。SoC 10C是在一个半导体衬底上形成的半导体装置。存储器20C是在一个半导体衬底上形成的半导体装置。存储器20C可由多个半导体芯片形成。系统1C可以是通过将SoC 10C和存储器20C密封到一个封装中而形成的或者可通过将它们密封到独立的封装中并将它们安装在一个衬底上而形成的SiP。系统1C也称为半导体装置。存储器20C可以是诸如内置在SoC 10C中的SRAM之类的存储器,类似于比较例2。

[0054] SoC 10C包括CPU 11C、H/W\_IP 12、存储器控制器(MEMC)16C以及总线15C。H/W\_IP 12C在预定时段(例如,16.6ms)内执行预定处理(例如,视频处理和声音处理),类似于H/W\_IP 12A,并且连续地按周期地执行该预定处理。H/W\_IP 12C包括CPU接口(CPU\_I/F)121C、控制电路122C、处理电路123C以及存储器接口(MEMORY\_I/F)124C。如短划线箭头W1C所示,CPU 11C通过总线15C和存储器控制器16C将寄存器设置列表写入存储器20C中。如短划线箭头W2C所示,CPU 11C通过总线15C将存储器20C内的寄存器设置列表的访问信息写入到H/W\_IP 12C的控制电路122C,类似于比较例2(图6),作为初始设置。如短划线箭头RC所示,H/W\_IP 12C通过存储器接口124C、总线15C以及存储器控制器16C将寄存器设置列表从存储器20C读入控制电路122C内的缓冲器1221C和1222C中。这是H/W\_IP控制112C。缓冲器1221C和1222C可不在控制电路122C内,而是可例如在CPU接口121C与控制电路122C之间提供。控制电路122C根据缓冲器1221C和1222C的寄存器设置列表来控制H/W\_IP 12C。处理电路123C根据缓冲器1221C和1222C内的寄存器设置列表来计算由存储器接口124C通过总线15C和存储器控制器16C读取的存储器14C内的数据(例如,视频数据和声音数据)。存储器接口124C通过总线15C和存储器控制器16C将所计算数据写入存储器14C中。控制电路122C生成关于存储器20C内的寄存器设置列表的通知访问开始(读取开始)和访问完成(读取完成)的信息;然而,

不同于第一和第二实施例,CPU接口121C不生成访问完成信号也不将该信号发射到CPU 11C。使得H/W\_IP 12C能够使用多个类型的寄存器设置列表,并且包括,例如,容纳列表A的缓冲器1221C和容纳列表B的缓冲器1222C。寄存器设置列表的内容取决于处理,在图像处理中的图像放大的情况下的寄存器设置列表与比较例2中相同,并且此外,为了执行下一列表,添加诸如在完成列表处理之后是否继续、连续方法(重复同一列表或使用另一列表)以及在使用列表的情况下的列表的存储地址之类的内容。

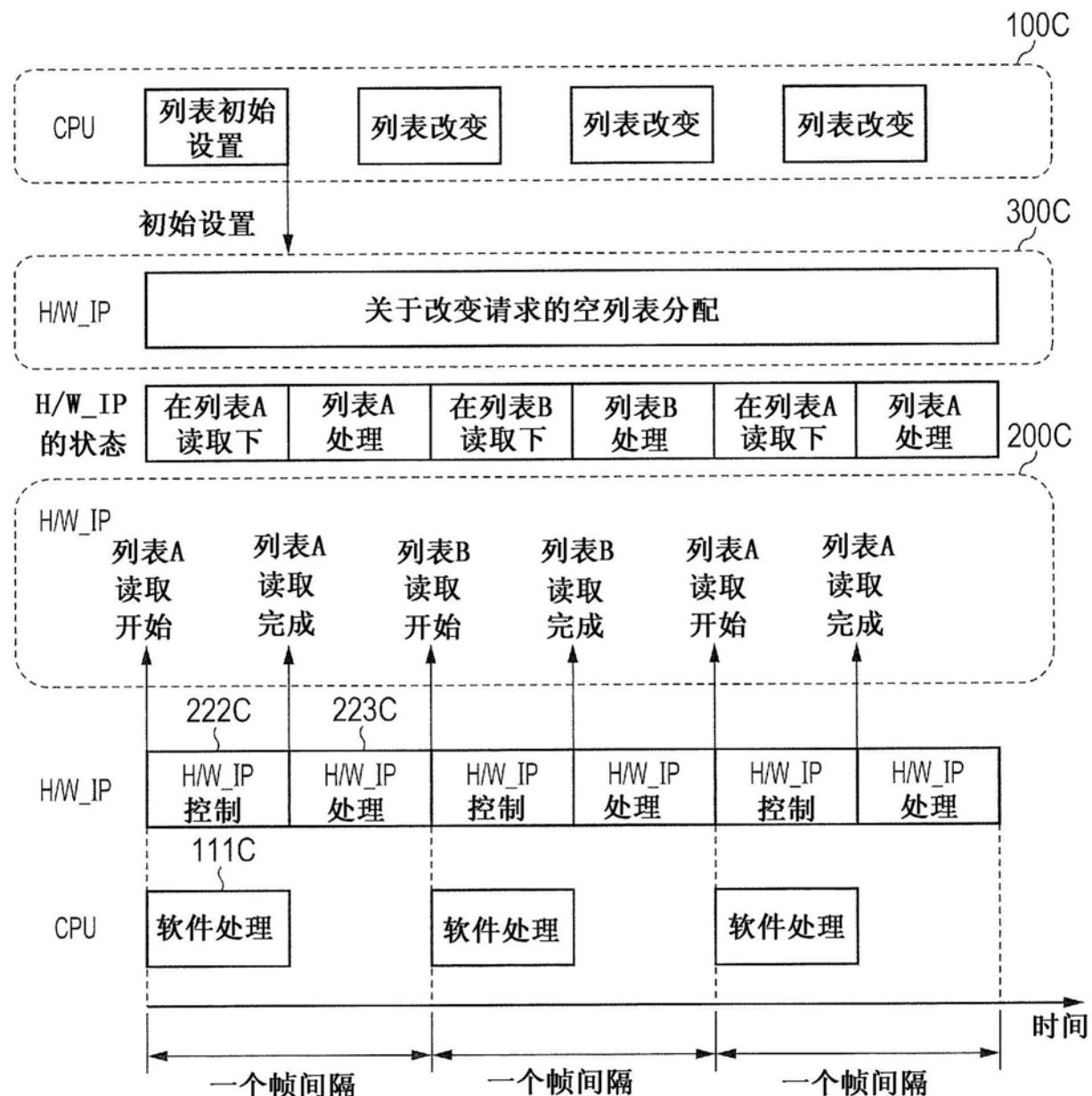

[0055] 图15是示出了根据第三实施例的用于改变SoC中的寄存器设置列表的控制时序的视图。H/W\_IP 12C在一个帧的前一半从存储器20C读取寄存器设置列表(读取列表A),并在一个帧的后一半执行相应处理(处理列表A)。短划线100C的该部分是被添加到比较例2的CPU功能(S/W\_IP功能)。短划线200C的该部分是被添加到比较例2的H/W\_IP功能,类似于第一实施例的短划线200A。短划线300C的该部分是被添加到第一实施例的缓冲器控制功能。在短划线100C的该部分中,除第一实施例中的列表改变之外,添加到缓冲器控制功能(孔列表分配功能)的改变请求发布。CPU 11C与H/W\_IP 12C异步地改变寄存器设置列表。

[0056] 图16是供在描述根据第三实施例的SoC中的缓冲控制功能时使用的视图。根据第三实施例的空列表分配功能(缓冲器控制功能)是根据通知H/W\_IP 12C中的读取开始或读取完成的信息和寄存器设置列表的访问信息来控制列表的功能。例如,当通知了列表A的读取完成时,确定列表B正在被使用直至通知列表B的读取完成为止。当从寄存器设置列表提出访问请求时,在从列表A的读取完成的通知到列表B的读取完成的通知的时段期间,H/W\_IP 12C将存储器20C内的寄存器设置列表中的被CPU 11C改变的内容写入缓冲器1221C内的列表A中,并且在通知列表B的读取完成之后,其将供在控制单元122C的控制中使用的寄存器设置从列表A切换至列表B。当通知了列表B的读取完成时,确定列表A正在被使用直至通知列表A的读取完成为止。当由寄存器设置列表提出访问请求时,在从列表B的读取完成的通知到列表A的读取完成的通知的时段期间,H/W\_IP 12C将存储器20C内的寄存器设置列表中的被CPU 11C改变的内容写入缓冲器1222C内的列表B中,并且在通知列表A的读取完成之后,其将供在控制单元122C的控制中使用的寄存器设置从列表A切换至列表B。

[0057] 在第二实施例中,CPU 11B必须向H/W\_IP 12B发布列表更新请求,并且在由H/W\_IP 12B的缓冲器控制功能进行的处理期间,CPU 12B必须等待H/W\_IP 12B的处理。然而,在第三实施例中,H/W\_IP 12C并不用来自CPU 11C的请求而是根据列表的所述内容来更新列表,因此将使得列表更新时刻在CPU 11C与H/W\_IP 12C之间完全异步。据此,CPU 11C不必等待,而H/W\_IP 12C可以在没有延迟的情况下更新列表。此外,用被添加到H/W\_IP 12C的空列表分配功能,CPU 11C不必等待H/W\_IP 12C的列表未使用时段。据此,类似于第二实施例,可以改善应用程序可用时间的减少。此外,CPU 11C不必每当更新列表时向H/W\_IP 12C发布列表更新请求。因此,可以解决CPU必须等待处理请求的完成直至H/W\_IP接受列表请求为止的问题。

[0058] 如上所述,虽然已基于实施例具体地描述了由本发明人等人完成的发明,但不用说,本发明不限于上述实施例,而是可以有各种修改。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16