(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-294514

(P2007-294514A)

(43) 公開日 平成19年11月8日(2007.11.8)

| (51) Int.CI.                 | F 1        |   | テーマコード (参考) |

|------------------------------|------------|---|-------------|

| <b>H01L 21/822</b> (2006.01) | H01L 27/04 | C | 5 F 03 3    |

| <b>H01L 27/04</b> (2006.01)  | H01L 21/90 | D | 5 F 03 8    |

| <b>H01L 21/768</b> (2006.01) | H01L 21/90 | B |             |

| <b>H01L 23/522</b> (2006.01) |            |   |             |

審査請求 未請求 請求項の数 2 O L (全 14 頁)

|           |                              |          |                                                 |

|-----------|------------------------------|----------|-------------------------------------------------|

| (21) 出願番号 | 特願2006-117720 (P2006-117720) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区大手町二丁目6番2号 |

| (22) 出願日  | 平成18年4月21日 (2006.4.21)       | (74) 代理人 | 100089233<br>弁理士 吉田 茂明                          |

|           |                              | (74) 代理人 | 100088672<br>弁理士 吉竹 英俊                          |

|           |                              | (74) 代理人 | 100088845<br>弁理士 有田 貴弘                          |

|           |                              | (72) 発明者 | 河野 祐一<br>東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内       |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】M I M構造のキャパシタをダマシン工程を利用して形成する場合に、ディッキングやエロージョンの発生により、キャパシタが不良になることを防止した半導体装置を提供する。

【解決手段】電極溝 11 c 上にビアホール開口用の開口部OP 1を、また、キャパシタ形成領域外に設けられた配線層9 bの上方部に対応する位置の層間絶縁膜6上に配線層9 bとの接続のためのビアホール開口用の開口部OP 2を形成する。このとき、開口部OP 1の開口直径は、開口部OP 2よりも大きく設定するものとし、例えば開口部OP 2の直径が0.36 μmであるならば、開口部OP 1の開口直径は0.38 μmに設定する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

半導体基板の上方に配設された層間絶縁膜と

前記層間絶縁膜の上層部に配設された下部電極と、

前記下部電極上に配設された誘電体膜と、

前記誘電体膜を間に挟んで前記下部電極に対向して配設された上部電極とを有したキャパシタを備え、前記下部電極は、その底部から前記半導体基板の正面に垂直な方向に前記層間絶縁膜を貫通するように設けられたコンタクトプラグと一体をなす半導体装置であって、

前記コンタクトプラグの直径は、前記層間絶縁膜を前記半導体基板の正面と垂直な方向に貫通するように設けられた他のコンタクトプラグの直径よりも広く形成される、半導体装置。

**【請求項 2】**

前記コンタクトプラグの直径は、前記他のコンタクトプラグの直径の1.05倍以上である、請求項1記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置に関し、特にMIM(Metal Insulator Metal)構造のキャパシタを有する半導体装置に関する。

**【背景技術】****【0002】**

通信用LSIや高速CMOSロジックデバイスでは、高速動作の実現のため、層間絶縁膜の低誘電率化とダマシン(Damascene)法を用いた銅(Cu)配線の使用が一般化しつつある。また、通信用LSIや高速CMOSロジックデバイスでは、アナログ回路中にMIM構造のキャパシタを有することが一般的である。

**【0003】**

ダマシン法は、層間絶縁膜中に配線用の溝および/またはコンタクトプラグ用のホールを形成し、その中に銅を埋め込んだ後、不要な部分の銅をCMP(Chemical Mechanical Polishing)により取り除く手法であり、配線またはコンタクトプラグを別個に形成するシングルダマシンと、配線およびコンタクトホールを同時に形成するデュアルダマシンがある。

**【0004】**

どちらを採用する場合でもCMPは必須であり、コンタクトプラグに比べて面積の大きな配線の形成に際しては、研磨時にディッシングやエロージョンという現象が発生する。

**【0005】**

ディッシングは、CMPで使用する研磨パッドが変形して配線の断面形状が皿状に窪むような現象であり、エロージョンは配線が密集する部分において配線の表面だけでなく層間絶縁膜の表面も併せて研磨される現象である。

**【0006】**

例えば特許文献1では、CMPの研磨条件を適切に選択することでディッシングやエロージョンの発生を防止することが開示されている。

**【0007】****【特許文献1】特開2004-14828号公報****【発明の開示】****【発明が解決しようとする課題】****【0008】**

最近では、MIM構造のキャパシタもダマシン工程を利用して形成する技術が開発されているが、キャパシタの電極は配線に比べてもさらに面積が広いので、ディッシングやエロージョンの問題についてはより深刻であるが、上記特許文献1にはMIM構造のキャパ

10

20

30

40

50

シタに関する記載はない。

【0009】

本発明は上記のような問題点を解消するためになされたもので、MIM構造のキャパシタをダマシン工程を利用して形成する場合に、ディッシングやエロージョンの発生により、キャパシタが不良になることを防止した半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明に係る請求項1記載の半導体装置は、半導体基板の上方に配設された層間絶縁膜と、前記層間絶縁膜の上層部に配設された下部電極と、前記下部電極上に配設された誘電体膜と、前記誘電体膜を間に挟んで前記下部電極に対向して配設された上部電極とを有したキャパシタを備え、前記下部電極は、その底部から前記半導体基板の主面に垂直な方向に前記層間絶縁膜を貫通するように設けられたコンタクトプラグと一緒にをなす半導体装置であって、前記コンタクトプラグの直径は、前記層間絶縁膜を前記半導体基板の主面と垂直な方向に貫通するように設けられた他のコンタクトプラグの直径よりも広く形成される。

10

【発明の効果】

【0011】

本発明に係る請求項1記載の半導体装置によれば、下部電極の底部から半導体基板の主面に垂直な方向に層間絶縁膜を貫通するように設けられたコンタクトプラグ直径を、他のコンタクトプラグの直径よりも広く形成することで、下部電極の製造時のフォトリソグラフィのフォーカスマージンが大きくなり。下部電極形成用の電極溝をより深く形成してもコンタクトプラグの形成に不具合が生じることがない。このため、電極溝の深さで規定される下部電極の厚さが厚くなり、CMPによる過剰研磨で、ディッシングやエロージョンが発生し、下部電極の表面が皿状に窪んでも、下部電極の厚さがディッシングやエロージョンによる過剰研磨量に比べて十分厚いので、下部電極が局所的にでも完全に除去されることはなく、キャパシタに不具合が生じることが防止される。

20

【発明を実施するための最良の形態】

【0012】

<はじめに>

本発明に係る実施の形態の説明に先立って、MIM構造のキャパシタに発生するディッシングについて説明する。

30

【0013】

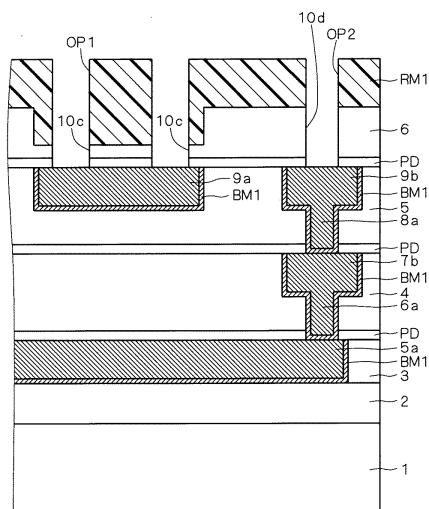

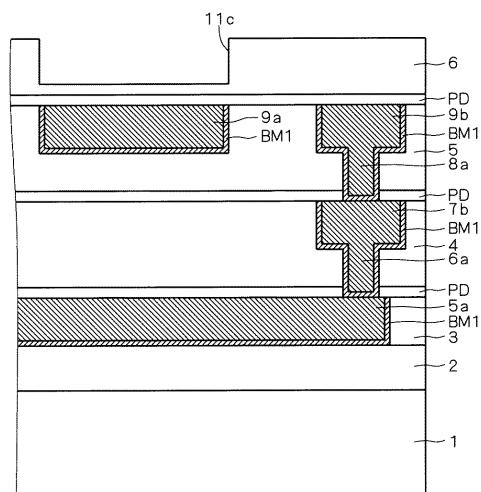

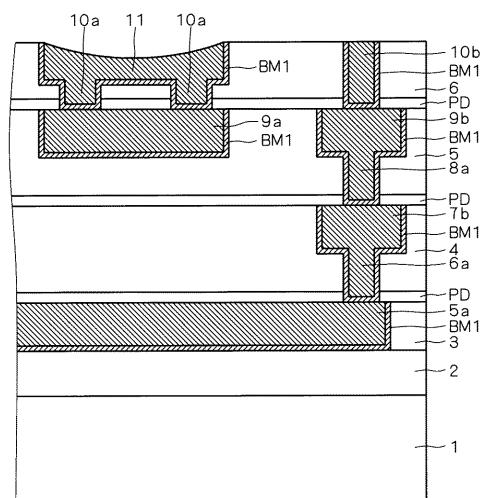

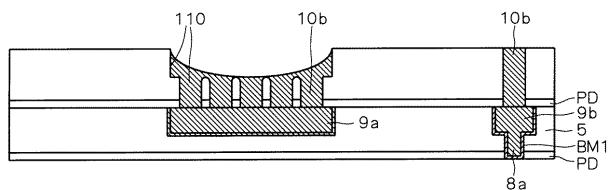

図1は、本発明を適用しない場合のMIM構造のキャパシタを有する半導体装置90を示す断面図である。

【0014】

図1に示すように、シリコン基板等の半導体基板1上に、例えばCVD法により形成されたシリコン酸化膜(SiO<sub>2</sub>)で構成される層間絶縁膜2が配設されている。

40

【0015】

ここで、図1においては半導体基板1上には半導体素子が形成されていない例を示しているが、同じ半導体基板1上の他の部分ではMOSトランジスタ等の半導体素子が形成されており、当該半導体素子を覆うために層間絶縁膜2が設けられている。

【0016】

また、層間絶縁膜2上には、例えばCVD法により形成されたSiOC等で構成される層間絶縁膜3が配設され、層間絶縁膜3の表面内には銅の配線層5aが配設されている。層間絶縁膜3はSiOCに限定されるものではなく、SiC膜などの、いわゆるLow-k膜と呼称される膜であれば良い。もちろん、シリコン酸化膜等の比較的誘電率の高い膜でも良い。

【0017】

配線層5aはダマシン法により形成され、配線層5aはバリアメタル膜BM1で囲まれている。

50

## 【0018】

バリアメタル膜BM1は、下側からTaN(窒化タンタル)、Ta(タンタル)、Ti(チタン)、TiN(窒化チタン)の順に積層された多層膜、あるいはTa(タンタル)、TaN(窒化タンタル)の順に積層された多層膜、あるいはTi(チタン)、TiN(窒化チタン)の順に積層された多層膜で構成される。

## 【0019】

層間絶縁膜3上には、例えばSiN膜等の絶縁膜で構成され、Cuの拡散を防止する拡散防止絶縁膜PDが配設される。なお、拡散防止絶縁膜PDは機械的強度の低いSiOCの層間絶縁膜を保護する保護膜(キャップ絶縁膜)としても機能し、シリコン酸化膜を用いる場合もある。10

## 【0020】

拡散防止絶縁膜PD上にはSiOC等で構成される層間絶縁膜4が配設され、層間絶縁膜4の上層部には銅の配線層7bが配設され、層間絶縁膜4の下層部には層間絶縁膜4および拡散防止絶縁膜PDを貫通して配線層7bと配線層5aとを電気的に接続するコントラクトプラグ6aが設けられている。なお、配線層7bとコントラクトプラグ6aとはデュアルダマシンにより形成され、両者は一体となっており、両者はバリアメタル膜BM1で囲まれている。コントラクトプラグ6aの直径は0.36μmに設定されている。

## 【0021】

層間絶縁膜4上には、拡散防止絶縁膜PDが配設され、拡散防止絶縁膜PD上にはSiOC等で構成される層間絶縁膜5が配設されている。そして、層間絶縁膜5の上層部には銅の配線層9aおよび9bが複数配設され、配線層9bは、層間絶縁膜5および拡散防止絶縁膜PDを貫通して配線層7bに達するコントラクトプラグ8aによって、配線層7bと電気的に接続される構成となっている。なお、配線層9bとコントラクトプラグ8aとはデュアルダマシンにより形成され、両者は一体となっており、配線層9a、9bおよびコントラクトプラグ8aはバリアメタル膜BM1で囲まれている。なおコントラクトプラグ8aの直径は0.36μmに設定されている。20

## 【0022】

層間絶縁膜5上には、拡散防止絶縁膜PDが配設され、拡散防止絶縁膜PD上にはシリコン酸化膜等で構成される層間絶縁膜6が配設されている。

## 【0023】

そして、層間絶縁膜6の上層部にはCVD法で形成されたタンゲステン(W)で構成されるキャパシタの下部電極110(設定深さ約250nm)が配設され、下部電極110は、層間絶縁膜6および拡散防止絶縁膜PDを貫通して配線層9aに達する複数のコントラクトプラグ10bによって、配線層9aと電気的に接続される構成となっている。なお、コントラクトプラグ10bの直径は0.36μmに設定されている。30

## 【0024】

ここで、下部電極110とコントラクトプラグ10bとはデュアルダマシンにより形成され、両者は一体となっている。

## 【0025】

また、層間絶縁膜6および拡散防止絶縁膜PDを貫通して配線層9bに達するコントラクトプラグ10bが配設され、コントラクトプラグ10b上には上層配線14が設けられている。なお、下部電極110、コントラクトプラグ10bはバリアメタル膜BM1で囲まれている。40

## 【0026】

ここで、図1に示すように、下部電極110の表面はディッシングによって皿状に窪んでおり、中央部では殆ど電極が残っていない状態となっている。

## 【0027】

そして、下部電極110上を覆うように、例えばシリコン窒化膜で構成されるキャパシタ誘電体膜12が配設されているが、下部電極110の窪みに合わせてキャパシタ誘電体膜12も窪んでいる。50

## 【0028】

さらに、キャパシタ誘電体膜12上には、例えばTiN膜で構成されるキャパシタの上部電極13が配設されおり、上部電極13およびキャパシタ誘電体膜12を覆うように、例えばアルミニウム膜（あるいはCu膜）で構成される最上層配線14が配設されている。またコントラクトプラグ10b上にも最上層配線14が選択的に配設されている。

## 【0029】

このように、ディッキングあるいはエロージョンにより下部電極110が削られると、場合によっては層間絶縁膜6が露出あるいは露出に近い状態になるが、その場合、本来ならばタンクスティン膜と界面を形成するキャパシタ誘電体膜12が、層間絶縁膜6と界面を形成する可能性があり、界面状態が変わることで、キャパシタが耐圧不良を起こす可能性がある。10

## 【0030】

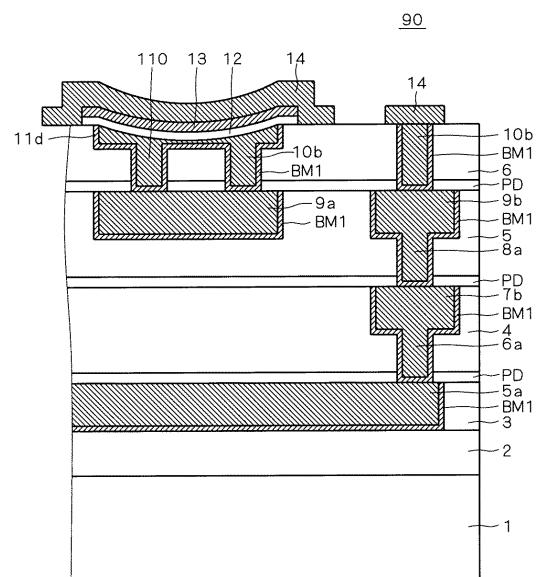

ここで、ディッキングあるいはエロージョンにより、下部電極110がどの程度削られるかについて図2に示すモデルを用いて説明する。

## 【0031】

図2は、下部電極110の形成後の断面形状を示す図であり、便宜的に下部電極110だけを示している。

## 【0032】

図2においては、下部電極110をCMPにより研磨する前の、層間絶縁膜6に下部電極110形成用の電極溝を設けた段階の層間絶縁膜6の主面SF1の位置を破線で示しており、上記電極溝の深さ、すなわち主面SF1から電極溝の中央部底面までの長さを下部電極深さAとする。20

## 【0033】

また、バリアメタル膜BM1の厚さをバリアメタル厚さBとし、CMPによりタンクスティン膜とともに除去された層間絶縁膜6の厚さを層間絶縁膜切削厚さCとする。

## 【0034】

CMP後の層間絶縁膜6の主面SF2と下部電極110の中央部との段差をディッキング量Dとし、下部電極110の中央部の厚さ（バリアメタル膜BM1含まず）を残膜量Eとする。

## 【0035】

ここで、下部電極110の設定深さを250nmとする場合のディッキングの一例について、中央部を例に採って説明するなら、下部電極深さAが245nm（実測値）、バリアメタル厚さBは88nm（断面SEM写真からの計測値）、層間絶縁膜切削厚さCは33nm（A - (B + E)により算出）、ディッキング量Dは33nm（A - (B + E)により算出）、残膜量Eは124nmとなる。30

## 【0036】

このように、ディッキングにより下部電極110中央部の厚さは設定値の半分程度となってしまうが、キャパシタは複数設けられ、エロージョンの影響も含めると、下部電極110の厚さがマイナス、すなわち、完全に除去されてしまうものもある。

## 【0037】

先に説明したように、局所的にせよ下部電極110が完全に除去されてしまうとキャパシタが耐圧不良を起こす可能性がある。

## 【0038】

発明者達はディッキングやエロージョンの発生により、下部電極が完全に除去されてしまうことを防止した半導体装置を開発したので、以下に当該構成について説明する。40

## 【0039】

## &lt;実施の形態1&gt;

まず発明者達は、下部電極が完全に除去される部分が発生するのを防止するには、下部電極の厚みを増せば良いという技術思想を得た。しかし、発明者達の採用する下部電極の製造方法は、デュアルダマシンの中でも電極形成用の電極溝を最初に形成するトレンチフ50

アーストという手法であり、この場合、最初に深い溝を形成すると、次に、ビア(via)ホールを形成する際にフォトリソグラフィによりレジストを感光するときのフォーカス位置が、深くなってしまうが、フォトリソグラフィ装置の焦点深度(DOF)の調整範囲(フォーカスマージン)にも制限があり、電極用の溝を深くするとビアホールの直径が設計通りに形成できず、下層配線とのコンタクトが確実にできないという問題があった。

#### 【0040】

発明者達は当該問題を解消する有効な構成に想到したので、以下、本発明に係る実施の形態1において説明する。

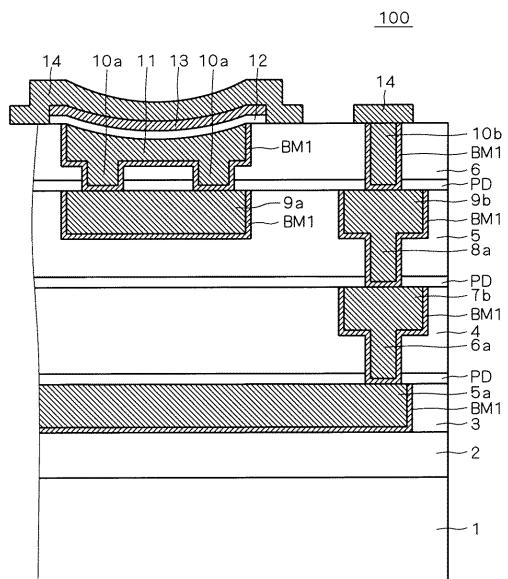

#### 【0041】

##### < 製造方法 >

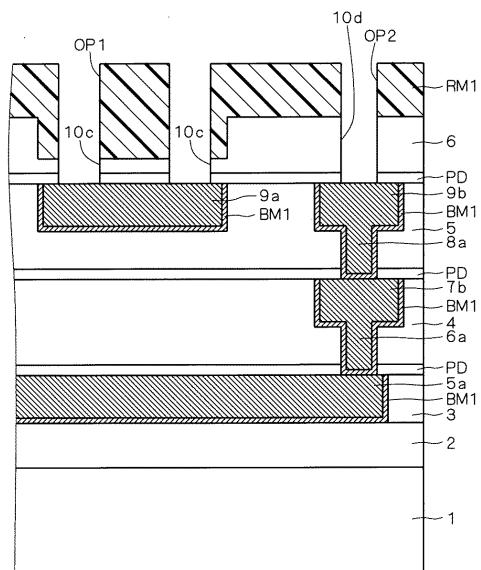

まず、製造工程を順に示す断面図である図3～図9を用いて本発明に係る半導体装置100の製造方法について説明する。なお、半導体装置100の構成については最終工程を示す図9に示す。なお、半導体装置100においては図1に示した半導体装置90と同一の構成には同一の符号を付し、重複する説明は省略する。

#### 【0042】

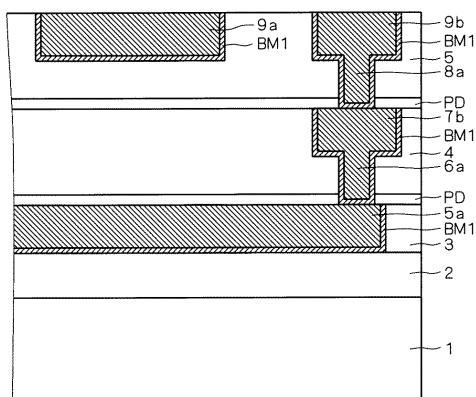

まず、従来からの製造方法を用いて図3に示す配線層9a、9bおよびコンタクトプラグ8aまでの構成を形成する。

#### 【0043】

その後、図4に示す工程において、層間絶縁膜5上に例えばCVD法によりSiN膜等の絶縁膜を形成して拡散防止絶縁膜PDを配設する。

#### 【0044】

その後、拡散防止絶縁膜PD上に、例えばCVD法によりシリコン酸化膜等で構成される厚さ400～1000nmの層間絶縁膜6を形成する。

#### 【0045】

そして配線層9aの上方部に対応する位置の層間絶縁膜6をフォトリソグラフィおよび異方性エッティングにより選択的にエッティングして深さ約350nmキャパシタの下部電極形成用の電極溝11cを形成する。この深さは、図1に示した半導体装置90の下部電極110形成用の電極溝よりも大きな値に設定する。

#### 【0046】

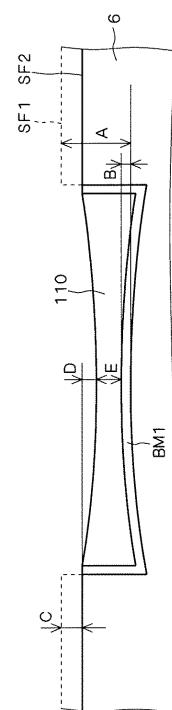

その後、図5に示す工程において層間絶縁膜6上にレジストマスクRM1を形成し、フォトリソグラフィによりパターニングして、電極溝11c上にビアホール開口用の開口部OP1を、また、キャパシタ形成領域外に設けられた配線層9bの上方部に対応する位置の層間絶縁膜6上に配線層9bとの接続のためのビアホール開口用の開口部OP2を形成する。このとき、開口部OP1の開口直径は、開口部OP2よりも大きく設定するものとし、例えば開口部OP2の直径が0.36μmであるならば、開口部OP1の開口直径は0.38μmに設定する。

#### 【0047】

そしてレジストマスクRM1をエッティングマスクとして異方性エッティングを行い、開口部OP1およびOP2に対応する部分の層間絶縁膜6および拡散防止絶縁膜PDを除去することで、それぞれ配線層9aおよび9bに達するビアホール10cおよび10dを形成する。

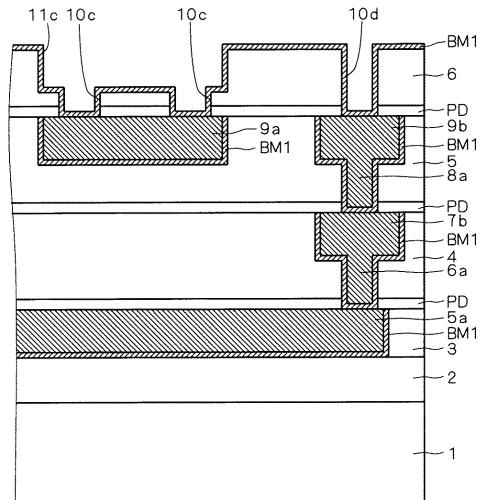

#### 【0048】

次に、レジストマスクRM1を除去した後、図6に示す工程において層間絶縁膜6の全面に例えばスパッタリング法によりバリアメタル膜BM1を形成することで、電極溝11cの内面および電極溝11cに連通するビアホール10cの内面、ビアホール10dの内面をバリアメタル膜BM1で覆う。

#### 【0049】

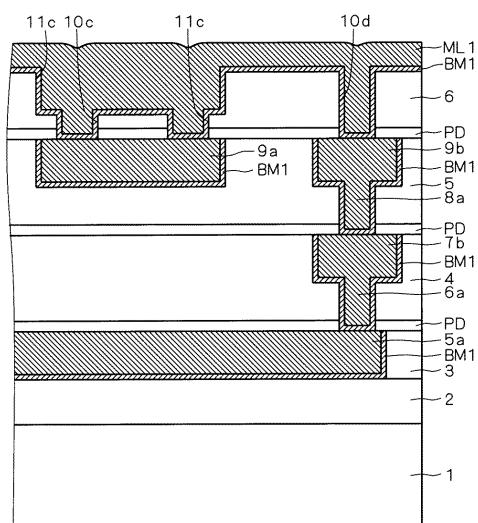

次に、図7に示す工程においてバリアメタル膜BM1で覆われた層間絶縁膜6の全面に、例えばCVD法によりタンゲステン膜ML1を形成し、電極溝11c内、ビアホール10c内およびビアホール10d内にタンゲステン膜ML1を充填する。

10

20

30

40

50

## 【0050】

その後、図8に示す工程において、CMPにより層間絶縁膜6上の不要なタンゲステン膜ML1を研磨除去して、電極溝11c内、ビアホール10c内および10d内にのみタンゲステン膜ML1を残して、それぞれキャパシタの下部電極11、コンタクトプラグ10aおよびコンタクトプラグ10bを形成する。

## 【0051】

このとき、CMPによる過剰研磨で、ディッシングやエロージョンが発生し、下部電極11の表面は皿状に窪むが、下部電極11の厚さ(350nm程度)がディッシングやエロージョンによる過剰研磨量に比べて十分厚いので、下部電極11が局所的にでも完全に除去されるということはない。

10

## 【0052】

その後、図9に示す工程において、下部電極11上を覆うように、例えばCVD法によりシリコン窒化膜で構成されるキャパシタ誘電体膜12を形成した後、さらに、キャパシタ誘電体膜12に、例えばスパッタリング法によりTiN膜(あるいはTaN膜あるいはW膜)で構成されるキャパシタの上部電極13を形成する。

20

## 【0053】

その後、上部電極13およびキャパシタ誘電体膜12を覆うように、例えばスパッタリング法によりアルミニウム膜(あるいはCu膜)で構成される最上層配線14を形成する。このとき、同時にコンタクトプラグ10b上にも最上層配線14を選択的に形成するようパターニングすることで半導体装置100を得る。

## 【0054】

なお、図9に示す半導体装置100は5層の層間絶縁膜を有する構成であったが、これに限定されるものではなく、さらに多くの層間絶縁膜、あるいはより少ない層間絶縁膜で構成される半導体装置にも本発明は適用可能である。

## 【0055】

また、図9においてはキャパシタを最上層の層間絶縁膜6上に形成した構成を示したが、キャパシタは最上層以外の層間絶縁膜上に設けても良い。

## 【0056】

## &lt;特徴的作用効果&gt;

ここで、図4を用いて説明したように、電極溝11cの深さを約350nmとして図1に示した半導体装置90よりも深くしたが、フォトリソグラフィ装置の焦点深度(DOF)の調整範囲の制限は問題とならなかった。

30

## 【0057】

それは、開口部OP2の直径が0.36μmであるならば、開口部OP1の直径は0.38μmになるように設定したためである。

## 【0058】

すなわち、発明者達の実験では、ビアホール直径を大きく設定すると、焦点深度が変わった場合にビアホール直径が変化する割合を低減できる、すなわちDOFマージン(フォーカスマージン)を大きくできるという知見が得られた。

40

## 【0059】

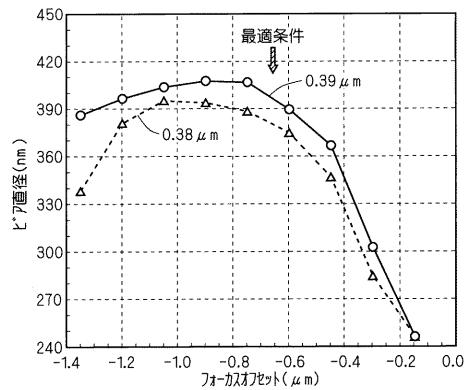

図10には発明者達が得たフォーカスオフセットとビアホール直径との関係を示す。

図10においては、横軸にフォーカスオフセット(μm)を縦軸にビアホールの直径(nm)を示し、0.38μmのビアホールを形成する場合と、0.39μmのビアホールを形成する場合について、フォーカスオフセットを変化させた場合にビアホール直径がどのように変化するかについて示している。なお、図10においてはDOFが深くなる方向をマイナス方向として示している。

## 【0060】

図10において0.38μmのビアホールおよび0.39μmのビアホールが形成されるフォーカスオフセットをリソグラフィ最適条件として矢印で示しているが、0.38μmのビアホールを形成する場合に、ビアホール直径が0.38μmより小さくならないフ

50

オーカスオフセットの範囲は -0.7 μm から -1.2 μm の範囲であるが、0.39 μm のビアホールを形成する場合に、ビアホール直径が 0.39 μm より小さくならないフォーカスオフセットの範囲は -0.7 μm から -1.3 μm の範囲となっており、ビアホール直径を大きく設定する方が D O F の変化の影響を受けにくいことが判る。

#### 【0061】

従って、電極溝 11c の底部に形成するコンタクトプラグ 10a の直径を、層間絶縁膜 6 中の他の部分に形成するコンタクトプラグ 10b の直径に比べて大きく設定することで、電極溝 11c の設定深さを約 350 nm として、図 1 に示した半導体装置 90 よりも約 100 nm 深くした場合でも、コンタクトプラグ 10b の直径が設定値よりも大幅に小さくなるということが防止される。10

#### 【0062】

以上説明したように、開口部 OP2 の直径が 0.36 μm であるのに対し、開口部 OP1 の直径は 0.38 μm であり、これは、コンタクトプラグ 10a の直径とコンタクトプラグ 10b の直径に対応し、コンタクトプラグ 10a の直径はコンタクトプラグ 10b の直径よりも 1.05 倍大きいということになる。

#### 【0063】

また、図 10 より、直径を大きくすれば D O F マージンを大きくできることが判るので、キャパシタの下部電極と下層の配線層とを電気的に接続するコンタクトプラグの直径は、少なくとも同じ層間絶縁膜に設けられた他のコンタクトプラグの直径より 1.05 以上大きくすることで、同じ層間絶縁膜中の他のコンタクトプラグに比べてフォーカスマージンを確実に大きくできる。20

#### 【0064】

電極溝 11c を深くすることで、当該電極溝 11c の深さで規定される下部電極 11 の厚さが厚くなり、CMP による過剰研磨で、ディッシングやエロージョンが発生し、下部電極 11 の表面が皿状に窪んでも、下部電極 11 の厚さ（350 nm 程度）がディッシングやエロージョンによる過剰研磨量に比べて十分厚いので、下部電極 11 が局所的にでも完全に除去されるということはない。

#### 【0065】

ここで、図 2 に示した下部電極の形成後の断面形状を示す図を用いて、下部電極のディッシングに関する発明者達の知見を紹介する。なお、以下の説明においては図 2 を下部電極 11 の形成後の断面形状を示す図として使用する。30

#### 【0066】

ここで、下部電極深さ A が 332 nm（実測値）、バリアメタル厚さ B は 79 nm（断面 SEM 写真からの計測値）、層間絶縁膜切削厚さ C は 84 nm（A - (B + E) により算出）、ディッシング量 D は 84 nm（A - (B + E) により算出）、残膜量 E は 169 nm となる。

#### 【0067】

このように、ディッシングにより下部電極 11 中央部の厚さは設定値の半分程度となってしまうが、複数設けられた下部電極 11 の中で、厚さがマイナスになるものは存在しなかった。40

#### 【0068】

以上説明した本発明に係る実施の形態 1 の半導体装置によれば、下部電極 11 の過研磨に対する耐性を高めることで、下部電極 11 が局所的にせよ完全に除去されることが防止され、耐圧不良を起こすキャパシタの発生を防止できるという効果が得られた。

#### 【0069】

なお、上記においては、電極溝 11c の底部に形成するコンタクトプラグ 10a の直径を、層間絶縁膜 6 中の他の領域に形成するコンタクトプラグ 10b の直径に比べて大きく設定するものとして説明したが、コンタクトプラグ 10a は、キャパシタが形成される層間絶縁膜 6 以下の層間絶縁膜において形成される何れのコンタクトプラグよりも大きく形成される。50

## 【0070】

## &lt;実施の形態2&gt;

以上説明した本発明に係る実施の形態1の半導体装置においては、下部電極11と下層配線とを電気的に接続するコンタクトプラグ10aの直径を他の部分のコンタクトプラグよりも大きくすることで、DOPマージンを大きくして、CMP時の下部電極11の過研磨に対する耐性を高める構成を示したが、下部電極の過研磨を低減することで耐圧不良を起こすキャパシタの発生を防止するようにしても良い。

## 【0071】

すなわち、CMP時の下部電極の過研磨は、CMPで使用する研磨パッドの変形等に起因するだけでなく、下部電極と下層配線とを電気的に接続するコンタクトプラグの単位面積当たりの配設個数によっても過研磨の程度が異なることが発明者達の試験により判った。

10

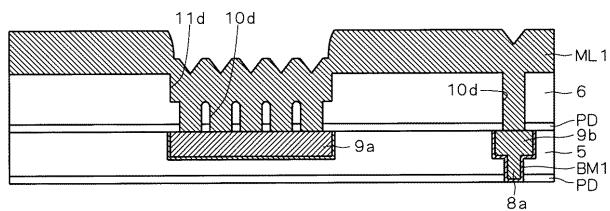

## 【0072】

図11は下部電極110の形成工程において、層間絶縁膜6の全面にタンゲステン膜ML1を形成して、電極溝11d内にタンゲステン膜ML1を充填した状態を示す断面図であり、電極溝11d内に配設され、下層の配線層9aに達するビアホール10d内にもタンゲステン膜ML1が充填され、また、キャパシタ形成領域外に設けられた配線層9bに達するビアホール10d内にもタンゲステン膜ML1が充填されている。

## 【0073】

なお、電極溝11dは図4に示した設定深さ350nmの電極溝11cより浅く、設定深さ250nmとし、また、ビアホール10dの直径は0.36μmで統一されている。また、便宜的に、バリアメタル膜は図示を省略した。

20

## 【0074】

ここで、電極溝11d内には図11に示す断面において5個のビアホール10dを配設しているが、ビアホール10dを配設すると、その部分ではビアホール10dを埋め込む分だけタンゲステン膜ML1の厚さが減少する。そして、図11に示すように多数のビアホール10dを密集させると、電極溝11d内でのタンゲステン膜ML1の平均膜厚が減少することになる。

## 【0075】

この状態でCMPを行うと、平均膜厚が薄くなった電極溝11d内ではディッキングが顕著になり、図12に示すように下部電極110が局所的に完全に除去されてしまう可能性があるという知見を得るに至った。

30

## 【0076】

そして、タンゲステン膜ML1の平均膜厚が大幅に減少しないように、電極溝11d内に設けるビアホール10dの個数を設定すれば、下部電極110が局所的に完全に除去される率を低減できることが判った。

## 【0077】

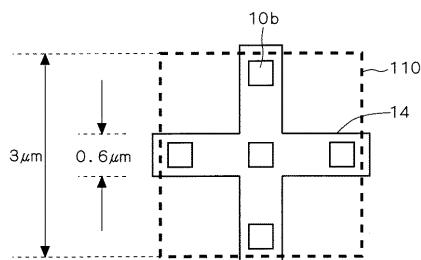

図13には、上記知見に基づいて得られたコンタクトプラグ10b(すなわちビアホール10d)の配設パターンの一例を示す。

40

## 【0078】

図13は、キャパシタを最上層配線側から見た平面図であり、下部電極110を破線で示しており、平面視形状が正方形の下部電極110において、5個のコンタクトプラグ10bが十字状をなすように、下部電極110の縦横の中心軸に沿って配設されている。

## 【0079】

なお、下部電極110の上方に配設される最上層配線14は、コンタクトプラグ10bの配列に沿って配設されており、その幅は0.6μm程度である。

## 【0080】

ここで、下部電極110は縦横の長さがそれぞれ3μm程度であり、3μmの長さの領域において3個程度のコンタクトプラグ10bを配設するのであれば、タンゲステン膜ML1の平均膜厚が大幅に減少するということがなく、下部電極110が局所的に完全に除

50

去される率を低減できると言える。

【0081】

なお、コンタクトプラグ10bが十字状をなすように配設することは一例であり、下部電極110内で並列に2列をなすように配設するようにも良く、また、1列だけであっても良い。

【図面の簡単な説明】

【0082】

【図1】本発明を適用しないMIM構造のキャパシタを有する半導体装置の構成を示す断面図である。

【図2】下部電極の過研磨を説明するための下部電極モデルを示す図である。 10

【図3】本発明に係る半導体装置の実施の形態1の製造工程を示す断面図である。

【図4】本発明に係る半導体装置の実施の形態1の製造工程を示す断面図である。

【図5】本発明に係る半導体装置の実施の形態1の製造工程を示す断面図である。

【図6】本発明に係る半導体装置の実施の形態1の製造工程を示す断面図である。

【図7】本発明に係る半導体装置の実施の形態1の製造工程を示す断面図である。

【図8】本発明に係る半導体装置の実施の形態1の製造工程を示す断面図である。

【図9】本発明に係る半導体装置の実施の形態1の製造工程を示す断面図である。

【図10】フォーカスオフセットとビアホール直径との関係を示す図である。

【図11】電極溝内のビアホールの個数と下部電極の過研磨との関係を説明する断面図である。 20

【図12】電極溝内のビアホールの個数と下部電極の過研磨との関係を説明する断面図である。

【図13】本発明に係る半導体装置の実施の形態2の構成を説明する平面図である。

【符号の説明】

【0083】

11 下部電極、12 キャパシタ誘電体膜、13 上部電極、10a、10b コンタクトプラグ。

【図1】

12 : キャバシタ誘電体膜

13 : 上部電極

10 b : コンタクトプラグ

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

11 : 下部電極

10a : コンタクトプラグ

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

F ターム(参考) 5F033 HH11 HH18 HH19 HH21 HH32 HH33 JJ11 JJ18 JJ19 JJ21

JJ32 JJ33 KK01 KK11 KK18 KK21 KK32 KK33 MM01 MM02

MM12 MM13 PP06 PP15 QQ01 QQ09 QQ16 QQ37 QQ48 RR01

RR04 RR06 SS11 VV10 XX01 XX28

5F038 AC02 AC05 AC15 AC18 CD20 EZ11 EZ14 EZ15 EZ20