US 20100116676A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2010/0116676 A1

### Kim et al.

## May 13, 2010 (43) **Pub. Date:**

### (54) METHOD OF FABRICATING PROBE PIN FOR PROBE CARD

Sang Jin Kim, Seoul (KR); Byeung (75) Inventors: Gyu Chang, Suwon (KR); Hee Ju Son, Suwon (KR); Ho Joon Park, Seoul (KR)

> Correspondence Address: MCDÊRMOTT WILL & EMERY LLP 600 13TH STREET, N.W. WASHINGTON, DC 20005-3096 (US)

- SAMSUNG (73) Assignee: **ELECTRO-MECHANICS CO.,** LTD.

- (21) Appl. No.: 12/502,652

- (22) Filed: Jul. 14, 2009

#### (30)**Foreign Application Priority Data**

#### Nov. 12, 2008 (KR) ..... 10-2008-0112201

### **Publication Classification**

- (51)Int. Cl. C25D 5/02 (2006.01)

- (52)

#### (57)ABSTRACT

Provided is a method of fabricating a probe pin. In the method, a concave region for a probe pin is formed on a mold substrate. The surface roughness of the concave region is reduced to smooth the surface of the concave region. A release layer is formed on the surface of the concave region of the mold substrate. A plating process is performed to form a probe pin corresponding to the concave region. After the performing of the plating process, the mold substrate having the probe pin is disposed on a circuit substrate and the probe pin is connected to a desired portion of the circuit substrate. Thereafter, the mold substrate is separated from the probe pin in such a way that the mold substrate remains unchanged. Also, the separated mold substrate may be reused.

FIG. 2A

FIG. 2B

FIG. 2C

### METHOD OF FABRICATING PROBE PIN FOR PROBE CARD

### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application claims the priority of Korean Patent Application No. 2008-0112201 filed on Nov. 12, 2008, in the Korean Intellectual Property Office, the disclosure of which is incorporated herein by reference.

### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

**[0003]** The present invention relates to a probe pin for a probe card, and more particularly, to a method of fabricating a probe pin for a probe card, which makes it possible to simplify a fabrication process of the probe pin and reuse a mold used for fabrication of the probe pin.

[0004] 2. Description of the Related Art

**[0005]** A probe card is a test device for determining the defects or the electrical characteristics of a semiconductor chip on a wafer by using the electrical contact with a probe pin. The probe card may include a circuit substrate such as a ceramic substrate with a circuit, and a plurality of fine probe pins that are electrically connected to the circuit.

**[0006]** In general, a probe pin for a probe card mechanically contacts a wafer. Therefore, the body of the probe pin requires an excellent mechanical elasticity because it must have a high yield strength and an excellent restoring force. Also, the probe pin body must have a low electrical resistance because it electrically tests a chip.

**[0007]** Also, a tip portion of the probe pin mechanically contacting the chip requires an anti-abrasion and a low contact resistance. A recent probe test device requires the improvement of the integration level of a probe pin in order to test a highly-integrated semiconductor memory chip on a wafer level in a batch fashion. Thus, the general trend is that a MEMS processing technology is used to form fine probe fines in a batch fashion, thereby improving the integration level of the probe pins.

**[0008]** In general, an electrode is formed at one side of a ceramic substrate; a MEMS process is performed to form a probe pin on a semiconductor wafer such as a silicon wafer; and the ceramic substrate and the silicon wafer are bonded together. Herein, the silicon wafer used as a mold is removed to form the probe pin on the ceramic substrate, thereby providing a desired probe card.

**[0009]** Herein, a probe pin fabrication method according to the related art can be summarized into the following two methods.

**[0010]** The first method uses a polymer material to fabricate a probe pin mold on a ceramic substrate, fills the probe pin mold through a plating process to form a probe pin, and removes only the mold material so that the probe pin remains on the ceramic substrate.

**[0011]** The second method processes a selectively-removable substrate into a desired mold structure by means of a mold material, forms a probe pin in the processed space through a plating process, bonds the probe pin with the ceramic substrate, and selectively removes the mold substrate.

**[0012]** In the probe pin fabrication method according to the related art, the mold forming process for fabrication of the probe pin is complex. Also, because the structure used as the

mold is finally removed, the mold must be formed in every probe pin fabrication process. For example, if the mold is fabricated using a polymer material, an exposing process, a developing process, a layer growing process, and a plating process are used to form a probe pin body (or a probe beam); the above processes are repeated to form a probe tip portion; and a bonding process and a mold removing process are performed to fabricate a probe pin. However, preprocessing processes such as a cleaning process, a surface treating process, a polymer coating process, and a drying process are required, when considering only the exposing process, which increases the fabrication process time and the fault repair time of the probe card and reduces the chip production due to the test efficiency reduction in the actual field.

### SUMMARY OF THE INVENTION

**[0013]** An aspect of the present invention provides a method of fabricating a probe pin for a probe card, which makes it possible to simplify a fabrication process of the probe pin and reuse a mold structure for fabrication of the probe pin by facilitating the separation of the mold structure from the probe pin.

**[0014]** According to an aspect of the present invention, there is provided a method of fabricating a probe pin, the method including: forming a concave region corresponding to a probe pin on a mold substrate; reducing the surface roughness of the concave region to smooth the surface of the concave region; forming a release layer on the surface of the concave region of the mold substrate; and performing a plating process to form a probe pin corresponding to the concave region.

**[0015]** The mold substrate may be a silicon substrate. The probe pin may have a probe beam and a probe tip provided at one end of the probe beam.

**[0016]** The reducing of the surface roughness of the concave region may include: forming an oxide layer on the surface of the concave region; and removing the oxide layer.

**[0017]** In this case, the oxide layer formed on the surface of the concave region may be a thermal oxide layer.

**[0018]** The release layer may be formed of a copper or a copper alloy.

**[0019]** The method may further include forming a mask layer on the surface of the mold substrate other than the surface of the concave region before the forming of the release layer. In this case, the method may further include removing the mask layer after the performing of the plating process.

**[0020]** The probe pin may be formed of one selected from the group consisting of Ti, Ni, Co and a combination thereof. **[0021]** The method may further include, after the performing of the plating process, disposing the mold substrate having the probe pin on a circuit substrate and connecting the probe pin to a desired portion of the circuit substrate; and separating the mold substrate from the probe pin in such away

**[0022]** The separating of the mold substrate from the probe pin may be performed using the thermal expansion coefficient difference between the probe pin and the mold substrate.

that the mold substrate remains unchanged.

**[0023]** Particularly, the separated mold substrate may be reused. That is, the mold substrate separated from the probe pin may be reused in the surface smoothing process for reduc-

May 13, 2010

tion of the surface roughness, the release layer forming process, and the plating process for formation of the probe pin.

### BRIEF DESCRIPTION OF THE DRAWINGS

**[0024]** The above and other aspects, features and other advantages of the present invention will be more clearly understood from the following detailed description taken in conjunction with the accompanying drawings, in which:

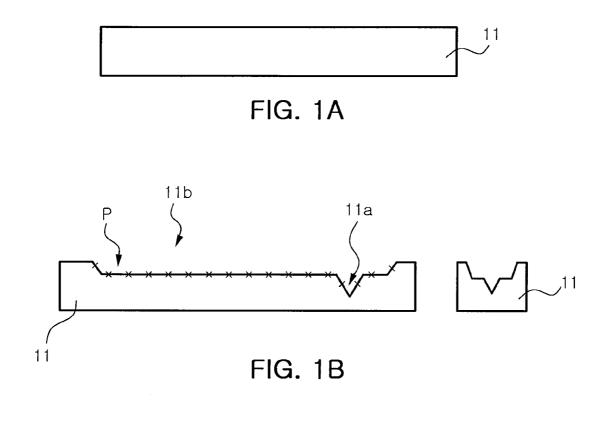

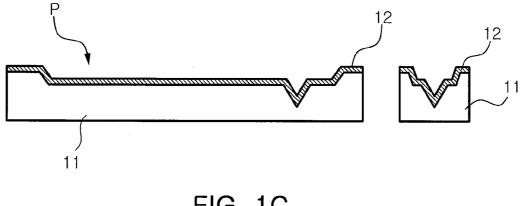

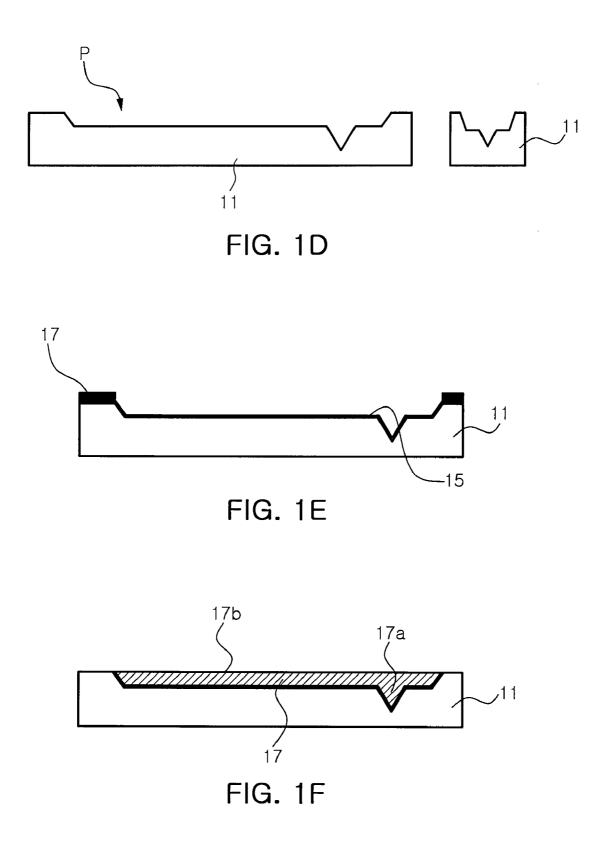

**[0025]** FIGS. 1A to 1F are cross-sectional views illustrating a process of forming a probe pin in a probe pin fabrication method according to an exemplary embodiment of the present invention; and

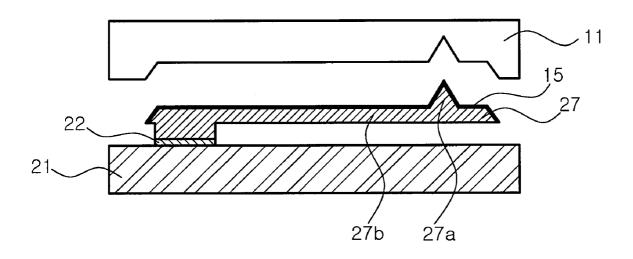

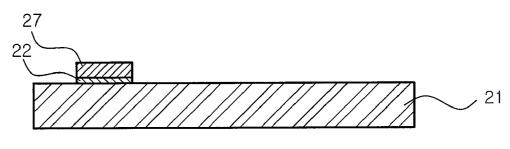

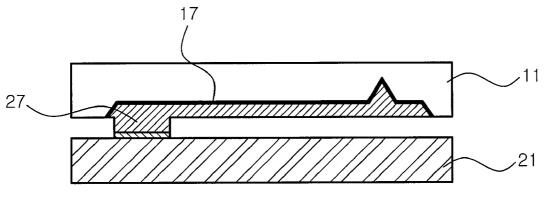

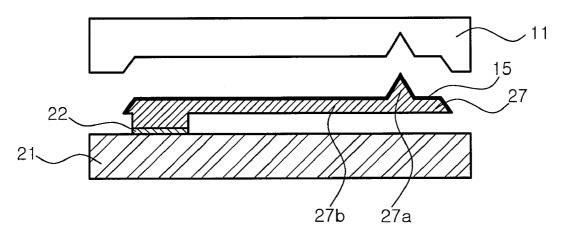

**[0026]** FIGS. 2A to 2C are cross-sectional views illustrating a transfer process in the probe pin fabrication method according to an exemplary embodiment of the present invention.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

**[0027]** Exemplary embodiments of the present invention will now be described in detail with reference to the accompanying drawings.

**[0028]** FIGS. 1A to 1F are cross-sectional views illustrating a process of forming a probe pin in a probe pin fabrication method according to an exemplary embodiment of the present invention.

**[0029]** As illustrated in FIG. 1A, a substrate 11 for a mold (hereinafter referred to as a mold substrate) is prepared for fabrication of a probe pin.

**[0030]** The mold substrate **11** may preferably be a silicon wafer, to which the present invention is not limited. For example, the mold substrate **11** may also be other well-known semiconductor substrates that are easy to process. Specifically, the mold substrate **11** may be any substrate that can have a desired concave structure formed through an anisotropic etching process such as a Reactive Ion Etching (RIE) process. **[0031]** Thereafter, as illustrated in FIG. **1B**, a concave

region P for a desired probe pin is formed at the mold substrate 11.

**[0032]** The concave region P may be formed to have a region 11b for a probe beam (hereinafter referred to as a probe beam region) and a region 11a for a probe tip (hereinafter referred to as a probe tip region), so that it corresponds to a desired probe pin structure. One concave region P for one probe pin is illustrated in this embodiment. However, in an actual process, a plurality of concave regions for a plurality of probe pins may be formed at a large-area silicon wafer.

**[0033]** The present process may be implemented using a well-known anisotropic etching process such as an RIE process, as described above. Particularly, if the concave region P is formed through an anisotropic etching process, each of the etched surfaces of the silicon mold substrate may have an inclined surface (e.g., **11***a*) with respect to a horizontal plane according to a desired probe shape. The etched surfaces with different crystal surfaces can improve the releasability of the mold.

**[0034]** Meanwhile, the surface of the concave region P, that is, the surface resulting from the anisotropic etching process may be damaged during the etching process and thus may have a high surface roughness. Because the high surface roughness of the concave region P hinders the achievement of the releasability of the mold, the present invention includes an improvement process for the surface of the concave region P. That is, the present invention uses at least a process of reducing the surface roughness (Ra) of the concave region P in order to smooth the surface of the concave region P.

**[0035]** For example, after the anisotropic etching process such as an RIE process is performed, a simple wet etching process may be performed in order to reduce the surface roughness of the concave region P. However, a process of reducing the surface roughness of the concave region P according to a preferred embodiment of the present invention may be performed through processes illustrated in FIGS. **1**C and **1**D.

**[0036]** That is, as illustrated in FIG. 1C, a thin oxide layer **12** is formed on the surface of the concave region P. The oxide layer **12** may be a silicon oxide layer if a silicon substrate is used as the mold substrate **11**. The oxide layer **12** formed on the surface of the concave region P may be a thermal oxide layer.

**[0037]** Thereafter, as illustrated in FIG. 1D, the oxide layer **12** formed on the surface of the concave region P is removed to achieve the smoother surface thereof. The removing process may be performed using a well-known wet etching process.

**[0038]** The smoothed surface of the concave region P achieved through the oxide layer forming/removing processes can guarantee the high releasability of the mold.

**[0039]** In addition, as illustrated in FIG. 1E, a release layer **15** is formed on the surface of the concave region P.

**[0040]** The release layer **15** of the present invention may be formed of any material that is electrically conductive and also provides the high releasability between the material of the mold substrate **11** and a metal used in the subsequent plating process.

[0041] For example, before forming a seed layer, the related art grows a Ti or Cr layer in order to increase the adhesion to the silicon. However, the present method may not use Ti or Cr in order to secure the releasability of a probe pin. [0042] The release layer 15 of the present invention may be formed of a copper or a copper alloy. The release layer 15 formed of a copper increases the current density, thus making it possible to increase the efficiency of the subsequent plating process and provide the high releasability. The adhesion (or the releasability) between the release layer 15 and the mold

substrate **11** formed of a silicon may be adjusted to a desired level by controlling the thickness of the release layer **15**.

**[0043]** The present process may be easily implemented by forming a mask layer **16** such as a photoresist pattern on the surface of the mold substrate **11** other than the surface of the concave region P before forming the release layer **15**. In this case, the mask layer **16** may remain until the start of the plating layer, and may be removed after the completion of the plating process.

**[0044]** Thereafter, as illustrated in FIG. 1F, the plating process is performed to form a probe pin **17** corresponding to the concave region P.

**[0045]** In a specific embodiment of the present invention, the probe pin 17 may be formed of one selected from the group consisting of Ti, Ni, Co and a combination thereof. The probe pin 17 formed by the plating process may have a prove beam 17b corresponding to the concave region P and a probe tip 17a formed at one end portion of the probe beam 17b. As described above, the release layer 15 formed of a copper of the present invention can guarantee the high current density, thus making it possible to easily perform an electrolytic plating process.

**[0046]** The advantages and effects of the present invention can be clearly understood through a process of transferring to a probe card substrate such as a ceramic substrate.

**[0047]** FIGS. 2A to 2C are cross-sectional views illustrating a transfer process in the probe pin fabrication method according to an exemplary embodiment of the present invention.

[0048] As illustrated in FIG. 2A, a probe card substrate 21 a having a circuit formed thereon is prepared. The probe card substrate 21 may be a multilayer ceramic substrate.

[0049] As illustrated in the drawings, a metal bonding unit 27 is formed on a circuit region 22 of the probe card substrate 21. The metal bonding unit 27 may have a predetermined height and may be formed of a portion of the probe pin.

**[0050]** Thereafter, as illustrated in FIG. 2B, the mold substrate 11 having the probe pin 17 formed therein is disposed on the probe card substrate 21, and then a portion of the probe pin 17 is connected to a desired portion of the probe card substrate 21.

[0051] Specifically, as illustrated in the drawings, one end portion of the probe beam 17b, formed on the opposite side of the end portion of the probe beam 17b having the probe tip 17a formed thereat, is connected to the metal bonding unit 27, thereby transferring the probe pin 17 to the probe card substrate 21.

**[0052]** Thereafter, as illustrated in FIG. 2C, the mold substrate **11** is separated from the probe pin **17** in such a way that the mold substrate **11** remains unchanged.

**[0053]** The advantages of the present invention well appear in the present process. That is, unlike the related art, the present invention separates the mold substrate **11** from the probe pin **17** on the basis of the high releasability, while maintaining the shape of the mold substrate **11**, without removing the mold structure. As described above, the high releasability can be implemented by removing the surface roughness and using the release layer **15** that is formed of a conductive material such as a copper.

**[0054]** Particularly, the separated mold substrate **11** can be reused. The mold substrate **11** separated from the probe pin **17** can be repeatedly used several times, due to the surface smoothing process for reduction of the surface roughness, the release layer forming process, and the plating process for formation of the probe pin **17**.

[0055] The separating process can be easily implemented by using the thermal expansion coefficient difference between the material of the mold substrate 11 and the material of the probe pin 17 (including the release layer 15). In general, the bonding process is performed at high temperature. Thereafter, only the probe pin 17 and the mold substrate 11 are locally cooled at low temperature, thereby increasing the interfacial stress due to the thermal expansion coefficient difference between the silicon and the metal and releasing the probe pin 17 along the metal layer introduced in the plating process. Actually, because the silicon and the general metal have a thermal expansion coefficient difference of about 4.4 times therebetween, the separating process using the thermal expansion coefficient difference, such as the local low-temperature cooling process, can be easily implemented.

**[0056]** As described above, the probe pin fabrication method according to the present invention can simplify the mold forming process for fabrication of the probe pin and can

continuously reuse the mold in the probe pin fabrication process. Consequently, the present invention can greatly reduce the fabrication time of the probe pin and can greatly increase the mass production through the reuse of the mold. Particularly, the present invention can reduce the fault repair time of the probe pin like a MEMS probe card, thus making it possible to increase the chip test efficiency.

[0057] While the present invention has been shown and described in connection with the exemplary embodiments, it will be apparent to those skilled in the art that modifications and variations can be made without departing from the spirit and scope of the invention as defined by the appended claims.

What is claimed is:

**1**. A method of fabricating a probe pin, the method comprising:

- forming a concave region corresponding to a probe pin on a mold substrate;

- reducing the surface roughness of the concave region to smooth the surface of the concave region;

- forming a release layer on the surface of the concave region of the mold substrate; and

- performing a plating process to form a probe pin corresponding to the concave region.

2. The method of claim 1, wherein the mold substrate is a silicon substrate.

**3**. The method of claim **1**, wherein the probe pin has a probe beam and a probe tip provided at one end of the probe beam.

**4**. The method of claim **1**, wherein the reducing of the surface roughness of the concave region comprises:

forming an oxide layer on the surface of the concave region; and

removing the oxide layer.

5. The method of claim 4, wherein the oxide layer formed on the surface of the concave region is a thermal oxide layer.

**6**. The method of claim **1**, wherein the release layer is formed of a copper or a copper alloy.

7. The method of claim 1, further comprising:

forming a mask layer on the surface of the mold substrate other than the surface of the concave region before the forming of the release layer.

8. The method of claim 7, further comprising:

removing the mask layer after the performing of the plating process.

**9**. The method of claim **1**, wherein the probe pin is formed of one selected from the group consisting of Ti, Ni, Co and a combination thereof.

**10**. The method of claim **1**, further comprising, after the performing of the plating process:

- disposing the mold substrate having the probe pin on a circuit substrate and connecting the probe pin to a desired portion of the circuit substrate; and

- separating the mold substrate from the probe pin in such a way that the mold substrate remains unchanged.

11. The method of claim 10, wherein the separating of the mold substrate from the probe pin is performed using the thermal expansion coefficient difference between the probe pin and the mold substrate.

12. The method of claim 10, further comprising:

performing the process of claim 1 by using the separated mold substrate.

\* \* \* \* \*