(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-232230

(P2010-232230A)

(43) 公開日 平成22年10月14日(2010.10.14)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12 501P

テーマコード(参考)

審査請求 未請求 請求項の数 19 O L (全 16 頁)

(21) 出願番号

特願2009-75277 (P2009-75277)

(22) 出願日

平成21年3月25日 (2009.3.25)

(71) 出願人 000001443

カシオ計算機株式会社

東京都渋谷区本町1丁目6番2号

100096699

弁理士 鹿嶋 英實

三原 一郎

東京都青梅市藤橋3丁目3番地2

カシオ計算機株式会社青梅

事業所内

(54) 【発明の名称】半導体装置およびその製造方法

(57) 【要約】 (修正有)

【課題】渦巻き形状の薄膜誘導素子を備えたCSPと呼ばれる半導体装置において、シリコン基板に発生する渦電流に起因する薄膜誘導素子の渦電流損を低減する。

【解決手段】シリコン基板1上にはパッシベーション膜3および第1の保護膜5が設けられている。第1の保護膜の周辺部を除く上面には第2の保護膜7が設けられている。第2の保護膜の上面には渦巻き形状の薄膜誘導素子11が設けられている。この場合、第1、第2の保護膜の合計厚さにより、シリコン基板に発生する渦電流に起因する薄膜誘導素子の渦電流損を低減することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

半導体基板と、前記半導体基板上に設けられた第1の樹脂膜と、前記第1の樹脂膜の少なくとも周辺部を除く上面に設けられた第2の樹脂膜と、前記第2の樹脂膜上に設けられた薄膜誘導素子とを備えていることを特徴とする半導体装置。

**【請求項 2】**

請求項1に記載の発明において、前記半導体基板の周辺部上に複数の接続パッドが設けられ、前記第2の樹脂膜は、前記半導体基板上における前記接続パッドよりも内側の領域に設けられていることを特徴とする半導体装置。

**【請求項 3】**

請求項2に記載の発明において、前記第2の樹脂膜の厚さは前記第1の樹脂膜の厚さよりも厚くなっていることを特徴とする半導体装置。

**【請求項 4】**

請求項3に記載の発明において、前記第1の樹脂膜の厚さと前記第2の樹脂膜の厚さの合計は10～20μmであることを特徴とする半導体装置。

**【請求項 5】**

請求項4に記載の発明において、前記第2の樹脂膜の厚さは前記第1の樹脂膜の厚さの2倍以上であることを特徴とする半導体装置。

**【請求項 6】**

請求項5に記載の発明において、前記第1の樹脂膜の厚さは2～6μmであることを特徴とする半導体装置。

**【請求項 7】**

請求項1に記載の発明において、前記第1、第2の樹脂膜上に配線および薄膜誘導素子用配線が設けられ、前記配線の一端部および前記薄膜誘導素子用配線の一端部は前記接続パッドに接続され、前記薄膜誘導素子用配線の他端部は前記薄膜誘導素子の外端部に接続されていることを特徴とする半導体装置。

**【請求項 8】**

請求項7に記載の発明において、前記第2の樹脂膜の側面は傾斜面となっていることを特徴とする半導体装置。

**【請求項 9】**

請求項8に記載の発明において、前記配線の接続パッド部上および前記薄膜誘導素子の内端部上に柱状電極が設けられていることを特徴とする半導体装置。

**【請求項 10】**

請求項1に記載の発明において、前記第1の樹脂膜下に薄膜誘導素子用下層配線が設けられ、前記薄膜誘導素子用下層配線の一端部は前記接続パッドに接続され、他端部は前記薄膜誘導素子の内端部に前記第1、第2の樹脂膜に設けられた開口部を介して接続されていることを特徴とする半導体装置。

**【請求項 11】**

周辺部に複数の接続パッドを有する半導体基板の上面全体に第1の樹脂膜を形成する工程と、

前記第1の樹脂膜上における前記接続パッドの内側領域に第2の樹脂膜を形成する工程と、

前記第2の樹脂膜上に薄膜誘導素子を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

**【請求項 12】**

請求項11に記載の発明において、前記第2の樹脂膜の厚さは前記第1の樹脂膜の厚さよりも厚くなるようにすることを特徴とする半導体装置の製造方法。

**【請求項 13】**

請求項12に記載の発明において、前記第1の樹脂膜の厚さと前記第2の樹脂膜の厚さの合計は10～20μmであることを特徴とする半導体装置の製造方法。

10

20

30

40

50

**【請求項 1 4】**

請求項 1 3 に記載の発明において、前記第 2 の樹脂膜の厚さは前記第 1 の樹脂膜の厚さの 2 倍以上となるようにすることを特徴とする半導体装置の製造方法。

**【請求項 1 5】**

請求項 1 4 に記載の発明において、前記第 1 の樹脂膜の厚さは 2 ~ 6  $\mu\text{m}$  とすることを特徴とする半導体装置の製造方法。

**【請求項 1 6】**

請求項 1 5 に記載の発明において、前記第 2 の樹脂膜を形成する工程の前に、前記半導体基板の周辺部上に形成された前記複数の接続パッドに対応する部分における前記第 1 の樹脂膜にフォトリソグラフィ法により開口部を形成する工程を有することを特徴とする半導体装置の製造方法。 10

**【請求項 1 7】**

請求項 1 6 に記載の発明において、前記薄膜誘導素子を形成する工程は、前記第 1 、第 2 の樹脂膜上に配線および薄膜誘導素子用配線を形成する工程を含み、前記配線の一端部および前記薄膜誘導素子用配線の一端部は前記接続パッドに接続され、前記薄膜誘導素子用配線の他端部は前記薄膜誘導素子の外端部に接続されることを特徴とする半導体装置の製造方法。

**【請求項 1 8】**

請求項 1 1 に記載の発明において、前記第 2 の樹脂膜はスクリーン印刷法により形成することを特徴とする半導体装置の製造方法。 20

**【請求項 1 9】**

請求項 1 8 に記載の発明において、前記スクリーン印刷法により塗布された液状樹脂膜の側面がだれることにより、前記第 2 の樹脂膜の側面が傾斜面となるようにすることを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

この発明は半導体装置およびその製造方法に関する。

**【背景技術】****【0 0 0 2】**

従来の半導体装置には、C S P (chip size package) と呼ばれ、且つ、渦巻き形状の薄膜誘導素子を備えたものが知られている（例えば、特許文献 1 参照）。この半導体装置は半導体基板を備えている。半導体基板の上面には絶縁膜が設けられている。絶縁膜の上面には複数の配線および渦巻き形状の薄膜誘導素子が設けられている。配線の接続パッド部上面には柱状電極が設けられている。柱状電極の周囲には封止膜が設けられている。柱状電極の上面には半田ボールが設けられている。 30

**【先行技術文献】****【特許文献】****【0 0 0 3】****【特許文献 1】特開 2 0 0 8 - 2 1 0 8 2 8 号公報****【0 0 0 4】**

ところで、上記のような半導体装置において、絶縁膜が、半導体基板の上面に設けられた酸化シリコン等からなるパッシベーション膜およびその上面に設けられたポリイミド系樹脂等からなる保護膜からなり、保護膜の上面に配線および薄膜誘導素子が設けられている場合には、配線に電流が流れたとき、誘導によって半導体基板に発生する渦電流により、薄膜誘導素子に渦電流損が生じ、薄膜誘導素子の特性が劣化してしまう。

**【0 0 0 5】**

これを解決するため、特許文献 1 に記載の半導体装置では、半導体基板上のパッシベーション膜と薄膜誘導素子との間に、ポリイミド系樹脂等からなる保護膜の代わりに、ポリイミド系樹脂等からなる熱硬化性樹脂中に軟磁性体粉末を混入したものからなる磁性膜を 40

設け、これにより、半導体基板に発生する渦電流に起因する薄膜誘導素子の渦電流損を低減するようにしている。

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記従来の半導体装置では、磁性膜をポリイミド系樹脂等からなる熱硬化性樹脂中に比較的高価な材料である軟磁性体粉末を混入したものによって形成しているので、比較的高価となるばかりでなく、熱硬化性樹脂中への軟磁性体粉末の分散を均一にしがたく、軟磁性体粉末の分散が密となる箇所が生じると、回路が短絡するおそれがあり、一方、軟磁性体粉末の分散が疎となる箇所が生じると、渦電流損低減の効果が薄れてしまう。

10

【0007】

そこで、この発明は、比較的安価である上、回路短絡を防止し、且つ、渦電流損低減の効果を均一に発揮することができる半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

請求項1に記載の発明に係る半導体装置は、半導体基板と、前記半導体基板上に設けられた第1の樹脂膜と、前記第1の樹脂膜の少なくとも周辺部を除く上面に設けられた第2の樹脂膜と、前記第2の樹脂膜上に設けられた薄膜誘導素子とを備えていることを特徴とするものである。

20

請求項2に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記半導体基板の周辺部上に複数の接続パッドが設けられ、前記第2の樹脂膜は、前記半導体基板上における前記接続パッドよりも内側の領域に設けられていることを特徴とするものである。

請求項3に記載の発明に係る半導体装置は、請求項2に記載の発明において、前記第2の樹脂膜の厚さは前記第1の樹脂膜の厚さよりも厚くなっていることを特徴とするものである。

請求項4に記載の発明に係る半導体装置は、請求項3に記載の発明において、前記第1の樹脂膜の厚さと前記第2の樹脂膜の厚さの合計は10~20μmであることを特徴とするものである。

30

請求項5に記載の発明に係る半導体装置は、請求項4に記載の発明において、前記第2の樹脂膜の厚さは前記第1の樹脂膜の厚さの2倍以上であることを特徴とするものである。

請求項6に記載の発明に係る半導体装置は、請求項5に記載の発明において、前記第1の樹脂膜の厚さは2~6μmであることを特徴とするものである。

請求項7に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記第1、第2の樹脂膜上に配線および薄膜誘導素子用配線が設けられ、前記配線の一端部および前記薄膜誘導素子用配線の一端部は前記接続パッドに接続され、前記薄膜誘導素子用配線の他端部は前記薄膜誘導素子の外端部に接続されていることを特徴とするものである。

40

請求項8に記載の発明に係る半導体装置は、請求項7に記載の発明において、前記第2の樹脂膜の側面は傾斜面となっていることを特徴とするものである。

請求項9に記載の発明に係る半導体装置は、請求項8に記載の発明において、前記配線の接続パッド部上および前記薄膜誘導素子の内端部上に柱状電極が設けられていることを特徴とするものである。

請求項10に記載の発明に係る半導体装置は、請求項1に記載の発明において、前記第1の樹脂膜下に薄膜誘導素子用下層配線が設けられ、前記薄膜誘導素子用下層配線の一端部は前記接続パッドに接続され、他端部は前記薄膜誘導素子の内端部に前記第1、第2の樹脂膜に設けられた開口部を介して接続されていることを特徴とするものである。

請求項11に記載の発明に係る半導体装置の製造方法は、周辺部に複数の接続パッドを

50

有する半導体基板の上面全体に第1の樹脂膜を形成する工程と、記第1の樹脂膜上における前記接続パッドの内側領域に第2の樹脂膜を形成する工程と、前記第2の樹脂膜上に薄膜誘導素子を形成する工程と、を有することを特徴とするものである。

請求項12に記載の発明に係る半導体装置の製造方法は、請求項11に記載の発明において、前記第2の樹脂膜の厚さは前記第1の樹脂膜の厚さよりも厚くなるようにすることを特徴とするものである。

請求項13に記載の発明に係る半導体装置の製造方法は、請求項12に記載の発明において、前記第1の樹脂膜の厚さと前記第2の樹脂膜の厚さの合計は10～20μmであることを特徴とするものである。

請求項14に記載の発明に係る半導体装置の製造方法は、請求項13に記載の発明において、前記第2の樹脂膜の厚さは前記第1の樹脂膜の厚さの2倍以上となるようにすることを特徴とするものである。

請求項15に記載の発明に係る半導体装置の製造方法は、請求項14に記載の発明において、前記第1の樹脂膜の厚さは2～6μmとすることを特徴とするものである。

請求項16に記載の発明に係る半導体装置の製造方法は、請求項15に記載の発明において、前記第2の樹脂膜を形成する工程の前に、前記半導体基板の周辺部上に形成された前記複数の接続パッドに対応する部分における前記第1の樹脂膜にフォトリソグラフィ法により開口部を形成する工程を有することを特徴とするものである。

請求項17に記載の発明に係る半導体装置の製造方法は、請求項16に記載の発明において、前記薄膜誘導素子を形成する工程は、前記第1、第2の樹脂膜上に配線および薄膜誘導素子用配線を形成する工程を含み、前記配線の一端部および前記薄膜誘導素子用配線の一端部は前記接続パッドに接続され、前記薄膜誘導素子用配線の他端部は前記薄膜誘導素子の外端部に接続されることを特徴とするものである。

請求項18に記載の発明に係る半導体装置の製造方法は、請求項11に記載の発明において、前記第2の樹脂膜はスクリーン印刷法により形成することを特徴とするものである。

請求項19に記載の発明に係る半導体装置の製造方法は、請求項18に記載の発明において、前記スクリーン印刷法により塗布された液状樹脂膜の側面がだれることにより、前記第2の樹脂膜の側面が傾斜面となるようにすることを特徴とするものである。半導体基板と、前記半導体基板上に設けられた第1の樹脂膜と、前記第1の樹脂膜の周辺部を除く上面に設けられた第2の樹脂膜と、前記第2の樹脂膜上に設けられた渦巻き形状の薄膜誘導素子とを備えていることを特徴とするものである。

#### 【発明の効果】

#### 【0009】

この発明によれば、半導体基板上に設けられた第1の樹脂膜の少なくとも周辺部を除く上面に設けられた第2の樹脂膜上に薄膜誘導素子を設けているので、第1、第2の樹脂膜の合計厚さにより、半導体基板に発生する渦電流に起因する薄膜誘導素子の渦電流損を低減することができる。この場合、第2の樹脂膜は比較的安価な樹脂によって形成しているので、比較的安価である上、回路短絡を防止し、且つ、渦電流損低減の効果を均一に発揮することができる。

#### 【図面の簡単な説明】

#### 【0010】

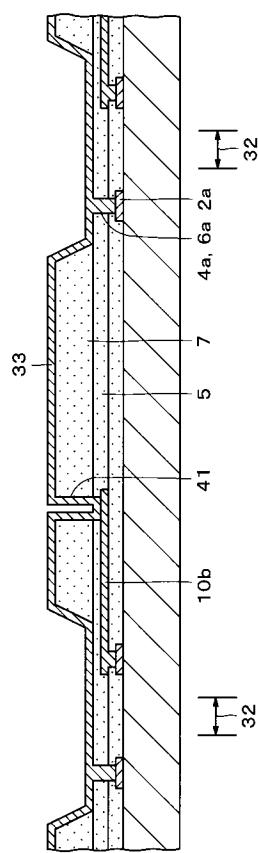

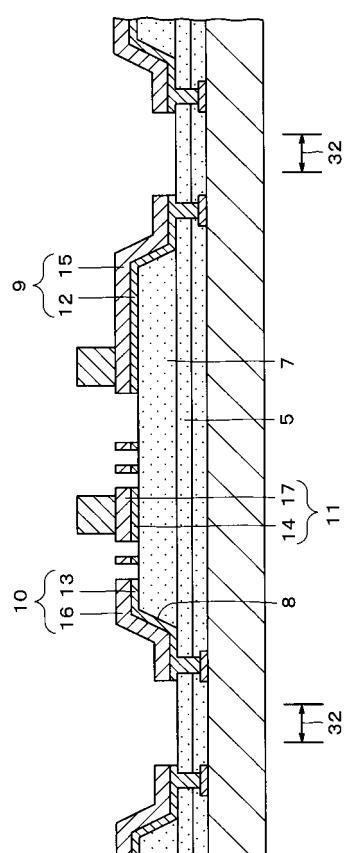

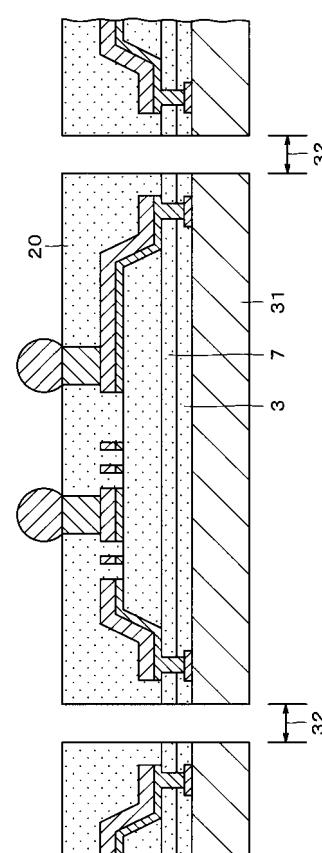

【図1】(A)はこの発明の第1実施形態としての半導体装置の要部の平面図(図1(B)における封止膜を除去した状態)、(B)はそのB-B線に沿う断面図。

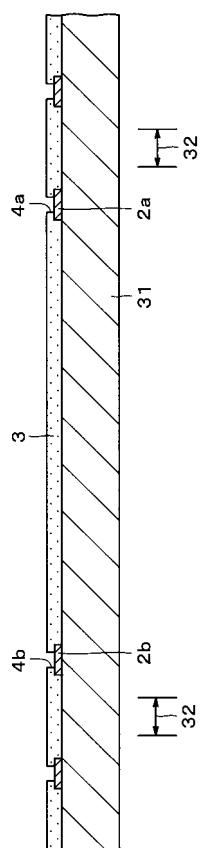

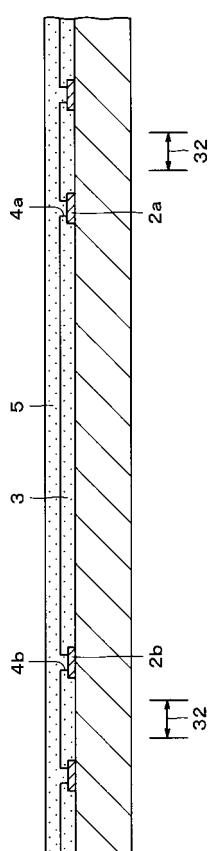

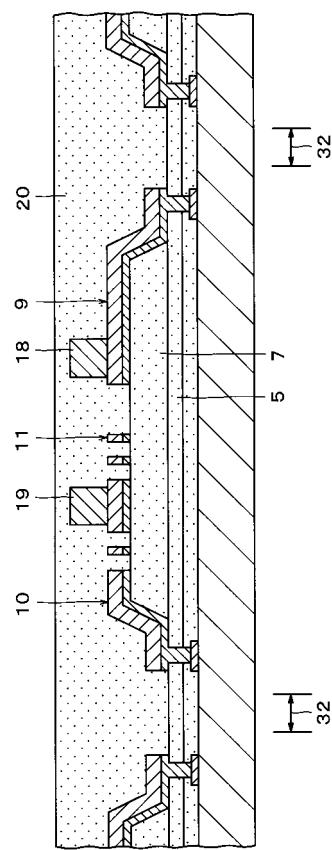

【図2】図1に示す半導体装置の製造方法の一例において、当初準備したものの断面図。

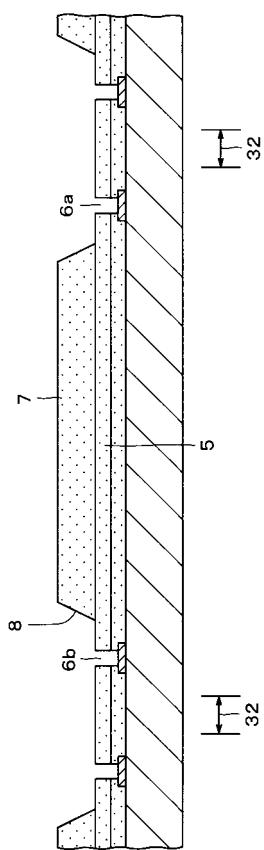

【図3】図2に続く工程の断面図。

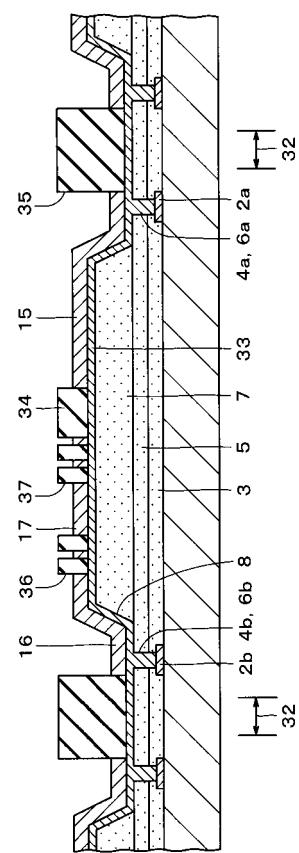

【図4】図3に続く工程の断面図。

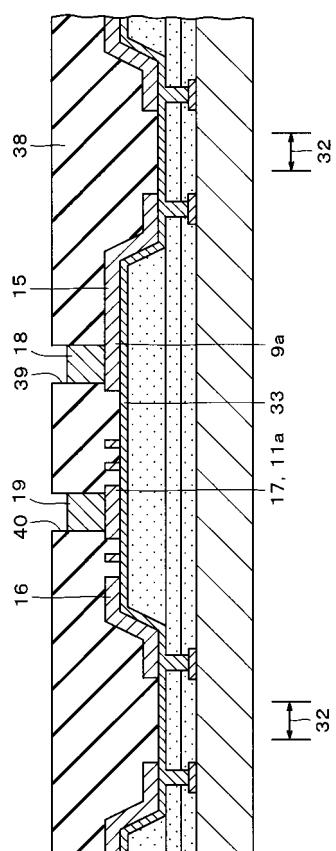

【図5】図4に続く工程の断面図。

【図6】図5に続く工程の断面図。

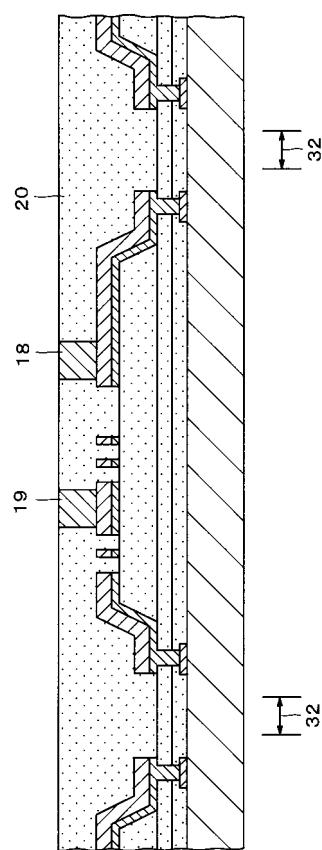

【図7】図6に続く工程の断面図。

10

20

30

40

50

【図 8】図 7 に続く工程の断面図。

【図 9】図 8 に続く工程の断面図。

【図 10】図 9 に続く工程の断面図。

【図 11】図 10 に続く工程の断面図。

【図 12】図 11 に続く工程の断面図。

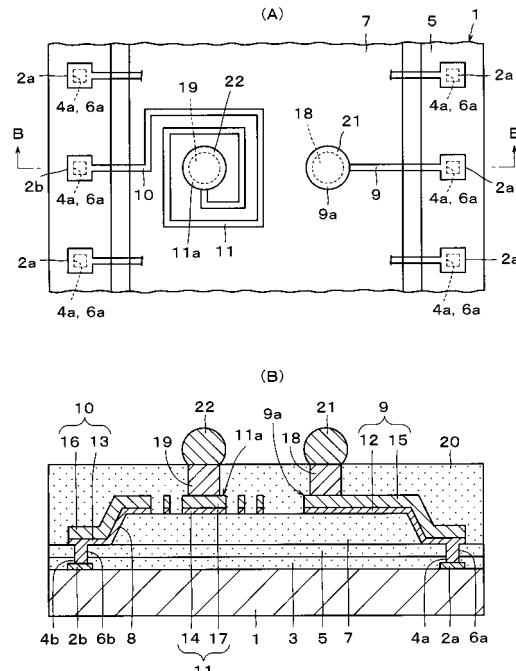

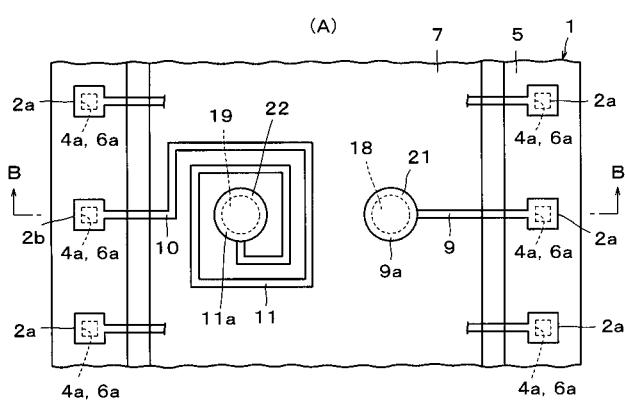

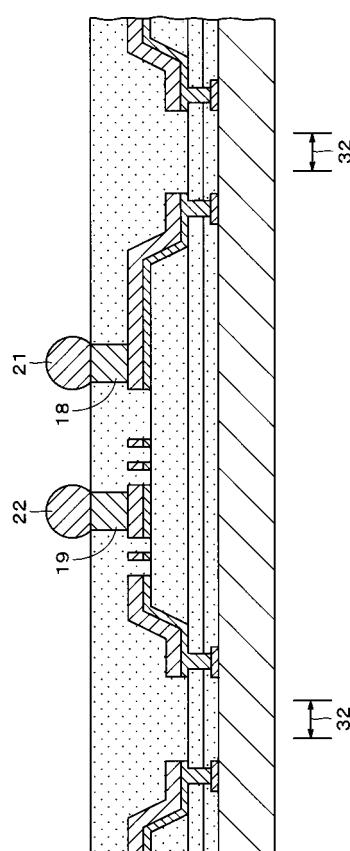

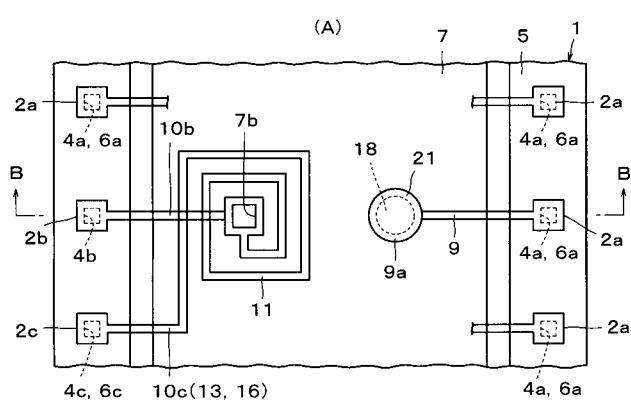

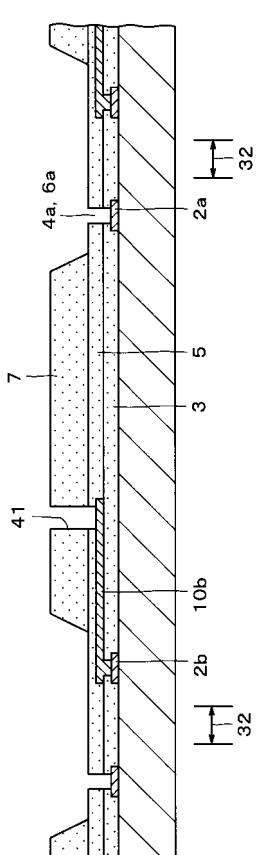

【図 13】(A) はこの発明の第 2 実施形態としての半導体装置の要部の平面図 (図 13 (B) における封止膜を除去した状態)、(B) はその B - B 線に沿う断面図。

【図 14】図 13 に示す半導体装置の製造方法の一例において、所定の工程の断面図。

【図 15】図 14 に続く工程の断面図。

【図 16】図 15 に続く工程の断面図。

【図 17】図 16 に続く工程の断面図。

【発明を実施するための形態】

【0011】

(第 1 実施形態)

図 1 (A) はこの発明の第 1 実施形態としての半導体装置の要部の平面図 (図 1 (B) における封止膜を除去した状態) を示し、図 1 (B) はその B - B 線に沿う断面図を示す。この半導体装置は、一般的には CSP と呼ばれるものであり、平面方形形状のシリコン基板 (半導体基板) 1 を備えている。シリコン基板 1 の上面には所定の機能の集積回路を構成する素子、例えば、トランジスタ、ダイオード、抵抗、コンデンサ等の素子 (図示せず) が設けられ、上面周辺部にはアルミニウム系金属等からなる複数の接続パッド 2a、2b が集積回路に接続されて設けられている。この場合、符号 2b で示す接続パッドは、後述する渦巻き形状の薄膜誘導素子 11 の外端部に接続されるものである。

【0012】

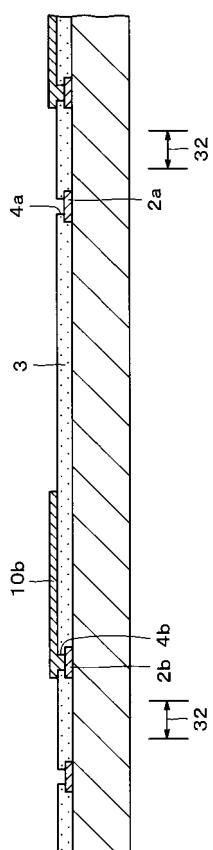

接続パッド 2a、2b の中央部を除くシリコン基板 1 の上面には酸化シリコン等からなるパッシベーション膜 3 が設けられ、接続パッド 2a、2b の中央部はパッシベーション膜 3 に設けられた開口部 4a、4b を介して露出されている。パッシベーション膜 3 の上面にはポリイミド系樹脂やポリベンザオキシドール等の樹脂からなる第 1 の保護膜 (第 1 の樹脂膜) 5 が設けられている。パッシベーション膜 3 の開口部 4a、4b に対応する部分における第 1 の保護膜 5 には開口部 6a、6b が設けられている。

【0013】

第 1 の保護膜 5 上における半導体基板 1 の上記接続パッドよりも内側領域、つまり開口部 6a、6b が設けられた周辺部を除く領域には、第 1 の保護膜 5 と同一の樹脂または異なる樹脂からなる第 2 の保護膜 (第 2 の樹脂膜) 7 が設けられている。この場合、第 2 の保護膜 7 の側面は傾斜面 8 となっている。

【0014】

ここで、第 1 の保護膜 5 の厚さは例えば 2 ~ 6 μm 程度と比較的薄いのに対し、第 2 の保護膜 7 の厚さはそれよりも厚く、例えば 8 ~ 14 μm 程度と 2 倍以上となっている。この場合、第 1 の保護膜 5 と第 2 の保護膜 7 の厚さの合計が 10 ~ 20 μm 程度とすればよく、必ずしも、第 2 の保護膜 7 の厚さを第 1 の保護膜 5 の厚さよりも大きくする必要は無いが、配線の高密度化のためには、開口部 6a、6b を形成する必要がある第 1 の保護膜 5 の厚さは、可能な限り薄い方が望ましい。

【0015】

第 1 の保護膜 5 の周辺部上面および第 2 の保護膜 7 の傾斜面 8 を含む上面には複数の配線 9 および 1 つの薄膜誘導素子用配線 10 が設けられ、第 2 の保護膜 7 の上面には渦巻き形状の薄膜誘導素子 11 が設けられている。配線 9、薄膜誘導素子用配線 10 および薄膜誘導素子 11 は、銅等からなる下地金属層 12、13、14 の上面に銅からなる上部金属層 15、16、17 が設けられた 2 層構造となっている。なお、薄膜誘導素子 11 の渦巻き形状は、図 1 (A) では、四角形状としているが、これよりも多角な角形状、円形状、橢円形状、多角形状と円弧形状の組合せ形状等としてもよい。また、渦巻き形状に限らず、ほぼ一重の環状としてもよい。

## 【0016】

配線 9 の一端部はパッシベーション膜 3 の開口部 4 a および第 1 の保護膜 5 の開口部 4 b を介して接続パッド 2 a に接続されている。薄膜誘導素子用配線 10 の一端部はパッシベーション膜 3 の開口部 4 b および第 1 の保護膜 5 の開口部 6 b を介して接続パッド 2 b に接続されている。薄膜誘導素子 11 の外端部は薄膜誘導素子用配線 10 の他端部に接続されている。配線 9 の他端部および薄膜誘導素子 11 の内端部は接続パッド部 9 a、11 a となっている。この場合、配線 9 の接続パッド部 9 a は第 2 の保護膜 7 の上面のみに設けられている。

## 【0017】

配線 9 および薄膜誘導素子 11 の接続パッド部 9 a、11 a の上面には銅からなる柱状電極 18、19 が設けられている。第 1 の保護膜 5 の周辺部上面、配線 9、薄膜誘導素子用配線 10 および薄膜誘導素子 11 の上面および第 2 の保護膜 7 の傾斜面 8 を含む上面にはエポキシ系樹脂等からなる封止膜 20 が設けられている。柱状電極 18、19 は、その上面が封止膜 20 の上面と面一乃至数  $\mu\text{m}$  低くなるように設けられている。柱状電極 18、19 の上面には半田ボール 21、22 が設けられている。

10

## 【0018】

以上のように、この半導体装置では、シリコン基板 1 上にパッシベーション膜 3 および第 1 の保護膜 5 を介して設けられた第 2 の保護膜 7 の上面に薄膜誘導素子 11 を設けているので、シリコン基板 1 に発生する渦電流に起因する薄膜誘導素子 11 の渦電流損を低減することができ、ひいては薄膜誘導素子 11 の特性劣化を抑制することができる。

20

## 【0019】

また、接続パッド 2 a、2 b に接続するための開口部 6 a、6 b を形成する第 1 の保護膜 5 上に第 2 の保護膜 7 を設けているので、高密度配線をすることができる。さらに、第 2 の保護膜 7 をポリイミド系樹脂等の比較的安価な樹脂によって形成しているので、比較的安価である上、回路短絡を防止し、且つ、渦電流損低減の効果を均一に発揮することができる。

## 【0020】

次に、この半導体装置の製造方法の一例について説明する。まず、図 2 に示すように、ウエハ状態のシリコン基板（以下、半導体ウエハ 31 という）の上面にアルミニウム系金属等からなる接続パッド 2 a、2 b および酸化シリコン等からなるパッシベーション膜 3 が形成され、接続パッド 2 a、2 b の中央部がパッシベーション膜 3 に形成された開口部 4 a、4 b を介して露出されたものを準備する。なお、図 2 において、符号 32 で示す領域はダイシングストリートである。

30

## 【0021】

次に、図 3 に示すように、パッシベーション膜 3 の開口部 4 a、4 b を介して露出された接続パッド 2 a、2 b の上面を含むパッシベーション膜 3 の上面に、スクリーン印刷法やスピンドルコート法等により、ポリイミド系樹脂やポリベンザオキシドール等の樹脂からなる第 1 の保護膜 5 を形成する。次に、図 4 に示すように、パッシベーション膜 3 の開口部 4 a、4 b に対応する部分における第 1 の保護膜 5 に、フォトリソグラフィ法により、開口部 6 a、6 b を形成する。

40

## 【0022】

次に、図 5 に示すように、ダイシングストリート 32 で囲まれた各半導体装置形成領域において、第 1 の保護膜 5 の周辺部つまり開口部 6 a、6 b が形成された周辺部を除く上面に、スクリーン印刷法により、第 1 の保護膜 5 と同一の樹脂または異なる樹脂からなる第 2 の保護膜 7 を形成する。この場合、スクリーン印刷法により塗布された液状樹脂膜の周辺部がだれることにより、第 2 の保護膜 7 の側面は傾斜面 8 となる。

## 【0023】

次に、図 6 に示すように、パッシベーション膜 3 および第 1 の保護膜 5 の開口部 4 a、6 a および開口部 4 b、6 b を介して露出された接続パッド 2 a、2 b の上面を含む第 1 の保護膜 5 の上面および第 2 の保護膜 7 の傾斜面 8 を含む上面に下地金属層 33 を形成す

50

る。この場合、下地金属層33は、無電解メッキにより形成された銅層のみであってもよく、またスパッタ法により形成された銅層のみであってもよく、さらにスパッタ法により形成されたチタン等の薄膜層上にスパッタ法により銅層を形成したものであってもよい。

#### 【0024】

次に、下地金属層33の上面にメッキレジスト膜34をパターン形成する。この場合、上部金属層15、16、17形成領域に対応する部分におけるメッキレジスト膜34には開口部35、36、37が形成されている。次に、下地金属層33をメッキ電流路とした銅の電解メッキを行なうことにより、メッキレジスト膜34の開口部35、36、37内の下地金属層33の上面に上部金属層15、16、17を形成する。次に、メッキレジスト膜34を剥離する。

10

#### 【0025】

次に、図7に示すように、上部金属層15、16、17および下地金属層33の上面にメッキレジスト膜38をパターン形成する。この場合、上部金属層15、17の接続パッド部9a、11aつまり柱状電極18、19形成領域に対応する部分におけるメッキレジスト膜38には開口部39、40が形成されている。次に、下地金属層33をメッキ電流路とした銅の電解メッキを行なうことにより、メッキレジスト膜38の開口部39、40内の上部金属層15、17の接続パッド部9a、11aの上面に柱状電極18、19を形成する。

20

#### 【0026】

次に、メッキレジスト膜38を剥離し、次いで、上部金属層15、16、17をマスクとして下地金属層33の不要な部分をエッチングして除去すると、図8に示すように、上部金属層15、16、17下にのみ下地金属層12、13、14が残存される。この状態では、上部金属層15、16、17およびその下に残存された下地金属層12、13、14により、2層構造の配線9、薄膜誘導素子用配線10および薄膜誘導素子11が形成されている。

20

#### 【0027】

なお、上記においては、配線9、薄膜誘導素子用配線10および薄膜誘導素子11をセミアディティブ法で形成する場合で説明したが、サブトラクト法により形成することもできる。その場合には、図6において、パッシベーション膜3および第1の保護膜5の開口部4a、6aおよび開口部4b、6bを介して露出された接続パッド2a、2bの上面を含む第1の保護膜5の上面および第2の保護膜7の傾斜面8を含む上面に下地金属層33を形成した後、該下地金属層33の上面全面に電解めっき法により上部金属形成用層を形成し、該上部金属形成用層上における上部15、16、17を形成する領域上にフォトレジストマスクを形成し、このフォトレジストマスクから露出された領域の上部金属形成用層および下地金属層33をエッチングすればよい。但し、このエッチングは、図7に示すように（但し、サブトラクト法の場合には、上部金属層15、16、17に代わって下地金属層33上全面に上部金属形成用層が形成されている）、柱状電極18、19を形成した後に行う。

30

#### 【0028】

ここで、配線9および薄膜誘導素子用配線10は第1、第2の保護膜5、7の上面に形成されているが、第2の保護膜7の側面が傾斜面8となっているので、配線9および薄膜誘導素子用配線10が断線しにくいようにすることができる。また、図6に示すように、下地金属層33を上面全体に形成するとき、下地金属層33を良好に形成することができる。

40

#### 【0029】

次に、図9に示すように、配線9、薄膜誘導素子用配線10、薄膜誘導素子11および柱状電極18、19を含む第1、第2の保護膜5、7の上面に、スクリーン印刷法やスピノコート法等により、エポキシ系樹脂等からなる封止膜20をその厚さが柱状電極18、19の高さよりも厚くなるように形成する。したがって、この状態では、柱状電極18、19の上面は封止膜20によって覆われている。

50

## 【0030】

次に、封止膜20の上面側を適宜に研削し、図10に示すように、柱状電極18、19の上面を露出させ、且つ、この露出された柱状電極18、19の上面を含む封止膜20の上面を平坦化する。次に、図11に示すように、柱状電極18、19の上面に半田ボール21、22を形成する。次に、図12に示すように、ダイシングストリート32に沿って、封止膜20、第1の保護膜5、パッシベーション膜3および半導体ウエハ31を切断すると、図1(A)、(B)に示す半導体装置が複数個得られる。

## 【0031】

ここで、図4に示すように、第2の保護膜7を第1の保護膜5の上面全体に形成せずに、ダイシングストリート32で囲まれた各半導体装置形成領域において、第1の保護膜5の周辺部つまり開口部6a、6bが形成された周辺部を除く上面に形成する理由および第1、第2の保護膜5、7の厚さについて説明する。

10

## 【0032】

第2の保護膜7を第1の保護膜5の上面全体に形成する場合には、接続パッド2a、2bを露出させるために、第1の保護膜5の開口部6a、6bに対応する部分における第2の保護膜7に開口部を形成する必要がある。しかるに、微細化に伴い、接続パッド2a、2bのピッチおよび平面サイズが小さくなった場合には、それに伴い、第1の保護膜5の開口部6a、6bおよび該開口部6a、6bに対応する部分における第2の保護膜7に形成する開口部のピッチおよび平面サイズも小さくなってしまう。これらの開口部をフォトロソグラフィ法により形成する場合には、第1、第2の保護膜3、7の合計厚さがかなり厚くなるので、解像度が悪くなり、好ましくない。

20

## 【0033】

そこで、この実施形態のように、第2の保護膜7を第1の保護膜5の上面全体に形成せずに、ダイシングストリート32で囲まれた各半導体装置形成領域において、第1の保護膜5の周辺部つまり開口部6a、6bが形成された周辺部を除く上面に形成すると、厚さが例えば2～6μm程度と比較的薄い第1の保護膜5のみに開口部6a、6bを形成すればよいので、微細化に対応することが可能となる。但し、第1の保護膜5の厚さはこれに限定されるものではない。また、上述した如く、渦電流損低減の効果を得るために、第1の保護膜5と第2の保護膜7の厚さの合計を10～20μm程度とすればよく、第2の保護膜7の厚さは、第1の保護膜5の厚さに対応して決定される。

30

## 【0034】

## (第2実施形態)

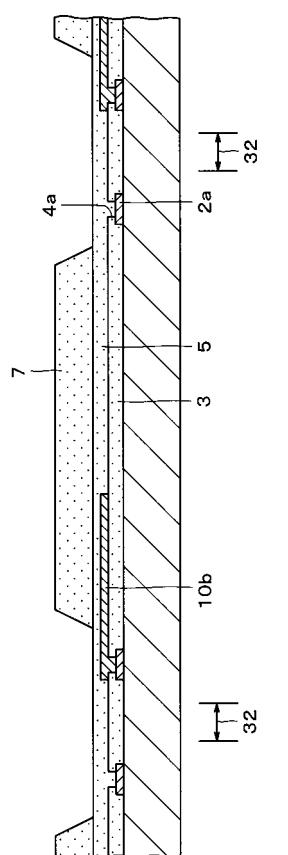

図13(A)はこの発明の第2実施形態としての半導体装置の要部の平面図(図13(B)における封止膜を除去した状態)を示し、図13(B)はそのB-B線に沿う断面図を示す。この半導体装置において、図1(A)、(B)に示す半導体装置と大きく異なる点は、渦巻き形状の薄膜誘導素子11の内端部のみならず外端部もシリコン基板1の上面に形成された集積回路(図示せず)に接続された接続パッドに接続するようにした点である。

## 【0035】

すなわち、符号2b、2cで示す接続パッドは、渦巻き形状の薄膜誘導素子13の内端部および外端部に接続されるものであり、図13(A)では互いに隣接して配置されている。接続パッド2a、2b、2cの中央部を除くシリコン基板1の上面にはパッシベーション膜3が設けられ、接続パッド2a、2b、2cの中央部はパッシベーション膜3に設けられた開口部4a、4b、4cを介して露出されている。

40

## 【0036】

パッシベーション膜3の上面には、接続パッド2a、2b、2cと異なる金属、例えばクロム系金属からなる薄膜誘導素子用(下層)配線10bが設けられている。薄膜誘導素子用配線10bの一端部は、パッシベーション膜3の開口部4bを介して接続パッド2bに接続されている。薄膜誘導素子用配線10bを含むパッシベーション膜3の上面には第1の保護膜5が設けられている。パッシベーション膜3の開口部4a、4cに対応する部

50

分における第1の保護膜5には開口部6a、6cが設けられている。

【0037】

第1の保護膜5の周辺部つまり開口部6a、6cが設けられた周辺部を除く上面には第2の保護膜7が設けられている。この場合も、第2の保護膜7の側面は傾斜面8となっている。また、第1の保護膜5の厚さおよび第2の保護膜7は、第1実施形態の場合と同様である。ここで、薄膜誘導素子用配線10bの接続パッド部に対応する部分における第1、第2の保護膜5、7には開口部41が設けられている。

【0038】

第1の保護膜5の周辺部上面および第2の保護膜7の傾斜面8を含む上面には複数の配線9および1つの薄膜誘導素子用配線10cが設けられ、第2の保護膜7の上面には渦巻き形状の薄膜誘導素子11が設けられている。配線9、薄膜誘導素子用配線10cおよび薄膜誘導素子11は、下地金属層12、13、14の上面に上部金属層15、16、17が設けられた2層構造となっている。

10

【0039】

配線9の一端部はパッシベーション膜3および第1の保護膜5の開口部4a、6aを介して接続パッド2aに接続されている。薄膜誘導素子用配線10cの一端部はパッシベーション膜3および第1の保護膜5の開口部4c、6cを介して接続パッド2cに接続されている。薄膜誘導素子11の内端部は第1、第2の保護膜5、7の開口部41を介して薄膜誘導素子用配線10bの接続パッド部に接続され、外端部は薄膜誘導素子用配線10cの他端部に接続されている。

20

【0040】

配線9の接続パッド部9aの上面には柱状電極18が設けられている。第1の保護膜5の周辺部上面、配線9、薄膜誘導素子用配線10cおよび薄膜誘導素子11の上面および第1の保護膜5の傾斜面8を含む上面には封止膜20が設けられている。柱状電極18の上面には半田ボール21が設けられている。

【0041】

以上のように、この半導体装置でも、シリコン基板1上にパッシベーション膜3および第1の保護膜5を介して設けられた第2の保護膜7の上面に薄膜誘導素子11を設けているので、シリコン基板1に発生する渦電流に起因する薄膜誘導素子11の渦電流損を低減することができ、ひいては薄膜誘導素子11の特性劣化を抑制することができる。

30

【0042】

次に、この半導体装置の製造方法の一例について説明する。この場合、図2に示すものを準備した後に、図14に示すように、パッシベーション膜3の上面に、スパッタ法等により成膜されたクロム系金属等からなる金属膜をフォトリソグラフィ法によりパターニングすることにより、薄膜誘導素子用配線10bを形成する。この状態では、薄膜誘導素子用配線10bの一端部は、パッシベーション膜3の開口部4bを介して接続パッド2bに接続されている。

【0043】

ここで、薄膜誘導素子用配線10bを接続パッド2a、2bと異なる金属によって形成するのは、パッシベーション膜3の開口部4aを介して接続パッド2aが露出されるため、この露出された接続パッド2aをエッチングしないようにするためである。なお、図13(A)において、符号2cで示す接続パッドについての説明は省略する。

40

【0044】

次に、図15に示すように、パッシベーション膜3の開口部4aを介して露出された接続パッド2aおよび薄膜誘導素子用配線10bを含むパッシベーション膜3の上面に、スクリーン印刷法やスピンドルコート法等により、第1の保護膜5を形成する。次に、ダイシングストリート32で囲まれた各半導体装置形成領域において、第1の保護膜5の周辺部を除く上面に、スクリーン印刷法により、第2の保護膜7を形成する。この場合も、スクリーン印刷法により塗布された液状樹脂膜の周辺部がだれることにより、第2の保護膜7の側面は傾斜面8となる。

50

## 【0045】

次に、図16に示すように、フォトリソグラフィ法により、パッシベーション膜3の開口部2aに対応する部分における第1の保護膜5に開口部6aを形成し、且つ、薄膜誘導素子用配線10bの接続パッド部に対応する部分における第1、第2の保護膜5、7に開口部41を形成する。この場合、第1、第2の保護膜5、7に形成する開口部41は、接続パッド2a、2bの微細化とは関係がないので、解像度の関係から平面サイズを比較的大きくしても、別に問題はない。

## 【0046】

次に、図17に示すように、パッシベーション膜3および第1の保護膜5の開口部4a、6aを介して露出された接続パッド2aの上面を含む第1の保護膜5の上面および第1、第2の保護膜5、7の開口部41を介して露出された薄膜誘導素子用配線10bの接続パッド部の上面を含む第2の保護膜7の傾斜面8を含む上面に下地金属層33を形成する。以下、上記第1実施形態の場合と同様の工程を経ると、図13(A)、(B)に示す半導体装置が複数個得られる。

10

## 【0047】

なお、第2実施形態において、薄膜誘導素子用配線10bの材料および構造を薄膜誘導素子用配線10cとは異なるものとして説明をしたが、両配線を同一の材料および構造としてもよいことは当然である。その場合には、図14に図示された、金属膜をフォトリソグラフィ法によりパターニングして薄膜誘導素子用配線10bを形成する工程において、接続パッド2aがエッチングされないように接続パッド2a上にマスクを形成した後、金属膜をフォトリソグラフィ法によりパターニングすればよい。

20

## 【0048】

また、上記各実施形態では、第2の保護膜7を、ダイシングストリート32で囲まれた各半導体装置形成領域において、第1の保護膜5の周辺部つまり開口部6a、6bが形成された周辺部を除く上面に形成する場合について説明したが、これに限定されるものではない。例えば、第2の保護膜7を薄膜誘導素子11の形成領域に対応する部分における第1の保護膜3の上面のみに形成するようにしてもよい。

20

## 【0049】

さらに、第2の保護膜7の形成はスクリーン印刷による場合で説明したが、第1の保護膜5の上面全体に、スピニコーティング、塗布、スクリーン印刷法等により被着した後、ウエットエッチングにより形成してもよい。この場合、等方的なエッチング液を用いることにより、第2の保護膜7の側面を好適な角度の傾斜面とすることができる。

30

## 【符号の説明】

## 【0050】

- |             |            |  |  |

|-------------|------------|--|--|

| 1           | シリコン基板     |  |  |

| 2 a、2 b、2 c | 接続パッド      |  |  |

| 3           | 絶縁膜        |  |  |

| 5           | 第1の保護膜     |  |  |

| 7           | 第2の保護膜     |  |  |

| 8           | 傾斜面        |  |  |

| 9           | 配線         |  |  |

| 10、10b、10c  | 薄膜誘導素子用配線  |  |  |

| 11          | 薄膜誘導素子     |  |  |

| 18、19       | 柱状電極       |  |  |

| 20          | 封止膜        |  |  |

| 21、22       | 半田ボール      |  |  |

| 31          | 半導体ウエハ     |  |  |

| 32          | ダイシングストリート |  |  |

| 33          | 下地金属層      |  |  |

40

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 図 6 】

【 図 7 】

【 図 8 】

【図9】

【図10】

【図11】

【図12】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図17】