(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 26 141 T2 2009.05.20

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 402 340 B1

(51) Int Cl.<sup>8</sup>: **G06F 5/06** (2006.01)

(21) Deutsches Aktenzeichen: **602 26 141.4**

(86) PCT-Aktenzeichen: **PCT/US02/14555**

(96) Europäisches Aktenzeichen: **02 734 283.1**

(87) PCT-Veröffentlichungs-Nr.: **WO 2003/001360**

(86) PCT-Anmeldetag: **07.05.2002**

(87) Veröffentlichungstag

der PCT-Anmeldung: **03.01.2003**

(97) Erstveröffentlichung durch das EPA: **31.03.2004**

(97) Veröffentlichungstag

der Patenterteilung beim EPA: **16.04.2008**

(47) Veröffentlichungstag im Patentblatt: **20.05.2009**

(30) Unionspriorität:

**885574 20.06.2001 US**

(84) Benannte Vertragsstaaten:

**DE, FR, GB, IT**

(73) Patentinhaber:

**Freescale Semiconductor, Inc., Austin, Tex., US**

(72) Erfinder:

**KIM, John J., Mountain View, CA 94040, US;**

**COLLINS, Richard G., Austin, TX 78729, US**

(74) Vertreter:

**Schumacher & Willsau Patentanwaltsgesellschaft mbH, 80335 München**

(54) Bezeichnung: **FIFO-SPEICHER SYSTEM UND VERFAHREN DAFÜR**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****Gebiet der Erfindung**

**[0001]** Die vorliegende Erfindung bezieht sich im Allgemeinen auf integrierte Schaltungen mit einer Speichersystemspeicherung und im Besonderen auf integrierte Schaltungen, die FIFO-Speicherstrukturen verwenden.

**Hintergrund der Erfindung**

**[0002]** In einem Echtzeit-Debug-System, das auf einem Datenverarbeitungssystem auf einer integrierten Schaltung implementiert ist, ist es notwendig, zuerst die Debug-Nachrichten zu speichern, bevor die Nachrichten an eine Vorrichtung zur Fehlerbeseitigung ausgegeben werden. Im Allgemeinen wird ein FIFO-Speichersystem verwendet, um die Debug-Nachrichten vorübergehend zu speichern. Einige der Nachrichten können über mehrere Einträge verfügen, die gleichzeitig gespeichert werden müssen, und andere müssen einzeln gespeichert werden.

**[0003]** Um beide Arten von Nachrichten in der selben FIFO-Struktur zu speichern, können ein Dual-Port-FIFO oder getrennte, dedizierte FIFOs verwendet werden. Ein Dual-Port-FIFO erfordert jedoch einen zu implementierenden großen Oberflächenbereich, weil Multiplexer für jeden Eintrag des FIFOs erforderlich sind, um eine Speicherung von beiden Nachrichtenarten zu erlauben. Außerdem erfordert die große Zahl von Multiplexern einen beträchtlichen Umfang an Logik, um die Multiplexerselektleitungen zu steuern, mit einer entsprechenden Zunahme des Stromverbrauchs aufgrund einer logischen Verschaltung.

**[0004]** Ein anderer Weg, um das FIFO-Speichersystem zu implementieren, besteht darin, zwei getrennte dedizierte FIFOs zu verwenden. Zum Beispiel kann ein FIFO nur Adresseninformationen und ein anderer FIFO nur Daten empfangen. Dies hat den Vorteil eines kleineren Oberflächenbereichs auf einer integrierten Schaltung und einer geringeren Konstruktionskomplexität. Allerdings kann er zu einer weniger effizienten FIFO-Ausnutzung führen, im Vergleich zu dem Dual-Port-FIFO, weil es sein kann, dass einer der FIFOs voll wird und überfließt, während der andere FIFO nicht voll ist.

**[0005]** Das japanische Patent JP 59177782 offenbart einen Pufferspeicher mit zwei abgegrenzten Teilen. Ein Teil des Pufferspeichers wird ausgewählt, um, basierend auf den niedrigsten Bit einer Anforderungsadresse, beschrieben zu werden. Das Dokument D2 (EP 0 869 431) offenbart ein serielles Kommunikationssystem mit Puffern, auf die gleichzeitig oder sequenziell zugegriffen werden kann.

**[0006]** Daher wäre es wünschenswert, über ein FIFO-Speichersystem und -verfahren zu verfügen, die ihren Speicherbereich effizient verwenden, während außerdem die Steuerlogik, die erforderlich, um sie zu implementieren, minimiert wird. Ein solches System und Verfahren werden in dem Anspruch 1 beziehungsweise dem Anspruch 7 beansprucht.

**Kurze Beschreibung der Zeichnungen**

**[0007]** Die vorliegende Erfindung wird in den begleitenden Zeichnungen beispielhaft und nicht beschränkend dargestellt, wobei gleiche Bezugszeichen gleiche Elemente anzeigen.

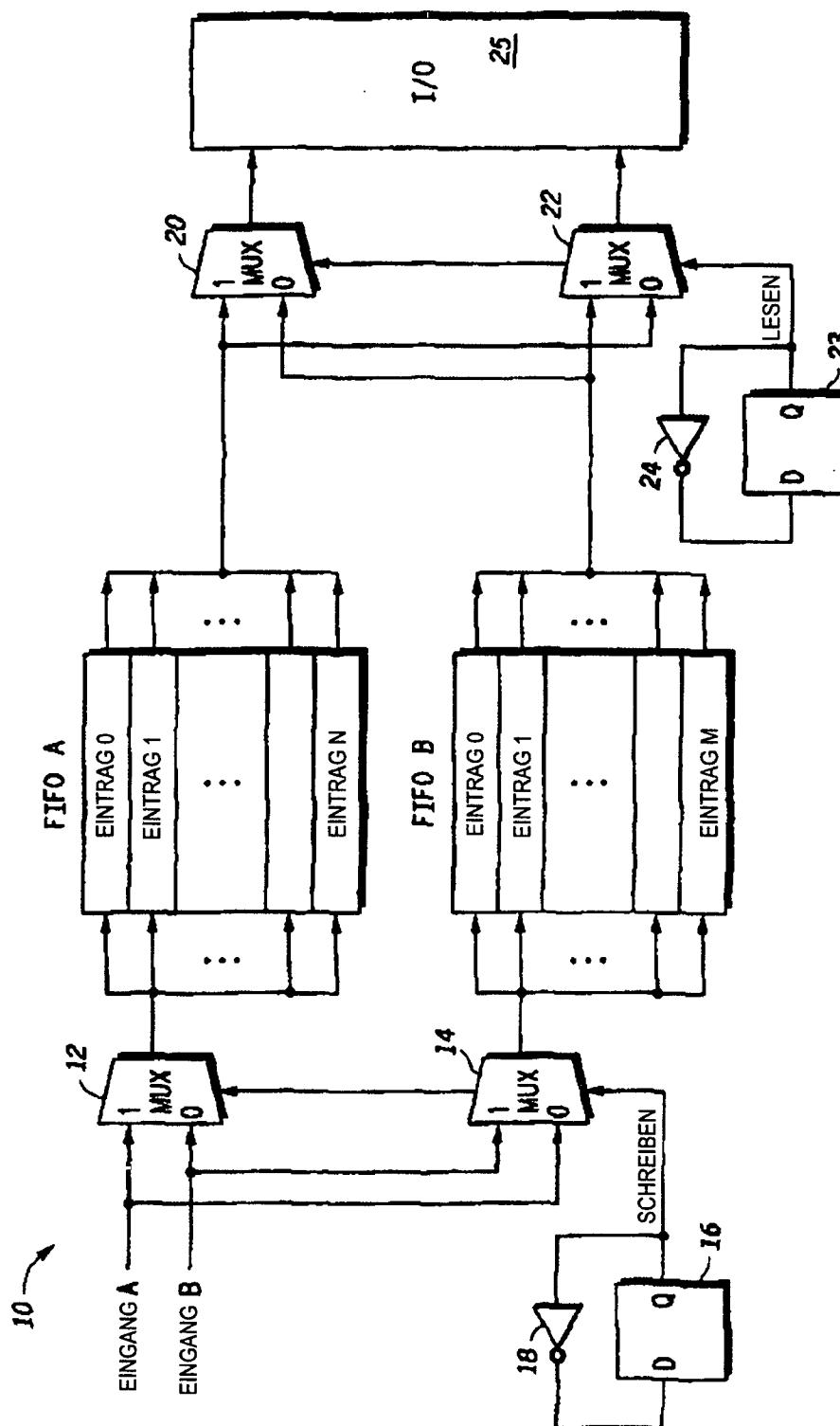

**[0008]** [Fig. 1](#) stellt ein FIFO-Speichersystem gemäß einer Ausführungsform der vorliegenden Erfindung in der Form eines Blockdiagramms dar; und

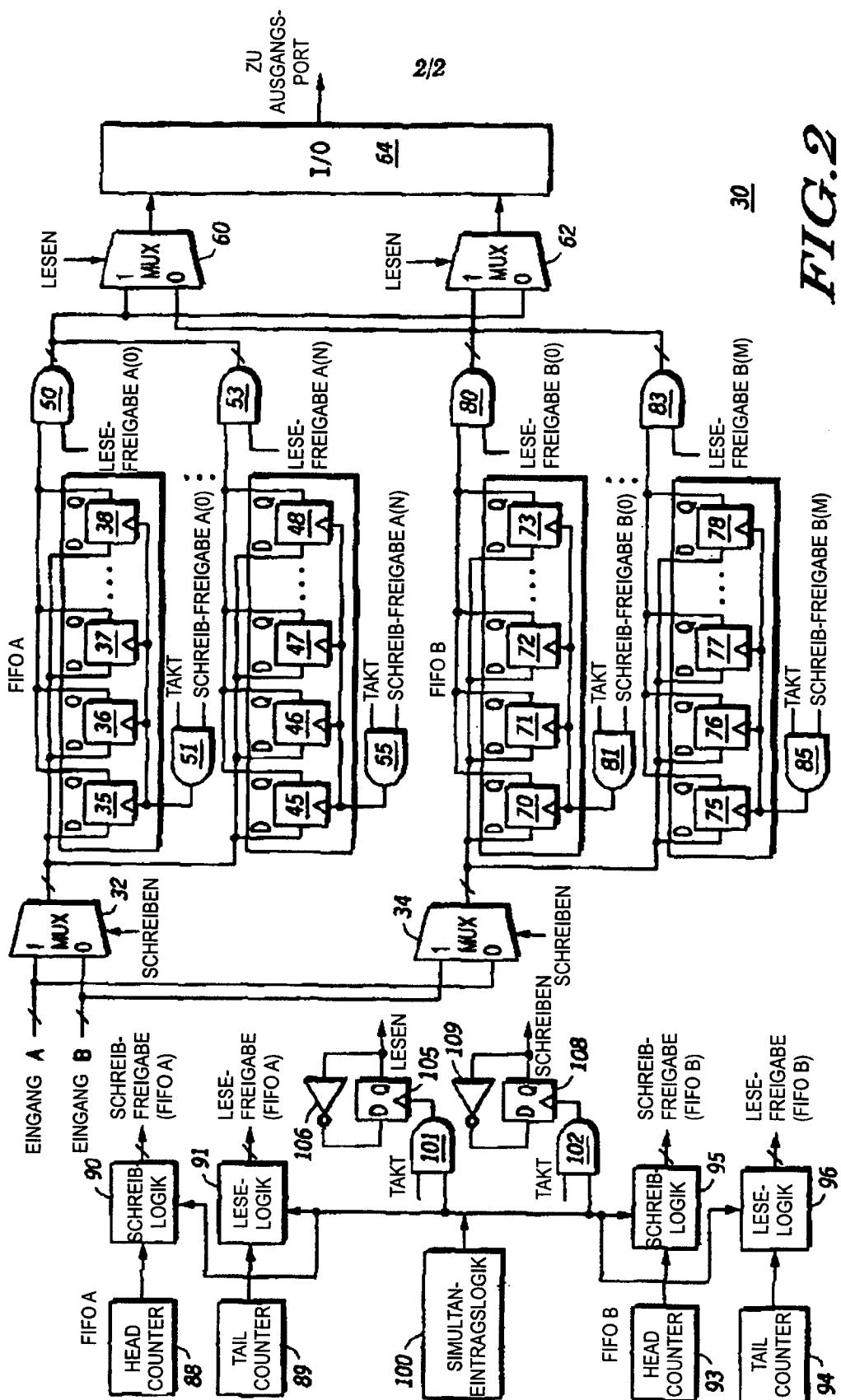

**[0009]** [Fig. 2](#) stellt weitere Einzelheiten des FIFO-Systems von [Fig. 1](#) in der Form eines Blockdiagramms dar.

**[0010]** Dem Fachmann auf dem Gebiet ist klar, dass die Elemente in den Zeichnungen der Einfachheit und Klarheit halber dargestellt werden und nicht notwendigerweise maßstabsgetreu gezeichnet worden sind. Zum Beispiel können die Dimensionen einiger der Elemente in den Zeichnungen relativ zu anderen Elementen übertrieben dargestellt sein, um dazu beizutragen, dass das Verständnis der Ausführungsformen der vorliegenden Erfindung verbessert wird.

**Ausführliche Beschreibung**

**[0011]** In [Fig. 1](#) wird ein FIFO-Speichersystem **10** gemäß der vorliegenden Erfindung dargestellt. In einer Form verfügt das FIFO-Speichersystem **10** über zwei FIFOs, die als ein FIFO A und ein FIFO B dargestellt werden. Es soll klar sein, dass das FIFO-Speichersystem **10** mit einer beliebigen Zahl von FIFOs implementiert werden kann. Sowohl der FIFO A als auch der FIFO B verfügen über eine beliebige Zahl von Speichereinträgen. Es wird angenommen, dass der FIFO A N Einträge und der FIFO B M Einträge hat, wobei N und M ganzzahlige Werte sind. Ein Eingang A ist an einen ersten Eingang eines Multiplexers **12** und an einen ersten Eingang eines Multiplexers **14** angeschlossen. Ein Eingang B ist an einen zweiten Eingang des Multiplexers **12** und einen zweiten Eingang des Multiplexers **14** angeschlossen. Eine Flip-Flop-Schaltung vom Typ D **16**, bei einem Ausgang der Flip-Flop-Schaltung **16** bereitgestellt, stellt ein SCHREIB-Signal zur Verfügung, das an einen Steuereingang eines jeden der Multiplexer **12** und **14** angeschlossen ist. Der Ausgang der Flip-Flop-Schaltung **16** ist an einen Eingang eines Invertierers **18** angeschlossen. Ein Ausgang des Invertierers **18** ist an einen D-Eingang der Flip-Flop-Schaltung **16** angeschlossen. Ein Ausgang des Multiple-

xers **12** ist an jeden Eintrag, wie zum Beispiel Eintrag 0, Eintrag 1 bis Eintrag N, des FIFO A angeschlossen. Ein Ausgang des Multiplexers **14** ist an jeden Eintrag, wie zum Beispiel Eintrag 0, Eintrag 1 bis Eintrag M, des FIFO B angeschlossen. Jeder Eintrag des FIFO A verfügt außerdem über einen Ausgangsanschluss, der zusammengeschaltet und an einen ersten Eingang des Multiplexers **20** angeschlossen ist. Jeder Eintrag des FIFO B verfügt außerdem über einen Ausgangsanschluss, der zusammengeschaltet und an einen ersten Eingang des Multiplexers **22** angeschlossen ist. Der Ausgangsanschluss des FIFO A ist außerdem an einen zweiten Eingang des Multiplexers **20** angeschlossen.

**[0012]** Der Ausgangsanschluss des FIFO B ist außerdem an einen zweiten Eingang des Multiplexers **20** angeschlossen. Eine Flip-Flop-Schaltung vom Typ D **23** verfügt über einen Q-Ausgang zum Bereitstellen eines LESE-Steuersignals, das an einen Steueranschluss eines jeden der Multiplexer **20** und **22** angeschlossen ist. Der Ausgang der Flip-Flop-Schaltung **23** ist an einen Eingang eines Invertierers **24** angeschlossen. Ein Ausgang des Multiplexers **20** ist an einen ersten Eingang einer Eingabe/Ausgabe (I/O)-Einheit **25** angeschlossen. Ein Ausgang des Multiplexers **22** ist an einen zweiten Eingang der Eingabe/Ausgabe-Einheit **25** angeschlossen. Die Eingabe/Ausgabe-Einheit koppelt mit einem I/O-Anschluss (nicht gezeigt).

**[0013]** Unter Betriebsbedingungen ist das FIFO-Speichersystem **10** in der Lage, mehrere Einträge gleichzeitig in einer effizienten Manier zu schreiben. Ein einzelner Multiplexer, wie zum Beispiel entweder der Multiplexer **12** oder der Multiplexer **14**, wird bei jedem Schreib-Port oder Eingangsanschluss jeweils entweder des FIFO A oder des FIFO B angeordnet. Zu Erklärungszwecken wird angenommen, dass bei dem Eingang A und Eingang B Informationen in der Form von Paketen empfangen werden. Ein einzelnes Paket oder ein Teil von Daten können nur in einen der FIFOs, FIFO A oder FIFO B, von entweder dem Eingang A oder dem Eingang B in einer Art und Weise geschrieben werden, wie unten in Verbindung mit [Fig. 2](#) beschrieben.

**[0014]** Wie in [Fig. 1](#) dargestellt, können zwei Pakete oder Teile von Daten von dem Eingang A und dem Eingang B gleichzeitig in den FIFO A und in den FIFO B geschrieben werden. Die Flip-Flop-Schaltung **16** funktioniert als ein Ein-Bit-Schreib-Register und das SCHREIB-Steuersignal wird verwendet, um auf den FIFO A oder den FIFO B zu zeigen. Wenn das SCHREIB-Steuersignal über einen "logisch Eins"-Wert verfügt, wählt der Multiplexer **12** den Eingang A aus, um ihn als einen Ausgang zur Verfügung zu stellen, und der Multiplexer **14** den Eingang B aus, um ihn als einen Ausgang zur Verfügung zu stellen. Wenn das SCHREIB-Steuersignal über einen "lo-

gisch Null"-Wert verfügt, wählt der Multiplexer **12** den Eingang B aus, um ihn als einen Ausgang zur Verfügung zu stellen, und der Multiplexer **14** den Eingang A aus, um ihn als einen Ausgang zur Verfügung zu stellen. Weiterhin funktioniert der Invertierer **18**, um den logischen Zustand der Flip-Flop-Schaltung **16** immer dann umzudrehen, wenn eine Einzeleintrags-Schreib-Operation stattfindet, wie durch ein Schreib-Gleichlaufsignal (nicht gezeigt) gesteuert, das an einen Takteingang (nicht gezeigt) der Flip-Flop-Schaltung **16** angeschlossen ist. Zusätzlich bleibt der logische Zustand der Flip-Flop-Schaltung **16** der selbe, wenn es erforderlich sein sollte, dass ein Betrieb in dem FIFO-Speichersystem **10** zwei Schreib-Operationen gleichzeitig durchführt. Für ein gleichzeitiges Schreiben, können Informationen von jedem der Eingänge A und B oder Informationen, die nacheinander an nur einen der Eingänge A oder B gekoppelt werden, in den FIFO A und den FIFO B geschrieben werden. In einer ähnlichen Art und Weise funktioniert die Flip-Flop-Schaltung **23** für eine Einzeleintrags-Lese-Operation als ein Ein-Bit-Lese-Register und das LESE-Steuersignal wird verwendet, um auf einen der FIFOs A oder B zu zeigen. Wenn das LESE-Steuersignal über einen "logisch Eins"-Wert verfügt, wählt der Multiplexer **20** den Ausgang des FIFO A aus, um ihn als einen Ausgang zur Verfügung zu stellen, und der Multiplexer **22** wählt den Ausgang des FIFO B aus, um ihn als einen Ausgang zur Verfügung zu stellen. Wenn das LESE-Steuersignal über einen "logisch Null"-Wert verfügt, wählt der Multiplexer **20** den Ausgang des FIFO B aus, um ihn als einen Ausgang zur Verfügung zu stellen, und der Multiplexer **22** wählt den Ausgang des FIFO A aus, um ihn als einen Ausgang zur Verfügung zu stellen. Das LESE-Steuersignal wird in Reaktion auf ein Lese-Gleichlaufsignal (nicht gezeigt) erzeugt, das an einen Takteingang (nicht gezeigt) der Flip-Flop-Schaltung **23** angeschlossen ist. Weiterhin funktioniert der Invertierer **24**, um den logischen Zustand der Flip-Flop-Schaltungen immer dann umzudrehen, wenn eine Einzel-Lese-Operation stattfindet. Zusätzlich bleibt der logische Zustand der Flip-Flop-Schaltung **23** der selbe, wenn zwei Lese-Operationen gleichzeitig stattfinden. Die Flip-Flop-Schaltung **23**, der Invertierer **24** und die Multiplexer **20** und **22** funktionieren, um das Lesen von zwei Paketen oder Teilen von Daten von dem FIFO A und dem FIFO B zur gleichen Zeit zu erlauben. Zusätzlich kann ein einzelnes Paket oder ein Teil von Daten aus beiden FIFOs über dem Ausgang von entweder dem Multiplexer **20** oder dem Multiplexer **22** gelesen werden. Daher ist das FIFO-Speichersystem **10** sehr effizient zum gleichzeitigen Speichern von mehreren Einträgen, um bestimmte Verarbeitungsoperationen zu implementieren, und zum Speichern einzelner Einträge, wenn andere Verarbeitungsoperationen implementiert werden, weil die selbe FIFO-Speicherstruktur verwendet werden kann, um beide Arten von Operationen abzuschließen.

**[0015]** Die Verwendung von nur einer einzigen Multiplexerschaltung für jeden FIFO, um eine Schreib-Operation in jeden FIFO durchzuführen, stellt eine beträchtliche Kostenersparnis dar. Eine zusätzliche Steuerschaltung wird vermieden, zusätzlich zu einem Vermeiden eines Multiplexers pro FIFO-Eintrag. Als ein Ergebnis wird, aufgrund der geringen Zahl von verwendeten Multiplexern, eine beachtliche Einsparung beim Leistungsverbrauch zur Verfügung gestellt. Eine zusätzliche Leistungseinsparung resultiert außerdem aus einer verringerten Zahl an Steuerschaltungen, die nicht benötigt werden, wenn Multiplexer eliminiert werden. Die vorliegende Erfindung ist außerdem skalierbar, um mehrere FIFOs zu verwenden, wobei nur ein Multiplexer pro FIFO erforderlich ist, um einzelne und gleichzeitige Schreib-Operationen in dem System zu implementieren, und nur ein Multiplexer pro FIFO ist erforderlich, um einzelne und gleichzeitige Lese-Operationen in dem System zu implementieren. Obwohl nur ein Multiplexer zum Zuführen von zu schreibenden Informationen an jeden FIFO angeschlossen ist, können Informationen von entweder dem Eingang A oder dem Eingang B in entweder den FIFO A oder den FIFO B geschrieben werden. Es sollte klar sein, dass der Eingang A und der Eingang B Informationen in der Form von Daten, Adresseninformationen, Steuerinformationen, oder einer Kombination von zwei oder mehr empfangen und speichern können. Zusätzlich kann das Wort "Daten" alle Arten von Informationen umfassen, die in den dargestellten FIFOs gespeichert werden.

**[0016]** In [Fig. 2](#) wird eine Ausführungsform des FIFO-Speichersystems **10** von [Fig. 1](#) ausführlicher dargestellt. Wie in [Fig. 2](#) dargestellt, verfügt ein FIFO-Speichersystem **30** wieder über einen Eingang A und einen Eingang B zum Empfangen von in den FIFO A und/oder FIFO B zu speichernden Informationen. Ein Multiplexer **32** verfügt über einen ersten Eingang, der an den Eingang A angeschlossen ist, und über einen zweiten Eingang, der an den Eingang B angeschlossen ist. Ein Multiplexer **34** verfügt über einen ersten Eingang, der an den Eingang A angeschlossen ist, und über einen zweiten Eingang, der an den Eingang B angeschlossen ist. Ein Ausgang des Multiplexers **32** ist an jeden einer Mehrzahl von N Einträgen des FIFO A angeschlossen. Ein erster Eintrag des FIFO A verfügt über eine Mehrzahl von Flip-Flop-Schaltungen, wie zum Beispiel die Flip-Flop-Schaltungen **35–38**. Ein Nter Eintrag des FIFO A verfügt über eine Mehrzahl von Flip-Flop-Schaltungen, wie zum Beispiel die Flip-Flop-Schaltungen **45–48**. Jede der Flip-Flop-Schaltungen **35–38** und **45–48** verfügt über einen D-Eingang, der an den Ausgang des Multiplexers **32** angeschlossen ist. Jede der Flip-Flop-Schaltungen **35–38** verfügt über einen Q-Ausgang, der an einen ersten Eingang eines UND-Gates **50** angeschlossen ist. Ein zweiter Eingang des UND-Gates

**50** ist an ein LESE-FREIGABE A(0)-Signal angeschlossen, das das erste Lese-Freigabesignal des FIFO A bedeutet. Ein UND-Gate **51** verfügt über einen ersten Eingang zum Empfangen eines Taktsignals, einen zweiten Eingang zum Empfangen eines SCHREIB-FREIGABE A(0)-Signals (das das erste Schreib-Freigabesignal für den FIFO A bedeutet) und einen Ausgang, der an jeden Takteingang der Flip-Flop-Schaltungen **35–38** angeschlossen ist. Jede der Flip-Flop-Schaltungen **45–49** verfügt über einen Q-Ausgang, der an einen ersten Eingang eines UND-Gates **53** angeschlossen ist. Ein zweiter Eingang des UND-Gates **53** ist an ein LESE-FREIGABE A(N)-Signal angeschlossen, das das Nte Lese-Freigabesignal des FIFO A bedeutet. Ein UND-Gate **55** verfügt über einen ersten Eingang zum Empfangen des Taktsignals, einen zweiten Eingang zum Empfangen eines SCHREIB-FREIGABE AN-Signals (das das Nte Schreib-Freigabesignal für den FIFO A bedeutet) und einen Ausgang, der an jeden Taktsignal-eingang der Flip-Flop-Schaltungen **45–48** angeschlossen ist. Ein Ausgang des UND-Gates **50** ist an einen Ausgang des UND-Gates **53**, an einen ersten Eingang eines Multiplexers **60** und einen ersten Eingang des Multiplexers **62** angeschlossen. Ein Ausgang des Multiplexers **60** ist an einen ersten Eingang einer Eingabe/Ausgabe (I/O)-Einheit **64** angeschlossen.

**[0017]** Ein Ausgang des Multiplexers **34** ist an jeden einer Mehrzahl von M Einträgen des FIFO B angeschlossen. Ein erster Eintrag des FIFO B verfügt über eine Mehrzahl von Flip-Flop-Schaltungen, wie zum Beispiel die Flip-Flop-Schaltungen **70–73**. Ein Mter Eintrag des FIFO B verfügt über eine Mehrzahl von Flip-Flop-Schaltungen, wie zum Beispiel die Flip-Flop-Schaltungen **75–78**. Jede der Flip-Flop-Schaltungen **70–73** und **75–78** verfügt über einen D-Eingang, der an den Ausgang des Multiplexers **34** angeschlossen ist. Jede der Flip-Flop-Schaltungen **70–73** verfügt über einen Q-Ausgang, der an einen ersten Eingang eines UND-Gates **80** angeschlossen ist. Ein zweiter Eingang des UND-Gates **80** ist an ein LESE-FREIGABE B(0)-Signal angeschlossen, das das erste Lese-Freigabesignal des FIFO B bedeutet. Ein UND-Gate **81** verfügt über einen ersten Eingang zum Empfangen des Taktsignals, einen zweiten Eingang zum Empfangen eines SCHREIB-FREIGABE B(0)-Signals (das das erste Schreib-Freigabesignal für den FIFO B bedeutet) und einen Ausgang, der an jeden Takteingang der Flip-Flop-Schaltungen **70–73** angeschlossen ist. Jede der Flip-Flop-Schaltungen **75–79** verfügt über einen Q-Ausgang, der an einen ersten Eingang eines UND-Gates **83** angeschlossen ist. Ein zweiter Eingang des UND-Gates **83** ist an ein LESE-FREIGABE B(M)-Signal angeschlossen, das das Mte Lese-Freigabesignal des FIFO B bedeutet. Ein UND-Gate **85** verfügt über einen ersten Eingang zum Empfangen des Taktsignals, einen zweiten Eingang zum Emp-

fangen eines SCHREIB-FREIGABE B(M)-Signals (das das Mte Schreib-Freigabesignal für den FIFO B bedeutet), und einen Ausgang, der an jeden Takteingang der Flip-Flop-Schaltungen **75–78** angeschlossen ist. Ein Ausgang des UND-Gates **80** ist an einen Ausgang des UND-Gates **83**, an einen zweiten Eingang eines Multiplexers **60** und an einen zweiten Eingang eines Multiplexers **62** angeschlossen. Ein Ausgang des Multiplexers **62** ist an einen zweiten Eingang einer Eingabe/Ausgabe (I/O)-Einheit **64** angeschlossen. Die Eingabe/Ausgabe-Einheit **64** verfügt über einen Ausgang, der an einen Ausgangs-Port angeschlossen ist. In einer Form ist der Ausgang der Eingabe/Ausgabe-Einheit **64** an ein Nexus-fähiges Software-Tool zu Fehlerbeseitigungszwecken bei einem Implementieren des IEEE ISTO 5001-Standards angeschlossen.

**[0018]** Zusätzlich verfügt das FIFO-Speichersystem **30** über eine "Head Counter"-Schaltung **88**, eine "Tail Counter"-Schaltung **89**, die Schreib-Steuerlogikschaltung **90** und die mit dem FIFO A verknüpfte Lese-Steuerlogikschaltung **91**. Das FIFO-Speichersystem **30** verfügt über einen "Head Counter" **93**, eine "Tail Counter"-Schaltung **94**, die Schreib-Steuerlogikschaltung **95** und die Lese-Steuerlogikschaltung **96**. Der Head Counter **88** und der Tail Counter **89** verfügen jeweils über einen Ausgang, der an einen Eingang der Schreib-Steuerlogikschaltung **90** beziehungsweise der Lese-Steuerlogikschaltung **91** angeschlossen ist. Ein Ausgang der Schreib-Steuerlogikschaltung **90** stellt ein Schreib-Freigabesignal für die FIFO A und ein erster Ausgang der Lese-Steuerlogikschaltung **91** ein Lese-Freigabesignal für den FIFO A zur Verfügung. Der Head Counter **93** und der Tail Counter **94** verfügen jeweils über einen Ausgang, der an einen Eingang der Schreib-Steuerlogikschaltung **95** beziehungsweise der Lese-Steuerlogikschaltung **96** angeschlossen ist. Ein Ausgang der Schreib-Steuerlogikschaltung **95** stellt ein Schreib-Freigabesignal für den FIFO B und ein erster Ausgang der Lese-Steuerlogikschaltung **96** ein Lese-Freigabesignal für den FIFO B zur Verfügung. Ein zweiter Ausgang der Lese-Steuerschaltung **96** ist an einen zweiten Eingang der Schreib-Steuerlogikschaltung **95** angeschlossen. Eine Simultaneintragslogikschaltung **100** verfügt über einen Ausgang, der an einen zweiten Eingang der Lese-Steuerlogikschaltung **91**, einen zweiten Eingang der Schreib-Steuerlogikschaltung **90**, einen zweiten Eingang der Schreib-Steuerlogikeinheit **95**, einen ersten Eingang eines UND-Gates **101**, einen ersten Eingang eines UND-Gates **102** und einen zweiten Eingang der Lese-Steuerlogikschaltung **96** angeschlossen ist. Das Taktsignal ist an einen zweiten Eingang sowohl des UND-Gates **101** als auch des UND-Gates **102** angeschlossen. Ein Ausgang des UND-Gates **101** ist an einen Takteingang einer Flip-Flop-Schaltung **105** angeschlossen. Ein Q-Ausgang der Flip-Flop-Schaltung **105** stellt ein LESE-Signal zur Verfügung und ist

an einen Eingang eines Invertierers **106** angeschlossen. Ein Ausgang des Invertierers **106** ist an einen D-Eingang der Flip-Flop-Schaltung **105** angeschlossen. Ein Ausgang des UND-Gates **102** ist an einen Takteingang einer Flip-Flop-Schaltung **108** angeschlossen. Ein Q-Ausgang der Flip-Flop-Schaltung **108** stellt ein SCHREIB-Signal zur Verfügung und ist an einen Eingang eines Invertierers **109** angeschlossen. Ein Ausgang des Invertierers **109** ist an einem D-Eingang der Flip-Flop-Schaltung **108** angeschlossen.

**[0019]** Unter Betriebsbedingungen verfügen der FIFO A und der FIFO B, wie in [Fig. 2](#) ausführlich dargestellt, über spezifische Einträge, die eine Mehrzahl von Flip-Flop-Schaltungen, wie zum Beispiel die Flip-Flop-Schaltungen **35–38** für den ersten Eintrag des FIFO A, verwenden. Das in [Fig. 2](#) dargestellte Taktsignal ist ein synchroner Takt, der unabhängig von der dargestellten Schaltung erzeugt wird; das selbe Taktsignal wird für alle beschriebenen Taktegänge verwendet. Wie bei dem Betrieb von [Fig. 1](#), wenn der Multiplexer **32** das SCHREIB-Steuersignal in einem "logisch Eins"-Zustand empfängt, wird der Eingang A zu seinem Ausgang geführt. Wenn der Multiplexer **32** das SCHREIB-Steuersignal in einem "logisch Null"-Zustand empfängt, wird der Eingang B zu seinem Ausgang geführt. Wenn der Multiplexer **34** das SCHREIB-Steuersignal in einem "logisch Eins"-Zustand empfängt, wird der Eingang B zu seinem Ausgang geführt. Wenn der Multiplexer **34** das SCHREIB-Steuersignal in einem "logisch Null"-Zustand empfängt, wird der Eingang A zu seinem Ausgang geführt. Genauso führt der Multiplexer **60**, wenn sich das LESE-Steuersignal in einem "logisch Eins"-Zustand befindet, den Ausgang des FIFO A und der Multiplexer **62** führt den Ausgang des FIFO B. Wenn sich das LESE-Steuersignal in einem "logisch Null"-Zustand befindet, führt der Multiplexer **60** den Ausgang des FIFO B und der Multiplexer **62** den Ausgang des FIFO A.

**[0020]** Wie dargestellt, funktioniert der Head Counter **88**, um einen sequenziellen Zählwert zu halten, der auf einen ausgewiesenen Anfangseintrag in dem FIFO A zeigt und der Tail Counter **89** funktioniert, um einen sequenziellen Zählwert zu halten, der auf einen ausgewiesenen letzten Eintrag in dem FIFO A zeigt. Der FIFO A funktioniert als eine kreisförmige Warteschlange, die über eine Anfangs- und eine Endadresse verfügt, die zurück zu der Anfangsadresse führt. Die Schreib-Steuerlogikschaltung **90** und die Lese-Steuerlogikschaltung **91** sind mit dem FIFO A verknüpft und verwenden den Head Counter und den Tail Counter, um teilweise zu steuern, wann eine Schreib- oder eine Lese-Operation freigegeben werden sollen. Die Ausgänge der Schreib-Steuerlogikschaltung **90** und der Lese-Steuerlogikschaltung **91** sind Mehrfachleiter, von denen jeder einem bestimmten Eintrag des FIFO A entspricht. Die Ausgänge des

Head Counters **88** und des Tail Counters **89** funktionieren als ein Zeiger auf den FIFO A, da diese zwei Ausgänge bestimmen, welcher Eintrag in dem FIFO A jeweils entweder beschrieben oder ausgelesen wird. Die analoge Operation findet für den FIFO B in Verbindung mit dem Head Counter **93**, dem Tail Counter **94**, der Schreib-Steuerlogikschaltung **95** und der Lese-Steuerlogikschaltung **96** statt.

**[0021]** Die Simultaneintragslogik **100** funktioniert, um zu erfassen, wann in dem FIFO-Speichersystem **30** eine simultane Schreib-Operation sowohl in den FIFO A als auch den FIFO B stattfinden soll, wann eine simultane Lese-Operation sowohl aus dem FIFO A als auch aus dem FIFO B stattfinden soll, wann eine Schreib-Operation in den FIFO A oder den FIFO B mit einer Lese-Operation aus dem jeweils anderen FIFO stattfinden soll, wann eine Lese-Operation aus einem Eintrag des FIFO A oder des FIFO B stattfinden soll, mit einer Schreib-Operation in einen anderen Eintrag des selben FIFO, und wann eine Schreib-Operation sowohl in den FIFO A als auch den FIFO B stattfinden soll, zur selben Zeit, wenn eine Lese-Operation aus verschiedenen Einträgen sowohl in dem FIFO A als auch dem FIFO B stattfindet. Es gibt zahlreiche Ereignisse und Mechanismen, die signalisieren können, wann eine simultane mehrfache Eintragsoperation stattfinden soll. Zum Beispiel können in einem Datenverarbeitungssystem bestimmte Anweisungen decodiert werden und ein Prozessor (nicht gezeigt) kann anweisen, dass simultane Mehrfach-FIFO-Operationen stattfinden sollen. In einer Form sind Daten, die mit dem FIFO A und dem FIFO B kommuniziert werden sollen, eine Echtzeit-Debug-Nachricht in Verbindung mit einer Datenverarbeitungs-Debug-Funktion. Eine Simultaneintragsoperation wird durch die Erzeugung von mehreren LESE- und SCHREIB-Freigabesignalen für einen oder mehrere der FIFOs implementiert. Wenn es ein Simultaneintragsereignis gibt, werden die UND-Gates **101** und **102** inaktiv, wodurch der Takt zu den Flip-Flop-Schaltungen **105** und **108** gesperrt wird. Das Sperren der Flip-Flop-Schaltungen **105** und **108** verhindert den Umschaltbetrieb der Multiplexer **32** und **34** zwischen den FIFOs A und B in der Art und Weise, wie zuvor in Verbindung mit [Fig. 1](#) beschrieben. Die Sperrung des Umschaltbetriebs verhindert, dass der nächste Eintragszugriff mit dem selben FIFO stattfindet, bevor das Simultaneintragsereignis stattfindet.

**[0022]** Inzwischen ist klar, dass eine FIFO-Speicherstruktur zur Verfügung gestellt worden ist, die über ein vereinfachtes Overhead und einen verringerten Leistungsverbrauch verfügt. Das hierin offenbare FIFO-Speichersystem ist kompakt und stellt Kosten- und Leistungseinsparungen zur Verfügung. In einer Anwendung ist die vorliegende Erfindung im Besonderen für eine Debug-Schaltung vorteilhaft, die im Allgemeinen in Verarbeitungssystemen imple-

mentiert ist. Weil Mehrfachinformationseinträge gleichzeitig gespeichert werden müssen, werden die Steuerung und die mit dieser Funktion verknüpfte Verschaltung durch die Verwendung der vorliegenden Erfindung erheblich verringert. Es ist klar, dass die vorliegende Erfindung in Verarbeitungssystemen verwendet werden kann, die eine FIFO-Speicherstruktur für andere Zwecke als in Verbindung mit Debug verwendet werden. Zusätzlich kann die vorliegende Erfindung mit einer beliebigen Art von Transistor und mit einer beliebigen Art von Halbleiterherstellungsverfahren implementiert werden.

**[0023]** Weil die Vorrichtung, die die vorliegende Erfindung implementiert, zum größten Teil aus elektronischen Komponenten und Schaltungen zusammengesetzt ist, die dem Fachmann auf dem Gebiet bekannt sind, werden Schaltungseinzelheiten nicht ausführlicher erklärt, als, wie oben dargestellt, für das Verständnis und die Beurteilung des zugrundeliegenden Konzepts der vorliegenden Erfindung für notwendig erachtet, und um nicht die Lehren der vorliegenden Erfindung zu vernebeln oder von ihnen abzulenken.

**[0024]** In der vorangehenden Spezifizierung ist die Erfindung unter Bezugnahme auf spezifische Ausführungsformen beschrieben worden. Dem Fachmann auf dem Gebiet ist jedoch klar, dass verschiedene Modifizierungen und Änderungen vorgenommen werden können, ohne von dem Umfang der vorliegenden Erfindung abzuweichen, wie in den Ansprüchen unten dargelegt. Dementsprechend sollen die Spezifizierung und die Abbildungen in einem veranschaulichenden anstatt einem einschränkenden Sinne verstanden werden und alle solche Modifizierungen sollen in dem Umfang der vorliegenden Erfindung enthalten sein.

**[0025]** Oben sind Nutzen, andere Vorteile und Lösungen von Problemen mit Bezug auf spezifische Ausführungsformen beschrieben worden. Jedoch sollen die Nutzen, Vorteile, Lösungen von Problemen und jedes beliebige Element, das irgend einen Nutzen oder Vorteil verursachen kann, oder verursachen kann, dass eine Lösung eintritt, oder ausgeprägter ausfällt, nicht als ein kritisches, erforderliches, oder wesentliches Merkmal, oder Element irgend eines Anspruchs oder aller Ansprüche gedeutet werden. Wie hierin verwendet, sollen die Ausdrücke "umfasst", "umfassend", oder eine beliebige andere ihrer Variationen, eine nicht exklusive Einbeziehung umfassen, sodass ein Prozess, ein Verfahren, ein Artikel oder eine Vorrichtung, die eine Liste von Elementen umfasst, nicht nur diese Elemente enthält, sondern weitere Elemente umfassen kann, die nicht ausdrücklich aufgelistet oder einem solchen Prozess, Verfahren, Artikel oder einer solchen Vorrichtung inhärent sind.

## Patentansprüche

1. FIFO-Speichersystem (10), umfassend:

einen ersten Multiplexer (12) mit einem ersten Dateneingangsanschluss, einem zweiten Dateneingangsanschluss, einem Datenausgangsanschluss und einem Steueranschluss;

einen ersten FIFO-Speicher (FIFO A) mit einer Mehrzahl von Einträgen, wobei jeder von der Mehrzahl von Einträgen einen Eingangsanschluss besitzt, der mit dem Datenausgangsanschluss des ersten Multiplexers gekoppelt ist;

einen zweiten Multiplexer (14) mit einem ersten Dateneingangsanschluss, der mit dem ersten Dateneingangsanschluss des ersten Multiplexers gekoppelt ist, einem zweiten Dateneingangsanschluss, der mit dem zweiten Dateneingangsanschluss des ersten Multiplexers gekoppelt ist, einem Datenausgangsanschluss und einem Steueranschluss; und

einen zweiten FIFO-Speicher (FIFO B) mit einer Mehrzahl von Einträgen, wobei jeder von der Mehrzahl von Einträgen einen Eingangsanschluss besitzt, der mit dem Datenausgangsanschluss des zweiten Multiplexers gekoppelt ist; wobei das Speichersystem gekennzeichnet ist durch:

eine Steuerlogikschaltung (16, 90, 95, 100) zum Bereitstellen eines Steuersignals zum Veranlassen, dass ein Schreib-Steuersignal für die Steueranschlüsse des ersten und zweiten Multiplexers bereitgestellt wird, wobei, wenn das Steuersignal in einem ersten logischen Zustand ist, das Schreib-Steuersignal zum abwechselnden Schreiben jeweils einer einzelnen Menge einer an einem der ersten oder zweiten Dateneingangsanschlüsse empfangenen Mehrzahl von Datenmengen in die ersten und zweiten FIFO-Speicher eingerichtet ist, und wenn das Steuersignal in einem zweiten logischen Zustand ist, das Schreib-Steuersignal eingerichtet ist zum gleichzeitigen Schreiben der Mehrzahl von Datenmengen von einem ersten und zweiten Dateneingangsanschluss in die ersten und zweiten FIFO-Speicher.

2. FIFO-Speichersystem (10) nach Anspruch 1, wobei die Steuerlogikschaltung geeignet ist zum Veranlassen, dass die Schreib-Steuerschaltung gleichzeitig, als Antwort darauf, dass die ersten und zweiten Dateneingangsanschlüsse einen ersten Datentyp empfangen, Daten in die ersten und zweiten FIFO-Speicher schreibt und dass die Steuerlogikschaltung zum Veranlassen, dass die Schreib-Steuerschaltung abwechselnd, als Antwort darauf, dass die ersten und zweiten Dateneingangsanschlüsse einen zweiten Datentyp empfangen, Daten in den ersten und zweiten FIFO-Speicher schreibt.

3. FIFO-Speichersystem (10) nach Anspruch 1, das des Weiteren umfasst:

einen dritten Multiplexer (20) mit einem ersten Dateneingangsanschluss, der mit einem Datenausgangsanschluss von jedem der Mehrzahl von Einträgen

des ersten FIFO-Speichers gekoppelt ist, einem zweiten Dateneingangsanschluss, der mit einem Datenausgangsanschluss von der Mehrzahl von Einträgen des zweiten FIFO-Speichers gekoppelt ist, und einem Steueranschluss;

einen vierten Multiplexer (22) mit einem ersten Dateneingangsanschluss, der mit einem Datenausgangsanschluss von jedem von der Mehrzahl von Einträgen des ersten FIFO-Speichers gekoppelt ist, einem zweiten Dateneingangsanschluss, der mit einem Datenausgangsanschluss von der Mehrzahl von Einträgen des zweiten FIFO-Speichers gekoppelt ist, und einem Steueranschluss; und

eine Lese-Steuerlogikschaltung (22) zum Bereitstellen eines Lese-Steuersignals für die Steueranschlüsse der dritten und vierten Multiplexer, wobei die Lese-Steuerlogik veranlasst, dass Daten aus dem ersten und zweiten FIFO-Speicher in derselben Reihenfolge gelesen werden, in der die Daten geschrieben wurden.

4. FIFO-Speichersystem (10) nach Anspruch 1, wobei die Mehrzahl von Datenmengen dadurch gekennzeichnet ist, dass es sich um eine Echtzeit-Debug-Meldung handelt.

5. FIFO-Speichersystem (10) nach Anspruch 1, das des Weiteren umfasst:

einen ersten Zähler (88) zum sequentiellen Zeigen auf jeden von der Mehrzahl von Einträgen des ersten FIFO-Speichers während des Schreibens von Daten in den ersten FIFO-Speicher; und

einen zweiten Zähler (93) zum sequentiellen Zeigen auf jeden von der Mehrzahl von Einträgen des zweiten FIFO-Speichers während des Schreibens von Daten in den zweiten FIFO-Speicher.

6. FIFO-Speichersystem (10) nach Anspruch 1, wobei die Schreib-Steuerlogikschaltung umfasst:

einen Invertierer (18) mit einem Eingangsanschluss und einem Ausgangsanschluss; und

einen Flip-Flop (16) mit einem Eingangsanschluss, der mit dem Ausgangsanschluss des Invertierers gekoppelt ist, und einem Ausgangsanschluss, der mit dem Eingangsanschluss des Invertierers gekoppelt ist, wobei der Ausgangsanschluss des Flip-Flops das Schreib-Steuersignal bereitstellt.

7. Verfahren zum Zugreifen auf ein FIFO-Speichersystem (10), wobei das FIFO-Speichersystem einen ersten FIFO-Speicher (FIFO A) und einen zweiten FIFO-Speicher (FIFO B) besitzt, wobei jeder der ersten und zweiten FIFO-Speicher eine Mehrzahl von Einträgen besitzt, wobei ein Eingangsanschluss von jedem von der Mehrzahl von Einträgen des ersten FIFO-Speichers mit einem Ausgangsanschluss eines ersten Multiplexers (12) gekoppelt ist und ein Eingangsanschluss von jedem von der Mehrzahl von Speicherplätzen des zweiten FIFO-Speichers mit einem Ausgangsanschluss eines zweiten Multiplexers

(14) gekoppelt ist, wobei das Verfahren die Schritte umfasst:

Empfangen von Daten an einem ersten Dateneingangsanschluss des ersten Multiplexers (12) und an einem ersten Dateneingangsanschluss des zweiten Multiplexers (14);

Empfangen von Daten an einem zweiten Dateneingangsanschluss des ersten Multiplexers (12) und an einem zweiten Dateneingangsanschluss des zweiten Multiplexers (14); wobei das Verfahren gekennzeichnet ist durch:

abwechselndes Schreiben von jeweils einer einzelnen Menge von der Mehrzahl von Datenmengen in die ersten und zweiten FIFO-Speicher als Antwort darauf, dass ein Steuersignal von einer Steuerschaltung (16) sich in einem ersten logischen Zustand befindet; und

gleichzeitiges Schreiben der Mehrzahl der Datenmengen, die von dem ersten Dateneingangsanschluss und zweiten Dateneingangsanschluss empfangen wurden, in die ersten und zweiten FIFO-Speicher als Antwort darauf, dass das Steuersignal von der Steuerschaltung sich in einem zweiten logischen Zustand befindet.

8. Verfahren nach Anspruch 7, wobei die Daten in den ersten und zweiten FIFO-Speichern in sequentiellen Einträgen als Antwort auf ein Erhöhen der ersten und zweiten Zähler (88, 93) gespeichert werden, wobei der erste Zähler dem ersten FIFO-Speicher zugeordnet ist und der zweite Zähler dem zweiten FIFO-Speicher zugeordnet ist.

9. Verfahren nach Anspruch 7, wobei bei dem Schritt des abwechselnden Schreibens die Daten in die ersten und zweiten FIFO-Speicher als Antwort darauf geschrieben werden, dass die Daten von einem ersten Datentyp sind.

10. Verfahren nach Anspruch 7, wobei bei dem Schritt des gleichzeitigen Schreibens die Daten in die ersten und zweiten FIFO-Speicher als Antwort darauf geschrieben werden, dass die Daten von einem zweiten Datentyp sind.

Es folgen 2 Blatt Zeichnungen

FIG. 1

FIG. 2