OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 657 965**

⑮ Int. Cl.:

**H04N 19/70** (2014.01)

**H04N 19/147** (2014.01)

**H04N 19/196** (2014.01)

**H04N 19/96** (2014.01)

**H04N 19/11** (2014.01)

**H04N 19/463** (2014.01)

**H04N 19/136** (2014.01)

**H04N 19/176** (2014.01)

⑫

TRADUCCIÓN DE PATENTE EUROPEA

T3

⑥ Fecha de presentación y número de la solicitud internacional: **29.06.2010 PCT/US2010/001862**

⑦ Fecha y número de publicación internacional: **06.01.2011 WO11002504**

⑨ Fecha de presentación y número de la solicitud europea: **29.06.2010 E 10743254 (4)**

⑩ Fecha y número de publicación de la concesión europea: **06.12.2017 EP 2449782**

---

⑮ Título: **Métodos y aparato para señalización de predicción intra para grandes bloques para codificadores y decodificadores de vídeo**

⑩ Prioridad:

**01.07.2009 US 222177 P**

⑮ Fecha de publicación y mención en BOPI de la traducción de la patente:

**07.03.2018**

⑮ Titular/es:

**THOMSON LICENSING (100.0%)**

1-5, rue Jeanne d'Arc

92130 Issy-les-Moulineaux, FR

⑮ Inventor/es:

**ZHENG, YUNFEI;**

**XU, QIAN;**

**LU, XIAOAN;**

**YIN, PENG;**

**SOLE, JOEL y**

**ABBAS, ADEEL**

⑮ Agente/Representante:

**ELZABURU, S.L.P**

**ES 2 657 965 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Métodos y aparato para señalización de predicción intra para grandes bloques para codificadores y decodificadores de vídeo

### Campo técnico

5 La presente invención se refiere de manera general a codificación y decodificación de vídeo y, más particularmente, a métodos y aparato para señalización de predicción intra para bloques grandes para codificadores y decodificadores de vídeo.

### Antecedentes

10 Los estándares más modernos de codificación de vídeo emplean diversos modos de codificación para reducir eficazmente las correlaciones en los dominios espacial y temporal. Por ejemplo, en el estándar de Codificación de Vídeo Avanzada (AVC) Parte 10 del Grupo de Expertos de Imágenes en Movimiento 4 (MPEG-4) de la Organización Internacional para Estandarización/Comisión Electrotécnica Internacional (ISO/IEC)/Recomendación H.264 del Sector de Telecomunicaciones, Unión Internacional de Telecomunicaciones (ITU-T) (en lo sucesivo el "Estándar AVC de MPEG-4"), una imagen puede ser codificada intra o inter. En imágenes intra, todos los macrobloques se codifican en modos intra, explotando de esta manera correlaciones espaciales dentro de la imagen. Los modos intra se pueden clasificar en los tres siguientes tipos: INTRA4x4; INTRA8x8; e INTRA16x16. INTRA4x4 e INTRA8x8 soportan 9 modos de predicción intra e INTRA16x16 soporta 4 modos de predicción intra.

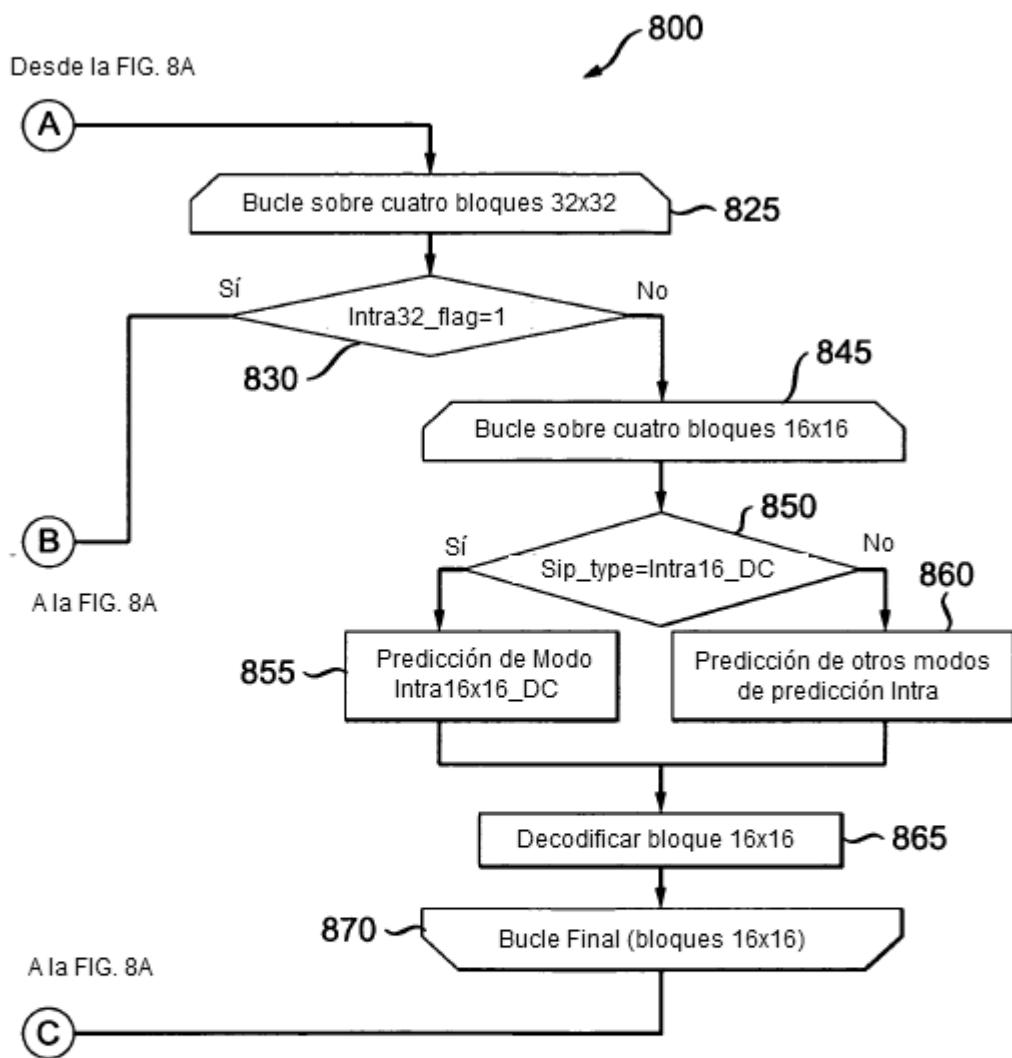

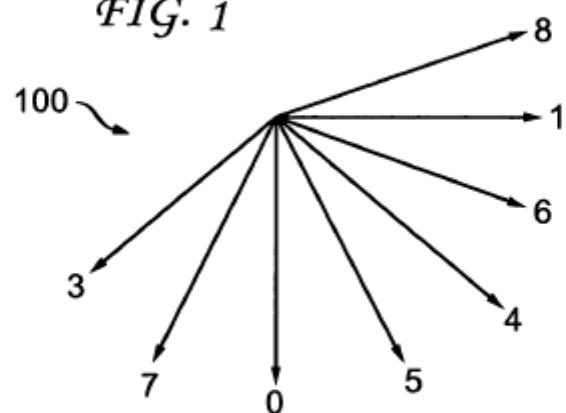

20 INTRA4x4 e INTRA8x8 soportan los 9 siguientes modos de predicción intra: predicción vertical; horizontal; DC; diagonal abajo/izquierda; diagonal abajo/derecha; vertical izquierda; horizontal abajo; vertical derecha; y horizontal arriba. INTRA16x16 soporta los 4 siguientes modos de predicción intra: predicción vertical; horizontal; DC; y plana. Volviendo a la FIG. 1, los modos de predicción INTRA4x4 e INTRA8x8 se indican de manera general mediante el número de referencia 100. En la FIG. 1, el número de referencia 0 indica un modo de predicción vertical, el número de referencia 1 indica un modo de predicción horizontal, el número de referencia 3 indica un modo de predicción diagonal abajo/izquierda, el número de referencia 4 indica un modo de predicción diagonal abajo/derecha, el número de referencia 5 indica un modo de predicción vertical derecha, el número de referencia 6 indica un modo de predicción horizontal abajo, el número de referencia 7 indica un modo de predicción vertical izquierda, y el número de referencia 8 indica un modo de predicción horizontal arriba. El modo de DC, que es parte de los modos de predicción INTRA4x4 e INTRA8x8, no se muestra. Volviendo a la FIG. 2, los modos de predicción INTRA16x16 se indican de manera general mediante el número de referencia 200. En la FIG. 2, el número de referencia 0 indica un modo de predicción vertical, el número de referencia 1 indica un modo de predicción horizontal, y el número de referencia 3 indica un modo de predicción plano. El modo DC, que es parte de los modos de predicción INTRA16x16, no se muestra.

30 INTRA4x4 usa una transformada coseno discreta (DCT) 4x4. INTRA8x8 usa transformadas 8x8. INTRA16x16 usa transformadas 4x4 en cascada. Para la señalización, INTRA4x4 e INTRA8x8 comparten el mismo tipo de macrobloque (mb\_type) 0 y se diferencian por una bandera de tamaño de transformada (transform\_8x8\_size\_flag). Entonces la elección de modo de predicción intra en INTRA4x4 o INTRA8x8 se señala por el modo más probable posiblemente con un modo restante si es necesario. Para INTRA16x16, todos los modos de predicción intra junto con un tipo de patrón de bloque codificado (cbp) se señalan en mb\_type, que usa un valor de mb\_type de 1 a 24. La TABLA 1 muestra la señalización detallada para tipos de macrobloques para segmentos codificados Intra (segmentos I). Si un tamaño de bloque más grande que 16x16 se usa para predicción intra, entonces se enfrentan distintos problemas posibles, como sigue.

35 (1) Si se añade predicción INTRA32x32 o INTRA64x64, simplemente extendiendo el mb\_type en el Estándar AVC de MPEG-4, causará demasiado sobredimensionamiento para esos dos nuevos modos y, además, no permitirán un tipo jerárquico de predicción intra. Un ejemplo de un tipo jerárquico de predicción intra se explica como sigue. Si se usa un bloque 32x32 como bloque grande y permitimos que las subdivisiones sean 16x16 entonces, para cada subdivisión 16x16, se deberían permitir INTRA4x4, INTRA8x8, INTRA16x16.

40 (2) Si se usa una transformada más grande (tal como una transformada 16x16) en lugar de una transformada en cascada para INTRA16x16, entonces no se puede aplicar señalización actual.

(3) Deberíamos dar diferente prioridad para modos de predicción intra en lugar de un tipo de división intra.

TABLA 1

| mb_type | Nombre de mb_type | transform-size_8x8_flag | MbPartPred Mode (mb_type, 0) | Intra16x16-PredMod | CodedBlock-PatternChroma | CodedBlock-PatternLuma |

|---------|-------------------|-------------------------|------------------------------|--------------------|--------------------------|------------------------|

| 0       | I_NxN             | 0                       | Intra_4x4                    | na                 | Ecuación 7-33            | Ecuación 7-33          |

| 0       | I_NxN             | 1                       | Intra_8x8                    | na                 | Ecuación 7-33            | Ecuación 7-33          |

| 1       | I_16x16_0_0_0     | na                      | Intra_16x16                  | 0                  | 0                        | 0                      |

| 2       | I_16x16_1_0_0     | na                      | Intra_16x16                  | 1                  | 0                        | 0                      |

| 3       | I_16x16_2_0_0     | na                      | Intra_16x16                  | 2                  | 0                        | 0                      |

| 4       | I_16x16_3_0_0     | na                      | Intra_16x16                  | 3                  | 0                        | 0                      |

| 5       | I_16x16_0_1_0     | na                      | Intra_16x16                  | 0                  | 1                        | 0                      |

| 6       | I_16x16_1_1_0     | na                      | Intra_16x16                  | 1                  | 1                        | 0                      |

| 7       | I_16x16_2_1_0     | na                      | Intra_16x16                  | 2                  | 1                        | 0                      |

| 8       | I_16x16_3_1_0     | na                      | Intra_16x16                  | 3                  | 1                        | 0                      |

| 9       | I_16x16_0_2_0     | na                      | Intra_16x16                  | 0                  | 2                        | 0                      |

| 10      | I_16x16_1_2_0     | na                      | Intra_16x16                  | 1                  | 2                        | 0                      |

| 11      | I_16x16_2_2_0     | na                      | Intra_16x16                  | 2                  | 2                        | 0                      |

| 12      | I_16x16_3_2_0     | na                      | Intra_16x16                  | 3                  | 2                        | 0                      |

| 13      | I_16x16_0_0_1     | na                      | Intra_16x16                  | 0                  | 0                        | 15                     |

| 14      | I_16x16_1_0_1     | na                      | Intra_16x16                  | 1                  | 0                        | 15                     |

| 15      | I_16x16_2_0_1     | na                      | Intra_16x16                  | 2                  | 0                        | 15                     |

| 16      | I_16x16_3_0_1     | na                      | Intra_16x16                  | 3                  | 0                        | 15                     |

| 17      | I_16x16_0_1_1     | na                      | Intra_16x16                  | 0                  | 1                        | 15                     |

| 18      | I_16x16_1_1_1     | na                      | Intra_16x16                  | 1                  | 1                        | 15                     |

| 19      | I_16x16_2_1_1     | na                      | Intra_16x16                  | 2                  | 1                        | 15                     |

| 20      | I_16x16_3_1_1     | na                      | Intra_16x16                  | 3                  | 1                        | 15                     |

| 21      | I_16x16_0_2_1     | na                      | Intra_16x16                  | 0                  | 2                        | 15                     |

| 22      | I_16x16_1_2_1     | na                      | Intra_16x16                  | 1                  | 2                        | 15                     |

| 23      | I_16x16_2_2_1     | na                      | Intra_16x16                  | 2                  | 2                        | 15                     |

| 24      | I_16x16_3_2_1     | na                      | Intra_16x16                  | 3                  | 2                        | 15                     |

| 25      | I_PCM             | na                      | na                           | na                 | na                       | na                     |

5 Existen algunos planteamientos de la técnica anterior con relación a señalización de divisiones de movimiento (inter) grandes en extensiones del Estándar AVC de MPEG-4. Un ejemplo de cómo se señalan divisiones de movimiento (inter) grandes en extensiones del Estándar AVC de MPEG-4 se describen con respecto a un primer planteamiento de la técnica anterior. El primer planteamiento de la técnica anterior describe cómo se hace la señalización para bloques 32x32 o bloques 64x64 usando una estructura de codificación jerárquica.

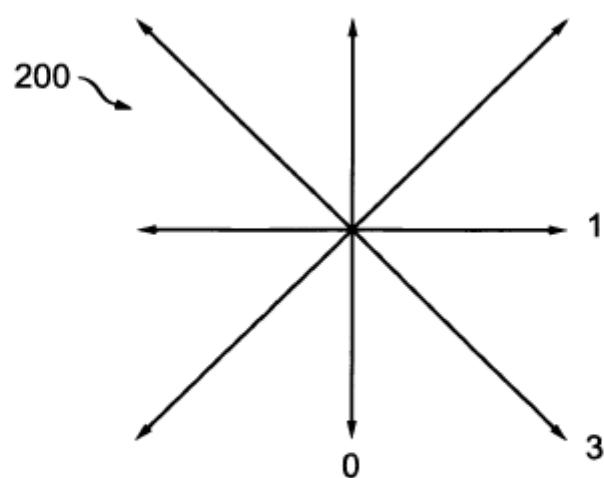

Además, en adición a los tamaños de división de movimiento existentes (16x16, 16x8, 8x16, 8x8, 8x4, 4x8 y 4x4) en el Estándar AVC de MPEG-4, también se ha propuesto codificación inter para una extensión del Estándar AVC de MPEG-4 usando divisiones 32x32, 32x16, y 16x32. Volviendo a la FIG. 3, las divisiones de movimiento para uso en bloques 32x32 se indican de manera general mediante el número de referencia 300. Las divisiones incluyen 32x32, 32x16, 16x32, y 16x16. Las divisiones 16x16 se pueden dividir además en divisiones de tamaños 16x16, 16x8, 8x16, y 8x8. Además, las divisiones 8x8 se pueden dividir además en divisiones de tamaños 8x8, 8x4, 4x8, y 4x4.

5 Para cada bloque 32x32, el modo SALTAR o el modo DIRECTO se señala usando una `mb32_skip_flag` de una forma similar a la realizada para otros modos del Estándar AVC de MPEG-4. Además, el `mb_type` original para una división  $MxN$  ( $M=8$ , o 16 y  $N=8$ , o 16) en el Estándar AVC de MPEG-4 también se usa para señalar una división  $2Mx2N$  en un bloque 32x32. Si el `mb32_type` de un 32x32 indica que se usa una división 16x16, entonces los cuatro bloques 16x16 se señalan en orden de escaneado de cuadro usando los mismos elementos de sintaxis que `macroblock_layer()` en el Estándar AVC de MPEG-4. Cada bloque 16x16 se puede dividir además de la manera de árbol cuádruple, desde el tamaño 16x16 hacia abajo hasta el tamaño 4x4.

10 Para el tamaño de macrobloque 64x64, las siguientes divisiones se añaden por encima de las divisiones usadas en bloques 32x32: 64x64, 64x32, y 32x64. De esta manera, se añade una capa más jerárquica en la división de macrobloque por encima del tamaño de bloque 32x32. El `mb_type` original para una división de macrobloque  $MxN$  ( $M=8$ , o 16 y  $N=8$ , o 16) en el Estándar AVC de MPEG-4 se usa para señalar una división de macrobloque  $4Mx4N$  en macrobloques 64x64. Si se usa una división de macrobloque 32x32 para un bloque 64x64, entonces cada bloque 32x32 se manejará de la misma manera que se ha descrito anteriormente.

15 20 No obstante, la literatura existente no aborda cómo se señala el modo intra grande, donde se define el modo intra grande que quiere decir predicción intra que implica bloques de división que tienen un tamaño igual o mayor que 32x32.

25 25 El documento US 2008/123977 A1 describe un codificador de imagen que incluye una unidad de generación de imagen predicha que genera una imagen predicha según una pluralidad de modos de predicción. En reglas tabuladas de un valor predicho que establecen reglas convencionales de modos de predicción intra no se compilan con y un valor predicho mejor se juzga a partir de la continuidad de un patrón de imagen.

30 35 Además, el artículo Kim J. et al.: "Enlarging MB size for high fidelity video coding beyond HD", 36. Reunión de VCEG; 8-10-2008 – 10-10-2008; San Diego, EE.UU.; (Grupo de Expertos de Codificación de Vídeo de SG. 16 de ITU-T), 5 de octubre de 2008 (05-10-2008), XP030003643 describe un método que comprende codificación de datos de imagen para al menos un bloque grande en una imagen señalando predicción para el al menos un bloque grande, en donde la predicción se señala seleccionando un tamaño de unidad de codificación básica y asignando un único tipo de división para el tamaño de unidad de codificación básica, el único tipo de división que se selecciona de entre una pluralidad de tipos de división intra espacial. La arquitectura extendida con la estructura de MB agrandado se propone primero para ME&MC pero no se pueden abordar aún nuevos diseños de núcleos de transformada, predicción intra, transformadas DC luma/croma, modelos de contexto CABAC y filtros de desbloqueo para MB agrandado.

### Compendio

40 Estos y otros inconvenientes y desventajas de la técnica anterior se abordan por los presentes principios, que se dirigen a métodos y aparato para señalar predicción intra para bloques grandes para codificadores y decodificadores de vídeo.

Según un aspecto de los presentes principios, se proporciona un método como se define en la reivindicación 1.

Estos y otros aspectos, rasgos y ventajas de los presentes principios llegarán a ser evidentes a partir de la siguiente descripción detallada de realizaciones ejemplares, que ha de ser leída en conexión con los dibujos anexos.

### Breve descripción de los dibujos

45 45 Los presentes principios se pueden entender mejor según las siguientes figuras ejemplares, en las que:

la FIG. 1 es un diagrama que muestra modos de predicción INTRA4x4 e INTRA8x8 a los que se pueden aplicar los presentes principios;

la FIG. 2 es un diagrama que muestra modos de predicción INTRA16x16 a los que se pueden aplicar los presentes principios;

50 50 la FIG. 3 es un diagrama que muestra divisiones de movimiento para uso en bloques 32x32 a las que se pueden aplicar los presentes principios;

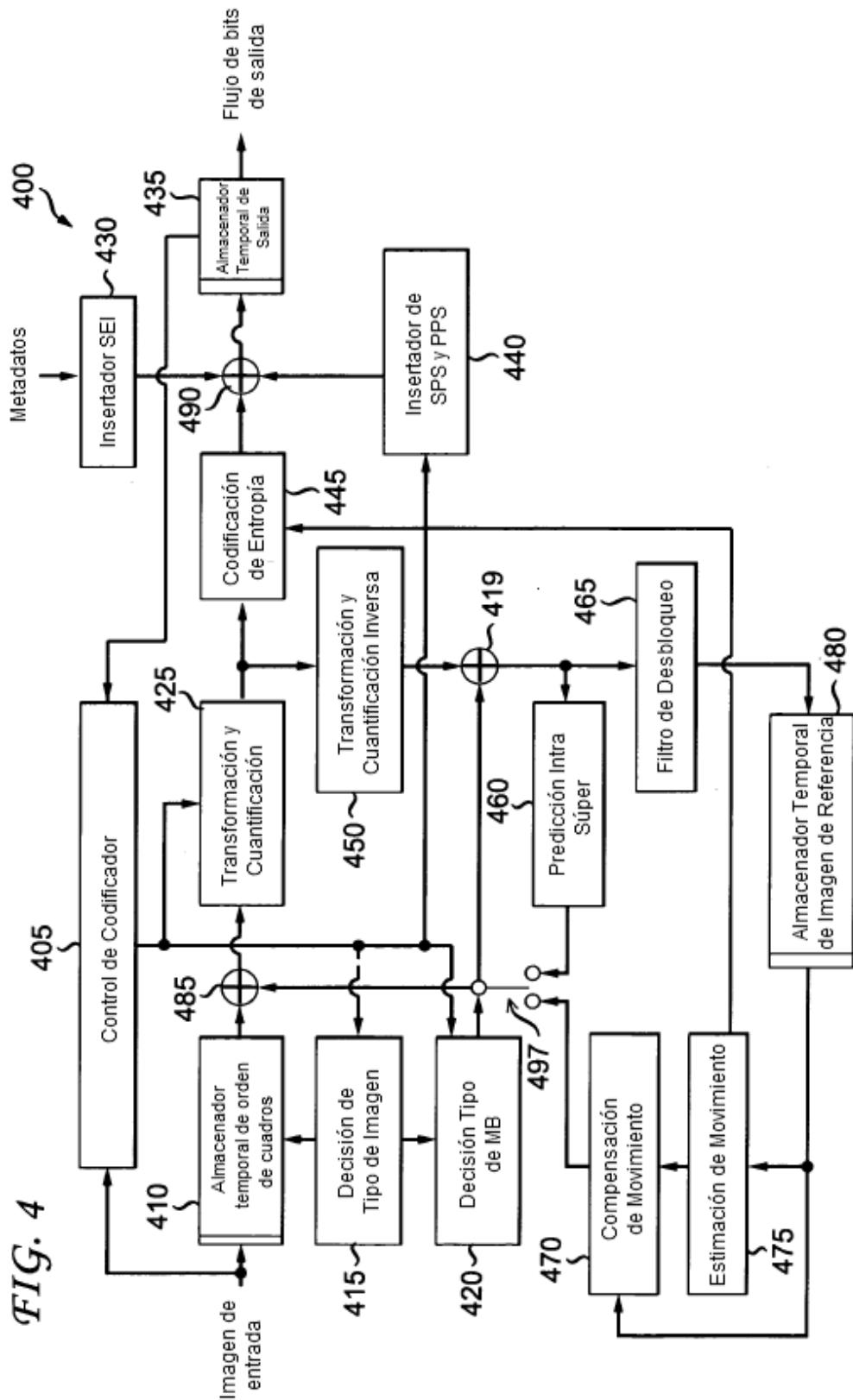

la FIG. 4 es un diagrama de bloques para un codificador de vídeo ejemplar al que se pueden aplicar los presentes principios según una realización de los presentes principios;

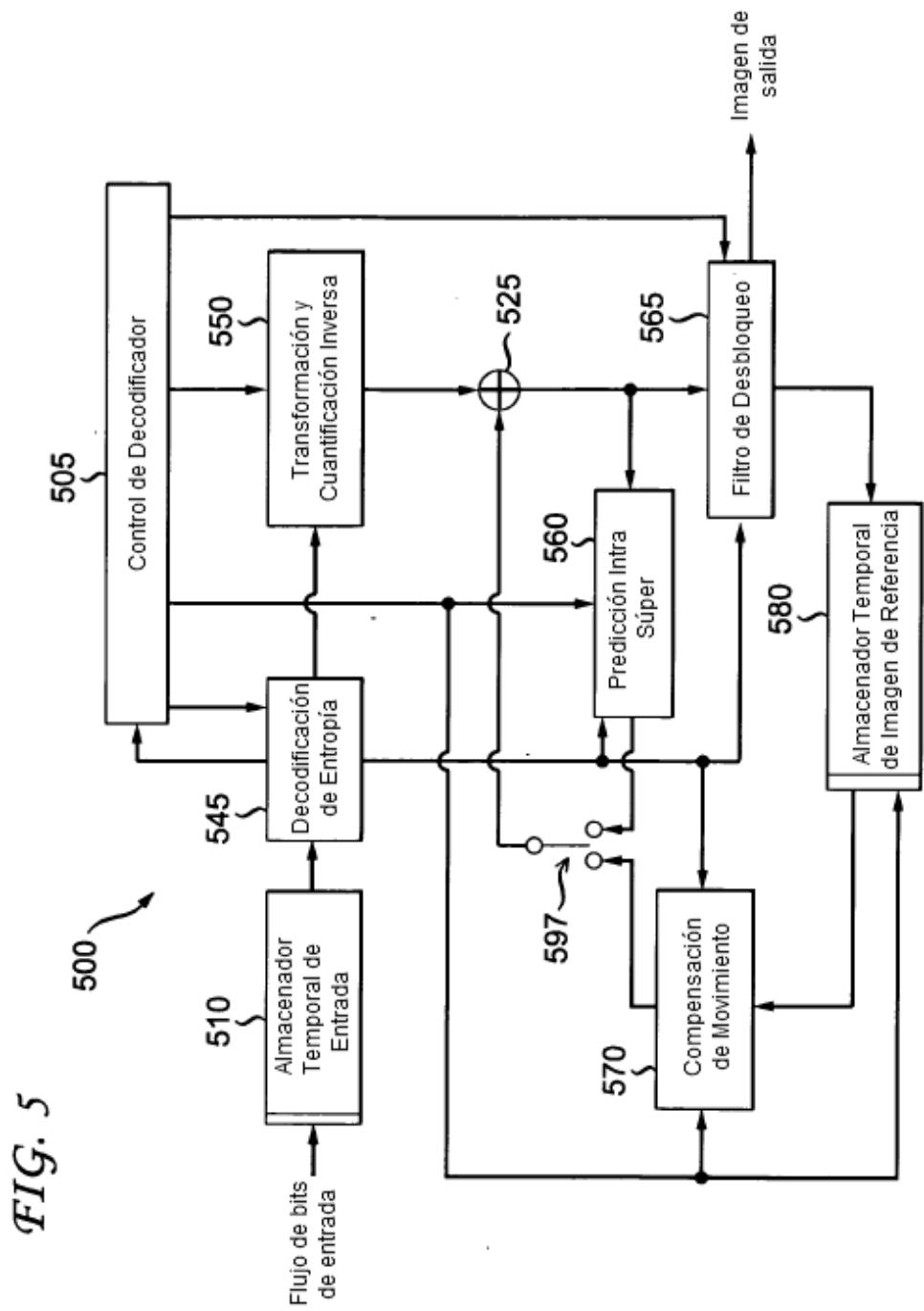

la FIG. 5 es un diagrama de bloques para un decodificador de vídeo ejemplar al que se pueden aplicar los presentes principios según una realización de los presentes principios;

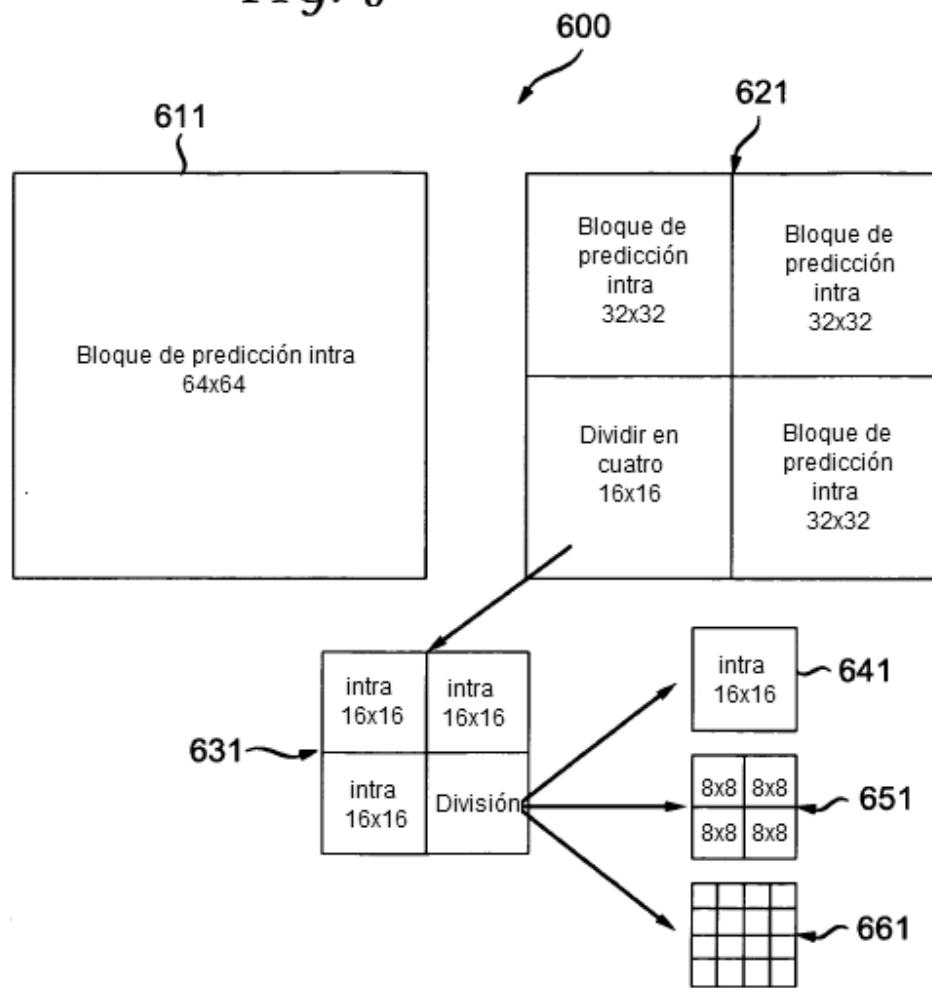

la FIG. 6 es un diagrama de bloques para divisiones jerárquicas ejemplares a las que se pueden aplicar los presentes principios según una realización de los presentes principios;

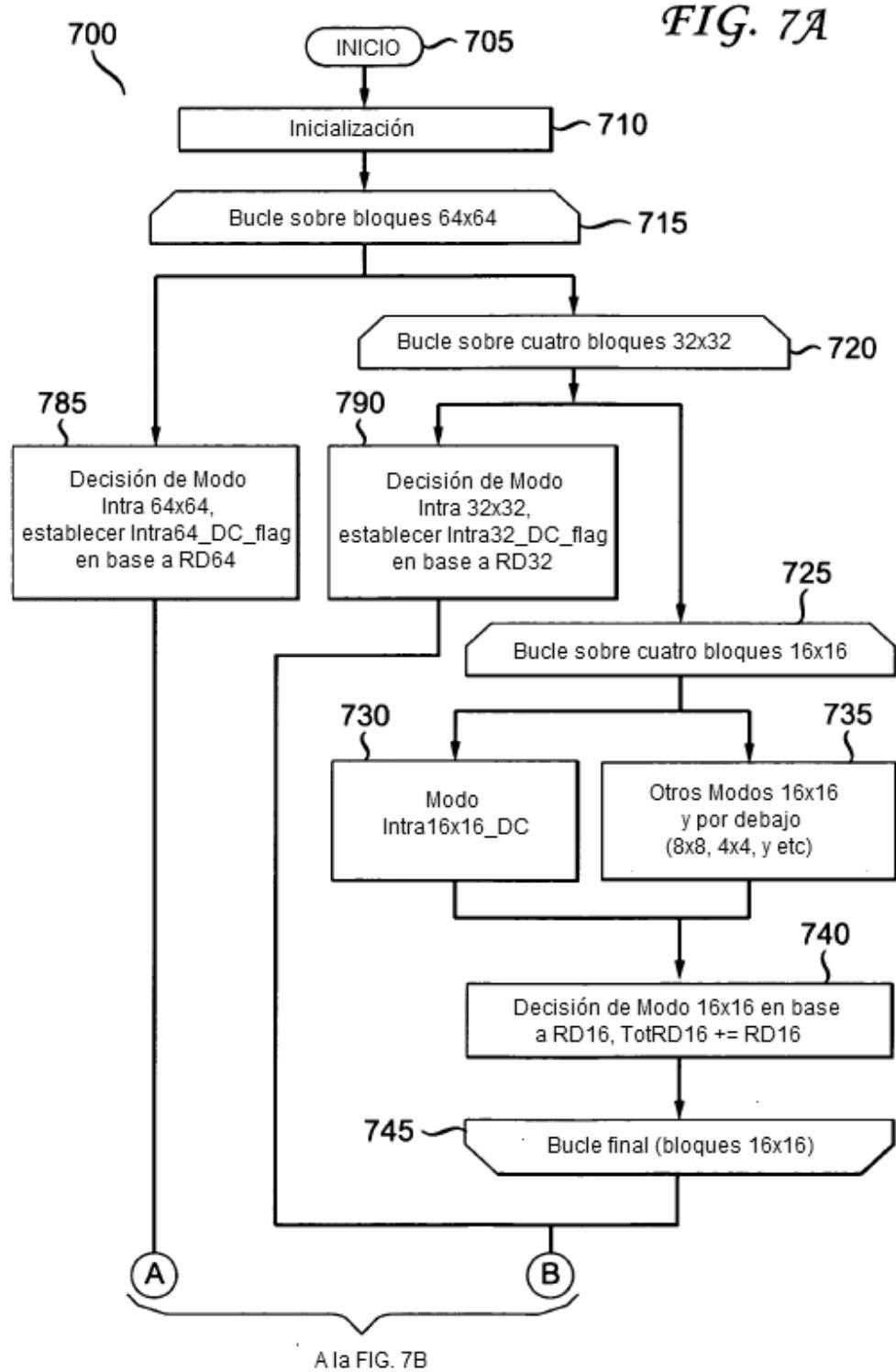

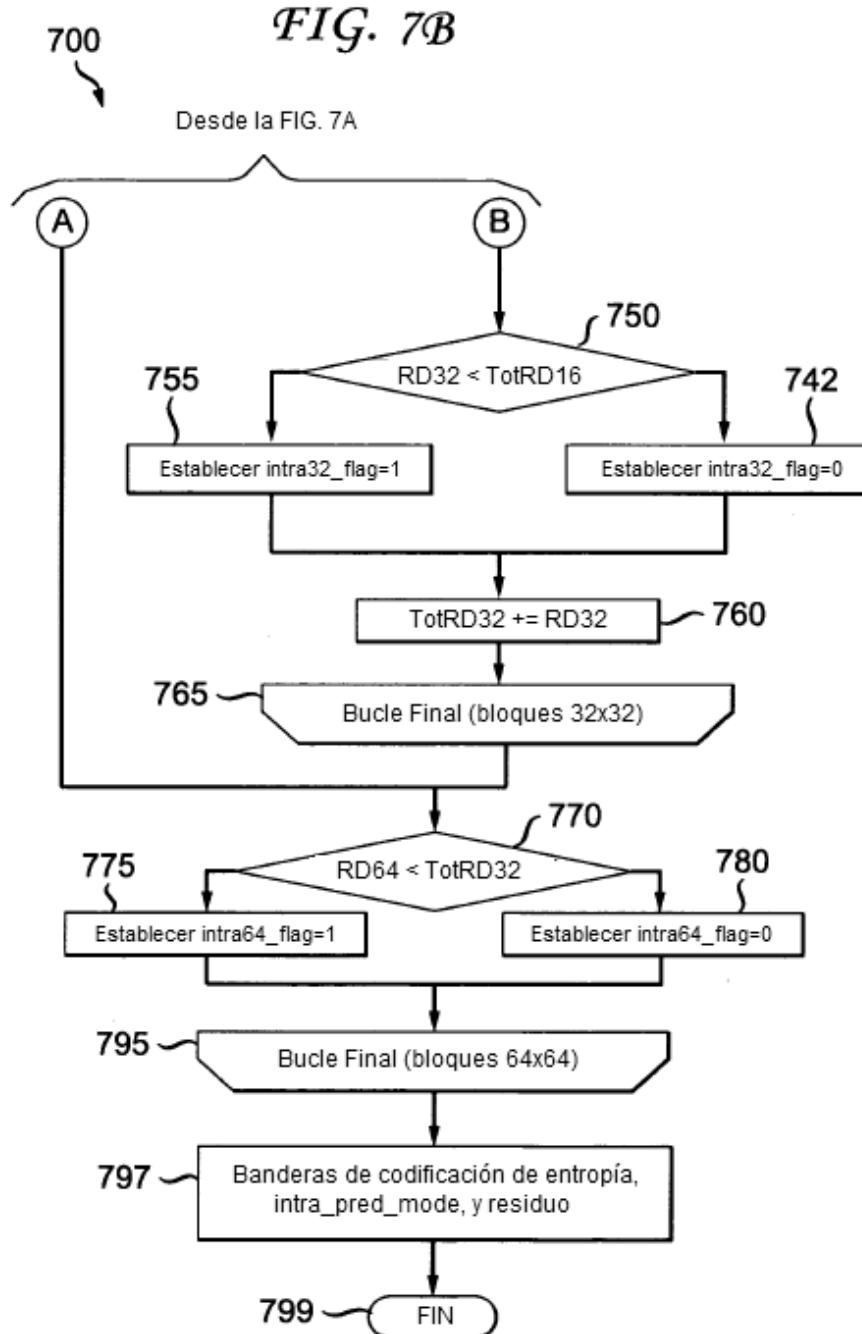

5 las FIG. 7A y 7B representan un diagrama de flujo para un método ejemplar para codificación de datos de imagen para bloques grandes mediante señalización de predicción intra para los bloques grandes según una realización de los presentes principios; y

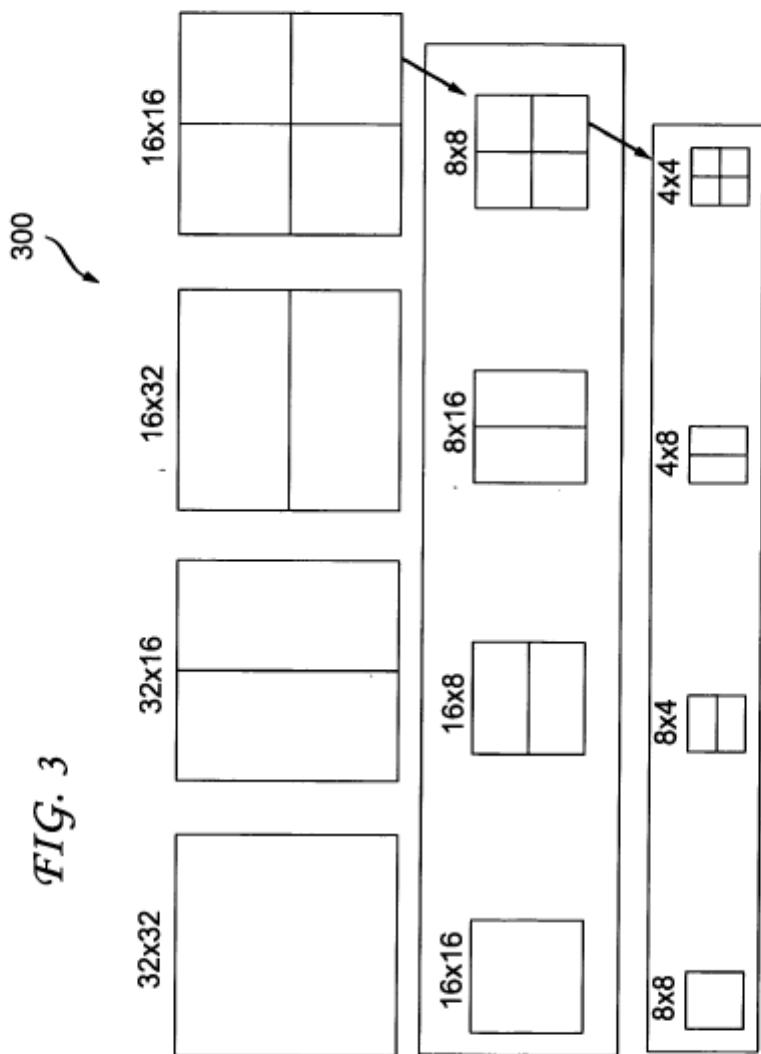

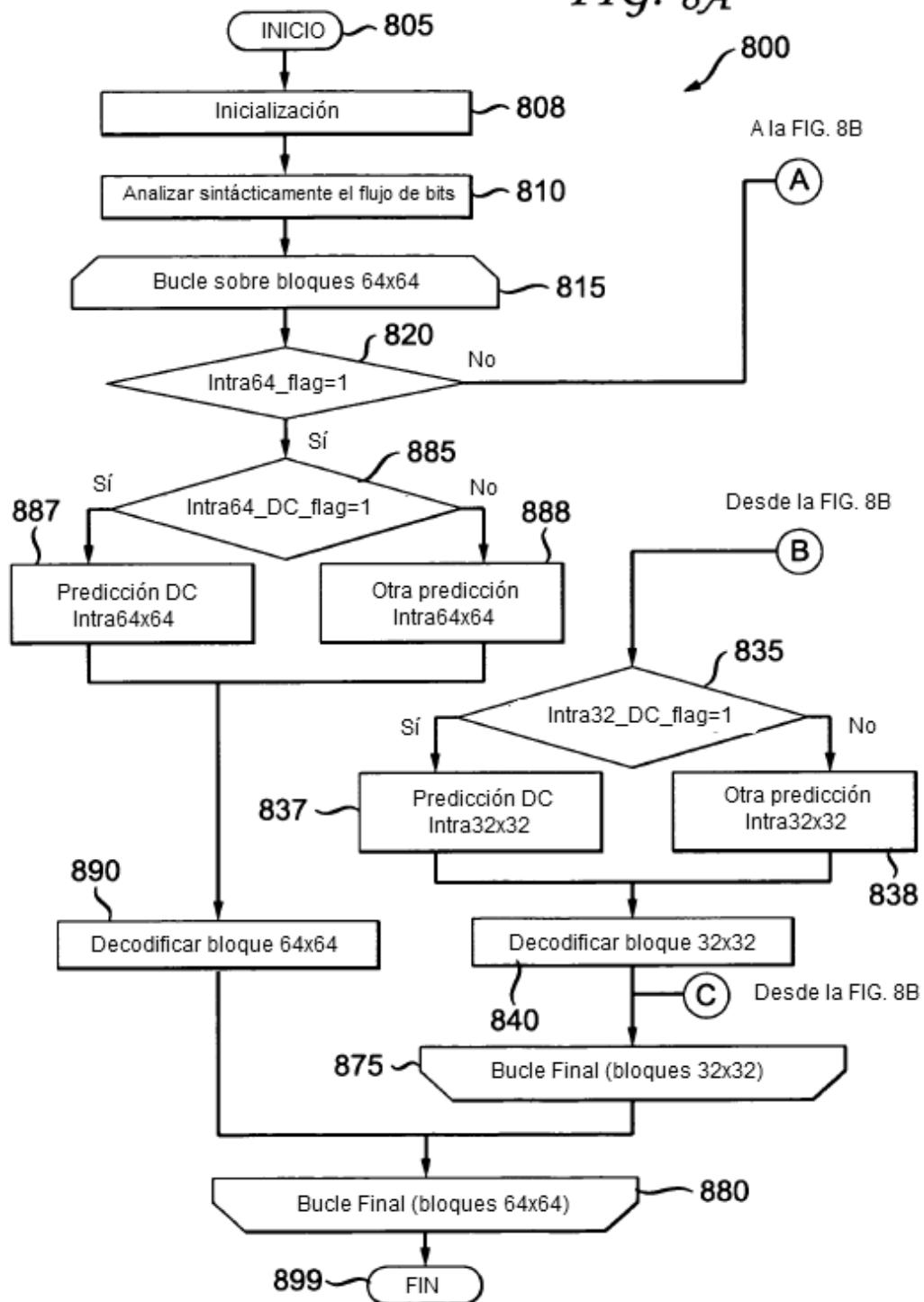

10 las FIG. 8A y 8B representan un diagrama de flujo que muestra un método ejemplar para decodificar datos de imagen para bloques grandes determinando que ha de ser aplicada predicción intra a los bloques grandes según una realización de los presentes principios.

#### Descripción detallada

Los presentes principios se dirigen a métodos y aparato para señalización de predicción intra para bloques grandes para codificadores y decodificadores de vídeo.

15 La presente descripción ilustra los presentes principios. De esta manera se apreciará que los expertos en la técnica serán capaces de idear diversas disposiciones que, aunque no se describen o se muestran explícitamente en la presente memoria, encarnen los presentes principios y se incluyen dentro de su espíritu y alcance.

20 Todos los ejemplos y lenguaje condicional expuesto en la presente memoria se pretenden con propósitos pedagógicos para ayudar al lector en la comprensión de los presentes principios y los conceptos contribuidos por el inventor o los inventores para avanzar la técnica, y han de ser interpretados como que son sin limitación a tales ejemplos y condiciones expuestos específicamente.

25 Además, todas las declaraciones en la presente memoria que exponen principios, aspectos, y realizaciones de los presentes principios, así como ejemplos específicos de los mismos, se pretenden que abarquen tanto equivalentes estructurales como funcionales de los mismos. Adicionalmente, se pretende que tales equivalentes incluyan tanto equivalentes conocidos actualmente así como equivalentes desarrollados en el futuro, es decir, cualquier elemento desarrollado que realice la misma función, con independencia de la estructura.

30 De esta manera, por ejemplo, se apreciará por los expertos en la técnica que los diagramas de bloques presentados en la presente memoria representan vistas conceptuales de circuitería ilustrativa que encarna los presentes principios. De manera similar, se apreciará que se muestran explícitamente cualesquiera gráficos de flujo, diagramas de flujo, diagramas de transición de estado, pseudocódigos, y similares representan diversos procesos que se pueden representar sustancialmente en medios legibles por ordenador y así ejecutar por un ordenador o procesador, ya sea o no tal ordenador o procesador.

35 Las funciones de los diversos elementos mostrados en las figuras se pueden proporcionar a través del uso de hardware dedicado así como hardware capaz de ejecutar software en asociación con software adecuado. Cuando se proporciona por un procesador, las funciones se pueden proporcionar por un procesador dedicado, por un único procesador compartido, o por una pluralidad de procesadores individuales, algunos de los cuales pueden ser compartidos. Además, el uso explícito del término "procesador" o "controlador" no se debería interpretar que se refiere exclusivamente a hardware capaz de ejecutar software, y puede incluir implícitamente, sin limitación, hardware de procesador digital de señal ("DSP"), memoria de sólo lectura ("ROM") para almacenar software, memoria de acceso aleatorio ("RAM"), y almacenamiento no volátil.

40 También se puede incluir otro hardware, convencional y/o personalizado. De manera similar, cualquier conmutador mostrado en las figuras es solamente conceptual. Su función se puede llevar a cabo a través de la operación de lógica de programa, a través de lógica dedicada, a través de la interacción de control de programa y lógica dedicada, o incluso manualmente, la técnica particular que es seleccionable por el implementador como se entiende más específicamente a partir del contexto.

45 En las reivindicaciones de esta, cualquier elemento expresado como medio para realizar una función específica se pretende que abarque cualquier forma de realización de esa función incluyendo, por ejemplo, a) una combinación de elementos de circuito que realiza esa función o b) software de cualquier forma, incluyendo, por lo tanto, microprogramas, microcódigo o similares, combinados con circuitería adecuada para ejecutar ese software para realizar la función. Los presentes principios que se definen por tales reivindicaciones residen en el hecho de que las 50 funcionalidades proporcionadas por los diversos medios expuestos se combinan y traen juntos de la manera que exigen las reivindicaciones. De esta manera se considera que cualquier medio que pueda proporcionar esas funcionalidades es equivalente a los mostrados en la presente memoria.

55 La referencia en la especificación a "una realización" de los presentes principios, así como otras variantes de la misma, significa que un rasgo, estructura, características, etc., particular descrita en conexión con la realización se incluyen en al menos una realización de los presentes principios. De esta manera, las apariciones de la frase "en

una realización", así como cualquier otra variante, que aparecen en diversos lugares en toda la especificación no se refieren todas necesariamente a la misma realización.

Se ha de apreciar que el uso de cualquiera de los siguientes "l", "y/o", y "en al menos uno de", por ejemplo, en los casos de "A/B", "A y/o B" y "al menos uno de A y B", se pretende que abarque la selección de la primera opción enumerada (A) solamente, o la selección de la segunda opción enumerada (B) solamente, o la selección de ambas opciones (A y B). Como ejemplo adicional, en los casos de "A, B, y/o C" y "al menos uno de A, B, y C", tal frase se pretende que abarque la selección de la primera opción enumerada (A) solamente, o la selección de la segunda opción enumerada (B) solamente, o la selección de la tercera opción enumerada (C) solamente, o la selección de la primera y la segunda opciones enumeradas (A y B) solamente, o la selección de la primera y la tercera opciones enumeradas (A y C) solamente, o la selección de la segunda y la tercera opciones enumeradas (B y C) solamente, o la selección de todas de las tres opciones enumeradas (A y B y C). Esto se puede extender, como es fácilmente evidente por un experto en ésta y las técnicas relacionadas, para tantos elementos enumerados.

Además, se ha de apreciar que mientras que una o más realizaciones de los presentes principios se describen en la presente memoria con respecto a una extensión del estándar AVC de MPEG-4, los presentes principios no se limitan solamente a esta extensión y/o este estándar y, de esta manera, se pueden utilizar con respecto a otros estándares, recomendaciones, y extensiones de codificación de vídeo de los mismos, mientras que se mantiene el espíritu de los presentes principios.

Como se usa en la presente memoria, "sintaxis de alto nivel" se refiere a sintaxis presente en el flujo de bits que reside jerárquicamente por encima de la capa de macrobloque. Por ejemplo, sintaxis de alto nivel, como se usa en la presente memoria, puede referirse a, pero no se limita a, sintaxis a nivel de cabecera de segmento, nivel de Información de Mejora Suplementaria (SEI), nivel de Conjunto de Parámetros de Imagen (PPS), nivel de Conjunto de Parámetros de Secuencia (SPS) y nivel de cabecera de unidad de Capa de Abstracción de Red (NAL).

También, como se usa en la presente memoria, las palabras "fotografía" e "imagen" se usan intercambiablemente y se refieren a una imagen fija o una fotografía de una secuencia de vídeo. Como se muestra, una fotografía puede ser un cuadro o un campo.

Adicionalmente, como se usa en la presente memoria, la palabra "señalar" se refiere a indicar algo a un decodificador correspondiente. Por ejemplo, el codificador puede señalar que la predicción intra está diseñada para ser usada para un bloque grande particular (como se define en la presente memoria) con el fin de hacer al decodificador consciente de qué tipo de predicción particular (por ejemplo, intra o inter) se usó en el lado del codificador. De esta forma, el mismo tipo de predicción se puede usar tanto en el lado del codificador como en el lado del decodificador. De esta manera, por ejemplo, un codificador puede transmitir una indicación (es decir, señalar) para un bloque grande particular que va a ser realizada predicción intra en ese bloque grande para permitir simplemente que el decodificador conozca y seleccione el mismo tipo de predicción para ese bloque grande. Ha de ser apreciado que la señalización se puede realizar de una variedad de formas. Por ejemplo, uno o más elementos de sintaxis, banderas, etc. se pueden usar para señalar información a un decodificador correspondiente.

Volviendo a la FIG. 4, un codificador de vídeo ejemplar al que se pueden aplicar los presentes principios según una realización de los presentes principios se indica de manera general mediante el número de referencia 400.

El codificador de vídeo 400 incluye un almacenador temporal de orden de cuadros 410 que tiene una salida en comunicación de señal con una entrada no inversora de un combinador 485. Una salida del combinador 485 está conectada en comunicación de señal con una primera entrada de un transformador y cuantificador 425. Una salida del transformador y cuantificador 425 está conectada en comunicación de señal con una primera entrada de un codificador de entropía 445 y una primera entrada de un transformador inverso y cuantificador inverso 450. Una salida del codificador de entropía 445 está conectada en comunicación de señal con una primera entrada no inversora de un combinador 490. Una salida del combinador 490 está conectada en comunicación de señal con una primera entrada de un almacenador temporal de salida 435.

Una primera salida de un controlador de codificador 405 está conectada en comunicación de señal con una segunda entrada del almacenador temporal de ordenación de cuadros 410, una segunda entrada del transformador inverso y cuantificador inverso 450, una entrada de un módulo de decisión de tipo de imagen 415, una entrada de un módulo de decisión de tipo de macrobloque (MB-type) 420, una segunda entrada de un módulo de predicción súper intra 460, una segunda entrada de un filtro de desbloqueo 465, una primera entrada de un compensador de movimiento 470, una primera entrada de un estimador de movimiento 475, y una segunda entrada de un almacenador temporal de imagen de referencia 480.

Una segunda salida del controlador de codificador 405 está conectada en comunicación de señal con una primera entrada de un insertador de Información de Mejora Suplementaria (SEI) 430, una segunda entrada del transformador y cuantificador 425, una segunda entrada del codificador de entropía 445, una segunda entrada del almacenador temporal de salida 435, y una entrada del insertador de Conjunto de Parámetros de Secuencia (SPS) y Conjunto de Parámetros de Imagen (PPS) 440.

Una primera salida del módulo de decisión de tipo de imagen 415 está conectada en comunicación de señal con una tercera entrada de un almacenador temporal de ordenación de cuadros 410. Una segunda salida del módulo de decisión de tipo de imagen 415 está conectada en comunicación de señal con una segunda entrada de un módulo de decisión de tipo macrobloque 420.

5 Una salida del insertador de Conjunto de Parámetros de Secuencia (SPS) y Conjunto de Parámetros de Imagen (PPS) 440 está conectada en comunicación de señal con una tercera entrada no inversora del combinador 490.

Una salida del cuantificador inverso y transformador inverso 450 está conectada en comunicación de señal con una primera entrada de no inversión de un combinador 419. Una salida del combinador 419 está conectada en comunicación de señal con una primera entrada del módulo de predicción súper intra 460 y una primera entrada del filtro de desbloqueo 465. Una salida del filtro de desbloqueo 465 está conectada en comunicación de señal con una primera entrada de un almacenador temporal de imagen de referencia 480. Una salida del almacenador temporal de imagen de referencia 480 está conectada en comunicación de señal con una segunda entrada del estimador de movimiento 475. Una primera salida del estimador de movimiento 475 está conectada en comunicación de señal con una segunda entrada del compensador de movimiento 470. Una segunda salida del estimador de movimiento 475 está conectada en comunicación de señal con una tercera entrada del codificador de entropía 445.

Una salida del compensador de movimiento 470 está conectada en comunicación de señal con una primera entrada de un conmutador 497. Una salida del módulo de predicción súper intra 460 está conectada en comunicación de señal con una segunda entrada del conmutador 497. Una salida del módulo de decisión de tipo de macrobloque 420 está conectada en comunicación de señal con una tercera entrada del conmutador 497. La tercera entrada del conmutador 497 determina si la entrada de "datos" del conmutador (en comparación con la entrada de control, es decir, la tercera entrada) va a ser proporcionada o no por el compensador de movimiento 470 o el módulo de predicción súper intra 460. La salida del conmutador 497 está conectada en comunicación de señal con una segunda entrada no inversora del combinador 419 y con una entrada inversora del combinador 485.

20 Las entradas del almacenador temporal de ordenación de cuadros 410 y el controlador de codificador 405 están disponibles como entrada del codificador 400, para recibir una imagen de entrada 401. Además, una entrada del insertador de Información de Mejora Suplementaria (SEI) 430 está disponible como entrada del codificador 400, para recibir metadatos. Una salida del almacenador temporal de salida 435 está disponible como salida del codificador 400, para emitir un flujo de bits.

25 Volviendo a la FIG. 5, un decodificador de vídeo ejemplar al que se pueden aplicar los presentes principios según una realización de los presentes principios se indica de manera general mediante el número de referencia 500.

El decodificador de vídeo 500 incluye un almacenador temporal de entrada 510 que tiene una salida conectada en comunicación de señal con una primera entrada del decodificador de entropía 545. Una primera salida del decodificador de entropía 545 está conectada en comunicación de señal con una primera entrada de un transformador inverso y cuantificador inverso 550. Una salida del transformador inverso y cuantificador inverso 550 está conectada en comunicación de señal con una segunda entrada no inversora de un combinador 525. Una salida del combinador 525 está conectada en comunicación de señal con una segunda entrada del filtro de desbloqueo 565 y una primera entrada de un módulo de predicción súper intra 560. Una segunda salida del filtro de desbloqueo 565 está conectada en comunicación de señal con una primera entrada de un almacenador temporal de imagen de referencia 580. Una salida del almacenador temporal de imagen de referencia 580 está conectada en comunicación de señal con una segunda entrada de un compensador de movimiento 570.

30 Una segunda salida del decodificador de entropía 545 está conectada en comunicación de señal con una tercera entrada del compensador de movimiento 570 y una primera entrada del filtro de desbloqueo 565. Una tercera salida del decodificador de entropía 545 está conectada en comunicación de señal con una entrada de un controlador de decodificador 505. Una primera salida del controlador de decodificador 505 está conectada en comunicación de señal con una segunda entrada del decodificador de entropía 545. Una segunda salida del controlador de decodificador 505 está conectada en comunicación de señal con una segunda entrada del transformador inverso y cuantificador inverso 550. Una tercera salida del controlador de decodificador 505 está conectada en comunicación de señal con una tercera entrada del filtro de desbloqueo 565. Una cuarta salida del controlador de decodificador 505 está conectada en comunicación de señal con una segunda entrada del módulo de predicción de súper intra 560, con una primera entrada del compensador de movimiento 570, y con una segunda entrada del almacenador temporal de imagen de referencia 580.

35 Una salida del compensador de movimiento 570 está conectada en comunicación de señal con una primera entrada de un conmutador 597. Una salida del módulo de predicción súper intra 560 está conectada en comunicación de señal con una segunda entrada del conmutador 597. Una salida del conmutador 597 está conectada en comunicación de señal con una primera entrada no inversora del combinador 525.

40 Una entrada del almacenador temporal de entrada 510 está disponible como entrada del decodificador 500, para recibir un flujo de bits de entrada. Una primera salida del filtro de desbloqueo 565 está disponible como salida del decodificador 500, para emitir una imagen de salida.

Como se ha señalado anteriormente, los presentes principios se dirigen a métodos y aparato para señalar predicción intra para bloques grandes de codificadores y decodificadores de vídeo. Además, como se ha señalado anteriormente, bloques grandes, a los que se pueden aplicar los presentes principios, se define que quiere decir que tienen un tamaño igual o mayor que 32x32.

5 En una realización, por facilidad de notación, dividimos la señalización de predicción intra en las dos siguientes partes: *sip\_type* (tipo de división intra espacial, que puede ser INTRA4x4, INTRA8x8, INTRA16x16, etc.), e *intra\_pred\_mode* (tal como, por ejemplo, 9 Modos de Predicción Intra dentro de INTRA4x4 e INTRA8x8) dentro de cada *sip\_type*. En más detalle con respecto a una realización particular, proponemos las tres siguientes reglas para los presentes principios: (1) seleccionar una unidad de codificación básica; (2) permitir predicción intra de capa jerárquica o bien dividiendo desde un tipo de predicción intra más grande o bien uniendo a partir de la unidad de codificación básica; y (3) para cada *sip\_type*, asignar una prioridad más alta al *intra\_pred\_mode* que se usa más frecuentemente. Con respecto a la Regla (1), permitamos varios *sip\_types* para la unidad de codificación básica.

#### Una realización

15 En una realización, establecemos que la unidad de codificación básica sea 16x16. En esta unidad de codificación, permitimos que *sip\_type* sea INTRA4x4, INTRA8x8 e INTRA16x16. También permitimos precisión intra de capa jerárquica como se muestra en la FIG. 6.

Volviendo a la FIG. 6, las divisiones jerárquicas ejemplares a las que se pueden aplicar los presentes principios se indican de manera general mediante el número de referencia 600. En esta realización, si el tamaño del bloque más grande se establece a 64x64, entonces usamos “señalización de división” para permitir predicción intra de capa jerárquica. Es decir, en una realización, añadimos *intra64\_flag*. Si *intra64\_flag* es igual a 1, entonces se usa INTRA64x64. De otro modo, si *intra64\_flag* es igual a 0, entonces dividimos un bloque 64x64 611 en cuatro bloques 32x32 621. Para cada uno de los bloques 32x32 621, añadimos *intra32\_flag*. Si *intra32\_flag* es igual a 1, entonces se usa INTRA32x32. De otro modo, si *intra32\_flag* es igual a 0, entonces todos los tipos *sip* permitidos en la unidad de codificación básica 16x16 se permiten aquí (es decir, para los bloques 32x32 621) también. Para *intra\_pred\_mode* en INTRA16x16, tenemos modo DC y los modos direccionales, estos últimos que permiten diferentes tipos de predicciones direccionales enviando la información de modo. De esta manera, un bloque de predicción intra 32x32 621 se puede dividir además en 4 bloques de predicción intra 16x16 631. Uno o más de los 4 bloques de predicción intra 16x16 631 se pueden dividir además a modo DC (no mostrado), un modo 16x16 641, un modo 8x8 651, y un modo 4x4 661. En esta realización, suponemos que tiene los cuatro siguientes modos de predicción intra 16x16: DC; horizontal (HOR); vertical (VER); y multidireccional (Multi-DIR). El *intra\_pred\_mode* se señala considerando la prioridad de cada modo. En INTRA16x16, dado que el modo DC se usa más a menudo que otros modos, añadimos INTRA16x16\_DC en la tabla *sip\_type* antes de INTRA16x16. Entonces eliminamos la indicación de *most\_probable\_mode* en *intra\_pred\_mode* para INTRA16x16. En su lugar, los otros 3 modos (16x16, 8x8, y 4x4) se indican absolutamente.

#### Sintaxis

Ilustramos un ejemplo de sintaxis para esta realización en la TABLA 2 y la TABLA 3. En particular, la TABLA 2 muestra una especificación ejemplar de tipos de *sip* para una unidad de codificación 16x16 según una realización de los presentes principios, y la TABLA 3 muestra modos de predicción INTRA16x16 ejemplares según una realización de los presentes principios. Para INTRA32x32/INTRA64x64, se usan los mismos modos que INTRA16x16. Para señalización, sustituimos la indicación *most\_probable\_mode* con *intra32\_DC\_flag* e *intra64\_DC\_flag* dado que se usa DC principalmente. Entonces codificamos absolutamente otro *intra\_pred\_mode*.

La señalización *intra\_pred\_mode* para INTRA4x4 e INTRA8x8 se puede realizar exactamente igual que en el Estándar AVC de MPEG-4, así que no enumeraremos estos modos en ninguna de las tablas.

TABLA 2

| Sip_type   | Índice | Bits de binarización |

|------------|--------|----------------------|

| SIP8x8     | 0      | 0                    |

| SIP16x16DC | 1      | 10                   |

| SIP16x16   | 2      | 110                  |

| SIP4x4     | 3      | 1110                 |

TABLA 3

| Modo de Predicción Intra | Índice | Bits de binarización |

|--------------------------|--------|----------------------|

| VER                      | 0      | 0                    |

| HOR                      | 1      | 10                   |

| Multi-DIR                | 2      | 11                   |

La TABLA 4 muestra la sintaxis de capa de macrobloque ejemplar, según una realización de los presentes principios.

5

TABLA 4

| macroblock_layer() {                      | C | Descriptor  |

|-------------------------------------------|---|-------------|

| ...                                       |   |             |

| intra64_flag                              | 2 | u(1)        |

| if (intra64_flag==1) {                    |   |             |

| intra64_DC_flag                           | 2 | u(1)        |

| if (intra64_DC_flag==0) {                 |   |             |

| intra_pred_mode_64                        | 2 | ue(v)/se(v) |

| if (intra_pred_mode_64==Multi-DIR) {      |   |             |

| Intra64_multidir_index                    | 2 | ue(v)/se(v) |

| }                                         |   |             |

| }                                         |   |             |

| }                                         |   |             |

| else {                                    |   |             |

| for (i32=0; i32<4; i32++) {               |   |             |

| intra32_flag[i32]                         | 2 | u(1)        |

| if (intra32_flag[i32]==1) {               |   |             |

| intra32_DC_flag[i32]                      | 2 | u(1)        |

| if (intra32_DC_flag[i32]==0) {            |   |             |

| intra_pred_mode_32[i32]                   | 2 | ue(v)/se(v) |

| if (intra_pred_mode_32[i32]==Multi-DIR) { |   |             |

| Intra32_multidir_index[i32]               | 2 | ue(v)/se(v) |

| }                                         |   |             |

| }                                         |   |             |

| }                                         |   |             |

| else {                                    |   |             |

| for (i16=0; i16<4; i16++) {               |   |             |

|                                                             |   |             |

|-------------------------------------------------------------|---|-------------|

| sip_type[i16]                                               | 2 | ue(v)/se(v) |

| if (sip_type[i16]==SIP16x16) {                              |   |             |

| intra_pred_mode_16[i16]                                     | 2 | ue(v)/se(v) |

| if (intra_pred_mode_16[i16]==Multi-DIR) {                   |   |             |

| intra16_multidir_index[i16]                                 | 2 | ue(v)/se(v) |

| }                                                           |   |             |

| }                                                           |   |             |

| else if (sip_type[i16]!=SIP16x16_DC) {                      |   |             |

| mb_intra_prediction_syntax();/*esta es la misma que H.264*/ |   |             |

| }                                                           |   |             |

| }                                                           |   |             |

| }                                                           |   |             |

| ...                                                         |   |             |

| }                                                           |   |             |

Las semánticas de algunos de los elementos de sintaxis de la TABLA 4 son como sigue:

Intra64\_flag igual a 1 especifica que se usa INTRA64x64. Intra64\_flag igual a 0 especifica que un bloque grande 64x64 se divide además en divisiones 32x32.

5 Intra64\_DC\_flag igual a 1 especifica que el intra\_pred\_mode es el modo DC para INTRA64x64. Intra64\_DC\_flag igual a 0 especifica que el intra\_pred\_mode no es el modo DC para INTRA64x64.

intra\_pred\_mode\_64 especifica un modo de predicción intra (que no incluye el modo DC) para INTRA64x64.

intra64\_multidir\_index especifica el índice del ángulo para el modo Multi\_Dir en INTRA64x64.

10 Intra32\_flag [i] igual a 1 especifica que se usa INTRA32x32 para el bloque grande 32x32 de orden i. Intra32\_flag [i] igual a 0 especifica que el bloque grande 32x32 de orden i se divide además en divisiones 16x16.

intra32\_DC\_flag [i] igual a 1 especifica que el intra\_pred\_mode es el modo DC para INTRA32x32 para el bloque 32x32 de orden i. intra32\_DC\_flag[i] igual a 0 especifica que el intra\_pred\_mode no es el modo DC para INTRA32x32 para el bloque 32x32 de orden i.

15 intra\_pred\_mode\_32 [i] especifica el modo de predicción intra (que no incluye el modo DC) para INTRA32x32 para el bloque grande 32x32 de orden i.

intra32\_multidir\_index especifica el índice del ángulo para el modo Multi\_Dir en INTRA32x32.

sip\_type [i] especifica el tipo de división intra espacial para la unidad de codificación de bloque básica en el bloque 16x16 de orden i.

20 intra\_pred\_mode\_16 [i] especifica el modo de predicción intra (que no incluye el modo DC) para INTRA16x16 para el bloque grande 16x16 de orden i.

Intra16\_multidir\_index especifica el índice del ángulo para el modo Multi\_Dir en INTRA16x16 para el bloque 16x16 de orden i.

Otra realización

25 En otra realización, seleccionamos adaptativamente que la unidad de bloque grande sea 32x32 o 64x64. La selección se puede señalar usando uno o más elementos de sintaxis de alto nivel. En una realización, si se selecciona 32x32, entonces sólo eliminamos toda la sintaxis relacionada con 64x64.

En otra realización, la predicción de capa intra jerárquica puede implicar la unión de la unidad de codificación básica. Por ejemplo, si la unidad de bloque más grande es 64x64 y la unidad de codificación básica es 16x16, entonces

usamos una bandera (is\_all\_16x16\_coding) para indicar si todos de los bloques 16x16 dentro de un bloque 64x64 son del tipo de codificación 16x16. Si is\_all\_16x16\_coding es igual a 1, entonces esto indica que se usa el tipo de codificación 16x16 y detenemos la señalización. De otro modo, usamos una bandera (is\_all\_32x32\_coding) para indicar si todos de los bloques 32x32 dentro de un bloque 64x64 son del tipo de codificación 32x32. Si is\_all\_32x32\_coding es igual a 1, entonces esto indica que todos de los bloques 32x32 dentro de un bloque 64x64 son del tipo de codificación 32x32. De otro modo, si is\_all\_32x32\_coding y is\_all\_16x16\_coding son iguales a 0, entonces esto indica que se usa INTRA64x64.

En otra realización, introducimos un tipo SIP para una unidad de bloques (large\_sip\_type) que tiene un tamaño no menor que 16x16. Los tres tipos se denominan como sigue: large\_intra\_16x16; large\_intra\_32x32; y large\_intra\_64x64. large\_intra\_16x16 significa que todos los bloques 16x16 dentro de un bloque grande son del tipo de codificación 16x16. large\_intra\_32x32 significa que todos los bloques 32x32 dentro de un bloque grande son del tipo de codificación 32x32. En una realización, large\_intra\_32x32 se puede combinar con la realización descrita anteriormente con intra32\_flag para permitir predicción intra jerárquica. large\_intra\_64x64 significa que todos los bloques 64x64 dentro de un bloque grande se codifican como INTRA64x64.

En otra realización, introducimos varias tablas sip/modo. Las tablas se pueden almacenar previamente tanto en un codificador como un decodificador, o las tablas se pueden especificar por el usuario y transmitir usando uno o más elementos de sintaxis de alto nivel. La TABLA 5 muestra la sintaxis de capa de macrobloque ejemplar, según una realización de los presentes principios.

TABLA 5

| macroblock_layer()              | C | Descriptor |

|---------------------------------|---|------------|

| ...                             |   |            |

| is_all_16x16_coding             | 2 | u(1)       |

| if (is_all_16x16_coding==0) {   |   |            |

| is_all_32x32_coding             | 2 | u(1)       |

| if (is_all_32x32_coding==0) {   |   |            |

| decode_with_64x64_coding_type() |   |            |

| }                               |   |            |

| else{                           |   |            |

| decode_with_32x32_coding_type() |   |            |

| }                               |   |            |

| }                               |   |            |

| else {                          |   |            |

| decode_with_16x16_coding_type() |   |            |

| }                               |   |            |

| ...                             |   |            |

| }                               |   |            |

Las semánticas de algunos de los elementos de sintaxis de la TABLA 5 son como sigue:

is\_all\_16x16\_coding igual a 1 especifica que todos los bloques 16x16 dentro de un bloque grande están codificados por un tipo de codificación 16x16. is\_all\_16x16\_coding igual a 0 especifica que el bloque grande no está codificado por un tipo de codificación 16x16.

is\_all\_32x32\_coding igual a 1 especifica que todos los bloques 32x32 dentro de un bloque grande están codificados por un tipo de codificación 32x32. is\_all\_32x32\_coding igual a 0 especifica que el bloque grande no está codificado por un tipo de codificación 32x32.

Volviendo a las FIG. 7A y 7B, que juntas representan un método ejemplar para codificación de datos de imagen para bloques grandes señalizando predicción intra para los bloques grandes, indicados de manera general por el número de referencia 700. El método 700 incluye un bloque de inicio 705 que pasa el control a un bloque de función 710. El bloque de función 710 realiza una inicialización, y pasa el control a un bloque de límite de bucle 715. El bloque de límite de bucle 715 realiza un bucle (en lo sucesivo también bucle 1) sobre bloques 64x64 (es decir, bloques que tienen un tamaño de bloque de 64x64), y pasa el control a un bloque de función 785 y un bloque de límite de bucle 720.

5 El bloque de función 785 realiza una decisión de modo 64x64 intra, establece una bandera Intra64\_DC en base a RD64 (es decir, la distorsión de tasa resultante de la decisión de modo 64x64 intra), y pasa el control a un bloque de decisión 770.

10 El bloque de límite de bucle 720 realiza un bucle (en lo sucesivo también bucle 2) sobre cuatro bloques 32x32 (es decir, los cuatro bloques que tienen un tamaño de bloque de 32x32 y obtenidos a partir del bloque 64x64 actual que se procesa por el bucle 1), y pasa el control a un bloque de función 790 y un bloque de límite de bucle 725.

15 El bloque de función 790 realiza una decisión de modo 32x32 Intra, establece la bandera Intra32\_DC en base a RD32 (es decir, la distorsión de tasa resultante de la decisión de modo 32x32 intra), y pasa el control a un bloque de decisión 750.

20 El bloque de límite de bucle 725 realiza un bucle (en lo sucesivo también bucle 3) sobre cuatro bloques 16x16 (es decir, los cuatro bloques que tienen un tamaño de bloque de 16x16 y obtenidos a partir del bloque 32x32 actual que se procesa por el bucle 2), y pasa el control a un bloque de función 730 y un bloque de función 735.

25 El bloque de función 730 evalúa el modo Intra 16x16\_DC, y pasa el control a un bloque de función 740. El bloque de función 735 evalúa otros modos 16x16 (es decir, otro distinto de Intra 16x16\_DC) y por debajo (por ejemplo, 8x8, 4x4, etc.), y pasa el control al bloque de función 740.

30 El bloque de función 740 realiza una decisión de modo 16x16 basado en RD16 (es decir, la distorsión de tasa resultante de la decisión de modo 16x16 intra), entonces acumula la RD16 de cada bloque 16x16 para obtener TotRD16 (que indica la distorsión de tasa total del bloque 32x32 entero cuando se codifica mediante cuatro bloques 16x16), y pasa el control a un bloque de límite de bucle 745. El bloque de límite de bucle 745 termina el bucle (es decir, el bucle 3) sobre los bloques 16x16, y pasa el control al bloque de decisión 750.

35 El bloque de decisión 750 determina si  $RD32 < TotRD16$  o no (es decir, si el coste de la distorsión de tasa para un bloque 32x32 actual es menor que el coste de distorsión de tasa total para los cuatro bloques 16x16 obtenidos a partir del bloque 32x32 actual). Si es así, entonces el control se pasa a un bloque de función 755. De otro modo, el control se pasa a un bloque de función 742.

40 El bloque de función 755 establece Intra32\_flag igual a uno, y pasa el control a un bloque de función 760. El bloque de función 742 establece Intra32\_flag igual a cero, y pasa el control al bloque de función 760.

45 El bloque de función 760 establece una acumulación de la RD32 de cada bloque 32x32 a TotRD32 para indicar la distorsión de tasa total del bloque 64x64 entero cuando se codifica mediante cuatro bloques 32x32, y pasa el control a un bloque de límite de bucle 765. El bloque de límite de bucle 765 termina el bucle (es decir, bucle 2) sobre los bloques 32x32, y pasa el control a un bloque de decisión 770.

50 El bloque de decisión 770 determina si  $RD64 < TotRD32$  o no (es decir, si el coste de distorsión de tasa para un bloque 64x64 actual es menor que el coste de distorsión de tasa total para los cuatro bloques 32x32 obtenidos a partir del bloque 64x64 actual). Si es así, entonces el control se pasa a un bloque de función 775. De otro modo, el control se pasa a un bloque de función 780.

55 El bloque de función 775 establece Intra64\_flag igual a uno, y pasa el control a un bloque de límite de bucle 795. El bloque de función 780 establece Intra64\_flag igual a cero, y pasa el control al bloque de función 795.

60 El bloque de función 795 termina el bucle (es decir, bucle 1) sobre los bloques 64x64, y pasa el control a un bloque de función 797. El bloque de función 797 codifica con entropía las banderas, intra\_pred\_mode, y un residuo, y pasa el control a un bloque final 799.

65 Volviendo a las FIG. 8A y 8B, que juntas representan un método ejemplar para decodificar datos de imagen para bloques grandes determinando que la predicción intra ha de ser aplicada a los bloques grandes, indicado de manera general por el número de referencia 800. El método 800 incluye un bloque de inicio 805 que pasa el control a un bloque de función 808. El bloque de función 808 inicializa el decodificador y entonces pasa el control a un bloque de función 810. El bloque de función 810 analiza sintácticamente el flujo de bits, y pasa el control a un bloque de límite de bucle 815. El bloque de límite de bucle 815 realiza un bucle (en lo sucesivo bucle 1) sobre bloques 64x64, y pasa el control a un bloque de decisión 820. El bloque de decisión 820 determina si Intra64\_flag se establece o no igual a uno. Si es así, entonces el control se pasa a un bloque de función 885. De otro modo, el control se pasa a un bloque de límite de bucle 825.

El bloque de función 885 determina si intra64\_DC\_flag se establece o no igual a uno. Si es así, entonces el control se pasa a un bloque de función 887. De otro modo, el control se pasa a un bloque de función 888. El bloque de función 887 realiza predicción DC 64x64 intra, y entonces pasa el control a un bloque de función 890. El bloque de función 888 realiza predicciones 64x64 intra distintas de modo DC 64x64 intra y entonces pasa el control a un

5 bloque de función 890. El bloque de función 890 decodifica un bloque 64x64 actual, y pasa el control a un bloque de límite de bucle 880. El bloque de límite de bucle 880 termina el bucle (es decir, bucle 1) sobre los bloques 64x64, y pasa el control a un bloque final 899.

El bloque de límite de bucle 825 realiza un bucle (en lo sucesivo bucle 2) sobre cuatro bloques 32x32, y pasa el control a un bloque de decisión 830. El bloque de decisión 830 determina si Intra32\_flag es o no igual a uno. Si es así, entonces el control se pasa a un bloque de función 835. De otro modo, el control se pasa a un bloque de límite de bucle 845.

10 El bloque de función 835 determina si Intra32\_DC\_flag es o no igual a uno. Si es así, entonces el control se pasa a un bloque de función 837. De otro modo, el control se pasa a un bloque de función 838. El bloque de función 837 realiza una predicción DC intra32x32, y pasa el control a un bloque de función 840. El bloque de función 838 realiza una predicción intra distinta del modo DC 32x32 intra, y entonces pasa el control al bloque de función 840. El bloque de función 840 decodifica un bloque 32x32, y pasa el control a un bloque de límite de bucle 875.

15 El bloque de límite de bucle 875 termina el bucle (es decir, bucle 2) sobre los bloques 32x32, y pasa el control al bloque de límite de bucle 880.

20 El bloque de límite de bucle 845 realiza un bucle (en lo sucesivo bucle 3) sobre cuatro bloques 16x16, y pasa el control a un bloque de decisión 850. El bloque de decisión 850 determina si sip\_type = Intra16\_DC o no. Si es así, entonces el control se pasa a un bloque de función 855. De otro modo, el control se pasa a un bloque de función 860.

25 El bloque de función 855 realiza predicción de modo Intra16x16\_DC, y pasa el control a un bloque de función 865. El bloque de función 860 realiza predicción de modo usando otros modos de predicción intra (es decir, distintos del modo Intra16x16\_DC), y pasa el control al bloque de función 865.

El bloque de función 865 decodifica un bloque 16x16, y pasa el control a un bloque de límite de bucle 870. El bloque de límite de bucle 870 termina el bucle (es decir, bucle 3) sobre los bloques 16x16, y pasa el control al bloque de límite de bucle 875.

30 Se dará ahora una descripción de algunas de las muchas ventajas/rasgos concurrentes de la presente invención, algunos de los cuales se han mencionado anteriormente. Por ejemplo, una ventaja/rasgo es un aparato que tiene un codificador de vídeo para codificar datos de imagen para al menos un bloque grande en una imagen señalizando predicción intra para al menos un bloque grande. La predicción intra se señala seleccionando un tamaño de unidad de codificación básica y asignando un único tipo de división intra espacial para el tamaño de unidad de codificación básica. El único tipo de división intra espacial es seleccionable de entre una pluralidad de tipos de división intra espacial. El al menos un bloque grande tiene un tamaño de bloque grande mayor que un tamaño de bloque de la unidad de codificación básica. La predicción intra es predicción intra de capa jerárquica y se realiza para el al menos un bloque grande por al menos una de división del tamaño de bloque grande al tamaño de unidad de codificación básica y unión desde el tamaño de unidad de codificación básica al tamaño de bloque grande.

40 Otra ventaja/rasgo es el aparato que tiene el codificador de vídeo como se ha descrito anteriormente, en donde para cada uno de la pluralidad de tipos de división intra espacial, se asigna una prioridad más alta a un modo de predicción intra particular que se usa más frecuentemente entre una pluralidad de modos de predicción intra disponibles.

45 Aún otra ventaja/rasgo es el aparato que tiene el codificador de vídeo como se ha descrito anteriormente, en donde se selecciona adaptativamente el tamaño de bloque grande.

50 Todavía otra ventaja/rasgo es el aparato que tiene el codificador de vídeo como se ha descrito anteriormente, en donde la señalización se realiza usando uno o más elementos de sintaxis de alto nivel.

Además, otra ventaja/rasgo es el aparato que tiene el codificador de vídeo como se ha descrito anteriormente, en donde al menos una tabla de tipo de división intra espacial y una tabla de modo de predicción intra está almacenada previamente y se usa por el codificador de vídeo para codificar el al menos un bloque grande. La al menos una de la tabla de tipo de división intra espacial y la tabla de modo de predicción intra se dispone para estar almacenada previamente y usada por un decodificador de vídeo correspondiente para decodificar el al menos un bloque grande.

55 Además, otra ventaja/rasgo es el aparato que tiene el codificador de vídeo como se ha descrito anteriormente, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra, se usa por el codificador de vídeo para codificar el al menos un bloque grande, y se transmite por el codificador de vídeo usando uno o más elementos de sintaxis de alto nivel.

Estos y otros rasgos y ventajas de los presentes principios se pueden comprobar fácilmente por un experto ordinario en la técnica pertinente en base a las enseñanzas en la presente memoria. Se ha de entender que las enseñanzas de los presentes principios se pueden implementar en diversas formas de hardware, software, microprogramas, procesadores de propósito especial, o combinaciones de los mismos.

5 Más preferiblemente, las enseñanzas de los presentes principios se implementan como una combinación de hardware y software. Además, el software se puede implementar como un programa de aplicaciones encarnado de manera tangible en una unidad de almacenamiento de programa. El programa de aplicaciones se puede cargar a, y ejecutar por, una máquina que comprende cualquier arquitectura adecuada. Preferiblemente, la máquina se implementa en una plataforma informática que tiene hardware tal como una o más unidades centrales de procesamiento ("CPU"), una memoria de acceso aleatorio ("RAM"), e interfaces de entrada/salida ("I/O"). La plataforma informática también puede incluir un sistema operativo y código de microinstrucciones. Los diversos procesos y funciones descritos en la presente memoria pueden ser o bien parte del código de microinstrucciones o bien parte del programa de aplicaciones, o cualquier combinación de los mismos, que se pueden ejecutar por una CPU. Además, otras diversas unidades periféricas pueden estar conectadas a la plataforma informática tales como una unidad de almacenamiento de datos adicional y una unidad de impresión.

10 Se ha de entender además que, debido a que algunos componentes del sistema constituyentes y métodos representados en los dibujos anexos se implementan preferiblemente en software, las conexiones reales entre los componentes de sistema o los bloques de función de proceso pueden diferir dependiendo de la manera en que se programan los presentes principios. Dadas las enseñanzas en la presente memoria, un experto ordinario en la técnica pertinente será capaz de contemplar éstas y similares implementaciones o configuraciones de los presentes principios.

15 Aunque las realizaciones ilustrativas se han descrito en la presente memoria con referencia a los dibujos anexos, ha de ser entendido que los presentes principios no están limitados a esas precisas realizaciones, y que diversos cambios y modificaciones se pueden efectuar en las mismas por un experto ordinario en la técnica pertinente sin apartarse del alcance de los presentes principios. Todos de tales cambios y modificaciones se pretende que estén incluidos dentro del alcance de los presentes principios como se expone en las reivindicaciones adjuntas.

## REIVINDICACIONES

## 1. Un método de decodificación que comprende:

decodificar datos de imagen para al menos un bloque grande en una imagen determinando que ha de ser realizada predicción intra para el al menos un bloque grande (820, 830),

5 en donde el al menos un bloque grande tiene un tamaño de bloque grande mayor que un tamaño de unidad de codificación básica, el tamaño de bloque grande que es uno de 32x32 y 64x64 y el tamaño de unidad de codificación básica que es 16x16, en donde se señala la predicción intra para el al menos un bloque grande:

- decodificando un elemento de sintaxis de señalización de división binaria que especifica si el bloque grande se divide además en cuatro subbloques dimensionados por igual;

10 - decodificando un modo de predicción intra para dicho bloque grande en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande no se divide aún más;

de otro modo en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande se divide aún más:

15 - decodificar para cada subbloque, en el caso donde dicho subbloque es 32x32, un elemento de sintaxis de señalización de división binaria que especifica si el subbloque 32x32 se divide además en cuatro bloques de unidad de codificación básica dimensionados por igual y decodificar un modo de predicción intra para dicho subbloque 32x32 en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que dicho subbloque 32x32 no se divide aún más; y

20 - decodificar para cada subbloque, en el caso donde dicho subbloque es 16x16, un único tipo de división intra espacial, el único tipo de división intra espacial que es determinable de entre una pluralidad de tipos de división intra espacial.

2. El método de la reivindicación 1, que comprende además decodificar al menos un elemento de sintaxis de señalización de unión binaria que especifica si los bloques dimensionados de unidad de codificación básica se unen en un bloque dimensionado grande.

25 3. El método de la reivindicación 1, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra está almacenada previamente y se usa por el método de decodificación para decodificar el al menos un bloque grande.

30 4. El método de la reivindicación 1, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra se recibe por dicho método de decodificación usando uno o más elementos de sintaxis de alto nivel y se usa por el método de decodificación para decodificar el al menos un bloque grande (810).

## 5. Un método de codificación que comprende:

codificar datos de imagen para al menos un bloque grande en una imagen determinando que ha de ser realizada predicción intra para el al menos un bloque grande (820, 830),

35 en donde el al menos un bloque grande tiene un tamaño de bloque grande mayor que un tamaño de unidad de codificación básica, el tamaño de bloque grande que es uno de 32x32 y 64x64 y el tamaño de unidad de codificación básica que es 16x16,

en donde se señala la predicción intra para el al menos un bloque grande:

- codificando un elemento de sintaxis de señalización de división binaria que especifica si el bloque grande se divide aún más en cuatro subbloques dimensionados por igual;

40 - codificando un modo de predicción intra para dicho bloque grande en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande no se divide aún más;

de otro modo en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande se divide aún más:

45 - codificar para cada subbloque, en el caso donde dicho subbloque es 32x32, un elemento de sintaxis de señalización de división binaria que especifica si dicho subbloque 32x32 se divide aún más en cuatro bloques de unidad de codificación básica dimensionados por igual y codificar un modo de predicción intra para dicho subbloque 32x32 en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que dicho subbloque 32x32 no se divide aún más; y

- codificar para cada subbloque, en el caso donde dicho subbloque es 16x16, un único tipo de división intra espacial, el único tipo de división intra espacial que es determinable de entre una pluralidad de tipos de división intra espacial.

5 6. El método de la reivindicación 5, que comprende además codificar al menos un elemento de sintaxis de señalización de unión binaria que especifica si los bloques dimensionados de unidad de codificación básica se unen en un bloque dimensionado grande.

7. El método de la reivindicación 5, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra está almacenada previamente y se usa por el método de codificación para codificar el al menos un bloque grande.

10 8. El método de la reivindicación 5, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra se codifica por dicho método de codificación usando uno o más elementos de sintaxis de alto nivel y se usa por el método de codificación para codificar el al menos un bloque grande (810).

9. Un decodificador de vídeo, que comprende:

15 medios para decodificar datos de imagen para al menos un bloque grande en una imagen determinando que ha de ser realizada predicción intra para el al menos un bloque grande (820, 830),

en donde el al menos un bloque grande tiene un tamaño de bloque grande mayor que un tamaño de unidad de codificación básica, el tamaño de bloque grande que es uno de 32x32 y 64x64 y el tamaño de unidad de codificación básica que es 16x16,

20 en donde se señala la predicción intra para el al menos un bloque grande por dichos medios para decodificar configurados para:

- decodificar un elemento de sintaxis de señalización de división binaria que especifica si el bloque grande se divide aún más en cuatro subbloques dimensionados por igual;

- decodificar un modo de predicción intra para dicho bloque grande en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande no se divide aún más;

25 de otro modo en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande se divide aún más:

- decodificar para cada subbloque, en el caso donde dicho subbloque es 32x32, un elemento de sintaxis de señalización de división binaria especificando si dicho subbloque 32x32 se divide aún más en cuatro bloques de unidad de codificación básica dimensionados por igual y decodificar un modo de predicción intra para dicho subbloque 32x32 en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que dicho subbloque 32x32 no se divide aún más; y

- decodificar para cada subbloque, en el caso donde dicho subbloque es 16x16, un único tipo de división intra espacial, el único tipo de división intra espacial que es determinable de entre una pluralidad de tipos de división intra espacial.

35 10. El decodificador de vídeo de la reivindicación 9, en donde dichos medios para decodificación están configurados además para decodificar al menos un elemento de sintaxis de señalización de unión binaria que especifica si los bloques dimensionados de unidad de codificación básica se unen en un bloque dimensionado grande.

11. El decodificador de vídeo de la reivindicación 9, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra está almacenada previamente y se usa por el decodificador de vídeo para decodificar el al menos un bloque grande.

40 12. El decodificador de vídeo de la reivindicación 9, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra se recibe por dicho decodificador de vídeo usando uno o más elementos de sintaxis de alto nivel y se usa por el decodificador de vídeo para decodificar el al menos un bloque grande (810).

45 13. Un codificador de vídeo, que comprende:

medios para codificar datos de imagen para al menos un bloque grande en una imagen determinando que ha de ser realizada predicción intra para el al menos un bloque grande (820, 830),

en donde el al menos un bloque grande tiene un tamaño de bloque grande mayor que un tamaño de unidad de codificación básica, el tamaño de bloque grande que es uno de 32x32 y 64x64 y el tamaño de unidad de codificación básica que es 16x16,

en donde se señala la predicción intra para el al menos un bloque grande por dichos medios para codificar configurados para:

- codificar un elemento de sintaxis de señalización de división binaria que especifica si el bloque grande se divide aún más en cuatro subbloques dimensionados por igual;

5 - codificar un modo de predicción intra para dicho bloque grande en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande no se divide aún más;

de otro modo en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande se divide aún más:

10 - codificar para cada subbloque, en el caso donde dicho subbloque es 32x32, un elemento de sintaxis de señalización de división binaria que especifica si dicho subbloque 32x32 se divide aún más en cuatro bloques de unidad de codificación básica dimensionados por igual y codificar un modo de predicción intra para dicho subbloque 32x32 en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que dicho subbloque 32x32 no se divide aún más; y

15 - codificar para cada subbloque, en el caso donde dicho subbloque es 16x16, un único tipo de división intra espacial, el único tipo de división intra espacial que es determinable de entre una pluralidad de tipos de división intra espacial.

14. El codificador de vídeo de la reivindicación 13, en donde dichos medios para codificar se codifican además para codificar al menos un elemento de sintaxis de señalización de unión binaria que especifica si los bloques dimensionados de unidad de codificación básica se unen en un bloque dimensionado grande.

20 15. El codificador de vídeo de la reivindicación 13, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra está almacenada previamente y se usa por el codificador de vídeo para codificar el al menos un bloque grande.

25 16. El codificador de vídeo de la reivindicación 13, en donde al menos una de una tabla de tipo de división intra espacial y una tabla de modo de predicción intra se codifica por dicho codificador de vídeo usando uno o más elementos de sintaxis de alto nivel y se usa por el codificador de vídeo para codificar el al menos un bloque grande (810).

17. Un flujo de bits que comprende:

30 - datos de imagen codificados representativos de al menos un bloque grande en una imagen obtenida determinado determinando que ha de ser realizada predicción intra para el al menos un bloque grande (820, 830), en donde el al menos un bloque grande tiene un tamaño de bloque grande mayor que un tamaño de unidad de codificación básica, el tamaño de bloque grande que es uno de 32x32 y 64x64 y el tamaño de unidad de codificación básica que es 16x16,

- un elemento de sintaxis de señalización de división binaria que especifica si el bloque grande se divide además en cuatro subbloques dimensionados por igual;

35 - un modo de predicción intra para dicho bloque grande en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande no se divide aún más;

de otro modo en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que el bloque grande se divide aún más:

40 - para cada subbloque, en el caso donde dicho subbloque es 32x32, un elemento de sintaxis de señalización de división binaria que especifica si dicho subbloque 32x32 se divide aún más en cuatro bloques de unidad de codificación básica dimensionados por igual y un modo de predicción intra para dicho subbloque 32x32 en el caso donde dicho elemento de sintaxis de señalización de división binaria especifica que dicho subbloque 32x32 no se divide aún más; y

45 - para cada subbloque, en el caso donde dicho subbloque es 16x16, un único tipo de división intra espacial, el único tipo de división intra espacial que es determinable de entre una pluralidad de tipos de división intra espacial.

18. El flujo de bits de la reivindicación 17, en donde dicho flujo de bits comprende además al menos un elemento de sintaxis de señalización de unión binaria que especifica si los bloques dimensionados de unidad de codificación básica se unen en un bloque dimensionado grande.

19. El flujo de bits de la reivindicación 17, en donde dicho flujo de bits además comprende datos representativos de al menos una de una tabla de tipo de división intra espacial y de una tabla de modo de predicción intra codificada en uno o más elementos de sintaxis de alto nivel, dicha al menos una tabla de tipo de división intra espacial y una tabla de modo de predicción intra que se usa para codificar dicho al menos un bloque grande.

*FIG. 1*

*FIG. 2*

FIG. 4

FIG. 6

FIG. 7A

FIG. 7B

FIG. 8A

FIG. 8B