(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2020-0087148

(43) 공개일자 2020년07월20일

- (51) 국제특허분류(Int. Cl.)

*H03M 13/13* (2006.01) *H03M 13/09* (2015.01)

*H03M 13/29* (2006.01) *H04L 1/00* (2006.01)

- (52) CPC특허분류

*H03M 13/13* (2013.01)

*H03M 13/09* (2019.01)

- (21) 출원번호 10-2020-7013553

- (22) 출원일자(국제) 2018년09월24일

심사청구일자 없음

- (85) 번역문제출일자 2020년05월12일

- (86) 국제출원번호 PCT/CN2018/107179

- (87) 국제공개번호 WO 2019/095853

국제공개일자 2019년05월23일

- (30) 우선권주장

PCT/CN2017/111600 2017년11월17일 중국(CN)

- (71) 출원인

퀄컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

- (72) 별명자

천 카이

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

수 창룡

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

(뒷면에 계속)

- (74) 대리인

특허법인코리아나

전체 청구항 수 : 총 88 항

(54) 발명의 명칭 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들

**(57) 요 약**

무선 통신을 위한 방법들, 시스템들 및 디바이스들이 설명된다. 일부 시스템들에서, 무선 디바이스들은 폴라 코드들을 사용하여 송신율들을 인코딩 및 디코딩 할 수도 있다. 송신 디바이스는 선택된 페이로드 사이즈에 기초하여 페이로드를 인코딩 할 수도 있다. 예를 들어, 송신 디바이스는 페이로드 비트들, 패리티 비트들, 동 (뒷면에 계속)

**대 표 도**

결된 비트들, 또는 이들의 일부 조합을 포함하는 비트 벡터를 구성할 수도 있고, 선택된 페이로드 사이즈에 기초하여 비트들 또는 비트들의 순서를 수정할 수도 있다. 디바이스는 이 비트 벡터에 기초하여 폴라-인코딩된 코드워드를 생성할 수도 있고 폴라-인코딩된 코드워드를 수신 디바이스로 송신할 수도 있다. 수신 디바이스는 폴라-인코딩된 코드워드를 블라인드 디코딩할 수도 있고 디코딩된 비트 벡터에 기초하여 정확한 페이로드 사이즈를 결정할 수도 있다. 예를 들어, 디바이스는 페이로드 사이즈 가설에 기초하여 디코딩된 비트들을 디코딩을 수행하고 체크할 수도 있고, 여기서 디코딩은 임의의 부정확한 페이로드 사이즈 가설에 대해 실패할 수도 있다.

## (52) CPC특허분류

**H03M 13/2906** (2013.01)**H04L 1/0038** (2013.01)**H04L 1/0057** (2013.01)

## (72) 발명자

**장 징**

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

**사르키스 가비**

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

**수 하오**

미국 92121-1714 캘리포니아주 샌디에고 모어하우스 드라이브 5775

## 명세서

### 청구범위

#### 청구항 1

무선 통신을 위한 방법으로서,

인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하는 단계;

상기 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하는 단계로서, 상기 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 상기 페이로드의 사이즈에 적어도 부분적으로 기초하는, 상기 비트 벡터를 결정하는 단계;

상기 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하는 단계; 및

상기 폴라-인코딩된 코드워드를 송신하는 단계를 포함하는, 무선 통신을 위한 방법.

#### 청구항 2

제 1 항에 있어서,

상기 페이로드의 사이즈에 대응하는 마스킹 벡터를 결정하는 단계; 및

상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하는 단계를 더 포함하는, 무선 통신을 위한 방법.

#### 청구항 3

제 2 항에 있어서,

상기 복수의 페이로드 비트들, 상기 복수의 패리티 비트들, 상기 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하는 단계는 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 방법.

#### 청구항 4

제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 비트 벡터는 상기 복수의 페이로드 비트들 및 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들을 포함하는, 무선 통신을 위한 방법.

#### 청구항 5

제 4 항에 있어서,

상기 비트 벡터를 결정하는 단계는:

상기 비트 벡터의 최저 인덱스에 상기 복수의 패리티 비트들의 적어도 하나의 비트를 위치시키는 단계를 포함하고, 상기 복수의 페이로드 비트들은 상기 비트 벡터의 상위 인덱스들에 위치되는, 무선 통신을 위한 방법.

#### 청구항 6

제 5 항에 있어서,

상기 폴라-인코딩된 코드워드를 생성하는 단계는:

상기 복수의 페이로드 비트들 및 상기 복수의 패리티 비트들을 폴라 코드의 복수의 정보 비트 채널들에 배정하는 단계를 포함하고, 상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 방법.

#### 청구항 7

제 4 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들을 생성하기 위해 상기 복수의 페이로드 비트들에 패리티 함수를 적용하는 단계를 더 포함하는, 무선 통신을 위한 방법.

#### 청구항 8

제 4 항 내지 제 7 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던던시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 방법.

#### 청구항 9

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하는 단계는:

상기 비트 벡터에 초기 비트를 첨부하는 단계를 포함하며, 상기 초기 비트는 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하는, 무선 통신을 위한 방법.

#### 청구항 10

제 9 항에 있어서,

상기 초기 비트는 상기 페이로드와 연관된 메시지 타입을 나타내는, 무선 통신을 위한 방법.

#### 청구항 11

제 1 항 내지 제 10 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하는 단계는:

상기 비트 벡터의 초기 비트가 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하도록, 상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 배열하는 단계를 포함하는, 무선 통신을 위한 방법.

#### 청구항 12

무선 통신을 위한 방법으로서,

풀라-인코딩된 코드워드를 수신하는 단계로서, 상기 풀라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 상기 풀라-인코딩된 코드워드를 수신하는 단계; 및

상기 풀라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하는 단계를 포함하고,

상기 블라인드 디코딩 프로세스는:

상기 비트 벡터와 연관된 적어도 하나의 로그-우도비 (LLR) 에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하는 단계;

결정된 상기 페이로드의 사이즈에 적어도 부분적으로 기초하여 상기 비트 벡터를 획득하기 위해 상기 풀라-인코딩된 코드워드를 디코딩하는 단계; 및

상기 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 상기 복수의 페이로드 비트들을 획득하기 위해 상기 비트 벡터를 파싱하는 단계를 포함하는, 무선 통신을 위한 방법.

#### 청구항 13

제 12 항에 있어서,

상기 페이로드의 사이즈를 결정하는 단계는:

상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 디스크램블링 동작들을 수행하는 단계를 포함하며, 각각의 디스크램бл링 동작은 페이로드 사이즈에 대응하는 마스킹 벡터를 사용하는, 무선 통신을 위한 방법.

**청구항 14**

제 13 항에 있어서,

복수의 디스크램블링된 패리티 비트들을 복수의 디스크램블링된 페이로드 비트들과 비교하는 것에 적어도 부분적으로 기초하여 성공적인 디스크램블링 동작을 식별하는 단계; 및

상기 페이로드의 사이즈를, 성공적인 디스크램블링 동작에 대한 마스킹 벡터에 대응하는 페이로드 사이즈로서 결정하는 단계를 더 포함하는, 무선 통신을 위한 방법.

**청구항 15**

제 13 항 또는 제 14 항에 있어서,

상기 디스크램블링 동작은 역 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 방법.

**청구항 16**

제 12 항 또는 제 15 항 중 어느 한 항에 있어서,

상기 폴라-인코딩된 코드워드는 또한, 복수의 패리티 비트들에 적어도 부분적으로 기초하여 생성되고, 상기 복수의 페이로드 비트들 및 복수의 패리티 비트들은 복수의 정보 비트 채널들에 배정되고, 그리고

상기 페이로드의 사이즈를 결정하는 단계는:

상기 복수의 패리티 비트들을 사용하여 상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 패리티 체크들을 수행하는 단계를 포함하며, 각각의 패리티 체크에 대한 상기 폴라-인코딩된 코드워드 내에서의 상기 복수의 패리티 비트들의 위치결정은 대응하는 페이로드 사이즈를 나타내는, 무선 통신을 위한 방법.

**청구항 17**

제 16 항에 있어서,

상기 복수의 패리티 비트들 및 상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 적어도 부분적으로 기초하여 성공적인 패리티 체크를 식별하는 단계; 및

상기 페이로드의 사이즈를, 상기 성공적인 패리티 체크를 가져오는 상기 복수의 패리티 비트들의 위치결정에 의해 나타내어지는 대응하는 페이로드 사이즈로서 결정하는 단계를 더 포함하는, 무선 통신을 위한 방법.

**청구항 18**

제 16 항 또는 제 17 항에 있어서,

상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 방법.

**청구항 19**

제 16 항 내지 제 18 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던던시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 방법.

**청구항 20**

제 12 항 내지 제 19 항 중 어느 한 항에 있어서,

상기 페이로드의 사이즈를 결정하는 단계는:

디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR 을 갖는 상기 폴라-인코딩된 코드워드의 최소 신뢰성 비트 채널을 식별하는 단계; 및

식별된 상기 최소 신뢰성 비트 채널에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하는 단계를

포함하는, 무선 통신을 위한 방법.

### 청구항 21

제 20 항에 있어서,

상기 비트 벡터를 파싱하는 단계는:

상기 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR에 대응하는 초기 비트를 제거하는 단계를 포함하는, 무선 통신을 위한 방법.

### 청구항 22

제 20 항 또는 제 21 항에 있어서,

상기 비트 벡터를 파싱하는 단계는:

상기 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR에 적어도 부분적으로 기초하여 상기 비트 벡터의 비트들을 재정렬하는 단계를 포함하는, 무선 통신을 위한 방법.

### 청구항 23

무선 통신을 위한 장치로서,

인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하기 위한 수단;

상기 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하기 위한 수단으로서, 상기 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 상기 페이로드의 사이즈에 적어도 부분적으로 기초하는, 상기 비트 벡터를 결정하기 위한 수단;

상기 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하기 위한 수단; 및

상기 폴라-인코딩된 코드워드를 송신하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

### 청구항 24

제 23 항에 있어서,

상기 페이로드의 사이즈에 대응하는 마스킹 벡터를 결정하기 위한 수단; 및

상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 25

제 24 항에 있어서,

상기 복수의 페이로드 비트들, 상기 복수의 패리티 비트들, 상기 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하는 것은 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 장치.

### 청구항 26

제 23 항 내지 제 25 항 중 어느 한 항에 있어서,

상기 비트 벡터는 상기 복수의 페이로드 비트들 및 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들을 포함하는, 무선 통신을 위한 장치.

### 청구항 27

제 26 항에 있어서,

상기 비트 벡터를 결정하기 위한 수단은:

상기 비트 벡터의 최저 인덱스에 상기 복수의 패리티 비트들의 적어도 하나의 비트를 위치시키기 위한 수단을 포함하고, 상기 복수의 페이로드 비트들은 상기 비트 벡터의 상위 인덱스들에 위치되는, 무선 통신을 위한

장치.

### 청구항 28

제 27 항에 있어서,

상기 폴라-인코딩된 코드워드를 생성하기 위한 수단은:

상기 복수의 페이로드 비트들 및 상기 복수의 패리티 비트들을 폴라 코드의 복수의 정보 비트 채널들에 배정하기 위한 수단을 포함하고, 상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 장치.

### 청구항 29

제 26 항 내지 제 28 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들을 생성하기 위해 상기 복수의 페이로드 비트들에 패리티 함수를 적용하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 30

제 26 항 내지 제 29 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던던시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 장치.

### 청구항 31

제 23 항 내지 제 30 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하기 위한 수단은:

상기 비트 벡터에 초기 비트를 침부하기 위한 수단을 포함하며, 상기 초기 비트는 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하는, 무선 통신을 위한 장치.

### 청구항 32

제 31 항에 있어서,

상기 초기 비트는 상기 페이로드와 연관된 메시지 타입을 나타내는, 무선 통신을 위한 장치.

### 청구항 33

제 23 항 내지 제 32 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하기 위한 수단은:

상기 비트 벡터의 초기 비트가 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하도록, 상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 배열하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

### 청구항 34

무선 통신을 위한 장치로서,

폴라-인코딩된 코드워드를 수신하기 위한 수단으로서, 상기 폴라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 상기 폴라-인코딩된 코드워드를 수신하기 위한 수단; 및

상기 폴라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하기 위한 수단을 포함하고,

상기 블라인드 디코딩 프로세스는:

상기 비트 벡터와 연관된 적어도 하나의 로그-우도비 (LLR) 에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하기 위한 수단;

결정된 상기 페이로드의 사이즈에 적어도 부분적으로 기초하여 상기 비트 벡터를 획득하기 위해 상기 폴라-인코딩된 코드워드를 디코딩하기 위한 수단; 및

상기 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 상기 복수의 페이로드 비트들을 획득하기 위해 상기 비트 벡터를 파싱하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

### 청구항 35

제 34 항에 있어서,

상기 페이로드의 사이즈를 결정하기 위한 수단은:

상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 디스크램블링 동작들을 수행하기 위한 수단을 포함하며, 각각의 디스크램бл링 동작은 페이로드 사이즈에 대응하는 마스킹 벡터를 사용하는, 무선 통신을 위한 장치.

### 청구항 36

제 35 항에 있어서,

복수의 디스크램블링된 패리티 비트들을 복수의 디스크램블링된 페이로드 비트들과 비교하는 것에 적어도 부분적으로 기초하여 성공적인 디스크램블링 동작을 식별하기 위한 수단; 및

상기 페이로드의 사이즈를, 성공적인 디스크램블링 동작에 대한 마스킹 벡터에 대응하는 페이로드 사이즈로서 결정하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 37

제 35 항 또는 제 36 항에 있어서,

상기 디스크램블링 동작은 역 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 장치.

### 청구항 38

제 34 항 내지 제 37 항 중 어느 한 항에 있어서,

폴라-인코딩된 코드워드를 위한 수단은 또한, 복수의 패리티 비트들에 적어도 부분적으로 기초하여 생성되고, 상기 복수의 페이로드 비트들 및 복수의 패리티 비트들은 복수의 정보 비트 채널들에 배정되고, 그리고

상기 페이로드의 사이즈를 결정하는 것은:

상기 복수의 패리티 비트들을 사용하여 상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 패리티 체크들을 수행하기 위한 수단을 포함하며, 각각의 패리티 체크에 대한 상기 폴라-인코딩된 코드워드 내에서의 상기 복수의 패리티 비트들의 위치결정은 대응하는 페이로드 사이즈를 나타내는, 무선 통신을 위한 장치.

### 청구항 39

제 38 항에 있어서,

상기 복수의 패리티 비트들 및 상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 적어도 부분적으로 기초하여 성공적인 패리티 체크를 식별하기 위한 수단; 및

상기 페이로드의 사이즈를, 상기 성공적인 패리티 체크를 가져오는 상기 복수의 패리티 비트들의 위치결정에 의해 나타내어지는 대응하는 페이로드 사이즈로서 결정하기 위한 수단을 더 포함하는, 무선 통신을 위한 장치.

### 청구항 40

제 38 항 또는 제 39 항에 있어서,

상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 장치.

**청구항 41**

제 38 항 내지 제 40 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던던시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 장치.

**청구항 42**

제 34 항 내지 제 41 항 중 어느 한 항에 있어서,

상기 페이로드의 사이즈를 결정하기 위한 수단은:

디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR 을 갖는 상기 폴라-인코딩된 코드워드의 최소 신뢰성 비트 채널을 식별하기 위한 수단; 및

식별된 상기 최소 신뢰성 비트 채널에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

**청구항 43**

제 42 항에 있어서,

상기 비트 벡터를 파싱하기 위한 수단은:

상기 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR 에 대응하는 초기 비트를 제거하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

**청구항 44**

제 42 항 또는 제 43 항에 있어서,

상기 비트 벡터를 파싱하기 위한 수단은:

상기 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR 에 적어도 부분적으로 기초하여 상기 비트 벡터의 비트들을 재정렬하기 위한 수단을 포함하는, 무선 통신을 위한 장치.

**청구항 45**

무선 통신을 위한 장치로서,

프로세서;

상기 프로세서와 전자 통신하는 메모리; 및

상기 메모리에 저장되는 명령들을 포함하고,

상기 명령들은 상기 장치로 하여금:

인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하게 하고;

상기 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하게 하는 것으로서, 상기 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 상기 페이로드의 사이즈에 적어도 부분적으로 기초하는, 상기 비트 벡터를 결정하게 하고;

상기 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하게 하고; 그리고

상기 폴라-인코딩된 코드워드를 송신하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

**청구항 46**

제 45 항에 있어서,

상기 명령들은 또한 상기 장치로 하여금:

상기 페이로드의 사이즈에 대응하는 마스킹 벡터를 결정하게 하고; 그리고

상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

#### 청구항 47

제 46 항에 있어서,

상기 복수의 페이로드 비트들, 상기 복수의 패리티 비트들, 상기 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하는 것은 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 장치.

#### 청구항 48

제 45 항 내지 제 47 항 중 어느 한 항에 있어서,

상기 비트 벡터는 상기 복수의 페이로드 비트들 및 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들을 포함하는, 무선 통신을 위한 장치.

#### 청구항 49

제 48 항에 있어서,

상기 비트 벡터를 결정하는 명령들은 상기 장치로 하여금:

상기 비트 벡터의 최저 인덱스에 상기 복수의 패리티 비트들의 적어도 하나의 비트를 위치시키게 하도록 상기 프로세서에 의해 실행가능하고, 상기 복수의 페이로드 비트들은 상기 비트 벡터의 상위 인덱스들에 위치되는, 무선 통신을 위한 장치.

#### 청구항 50

제 49 항에 있어서,

상기 폴라-인코딩된 코드워드를 생성하는 명령들은 상기 장치로 하여금:

상기 복수의 페이로드 비트들 및 상기 복수의 패리티 비트들을 폴라 코드의 복수의 정보 비트 채널들에 배정하게 하도록 상기 프로세서에 의해 실행가능하고, 상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 장치.

#### 청구항 51

제 48 항 내지 제 50 항 중 어느 한 항에 있어서,

상기 명령들은 또한 상기 장치로 하여금:

상기 복수의 패리티 비트들을 생성하기 위해 상기 복수의 페이로드 비트들에 패리티 함수를 적용하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

#### 청구항 52

제 48 항 내지 제 51 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던던시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 장치.

#### 청구항 53

제 45 항 내지 제 52 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하는 명령들은 상기 장치로 하여금:

상기 비트 벡터에 초기 비트를 첨부하게 하도록 상기 프로세서에 의해 실행가능하며, 상기 초기 비트는 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하는, 무선 통신을 위한 장치.

#### 청구항 54

제 53 항에 있어서,

상기 초기 비트는 상기 페이로드와 연관된 메시지 타입을 나타내는, 무선 통신을 위한 장치.

### 청구항 55

제 45 항 내지 제 54 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하는 명령들은 상기 장치로 하여금:

상기 비트 벡터의 초기 비트가 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하도록, 상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 배열하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

### 청구항 56

무선 통신을 위한 장치로서,

프로세서;

상기 프로세서와 전자 통신하는 메모리; 및

상기 메모리에 저장된 명령들을 포함하고,

상기 명령들은 상기 장치로 하여금:

풀라-인코딩된 코드워드를 수신하게 하는 것으로서, 상기 폴라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 상기 폴라-인코딩된 코드워드를 수신하게 하고; 그리고

풀라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하게 하도록 상기 프로세서에 의해 실행가능하고,

상기 블라인드 디코딩 프로세스를 위하여 상기 메모리에 저장된 명령들은 상기 장치로 하여금:

상기 비트 벡터와 연관된 적어도 하나의 로그-우도비 (LLR) 에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하게 하고;

결정된 상기 페이로드의 사이즈에 적어도 부분적으로 기초하여 비트 벡터를 획득하기 위해 폴라-인코딩된 코드워드를 디코딩하게 하고; 그리고

상기 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 복수의 페이로드 비트들을 획득하기 위해 비트 벡터를 파싱하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

### 청구항 57

제 56 항에 있어서,

상기 페이로드의 사이즈를 결정하는 명령들은 상기 장치로 하여금:

상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 디스크램블링 동작들을 수행하게 하도록 상기 프로세서에 의해 실행가능하며, 각각의 디스크램бл링 동작은 페이로드 사이즈에 대응하는 마스킹 벡터를 사용하는, 무선 통신을 위한 장치.

### 청구항 58

제 57 항에 있어서,

상기 명령들은 또한 상기 장치로 하여금:

복수의 디스크램블링된 패리티 비트들을 복수의 디스크램블링된 페이로드 비트들과 비교하는 것에 적어도 부분적으로 기초하여 성공적인 디스크램블링 동작을 식별하게 하고; 그리고

상기 페이로드의 사이즈를, 성공적인 디스크램블링 동작에 대한 마스킹 벡터에 대응하는 페이로드 사이즈로서

결정하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

### 청구항 59

제 57 항 또는 제 58 항에 있어서,

상기 디스크램블링 동작은 역 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 장치.

### 청구항 60

제 56 항 내지 제 59 항 중 어느 한 항에 있어서,

폴라-인코딩된 코드워드에 대한 명령들은 또한, 복수의 패리티 비트들에 적어도 부분적으로 기초하여 생성되고, 상기 복수의 페이로드 비트들 및 복수의 패리티 비트들은 복수의 정보 비트 채널들에 배정되고, 그리고

상기 페이로드의 사이즈를 결정하는 명령들은 상기 장치로 하여금:

상기 복수의 패리티 비트들을 사용하여 상기 적어도 하나의 LLR에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 패리티 체크들을 수행하게 하도록 상기 프로세서에 의해 실행가능하며, 각각의 패리티 체크에 대한 상기 폴라-인코딩된 코드워드 내에서의 상기 복수의 패리티 비트들의 위치결정은 대응하는 페이로드 사이즈를 나타내는, 무선 통신을 위한 장치.

### 청구항 61

제 60 항에 있어서,

상기 명령들은 또한 상기 장치로 하여금:

상기 복수의 패리티 비트들 및 상기 적어도 하나의 LLR에 대한 적어도 하나의 비트 결정에 적어도 부분적으로 기초하여 성공적인 패리티 체크를 식별하게 하고; 그리고

상기 페이로드의 사이즈를, 상기 성공적인 패리티 체크를 가져오는 상기 복수의 패리티 비트들의 위치결정에 의해 나타내어지는 대응하는 페이로드 사이즈로서 결정하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

### 청구항 62

제 60 항 또는 제 61 항에 있어서,

상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 장치.

### 청구항 63

제 60 항 내지 제 62 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던더시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 장치.

### 청구항 64

제 56 항 내지 제 63 항 중 어느 한 항에 있어서,

상기 페이로드의 사이즈를 결정하는 명령들은 상기 장치로 하여금:

디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR을 갖는 상기 폴라-인코딩된 코드워드의 최소 신뢰성 비트 채널을 식별하게 하고; 그리고

식별된 상기 최소 신뢰성 비트 채널에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

### 청구항 65

제 64 항에 있어서,

상기 비트 벡터를 파싱하는 명령들은 상기 장치로 하여금:

상기 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR에 대응하는 초기 비트를 제거하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

### 청구항 66

제 64 항 또는 제 65 항에 있어서,

상기 비트 벡터를 파싱하는 명령들은 상기 장치로 하여금:

상기 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR에 적어도 부분적으로 기초하여 상기 비트 벡터의 비트들을 재정렬하게 하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 장치.

### 청구항 67

무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체로서,

상기 코드는:

인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하고;

상기 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하는 것으로서, 상기 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 상기 페이로드의 사이즈에 적어도 부분적으로 기초하는, 상기 비트 벡터를 결정하고;

상기 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하고; 그리고

상기 폴라-인코딩된 코드워드를 송신하도록 실행가능한 명령들을 포함하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 68

제 67 항에 있어서,

상기 명령들은 또한:

상기 페이로드의 사이즈에 대응하는 마스킹 벡터를 결정하고; 그리고

상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하도록 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 69

제 68 항에 있어서,

상기 복수의 페이로드 비트들, 상기 복수의 패리티 비트들, 상기 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하는 것은 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 70

제 67 항 내지 제 69 항 중 어느 한 항에 있어서,

상기 비트 벡터는 상기 복수의 페이로드 비트들 및 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들을 포함하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 71

제 70 항에 있어서,

상기 비트 벡터를 결정하는 명령들은:

상기 비트 벡터의 최저 인덱스에 상기 복수의 패리티 비트들의 적어도 하나의 비트를 위치시키도록 프로세서에 의해 실행가능하고, 상기 복수의 페이로드 비트들은 상기 비트 벡터의 상위 인덱스들에 위치되는, 무선 통신을

위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

## 청구항 72

제 71 항에 있어서,

상기 폴라-인코딩된 코드워드를 생성하는 명령들은:

상기 복수의 페이로드 비트들 및 상기 복수의 패리티 비트들을 폴라 코드의 복수의 정보 비트 채널들에 배정하도록 상기 프로세서에 의해 실행가능하고, 상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

## 청구항 73

제 70 항 내지 제 72 항 중 어느 한 항에 있어서,

상기 명령들은 또한:

상기 복수의 패리티 비트들을 생성하기 위해 상기 복수의 페이로드 비트들에 패리티 함수를 적용하도록 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

## 청구항 74

제 70 항 내지 제 73 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던던시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

## 청구항 75

제 67 항 내지 제 74 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하는 명령들은:

상기 비트 벡터에 초기 비트를 첨부하도록 프로세서에 의해 실행가능하며, 상기 초기 비트는 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

## 청구항 76

제 75 항에 있어서,

상기 초기 비트는 상기 페이로드와 연관된 메시지 타입을 나타내는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

## 청구항 77

제 67 항 내지 제 76 항 중 어느 한 항에 있어서,

상기 비트 벡터를 결정하는 명령들은:

상기 비트 벡터의 초기 비트가 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하도록, 상기 복수의 페이로드 비트들, 상기 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 배열하도록 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

## 청구항 78

무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체로서,

상기 코드는:

폴라-인코딩된 코드워드를 수신하는 것으로서, 상기 폴라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비

트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 상기 폴라-인코딩된 코드워드를 수신하고; 그리고

폴라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하도록 실행가능한 명령들을 포함하고,

상기 블라인드 디코딩 프로세스를 위한 명령들은:

상기 비트 벡터와 연관된 적어도 하나의 로그-우도비 (LLR) 에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하고;

결정된 상기 페이로드의 사이즈에 적어도 부분적으로 기초하여 비트 벡터를 획득하기 위해 폴라-인코딩된 코드워드를 디코딩하고; 그리고

상기 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 복수의 페이로드 비트들을 획득하기 위해 비트 벡터를 파싱하도록 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 79

제 78 항에 있어서,

상기 페이로드의 사이즈를 결정하는 명령들은:

상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 디스크램블링 동작들을 수행하도록 상기 프로세서에 의해 실행가능하며, 각각의 디스크램бл링 동작은 페이로드 사이즈에 대응하는 마스킹 벡터를 사용하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 80

제 79 항에 있어서,

상기 명령들은 또한:

복수의 디스크램블링된 패리티 비트들을 복수의 디스크램블링된 페이로드 비트들과 비교하는 것에 적어도 부분적으로 기초하여 성공적인 디스크램블링 동작을 식별하고; 그리고

상기 페이로드의 사이즈를, 성공적인 디스크램블링 동작에 대한 마스킹 벡터에 대응하는 페이로드 사이즈로서 결정하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 81

제 79 항 또는 제 80 항에 있어서,

상기 디스크램블링 동작은 역 배타적 or (XOR) 연산을 포함하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 82

제 78 항 내지 제 81 항 중 어느 한 항에 있어서,

폴라-인코딩된 코드워드에 대한 명령들은 또한, 복수의 패리티 비트들에 적어도 부분적으로 기초하여 생성되고, 상기 복수의 페이로드 비트들 및 복수의 패리티 비트들은 복수의 정보 비트 채널들에 배정되고, 그리고

상기 페이로드의 사이즈를 결정하는 것은:

상기 복수의 패리티 비트들을 사용하여 상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 패리티 체크들을 수행하도록 상기 프로세서에 의해 실행가능하며, 각각의 패리티 체크에 대한 상기 폴라-인코딩된 코드워드 내에서의 상기 복수의 패리티 비트들의 위치결정은 대응하는 페이로드 사이즈를 나타내는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 청구항 83

제 82 항에 있어서,

상기 명령들은 또한:

상기 복수의 패리티 비트들 및 상기 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 적어도 부분적으로 기초하여 성공적인 패리티 체크를 식별하고; 그리고

상기 페이로드의 사이즈를, 상기 성공적인 패리티 체크를 가져오는 상기 복수의 패리티 비트들의 위치결정에 의해 나타내어지는 대응하는 페이로드 사이즈로서 결정하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 84

제 82 항 또는 제 83 항에 있어서,

상기 복수의 패리티 비트들의 적어도 하나의 비트는 상기 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정되는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 85

제 82 항 내지 제 84 항 중 어느 한 항에 있어서,

상기 복수의 패리티 비트들은 복수의 시클릭 리던던시 체크 (CRC) 비트들을 포함하는, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 86

제 78 항 내지 제 85 항 중 어느 한 항에 있어서,

상기 페이로드의 사이즈를 결정하는 명령들은:

디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR 을 갖는 상기 폴라-인코딩된 코드워드의 최소 신뢰성 비트 채널을 식별하고; 그리고

식별된 상기 최소 신뢰성 비트 채널에 적어도 부분적으로 기초하여 상기 페이로드의 사이즈를 결정하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 87

제 86 항에 있어서,

상기 비트 벡터를 파싱하는 명령들은:

상기 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR 에 대응하는 초기 비트를 제거하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

#### 청구항 88

제 86 항 또는 제 87 항에 있어서,

상기 비트 벡터를 파싱하는 명령들은:

상기 디폴트 동결된 비트 값을 나타내는 LLR 에 적어도 부분적으로 기초하여 상기 비트 벡터의 비트들을 재정렬하도록 상기 프로세서에 의해 실행가능한, 무선 통신을 위한 코드를 저장하는 비일시적 컴퓨터 판독가능 저장 매체.

### 발명의 설명

#### 기술 분야

상호 참조들

[0001] 본 특허 출원은 2017년 11월 17일 출원되고 발명의 명칭이 "POLAR CODING TECHNIQUES FOR BLIND DETECTION OF DIFFERENT PAYLOAD SIZES" 인 Chen 등의 국제 특허 출원 PCT/CN2017/111600 의 이익을 주장하고, 이는 본 출원

의 양수인에게 양도되었으며 본원에서 참조로서 그 전체 내용이 통합된다.

#### [0003] 기술 분야

[0004] 다음은 일반적으로 무선 통신에 관한 것이고, 보다 구체적으로는 상이한 페이로드 사이즈들의 블라이드 검출에 대한 폴라 코딩 기법들에 관한 것이다.

### 배경 기술

[0005] 무선 통신 시스템들은 음성, 비디오, 패킷 데이터, 메시징, 브로드캐스트 등과 같은 다양한 유형들의 통신 컨텐츠를 제공하기 위해 널리 전개된다. 이들 시스템들은 이용 가능한 시스템 리소스들 (예를 들어, 시간, 주파수, 및 전력) 을 공유함으로써 다수의 사용자들과의 통신을 지원 가능할 수도 있다. 그러한 다중 액세스 시스템들의 예들은 롱 텀 에볼루션 (Long Term Evolution; LTE) 시스템들 또는 LTE-어드밴스드 (LTE-Advanced; LTE-A) 시스템들과 같은 제 4 세대 (4G) 시스템들, 및 뉴 라디오 (New Radio; NR) 시스템들로 지칭될 수도 있는 제 5 세대 (5G) 시스템들을 포함한다. 이들 시스템은 코드 분할 다중 액세스 (CDMA), 시분할 다중 액세스 (TDMA), 주파수 분할 다중 액세스 (FDMA), 직교 FDMA (OFDMA) 또는 이산 푸리에 변환-확산-직교 OFDM (DFT-S-OFDM) 과 같은 기술을 채용할 수도 있다. 무선 다중 액세스 통신 시스템은 다수의 기지국들 또는 네트워크 액세스 노드들을 포함할 수도 있고, 이들 각각은, 다르게는 사용자 장비 (UE들) 로서 공지될 수도 있는 다수의 통신 디바이스들에 대한 통신을 동시에 지원한다.

[0006] 일부 무선 통신 시스템들에서, 무선 디바이스들은 송신물을 인코딩 및 디코딩하기 위하여, 예러-수정 코드들, 이를 테면, 폴라 코드들을 구현할 수도 있다. 무선 디바이스는 폴라 코드들을 구현할 때 코드워드 내에서 인코딩된 페이로드의 사이즈를 포함하는 다수의 상이한 코드워드 구성들을 사용하여 송신될 수도 있다. 그러나, 상이한 사이즈들의 특정 고유 페이로드들을 인코딩하는 것은 송신에 대한 동일한 코드워드들로 이어진다.

이들 경우에, 수신된 코드워드가 다수의 상이한 페이로드들 및 대응하는 페이로드 사이즈들에 맵핑 할 수 있기 때문에, 무선 디바이스가 이들 코드워드들 중 하나를 수신하는 것은 페이로드 또는 페이로드 사이즈를 정확하게 결정 가능하지 못할 수도 있다.

### 발명의 내용

#### 해결하려는 과제

### 과제의 해결 수단

[0007] 상술한 기법들은 상이한 페이로드 사이즈들의 블라이드 검출을 위한 폴라 코딩 기법들을 지원하는 개선된 방법들, 시스템들, 디바이스들, 또는 장치들에 관한 것이다. 일반적으로, 상술한 기법들은 폴라 코드들을 사용하여 코드워드들을 인코딩 및 디코딩하기 위하여 제공하며, 여기서 코드워드들은 페이로드 사이즈를 표시한다.

무선 디바이스는 송신을 위한 페이로드 (예를 들어, 페이로드 비트들의 세트) 를 선택할 수도 있고 페이로드의 사이즈에 기초하여 페이로드를 인코딩할 수도 있다. 예를 들어, 송신 디바이스는 페이로드 비트들, 패리티 비트들, 동결된 비트들, 또는 이들 비트들의 일부 조합을 포함하는 비트 벡터를 구성할 수도 있고, 선택된 페이로드 사이즈에 기초하여 비트 벡터에서 비트들 또는 비트들의 순서를 수정할 수도 있다. 디바이스는 비트 벡터 및 폴라 코드에 기초하여 코드워드를 생성할 수도 있고 코드워드를 수신 디바이스로 송신할 수도 있다.

수신 디바이스는 수신된 코드워드의 페이로드 사이즈를 알지 못할 수도 있고 정확한 페이로드 사이즈를 결정하기 위해 블라이드 디코딩 프로세스를 수행할 수도 있다. 예를 들어, 디바이스는 페이로드 사이즈 가설에 기초하여 코드워드에 대한 디코딩된 비트들을 디코딩을 수행하고 체크할 수도 있고, 여기서 디코딩 프로세스는 임의의 부정확한 페이로드 사이즈 가설에 대해 실패할 수도 있다. 페이로드 사이즈 가설이 패리티 체크들을 통과한 디코딩된 비트 벡터를 가져올 때, 디바이스는 가설된 페이로드 사이즈가 정확하다고 결정할 수도 있고, 송신된 정보를 결정하기 위해 디코딩된 비트 벡터로부터 페이로드 비트들을 파싱할 수도 있다.

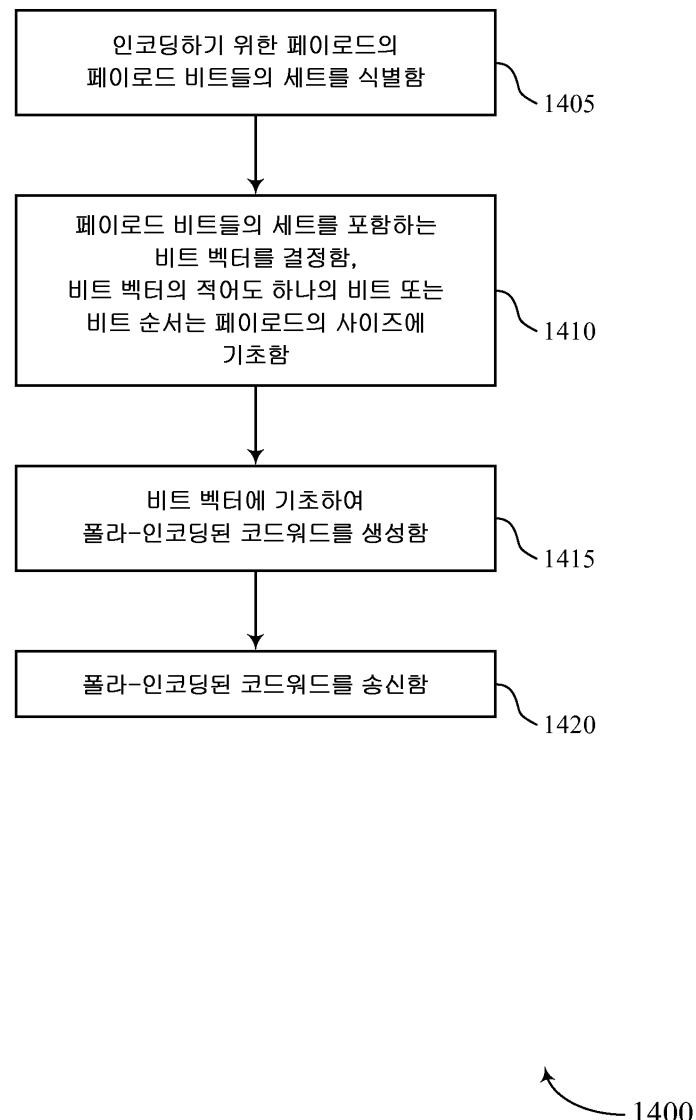

[0008] 무선 통신의 방법이 설명된다. 본 방법은, 인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하는 단계, 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하는 단계로서, 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 페이로드의 사이즈에 적어도 부분적으로 기초하는, 비트 벡터를 결정하는 단계, 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하는 단계, 및 폴라-인코딩된 코드워드를 송신하는 단

계를 포함할 수도 있다.

[0009] 무선 통신을 위한 장치가 설명된다. 본 장치는 인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하기 위한 수단, 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하기 위한 수단으로서, 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 페이로드의 사이즈에 적어도 부분적으로 기초하는, 비트 벡터를 결정하기 위한 수단, 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하기 위한 수단, 및 폴라-인코딩된 코드워드를 송신하기 위한 수단을 포함할 수도 있다.

[0010] 무선 통신을 위한 다른 장치가 설명된다. 본 장치는, 프로세서, 프로세서와 전자 통신하는 메모리, 및 메모리에 저장된 명령들을 포함할 수도 있다. 명령들은 프로세서로 하여금, 인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하게 하고, 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하게 하는 것으로서, 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 페이로드의 사이즈에 적어도 부분적으로 기초하는, 비트 벡터를 결정하게 하고, 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하게 하고, 그리고 폴라-인코딩된 코드워드를 송신하게 하도록 동작가능할 수도 있다.

[0011] 무선 통신을 위한 비일시적 컴퓨터 판독가능 매체가 설명된다. 비-일시적인 컴퓨터 판독가능 매체는 명령들을 포함할 수 있고 명령들은 프로세서로 하여금, 인코딩을 위한 페이로드의 복수의 페이로드 비트들을 식별하게 하고, 복수의 페이로드 비트들을 포함하는 비트 벡터를 결정하게 하는 것으로서, 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 페이로드의 사이즈에 적어도 부분적으로 기초하는, 비트 벡터를 결정하게 하고, 비트 벡터에 적어도 부분적으로 기초하여 폴라-인코딩된 코드워드를 생성하게 하고, 그리고 폴라-인코딩된 코드워드를 송신하게 하도록 동작가능하다.

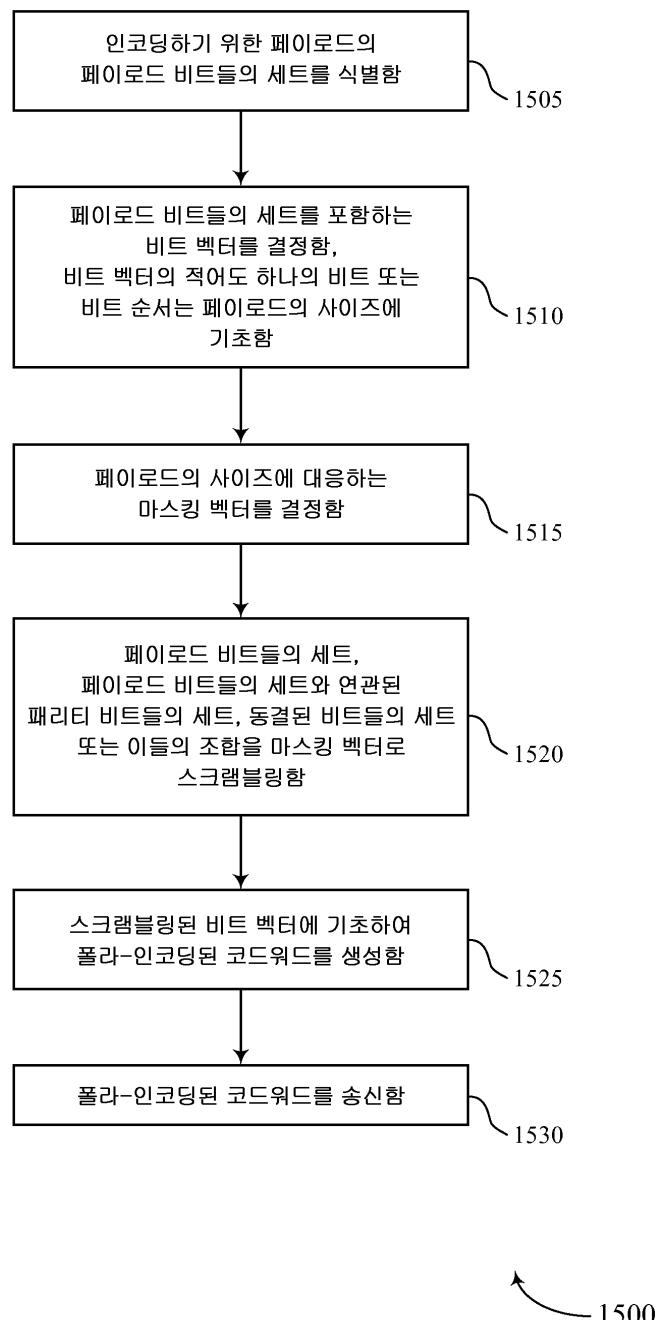

[0012] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들은, 페이로드의 사이즈에 대응하는 마스킹 벡터를 결정하기 위한 프로세스들, 피쳐들, 수단들 또는 명령들을 더 포함할 수도 있다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들은, 복수의 페이로드 비트들, 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하기 위한 프로세스들, 피쳐들, 수단들 또는 명령들을 더 포함할 수도 있다.

[0013] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 복수의 페이로드 비트들, 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 마스킹 벡터로 스크램블링하는 것은 배타적 or (XOR) 연산을 포함한다.

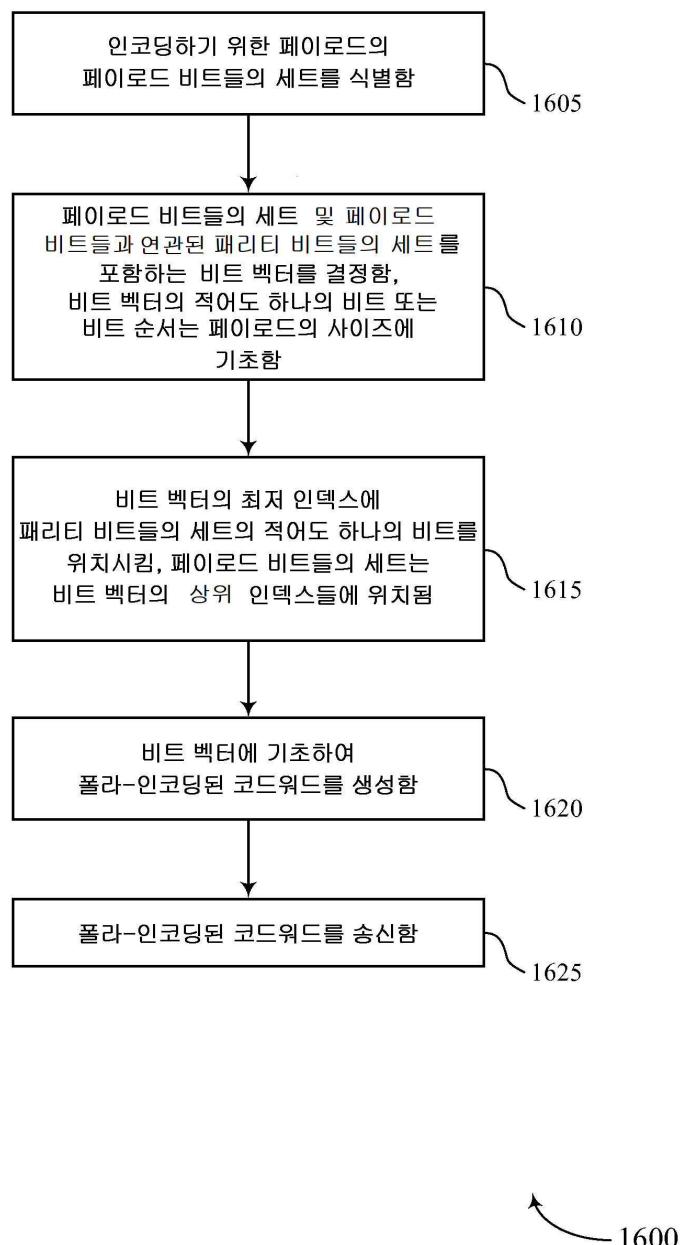

[0014] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 비트 벡터는 복수의 페이로드 비트들 및 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들을 포함한다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 비트 벡터를 결정하는 것은 비트 벡터의 최저 인덱스에서 복수의 패리티 비트들의 적어도 하나의 비트를 위치시키는 것을 포함하고, 복수의 페이로드 비트들은 비트 벡터의 상위 인덱스들에 위치될 수도 있다.

[0015] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 폴라-인코딩된 코드워드를 생성하는 것은 복수의 페이로드 비트들 및 복수의 패리티 비트들을 폴라 코드의 복수의 정보 비트 채널들에 배정하는 것을 포함하고, 복수의 패리티 비트들의 적어도 하나의 비트는 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정될 수도 있다.

[0016] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들은, 복수의 패리티 비트들을 생성하기 위해 복수의 페이로드 비트들에 패리티 함수를 적용하기 위한 프로세스들, 피쳐들, 수단들 또는 명령들을 더 포함할 수도 있다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 복수의 패리티 비트들은 복수의 시클릭 리턴던시 체크 (CRC) 비트들을 포함한다.

[0017] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 비트 벡터를 결정하는 것은 비트 벡터에 초기 비트를 첨부하는 것을 포함하며, 초기 비트는 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함한다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 초기 비트는 페이로드와 연관된 메시지 타입을 나타낸다.

[0018] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 비트 벡터를 결정하는 것은 비트 벡터의 초기 비트가 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하도록, 복수의 페이로드 비트들, 복수의 페이로드 비트들과 연관된 복수의 패리티 비트들, 복수의 동결된 비트들, 또는 이들의 조합을 배열하는 것

을 포함한다.

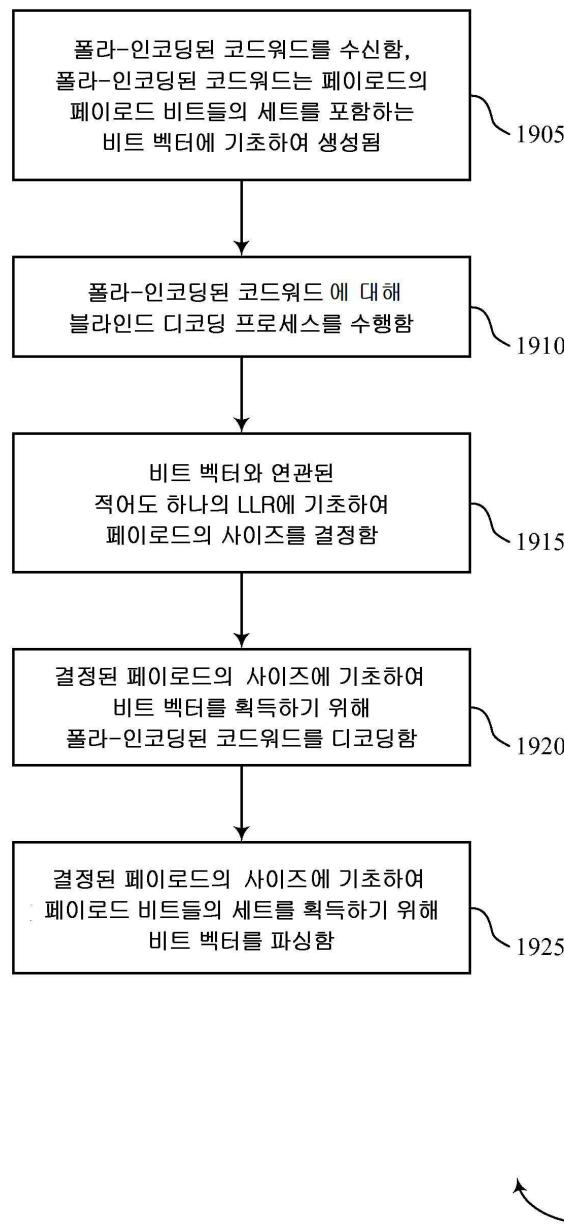

[0019] 무선 통신의 방법이 설명된다. 본 방법은, 폴라-인코딩된 코드워드를 수신하는 단계로서, 폴라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 폴라-인코딩된 코드워드를 수신하는 단계, 및 폴라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하는 단계를 포함할 수도 있고, 블라인드 디코딩 프로세스는: 비트 벡터와 연관된 적어도 하나의 로그-우도비 (LLR) 에 적어도 부분적으로 기초하여 페이로드의 사이즈를 결정하는 단계; 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 비트 벡터를 획득하기 위해 폴라-인코딩된 코드워드를 디코딩하는 단계; 및 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 복수의 페이로드 비트들을 획득하기 위해 비트 벡터를 파싱하는 단계를 포함한다.

[0020] 무선 통신을 위한 장치가 설명된다. 본 장치는 폴라-인코딩된 코드워드를 수신하기 위한 수단으로서, 폴라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 폴라-인코딩된 코드워드를 수신하기 위한 수단, 및 폴라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하기 위한 수단을 포함할 수도 있고, 블라인드 디코딩 프로세스는: 비트 벡터와 연관된 적어도 하나의 LLR 에 적어도 부분적으로 기초하여 페이로드의 사이즈를 결정하기 위한 수단; 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 비트 벡터를 획득하기 위해 폴라-인코딩된 코드워드를 디코딩하기 위한 수단; 및 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 복수의 페이로드 비트들을 획득하기 위해 비트 벡터를 파싱하기 위한 수단을 포함한다.

[0021] 무선 통신을 위한 다른 장치가 설명된다. 장치는, 프로세서, 프로세서와 전자 통신하는 메모리, 및 메모리에 저장된 명령들을 포함할 수도 있다. 명령들은 프로세서로 하여금, 폴라-인코딩된 코드워드를 수신하게 하는 것으로서, 폴라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 폴라-인코딩된 코드워드를 수신하게 하고, 그리고 폴라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하게 하도록 동작가능할 수 있고, 블라인드 디코딩 프로세스를 위한 명령들은 프로세서로 하여금: 비트 벡터와 연관된 적어도 하나의 LLR 에 적어도 부분적으로 기초하여 페이로드의 사이즈를 결정하게 하고; 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 비트 벡터를 획득하기 위해 폴라-인코딩된 코드워드를 디코딩하게 하고; 그리고 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 복수의 페이로드 비트들을 획득하기 위해 비트 벡터를 파싱하게 하도록 동작가능한 명령들을 더 포함한다.

[0022] 무선 통신을 위한 비일시적 컴퓨터 관독가능 매체가 설명된다. 비-일시적인 컴퓨터 관독가능 매체는 명령들을 포함할 수 있고 명령들은 프로세서로 하여금, 폴라-인코딩된 코드워드를 수신하게 하는 것으로서, 폴라-인코딩된 코드워드는 페이로드의 복수의 페이로드 비트들을 포함하는 비트 벡터에 적어도 부분적으로 기초하여 생성되는, 폴라-인코딩된 코드워드를 수신하게 하고, 그리고 폴라-인코딩된 코드워드에 대해 블라인드 디코딩 프로세스를 수행하게 하도록 동작가능할 수 있고, 블라인드 디코딩 프로세스를 위한 명령들은 프로세서로 하여금: 비트 벡터와 연관된 적어도 하나의 LLR 에 적어도 부분적으로 기초하여 페이로드의 사이즈를 결정하게 하고; 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 비트 벡터를 획득하기 위해 폴라-인코딩된 코드워드를 디코딩하게 하고; 그리고 결정된 페이로드의 사이즈에 적어도 부분적으로 기초하여 복수의 페이로드 비트들을 획득하기 위해 비트 벡터를 파싱하게 하도록 동작가능한 명령들을 더 포함한다.

[0023] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 관독가능 매체의 일부 예들에서, 페이로드의 사이즈를 결정하는 것은 적어도 하나의 LLR 에 대한 적어도 하나의 비트 결정에 대해 하나 이상의 디스크램블링 동작들을 수행하는 것을 포함하고, 각각의 디스크램블링 동작은 페이로드 사이즈에 대응하는 마스킹 벡터를 사용한다.

[0024] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 관독가능 매체의 일부 예들은, 복수의 디스크램블링된 패리티 비트들을 복수의 디스크램블링된 페이로드 비트들과 비교하는 것에 적어도 부분적으로 기초하여 성공적인 디스크램블링 동작을 식별하기 위한 프로세스들, 피처들, 수단들 또는 명령들을 더 포함할 수도 있다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 관독가능 매체의 일부 예들은, 페이로드의 사이즈를, 성공적인 디스크램블링 동작에 대한 마스킹 벡터에 대응하는 페이로드 사이즈로서 결정하기 위한 프로세스들, 피처들, 수단들 또는 명령들을 더 포함할 수도 있다.

[0025] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 관독가능 매체의 일부 예들에서, 디스크램블링 동작은 역 XOR 연산을 포함한다.

[0026] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 관독가능 매체의 일부 예들에서, 폴라-인코딩된 코드워드는 또

한, 복수의 패리티 비트들에 적어도 부분적으로 기초하여 생성될 수 있고, 복수의 페이로드 비트들 및 복수의 패리티 비트들은 복수의 정보 비트 채널들에 배정되고, 페이로드의 사이즈를 결정하는 것은 복수의 패리티 비트들을 사용하여 적어도 하나의 LLR에 대한 적어도 하나의 비트 결정을 체크하고, 각각의 패리티 체크에 대한 폴라-인코딩된 코드워드 내에서 복수의 패리티 비트들의 위치는 대응하는 페이로드 사이즈를 나타낸다.

[0027] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들은, 복수의 패리티 비트들 및 적어도 하나의 LLR에 대한 적어도 하나의 비트 결정에 적어도 부분적으로 기초하여 성공적인 패리티 체크를 식별하기 위한 프로세스들, 피쳐들, 수단들 또는 명령들을 더 포함할 수도 있다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들은, 성공적인 패리티 체크를 가져오는 복수의 패리티 비트들의 위치결정에 의해 표시되는 대응하는 페이로드 사이즈로서 페이로드의 사이즈를 결정하기 위한 프로세스들, 피쳐들, 수단들 또는 명령들을 더 포함할 수도 있다.

[0028] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 복수의 패리티 비트들의 적어도 하나의 비트는 복수의 정보 비트 채널들의 최소 신뢰성 채널에 배정될 수도 있다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 복수의 패리티 비트들은 복수의 CRC 비트들을 포함한다.

[0029] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 페이로드의 사이즈를 결정하는 것은 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR을 갖는 폴라-인코딩된 코드워드의 최소 신뢰성 비트 채널을 식별하는 것을 포함한다. 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들은, 식별된 최소의 신뢰성 비트 채널에 적어도 부분적으로 기초하여 페이로드의 사이즈를 결정하기 위한 프로세스들, 피쳐들, 수단들 또는 명령들을 더 포함할 수도 있다.

[0030] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 비트 백터를 파싱하는 것은 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 LLR에 대응하는 초기 비트를 제거하는 것을 포함한다.

[0031] 위에 설명된 방법, 장치, 및 비일시적인 컴퓨터 판독가능 매체의 일부 예들에서, 비트 백터를 파싱하는 것은 LLR이 디폴트 동결된 비트 값에 대한 반대 비트 값을 나타내는 것에 적어도 부분적으로 기초하여 비트 백터의 비트들을 재정렬하는 것을 포함한다.

### 도면의 간단한 설명

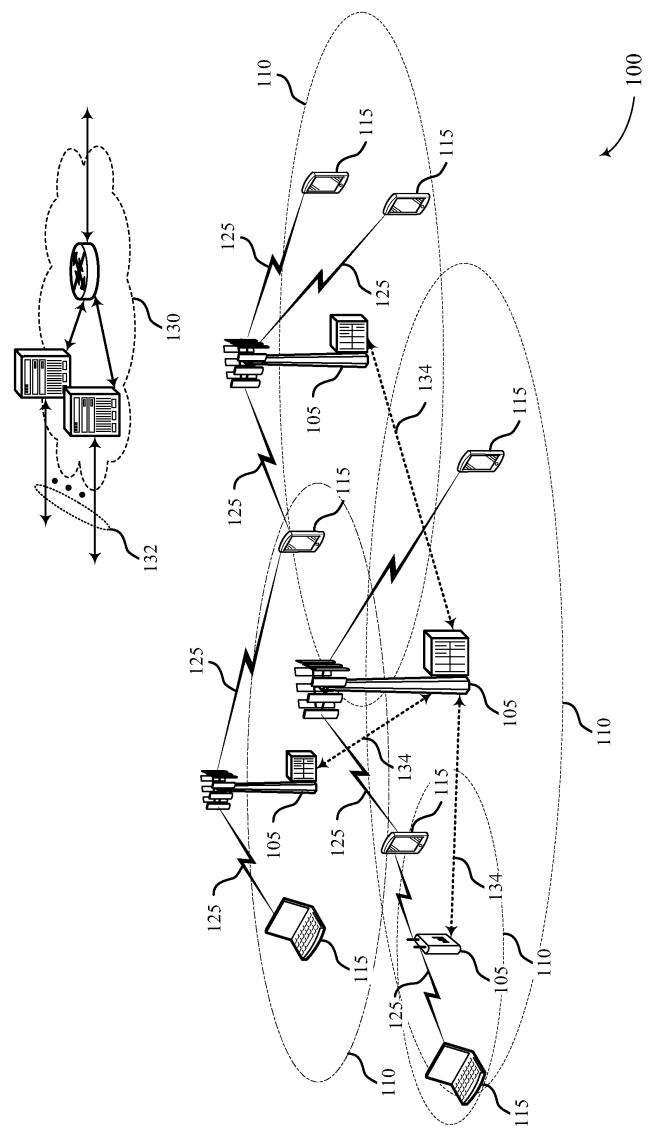

[0032] 도 1은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 무선 통신 시스템의 예를 나타낸다.

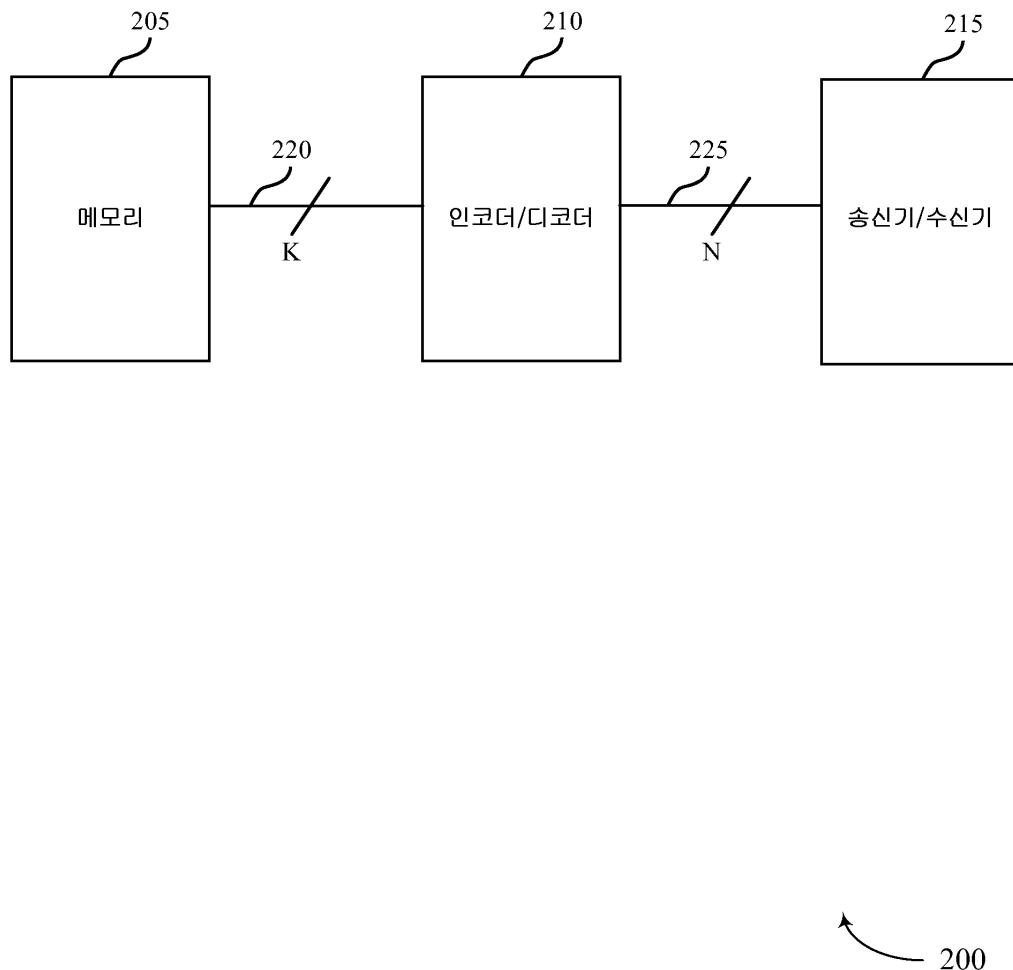

도 2는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 디바이스의 예를 나타낸다.

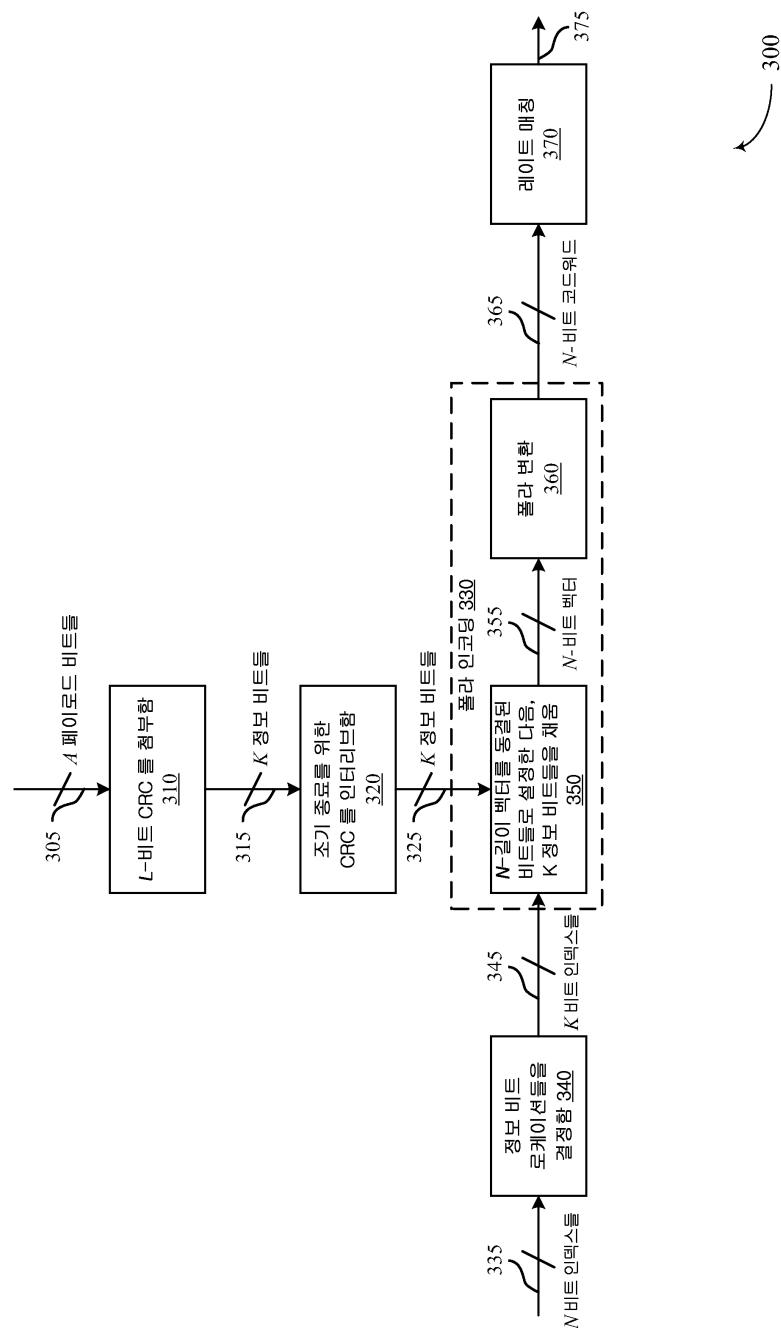

도 3은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 폴라-인코딩 프로세스의 예를 나타낸다.

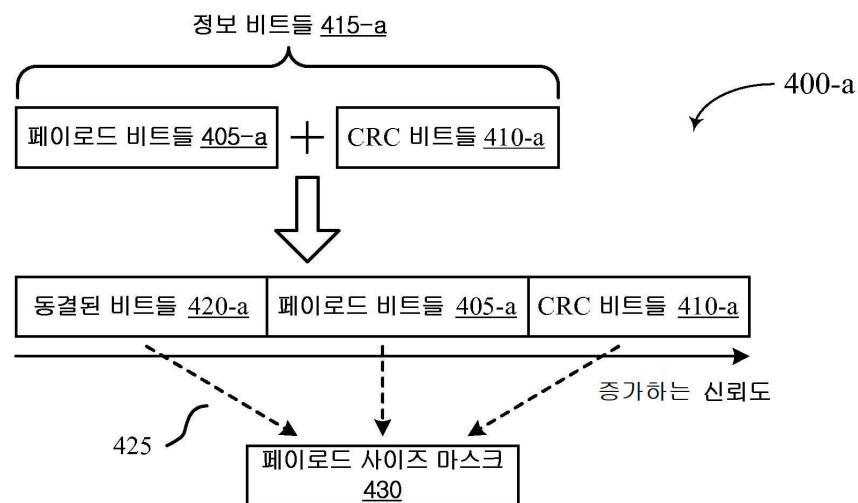

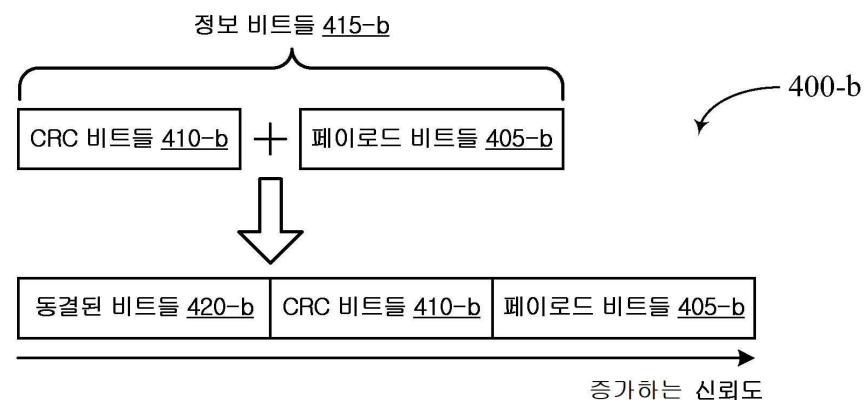

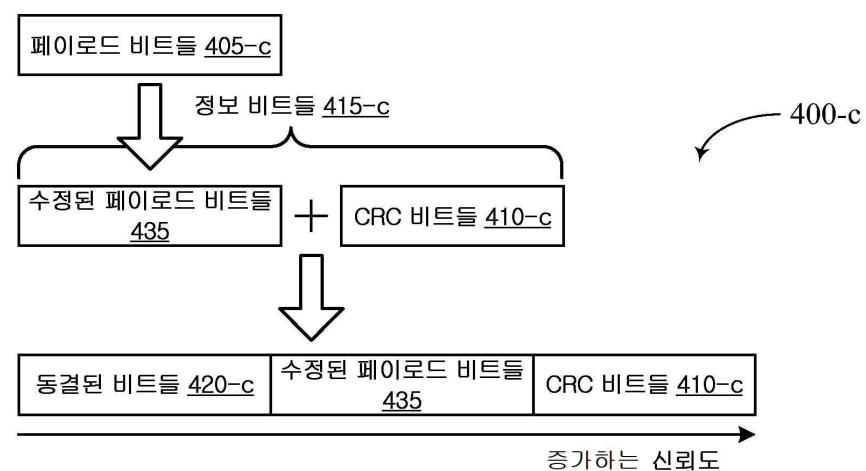

도 4a, 도 4b 및 도 4c는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 페이로드 사이즈 표시들의 예들을 나타낸다.

도 5는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 프로세스 플로우의 예를 나타낸다.

도 6 및 도 7은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 디바이스의 블록 다이어그램을 나타낸다.

도 8은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 인코더 폴라 코딩 모듈의 블록 다이어그램을 나타낸다.

도 9는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 디바이스를 포함하는 시스템의 블록 다이어그램을 나타낸다.

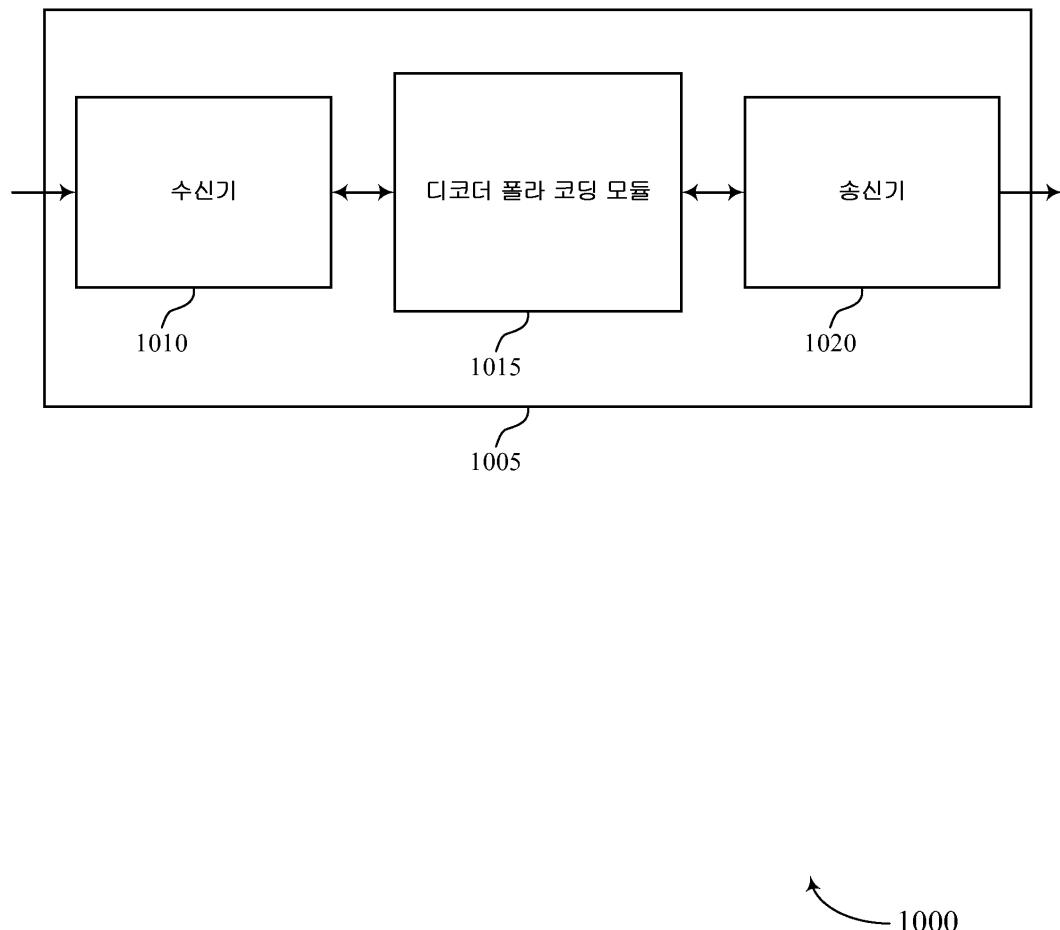

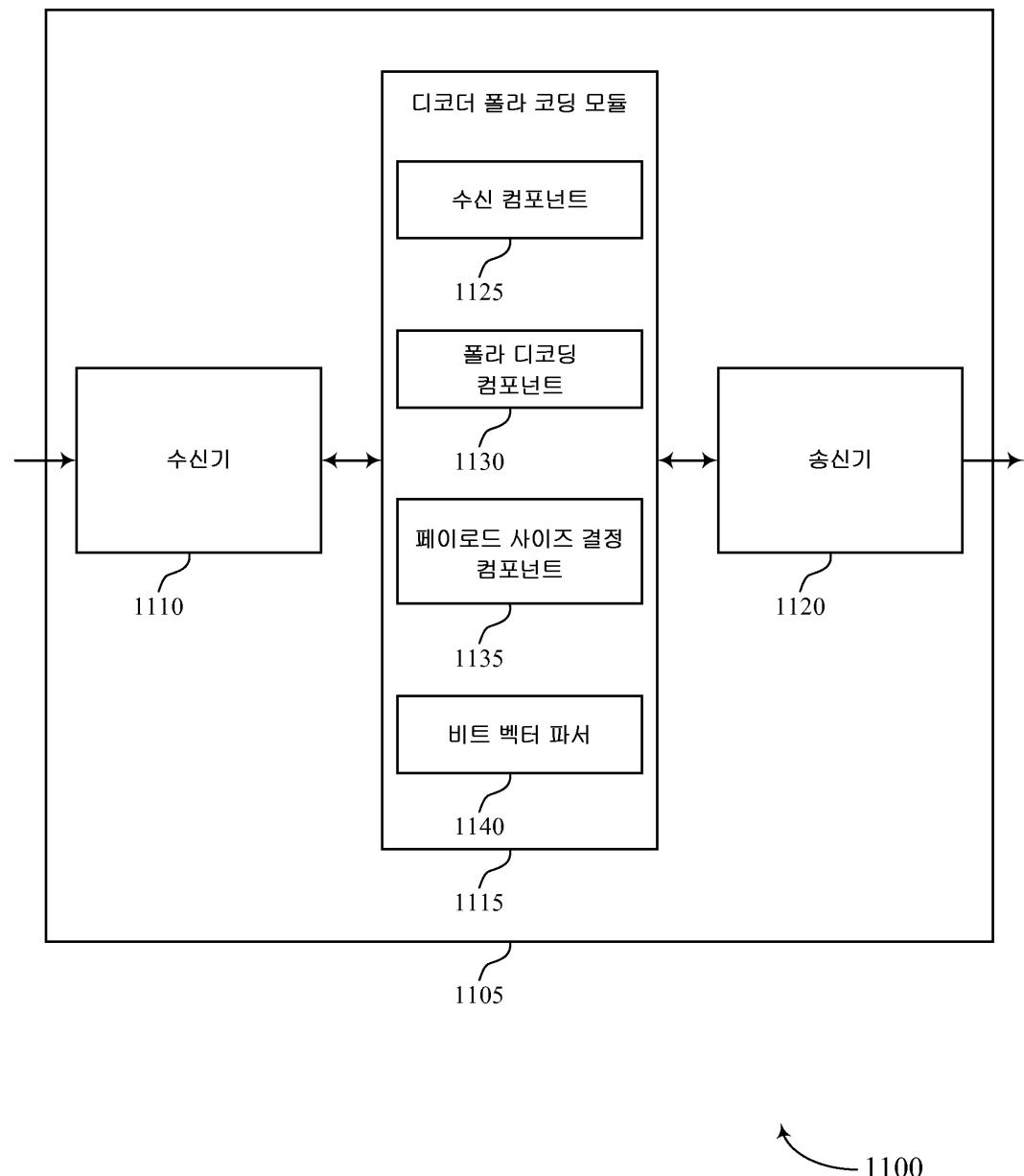

도 10 및 도 11은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 무선 디바이스의 블록 다이어그램을 나타낸다.

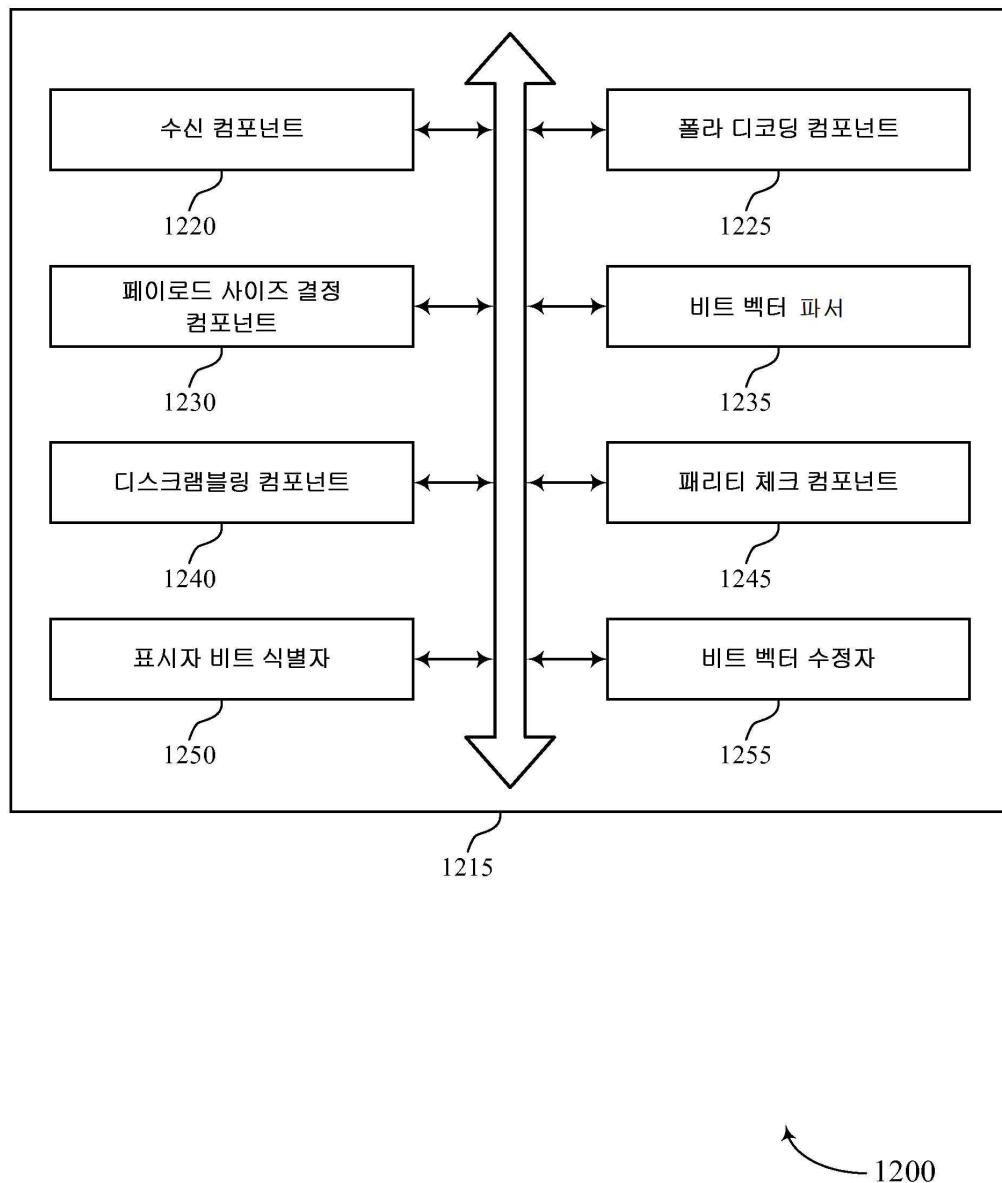

도 12는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원

하는 디코더 폴라 코딩 모듈의 블록 다이어그램의 예를 나타낸다.

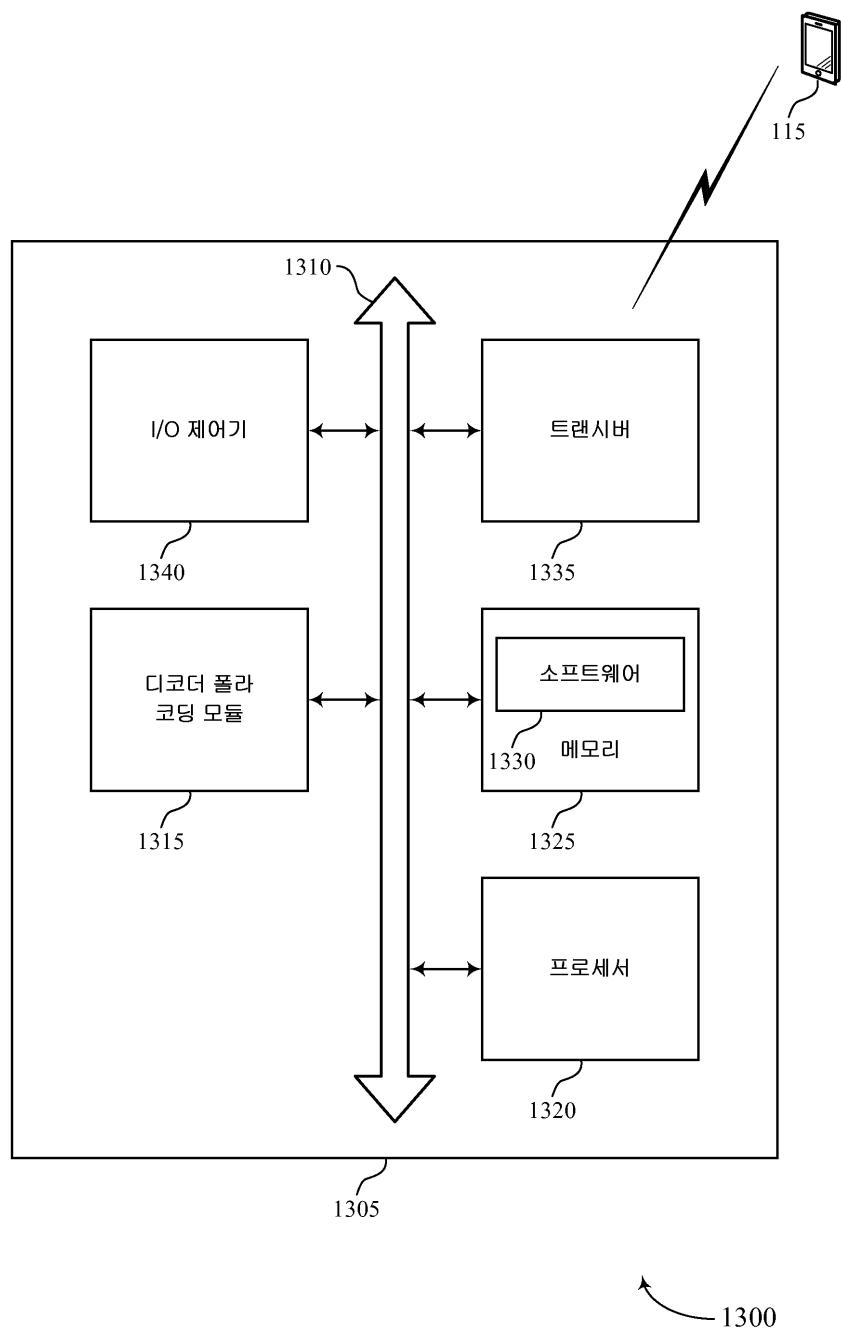

도 13 은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 디코더를 포함하는 시스템의 블록 다이어그램을 나타낸다.

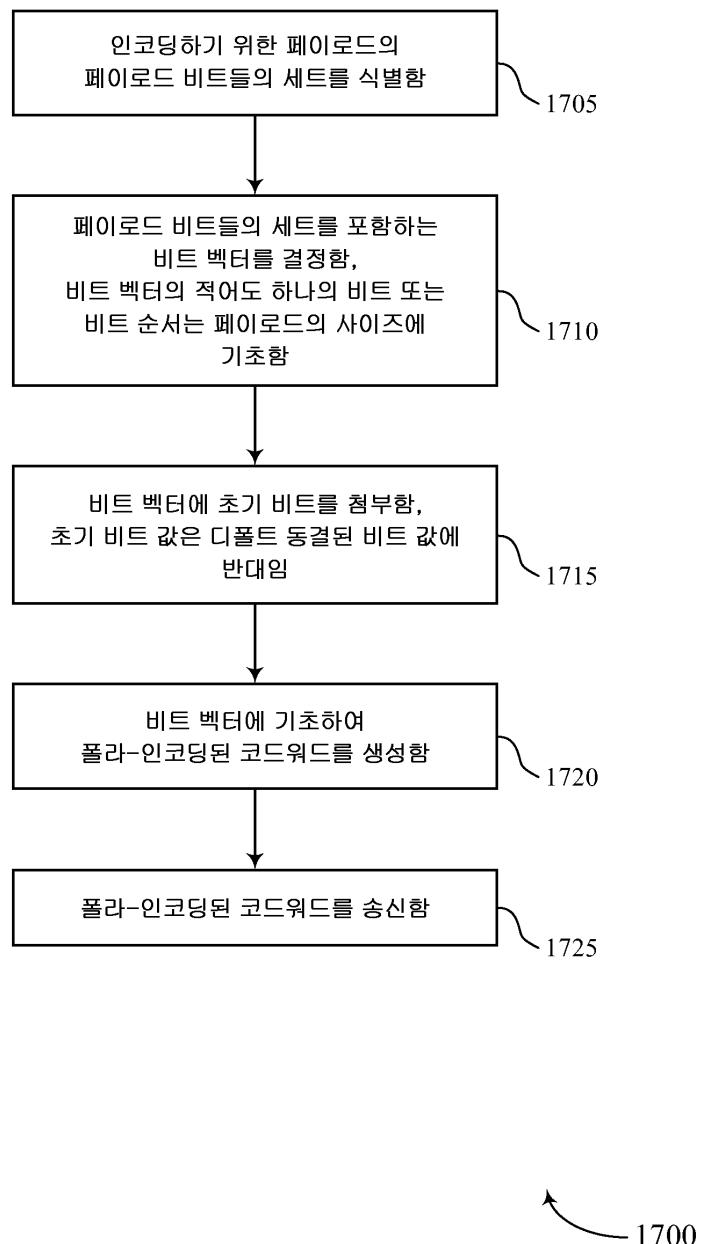

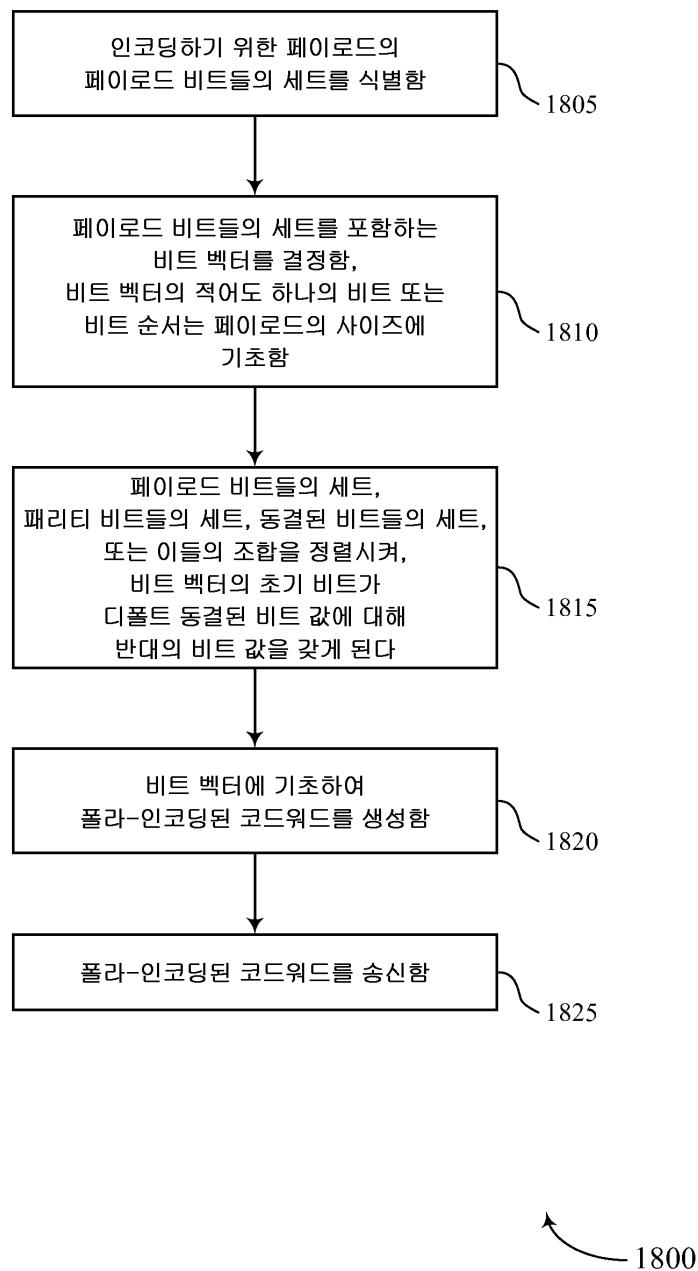

도 14 내지 도 19 는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들에 대한 방법들을 예시하는 플로우차트들을 나타낸다.

### 발명을 실시하기 위한 구체적인 내용

[0033]

일부 무선 통신 시스템들에서, 무선 디바이스들 (예를 들어, 기지국들 또는 사용자 장비들 (UE들)) 은 송신물들을 인코딩 및 디코딩하기 위하여, 폴라 코드들을 구현할 수도 있다. 일부 경우들에, 송신 디바이스는 송신을 위한 페이로드를 선택할 수도 있다. 페이로드의 사이즈는 예를 들어, 가능한 페이로드 사이즈들의 리스트로부터 구성가능할 수도 있다. 일부 경우들에, 송신 디바이스는 선택된 페이로드 사이즈를 코드워드를 디코딩하는 디바이스에 나타내는 하나 이상의 기법들을 구현할 수도 있다. 이를 기법들은 코드워드를 블라인드 디코딩하는 디바이스가 인코딩된 페이로드를 정확하게 결정할 수도 있도록, 임의의 페이로드에 대한 고유의 코드워드를 가져올 수 있다. 예를 들어, 수신 디바이스는 가능한 페이로드 사이즈들의 어느 것을 사용하여 생성되는 코드워드들을 모니터링할 수도 있다. 수신 디바이스는 코드워드의 페이로드 사이즈를 결정하기 위하여 송신 디바이스에 의해 활용된 기법들에 대응하는 하나 이상의 기법들을 구현할 수도 있다.

[0034]

이들 기법들을 수행하기 위해, 송신 디바이스는 인코딩하기 위한 정보 비트들의 세트를 결정할 수도 있고, 여기서 정보 비트들은 페이로드 비트들 및 페이로드 비트들에 기초하여 생성되는 패리티 비트들을 포함할 수도 있다. 이를 정보 비트들은 비트 벡터로 조직화될 수도 있다. 송신 디바이스는 페이로드의 사이즈 (예를 들어, 페이로드 비트들의 수)에 기초하여 비트 벡터를 수정할 수도 있다. 제 1 기법에서, 송신 디바이스는 (예를 들어, 식에 기초하여 그리고 메모리에서의 테이블로부터) 페이로드 사이즈에 대응하는 마스킹 벡터를 결정할 수도 있다. 디바이스는 마스킹 벡터를 사용하여 비트 벡터의 하나 이상의 비트들을 마스킹 또는 스크램블링할 수도 있다. 제 2 기법에서, 디바이스는 페이로드 비트들보다 더 낮은 비트 인덱스들에 비트 벡터에서의 패리티 비트들의 적어도 일부분을 위치시킬 수도 있다. 제 3 기법에서, 디바이스는 비트 벡터의 제 1 비트 인덱스가 디폴트 동결된 비트 값의 것과는 상이한 비트 값을 포함함 (예를 들어, 동결된 비트 값이 0 의 디폴트 값을 갖는다면, 제 1 비트 인덱스는 1 의 비트 값을 가질 것임) 을 보장할 수도 있다. 예를 들어, 디바이스는 제 1 비트가 1 비트이도록, 비트 벡터의 제 1 비트 인덱스에서 추가적인 비트를 삽입할 수도 있거나 또는 페이로드 비트들을 배열할 수도 있다. 일부 경우들에, 위에 설명된 비트 벡터는 정보 비트 벡터로서 지칭될 수도 있고, 더 많은 비트 벡터의 일부분일 수도 있다. 이 더 큰 비트 벡터는 추가적으로, 정보 비트 벡터보다 더 낮은 비트 인덱스들에 동결된 비트들의 세트를 포함할 수도 있다. 송신 디바이스는 대응하는 비트 채널들에, 비트 벡터의 비트들을 배정할 수도 있고 (예를 들어, 증가하는 채널 신뢰성 순서로 비트 채널에 대한 증가하는 인덱스 순서에서 비트 벡터의 각각의 비트를 배정하는 것), 배정된 비트 채널들 및 폴라 코드를 사용하여 코드워드를 생성할 수도 있다. 디바이스는 생성된 코드워드를 수신 디바이스로 송신할 수도 있다.

[0035]

수신 디바이스는 블라인드 디코딩 프로세스를 사용하여 코드워드를 디코딩할 수도 있다. 예를 들어, 수신 디바이스는 페이로드 사이즈를 위한 하나 이상의 가설들을 사용하여 수신된 신호를 디코딩할 수도 있다. 위에 설명된 기법들 각각에 대해, 디코딩 프로세스는 수신 디바이스가 부정확한 페이로드 사이즈 가설을 가정하면 실패할 수도 있다. 예를 들어, 제 1 의 2 가지 기법들에서, 패리티 체크 또는 시클릭 리던던시 체크 (CRC) 는 코드워드가 부정확한 마스킹 벡터 또는 CRC 에 대한 부정확한 시작 포지션을 사용하여 디코딩되면 실패할 수도 있다. 제 3 기법에서, 제 1 정보 비트가 디폴트 동결된 비트 값과는 상이한 값과 제 1 비트일 때, 수신 디바이스는 비트 벡터 내에서 이 제 1 정보 비트의 포지션을 결정할 수도 있다. 이를 기법들의 하나 이상을 사용하여, 수신 디바이스는 상이한 페이로드 사이즈들의 코드워드들을 성공적으로 디코딩할 수도 있다.

[0036]

본 개시의 양태들은 처음에, 무선 통신 시스템의 문맥에서 설명된다. 추가적인 양태들은 폴라 코딩 디바이스, 인코딩 프로세스, 페이로드 사이즈 표시들 및 프로세스 플로우에 대해 설명된다. 본 개시의 양태들은 추가로, 상이한 페이로드 사이즈들의 폴라 코딩 기법들과 관련되는 장치 다이어그램들, 시스템 다이어그램들, 및 플로우차트들에 의해 도시되고 이들을 참조하여 설명된다.

[0037]

도 1 은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 무선 통신 시스템 (100) 의 예를 나타낸다. 무선 통신 시스템 (100) 은 기지국들 (105), UE들 (115), 및 코어 네트워크 (130) 를 포함한다. 일부 예들에서, 무선 통신 시스템 (100) 은 롱 텀 에볼루션 (LTE) 네

트워크, LTE-어드밴스드 (LTE-A) 네트워크, 또는 뉴 라디오 (NR) 네트워크일 수도 있다. 일부 경우들에서, 무선 통신 시스템 (100) 은 향상된 브로드밴드 통신들, 초-신뢰가능 (예를 들어, 미션 크리티컬) 통신들, 저 레이턴시 통신들, 또는 저 비용 및 저 복잡도 디바이스들과의 통신들을 지원할 수도 있다. 일부 경우들에서, 무선 통신 시스템들 (100) 의 무선 디바이스들 (예를 들어, 기지국 (105) 및 UE들 (115)) 은 폴라 코딩 기법들을 활용할 수도 있다.

[0038] 기지국들 (105) 은 하나 이상의 기지국 안테나들을 통해 UE들 (115) 과 무선으로 통신할 수도 있다. 기지국들 (105) 은 베이스 트랜시버 스테이션, 무선 기지국, 액세스 포인트, 무선 트랜시버, NodeB, eNodeB (eNB), 차세대 노드 B 또는 기가-nodeB (둘 중 어느 하나가 gNB 로 지칭될 수도 있음), 홈 NodeB, 홈 eNodeB, 또는 일부 다른 적합한 용어를 포함할 수도 있거나 또는 이들로 당업자들에 의해 지칭될 수도 있다. 무선 통신 시스템 (100) 은 상이한 타입들의 기지국들 (105) (예를 들어, 매크로 또는 소형 셀 기지국들) 을 포함할 수도 있다.

본원에서 설명된 UE들 (115) 은 매크로 eNB들, 소형 셀 eNB들, gNB들, 중계기 기지국들 등을 포함한 다양한 타입들의 기지국들 (105) 및 네트워크 장비와 통신 가능할 수도 있다.

[0039] 각각의 기지국 (105) 은, 다양한 UE들 (115) 과의 통신들이 지원되는 특정한 지리적 커버리지 영역 (110) 과 연관될 수도 있다. 각각의 기지국 (105) 은 통신 링크들 (125) 을 통해 개별의 지리적 커버리지 영역 (110) 에 대한 통신 커버리지를 제공할 수도 있고, 기지국 (105) 과 UE (115) 사이의 통신 링크들 (125) 은 하나 이상의 캐리어들을 활용할 수도 있다. 무선 통신 시스템 (100) 에 도시된 통신 링크들 (125) 은 UE (115) 로부터 기지국 (105) 으로의 업링크 송신들, 또는 기지국 (105) 으로부터 UE (115) 로의 다운링크 송신들을 포함할 수도 있다. 다운링크 송신들은 또한 순방향 링크 송신들로 불릴 수도 있는 한편, 업링크 송신들은 또한 역 방향 링크 송신들로 불릴 수도 있다.

[0040] 기지국 (105) 에 대한 지리적 커버리지 영역 (110) 은 지리적 커버리지 영역 (110) 의 일 부분만을 구성하는 섹터들로 분할될 수도 있고, 각각의 섹터는 셀과 연관될 수도 있다. 예를 들어, 각각의 기지국 (105) 은 매크로 셀, 소형 셀, 핫 스팟, 또는 다른 타입들의 셀들, 또는 이들의 다양한 조합들에 대한 통신 커버리지를 제공할 수도 있다. 일부 예들에서, 기지국 (105) 은 이동가능하며 따라서, 이동하는 지리적 커버리지 영역 (110) 에 대해 통신 커버리지를 제공할 수 있다. 일부 예들에서, 상이한 기술들과 연관되는 상이한 지리적 커버리지 영역들 (110) 은 오버랩할 수도 있고 상이한 기술들과 연관된 오버랩하는 지리적 커버리지 영역들 (110) 은 동일한 기지국 (105) 에 의해 또는 상이한 기지국들 (105) 에 의해 지원될 수도 있다. 무선 통신 시스템 (100) 은 예를 들어, 이종의 LTE/LTE-A 또는 NR 네트워크를 포함할 수도 있고, 여기서 상이한 유형들의 기지국들 (105) 은 여러 지리적 커버리지 영역들 (110) 에 커버리지를 제공한다.

[0041] 용어 "셀"은 (예를 들어, 캐리어를 통하여) 기지국 (105) 과의 통신을 위하여 사용되는 논리적 통신 엔티티를 지칭할 수도 있고 동일 또는 상이한 캐리어를 통하여 동작하는 이웃하는 셀들을 구별하기 위한 식별자 (예를 들어, 물리 셀 식별자 (PCID), 가상 셀 식별자 (VCID)) 와 연관될 수도 있다. 일부 예들에서, 캐리어는 다수의 셀들을 지원할 수도 있고 상이한 셀들은 상이한 유형들의 디바이스들에 대하여 액세스를 제공할 수도 있는 상이한 프로토콜 유형들 (예를 들어, 머신-타입 통신 (MTC), 협대역 사물 인터넷 (NB-IoT), 강화된 모바일 브로드밴드 (eMBB), 또는 그 외의 것) 에 따라 구성될 수도 있다. 일부 경우들에, 용어 "셀"은 논리적 엔티티가 동작하는 지리적 커버리지 영역 (110) 의 일부분 (예를 들어, 섹터) 을 지칭할 수도 있다.

[0042] UE들 (115) 은 무선 통신 시스템 (100) 전체에서 분산될 수도 있고, 각각의 UE (115) 는 고정식이거나 이동식일 수도 있다. UE (115) 는 또한 모바일 디바이스, 무선 디바이스, 원격 디바이스, 핸드헬드 디바이스, 또는 가입자 디바이스, 또는 일부 다른 적절한 용어로 지칭될 수도 있고 "디바이스"는 또한 유닛, 스테이션, 단말 또는 클라이언트로서 지칭될 수도 있다. UE (115) 는 또한 퍼스널 전자 디바이스, 이를 테면, 셀룰라 폰, 개인 휴대정보 단말기 (PDA), 테블릿 컴퓨터, 랩탑 컴퓨터, 또는 퍼스널 컴퓨터일 수도 있다. 일부 예들에서, UE (115) 는 또한 무선 로컬 루프 (WLL) 스테이션, 사물 인터넷 (IoT) 디바이스, 만물 인터넷 (IoE) 디바이스, 또는 MTC 디바이스 등을 지칭할 수도 있으며, 이는 여러 제품들, 가전제품, 차량들, 계측기 등에서 구현될 수도 있다.

[0043] MTC 또는 IoT 디바이스들과 같은 일부 UE들 (115) 은 저비용 또는 저복잡성 디바이스일 수 있고, 머신들 간의 자동화된 통신을 (예를 들어, M2M (Machine-to-Machine) 통신을 통하여) 제공할 수 있다. M2M 통신 또는 MTC 는 인간의 개입 없이, 디바이스들이 서로 또는 기지국 (105) 과 통신하게 허용하는 데이터 통신 기술들을 지칭할 수도 있다. 일부 예들에서, M2M 통신 또는 MTC 는 정보를 측정 또는 캡처하기 위한 센서들 또는 계량기들을 통합하고, 정보를 이용할 수 있는 중앙 서버 또는 애플리케이션 프로그램에 그 정보를 중계하거나 또

는 프로그램 또는 애플리케이션과 상호작용하는 인간들에게 정보를 제시하는 디바이스들로부터의 통신들을 포함할 수도 있다. 일부 UE들 (115)은 정보를 수집하거나 또는 머신들의 자동화된 거동을 가능하게 하도록 설계될 수도 있다. MTC 디바이스들에 대한 애플리케이션들의 예들은 스마트 미터링 (smart metering), 재고 모니터링, 수위 모니터링, 장비 모니터링, 건강관리 모니터링, 야생동물 모니터링, 기상 및 지질학적 이벤트 모니터링, 차량군 관리 및 추적, 원격 보안 감지, 물리적 액세스 제어, 및 트랜잭션-기반 비즈니스 충전을 포함한다.

[0044] 일부 UE들 (115)은 전력 소모를 감소시키는 동작 모드들, 이를 테면, 하프-듀플렉스 통신 (예를 들어, 동시적인 송수신이 아닌 송신 또는 수신을 통하여 1-웨이 통신을 지원하는 모드)을 채택하도록 구성될 수도 있다.

일부 예들에서, 하프 듀플렉스 통신들은 감소된 피크 레이트에서 수행될 수도 있다. UE들 (115)에 대한 다른 전력 보존 기술들은 액티브 통신에 참여하지 않을 때 전력 절감 "딥 슬립" 모드에 진입하는 것, 또는 (예를 들어, 협대역 통신들에 따라) 제한된 대역폭 상에서 동작하는 것을 포함한다. 일부 경우들에, UE들 (115)은 중요 기능들 (예를 들어, 미션 크리티컬 기능들)을 지원하도록 설계될 수도 있으며, 무선 통신 시스템 (100)은 초신뢰가능 통신에 이들 기능들을 제공하도록 구성될 수도 있다.

[0045] 일부 경우들에, UE (115)는 또한 다른 UE들 (115)과 (예를 들어, 퍼어 투 퍼어 (P2P) 또는 디바이스 투 디바이스 (D2D) 프로토콜을 사용하여) 직접 통신가능할 수도 있다. D2D 통신을 활용하는 UE들 (115)의 그룹 중 하나 이상은 기지국 (105)의 지리적 커버리지 영역 (110) 내에 있을 수도 있다. 그러한 그룹에서의 다른 UE들 (115)은 기지국 (105)의 지리적 커버리지 영역 (110) 밖에 있을 수도 있거나 또는 그렇지 않으면 기지국 (105)으로부터의 송신물들을 수신할 수 없을 수도 있다. 일부 경우들에서, D2D 통신을 통해 통신하는 UE들 (115)의 그룹은 각각의 UE (115)가 그룹에서의 모든 다른 UE (115)에 송신하는 일 대 다 (1 : M) 시스템을 이용할 수도 있다. 일부 경우들에, 기지국 (105)은 D2D 통신들에 대한 리소스들의 스케줄링을 용이하게 한다. 다른 경우들에서, D2D 통신은 기지국 (105)의 관여없이 UE들 (115) 사이에서 수행된다.

[0046] 기지국들 (105)은 코어 네트워크 (130)와 그리고 서로 통신할 수도 있다. 예를 들어, 기지국들 (105)은 백홀 링크들 (132)을 통해 (예를 들어, S1 또는 다른 인터페이스를 통해) 코어 네트워크 (130)와 인터페이싱 할 수도 있다. 기지국들 (105)은 직접 (예를 들어, 직접 기지국들 (105) 간에) 또는 간접적으로 (예를 들어, 코어 네트워크 (130)를 통해) 백홀 링크들 (134) 위로 (예를 들어, X2 또는 다른 인터페이스를 통해) 서로 통신할 수도 있다.

[0047] 코어 네트워크 (130)는 사용자 인증, 액세스 인가, 추적, 인터넷 프로토콜 (IP) 접속성, 및 다른 액세스, 라우팅, 또는 이동성 기능들을 제공할 수도 있다. 코어 네트워크 (130)는, 적어도 하나의 이동성 관리 엔티티 (MME), 적어도 하나의 서빙 게이트웨이 (S-GW), 및 적어도 하나의 패킷 데이터 네트워크 (PDN) 게이트웨이 (P-GW)를 포함할 수도 있는 진화된 패킷 코어 (EPC) 일 수도 있다. MME는 EPC 와 연관된 기지국들 (105)에 의해 서빙된 UE들 (115)에 대한 이동성, 인증, 및 베어러 관리와 같은 비-액세스 계층 (예를 들어, 제어 평면) 기능들을 관리할 수도 있다. 사용자 IP 패킷들은 S-GW를 통해 전송될 수도 있고, S-GW 그 자체는 P-GW에 접속될 수도 있다. P-GW는 IP 어드레스 할당 뿐만 아니라 다른 기능들을 제공할 수도 있다. P-GW는 네트워크 오퍼레이터들 IP 서비스들에 접속될 수도 있다. 오퍼레이터들 IP 서비스들은 인터넷, 인트라넷(들), IP 멀티미디어 서브시스템 (IMS), 및 패킷 교환 (PS) 스트리밍 서비스로의 액세스를 포함할 수도 있다.

[0048] 기지국 (105)과 같은 네트워크 디바이스들 중 적어도 일부는 액세스 노드 제어기 (ANC)의 일례일 수도 있는 액세스 네트워크 엔티티와 같은 서브컴포넌트들을 포함할 수도 있다. 각각의 액세스 네트워크 엔티티는 라디오 헤드, 스마트 라디오 헤드, 또는 송/수신 포인트 (TRP)로서 지정될 수도 있는 다수의 다른 액세스 네트워크 송신 엔티티들을 통해 UE들 (115)과 통신할 수도 있다. 일부 구성들에서, 각각의 액세스 네트워크 엔티티 또는 기지국 (105)의 다양한 기능들은 다양한 네트워크 디바이스들 (예를 들어, 무선 헤드들 및 액세스 네트워크 제어기들)에 걸쳐 분배되거나 또는 단일의 네트워크 디바이스 (예를 들어, 기지국 (105))에 통합될 수도 있다.

[0049] 무선 통신 시스템 (100)은 통상적으로 300 MHz 내지 300 GHz의 범위에서 하나 이상의 주파수 대역들을 사용하여 동작할 수도 있다. 일반적으로 300 MHz 내지 3 GHz의 영역은 초고주파수 (UHF) 영역 또는 데시미터 대역으로서 알려져 있는데 이는 파장들이 대략 1 데시미터에서부터 1 미터까지의 길이의 범위이기 때문이다. UHF 파들은 빌딩 및 환경적 특징들에 의해 차단되거나 방향이 변경될 수도 있다. 그러나, 파들은 매크로 셀들이 실내에 위치된 UE들 (115)에 서비스를 제공하기에 충분한 구조물들을 관통할 수도 있다. UHF파들의

송신은, 300 MHz 미만의 스펙트럼의 고주파수 (HF) 또는 초고주파수 (VHF) 부분의 더 작은 주파수들 및 더 긴 파들을 사용한 송신에 비교하여 더 작은 안테나들 및 더 짧은 범위 (예를 들어, 100 km 미만) 와 연관될 수도 있다.

[0050] 무선 통신 시스템 (100) 은 또한 센티미터 대역으로 알려진 3 GHz 내지 30 GHz 의 주파수 대역을 사용하여 초고주파수 (SHF) 영역에서 동작할 수도 있다. SHF 영역은 대역들, 이를 테면, 5 GHz 산업적, 과학적, 의료적 (ISM) 대역들을 포함하며, 이는 다른 사용자들로부터 간섭을 허용할 수 있는 디바이스들에 의해 기회적으로 사용될 수도 있다.

[0051] 무선 통신 시스템 (100) 은 또한 밀리미터 대역으로서 잘 알려진, 스펙트럼의 극초고 주파수 (EHF) 영역 (예를 들어, 30 GHz 내지 300 GHz) 에서 동작할 수도 있다. 일부 예들에서, 무선 통신 시스템 (100) 은 UE들 (115) 과 기지국들 (105) 사이의 밀리미터파 (mmW) 통신들을 지원할 수도 있고, 개별적인 디바이스들의 EHF 안테나들은 UHF 안테나들보다 훨씬 더 작게 그리고 더 가깝게 이격될 수도 있다. 일부 경우들에, 이는 UE (115) 내의 안테나 어레이들의 사용을 용이하게 할 수도 있다. 그러나, EHF 송신물들의 전파는 SHF 또는 UHF 송신물들보다 훨씬 더 큰 대기 감쇠 및 더 짧은 범위를 겪게 될 수도 있다. 본원에 설명된 기법들은 하나 이상의 상이한 주파수 영역들을 사용하는 송신들에 걸쳐 채택될 수도 있고 이들 주파수 영역들을 따르는 대역들의 지정된 사용은 나라별로 또는 규제 요체별로 상이할 수도 있다.

[0052] 일부 경우들에, 무선 통신 시스템 (100) 은 허가 및 비허가 무선 주파수 스펙트럼 대역들 모두를 이용할 수 있다. 예를 들어, 무선 통신 시스템 (100) 은 5 GHz ISM 대역과 같은 비허가 대역에서 LAA (License Assisted Access), LTE-U (LTE-Unlicensed) 무선 액세스 기술 또는 NR 기술을 채택할 수도 있다. 비허가 무선 주파수 스펙트럼 대역들에서 동작할 때, 기지국들 (105) 및 UE들 (115) 과 같은 무선 디바이스들은 데이터를 송신하기 전에 주파수 채널이 클리어임을 보장하기 위해 LBT (listen-before-talk) 절차들을 채용할 수도 있다. 일부 경우들에, 비허가 대역들에서의 동작들은 비허가 대역에서 동작하는 CA들과 연관되어 CA 구성 (예를 들어, LAA) 에 기초할 수도 있다. 비허가 스펙트럼에서의 동작들은 다운링크 송신들, 업링크 송신들, 피어 투 피어 송신들 또는 이들의 조합을 포함할 수 있다. 비허가 스펙트럼에서의 듀플렉싱은 주파수 분할 듀플렉싱 (FDD), 시분할 듀플렉싱 (TDD) 또는 이들의 조합에 기초할 수 있다.

[0053] 일부 예들에서, 기지국 (105) 또는 UE (115) 에는 다수의 안테나들이 설치될 수도 있으며, 이는 송신 다이버시티, 수신 다이버시티, 다중-입력 다중-출력 (MIMO) 통신들 또는 빔포밍과 같은 기술을 채택하는데 사용될 수도 있다. 예를 들어, 무선 통신 시스템은 송신 디바이스 (100) (예를 들어, 기지국 (105)) 와 수신 디바이스 (예를 들어, UE (115)) 사이에 송신 방식을 사용할 수도 있고, 여기서, 송신 디바이스는 다수의 안테나들을 구비하고 수신 디바이스들은 하나 이상의 안테나들을 구비한다. MIMO 통신은 상이한 공간 계층들을 통해 다수의 신호들을 송신 또는 수신함으로써 스펙트럼 효율을 증가시키기 위해 다수의 경로 신호 전파를 채용할 수도 있고, 이는 공간적 멀티플렉싱으로서 지칭될 수도 있다. 다수의 신호들은, 예를 들어, 상이한 안테나들 또는 안테나들의 상이한 조합들을 통해 송신 디바이스에 의해 송신될 수도 있다. 마찬가지로 다수의 신호들은, 상이한 안테나들 또는 안테나들의 상이한 조합들을 통해 수신 디바이스에 의해 수신될 수도 있다. 다수의 신호들의 각각은 별개의 공간적 스트림으로서 지칭될 수도 있고, 동일한 데이터 스트림 (예를 들어, 동일한 코드워드) 또는 상이한 데이터 스트림과 연관된 비트들을 반송할 수도 있다. 상이한 공간 계층들은 채널 측정 및 보고를 위하여 사용되는 상이한 안테나 포트들과 연관될 수도 있다. MIMO 기술들은 다수의 공간 계층들이 동일한 수신 디바이스로 송신되는 단일-사용자 MIMO (SU-MIMO) 및 다수의 공간 계층들이 다수의 디바이스들로 송신되는 다수의 사용자 MIMO (MU-MIMO) 를 포함한다.

[0054] 공간 필터링, 지향성 송신 또는 지향성 수신으로서 또한 지칭될 수도 있는 빔포밍은 송신 디바이스와 수신 디바이스 사이의 공간적 경로를 따라 안테나 빔 (예를 들어, 송신 빔 또는 수신 빔) 을 성형 또는 스티어링하기 위해 송신 디바이스 또는 수신 디바이스 (예를 들어, 기지국 (105) 또는 UE (115)) 에서 사용될 수도 있는 신호 프로세싱 기술이다. 빔포밍은 안테나 어레이에 대하여 특정 배향들에서 전파하는 신호들은 구성적 간섭을 경험하는 한편, 다른 것들은 파괴적 간섭을 경험하도록 안테나 어레이의 안테나 엘리먼트들을 통하여 통신되는 신호들을 결합하는 것에 의해 실현된다. 안테나 엘리먼트들을 통하여 통신되는 신호들의 조정은 송신 디바이스 또는 수신 디바이스가 디바이스와 연관된 안테나 엘리먼트들의 각각을 통하여 반송되는 신호들에 특정 진폭 및 위상 오프셋들을 적용하는 것을 포함할 수도 있다. 안테나 엘리먼트의 각각과 연관된 조정들은 (예를 들어, 송신 디바이스 또는 수신 디바이스의 안테나 어레이에 대해 또는 일부 다른 배향에 대해) 특정 배향과 연관된 빔포밍 가중치 세트에 의해 정의될 수도 있다.

[0055]

일 예에서, 기지국 (105) 은 다수의 안테나들 또는 안테나 어레이들을 사용하여 UE (115) 와의 방향성 통신을 위한 빔포밍 동작들을 수행할 수도 있다. 예를 들어, 일부 신호들 (예를 들어, 동기 신호들, 참조 신호들, 빔 선택 신호들, 또는 다른 제어 신호들) 은 기지국 (105) 에 의해 다수회 상이한 방향들로 송신될 수 있고, 이는 신호가 상이한 방향들의 송신과 연관되는 상이한 빔포밍 가중치 세트들에 따라 송신되는 것을 포함할 수도 있다. 상이한 빔 방향들에서의 송신들은 기지국 (105) 에 의한 후속하는 송신 및/또는 수신을 위한 빔 방향을 (예를 들어, 기지국 (105) 또는 수신 디바이스, 이를 테면, UE (115) 에 의해) 식별하기 위해 사용될 수도 있다. 일부 신호들, 이를 테면, 특정 수신 디바이스와 연관된 데이터 신호들은 기지국 (105) 에 의해 단일 빔 방향으로 (예를 들어, 수신 디바이스, 이를 테면, UE (115) 와 연관된 방향으로) 송신될 수도 있다. 일부 예들에서, 단일 빔 방향을 따른 송신들과 연관된 빔 방향은 상이한 빔 방향들에서 송신되었던 신호에 적어도 부분적으로 기초하여 결정될 수도 있다. 예를 들어, UE (115) 는 기지국 (105) 에 의해 상이한 방향들로 송신되는 신호들 중 하나 이상을 수신할 수도 있고 UE (115) 는 자신이 최고 신호 품질 또는 달리 허용가능한 신호 품질로 수신하였다는 신호의 표시를 기지국 (105) 에 보고할 수도 있다. 이들 기술들이 기지국 (105) 에 의해 하나 이상의 방향들로 송신되는 신호들을 참조하여 설명되어 있지만, UE (115) 는 상이한 방향들로 다수회 신호들을 송신하기 위한 (예를 들어, UE (115) 에 의한 후속 송신 또는 수신을 위한 빔 방향을 식별하기 위한), 또는 단일의 방향으로 신호를 송신하기 위한 (예를 들어, 수신 디바이스로 데이터를 송신하기 위한) 유사한 기술들을 채용할 수도 있다.

[0056]

수신 디바이스 (예를 들어, mmW 수신 디바이스의 일례일 수도 있는 UE (115)) 는 동기화 신호들, 레퍼런스 신호들, 빔 선택 신호들, 또는 다른 제어 신호들과 같이 기지국 (105) 으로부터 다양한 신호들을 수신할 때 다중 수신 빔들을 시도할 수도 있다. 예를 들어, 수신 디바이스는, 상이한 안테나 서브어레이들을 통해 수신함으로써, 상이한 안테나 서브어레이들에 따라 수신 신호들을 프로세싱함으로써, 안테나 어레이의 복수의 안테나 엘리먼트들에서 수신된 신호들에 적용된 상이한 수신 빔포밍 가중치 세트들에 따라 수신함으로써, 또는, 안테나 어레이의 복수의 안테나 엘리먼트들에서 수신된 신호들에 적용된 상이한 수신 빔포밍 가중치 세트들에 따라 수신 신호들을 프로세싱함으로써, 다중 수신 방향들을 시도할 수도 있고, 이들 중 임의의 것은 상이한 수신 빔들 또는 수신 방향들에 따라 "리스닝 (listening)" 하는 것으로서 지칭될 수도 있다. 일부 예들에서, 수신 디바이스는 (예를 들어, 데이터 신호를 수신할 때) 단일의 빔 방향을 따라 수신하도록 단일의 수신 빔을 사용할 수도 있다. 단일의 수신 빔은 상이한 수신 빔 방향들 (예를 들어, 다수의 빔 방향들에 따른 리스닝에 적어도 부분적으로 기초하여 최고 신호 강도, 최고 신호 대 잡음 비 또는 달리 허용가능한 신호 품질을 갖도록 결정되는 빔 방향) 에 따라 적어도 부분적으로 기초하여 결정되는 빔 방향으로 정렬될 수도 있다.

[0057]

일부 경우들에, 기지국 (105) 또는 UE (115) 의 안테나들은 하나 이상의 안테나 어레이들 내에 위치될 수도 있고, 이는 MIMO 동작들 또는 송신 또는 수신 빔포밍들을 지원할 수도 있다. 예를 들어, 하나 이상의 기지국 안테나들 또는 안테나 어레이들은 안테나 어셈블리, 이를 테면, 안테나 타워에 병치될 수도 있다. 일부 경우들에, 기지국 (105) 과 연관된 안테나들 또는 안테나 어레이들은 다양한 지리적 위치들에 위치될 수도 있다.

기지국 (105) 은 기지국 (105) 이 UE (115) 와의 통신들의 빔포밍을 지원하기 위해 사용할 수 있는 안테나 포트들의 복수의 로우들 및 컬럼들을 갖는 안테나 어레이를 가질 수도 있다. 이와 마찬가지로, UE (115) 는 여러 MIMO 또는 빔포밍 동작들을 지원할 수도 있는 하나 이상의 안테나 어레이들을 가질 수도 있다.

[0058]

일부 경우들에, 무선 통신 시스템 (100) 은 계층화된 프로토콜 스택에 따라 동작하는 패킷 기반 네트워크일 수도 있다. 사용자 평면에서, 베어러 또는 패킷 데이터 수렴 프로토콜 (PDCP) 계층에서의 통신은 IP 기반일 수도 있다. 무선 링크 제어 (RLC) 계층은, 일부 경우들에, 패킷 세그먼트화 및 채어셈블리를 수행하여 논리 채널들을 통해 통신할 수도 있다. 매체 액세스 제어 (MAC) 계층은 논리 채널들을 우선순위 처리하여 수송 채널들로의 멀티플렉싱을 수행할 수도 있다. MAC 계층은 또한 하이브리드 자동 반복 요청 (HARQ) 을 사용하여 MAC 계층에서의 재송신을 제공하여 링크 효율성을 개선할 수도 있다. 제어 평면에 있어서, 무선 리소스 제어 (RRC) 프로토콜 계층은 사용자 평면 데이터에 대한 라디오 베어러들을 지원하는 코어 네트워크 (130) 또는 기지국들 (105) 과 UE (115) 사이의 RRC 접속의 확립, 구성, 및 유지보수를 제공할 수도 있다. 물리 (PHY) 계층에서, 전송 채널들은 물리 채널들에 매핑될 수도 있다.

[0059]

일부 경우들에서, UE 들 (115) 및 기지국들 (105) 은 데이터가 성공적으로 수신되는 가능성을 증가시키기 위해 데이터의 재송신을 지원할 수도 있다. HARQ 피드백은 데이터가 통신 링크 (125) 를 통해 정확하게 수신되는 가능성을 증가시키는 한 가지 기법이다. HARQ 는 (예를 들어, CRC 를 사용한) 여러 검출, 순방향 여러 정정 (FEC), 및 재송신 (예를 들어, 자동 반복 요청 (ARQ)) 의 조합을 포함할 수도 있다. HARQ 는 열악한 무선 조건들 (예를 들어, 신호 대 노이즈 조건들) 에서 MAC 계층에서의 스루풋을 개선할 수도 있다. 일부 경우들

에서, 무선 디바이스는 동일한 슬롯 HARQ 피드백을 지원할 수 있으며, 여기서 디바이스는 슬롯에서의 이전 심볼에서 수신된 데이터에 대해 특정 슬롯에서 HARQ 피드백을 제공할 수도 있다. 다른 경우들에서, 디바이스는 후속 슬롯에서 또는 일부 다른 시간 인터벌에 따라 HARQ 피드백을 제공할 수도 있다.

[0060] LTE 또는 NR에서의 시간 간격들은 기본 시간 단위의 배수들로 표현될 수 있고, 이는 예를 들어,  $T_s = 1/30,720,000$  초의 샘플링 주기로 지칭할 수도 있다. 통신 리소스의 시간 간격들은 10 밀리초 (ms)의 지속 기간을 각각 갖는 무선 프레임들에 따라 구성될 수 있고, 여기서 프레임 주기는  $T_f = 307,200 T_s$ 로서 표현될 수도 있다. 무선 프레임들은 0 내지 1023의 범위에 있는 시스템 프레임 넘버 (SFN)에 의해 식별될 수도 있다. 각각의 프레임은 0 내지 9로 넘버링되는 10 개의 서브프레임들을 포함할 수도 있고, 각각의 서브프레임은 1 ms의 지속기간을 가질 수도 있다. 서브프레임은 0.5 ms의 지속기간을 각각 갖는 2 개의 슬롯들로 추가로 분할될 수도 있고, 각각의 슬롯은 (예를 들어, 각각의 심볼 주기의 앞에 덧붙여진 시클릭 프리픽스의 길이에 의존하여) 6 또는 7 개의 변조 심볼 주기들을 포함할 수도 있다. 시클릭 프리픽스를 제외하고, 각각의 심볼 주기는 2048 개의 샘플 주기들을 포함할 수도 있다. 일부 경우들에 서브프레임은 무선 통신 시스템 (100)의 최소 스케줄링 유닛일 수도 있고, 송신 시간 간격 (TTI)으로 지칭될 수도 있다. 다른 경우들에, 무선 통신 시스템 (100)의 최소 스케줄링 유닛은 서브프레임보다 더 짧을 수도 있거나 또는 (예를 들어, 단축된 TTI들 (sTTI들)의 베스트로 또는 sTTI들을 사용한 선택된 컴포넌트 캐리어들로) 동적으로 선택될 수도 있다.

[0061] 일부 무선 통신 시스템들에서, 슬롯은 하나 이상의 슬롯들을 포함하는 다수의 미니-슬롯들로 추가로 분할될 수도 있다. 일부 사례들에서, 미니슬롯들의 심볼 또는 미니슬롯은 스케줄링의 최소 유닛일 수도 있다. 각각의 심볼은 예를 들어 동작의 주파수 대역 또는 서브캐리어 간격에 따라 지속기간에서 다를 변경될 수 있다. 또한, 일부 무선 통신 시스템들은 다수의 슬롯들 또는 미니-슬롯들이 UE (115)와 기지국 (105) 사이의 통신에 사용되고 함께 어그리게이트되는 슬롯 어그리게이션을 구현할 수도 있다.

[0062] 용어 "캐리어"는 통신 링크 (125) 상에서 통신들을 지원하기 위해 정의된 물리 계층 구조를 갖는 무선 주파수 스펙트럼 리소스들의 세트를 지칭할 수도 있다. 예를 들어, 통신 링크 (125)의 캐리어는 주어진 무선 액세스 기술에 대한 물리 계층 채널들에 따라 동작되는 무선 주파수 스펙트럼 대역의 부분을 포함할 수도 있다. 각각의 물리 계층 채널은 사용자 데이터, 제어 정보 또는 다른 시그널링을 반송할 수도 있다. 캐리어는 미리 정의된 주파수 채널 (예를 들어, E-UTRA (Evolved Universal Terrestrial Radio Access (UTRA)) 절대 무선 주파수 채널 넘버 (EARFCN))과 연관될 수도 있고, UE들 (115)에 의한 디스커버리를 위하여 채널 래스터에 따라 위치될 수도 있다. 캐리어들은 (예를 들어, FDD 모드에서) 다운링크 또는 업링크일 수도 있거나, 또는 (예를 들어, TDD 모드에서) 다운링크 및 업링크 통신들을 반송하도록 구성될 수도 있다. 일부 예들에서, 캐리어를 통해 송신된 신호 패형들은 (예를 들어, 직교 주파수 분할 멀티플렉싱 (OFDM) 또는 이산 푸리에 변환-확산-OFDM (DFT-s-OFDM)과 같은 멀티-캐리어 변조 (MCM) 기법들을 사용하여) 다중 서브캐리어들로 구성될 수도 있다.

[0063] 캐리어들의 조직적 구조는 상이한 라디오 액세스 기술들 (예를 들어, LTE, LTE-A, NR 등)에 대해 상이할 수도 있다. 예를 들어, 캐리어를 통한 통신물들은 TTI들 또는 슬롯들에 따라 조직될 수도 있고, 이들의 각각은 사용자 데이터 및 그 사용자 데이터의 디코딩을 지원하기 위한 제어 정보 또는 시그널링을 포함할 수도 있다. 캐리어는 또한, 전용 획득 시그널링 (예를 들어, 동기화 신호들 또는 시스템 정보 등) 및 캐리어에 대한 동작을 통합조정하는 제어 시그널링을 포함할 수도 있다. 일부 예들에서 (예를 들어, 캐리어 어그리게이션 구성에서), 캐리어는 또한, 다른 캐리어들에 대한 동작들을 통합조정하는 제어 시그널링 또는 획득 시그널링을 가질 수도 있다.

[0064] 물리 채널들은 다양한 기법들에 따라 캐리어 상에서 멀티플렉싱될 수도 있다. 물리 제어 채널 및 물리 데이터 채널은 예를 들어, 시간 분할 멀티플렉싱 (TDM) 기법들, 주파수 분할 멀티플렉싱 (FDM) 기법들, 또는 하이브리드 TDM-FDM 기법들을 사용하여 다운링크 캐리어 상에서 멀티플렉싱될 수도 있다. 일부 예들에서, 물리 제어 채널에서 송신되는 제어 정보는 캐스케이드형 방식으로 상이한 제어 영역들 사이에 (예를 들어, 공통 제어 영역 또는 공통 검색 공간과 하나 이상의 UE-특정의 제어 영역들 또는 UE-특정 검색 공간들 사이에) 분포될 수 있다.

[0065] 캐리어는 무선 주파수 스펙트럼의 특정 대역폭과 연관될 수도 있고 일부 예들에서, 캐리어 대역폭은 무선 통신 시스템 (100) 또는 캐리어의 "시스템 대역폭"으로 지칭될 수도 있다. 예를 들어, 캐리어 대역폭은 특정 무선 액세스 기술의 캐리어들에 대한 복수의 미리 결정된 대역폭들 중 하나 (예를 들어, 1.4, 3, 5, 10, 15, 20,

40, 또는 80 MHz) 일 수도 있다. 일부 예들에서, 각각의 서비스되는 UE (115)는 캐리어 대역폭 전부 또는 일부 상에서 동작하기 위하여 구성될 수도 있다. 다른 예들에서, 일부 UE들 (115)은 캐리어 (예를 들어, 협대역 프로토콜 유형의 "대역내" 배치) 내에서 미리 정의된 부분 또는 범위 (예를 들어, 서브캐리어들 또는 RB들의 세트)와 연관된 협대역 프로토콜 유형을 사용한 동작을 위하여 구성될 수도 있다.

[0066] MCM 기술들을 채용하는 시스템들에서, 리소스 엘리먼트는 하나의 심볼 주기 (예를 들어, 하나의 변조 심볼의 지속기간) 및 하나의 서브캐리어로 구성될 수도 있고 심볼 주기 및 서브캐리어 간격은 역으로 관련되어 있다. 각각의 리소스 엘리먼트에 의해 반송되는 비트들의 수는 변조 방식 (예를 들어, 변조 방식의 순서)에 의존할 수도 있다. 따라서, UE (115)가 수신하는 리소스 엘리먼트들이 더 많고 변조 방식의 순서가 더 높을수록 UE (115)에 대해 데이터 레이트가 더 높을 수도 있다. MIMO 시스템들에서, 무선 통신 리소스는 무선 주파수 스펙트럼 리소스, 시간 리소스, 및 공간 리소스 (예를 들어, 공간 계층들)의 조합을 지칭할 수도 있고, 다수의 공간 계층들의 사용은 추가로 UE (115) 와의 통신을 위한 데이터 레이트를 증가시킬 수도 있다.

[0067] 무선 통신 시스템 (100)의 디바이스들 (예를 들어, 기지국들 (105) 또는 UE들 (115))은 특정 캐리어 대역폭 상에서의 통신들을 지원하는 하드웨어 구성을 가질 수도 있거나 또는 캐리어 대역폭들의 세트 중 하나를 통한 통신들을 지원하도록 구성 가능할 수도 있다. 일부 예들에서, 무선 통신 시스템 (100)은 하나 보다 많은 상이한 캐리어 대역폭과 연관된 캐리어들을 통한 동시 통신들을 지원할 수 있는 기지국들 (105) 및/또는 UE들을 포함할 수도 있다.

[0068] 무선 통신 시스템 (100)은 다수의 셀들 또는 캐리어들에 상에서 UE (115) 와의 통신을 지원할 수도 있으며, 그 특징은 캐리어 어그리게이션 (CA) 또는 멀티-캐리어 동작으로서 지칭될 수도 있다. UE (115)는 캐리어 어그리게이션 구성에 따라 다수의 다운링크 CC들 및 하나 이상의 업링크 CC들로 구성될 수도 있다. 캐리어 어그리게이션은 양쪽 FDD 및 TDD 컴포넌트 캐리어들에 사용될 수도 있다.

[0069] 일부 경우들에, 무선 통신 시스템 (100)은 강화된 컴포넌트 캐리어들 (eCCs)을 활용할 수도 있다. eCC는 더 넓은 캐리어 또는 주파수 채널 대역폭, 더 짧은 심볼 지속기간, 더 짧은 TTI 지속기간, 또는 수정된 제어 채널 구성을 포함하는 하나 이상의 피처들에 의해 특징화될 수도 있다. 일부 경우들에, eCC는 (예를 들어, 다수의 서비스 셀들이 준최적 또는 비이상적 백홀 링크를 가질 때) 듀얼 접속성 구성 또는 캐리어 어그리게이션 구성과 연관될 수도 있다. eCC는 또한, (예를 들어, 하나보다 많은 오퍼레이터가 스펙트럼을 사용하도록 허용되는 경우) 비허가 스펙트럼 또는 공유 스펙트럼에서 사용하기 위하여 구성될 수도 있다. 넓은 캐리어 대역폭을 특징으로 하는 eCC는 전체 캐리어 대역폭을 모니터링 가능하지 않거나 또는 (예를 들어, 전력을 보존하기 위해) 제한된 캐리어 대역폭을 사용하기 위해 달리 구성되는 UE들 (115)에 의해 활용될 수도 있는 하나 이상의 세그먼트들을 포함할 수도 있다.

[0070] 일부 경우들에, eCC는 다른 CC들과는 상이한 심볼 지속기간을 활용할 수도 있고, 이는 다른 CC들의 심볼 지속기간들에 비해 감소된 심볼 지속기간의 사용을 포함할 수도 있다. 더 짧은 심볼 지속기간은 인접하는 서브캐리어들 사이의 증가된 간격과 연관될 수도 있다. eCC들을 활용하는 디바이스, 이를 테면, UE (115) 또는 기지국 (105)은 감소된 심볼 지속기간들 (예를 들어, 16.67 마이크로초)에서 (예를 들어, 20, 40, 60, 80 MHz 등의 캐리어 대역폭 또는 주파수 채널에 따라) 대역폭 신호들을 송신할 수도 있다. eCC에서의 TTI는 하나 또는 다수의 심볼 주기들로 구성될 수도 있다. 일부 경우들에, TTI 지속기간 (즉, TTI에서 심볼 주기들의 수)는 가변적일 수도 있다.

[0071] NR 시스템과 같은 무선 통신 시스템 (100)은 다른 것들 중에서도 허가, 공유, 및 비허가 스펙트럼 대역들의 임의의 조합을 이용할 수도 있다. eCC 심볼 지속기간 및 서브캐리어 간격의 유연성은 다수의 스펙트럼들에 걸친 eCC의 사용을 허용할 수도 있다. 일부 예들에서, NR 공유 스펙트럼은 특히 리소스들의 동적 수직 (예를 들어, 주파수에 걸침) 및 수평 (예를 들어, 시간에 걸침) 공유를 통해 스펙트럼 사용 및 스펙트럼 효율을 증가시킬 수 있다.

[0072] 일부 무선 통신 시스템들 (100)에서, 기지국들 (105) 또는 UE들 (115)은 송신물들을 인코딩 및 디코딩하기 위하여, 폴라 코드들을 구현할 수도 있다. 일부 경우들에, 송신 디바이스 (예를 들어, 기지국 (105) 또는 UE (115))는 송신을 위한 페이로드를 선택할 수도 있다. 페이로드의 사이즈는 예를 들어, 가능한 페이로드 사이즈들의 리스트로부터 또는 코드워드의 길이에 기초하여 구성 가능할 수도 있다. 일부 경우들에, 코드워드들을 모니터링하는 수신 디바이스는 가능한 페이로드 사이즈들 또는 코드워드 길이들의 어느 것을 모니터링 할 수도 있다. 디코더가 코드워드 또는 페이로드 사이즈들을 알지 못할 경우 이를 디코딩은 블라인드 디코딩으로서 지칭될 수도 있다.

[0073]

블라인드 디코딩 프로세스들의 성공을 개선하기 위해, 송신 디바이스는 페이로드 사이즈를 나타내는 하나 이상의 기법들을 사용하여 코드워드를 인코딩할 수도 있다. 송신 디바이스는 인코딩하기 위한 정보 비트들의 세트를 결정할 수도 있고, 여기서 정보 비트들은 페이로드 비트들 및 페이로드 비트들에 기초하여 생성되는 패리티 비트들을 포함할 수도 있다. 이들 정보 비트들은 비트 벡터로 조직화될 수도 있다. 송신 디바이스는 페이로드의 사이즈 (예를 들어, 페이로드 비트들의 수)에 기초하여 비트 벡터를 수정할 수도 있다. 제 1 기법에서, 송신 디바이스는 (예를 들어, 식에 기초하여 그리고 메모리에서의 테이블로부터) 페이로드 사이즈에 대응하는 마스킹 벡터를 결정할 수도 있다. 디바이스는 마스킹 벡터를 사용하여 비트 벡터의 하나 이상의 비트들을 마스킹 또는 스킵램블링할 수도 있다. 제 2 기법에서, 디바이스는 페이로드 비트들보다 더 낮은 비트 인덱스들에 비트 벡터에서의 패리티 비트들의 적어도 일부분을 위치시킬 수도 있다. 제 3 기법에서, 디바이스는 비트 벡터의 제 1 비트 인덱스가 디폴트 동결된 비트 값의 것과는 상이한 비트 값을 포함함 (예를 들어, 동결된 비트 값이 0의 값을 갖는다면, 제 1 비트 인덱스는 1의 값을 가질 것임)을 보장할 수도 있다.

예를 들어, 디바이스는 제 1 비트가 1 비트이도록, 비트 벡터의 제 1 비트 인덱스에서 추가적인 비트를 삽입할 수도 있거나 또는 페이로드 비트들을 배열할 수도 있다. 일부 경우들에, 위에 설명된 비트 벡터는 정보 비트 벡터로서 지칭될 수도 있고, 정보 비트 벡터를 선행하는 하나 이상의 동결된 비트들을 포함하는 더 많은 비트 벡터의 일부분일 수도 있다. 송신 디바이스는 비트 벡터의 비트들을 대응 비트 채널들에 배정할 수도 있고 그리고 배정된 비트 채널들 및 폴라 코드를 사용하여 코드워드를 생성할 수도 있다. 디바이스는 이 생성된 코드워드를 수신 디바이스 (예를 들어, 기지국 (105) 또는 UE (115))로 송신할 수도 있다.

[0074]

수신 디바이스는 블라인드 디코딩 프로세스를 사용하여 코드워드를 디코딩할 수도 있다. 예를 들어, 수신 디바이스는 페이로드 사이즈를 위한 하나 이상의 가설들을 사용하여 수신된 신호를 디코딩할 수도 있다. 위에 설명된 기법들 각각에 대해, 디코딩 프로세스는 수신 디바이스가 부정확한 페이로드 사이즈 가설을 가정하면 실패할 수도 있다. 예를 들어, 제 1의 2 가지 기법들에서, 패리티 체크 또는 CRC는 코드워드가 부정확한 마스킹 벡터 또는 CRC에 대한 부정확한 시작 포지션을 사용하여 디코딩되면 실패할 수도 있다. 제 3 기법에서, 제 1 정보 비트가 디폴트 동결된 비트 값과는 상이한 값과 제 1 비트일 때, 수신 디바이스는 비트 벡터 내에서 이 제 1 정보 비트의 포지션을 결정할 수도 있다. 이들 기법들의 하나 이상을 사용하여, 수신 디바이스는 상이한 페이로드 사이즈들의 코드워드들을 성공적으로 디코딩할 수도 있다.

[0075]

도 2는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 디바이스 (200)의 예를 나타낸다. 디바이스 (200)는 (예를 들어, 여러 정정 코드, 이를 테면, 폴라 코드를 사용하여) 인코딩 또는 디코딩 프로세스를 수행하는 무선 통신 시스템 (100) 내의 임의의 디바이스에 포함될 수도 있다. 예를 들어, 디바이스 (200)는 도 1을 참조하여 설명된 UE (115) 또는 기지국 (105)에 포함될 수도 있다.

[0076]

도시된 바와 같이, 디바이스 (200)는 메모리 (205), 인코더/디코더 (210), 및 송신기/수신기 (215)를 포함한다. 제 1 버스 (220)는 메모리 (205)를 인코더/디코더 (210)에 접속할 수도 있고 제 2 버스 (225)는 인코더/디코더 (210)를 송신기/수신기 (215)에 접속할 수도 있다. 일부 사례들에서, 디바이스 (200)는 메모리 (205)에 저장된 데이터를, UE (115) 또는 기지국 (105)과 같은 다른 디바이스로 송신되게 할 수도 있다. 송신 프로세스를 개시하기 위해, 디바이스 (200)는 메모리 (205)로부터 송신을 위한 데이터를 취출할 수 있다. 데이터는 제 1 버스 (220)를 통해 메모리 (205)로부터 인코더/디코더 (210)에 제공되는 1 또는 0 들일 수 있는 다수의 페이로드 비트들 "A"를 포함할 수 있다. 일부 경우들에, 이들 페이로드 비트들은 정보 비트들의 전체 세트 'A+L'를 형성하기 위해 다수의 패리티 비트들 'L'과 결합할 수도 있다. 정보 비트들의 수는 도시된 바와 같이, 값 'K'로서 표현될 수도 있다. 인코더/디코더 (210)는 정보 비트들을 인코딩하고 K와 같거나 또는 다를 수도 있는 길이 'N'을 갖는 코드워드를 출력할 수도 있다. 정보 비트로서 할당되지 않은 비트들 (즉, N-k 비트들)은 동결된 비트들로서 배정될 수 있다. 일부 경우들에, 정보 비트들은 K개의 가장 신뢰할 수 있는 비트 채널들에 배정될 수 있고, 동결된 비트들은 나머지 비트 채널들에 할당될 수 있다. 동결된 비트들은 인코더와 디코더 (즉, 송신기에서 정보 비트들을 인코딩하는 인코더, 및 수신기에서 수신된 코드워드를 디코딩하는 디코더) 모두에게 알려진 디폴트 값 (예를 들어, 0 또는 1 또는 일부 다른 값)의 비트들일 수도 있다. 또한, 수신 디바이스 관점에서, 디바이스 (200)는 수신기 (215)를 통해 인코딩된 데이터를 수신할 수도 있고, 송신된 데이터를 획득하기 위해 디코더 (210)를 사용하여 인코딩된 데이터를 디코딩할 수도 있다.

[0077]

일부 무선 시스템들에서, 디코더 (210)는 연속 제거 (SC) 또는 연속 제거 리스트 (SCL) 디코더의 예일 수 있다. UE (115) 또는 기지국 (105)은 수신기 (215)에서 코드워드를 포함하는 송신물을 수신할 수 있고,

송신물을 SCL 디코더 (예를 들어, 디코더 (210))로 전달할 수 있다. SCL 디코더는 수신된 코드워드의 비트 채널들에 대한 입력 로그-우도 비들 (LLR들)을 결정할 수 있다. 디코딩 동안, SCL 디코더는 이들 입력 LLR 들에 기초하여 디코딩된 LLR들을 결정할 수 있고, 디코딩된 LLR들은 폴라 코드의 각각의 비트 채널들에 대응한다. 이들 디코딩된 LLR들은 비트 매트릭들로 지정될 수도 있다. 일부 경우들에, LLR이 0 또는 양의 값이면, SCL 디코더는 대응하는 비트가 0 비트인 것으로 결정할 수도 있고, 음의 LLR은 1 비트에 대응할 수 있다. SCL 디코더는 비트 매트릭을 사용하여 디코딩된 비트 값을 결정할 수 있다.

[0078] SCL 디코더는 다수의 동시적 SC 디코딩 프로세스를 이용할 수 있다. 각각의 SC 디코딩 프로세스는 코드워드를 순차적으로 (예를 들어, 비트 채널 인덱스 순서로) 디코딩할 수 있다. 다수의 SC 디코딩 프로세스들의 조합으로 인해, SCL 디코더는 다수의 디코딩 경로 후보들을 계산할 수 있다. 예를 들어, 리스트 사이즈 'L'의 SCL 디코더 (즉, SCL 디코더는 L 개의 SC 디코딩 프로세스들을 가짐)는 L 개의 디코딩 경로 후보들을 계산할 수도 있고 각각의 디코딩 경로 후보에 대한 대응하는 신뢰성 매트릭 (예를 들어, 경로 매트릭)을 계산할 수도 있다. 경로 매트릭은 대응하는 디코딩 경로 후보가 디코딩된 비트들의 정확한 세트일 확률 또는 디코딩 경로 후보의 신뢰성을 나타낼 수 있다. 경로 매트릭은 결정된 비트 매트릭 및 각각의 비트 채널에서 선택된 비트 값에 기초할 수 있다. SCL 디코더는 수신된 코드워드에서 비트 채널들의 수와 동일한 수의 레벨들을 가질 수 있다. 각각의 레벨에서, 각각의 디코딩 경로 후보는 0 비트 및 1 비트의 경로 매트릭에 기초하여 0 비트 또는 1 비트를 선택할 수도 있다. SCL 디코더는 경로 매트릭들에 기초하여 디코딩 경로 후보를 선택할 수도 있고 비트들의 디코딩된 세트들로서 선택된 디코딩 경로에 대응하는 비트들을 출력할 수도 있다. 예를 들어, SCL 디코더는 가장 높은 경로 매트릭을 갖는 디코딩 경로를 선택할 수 있다.

[0079] SCL 디코더는 제 1 수의 비트들이 모든 동결된 비트들이면, SCL 디코더는 제 1 수의 비트들에 대한 정확한 디코딩 경로가 디폴트 동결된 비트 값들이어야 한다고 결정할 수도 있다 (예를 들어, 디폴트 동결된 비트 값이 0 이면, 제 1 수의 비트들에 대한 정확한 디코딩 경로는 모두 0들이다). SCL 디코더가 후속 디코딩 동작들 없이 앞으로 제 1 정보 비트로부터의 정확한 디코딩 경로를 결정할 수 없기 때문에 (예를 들어, 제 1 정보 비트가 0 또는 1 일 수 있기 때문에), 일단 SCL 디코더가 제 1 정보 비트에 도달하면, SCL 디코더는 코드워드의 나머지 비트들을 디코딩하는 동작들을 수행하기 시작할 수도 있다. 그러나, SCL 디코더는 동결된 비트들을 포함하는 비트 채널들에 대한 비트 매트릭들을 여전히 결정할 수도 있고 디코딩 경로 후보들에 대한 경로 매트릭들을 계산할 때 이들 비트 매트릭들을 사용할 수도 있다. 예를 들어, SCL 디코더는 비트 타입과 무관하게 매 비트 뒤에 (예를 들어, 각각의 동결된 비트 또는 정보 비트 뒤에) 디코딩 후보들에 대한 경로 매트릭들을 업데이트할 수도 있다.

[0080] 폴라 코딩된 코드워드를 디코딩하기 위해, 디바이스 (200)는 블라인드 디코딩을 수행할 수도 있다. 예를 들어, 수신기 (215)는 코드워드에 대한 후보 가설들의 세트로 구성될 수도 있고, 여기서 각각의 후보는 N:K 또는 N:A 가설들의 세트에 대응할 수도 있다. 수신기 (215)는 채널을 통해 수신된 하나 이상의 후보 코드워드들을 식별할 수도 있고 상이한 N:K 또는 N:A 가설들을 사용하여 각각의 후보 코드워드를 프로세싱하려 시도할 수도 있다. 일부 경우들에, 디코더 (210)는 데이터 페이로드에 대한 패리티 비트들 및 페이로드 비트들을 포함할 수도 있는 정보 비트들의 세트를 획득하기 위해 수신기 (215)에 의해 수신된 신호를 디코딩할 수도 있다. 디코더 (210)는 패리티 비트들을 사용하여 데이터 페이로드들에 대한 페이로드 비트들 상에서 CRC 또는 패리티 체크를 수행할 수도 있고, 그리고 패리티 체크가 통과하면, 데이터 페이로드가 디바이스 (200)에 대한 성공적으로 디코딩된 코드워드를 나타낸다고 결정할 수도 있다.

[0081] 그러나, 일부 경우들에, 코드워드가 과도한 봉괴를 경험하거나 (예를 들어, 채널이 매우 낮은 신호 대 잡음 비 (SNR)를 가짐), 후보 가설들에 대한 코드워드가 송신되지 않거나 (예를 들어, 코드워드는 랜덤 노이즈를 나타내거나), 송신된 코드워드가 상이한 디바이스에 대해 의도되거나 또는 후보 가설이 부정확할 수도 있기 때문에 (예를 들어, N:K 또는 N:A 가설들이 부정확함) 디코딩 동작은 실패할 수도 있다. 이들 경우들에, 디코더 (210)는 디코딩 실패를 검출하고, 상이한 후보 코드워드를 사용하여 디코딩을 시도할 수도 있다.

[0082] 또한, 블라인드 디코딩의 일부 경우들에, 디코더 (210)는 특정 코드워드들 간을 구별하지 못할 수도 있다. 블라인드 디코딩 프로세스에서, 예를 들어, 디코더 (210)는 동결된 비트들 및 동결된 비트들과 동일한 비트들을 갖는 정보 비트들을 동일하게 프로세싱할 수도 있다. 예를 들어, 디코더 (210)가 코드워드 내에서 정보 비트들의 수 (K)를 식별하지 못하면, 디코더 (210)는 디폴트 동결된 비트 값 (예를 들어, 0)을 나타내는 LLR이 동결된 비트 또는 동일한 값을 갖는 것으로 발생한 정보 비트에 대응하는지의 여부를 결정하지 못할 수도 있다. 따라서, 인코더 (210)가 동결된 비트 값을 갖는 정보 비트들 (예를 들어, 0의 값을 갖는 정보 비트)을 최소 신뢰성 정보 비트 채널들에 맵핑하면 코드워드를 수신하는 디코더 (210)는 이들 비트 채널들이 최

소 신뢰성 정보 비트 채널들인지 또는 최대 신뢰성의 동결된 비트 채널들인지를 결정하지 못할 수도 있다. 이러한 경우들에서, 디코더 (210)는 코드워드에서 인코딩된 정확한 수의 정보 비트들 (K), 또는 페이로드 비트들 (A)을 결정하지 못할 수도 있다.

[0083] 일부 경우들에, 패리티 비트들은 동결된 비트들과 동일한 값들을 갖는 비트들이 정보 비트들인지 또는 동결된 비트들인지의 여부를 표시하지 않을 수도 있다. 예를 들어, 패리티 비트들이 CRC 비트들이라면 인코더 (210)는 페이로드 비트들에 기초하여 패리티 비트들에 대한 비트 값들을 결정할 수도 있다. 그러나, 패리티 비트들은 증가하는 페이로드 신뢰도의 순서로 인코더 (210)에 의해 결정될 수도 있고 동결된 비트 값들의 관점에서 업데이트되지 않을 수도 있다. 예를 들어, 인코더 (210)는 페이로드 비트들의 부분 또는 전체에 대응하는 디폴트 패리티 비트 스트링을 생성할 수도 있다. 인코더 (210)는 1의 비트 값을 갖는 페이로드 비트마다 디폴트 패리티 비트 스트링을 업데이트할 수도 있고, (예를 들어, 동결된 비트들이 0의 비트 값을 가지면) 0의 비트 값을 갖는 페이로드 비트들에 대한 패리티 비트 스트링을 업데이트하지 않을 수도 있다. 이러한 식으로, 디코더 (210)가 페이로드 비트들을 디코딩할 때 디코더 (210)는 패리티 비트 스트링을 결정하기 위해 동일한 프로세스를 수행할 수도 있고 결정된 패리티 비트 스트링을 실제 수신된 패리티 비트 스트링에 비교하여 페이로드 비트들이 정확하게 디코딩되는지를 (예를 들어, 패리티 비트 스트링이 매칭하는지를) 결정할 수도 있다. 그러나, 인코더 (210)가 0의 값을 갖는 선두 정보 비트들에 대한 디폴트 패리티 비트 스트링을 업데이트하지 않기 때문에, 패리티 비트 스트링들은 선두 0 비트들을 갖는 페이로드에 대해 그리고 달리 동일한 비트들이지만 선두 0 비트들이 없는 페이로드에 대해 동일할 수도 있다.

[0084] 정보 비트 인덱스 맵핑의 일 특정 예에서, 인코더 (210)는 제 1 경우에, 108 비트 코드워드 내에서 78 정보 비트들 (예를 들어, 54 페이로드 비트들 및 24 CRC 비트들)을 인코딩할 수도 있다. 인코더 (210)는 폴라 코드에 대한 108 개의 총 비트 채널들의 78 개의 최대 신뢰성 비트 채널들을 선택할 수도 있고 78 정보 비트들을 이들 78 선택된 비트 채널들에 맵핑할 수도 있다. 이러한 경우에, 108 개의 총 비트 채널들의 최대 신뢰성 비트 채널은 비트 채널 (107) 일 수도 있고, 비트 채널 (14)은 최저 신뢰성의 78 개의 선택된 정보 비트 채널들을 갖는다. 인코더 (210)는 (예를 들어, 비트 벡터의 종료시 CRC 비트들을 갖거나 또는 비트 벡터 전반에 걸쳐 인터리브된 CRC 비트들 등을 갖는) 페이로드 비트들 및 CRC 비트들을 포함하는 비트 벡터를 생성할 수도 있고, 정보 비트 채널들에 비트 벡터의 비트들을 배정할 수도 있다. 예를 들어, 인코더 (210)는 비트 벡터의 제 1 비트 인덱스에서의 정보 비트를 최저 신뢰성 정보 비트 채널 (예를 들어, 비트 채널 (14))에 배정할 수도 있다. 이러한 제 1 정보 비트가 0 비트 (예를 들어, 동결된 비트 값)이면, 인코더 (210)는 비트 채널 (14)을 0 비트로 설정할 수도 있다. 그러나, 다른 경우에, 인코더 (210)가 108 비트 코드워드 내에서 77 개의 정보 비트들 (예를 들어, 54 페이로드 비트들 및 24 CRC 비트들)을 인코딩하면, 비트 채널 (14)은 최대 신뢰성의 동결된 비트 채널일 수도 있다. 어느 경우에도, 인코더 (210)는 0 비트를 비트 채널 (14)에 배정할 수도 있다. 따라서, 위에 설명된 2 개의 경우들에서 비트 벡터들의 나머지 77 비트들이 동일하면, 제 1 코드워드가 78 정보 비트들을 포함하고 제 2 코드워드가 77 정보 비트들을 포함함에도 불구하고, 인코더 (210)는 2 개의 경우들에 대해 동일한 코드워드들을 출력할 수도 있다. 따라서, 이를 코드워드들을 블라인드 디코딩하는 디코더 (210)는 코드워드가 77 또는 78 정보 비트들을 포함하는지의 여부를 결정하지 못할 수도 있다.

[0085] 위에 설명된 두 개와 같이 코드워드들 간의 차별화를 용이하게 하기 위해, 인코더 (210)는 페이로드 사이즈 (예를 들어, 페이로드 비트들의 수) 또는 코드워드에서의 정보 비트들의 수의 표시를 포함할 수도 있다. 예를 들어, 인코더 (210)는 페이로드 사이즈에 기초하여 비트 벡터 (예를 들어, 비트 벡터의 순서 또는 비트 벡터의 컨텐츠)를 수정할 수도 있다. 제 1의 이러한 기법들에서, 인코더 (210)는 마스킹 벡터를 사용하여 비트 벡터 상에서 마스킹 동작을 수행할 수도 있고 여기서 선택된 마스킹 벡터는 페이로드 사이즈에 기초한다. 제 2의 이러한 기법들에서, 인코더 (210)는 패리티 비트들의 하나 이상이 비트 벡터에 먼저 위치되도록, 비트 벡터에서 페이로드 비트들 및 패리티 비트들을 배열할 수도 있다. 프론트 로딩된 패리티 비트들의 적어도 하나가 디폴트 동결된 값과는 상이한 비트 값을 가지면 (예를 들어, 이를 패리티 비트들의 적어도 하나가 1이면), 디코더 (210)는 코드워드에서 정확한 수의 페이로드 또는 코드워드에서의 정보 비트들을 결정 가능할 수도 있다. 이러한 제 3 기법에서, 인코더 (210)는 정보 비트들의 시작을 표시하기 위해 비트 벡터의 컨텐츠들을 수정할 수도 있다. 이러한 제 3 기법의 일 예로서, 인코더 (210)는 최소 신뢰성 정보 비트 채널들을 표시하기 위해 비트 벡터의 앞에 1 비트를 삽입할 수도 있다. 이러한 제 3 기법의 다른 예로서, 인코더 (210)는 비트 벡터에서의 제 1 비트가 1 비트이도록 페이로드 비트들을 배열할 수도 있다. 이들 기법들의 어느 것은 최소 신뢰성 정보 비트 채널의 표시를, 코드워드를 디코딩하는 디코더 (210)에 제공할 수도 있다. 표시된 채널의 인덱스, 코드워드 사이즈 및 구성된 수의 패리티 비트들 (예를 들어, 인코더 (210) 및

디코더 (210) 는 코드워드에 대한 구성된 수의 패리티 또는 CRC 비트들의 표시를 포함할 수도 있음) 에 기초하여, 디코더 (210) 는 위에 설명된 바와 같이 문제가 되는 경우에도 블라인드 디코딩 프로세스에서 페이로드 비트들의 수를 결정할 수도 있고, 이는 블록 에러 비 (BLER) 에 대한 어떠한 부정적인 충격 없이도 송신된 데이터 페이로드를 정확하게 결정함에 있어서 디코더 (210) 를 보조할 수 있다.

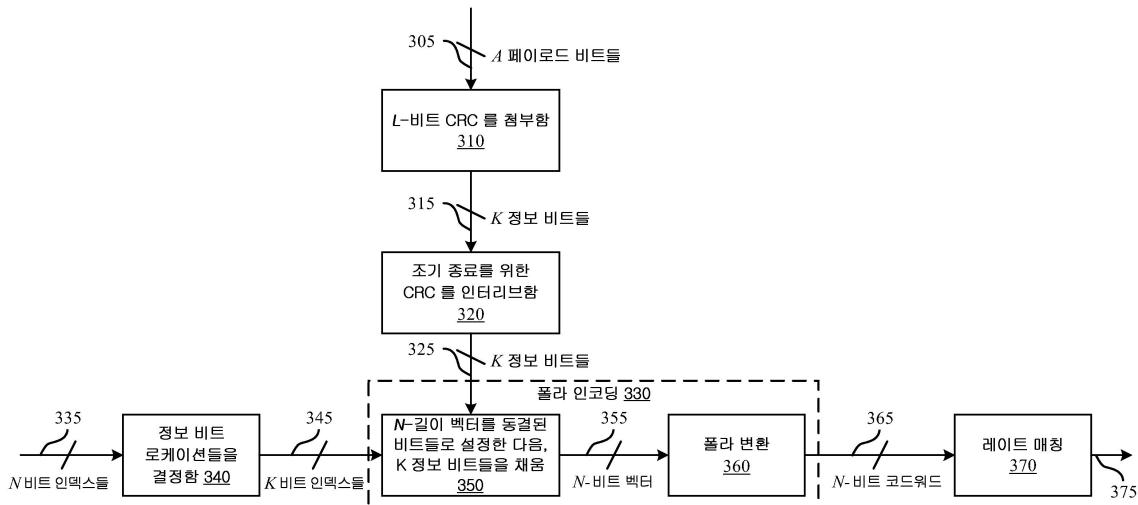

[0086] 도 3 은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 폴라-인코딩 프로세스 (300) 의 예를 나타낸다. 폴라-인코딩 프로세스 (300) 는 예를 들어, 도 2 을 참조하여 상기 설명된 바와 같은 인코더 (210) 에 의해 수행될 수도 있다. 인코더 (210) 는 무선 디바이스, 이를 테면, 도 1 을 참조하여 설명된 바와 같이 기지국 (105) 또는 UE (115) 의 컴포넌트일 수도 있다. 폴라-인코딩 프로세스 (300) 는 수신 디바이스에서 블라인드 디코딩시에 보조하기 위해 페이로드 사이즈를 나타내는 비트 벡터 조작을 포함할 수도 있다.

[0087] 305 에서, 인코더는 데이터 페이로드에 대응하는 다수의 페이로드 비트들 (A) 을 수신할 수도 있다. 예를 들어, 디바이스는 페이로드 비트들에 의해 표현되는 메모리로부터의 정보를 인코더로 전송할 수도 있다. 이 정보는 코드워드로 인코딩되어 수신 디바이스에 송신될 수도 있다.

[0088] 310 에서, 인코더는 L-비트 CRC 를 생성하여 A 개의 페이로드 비트들에 첨부하여 K 정보 비트들의 세트를 형성 할 수도 있다. 일부 경우들에, 인코더는 CRC 비트들 대신에 또는 이들에 더하여, 다른 형태들의 패리티 비트들을 사용할 수도 있다. CRC 비트들을 결정하기 위해, 인코더는 페이로드 비트들에 대해 CRC 동작을 수행 할 수도 있다. 이 CRC 동작은 수신 디바이스에 또한 알려질 수 있어, 코드워드를 디코딩하는 수신 디바이스 가 동일한 CRC 동작을 사용하여 디코딩 프로세스가 성공적이였는지의 여부를 결정할 수 있게 한다. 일부 CRC 동작들에서, 생성된 CRC 비트들은 페이로드에서의 선두 제로들에 의해 영향을 받지 않을 수도 있다.

[0089] 315 에서, 인코더는 K 개의 정보 비트들 (예를 들어, A 개의 페이로드 비트들 및 L 개의 CRC 비트들을 포함함) 을 인터리버에 선택적으로 전달할 수도 있다. 320 에서, 인터리버는 (예를 들어, 디코더에서 조기 종료를 지원하기 위해) 페이로드 비트들 전반에 걸쳐 CRC 비트들의 부분들을 인터리브할 수도 있다. 예를 들어, 24-비트 CRC 에 대해, 6-비트 CRC 는 정보 비트들을 통해 대략 1/4 정도에 위치될 수도 있고, 다른 6-비트 CRC 는 정보 비트들을 통해 1/2 정도에 위치될 수도 있고 나머지 12-비트 CRC 는 정보 비트들의 끝에 위치될 수도 있다. 325 에서, 인터리버는 인터리브된 K 정보 비트들을 폴라-인코딩 프로세스 (330) 에 전달할 수도 있다.

[0090] K 개의 정보 비트들에 더하여, 폴라-인코딩 프로세스 (330) 는 정보 비트들에 대한 비트 채널들에 대응하는 K 비트 인덱스들을 수신할 수도 있다. 예를 들어, 335 에서, 인코더는 코드워드의 길에 대응하는 다수의 비트 인덱스들 (N) 을 수신할 수도 있다. 340 에서, 인코더는 코드워드 (K) 내에서 인코딩하기 위해 비트 인덱스 들의 수 (N) 및 정보 비트들의 수에 기초하여 정보 비트 로케이션들을 결정할 수도 있다. 예를 들어, 인코 더는 다수의 N, K 페어들에 대한 N 개의 총 비트 채널들 내에서 K 개의 최대 신뢰성 비트 채널들을 나타내는 테이블을 메모리에 저장할 수도 있다. 다른 경우들에, 인코더는 N 및 K 값들을 입력하는 것에 기초하여 폴라 코드에 대한 최대 신뢰성 비트 채널들을 결정하는 기능을 포함할 수도 있다. 345 에서, 인코더는 이들 K 개의 최대 신뢰성 비트 채널들에 대응하는 K 비트 인덱스들을 폴라-인코딩 프로세스 (330) 로 전달할 수도 있다.

[0091] 350 에서, 인코더는 N-길이 비트 벡터의 각각의 비트를 동결된 비트 값 (예를 들어, 0) 으로 설정할 수도 있다. 대안적으로, 인코더는 비트 벡터의 제 1 의 N-K 비트들을 동결된 비트 값으로 설정할 수도 있다. 어느 경우에도, 인코더는 정보 비트들로 비트 벡터를 채울 수 있다. 예를 들어, 비트 인덱스가 N-K 동결된 비트 들을 채우는 것으로 시작하여, 인코더가 정보 비트들의 제 1 비트를 비트 벡터에 삽입할 수도 있고, 최종 정보 비트가 N-길이 비트 벡터의 최종 비트 인덱스에 삽입될 때까지 정보 비트들을 비트 벡터에 삽입하는 것을 계속 할 수도 있다.

[0092] 상이한 페이로드 사이즈들의 블라인드 검출을 지원하기 위해, 인코더는 하나 이상의 기법들을 사용하여 이 비트 벡터를 수정할 수도 있다. 예를 들어, 인코더는 페이로드 사이즈 A 또는 정보 비트들의 수 (K) 에 대응하는 마스킹 값 또는 벡터를 사용하여 A 페이로드 비트들, L 패리티 비트들, N-K 동결된 비트들 또는 이들 비트들의 임의의 조합을 스크램블할 수도 있다 (예를 들어, 정보 비트들의 수는 페이로드 사이즈 및 구성된 수의 CRC 비트들 (L) 에 목시적으로 기초한다). 다른 예에서, (예를 들어, 인터리버에서 또는 폴라-인코딩 프로세스 (330) 동안에) 인코더는 비트 벡터에서의 동결된 비트들 뒤에 하나 이상의 CRC 비트들을 위치시킬 수도 있고, 여기서, CRC 비트들의 적어도 하나는 동결된 비트들과는 상이한 비트 값을 갖는다 (예를 들어, 동결된 비트들이 0 의 비트 값을 가지면 1 의 비트 값을 갖는다). 또 다른 예들에서, 인코더는 동결된 비트들과는 상이한 비

트 값 (예를 들어, 동결된 비트들이 0 의 비트 값을 가지면 1 의 비트 값) 을 갖는 추가적인 비트를 동결된 비트들 뒤에 삽입할 수도 있거나, 또는 동결된 비트들과는 상이한 비트 값 (예를 들어, 동결된 비트들이 0 의 비트 값을 가지면 1 의 비트 값) 을 갖도록 페이로드 비트들을 배열할 수도 있다. 이들 기법들 어느 것에도, 단독으로 또는 조합하여, 인코더는 비트 벡터 또는 비트 벡터 내의 비트들의 순서가 페이로드 사이즈 또는 정보 비트들의 수를 표시하도록 비트 벡터를 수정할 수도 있다.

[0093] 355 에서, 인코더는 이 수정된 N-비트 비트 벡터를 폴라-인코딩 동작에 전송할 수도 있고, 여기서 인코더는 N-비트 벡터에 대해 폴라 변환 (360) 을 수행할 수도 있다. 예를 들어, 폴라 변환 (360) 은 비트 벡터의 N 비트들을 폴라 코드의 N 개의 비트 채널들에 배정할 수도 있고, K 정보 비트들은 345 에서 수신된 K 비트 인덱스들에 따라 최대 신뢰성 채널들에 배정된다. 이들 비트 채널 배정들에 기초하여, 인코더는 코드워드 내에서 송신할 비트들을 결정하기 위해 (예를 들어, F 및 G 동작을 구현하는) 분극화 변환을 사용하여 비트들을 변화할 수도 있다. 이 분극화 변환은 비트 채널들에 대한 상이한 신뢰도들을 가져올 수도 있다.

[0094] 365 에서, 인코더는 폴라-인코딩 프로세스 (330) 로부터 초래되는 N-비트 코드워드를 레이트 매칭 프로세스 (370) 로 전송할 수도 있다. 레이트 매칭 프로세스 (370) 는 특정 코딩 레이트에서 송신을 위하여 코드워드를 수정할 수도 있다. 레이트 매칭 프로세스 (370) 에 후속하여, 코드워드는 375 에서 송신기로 전송될 수도 있다. 송신기는 코드워드를 채널을 통하여 수신 디바이스로 송신할 수도 있다. 일부 경우들에 (예를 들어, 수신 디바이스는 송신 디바이스로부터의 코드워드를 이전에 수신하지 않은 경우 또는 송신 디바이스가 송신을 위하여 페이로드 사이즈를 수정한 경우), 수신 디바이스는 코드워드를 사용하여 송신되는 페이로드의 사이즈를 결정하기 위해 블라인드 디코딩 프로세스에서, N, K 또는 N, A 가설들을 사용할 수도 있다. 비트 벡터 (예를 들어, 비트 벡터의 순서 또는 비트 벡터의 컨텐츠) 에 대한 수정에 기초하여, 수신 디바이스는 페이로드에서의 선두 제로 비트들과 무관하게 수신된 코드워드의 페이로드 사이즈를 정확하게 결정할 수도 있다.

[0095] 도 4a, 도 4b 및 도 4c 는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 페이로드 사이즈 표시들 (400) 의 예들을 나타낸다. 페이로드 사이즈 표시들 (400) 은 상이한 페이로드 사이즈들의 블라인드 검출을 위하여 비트 벡터들에 통합될 수도 있다. 이들 페이로드 사이즈 표시들 (400) 은 단일 폴라 디코딩 프로세스에 기초하여 페이로드 사이즈의 디코더에 의한 결정을 용이하게 할 수도 있다.

[0096] 도 4a 는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 페이로드 사이즈 표시 (400-a) 의 예를 나타낸다. 페이로드 사이즈 표시 (400-a) 는 정보 비트들 (415-a) 을 포함하고, 이는 페이로드 비트들 (405-a) 및 페이로드 비트들 (405-a) 과 연관된 패리티 비트들 (예를 들어, CRC 비트들 (410-a)) 을 포함한다. 정보 비트들 (415-a) 은 비트 벡터를 형성하기 위해 동결된 비트들 (420-a) 과 결합될 수도 있다. (예를 들어, 도 2 및 도 3 에 대하여 설명된 바와 같은) 인코더는 페이로드 사이즈를 표시하기 위해 페이로드 사이즈에 기초하여 이 비트 벡터를 수정할 수도 있다.

[0097] 예를 들어, 인코더는 페이로드 사이즈들의, (예를 들어, 페이로드 사이즈 마스크 (430) 로서 지칭된) 마스킹 벡터들 또는 값들로의 맵핑을 포함할 수도 있다. 일부 경우들에, 인코더는 메모리에 테이블을 저장할 수도 있고, 페이로드 사이즈는 대응하는 페이로드 사이즈 마스크 (430) 에 나타낸다. 일부 예들에서, 이 맵핑은 코드워드 사이즈, CRC 비트들 (410-a) 의 수, 또는 이들의 일부 조합에 추가로 기초할 수도 있다. 인코더는 페이로드 사이즈에 기초하여 페이로드 사이즈 마스크 (430) 를 결정할 수도 있고, 결정된 페이로드 사이즈 마스크 (430) 를 사용하여 비트 벡터에 대해 마스킹 또는 스크램블링 동작 (425) 을 수행할 수도 있다. 예를 들어, 마스킹 또는 스크램블링 동작 (425) 은 배타적 or (XOR) 연산의 예일 수도 있다. 페이로드 사이즈 마스크 (430) 의 사이즈에 따라, 이 마스킹 또는 스크램블링 동작 (425) 은 비트별 동작으로서 수행될 수도 있거나 또는 비트 벡터의 부분들 상에서 수행될 수도 있다. 페이로드 사이즈 마스크 (430) 의 사이즈는 가능한 페이로드 사이즈들의 수에 의존할 수도 있다 (예를 들어, 인코더가 2 개의 가능한 페이로드 사이즈 구성들을 지원하면, 인코더는 하나의 비트 페이로드 사이즈 마스크 (430) 를 통합할 수도 있고, 여기서 0 의 값을 갖는 마스크는 하나의 페이로드 사이즈를 표시하고 1 의 값을 갖는 마스크는 다른 하나의 페이로드 사이즈를 표시한다).

추가적으로 또는 대안적으로, 페이로드 사이즈 마스크 (430) 의 사이즈는 스크램블링 또는 마스킹을 위해 (예를 들어, 벡터-투-벡터 마스킹 또는 스크램블링 동작 (425) 이 수행되기 위하여) 비트들의 수에 의존할 수도 있다. 일부 경우들에, 인코더는 마스킹 또는 스크램블링 동작 (425) 을 동결된 비트들 (420-a), 페이로드 비트들 (405-a), CRC 비트들 (410-a), 또는 이들 비트들의 임의의 조합 중 하나 이상에 대해 마스킹 또는 스크램블링 동작 (425) 을 수행할 수도 있다. 인코더는 폴라 코드를 사용하여 코드워드를 생성하기 위해 이 마

스킹 또는 스크램블링 비트 벡터를 사용할 수도 있다.

[0098] 코드워드 (예를 들어, 블라인드 검출 프로세스에서 후보 코드워드로서) 를 수신하는 수신 디바이스는 블라인드 디코딩을 위한 폴라 디코더로 코드워드를 전송할 수도 있다. 폴라 디코더는 코드워드에 대해 수신된 LLR들에 기초하여 디코딩된 LLR들을 결정할 수도 있고 이들 디코딩된 LLR들에 기초하여 소프트 또는 하드 비트 결정을 행할 수도 있다. 이들 디코딩된 LLR들을 각각은 수정된 비트 벡터의 비트에 대응할 수도 있다. 디코딩된 LLR들을 결정하기 위해 디코더는 N, K 가설을 추정할 수도 있다. 디코더는 구성된 수의 CRC 비트들 (410-a) 에 기초하여 추정된 페이로드 사이즈를 결정하기 위해 K 값의 가설들을 사용할 수도 있다. 디코더는 메모리에 페이로드 사이즈의, 페이로드 사이즈 마스크들 (430) 에 대한 동일한 맵핑을 포함할 수도 있다.

이 맵핑을 사용하여, 디코더는 추정된 페이로드 사이즈에 대응하는 페이로드 사이즈 마스크 (430) 를 선택할 수도 있고, 선택된 페이로드 사이즈 마스크 (430) 를 사용하여, 디코딩된 LLR들에 대한 하드 비트 결정들을 디마스킹 또는 디스크램블링할 수도 있다. 디마스킹된 또는 디스크램블링된 비트가 (예를 들어, 페이로드 비트들 (405-a) 및 CRC 비트들 (410-a) 에 기초하여) CRC를 통과하면, 디코더는 정확한 페이로드 사이즈가 추정되었다고 결정할 수도 있다. 이들 기법들을 사용하여, 디코더는 페이로드 비트들 (405-a) 이 동결된 비트들 (예를 들어, 선두 0 비트들) 과 동일한 비트 값을 갖는 선두 비트들을 포함하는 경우에도, 정확한 데이터 페이로드 (예를 들어, 페이로드 비트들 (405-a)) 를 결정할 수도 있다.

[0099] 도 4b 는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 페이로드 사이즈 표시 (400-b) 의 예를 나타낸다. 페이로드 사이즈 표시 (400-b) 는 페이로드 비트들 (405-b) 및 페이로드 비트들 (405-b) 과 연관된 (예를 들어, 페이로드 비트들 (405-b) 에 기초하여 결정된) CRC 비트들 (410-b) 양쪽을 포함할 수도 있는 정보 비트들 (415-b) 을 포함한다. 정보 비트들 (415-b) 은 비트 벡터를 형성하기 위해 동결된 비트들 (420-b) 과 결합될 수도 있다. (예를 들어, 도 2 및 도 3 에 대하여 설명된 바와 같은) 인코더는 페이로드 사이즈를 표시하기 위해 이 비트 벡터 내에서 정보 비트들 (415-b) 의 인터리빙을 수정할 수도 있다. 다음은 CRC 비트들에 대해 설명되어 있지만, 동작들은 임의의 유형의 패리티 또는 체크 비트들에도 적용함을 이해해야 한다.

[0100] 페이로드의 사이즈를 표시하기 위해, 인코더는 비트 벡터에서 페이로드 비트들 (405-b) 의 앞에 하나 이상의 CRC 비트들 (410-b) 을 위치시킬 수 있다. 예를 들어, CRC 비트들 (410-b) 은 페이로드 비트들 (405-b) 보다 더 낮은 비트 인덱스들에 배치될 수도 있다. 일부 경우들에, 인코더는 페이로드 비트들 (405-b) 전반에 걸쳐 CRC 비트들 (410-b) 을 인터리브할 수도 있지만, 이 비트 벡터에서 동결된 비트들 (420-b) 을 바로 뒤따르는 비트 인덱스들에 하나 이상의 CRC 비트들을 위치시킬 수도 있고, 여기서 이들 CRC 비트들의 적어도 하나는 디폴트 동결된 비트 값과는 상이한 비트 값을 갖는다. 이 적어도 하나의 CRC 비트-및 임의의 다른 인접하는 CRC 비트들-는 전방 로딩된 CRC 비트들로 지칭될 수도 있다. 인코더는 송신을 위한 코드워드를 인코딩하기 위해 비트 벡터에서의 비트의 배열을 사용할 수도 있다. 예를 들어, 인코더는 재정렬된 비트 벡터를 폴라 코드의 비트 채널들에 맵핑할 수도 있고, 여기서, 비트 벡터의 비트들은 오름차순 인덱스로 내림차순 신뢰도로의 폴라 코드의 비트 채널들에 맵핑될 수도 있다.

[0101] 수신 디바이스에서 코드워드를 디코딩하는 디코더는 전방 로딩된 CRC 비트들의 위치에 대한 하나 이상의 가설들에 기초하여 하나 이상의 CRC들을 수행할 수도 있다. 예를 들어, 인코더 및 디코더는 비트 벡터에서의 전방 로딩을 위한 CRC 비트들의 세트 넘버로 구성될 수도 있다. 수신된 LLR들, 전방 로딩된 CRC 비트들의 세트 넘버, 가능한 페이로드 사이즈 구성들, 또는 이들 파라미터들의 임의의 조합에 기초하여, 디코더는 전방 로딩된 CRC 비트들의 위치결정을 위한 상이한 가설들을 사용하여 CRC들을 수행할 수도 있다. 가설들이 CRC를 통과하면, 디코더는 추정된 전방 로딩된 CRC 위치가 정확하다고 결정할 수도 있다. 이러한 경우들에, 전방 로딩된 CRC의 위치결정에 기초하여, 디코더는 코드워드에서 인코딩된 정보 비트들 (415-b) 의 수, 이에 따라 페이로드 사이즈를 결정할 수도 있다. 이 식으로, 페이로드 비트들 (405-b) 또는 CRC 비트들 (410-a) 이 선두 0 비트들을 포함하는 경우에도, CRC 는 정확한 페이로드 사이즈가 디코더에서 추정되는 경우에만 통과할 것이다.

[0102] 도 4c 는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 페이로드 사이즈 표시 (400-c) 의 예를 나타낸다. 페이로드 사이즈 표시 (400-c) 는 페이로드 비트들 (405-c) 및 페이로드 비트들 (405-c) 과 연관된 CRC 비트들 (410-c) 양쪽을 포함할 수도 있는 정보 비트들 (415-c) 을 포함한다. (예를 들어, 도 2 및 도 3 에 대하여 설명된 바와 같은) 인코더는 페이로드 사이즈를 표시하기 위해 페이로드 비트들 (405-c) 을 수정할 수도 있다. 인코더는 이들 수정된 페이로드 비트들 (435) 을 CRC 비트들 (410-c) 과 결합하여 정보 비트들 (415-c) 을 형성할 수도 있고, 그리고 추가로 정보 비트

들 (415-c) 을 동결된 비트들 (420-c) 과 결합하여 인코딩을 위한 비트 벡터를 형성할 수도 있다.

[0103] 제 1 예에서, 인코더는 페이로드 비트들 (405-c) 의 전방에 단일 비트를 첨부하여 수정된 페이로드 비트들 (435) 을 형성할 수도 있다. 이 단일 비트는 동결된 비트들의 것과는 상이한 비트 값을 가질 수도 있다.

예를 들어, 디폴트 동결된 비트 값이 0 이면, 인코더는 비트 값 1 의 비트를 삽입할 수도 있다. 이 삽입된 비트는 비트 벡터 내에서 동결된 비트들 (420-c) 을 바로 뒤따르는 비트 인덱스에 위치될 수도 있다.

[0104] 일부 경우들에, 비트는 비트 벡터 내에서 최고 비트 인덱스에서의 동결된 비트의 값을 변경하는 것 (예를 들어, 0 에서부터 1 로 스위칭하는 것) 에 의해 삽입된다. 다른 경우들에, 인코더는 추가 비트에 기초하여 인코딩하기 위해 정보 비트들 (415-c) 의 수를 선택할 수도 있다. 예를 들어, 정보 비트들 (415-c) 의 수가 페이로드 비트들 (405-c) 의 수와 CRC 비트들 (410-c) 의 수의 합에 1 을 더한 것과 같을 수도 있다. 특정 예들에서, 인코더는 상이한 유형들의 메시지들을 표시하기 위해 이 추가 비트를 포함할 수도 있다. 예를 들어, 데이터 페이로드에 대응하는 정보에 따라, 인코더는 비트 벡터 내에서 정보 비트들 (415-c) 의 시작을 나타내는 비트를 삽입할지의 여부를 결정할 수도 있다.

[0105] 제 2 예에서, 인코더는 특정 값 (예를 들어, 1 의 값) 을 갖는 비트가 이 제 1 비트 위치에 있도록 페이로드 비트들 (405-c) 을 배열할 수도 있다. 예를 들어, 인코더는 "포맷 0/1A 구별을 위한 플래그" 필드를 나타내는 비트가 페이로드에 첫번째에 위치하도록 다운링크 제어 정보 (DCI) 포맷 1A 메시지에 대해 페이로드 비트들 (405-a) 을 배열할 수도 있다. 이 비트가 모든 DCI 포맷 1A 메시지들에 대해 1 의 비트 값을 가질 때, 인코더는 수정된 페이로드 비트들 (435) 에서의 제 1 비트가 1 이라고 보장할 수도 있다. 인코더는 그 다음 수정된 페이로드 비트들 (435) 을, 동결된 비트들 (420-c) 을 뒤따르는 비트 벡터에 위치시킬 수도 있어, 동결된 비트들 (420-c) 을 뒤따르는 비트 인덱스에 위치된 제 1 정보 비트 (415-c) 가 동결된 비트들 (420-c) 과는 상이한 비트 값을 가질 것이다. 이 비트는 비트 벡터 내에서 정보 비트들 (415-c) 의 시작을 마킹할 수도 있고 따라서 페이로드 사이즈를 표시할 수도 있다.

[0106] 수신 디바이스에서 코드워드를 디코딩하는 디코더는 동결된 비트의 것과는 상이한 값을 나타내는 디코딩된 LLR 에 기초하여 코드워드 내에서 정보 비트들 (415-c) 의 시작을 결정하도록 구성될 수도 있다 (예를 들어, 0 의 디폴트 동결된 비트 값에 대해, 디코더는 1 에 대응하는 LLR 을 식별할 때 정보 비트들 (415-c) 시작을 결정할 수도 있다). 비트 벡터 내에서 정보 비트들의 식별된 시작에 기초하여, 디코더는 페이로드의 사이즈를 정확하게 결정할 수도 있다.

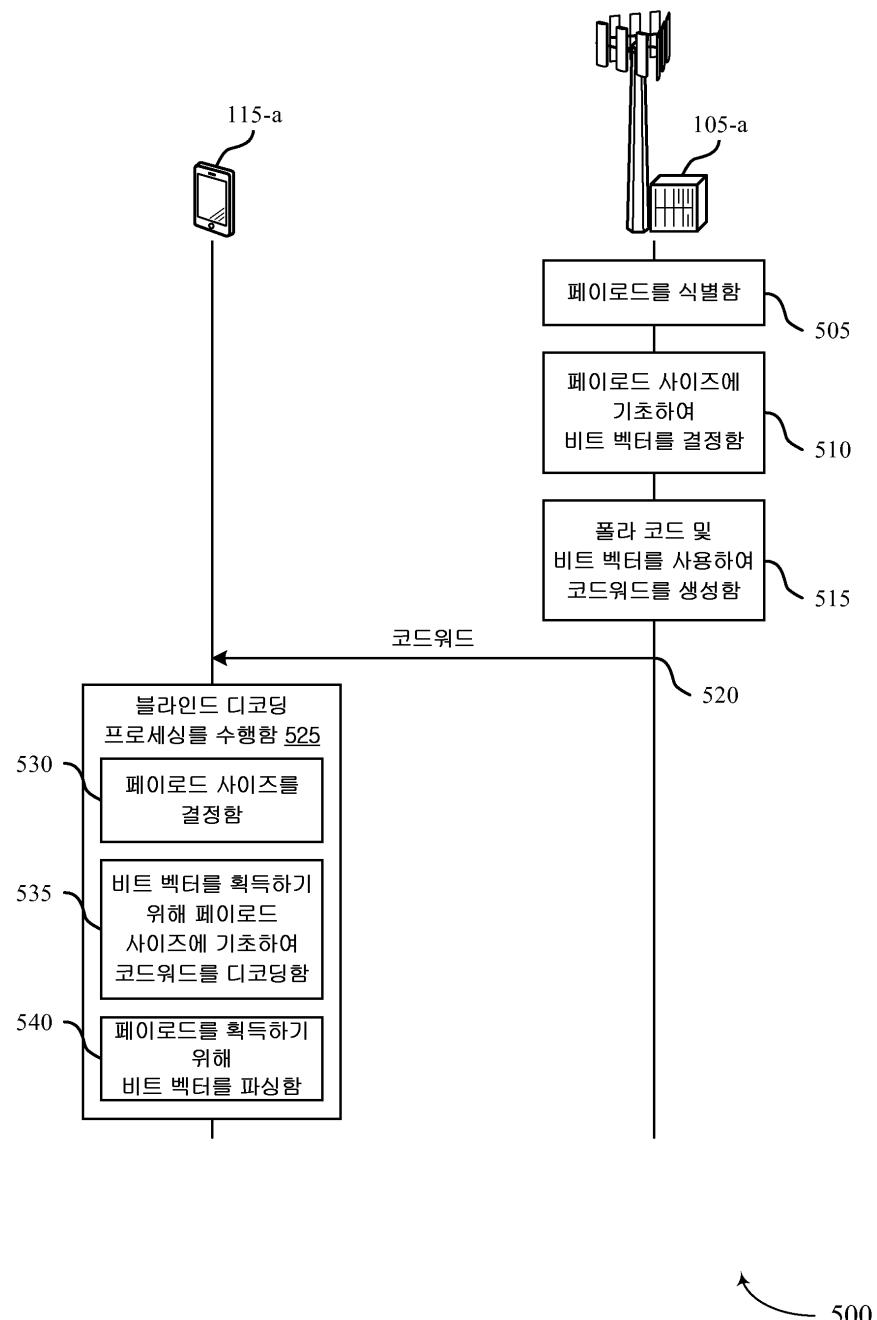

[0107] 도 5 는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 프로세스 플로우 (500) 의 예를 나타낸다. 프로세스 플로우 (500) 는 기지국 (105-a) 및 UE (115-a) 를 포함할 수도 있고, 이들은 도 1 을 참조하여 설명된 대응하는 디바이스들의 예들일 수도 있다. 예시된 바와 같이, 기지국 (105-a) 은 인코딩 프로세스를 수행할 수도 있고 UE (115-a) 는 다운링크에서 송신되는 코드워드에 대해 디코딩 프로세스를 수행할 수도 있다. 그러나, UE (115-a) 는 또한 인코딩 프로세스를 수행할 수도 있고 기지국 (105-a) 이 디코딩 프로세스를 수행할 수도 있음을 이해해야 한다. 추가적으로 또는 대안적으로, 설명된 폴라 코딩 프로세스들은 기지국들 (105) 또는 UE들 (115), 또는 다른 디바이스들 사이에서의 디바이스 투 디바이스 (D2D) 통신들, 또는 백홀 통신들에서 구현될 수도 있다.

[0108] 505 에서, 인코딩 디바이스 (예를 들어, 기지국 (105-a)) 는 송신을 위한 페이로드를 식별할 수도 있다. 페이로드는 페이로드 비트들의 순서화된 세트를 포함할 수도 있고, 이 세트는 동결된 비트 값과 같은 비트 값을 갖는 하나 이상의 선두 비트들 (예를 들어, 폴라 코드에 대한 디폴트 동결된 비트 값이 0 이면 0 의 비트 값을 갖는 선두 비트들) 을 포함할 수도 또는 포함하지 않을 수도 있다.

[0109] 510 에서, 기지국 (105-a) 은 페이로드의 사이즈에 기초하여 비트 벡터를 결정할 수도 있다. 비트 벡터는 페이로드 비트들의 세트를 포함할 수도 있고, 일부 경우들에 페이로드 비트들에 기초한 패리티 비트들, 동결된 비트들, 또는 이들 비트들의 일부 조합의 세트를 포함할 수도 있다. 비트 벡터에서의 비트들 또는 비트 벡터에서의 비트들의 순서는 페이로드 사이즈에 기초할 수도 있다. 예를 들어, 기지국 (105-a) 은 마스킹 벡터를 사용하여 비트 벡터에서 비트들을 스킁램블할 수도 있고, 여기서 마스킹 벡터는 페이로드 사이즈에 기초하여 결정된다. 다른 예에서, 기지국 (105-a) 은 비트 벡터의 최저 비트 인덱스에 패리티 비트들의 세트를 위치시킬 수도 있고 여기서, 페이로드 비트들은 비트 벡터의 상위 비트 인덱스들에 위치된다. 일부 경우들에, "최저" 비트 인덱스는 정보 비트 인덱스들 중에서 최저 비트 인덱스를 지칭할 수도 있고, 여기서 동결된 비트들은 "최저" 비트 인덱스보다 더 낮은 비트 인덱스들에 위치될 수도 있다. 또 다른 예에서, 기지국 (105-a) 은 비트 벡터에 초기 비트를 첨부할 수도 있고, 여기서 초기 비트는 디폴트 동결된 비트 값의 것과는 상이한 비

트 값을 갖는다. 대안적으로, 기지국 (105-a)은 비트 벡터의 초기 비트가 디폴트 동결된 비트 값의 것과는 상이한 비트 값을 갖도록, 페이로드 비트들 또는 패리티 비트들을 배열할 수도 있다. 위와 유사하게, "초기" 비트는 초기 정보 비트에 대응할 수도 있고, 여기서 동결된 비트들은 비트 벡터 내에서 "초기" 비트를 선행할 수도 있다.

[0110] 515에서, 기지국 (105-a)은 폴라 코드 및 비트 벡터를 사용하여 코드워드를 생성할 수도 있다. 예를 들어, 기지국 (105-a)은 폴라 코드의 비트 채널들에 비트 벡터의 비트들을 배정할 수도 있다. 520에서, 기지국 (105-a)은 생성된 코드워드를 송신할 수도 있다. 수신 디바이스 (예를 들어, UE (115-a))는 후보 코드워드로서 코드워드를 수신할 수도 있고, 후보 코드워드를 디코딩하려 시도할 수도 있다.

[0111] 525에서, UE (115-a)는 수신된 코드워드에 대해 블라인드 디코딩 프로세스를 수행할 수도 있다. 예를 들어, 530에서, UE (115-a)는 코드워드에 대한 페이로드 사이즈를 결정할 수도 있다. 535에서, UE (115-a)는 비트 벡터를 획득하기 위해 결정된 페이로드 사이즈에 기초하여 코드워드를 디코딩할 수도 있다. 일부 경우들에, 페이로드 사이즈를 결정하는 것 및 코드워드를 디코딩하는 것은 UE (115-a)가 하나 이상의 가설 페이로드 사이즈를 추정하는 것 및 가설 페이로드 사이즈가 정확하게 디코딩된 코드워드를 가져오는지를 결정하기 위한 체크들을 수행하는 것에 기초하여 발생할 수도 있다. 예를 들어, UE (115-a)는 가설 페이로드 사이즈에 대응하는 마스킹 벡터를 사용하여 코드워드의 LLR들에 대한 하드 비트 결정들을 디스크램블할 수도 있다. 디스크램블된 비트들이 CRC를 통과하면 (예를 들어, 디스크램블링이 성공적이면), UE (115-a)는 가설 페이로드 사이즈가 정확하다고 결정할 수도 있다. 다른 예에서, UE (115-a)는 비트 벡터 내에서 CRC 또는 패리티 비트들의 추정된 위치들에 기초하여 하나 이상의 CRC들 또는 패리티 체크들을 수행할 수도 있고 그리고 성공적인 CRC 또는 패리티 체크를 가져오는 위치결정에 기초하여 정확한 페이로드 사이즈를 결정할 수도 있다. 또 다른 예들에서, UE (115-a)는 디폴트 동결된 비트 값의 것과는 상이한 비트 값을 갖는 비트를 나타내는 LLR을 갖는 최소 신뢰성 비트 채널을 식별할 수도 있고, 이 비트 채널이 제 1 정보 비트 채널이라고 결정할 수도 있다. 이 결정에 기초하여, UE (115-a)는 페이로드 사이즈를 결정할 수도 있다. 540에서, UE (115-a)는 코드워드 내에서 인코딩된 페이로드 비트들을 식별하기 위해 결정된 페이로드 사이즈에 기초하여 획득된 비트 벡터를 파싱할 수도 있다.

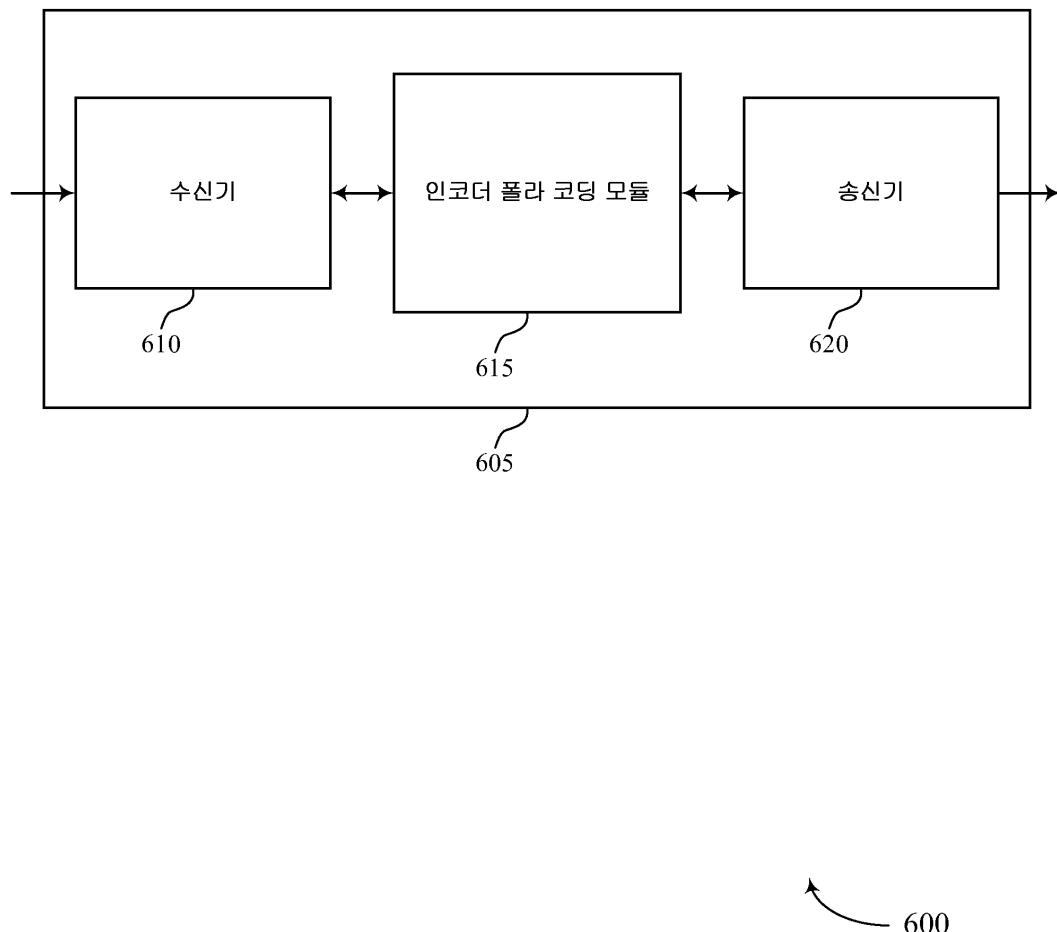

[0112] 도 6은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 무선 디바이스 (605)의 블록 다이어그램 (600)을 나타낸다. 무선 디바이스 (605)는 도 1 및 도 2을 참조하여 위에 설명된, 인코더를 포함하는 기지국 (105) 또는 UE (115)의 양태들의 일 예일 수도 있다. 무선 디바이스 (605)는 수신기 (610), 인코더 폴라 코딩 모듈 (615), 및 송신기 (620)를 포함할 수도 있다. 무선 디바이스 (605)는 프로세서를 또한 포함할 수도 있다. 이를 컴포넌트들의 각각은 (예를 들어, 하나 이상의 버스들을 통해) 서로 통신 상태에 있을 수도 있다.

[0113] 수신기 (610)는 정보, 이를 테면 다양한 정보 채널들 (예를 들어, 제어 채널들, 데이터 채널들, 및 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들에 관련된 정보 등)과 연관된 제어 정보, 패킷들, 또는 사용자 데이터를 수신할 수도 있다. 정보는 디바이스의 다른 컴포넌트들 상으로 전달될 수도 있다. 수신기 (610)는 도 9를 참조하여 설명된 트랜시버 (935)의 양태들의 예일 수도 있다. 수신기 (610)는 단일 안테나 또는 또는 안테나들의 세트를 활용할 수도 있다.

[0114] 인코더 폴라 코딩 모듈 (615)은 도 9를 참조하여 설명된 인코더 폴라 코딩 모듈 (915)의 양태들의 예일 수도 있다. 인코더 폴라 코딩 모듈 (615) 및/또는 그것의 다양한 서브 컴포넌트들 중 적어도 일부는 하드웨어, 프로세서에 의해 실행되는 소프트웨어, 펌웨어, 또는 이들의 임의의 조합으로 구현될 수 있다. 프로세서에 의해 실행된 소프트웨어로 구현되면, 인코더 폴라 코딩 모듈 (615) 또는 그의 다양한 서브-컴포넌트들의 적어도 일부의 기능들은 병용 프로세서, 디지털 신호 프로세서 (DSP), 주문형 집적 회로 (ASIC), 필드 프로그래밍 가능 게이트 어레이 (FPGA) 또는 다른 프로그래밍 가능 로직 디바이스, 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들, 또는 본 개시에서 설명된 기능들을 수행하도록 설계된 이들의 임의의 조합에 의해 실행될 수도 있다. 인코더 폴라 코딩 모듈 (615) 및/또는 그것의 다양한 서브컴포넌트들의 적어도 일부는, 기능들의 부분들이 하나 이상의 물리적 디바이스들에 의해 상이한 물리적 위치들에서 구현되도록 분산되는 것을 포함한다양한 포지션들에서 물리적으로 위치될 수도 있다. 일부 예들에서, 인코더 폴라 코딩 모듈 (615) 및/또는 그것의 다양한 서브-컴포넌트들의 적어도 일부는 본 개시의 다양한 양태들에 따른 별도의 그리고 별개의 컴포넌트일 수도 있다. 다른 예들에서, 인코더 폴라 코딩 모듈 (615) 및/또는 그것의 다양한 서브-컴포넌트들의 적어도 일부는 I/O 컴포넌트, 트랜시버, 네트워크 서버, 다른 컴퓨팅 디바이스, 본 개시에서 설명된 하나 이상의 다른 컴포넌트들, 또는 본 개시의 양태들에 따른 이들의 조합을 포함하지만 이에 한정되지 않는 하나 이상의

다른 하드웨어 컴포넌트들과 결합될 수도 있다.

[0115] 인코더 폴라 코딩 모듈 (615) 은 인코딩을 위한 페이로드의 페이로드 비트들의 세트를 식별하고, 페이로드 비트들의 세트를 포함하는 비트 벡터를 결정하는 것으로서, 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 페이로드의 사이즈에 적어도 부분적으로 기초하는, 비트 벡터를 결정하고, 비트 벡터를 사용하여 폴라-인코딩된 코드워드를 생성하고, 그리고 코드워드를 송신할 수도 있다.

[0116] 송신기 (620) 는 디바이스의 다른 컴포넌트들에 의해 생성된 신호들을 송신할 수도 있다. 일부 예들에서, 송신기 (620) 는 트랜시버 모듈에서 수신기 (610) 와 병치될 수도 있다. 예를 들어, 송신기 (620) 는 도 9 를 참조하여 설명된 트랜시버 (935) 의 양태들의 일 예일 수도 있다. 송신기 (620) 는 단일의 안테나 또는 안테나들의 세트를 활용할 수도 있다.

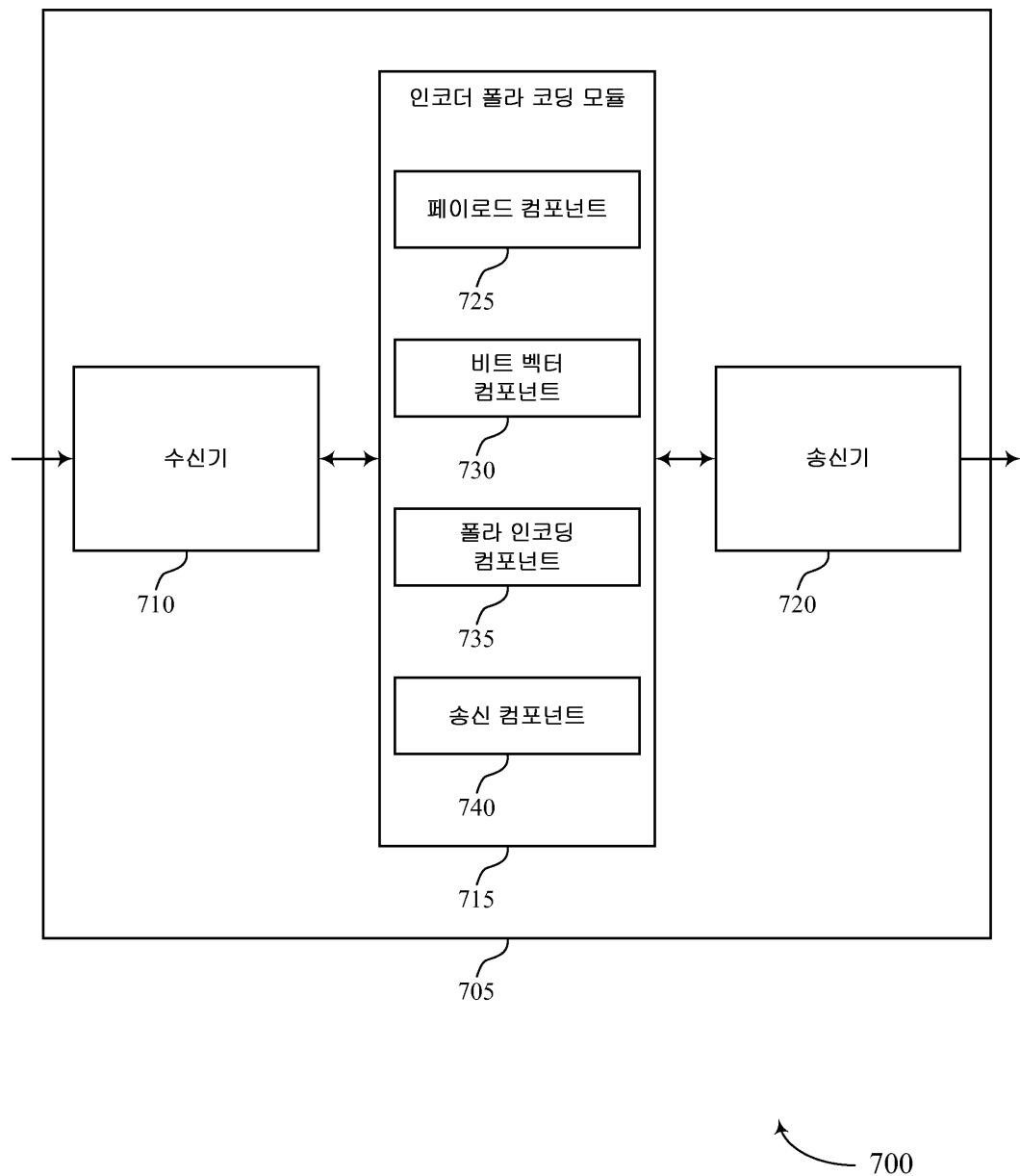

[0117] 도 7 은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 무선 디바이스 (705) 의 블록 다이어그램 (700) 을 나타낸다. 무선 디바이스 (705) 는 도 1, 도 2 및 도 6 을 참조하여 위에 설명된, (예를 들어, 인코더를 포함하는) 무선 디바이스 (605), 기지국 (105) 또는 UE (115) 의 양태들의 일 예일 수도 있다. 무선 디바이스 (705) 는 수신기 (710), 인코더 폴라 코딩 모듈 (715), 및 송신기 (720) 를 포함할 수도 있다. 무선 디바이스 (705) 는 프로세서를 또한 포함할 수도 있다. 이들 컴포넌트들의 각각은 (예를 들어, 하나 이상의 버스들을 통해) 서로 통신 상태에 있을 수도 있다.

[0118] 수신기 (710) 는 정보, 이를 테면 다양한 정보 채널들 (예를 들어, 제어 채널들, 데이터 채널들, 및 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들에 관련된 정보 등) 과 연관된 제어 정보, 패킷들, 또는 사용자 데이터를 수신할 수도 있다. 정보는 디바이스의 다른 컴포넌트들 상으로 전달될 수도 있다. 예를 들어, 수신기 (710) 는 도 9 를 참조하여 설명된 트랜시버 (935) 의 양태들의 일 예일 수도 있다. 수신기 (710) 는 단일 안테나 또는 또는 안테나들의 세트를 활용할 수도 있다.

[0119] 인코더 폴라 코딩 모듈 (715) 은 도 9 를 참조하여 설명된 인코더 폴라 코딩 모듈 (915) 의 양태들의 예일 수도 있다. 인코더 폴라 코딩 모듈 (715) 은 또한, 페이로드 컴포넌트 (725), 비트 벡터 컴포넌트 (730), 폴라-인코딩 컴포넌트 (735) 및 송신 컴포넌트 (740) 를 포함할 수도 있다.

[0120] 페이로드 컴포넌트 (725) 는 인코딩을 위한 페이로드의 페이로드 비트들의 세트를 식별할 수도 있다. 비트 벡터 컴포넌트 (730) 는 페이로드 비트들의 세트를 포함하는 비트 벡터를 결정할 수 있고, 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 페이로드의 사이즈에 적어도 부분적으로 기초한다. 일부 경우들에, 비트 벡터는 페이로드 비트들의 세트 및 페이로드 비트들의 세트와 연관된 패리티 비트들의 세트를 포함한다. 폴라-인코딩 컴포넌트 (735) 는 비트 벡터에 기초하여 폴라-인코딩된 코드워드를 생성할 수도 있다. 송신 컴포넌트 (740) 는 코드워드를 송신할 수도 있다.

[0121] 송신기 (720) 는 디바이스의 다른 컴포넌트들에 의해 생성된 신호들을 송신할 수도 있다. 일부 예들에서, 송신기 (720) 는 트랜시버 모듈에서 수신기 (710) 와 병치될 수도 있다. 예를 들어, 송신기 (720) 는 도 9 를 참조하여 설명된 트랜시버 (935) 의 양태들의 일 예일 수도 있다. 송신기 (720) 는 단일의 안테나 또는 안테나들의 세트를 활용할 수도 있다.

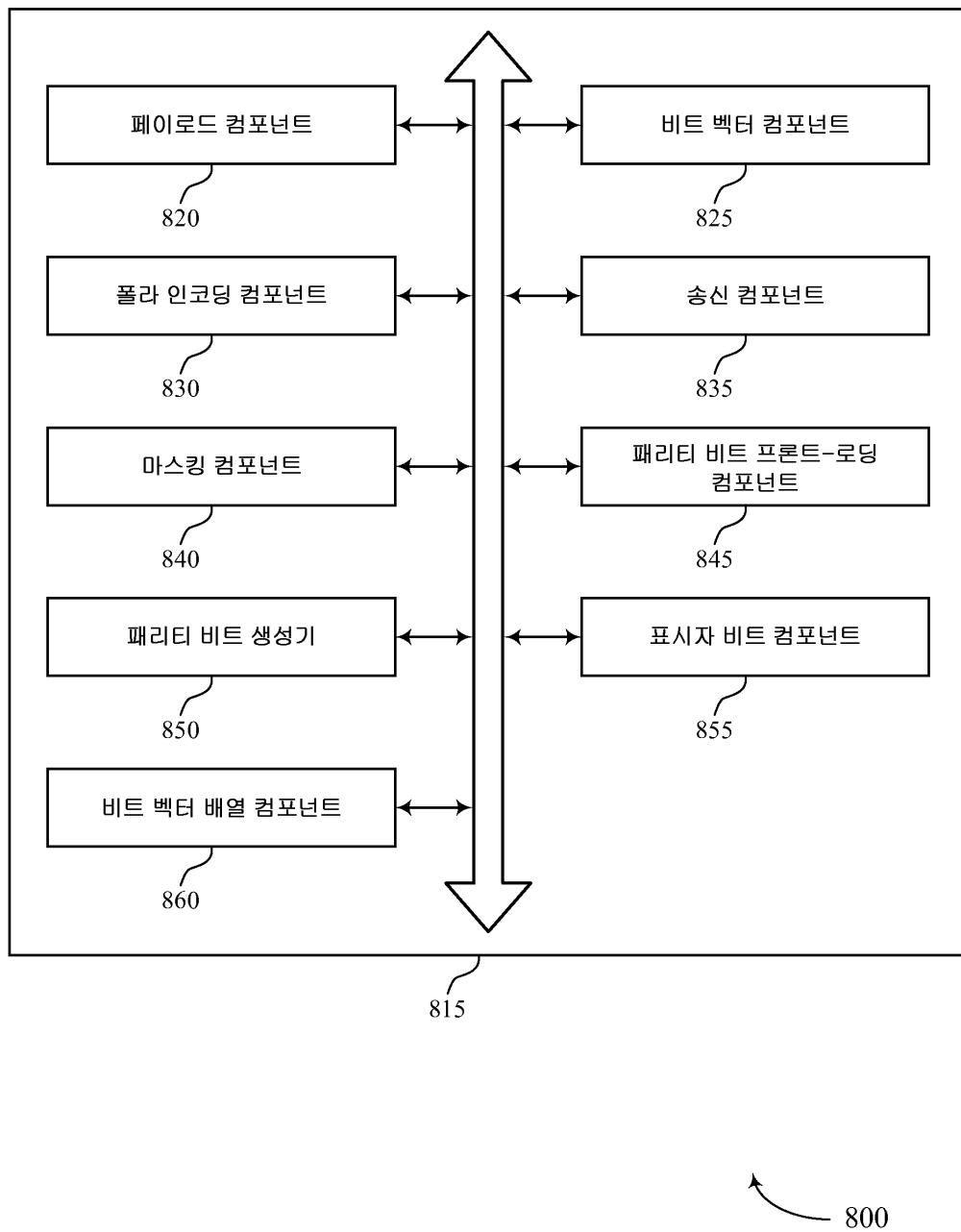

[0122] 도 8 은 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 인코더 폴라 코딩 모듈 (815) 의 블록 다이어그램 (800) 을 나타낸다. 인코더 폴라 코딩 모듈 (815) 은 도 6, 도 7, 및 도 9 를 참조하여 설명된 인코더 폴라 코딩 모듈 (615), 인코더 폴라 코딩 모듈 (715), 또는 인코더 폴라 코딩 모듈 (915) 의 양태들의 일 예일 수도 있다. 인코더 폴라 코딩 모듈 (815) 은 페이로드 컴포넌트 (820), 비트 벡터 컴포넌트 (825), 폴라-인코딩 컴포넌트 (830), 송신 컴포넌트 (835), 마스킹 컴포넌트 (840), 패리티 비트 프론트-로딩 컴포넌트 (845), 패리티 비트 생성기 (850), 표시자 비트 컴포넌트 (855), 및 비트 벡터 배열 컴포넌트 (860) 를 포함할 수도 있다. 이들 모듈들의 각각은 (예를 들어, 하나 이상의 버스들을 통해) 서로 직접 또는 간접적으로 통신할 수도 있다.

[0123] 페이로드 컴포넌트 (820) 는 인코딩을 위한 페이로드의 페이로드 비트들의 세트를 식별할 수도 있다. 비트 벡터 컴포넌트 (825) 는 페이로드 비트들의 세트를 포함하는 비트 벡터를 결정할 수 있고, 비트 벡터의 적어도 하나의 비트 또는 비트 순서는 페이로드의 사이즈에 적어도 부분적으로 기초한다. 일부 경우들에, 비트 벡터는 페이로드 비트들의 세트 및 페이로드 비트들의 세트와 연관된 패리티 비트들의 세트를 포함한다.

[0124] 폴라-인코딩 컴포넌트 (830) 는 비트 벡터에 기초하여 폴라-인코딩된 코드워드를 생성할 수도 있다. 송신

컴포넌트 (835) 는 코드워드를 송신할 수도 있다.

[0125] 마스킹 컴포넌트 (840) 는 페이로드 사이즈에 대응하는 마스킹 벡터를 결정할 수도 있고, 페이로드 비트들의 세트, 페이로드 비트들의 세트와 연관된 패리티 비트들의 세트, 동결된 비트들의 세트, 또는 이들의 조합을 마스킹 벡터로 스크램블링할 수도 있다. 일부 경우들에, 페이로드 비트들의 세트, 페이로드 비트들의 세트와 연관된 패리티 비트들의 세트, 동결된 비트들의 세트, 또는 이들의 조합을 마스킹 벡터로 스크램블링하는 것은 XOR 연산을 포함한다.

[0126] 일부 경우들에, 비트 벡터는 패리티 비트들의 세트를 포함할 수도 있다. 패리티 비트 프론트-로딩 컴포넌트 (845) 는 비트 벡터의 최저 인덱스에 패리티 비트들의 세트의 적어도 하나의 비트를 위치시킬 수도 있고 페이로드 비트들의 세트는 비트 벡터의 상위 인덱스들에 위치된다. 일부 경우들에, 패리티 비트 프론트-로딩 컴포넌트 (845) 는 페이로드 비트들의 세트 및 패리티 비트들의 세트를 폴라 코드의 정보 비트 채널들의 세트에 배정할 수도 있고, 패리티 비트들의 세트의 적어도 하나의 비트는 정보 비트 채널들의 세트의 최소 신뢰성 채널에 배정된다.

[0127] 패리티 비트 생성기 (850) 는 패리티 비트들의 세트를 생성하기 위해 페이로드 비트들의 세트에 패리티 기능을 적용할 수도 있다. 일부 경우들에, 패리티 비트들의 세트는 CRC 비트들의 세트를 포함한다.

[0128] 표시자 비트 컴포넌트 (855) 는 비트 벡터에 초기 비트를 첨부할 수 있으며, 초기 비트는 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함한다. 일부 경우들에, 초기 비트는 페이로드와 연관된 메시지 타입을 나타낸다.

[0129] 비트 벡터 배열 컴포넌트 (860) 는 비트 벡터의 초기 비트가 디폴트 동결된 비트 값에 대한 반대 비트 값을 포함하도록, 페이로드 비트들의 세트, 페이로드 비트들의 세트와 연관된 패리티 비트들의 세트, 동결된 비트들의 세트, 또는 이들의 조합을 배열할 수도 있다.

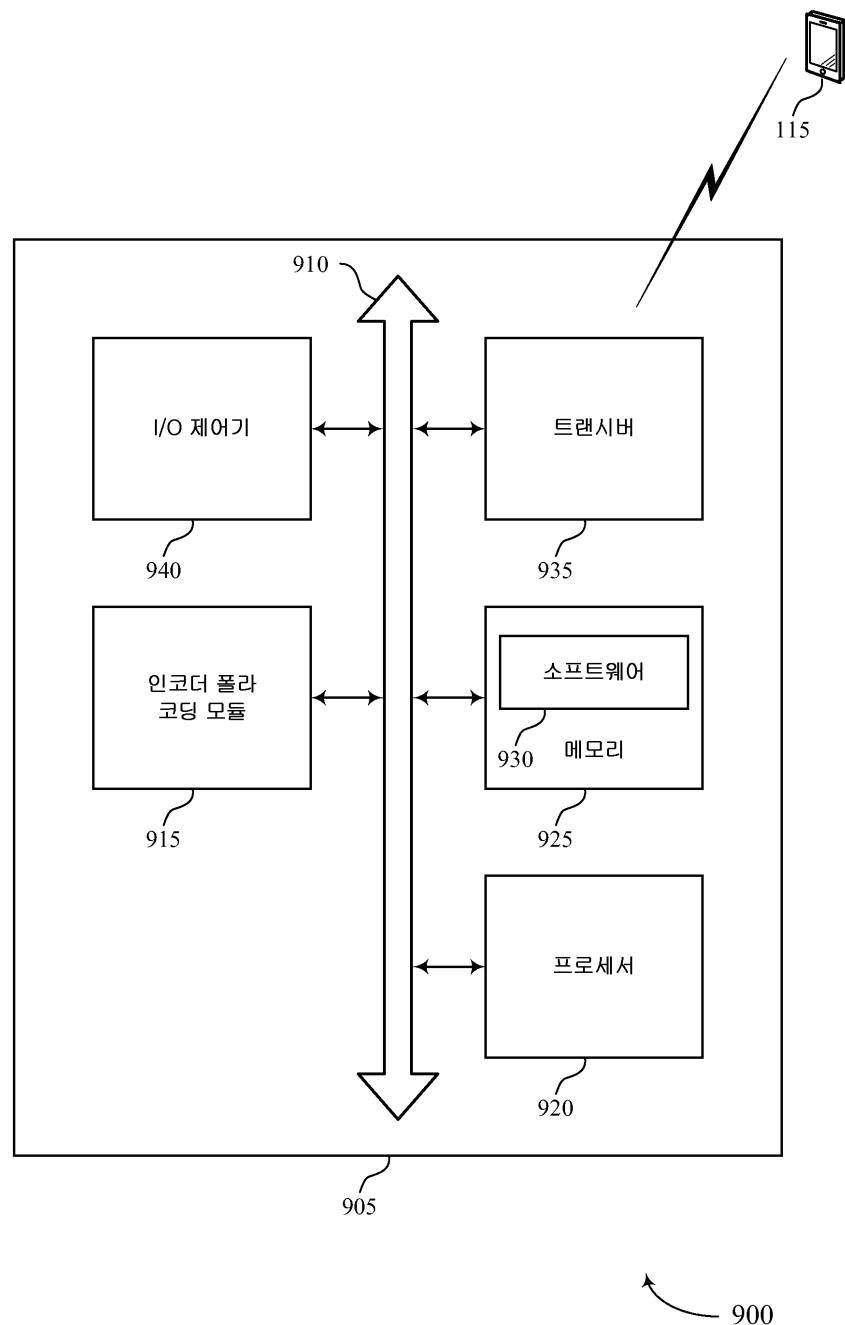

[0130] 도 9 는 본 개시의 양태들에 따라 상이한 페이로드 사이즈들의 블라인드 검출을 위한 폴라 코딩 기법들을 지원하는 디바이스 (905) 를 포함하는 시스템 (900) 의 블록 다이어그램을 나타낸다. 디바이스 (905) 는 예를 들어 도 1, 도 2, 도 6 및 도 7 을 참조하여, 앞서 설명된 것과 같은 무선 디바이스 (605), 무선 디바이스 (705) 또는 기지국 (105) 또는 UE (115) 또는 인코더의 컴포넌트들을 포함하거나 그 일 예일 수도 있다. 디바이스 (905) 는 인코더 폴라 코딩 모듈 (915), 프로세서 (920), 메모리 (925), 소프트웨어 (930), 트랜시버 (935), 및 I/O 제어기 (940) 를 포함하는, 통신들을 송신하고 수신하기 위한 컴포넌트들을 포함하는 양방향 음성 및 데이터 통신들을 위한 컴포넌트들을 포함할 수도 있다. 이들 컴포넌트들은 하나 이상의 버스들 (예를 들어, 버스 (910)) 를 통해 전자 통신할 수도 있다.