(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4380552号

(P4380552)

(45) 発行日 平成21年12月9日(2009.12.9)

(24) 登録日 平成21年10月2日(2009.10.2)

(51) Int.Cl.

F 1

G09F 9/00 (2006.01)

G09F 9/00 342Z

G02F 1/1343 (2006.01)

G02F 1/1343

G02F 1/1368 (2006.01)

G02F 1/1368

請求項の数 5 (全 19 頁)

(21) 出願番号

特願2005-28587 (P2005-28587)

(22) 出願日

平成17年2月4日(2005.2.4)

(65) 公開番号

特開2006-215305 (P2006-215305A)

(43) 公開日

平成18年8月17日(2006.8.17)

審査請求日

平成17年12月14日(2005.12.14)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100107836

弁理士 西 和哉

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100140774

弁理士 大浪 一徳

(74) 代理人 100095728

弁理士 上柳 雅善

(74) 代理人 100107261

弁理士 須澤 修

最終頁に続く

(54) 【発明の名称】アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1方向に延びるように形成された第1の配線と第2方向に延びるように形成された第2の配線とのうちのいずれか一方の配線が交差部において分断された格子パターンの配線を基板上に形成する第1工程と、

前記交差部及び前記格子パターンの配線の一部上に絶縁膜と半導体膜とからなる積層部を形成する第2工程と、

前記積層部上に前記交差部において分断された前記一方の配線を電気的に連結させる導電層を形成し、且つ、前記半導体膜を介して前記格子パターンの配線と電気的に接続される画素電極を形成する第3工程と、を有し、

前記第1工程は、前記格子パターンの配線を区画する第1のバンクをフォトリソグラフィ法により形成する工程と、前記第1のバンクによって区画された領域に液滴吐出法により前記格子パターンの配線を形成する工程とを含み、

前記第3工程は、前記導電層と前記画素電極とを区画する第2のバンクを液滴吐出法により形成する工程と、前記第2のバンクによって区画された領域に液滴吐出法により前記導電層と前記画素電極とを形成する工程とを含むことを特徴とする、アクティブマトリクス基板の製造方法。

## 【請求項 2】

前記第1工程は、ソース配線と、前記ソース配線と交差して配置されたゲート配線とを含む前記格子パターンの配線を基板上に形成する工程であり、

前記第2工程は、前記ソース配線と前記ゲート配線との交差部上及び前記ゲート配線の一部であるゲート電極上に、絶縁膜と半導体膜とを順に積層してなる積層部を形成する工程であり、

前記第3工程は、前記ソース配線と前記ゲート配線との交差部に形成された前記積層部上に、前記交差部を挟んで分断された前記一方の配線を電気的に連結させる前記導電層を形成し、前記ゲート電極上に形成された前記積層部の一方の端部上に、前記半導体膜と前記ソース配線とを電気的に接続するソース電極を形成し、前記ゲート電極上に形成された前記積層部の他方の端部上にドレイン電極を形成し、前記ドレイン電極の端部に前記ドレイン電極と電気的に接続される前記画素電極を形成する工程であり、

前記第3工程は、

10

前記導電層の形成位置に第1の開口部を有し、前記ソース電極の形成位置に第2の開口部を有し、前記ドレイン電極の形成位置に第3の開口部を有し、前記画素電極の形成位置に前記第4の開口部を有する前記第2のバンクを液滴吐出法により形成する工程と、

前記第1の開口部と前記第2の開口部と前記第3の開口部に、第1の導電性微粒子を含む第1のインクを配置する工程と、

前記第3の開口部と前記第4の開口部との間に配置された前記第2のバンクを除去する工程と、

前記第2のバンクが除去された部分と前記第4の開口部とに、前記第1の導電性微粒子とは異なる第2の導電性微粒子を含む第2のインクを配置する工程と、を含むことを特徴とする、請求項1記載のアクティブマトリクス基板の製造方法。

20

### 【請求項3】

前記格子パターンの配線は、前記ソース配線と、前記ゲート配線と、前記ゲート配線と平行に配置された容量線とからなり、前記ソース配線が前記ゲート配線との交差部及び前記容量線との交差部において分断されていることを特徴とする、請求項2記載のアクティブマトリクス基板の製造方法。

### 【請求項4】

前記第2のバンクは、撥液性の材料によって形成されることを特徴とする、請求項1～3のいずれかの項に記載のアクティブマトリクス基板の製造方法。

### 【請求項5】

前記第1のバンクと前記第2のバンクの形成材料は、無機質の材料を含むことを特徴とする、請求項1～4のいずれかの項に記載のアクティブマトリクス基板の製造方法。

30

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、アクティブマトリクス基板の製造方法、アクティブマトリクス基板、電気光学装置並びに電子機器に関するものである。

#### 【背景技術】

#### 【0002】

ノートパソコン、携帯電話などの携帯機器の普及に伴い、薄くて軽量な液晶表示装置等が幅広く用いられている。この種の液晶表示装置等は、上基板及び下基板間に液晶層を挟持したものとなっている。

40

前記下基板（アクティブマトリクス基板）の一例を、図17に示す。同図に示すように、下基板1は、ガラス基板2と、このガラス基板2上に互いに交差するよう配線されたゲート走査電極3及びソース電極4と、同じくガラス基板2上に配線されたドレイン電極5と、このドレイン電極5に接続された画素電極（ITO）6と、ゲート走査電極3とソース電極4との間に介在された絶縁層7と、薄膜半導体からなるTFT（Thin Film Transistor）8とを備えて構成されている。下基板1における各金属配線の形成においては、例えば、特許文献1に示されるように、ドライプロセスとフォトリソエッティングを組み合わせた工程を複数回繰り返す手法が用いられている。

#### 【特許文献1】特開平9-506553号公報

50

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

しかしながら、上述した技術では、ドライプロセスとフォトリソエッティングを組み合わせた処理を複数回行っているので、材料費や管理費やかさみやすく、また歩留まりも上げにくいという問題がある。すなわち、予め導電膜を塗布した基板上にレジストと呼ばれる感光材を塗布し、回路パターンを照射して現像し、レジストパターンに応じて導電膜をエッチングすることで薄膜の配線パターンを形成している。また、真空装置などの大掛かりな設備と複雑な工程を必要とし、材料使用効率も数%程度でそのほとんどを廃棄せざるを得ず、製造コストが高い。したがって、製品コストの低価格化が要請されている液晶表示装置等にとっては、ドライプロセスとフォトリソエッティングを組み合わせた処理の回数を減らすことが大きな課題となっている。

本発明は、以上のような点を考慮してなされたもので、ドライプロセスとフォトリソエッティングを組み合わせた工程の回数を低減することができるアクティブマトリクス基板の製造方法等を提供することを目的とする。

**【課題を解決するための手段】****【0004】**

上記の目的を達成するために、本発明は、以下の構成を採用している。

本発明のアクティブマトリクス基板の製造方法は、画素電極を有するアクティブマトリクス基板の製造方法であって、前記画素電極の形成工程は、前記画素電極を区画するバンクを液滴吐出法により形成する工程と、前記バンクによって区画された領域に導電材料を含む機能液を配置する工程とを含むことを特徴とする。

この方法によれば、必要となるフォト工程の回数を従来の4回（ゲートライン形成プロセス、TFT素子形成プロセス、ソースライン形成プロセス、画素電極形成プロセス）から3回（ゲートライン形成プロセス、TFT素子形成プロセス、ソースライン形成プロセス、）に減らすことができる。

**【0005】**

本発明のアクティブマトリクス基板の製造方法は、第1方向又は第2方向のいずれか一方の配線が交差部において分断された格子パターンの配線を基板上に形成する第1工程と、前記交差部及び前記配線の一部上に絶縁膜と半導体膜とからなる積層部を形成する第2工程と、前記積層部上に前記分断された配線を電気的に連結させる導電層、及び前記半導体膜を介して前記配線と電気的に接続される画素電極を形成する第3工程と、を有し、前記導電層及び前記画素電極の形成工程は、前記導電層及び前記画素電極を区画するバンクを液滴吐出法により形成する工程と、前記バンクによって区画された領域に導電材料を含む機能液を配置する工程とを含むことを特徴とする。

この方法によれば、必要となるフォト工程は第1工程と第2工程の2回のみであり、従来に比べて、その回数を半分に減らすことができる。

**【0006】**

本発明においては、前記配線は、ソース線、ゲート線、及びゲート線に沿って略直線状に伸びる容量線からなり、前記ソース線が前記交差部において分断されているものとすることができる。

この方法によれば、これらの配線の接触が回避されるので、これらの配線を同一面上に同時に形成することが可能となる。

**【0007】**

本発明においては、前記配線は液滴吐出法により形成されるものとすることができます。

この方法によれば、更にフォト工程の回数を減らすことができる。

**【0008】**

本発明においては、前記第2工程は、前記容量線上に前記交差部において分断された積層部を形成する工程を含むものとすることができます。

この方法によれば、容量線上の積層部が交差部上の積層部と接触していないので、交差

10

20

30

40

50

部の積層部上に形成される導電層を流れる電流が、容量線の積層部に流れ込んでしまうことを回避することができる。

#### 【0009】

本発明においては、前記第2工程は、前記半導体膜にハーフ露光処理を施してスイッチング素子を形成する工程を含むものとすることができる。

この方法によれば、容易にスイッチング素子を形成することができる。

#### 【0010】

本発明においては、前記バンクは、撥液性の材料によって形成されるものとすることができる。

この方法によれば、バンク自体が撥液性を有するため、バンク表面を改めて撥液処理する必要がなくなり、工程の簡素化が図られる。 10

#### 【0011】

本発明においては、前記バンクの形成材料は、無機質の材料を含むものとすることができます。

この方法によれば、バンクの形成材料が無機質の材料を含むことから、バンクの耐熱性が高く、しかもバンクと基板との間の熱膨張率の差が小さい。そのため、機能液の乾燥時の熱などによるバンクの劣化が抑制され、膜パターンが良好な形状で形成される。

#### 【0012】

本発明のアクティブマトリックス基板は、前述した本発明のアクティブマトリックス基板の製造方法を用いて製造されたことを特徴とする。 20

この構成によれば、低コストのアクティブマトリックス基板を得ることができる。

#### 【0013】

本発明の電気光学装置は、前述した本発明のアクティブマトリックス基板を備えることを特徴とする。また、本発明の電子機器は、前述した本発明の電気光学装置を備えることを特徴とする。

これらの構成によれば、低コストのアクティブマトリックス基板を用いることができるので、電気光学装置、電子機器のコストを抑えることができる。

#### 【発明を実施するための最良の形態】

#### 【0014】

以下、本発明のアクティブマトリックス基板の製造方法、アクティブマトリックス基板、電気光学装置並びに電子機器の実施形態について図を参照して説明する。 30

#### 【0015】

##### <アクティブマトリックス基板>

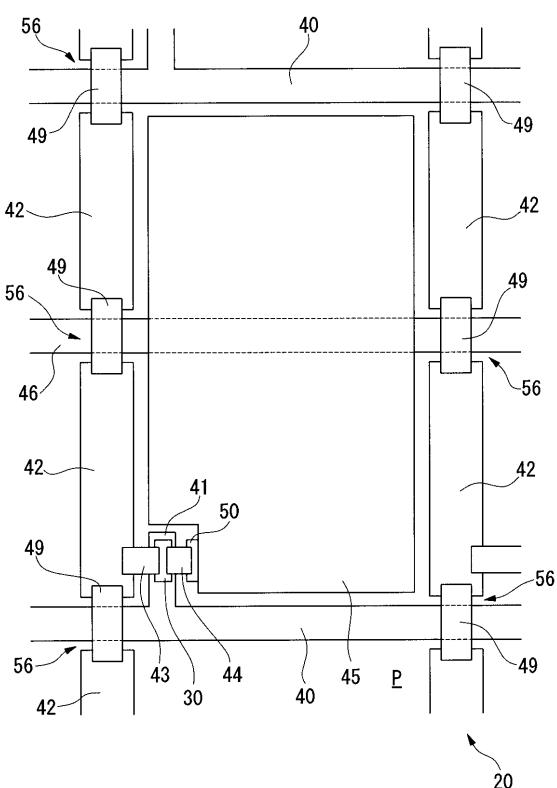

図1は、本実施形態に係るアクティブマトリックス基板の一部を拡大した図である。

アクティブマトリックス基板20上は、格子状に配線されたゲート配線40とソース配線42とを備える。すなわち、複数のゲート配線40がX方向（第1方向）に延びるように形成され、ソース配線42がY方向（第2方向）に延びるように形成されている。

また、ゲート配線40には、ゲート電極41が接続され、ゲート電極41上に絶縁層を介してTFT30が配置される。一方、ソース配線42には、ソース電極43が接続され、ソース電極43の一端は、TFT（スイッチング素子）30に接続する。 40

そして、ゲート配線40とソース配線42に囲まれた領域には、画素電極45が配置され、ドレイン電極44を介してTFT30に接続する。

また、アクティブマトリックス基板20上には、ゲート配線40と略平行するように、容量線46が配線される。容量線46は、画素電極45及びソース配線42の下層に絶縁層を介して配置される。

なお、ゲート配線40、ゲート電極41、ソース配線42、容量線46は、同一の面上に形成される。

#### 【0016】

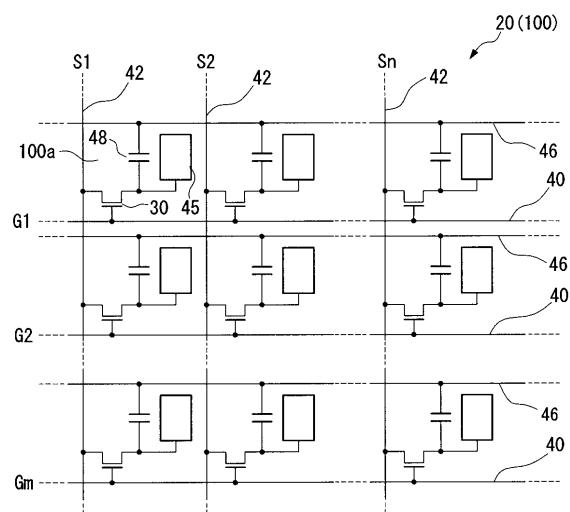

図2は、アクティブマトリックス基板20の等価回路図であって、液晶表示装置に用了いた場合である。 50

アクティブマトリックス基板 20 を液晶表示装置に用いた場合には、画像表示領域には複数の画素 100a がマトリックス状に構成される。これらの画素 100a の各々には、画素スイッチング用の TFT30 が形成されており、画素信号 S1、S2、…、Sn を供給するソース配線 42 がソース電極 43 を介して TFT30 のソースに電気的に接続されている。ソース配線 42 に供給する画素信号 S1、S2、…、Sn は、この順に線順次で供給してもよく、相隣接する複数のソース配線 42 同士に対して、グループ毎に供給するようにしてよい。

また、TFT30 のゲートには、ゲート配線 40 がゲート電極 41 を介して電気的に接続されている。そして、所定のタイミングで、ゲート配線 40 にパルス的に走査信号 G1、G2、…、Gm をこの順に線順次で印加するように構成されている。

10

#### 【0017】

画素電極 45 は、TFT30 のドレインにドレイン電極 44 を介して電気的に接続されている。そして、スイッチング素子である TFT30 を一定期間だけオン状態とすることにより、ソース配線 42 から供給される画素信号 S1、S2、…、Sn を各画素に所定のタイミングで書き込む。このようにして画素電極 45 を介して液晶に書き込まれた所定レベルの画素信号 S1、S2、…、Sn は、図 17 に示す対向基板 120 の対向電極 121 との間で一定期間保持される。

なお、保持された画素信号 S1、S2、…、Sn がリークするのを防ぐために、容量線 46 によって、画素電極 45 と対向電極 121 との間に形成される液晶容量と並列に蓄積容量 48 が付加されている。例えば、画素電極 45 の電圧は、ソース電圧が印加された時間よりも 3 枝も長い時間だけ蓄積容量 48 により保持される。これにより、電荷の保持特性は改善され、コントラスト比の高い液晶表示装置 100 を実現することができる。

20

#### 【0018】

<アクティブマトリックス基板の製造方法>

次に、アクティブマトリックス基板 20 の製造方法について説明する。

アクティブマトリックス基板 20 は、基板 P 上に格子パターンの配線を形成する第 1 工程と、積層部 35 を形成する第 2 工程と、画素電極 45 等を形成する第 3 工程により製造される。本実施形態においては、ソース電極 43、ドレイン電極 44、画素電極 45 の形成工程に本発明の膜パターンの形成方法が適用される。

以下、各工程毎に詳細に説明する。

30

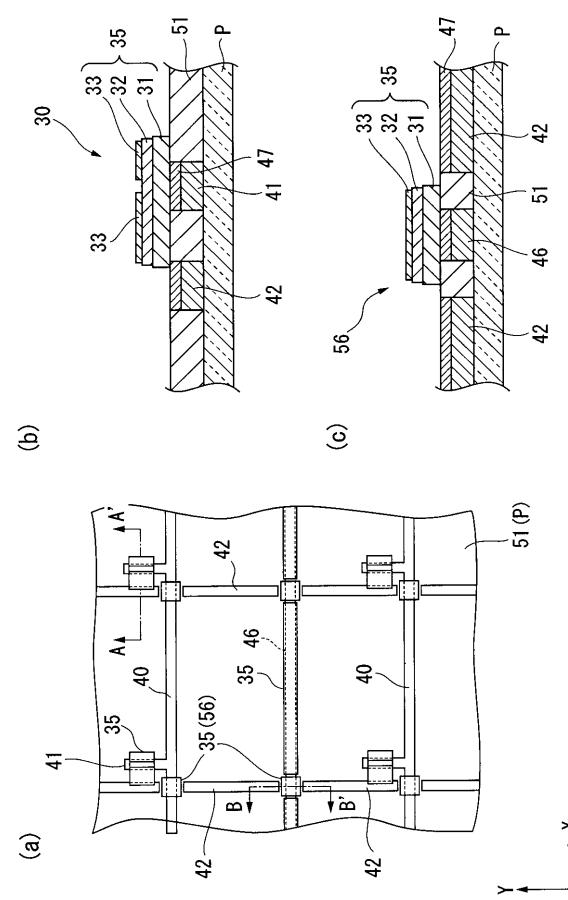

#### 【0019】

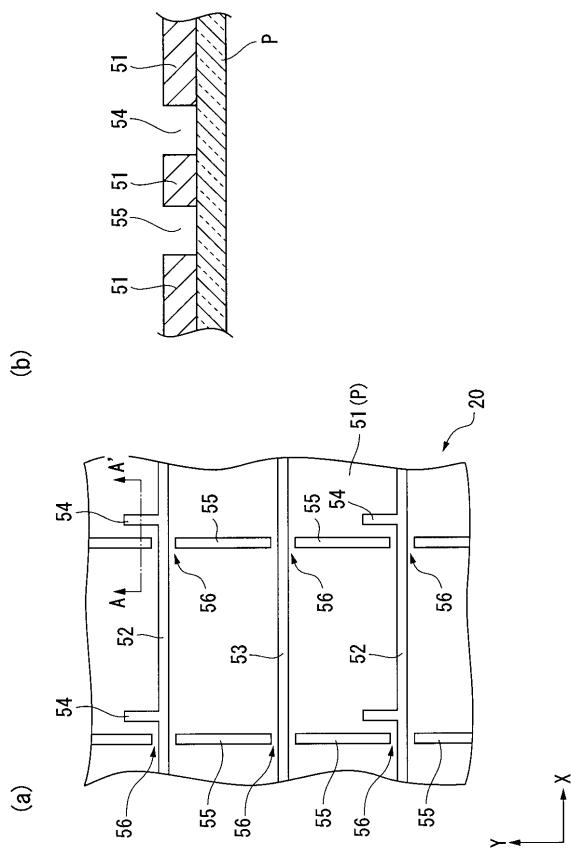

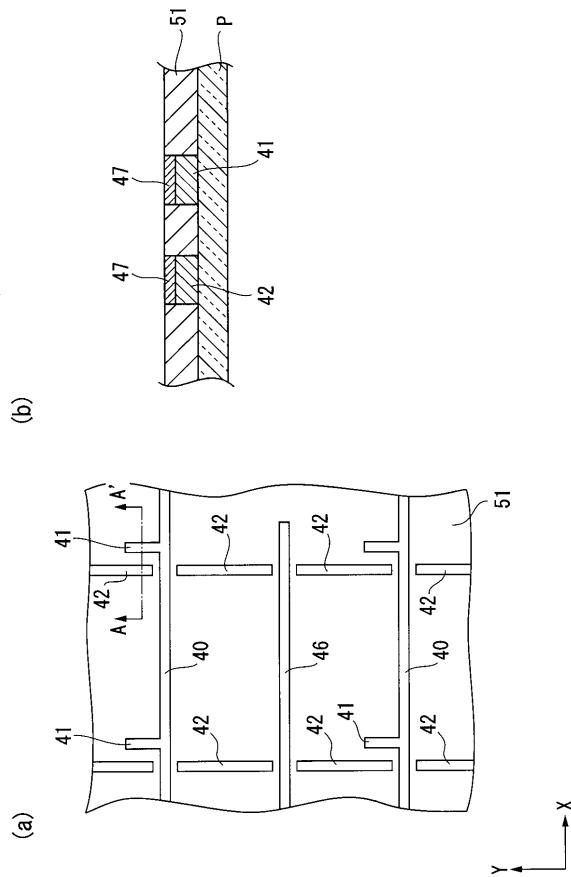

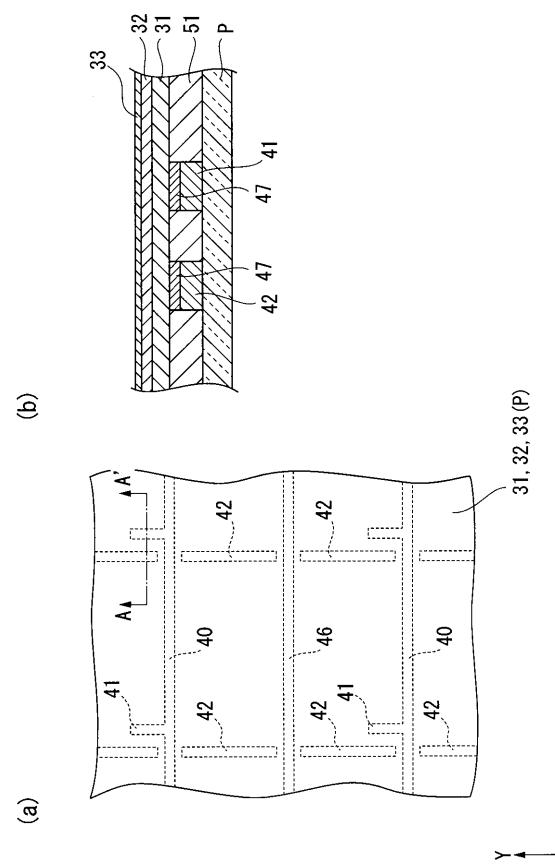

(第 1 工程：配線形成)

図 3、図 4 は、第 1 工程である配線形成工程を説明する図である。なお、図 3 (b)、図 4 (b) は、それぞれ図 3 (a)、図 4 (a) における A-A' 線に沿う断面図である。

ゲート配線 40 やソース配線 42 等の格子パターンの配線が形成される基板 P としては、ガラス、石英ガラス、Si ウエハ、プラスチックフィルム、金属板など各種の材料を用いることができる。また、これら各種の素材基板の表面に半導体膜、金属膜、誘電体膜、有機膜などが下地層として形成されたものも含む。

そして、まず、図 3 に示すように、基板 P 上に、絶縁性の材料からなるバンク 51 が形成される。バンクは、後述する配線用インクを基板 P の所定位置に配置するためのものである。

40

具体的には、図 3 (a) に示すように、洗浄した基板 P の上面に、格子パターンの配線の形成位置に対応した複数の開口部 52、53、54、55 を有するバンク 51 をフォトソグラフィ法に基づいて形成する。

#### 【0020】

バンク 51 の材料としては、例えば、アクリル樹脂、ポリイミド樹脂、オレフィン樹脂、メラミン樹脂などの高分子材料が用いられる。また、耐熱性等を考慮して、無機質の材料を含むものとすることもできる。無機質のバンク材料としては、例えば、ポリシラザン、ポリシロキサン、シロキサン系レジスト、ポリシラン系レジスト等の骨格にケイ素を含

50

む高分子無機材料や感光性無機材料、シリカガラス、アルキルシロキサンポリマー、アルキルシリセスキオキサンポリマー、水素化アルキルシリセスキオキサンポリマー、ポリアリールエーテルのうちいずれかを含むスピノングラス膜、ダイヤモンド膜、及びフッ素化アモルファス炭素膜、などが挙げられる。さらに、無機質のバンク材料として、例えば、エアロゲル、多孔質シリカ、などを用いてもよい。ポリシラザンと光酸発生剤とを含む感光性ポリシラザン組成物のように感光性を有する材料とした場合には、レジストマスクが不要になるため、好適である。なお、バンク51には、開口部52, 53, 54, 55内に配線パターン用インクを良好に配置するために、撥液処理が施される。撥液処理として、CF<sub>4</sub>プラズマ処理等（フッ素成分を有するガスを用いたプラズマ処理）を施す。なお、CF<sub>4</sub>プラズマ処理等に代えて、バンク51の素材自体に予め撥液成分（フッ素基等）を充填しておいても良い。

#### 【0021】

バンク51により形成される開口部52, 53, 54, 55は、ゲート配線40やソース配線42等の格子パターンの配線に対応している。すなわち、バンク51の開口部52, 53, 54, 55に配線用インクを配置することにより、ゲート配線40やソース配線42等の格子パターンの配線が形成される。

具体的には、X方向に延びるように形成された開口部52, 53は、ゲート配線40、容量線46の形成位置に対応する。そして、ゲート配線40の形成位置に対応する開口部52には、ゲート電極41の形成位置に対応する開口部54が接続している。また、Y方向に延びるように形成された開口部55は、ソース配線42の形成位置に対応する。なお、Y方向に延びる開口部55は、X方向に延びる開口部52, 53と交差しないように、交差部56において分断されるように形成される。

#### 【0022】

次いで、後述する液滴吐出装置IJによって、導電性微粒子を含む配線用インクを開口部52, 53, 54, 55内に吐出・配置して、基板上にゲート配線40やソース配線42等からなる格子パターンの配線を形成する。

配線用インクは、導電性微粒子を分散媒に分散させた分散液や有機銀化合物や酸化銀ナノ粒子を溶媒（分散媒）に分散した溶液からなるものである。導電性微粒子としては、例えば、金、銀、銅、錫、鉛等の金属微粒子の他、これらの酸化物、並びに導電性ポリマーや超電導体の微粒子などが用いられる。これらの導電性微粒子は、分散性を向上させるために表面に有機物などをコーティングして使うこともできる。

#### 【0023】

導電性微粒子の粒径は1nm以上0.1μm以下であることが好ましい。0.1μmより大きいと、後述する液滴吐出ヘッドのノズルに目詰まりが生じるおそれがある。また、1nmより小さいと、導電性微粒子に対するコーティング剤の体積比が大きくなり、得られる膜中の有機物の割合が過多となる。

#### 【0024】

分散媒としては、上記の導電性微粒子を分散できるもので、凝集を起こさないものであれば特に限定されない。例えば、水の他に、メタノール、エタノール、プロパノール、ブタノールなどのアルコール類、n-ヘプタン、n-オクタン、デカン、ドデカン、テトラデカン、トルエン、キシレン、シメン、デュレン、インデン、ジベンテン、テトラヒドロナフタレン、デカヒドロナフタレン、シクロヘキシルベンゼンなどの炭化水素系化合物、またエチレングリコールジメチルエーテル、エチレングリコールジエチルエーテル、エチレングリコールメチルエチルエーテル、ジエチレングリコールジメチルエーテル、ジエチレングリコールジエチルエーテル、ジエチレングリコールメチルエチルエーテル、1,2-ジメトキシエтан、ビス(2-メトキシエチル)エーテル、p-ジオキサンなどのエーテル系化合物、さらにプロピレンカーボネート、-ブチロラクトン、N-メチル-2-ピロリドン、ジメチルホルムアミド、ジメチルスルホキシド、シクロヘキサンなどの極性化合物を例示できる。これらのうち、微粒子の分散性と分散液の安定性、また液滴吐出法（インクジェット法）への適用の容易さの点で、水、アルコール類、炭化水素系化合物

10

20

30

40

50

、エーテル系化合物が好ましく、より好ましい分散媒としては、水、炭化水素系化合物を挙げることができる。

#### 【0025】

導電性微粒子の分散液の表面張力は、例えば0.02 N/m以上0.07 N/m以下の範囲内であることが好ましい。インクジェット法にて液体を吐出する際、表面張力が0.02 N/m未満であると、インク組成物のノズル面に対する濡れ性が増大するため飛行曲りが生じやすくなり、0.07 N/mを超えるとノズル先端でのメニスカスの形状が安定しないため吐出量や、吐出タイミングの制御が困難になる。表面張力を調整するため、上記分散液には、基板との接触角を大きく低下させない範囲で、フッ素系、シリコーン系、ノニオン系などの表面張力調節剤を微量添加するとよい。ノニオン系表面張力調節剤は、液体の基板への濡れ性を向上させ、膜のレベリング性を改良し、膜の微細な凹凸の発生などの防止に役立つものである。上記表面張力調節剤は、必要に応じて、アルコール、エーテル、エステル、ケトン等の有機化合物を含んでもよい。

#### 【0026】

分散液の粘度は、例えば1 mPa·s以上50 mPa·s以下であることが好ましい。インクジェット法を用いて液体材料を液滴として吐出する際、粘度が1 mPa·sより小さい場合にはノズル周辺部がインクの流出により汚染されやすく、また粘度が50 mPa·sより大きい場合は、ノズル孔での目詰まり頻度が高くなり円滑な液滴の吐出が困難となる。

#### 【0027】

基板Pに配線用インクを吐出した後には、分散媒の除去のため、必要に応じて乾燥処理、焼成処理を行う。

乾燥処理は、例えば基板Pを加熱する通常のホットプレート、電気炉などによる加熱処理によって行うことができる。例えば180 加熱を60分間程度行う。

焼成処理の処理温度は、分散媒の沸点(蒸気圧)、微粒子の分散性や酸化性等の熱的挙動、コーティング剤の有無や量、基材の耐熱温度などを考慮して適宜決定される。例えば、有機物からなるコーティング剤を除去するために、約250 で焼成することが必要である。

このような乾燥・焼成処理により、導電性微粒子間の電気的接触が確保され、導電性膜に変換される。

#### 【0028】

なお、ゲート配線40やソース配線42等の配線上には、金属保護膜47を成膜させてよい。金属保護膜47は、銀や銅等からなる導電性膜の(エレクトロ)マイグレーション現象等を抑制するための薄膜である。金属保護膜47を形成する材料としては、ニッケルが好ましい。なお、ニッケルからなる金属保護膜47も液滴吐出法によって基板P上に配置されて形成される。

#### 【0029】

以上の工程により、基板P上には、図4に示すように、バンク51及び格子パターンの配線からなる層が形成される。

#### 【0030】

ところで、液滴吐出法の吐出技術としては、帯電制御方式、加圧振動方式、電気機械変換式、電気熱変換方式、静電吸引方式などが挙げられる。帯電制御方式は、材料に帯電電極で電荷を付与し、偏向電極で材料の飛翔方向を制御してノズルから吐出させるものである。また、加圧振動方式は、材料に例えば30 kg/cm<sup>2</sup>程度の超高压を印加してノズル先端側に材料を吐出させるものであり、制御電圧をかけない場合には材料が直進してノズルから吐出され、制御電圧をかけると材料間に静電的な反発が起り、材料が飛散してノズルから吐出されない。また、電気機械変換方式は、ピエゾ素子(圧電素子)がパルス的な電気信号を受けて変形する性質を利用したもので、ピエゾ素子が変形することによって材料を貯留した空間に可撓物質を介して圧力を与え、この空間から材料を押し出してノズルから吐出せるものである。

10

20

30

40

50

## 【0031】

また、電気熱変換方式は、材料を貯留した空間内に設けたヒータにより、材料を急激に気化させてバブル（泡）を発生させ、バブルの圧力によって空間内の材料を吐出させるものである。静電吸引方式は、材料を貯留した空間内に微小圧力を加え、ノズルに材料のメニスカスを形成し、この状態で静電引力を加えてから材料を引き出すものである。また、この他に、電場による流体の粘性変化を利用する方式や、放電火花で飛ばす方式などの技術も適用可能である。液滴吐出法は、材料の使用に無駄が少なく、しかも所望の位置に所望の量の材料を的確に配置できるという利点を有する。なお、液滴吐出法により吐出される液状材料（流動体）の一滴の量は、例えば1～300ナノグラムである。

## 【0032】

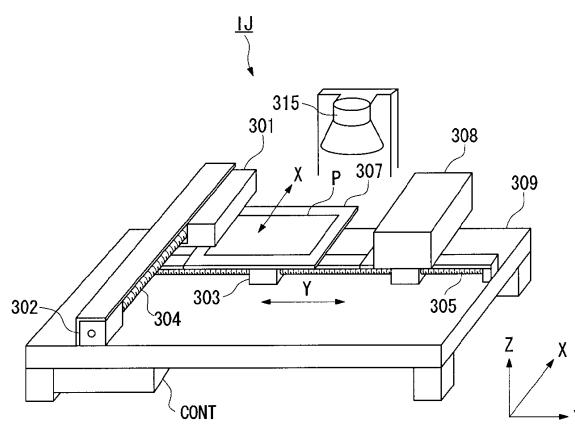

格子パターンの配線を形成する際に用いられる液滴吐出装置IJとしては、例えば、図5に示す液滴吐出装置IJが用いられる。

液滴吐出装置（インクジェット装置）IJは、液滴吐出ヘッドから基板Pに対して液滴を吐出（滴下）するものであって、液滴吐出ヘッド301と、X方向駆動軸304と、Y方向ガイド軸305と、制御装置CONTと、ステージ307と、クリーニング機構308と、基台309と、ヒータ315とを備えている。ステージ307は、この液滴吐出装置IJによりインク（液体材料）を設けられる基板Pを支持するものであって、基板Pを基準位置に固定する不図示の固定機構を備えている。

## 【0033】

液滴吐出ヘッド301は、複数の吐出ノズルを備えたマルチノズルタイプの液滴吐出ヘッドであり、長手方向とY軸方向とを一致させている。複数の吐出ノズルは、液滴吐出ヘッド301の下面にY軸方向に並んで一定間隔で設けられている。液滴吐出ヘッド301の吐出ノズルからは、ステージ307に支持されている基板Pに対して、上述した導電性微粒子を含むインクが吐出される。

## 【0034】

X方向駆動軸304には、X方向駆動モータ302が接続されている。X方向駆動モータ302はステッピングモータ等であり、制御装置CONTからX方向の駆動信号が供給されると、X方向駆動軸304を回転させる。X方向駆動軸304が回転すると、液滴吐出ヘッド301はX軸方向に移動する。

Y方向ガイド軸305は、基台309に対して動かないように固定されている。ステージ307は、Y方向駆動モータ303を備えている。Y方向駆動モータ303はステッピングモータ等であり、制御装置CONTからY方向の駆動信号が供給されると、ステージ307をY方向に移動する。

## 【0035】

制御装置CONTは、液滴吐出ヘッド301に液滴の吐出制御用の電圧を供給する。また、X方向駆動モータ302に液滴吐出ヘッド301のX方向の移動を制御する駆動パルス信号を、Y方向駆動モータ303にステージ307のY方向の移動を制御する駆動パルス信号を供給する。

クリーニング機構308は、液滴吐出ヘッド301をクリーニングするものである。クリーニング機構308には、図示しないY方向の駆動モータが備えられている。このY方向の駆動モータの駆動により、クリーニング機構は、Y方向ガイド軸305に沿って移動する。クリーニング機構308の移動も制御装置CONTにより制御される。

ヒータ315は、ここではランプアニールにより基板Pを熱処理する手段であり、基板P上に塗布された液体材料に含まれる溶媒の蒸発及び乾燥を行う。このヒータ315の電源の投入及び遮断も制御装置CONTにより制御される。

## 【0036】

液滴吐出装置IJは、液滴吐出ヘッド301と基板Pを支持するステージ307とを相対的に走査しつつ基板Pに対して液滴を吐出する。ここで、以下の説明において、X方向を走査方向、X方向と直交するY方向を非走査方向とする。

したがって、液滴吐出ヘッド301の吐出ノズルは、非走査方向であるY方向に一定間

10

20

30

40

50

隔で並んで設けられている。なお、図5では、液滴吐出ヘッド301は、基板Pの進行方向に対し直角に配置されているが、液滴吐出ヘッド301の角度を調整し、基板Pの進行方向に対して交差させるようにしてもよい。このようにすれば、液滴吐出ヘッド301の角度を調整することで、ノズル間のピッチを調節することが出来る。また、基板Pとノズル面との距離を任意に調節することが出来るようにしてもよい。

#### 【0037】

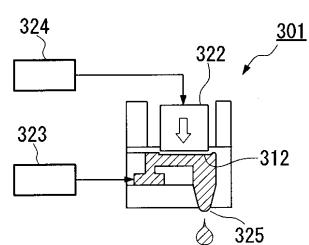

図6は、液滴吐出ヘッド301の断面図である。

液滴吐出ヘッド301には、液体材料(配線用インク等)を収容する液体室321に隣接してピエゾ素子322が設置されている。液体室321には、液体材料を収容する材料タンクを含む液体材料供給系323を介して液体材料が供給される。

10

ピエゾ素子322は駆動回路324に接続されており、この駆動回路324を介してピエゾ素子322に電圧を印加し、ピエゾ素子322を変形させることにより、液体室321が変形し、ノズル325から液体材料が吐出される。

この場合、印加電圧の値を変化させることにより、ピエゾ素子322の歪み量が制御される。また、印加電圧の周波数を変化させることにより、ピエゾ素子322の歪み速度が制御される。ピエゾ方式による液滴吐出は材料に熱を加えないため、材料の組成に影響を与えるにくいという利点を有する。

#### 【0038】

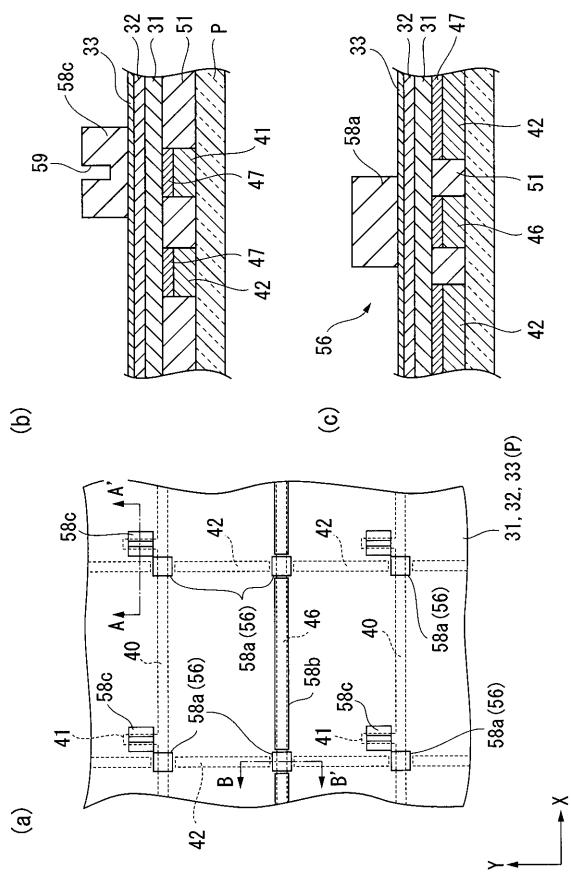

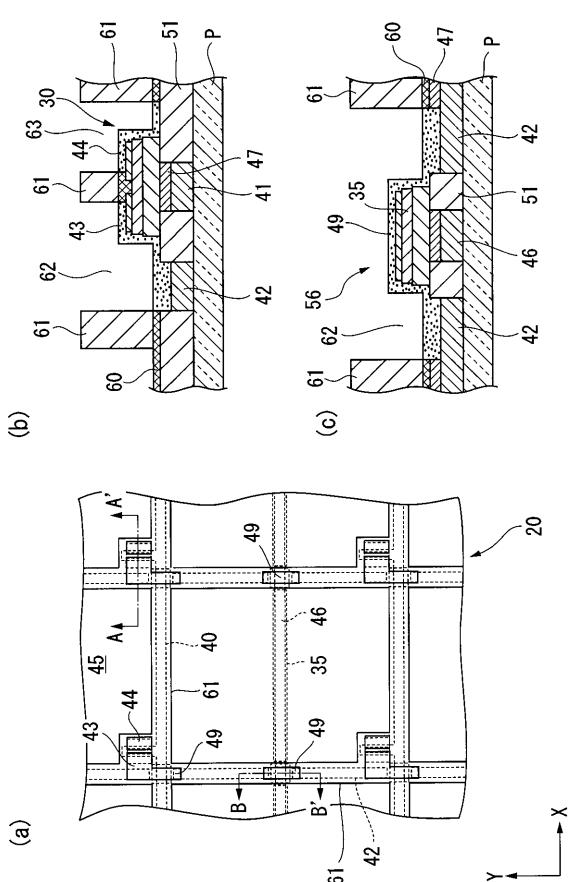

(第2工程：積層部形成)

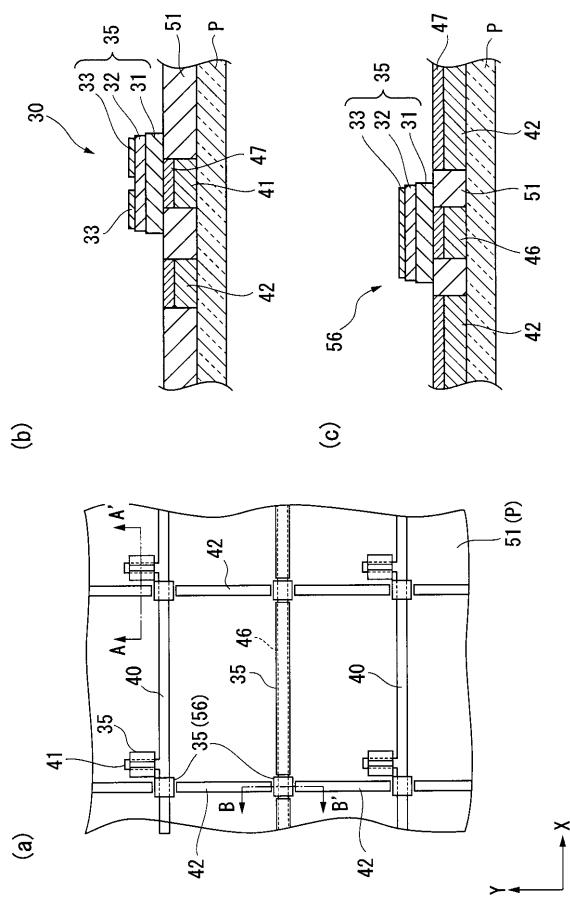

図7～図10は、第2工程である積層部形成工程を説明する図である。なお、図7(b)～図10(b)は、それぞれ図7(a)～図10(a)におけるA-A'線に沿う断面図であり、図8(c)～図10(c)は、それぞれ図8(a)～図10(a)におけるB-B'線に沿う断面図である。

20

第2工程では、バンク51及び格子パターンの配線からなる層上の所定位置に絶縁膜31と半導体膜(コンタクト層33、活性層32)からなる積層部35を形成する。

まず、プラズマCVD法により、基板P上の全面に対して、絶縁膜31、活性層32、コンタクト層33の連続成膜を行う。具体的には、図7に示すように、絶縁膜31として窒化シリコン膜、活性層32としてアモルファスシリコン膜、コンタクト層33としてn<sup>+</sup>型シリコン膜を原料ガスやプラズマ条件を変化させることにより連続して形成する。

#### 【0039】

30

次いで、図8に示すように、フォトリソグラフィ法を用いて、所定位置にレジスト58(58a～58c)を配置する。所定位置とは、図8(a)に示すように、ゲート配線40とソース配線42の交差部56上、ゲート電極41上、及び容量線46上である。

なお、交差部56上に配置するレジスト58aと容量線46上に配置するレジスト58bとは、接触しなように形成される。また、ゲート電極41上に配置するレジスト58cには、ハーフ露光を行うことにより、図8(b)に示すように、溝59を形成する。

#### 【0040】

次いで、基板Pの全面に対してエッティング処理を施して、コンタクト層33及び活性層32を除去する。更に、エッティング処理を施して、絶縁膜31を除去する。

これにより、図9に示すように、レジスト58(58a～58c)を配置した所定位置以外の領域から、コンタクト層33、活性層32、絶縁膜31が取り除かれる。一方、レジスト58が配置された所定位置には、絶縁膜31と半導体膜(コンタクト層33、活性層32)からなる積層部35が形成される。

40

なお、ゲート電極41上に形成される積層部35では、レジスト58cにハーフ露光を行って溝59を形成しておいたので、エッティング前に再度現像することにより溝が貫通する。図9(b)示すように、溝59に対応するコンタクト層33が除去され、2つに分断された状態に形成される。これにより、ゲート電極41上に活性層32及びコンタクト層33からなるスイッチング素子としてTFT30が形成される。

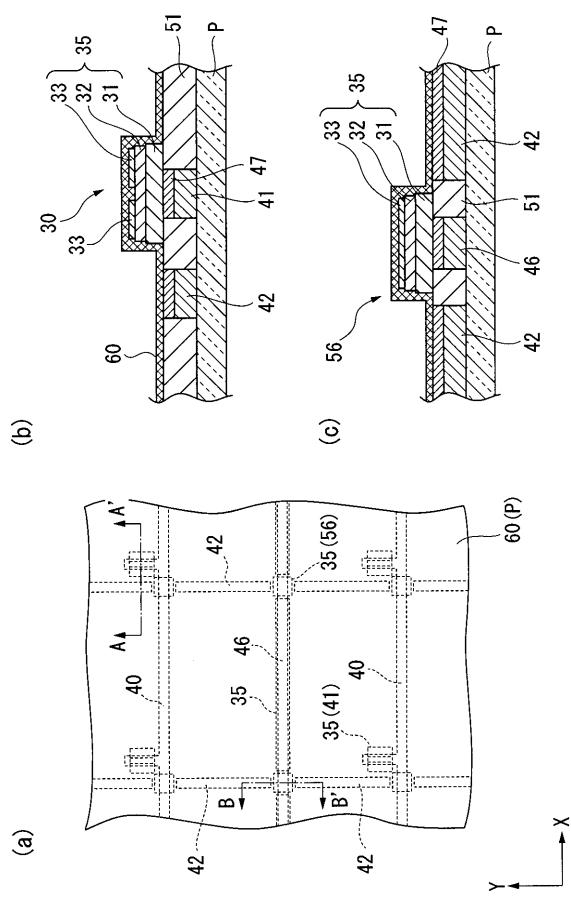

#### 【0041】

そして、図10に示すように、コンタクト層33を保護する保護膜60として、窒化シ

50

リコン膜を基板 P の全面に成膜する。

このようにして、積層部 35 の形成が完了する。

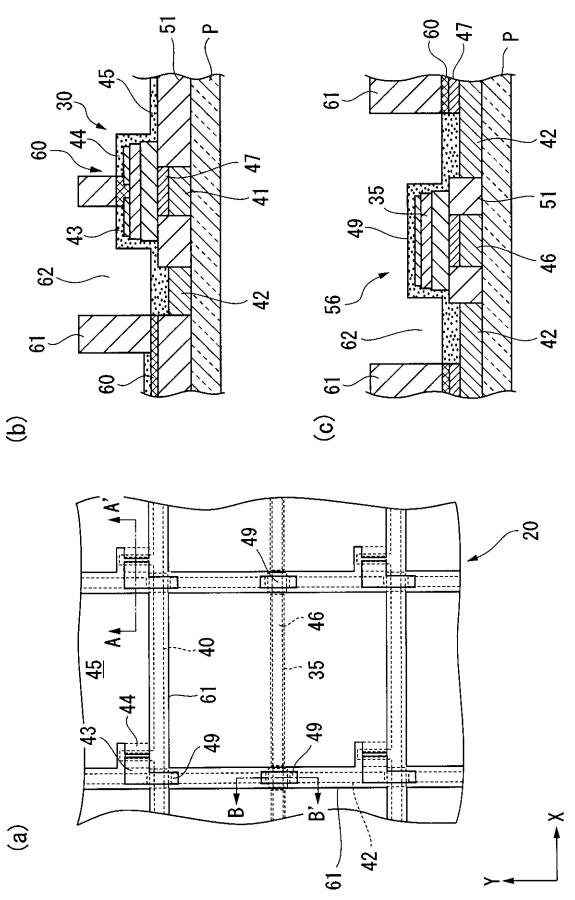

#### 【0042】

##### (第3工程)

図11～図14は、第3工程である画素電極45等の形成工程を説明する図である。なお、図11(b)～図14(b)は、それぞれ図11(a)～図14(a)におけるA-A'線に沿う断面図であり、図11(c)～図14(c)は、それぞれ図11(a)～図14(a)におけるB-B'線に沿う断面図である。

第3工程では、ソース電極43、ドレイン電極44、導電層49及び画素電極45を形成する。

ソース電極43、ドレイン電極44、導電層49は、ゲート配線40やソース配線42を形成したのと同じ材料によって形成することができる。画素電極45は、透明性が必要であることから、ITO(Indium Tin Oxide: インジウムスズ酸化物)等の透光性材料によって形成することが望ましい。これらの形成には、第1工程と同様に、液滴吐出法が用いられる。

#### 【0043】

まず、ゲート配線40及びソース配線42等を覆うようにバンク61を形成する。このバンク61は、液滴吐出法により形成される。すなわち、前述した液滴吐出装置IJによって、バンク形成材料を含むバンク形成用インク(機能液)を基板P上に直接吐出・配置し、これを乾燥処理、焼成処理してバンク61とする。これにより、図11に示すように、略格子状のバンク61が形成される。なお、ソース配線42とゲート配線40、及びソース配線42容量線46との交差部56には開口部62が形成され、TFT30のドレイン領域に対応する位置には開口部63が形成される。

また、開口部62, 63は、図11(b)に示すように、ゲート電極41上に形成した積層部35(TFT30)の一部が露出するように形成される。すなわち、バンク61が積層部35(TFT30)をX方向に2分割するように形成される。

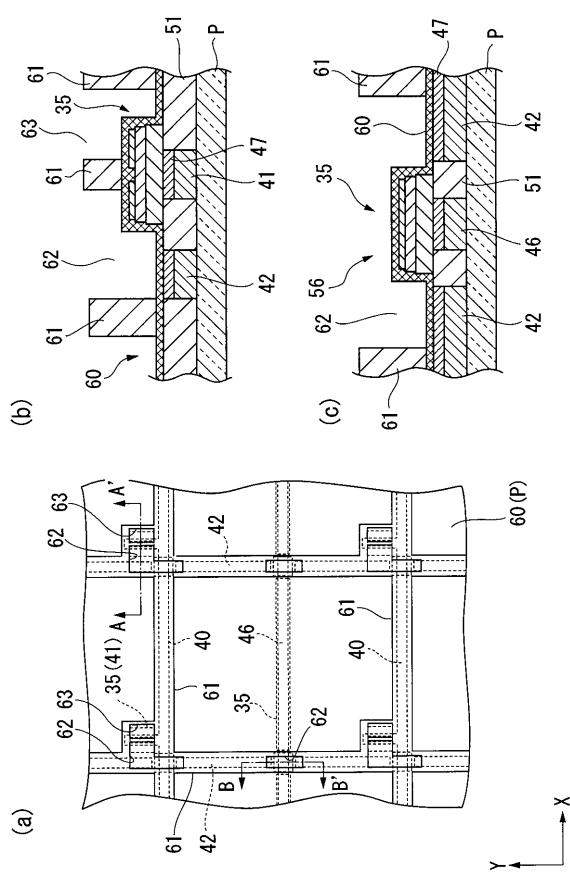

#### 【0044】

このバンク61は、インクの着弾径で描画されるため、フォトプロセスを用いた場合(例えばゲート配線形成用バンク51)よりも粗いパターンになる。しかし、画素電極45やソース電極43、ドレイン電極44を形成する場合には、ゲート配線40を形成する場合のように微細構造をとらなくてもよいため、インクの着弾径と同程度の幅(20μm～30μmの幅)で描画することができる。しかし、バンク61の幅があまりにも広くなりすぎると開口率の点で問題があるため、バンク形成用インクは、下地の基板に対して接触角の大きなものを用いることが望ましい。また、耐熱性及び透明性を高めるために、ポリシラザン等の無機質の材料によって形成することが望ましい。

#### 【0045】

バンク61の材料としては、例えば、バンク51と同様に、アクリル樹脂、ポリイミド樹脂、オレフィン樹脂、メラミン樹脂などの高分子材料を用いることができる。この際、素材自体に撥液成分(フッ素基等)を充填しておくことが望ましい。このように、バンク61を撥液性の材料によって形成することで、バンク61を撥液化するための後処理が不要になる。特に、本実施形態のアクティブマトリクス基板のように複数の配線層が積層される場合には、バンクの撥液化のために基板全面にCF<sub>4</sub>プラズマ処理等を行なうと、下地の材料によっては、バンクの表面だけでなく、バンク間に露出した部分(バンクによって区画された領域)の表面も撥液化されてしまうため、インクを吐出したときに濡れ性が悪くなり、不均一な膜になってしまい虞がある。一方、バンク自体を撥液性の材料によって形成すれば、このような問題はなくなるため、下地の状態によらずに均一性の良い膜を形成することができる。

#### 【0046】

バンク61により形成される開口部62は、分断されたソース配線42を連結する導電層49又はソース電極43の形成位置に対応しており、バンク61に形成される開口部6

3は、ドレイン電極44の形成位置に対応している。また、それ以外の部分でバンク61により取り囲まれた領域は、画素電極45の形成位置に対応している。すなわち、バンク61を用いて保護膜60を開口し、その開口部62, 63に対応する開口部内及びバンク61により取り囲まれた領域に対応する開口部に導電性材料を配置することにより、分断されたソース配線42を連結する導電層49、ソース電極43、ドレイン電極44、画素電極45が形成される。

#### 【0047】

次いで、図12に示すように、開口部62, 63内に位置する保護膜60をレーザ等により除去し、コンタクト層33を露出させる。なお、格子パターンの配線上に形成した金属保護膜47も取り除かれる。

10

#### 【0048】

次いで、前述した液滴吐出装置IJによって、ソース電極43やドレイン電極44等の電極材料を含む電極用インクをバンク61の開口部62, 63内に吐出・配置する。電極用インクは、ゲート配線40等を形成するために用いた配線用インクと同様のものを用いることができる。基板Pに電極用インクを吐出した後には、分散媒の除去のため、必要に応じて乾燥処理、焼成処理を行う。乾燥・焼成処理により、導電性微粒子間の電気的接触が確保され、導電性膜に変換される。

このようにして、基板P上には、図13に示すように、分断されたソース配線42を連結する導電層49、ソース電極43、ドレイン電極44が形成される。

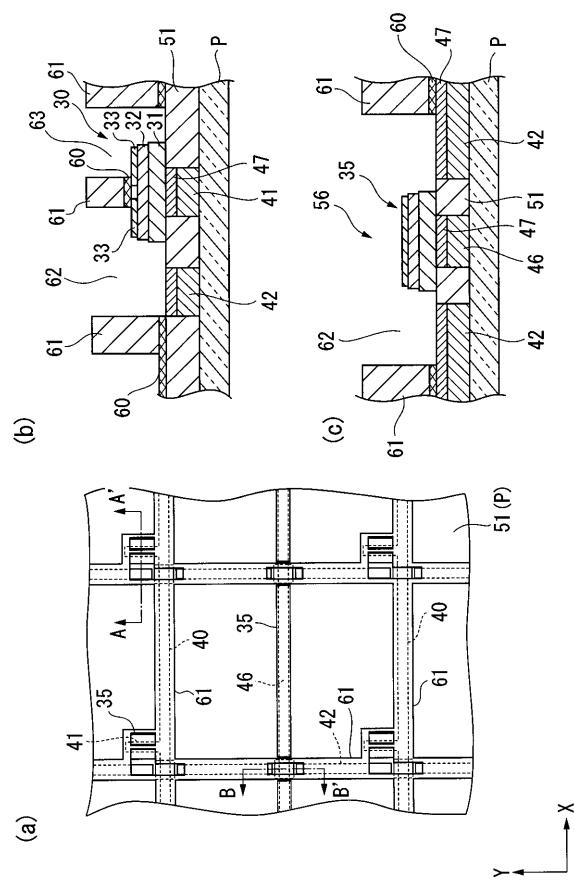

#### 【0049】

20

次いで、バンク61において画素電極45とドレイン電極44との境界に位置する部分をレーザ等により除去し、画素電極45の電極材料を含む画素電極用インクをバンク61により取り囲まれた領域内に吐出・配置する。画素電極用インクは、ITO等の導電性微粒子を分散媒に分散させた分散液である。基板Pに画素電極用インクを吐出した後には、分散媒の除去のため、必要に応じて乾燥処理、焼成処理を行う。乾燥・焼成処理により、導電性微粒子間の電気的接触が確保され、導電性膜に変換される。

このようにして、基板P上には、図14に示すように、ドレイン電極44と導通する画素電極45が形成される。

#### 【0050】

30

以上の工程を経ることにより、アクティブマトリックス基板20が製造される。

このように、本実施形態では、アクティブマトリックス基板20を、基板P上に格子パターンの配線を形成する第1工程と、積層部35を形成する第2工程と、画素電極45等を形成する第3工程とによって製造したので、ドライプロセスとフォトリソエッチングを組み合わせた処理を減らすことができる。すなわち、ゲート配線40及びソース配線42を同時に形成するようにしたので、ドライプロセスとフォトリソエッチングを組み合わせた処理を1回減らすことができる。

また、第3工程において、バンク61の形成を液滴吐出法により行なっているので、更にドライプロセスとフォトリソエッチングを組み合わせた処理を減らすことができる。

#### 【0051】

40

また、容量線46上に形成される積層部35(絶縁膜31, 活性層32, コンタクト層33)が交差部56上に形成される積層部35と接触しないように分断されて形成されることから、ソース配線42を流れる電流が容量線46上の積層部35に流れ込んでしまう不都合を回避することができる。

すなわち、積層部35を形成する層のうち、コンタクト層33は導電性膜であり、そして、交差部56上の積層部35(コンタクト層33)上には、ソース配線42を連結する導電部49が形成される。このため、ソース配線42を流れる電流は、コンタクト層33にも流れる。したがって、容量線46上の積層部35と交差部56上の積層部35と接触していると、上述したように、ソース配線42を流れる電流が容量線46上の積層部35に流れ込んでしまうという現象が発生してしまう。

したがって、本発明のアクティブマトリックス基板20によれば、このような不都合が

50

回避されるので、所望の性能を発揮することが可能となる。

#### 【0052】

なお、本実施形態においては、ソース配線42を交差部56において分割する構成について説明したが、ゲート配線40や容量線46を交差部56において分割する構成とすることも勿論可能である。ただし、容量線46はソース配線42に比べて表示への影響が大きいため、高い表示品質が求められる場合には、ソース配線42を分割する構造を探ることが望ましい。

また、本実施形態では、アクティブマトリクス基板の好適な一形態例について説明したが、その構成部材の形状や組み合わせは係る形態に限定されるものではない。例えば、図図9に代えて、積層部35の形状・配置を図15のようなものにすることもできる。この場合、ソース領域とソース配線43とが近接して配置されるため、ソース電極43の形成面積を小さくし、より性能の高いアクティブマトリクス基板を製造することができる。10

#### 【0053】

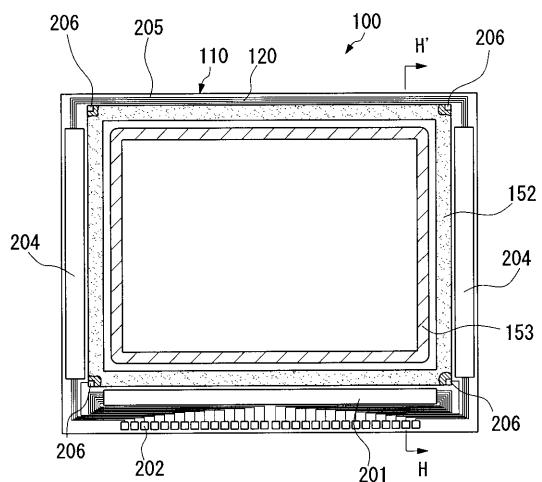

##### <電気光学装置>

次に、アクティブマトリックス基板20を用いた電気光学装置の一例である液晶表示装置100について説明する。

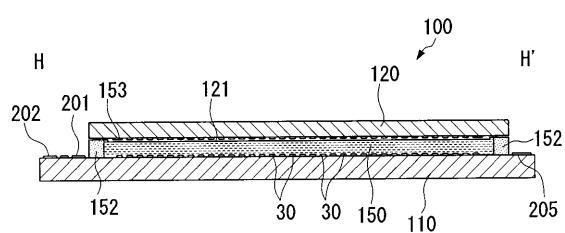

図16は、液晶表示装置100を対向基板側から見た平面図であり、図17は、図16のH-H'線に沿う断面図である。

なお、以下の説明に用いた各図においては、各層や各部材を図面上で認識可能な程度の大きさとするため、各層や各部材毎に縮尺を異ならせてある。20

#### 【0054】

図16及び図17において、液晶表示装置（電気光学装置）100は、アクティブマトリックス基板20を含むTFTアレイ基板110と対向基板120とが光硬化性の封止材であるシール材152によって貼り合わされ、このシール材152によって区画された領域内に液晶150が封入、保持されている。シール材152は、基板面内の領域において閉ざされた枠状に形成されており、液晶注入口を備えず、封止材にて封止された痕跡がない構成となっている。

#### 【0055】

シール材152の形成領域の内側の領域には、遮光性材料からなる周辺見切り153が形成されている。シール材152の外側の領域には、データ線駆動回路201及び実装端子202がTFTアレイ基板110の一辺に沿って形成されており、この一辺に隣接する2辺に沿って走査線駆動回路204が形成されている。TFTアレイ基板110の残る一辺には、画像表示領域の両側に設けられた走査線駆動回路204の間を接続するための複数の配線205が設けられている。また、対向基板120のコーナー部の少なくとも1箇所においては、TFTアレイ基板110と対向基板120との間で電気的導通をとるための基板間導通材206が配設されている。30

なお、データ線駆動回路201及び走査線駆動回路204をTFTアレイ基板110の上に形成する代わりに、例えば、駆動用LSIが実装されたTAB（Tape Automated Bonding）基板とTFTアレイ基板110の周辺部に形成された端子群とを異方性導電膜を介して電気的及び機械的に接続するようにしてもよい。40

なお、液晶表示装置100においては、使用する液晶150の種類、すなわち、TN（Twisted Nematic）モード、C-TN法、VA方式、IPS方式モード等の動作モードや、ノーマリホワイトモード／ノーマリブラックモードの別に応じて、位相差板、偏光板等が所定の向きに配置されるが、ここでは図示を省略する。

また、液晶表示装置100をカラー表示用として構成する場合には、対向基板120において、TFTアレイ基板110の後述する各画素電極に対向する領域に、例えば、赤（R）、緑（G）、青（B）のカラーフィルタをその保護膜とともに形成する。

#### 【0056】

この液晶表示装置100においては、アクティブマトリックス基板20が前述の方法により製造されているので、高品質な表示が可能な表示装置となる。50

## 【0057】

なお、本実施形態では、液晶表示装置の配線構造を形成する方法として本発明の膜パターンの形成方法を適用したが、本発明は必ずしもこれに限定されず、例えばアクティブマトリックス基板又は対向基板にカラーフィルタを形成する場合に本発明を適用することもできる。

また、前記のアクティブマトリックス基板は、液晶表示装置以外の他の電気光学装置、例えば有機EL（エレクトロルミネッセンス）表示装置等にも応用が可能である。有機EL表示装置は、蛍光性の無機および有機化合物を含む薄膜を、陰極と陽極とで挟んだ構成を有し、前記薄膜に電子および正孔（ホール）を注入して励起させることにより励起子（エキシトン）を生成させ、このエキシトンが再結合する際の光の放出（蛍光・熒光）を利用して発光させる素子である。そして、上記のTFT30を有する基板上に、有機EL表示素子に用いられる蛍光性材料のうち、赤、緑および青色の各発光色を呈する材料すなわち発光層形成材料及び正孔注入／電子輸送層を形成する材料をインクとし、各々をパテーニングすることで、自発光フルカラーELデバイスを製造することができる。本発明における電気光学装置の範囲には、このような有機ELデバイスも含まれるものとする。なお、有機EL表示装置においては、正孔注入／輸送層形成材料や発光層形成材料を形成する方法として本発明の膜パターンの形成方法を適用することも可能である。

更に、アクティブマトリックス基板20は、PDP（プラズマディスプレイパネル）や、基板上に形成された小面積の薄膜に膜面に平行に電流を流すことにより、電子放出が生ずる現象を利用する表面伝導型電子放出素子等にも適用可能である。

## 【0058】

## &lt;電子機器&gt;

次に、本発明の電子機器の具体例について説明する。

図18(a)は、携帯電話の一例を示した斜視図である。図18(a)において、600は携帯電話本体を示し、601は上記実施形態の液晶表示装置100を備えた表示部を示している。

図18(b)は、ワープロ、パソコンなどの携帯型情報処理装置の一例を示した斜視図である。図18(b)において、700は情報処理装置、701はキーボードなどの入力部、703は情報処理本体、702は上記実施形態の液晶表示装置100を備えた表示部を示している。

図18(c)は、腕時計型電子機器の一例を示した斜視図である。図18(c)において、800は時計本体を示し、801は上記実施形態の液晶表示装置100を備えた表示部を示している。

このように、図18(a)～(c)に示す電子機器は、上記実施形態の液晶表示装置100を備えたものであるので、高い品質や性能が得られる。

また、テレビやモニター等の大型液晶パネルにおいても本実施形態を用いることができる。

## 【0059】

なお、本実施形態の電子機器は液晶表示装置100を備えるものとしたが、有機エレクトロルミネッセンス表示装置、プラズマ型表示装置等、他の電気光学装置を備えた電子機器とすることもできる。

## 【0060】

以上、添付図面を参照しながら本発明についての好適な実施の形態例について説明したが、本発明は係る例に限定されないことは言うまでもない。上述した例において示した各構成部材の諸形状や組み合わせ等は一例であって、本発明の主旨から逸脱しない範囲において設計要求等に基づき種々変更可能である。

## 【図面の簡単な説明】

## 【0061】

【図1】アクティブマトリックス基板の一部拡大図である。

【図2】アクティブマトリックス基板の等価回路図である。

10

20

30

40

50

【図3】アクティブマトリックス基板を製造する手順を示す図である。

【図4】図4に続く手順を示す図である。

【図5】液滴吐出装置の概略斜視図である。

【図6】液滴吐出ヘッドの断面図である。

【図7】図5に続く手順を示す図である。

【図8】図8に続く手順を示す図である。

【図9】図9に続く手順を示す図である。

【図10】図10に続く手順を示す図である。

【図11】図11に続く手順を示す図である。

【図12】図12に続く手順を示す図である。

【図13】図13に続く手順を示す図である。

【図14】図14に続く手順を示す図である。

【図15】アクティブマトリックス基板の他の形態例を示す模式図である。

【図16】液晶表示装置を対向基板の側から見た平面図である。

【図17】液晶表示装置の断面図である。

【図18】電子機器の具体例を示す図である。

#### 【符号の説明】

##### 【0062】

P...基板、20...アクティブマトリックス基板、30...TFT(薄膜トランジスタ)、31...絶縁膜、32...活性層(半導体膜)、33...コンタクト層(半導体膜)、35...積層部、40...ゲート配線、42...ソース配線、44...ドレイン電極、45...画素電極、46...容量線、49...導電層、56...交差部、61...バンク、100...液晶表示装置、600...携帯電話本体(電子機器)、700...情報処理装置(電子機器)、800...時計本体(電子機器)

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

【図17】

---

フロントページの続き

(72)発明者 守屋 克之

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 小野 博之

(56)参考文献 特開2005-005694 (JP, A)

特開平10-048651 (JP, A)

特開平04-280231 (JP, A)

特開2003-208111 (JP, A)

特開2002-268084 (JP, A)

特開2005-013985 (JP, A)

特開2004-337779 (JP, A)

国際公開第97/013177 (WO, A1)

特開2003-318192 (JP, A)

特開2003-318131 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |             |

|--------|-------------|

| G 09 F | 9 / 0 0     |

| G 02 F | 1 / 1 3 4 3 |

| G 02 F | 1 / 1 3 6 8 |